# Physics-Based SPICE Model of a-InGaZnO Thin-Film Transistor Using Verilog-A

Yong Woo Jeon, Inseok Hur, Yongsik Kim, Minkyung Bae, Hyun Kwang Jung, Dongsik Kong, Woojoon Kim, Jaehyeong Kim, Jaeman Jang, Dong Myong Kim, and Dae Hwan Kim

Abstract—In this work, we report the physics-based SPICE model of amorphous oxide semiconductor (AOS) thin-film transistors (TFTs) and demonstrate the SPICE simulation of amorphous InGaZnO (a-IGZO) TFT inverter by using Verilog-A. As key physical parameter, subgap density-of-states (DOS) is extracted and used for calculating the electric potential, carrier density, and mobility along the depth direction of active thin-film. It is confirmed that the proposed DOS-based SPICE model can successfully voltage reproduce the transfer characteristic of a-IGZO inverter as well as the measured I-V characteristics of a-IGZO TFTs within the average error of 6% at  $V_{DD}$ =20 V.

*Index Terms*—Amorphous InGaZnO (a-IGZO), SPICE, Verilog-A, density-of-states (DOS), thin-film transistors (TFTs)

# I. INTRODUCTION

As a representative amorphous oxide semiconductor (AOS) material, amorphous InGaZnO (a-IGZO) has been studied and developed intensively as an active layer of thin-film transistors (TFTs) for switching/driving devices in flexible e-paper, transparent/lightweight display backplanes for active-matrix liquid crystal display (AMLCD) and/or active-matrix organic light-emitting diode display (AMOLED) [1, 2], stackable logic circuitry

[3], and 3-D memories [4]. In order to design and integrate various innovative systems using AOS TFTs, the circuit simulation with physics-based and process-controlled parameters, not fitting parameters, is indispensible for process/structure optimization. However, physical parameter-based SPICE simulations of oxide TFTs have been rarely reported.

In this work, we report the physics-based SPICE model of AOS TFTs and demonstrate the SPICE simulation of a-IGZO TFT inverter by incorporating the proposed model into HSPICE via Verilog-A. As key physical parameter, subgap density-of-states (DOS) is experimentally extracted and used for calculating the electric potential, carrier density, and mobility along the depth direction of active thin-film. Then, the DC *I-V* characteristics is calculated by using the double integral with the surface potential ( $\phi_{\rm S}$ ) and back potential ( $\phi_{\rm B}$ ) as the function of  $V_{\rm GS}$  (gate-to-source voltage) and  $V_{\rm DS}$  (drain-to-source voltage). The simulated voltage transfer characteristic (VTC) of a-IGZO TFT inverter agrees well with the measured one, within the error ratio of 6%.

# **II. DOS-BASED MODEL**

The acceptor-like subgap DOS  $(g_A(E) \text{ [eV}^{-1}\text{cm}^{-3}\text{]})$  of AOS thin-films can be modeled as

$$g_A(E) = N_{TA} \times \exp\left(\frac{E - E_C}{kT_{TA}}\right) + N_{DA} \times \exp\left(\frac{E - E_C}{kT_{DA}}\right)$$

(1)

In addition, the donor-like DOS  $(g_D(E) [eV^{-1}cm^{-3}])$  is

Manuscript received Apr. 29, 2011; revised Jul. 6, 2011.

School of Electrical Engineering, Kookmin University, Korea E-mail : drlife@kookmin.ac.kr

Here, the subscript of TA/DA means the acceptor-like tail/deep state, respectively.

presumably modeled as [5]

$$g_D(E) = N_{TD} \times \exp\left(\frac{E_V - E}{kT_{TD}}\right) + N_{DD} \times \exp\left(\frac{E_V - E}{kT_{DD}}\right)$$

(2)

Here, the subscript of TD/DD means the donor-like tail/deep state, respectively. Then, the flat band voltage  $(V_{\rm FB})$  and  $E_{\rm FB}$  (defined as the energy difference between Fermi-level  $E_{\rm F}$  and conduction band minimum  $(E_{\rm C})$  at  $V_{\rm GS}=V_{\rm FB}$  condition) are calculated as following equations:

$$V_{FB} = \phi_{Gate} - \phi_{AOS} - \frac{Q_{ox}}{C_{ox}}$$

$$\phi_{Gate} - \phi_{AOS} = (\chi_{Gate} - \chi_{AOS}) - \frac{E_{FB}}{q}$$

(3)

$$q \Big[ n_{loc}(E_F) - n_{free}(E_F) + N_D^+ \Big] = 0$$

(4)

Here,  $\phi$ ,  $\chi$ ,  $Q_{\text{ox}}$ ,  $C_{\text{ox}} = \varepsilon_{\text{ox}}/T_{\text{ox}}$ ,  $T_{\text{ox}}$ , q,  $n_{\text{loc}}$ ,  $n_{\text{free}}$ , and  $N_{\text{D}}^+$ are the work function, the electron affinity, the charge density per unit area in gate oxide, the gate oxide capacitance per unit area, the thickness of gate oxide, the charge of single electron, the localized charge density due to trapped charge in subgap DOS, the free electron density, and the donor doping concentration, respectively. In this work,  $Q_{\text{ox}}$  is postulated to be negligible and  $E_{\text{FB}}$ acts as a reference energy level in the calculation of  $V_{\text{GS}}$ modulated electric potential  $\phi(x, V_{\text{CH}}(y)) = \phi(x, y)$  at a given location as shown in Fig. 1(a).

Then,  $n_{\text{free}}$  and  $n_{\text{loc}}$  can be calculated as follows:

$$n_{free}(x, V_{CH}(y)) = \frac{2}{\sqrt{\pi}} N_C F_{1/2}(\eta_F)$$

(5)

$$F_{1/2}(\eta_F) = \int_0^\infty \frac{\sqrt{\eta}}{1 + \exp(\eta - \eta_F)} d\eta$$

(6)

$$\eta_F(x, V_{CH}(y)) = \frac{q\phi(x, y) - qV_{CH}(y) - E_{FB}}{kT}$$

(7)

$$n_{loc}(x, V_{CH}(y)) = \int_{E_{V}}^{E_{C}} g_{D}(E)[1 - f(E)]dE - \int_{E_{V}}^{E_{C}} g_{A}(E)f(E)dE$$

(8)

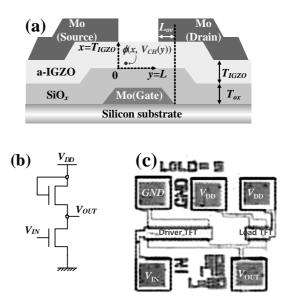

**Fig. 1.** (a) The cross-section of a-IGZO TFT with an inverted staggered bottom gate structure and the definition of local potential  $\phi(x, V_{CH}(y))$ , (b) The schematic circuit diagram and (c) The top view of integrated a-IGZO TFT-based inverter.

where  $N_{\rm C}$  and f(E) are the effective DOS in conduction band and the Fermi-Dirac distribution function, respectively. In addition, the potential difference along the channel length direction, as denoted by  $V_{CH}(y)$ , describes the electron quasi Fermi-level  $E_{\rm Fn}$  lowering by  $qV_{\rm CH}(y)$  due to applied  $V_{\rm DS}$ . Therefore, it is given that  $V_{\rm CH}(y=0)=V_{\rm S}$  (near source region) and  $V_{\rm CH}(y=L)=V_{\rm D}$ (near drain region). Here, if the surface potential  $\phi_{\rm S}$  is defined as  $\phi(x=0, V_{CH}(y))=\phi(x=0, y), V_{CH}(y)$  plays the role of increasing  $\phi_s$  from y=0 to L. However,  $E_{Fn}$  is also lowered by  $qV_{CH}(y)$ , consequently,  $n_{\text{free}}$  decreases from y=0 to L, as shown in Eqs. (5-7). In addition, it is noticeable that even though  $V_{CH}(y)$  is not given as the exact function of y, the double integrals in Eq. (13) can be calculated with a given  $V_{\rm DS}$ . Meanwhile, the 2-D Poisson's equation can be solved, as denoted by Eq. (9), with the charge density  $\rho$  which is described with DOS parameters and  $\varepsilon_{AOS}$ =the dielectric constant of AOS thinfilm as denoted by Eq. (9). Also, the free and localized charge density per unit area ( $Q_{\text{free}}$  and  $Q_{\text{loc}}$ ) at a given  $y=y_0$  can be calculated from Eqs. (10-11) with  $T_{AOS}$ =the thickness of AOS thin-film. Finally, the self-consistent pair of  $\phi_{\rm B}(\phi_{\rm S})$  and  $V_{\rm GS}(\phi_{\rm S})$  can be extracted with the surface electric field  $E_{AOS}(x=0)$  by Eq. (12) and the current  $I_{\rm DS}$  is given by using the double integrals as Eq. (13):

$$\frac{\partial^2 \phi(x, y = y_0)}{\partial x^2} = \frac{-\rho}{\varepsilon_{AOS}}$$

$$= \frac{q}{\varepsilon_{AOS}} \Big[ n_{loc}(x, V_{CH}(y)) + n_{free}(x, V_{CH}(y)) - N_D^+ \Big]$$

(9)

$$Q_{free}(x, V_{CH}(y))$$

$$= q \int_{x=x}^{x=T_{AOS}} n_{free}(x, V_{CH}(y)) dx$$

(10)

$$Q_{loc}(x, V_{CH}(y)) = q \int_{x=x}^{x=T_{AOS}} n_{loc}(x, V_{CH}(y)) dx$$

(11)

$$V_{GS} = V_{FB} + \phi_{s}\Big|_{y=y_{0}} + \frac{Q_{loc}(x=0) + Q_{free}(x=0) + qN_{D}^{+} \times T_{AOS}}{C_{ox}}\Big|_{y=y_{0}}$$

$$= V_{FB} + \phi_{s}\Big|_{y=y_{0}} + \frac{\varepsilon_{AOS} \times E_{AOS}(x=0)}{C_{ox}}\Big|_{y=y_{0}}$$

(12)

$$I_{DS} = q \mu_{Band} \frac{W}{L} \int_{V_{S}}^{V_{S}+V_{D}} \int_{\phi_{\theta}}^{\phi_{\theta}} \frac{Q_{free}(\phi, V_{CH}(y))}{Q_{free}(\phi, V_{CH}(y)) + Q_{loc}(\phi, V_{CH}(y))} \times \frac{n_{free}(\phi, V_{CH}(y))}{E_{AOS}(\phi, V_{CH}(y))} d\phi dV_{CH}(y)$$

(13)

where  $\rho$ ,  $\mu_{\text{Band}}$ , W, and L are the charge density, the conduction band mobility, the channel width, and the channel length, respectively. The detailed process of the derivation of (13) was given in [5].

# **III. SPICE IMPLEMENTATION**

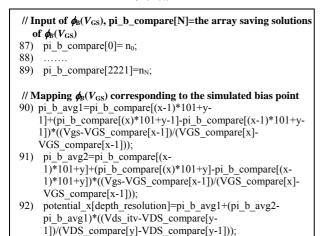

In order to implement the DOS-based model into SPICE via Verilog-A, the core process is calculating  $\phi(x, y=y_0)$  [at a given lateral location  $y=y_0$ ] from  $g_A(E)$  and  $g_D(E)$  under a specific  $V_{GS}$  and  $V_{DS}$ , where  $0 \le x \le T_{AOS}$  and  $0 \le y_0 \le L$ . Once the *fundamental physical parameters* such as  $\mu_{Band}$ ,  $N_C$ ,  $N_D^+$ ,  $g_A(E)$  and  $g_D(E)$  are known, we can divide the AOS thin-film into infinitesimal sectors  $\Delta x$ along the vertical direction and assume the charge density  $\rho$  to be constant within a single sector. In this work, the AOS thin-film is divided into 100 sectors. Then, under specific  $V_{GS}$  and  $V_{DS}$ , the calculation of  $\phi(x, y=y_0)$  can be conducted via 1-D field solver from  $x=T_{AOS}$ [back interface] to x=0 [front interface] by assuming the back potential  $\phi_B$  [defined as  $\phi(x=T_{AOS}, V_{CH}(y))=\phi(x=T_{AOS}, y=T_{AOS})$  *y*)] as an appropriate value. The detailed procedure of 1-D field solver was given in Fig. 3 in [5] and the related description therein.

Under a specific  $V_{GS}$  and *fundamental physical parameters*, the  $\phi_S$  is acquired with the assumed value of

Table 1. Module declaration and parameter definition

| Table    | Table 1. Module declaration and parameter definition         |  |  |

|----------|--------------------------------------------------------------|--|--|

| //**     | <sup>5</sup> Module declaration and Input / Output terminals |  |  |

| 1)       | `include "discipline.h"                                      |  |  |

| 2)       | module TFT(D, G, S);                                         |  |  |

| 3)       | inout D, G, S;                                               |  |  |

| 4)       | electrical D, G, S;                                          |  |  |

| //**     | Parameters define                                            |  |  |

| 5)       | parameter real PI= 3.14159;                                  |  |  |

| 6)       | parameter integer depth resolution= 100;                     |  |  |

| 7)       | parameter integer DOS_resolution=100;                        |  |  |

| // DI    |                                                              |  |  |

|          | hysical Parameters                                           |  |  |

| 8)<br>9) | parameter real tox=100e-7;<br>parameter real L=30*1e-4;      |  |  |

| 10)      | parameter real W=175*1e-4;                                   |  |  |

| 11)      | parameter real Tgizo = 50e-7;                                |  |  |

| 12)      | parameter real epsilon_gizo=11.5;                            |  |  |

| 13)      | parameter real epsilon=8.854e-14;                            |  |  |

| 14)      | parameter real band mobility=23.5;                           |  |  |

| 15)      | parameter real delta Vfb=0;                                  |  |  |

| 16)      | parameter real $Ec = 3.2$ ;                                  |  |  |

| 17)      | parameter real Nc = $6.00e18$ ;                              |  |  |

| 18)      | parameter real Nv = $1.00e16$ ;                              |  |  |

| 19)      | parameter real Nd = $5e16$ ;                                 |  |  |

| 20)      |                                                              |  |  |

| 21)      | parameter real kT=0.0259;                                    |  |  |

| 22)      | parameter real Ioff=1e-18;                                   |  |  |

| // Ac    | cceptor_like DOS parameters                                  |  |  |

| 23)      |                                                              |  |  |

| 24)      |                                                              |  |  |

| 25)      | parameter real NDA = $3e_{16}$ ;                             |  |  |

| 26)      | parameter real $kTda = 0.8$ ;                                |  |  |

| // De    | onor_like DOS parameters                                     |  |  |

| 27)      | parameter real NTD = $1e20$ ;                                |  |  |

| 28)      | parameter real kTtd = $0.06$ ;                               |  |  |

| 29)      | parameter real NDD = $1e18$ ;                                |  |  |

| 30)      | parameter real kTdd = $0.55$ ;                               |  |  |

| // Ат    | ray and local variables                                      |  |  |

| 31)      |                                                              |  |  |

| 32)      |                                                              |  |  |

| 33)      |                                                              |  |  |

| 34)      |                                                              |  |  |

| 35)      |                                                              |  |  |

| 36)      | real Rho1[0:depth_resolution-1];                             |  |  |

| 37)      | real Qfree[0:depth_resolution-1];                            |  |  |

| 38)      | real Qloc[0:depth_resolution-1];                             |  |  |

| 39)      | real VGS_compare[0:21];                                      |  |  |

| 40)      | real VDS_compare[0:100];                                     |  |  |

| 41)      | real pi_b_compare[0:2221];                                   |  |  |

| 42)      | real Cox;                                                    |  |  |

| 43)      | real eta_f,mu,xi,FDIn,FDIp,Dop_effect,E_step;                |  |  |

| 44)      | real depth,lateral,Qfreei,pi_b_avg1,pi_b_avg2,Efbo,Efb,Vfb;  |  |  |

| 45)      | real t,A,DD ;                                                |  |  |

| 46)      | real Vgd,Vgs,Vds;                                            |  |  |

| 47)      | real itv,Vds_itv;                                            |  |  |

48) integer i,x,y;

### **Table 2.** The initiation of $\phi_B(V_{GS})$

156

**Table 3.** The calculation of  $n_{\text{free}}$  and  $n_{\text{loc}}$

| //** Declaration of $E_{\rm FB}$ by using $\phi_{\rm B}(V_{\rm GS})$        |

|-----------------------------------------------------------------------------|

| 93) analog begin                                                            |

| 94) $Vgd=V(G, D);$                                                          |

| 95) Vgs=V(G, S);                                                            |

| 96) Vds=V(D, S);                                                            |

| 97) Efbo=0.2475733;                                                         |

|                                                                             |

| // Calculating <i>n</i> <sub>free</sub>                                     |

| 98) if(Vds_itv<0)                                                           |

| 99) begin                                                                   |

| 100) lateral=Ioff;                                                          |

| 101) end                                                                    |

| 102) else                                                                   |

| 103) begin                                                                  |

| 104) Efb=Efbo+Vds_itv;                                                      |

| 105) Vfb=0.3-Efb+delta_Vfb;                                                 |

| 106) for(i=depth_resolution;i>0;i=i-1)                                      |

| 107) begin                                                                  |

| 108) eta_f=(potential_x[i]-Efb-Vds_itv)/(kT);                               |

| 109) mu=pow(eta_f, $4$ )+50+33.6*eta_f*(1-0.68*exp(-                        |

| 0.17*pow(eta_f+1,2));                                                       |

| 110) $xi=3*sqrt(PI)/(4*pow(mu,(3/8)));$                                     |

| 111) FDIn=pow((exp(-eta f)+xi),-1); /*Relative error +-0.4% */              |

| 112) FDIp=pow((exp(-(eta_f-(Ec/kT)))+xi),-1); /*Relative error -<br>0.4% */ |

| 113) function_n[i-1]=2*Nc*FDIn/pow(PI,0.5); /* [1/cm3] */                   |

| 114) function_p[i-1]=2*Nv*FDIp/pow(PI,0.5); /* [1/cm3] */                   |

| 115) Dop effect=Nd;                                                         |

|                                                                             |

| // Calculating n <sub>loc</sub>                                             |

| 116) A=0;                                                                   |

| 117) DD=0;                                                                  |

| 118) for(t=0;t<=Ec;t=t+E_step)                                              |

| 119) begin                                                                  |

| 120) A=A+(NTA*exp((t-Ec)/kTta)+NDA*exp((t-                                  |

| Ec)/kTda))*(1/(1+exp((t-(Ec-Efb-                                            |

| (Vds_itv)+potential_x[i]))/kT)))*E_step;                                    |

| 121) end                                                                    |

| 122) for(t=0;t<=Ec;t=t+E_step)                                              |

| 123) begin                                                                  |

| 124) $DD=DD+(NTD*exp((-1*t)/kTtd)+NDD*exp((-1*t)/kTtd))$                    |

| 1*t)/kTdd))*(1-(1/(1+exp((t-(Ec-Efb-                                        |

| (Vds_itv)+potential_x[i]))/kT))))*E_step;                                   |

| 125) end                                                                    |

| 126) DOS[i-1]=A-DD;                                                         |

|                                                                             |

|                                                                             |

$\phi_{\rm B}$ . Then, whether the relation between  $V_{\rm GS}$  and  $\phi_{\rm S}$  is satisfied consistently with Eq. (12) or not is checked with the present values of  $V_{GS}$  and  $\phi_{B}$ . Unless it is satisfied,

**Table 4.** The calculation of  $\phi(x)$ ,  $E_{AOS}(x)$ ,  $\rho(x)$ ,  $Q_{free}$  and  $Q_{loc}$

potential\_x[i])\*(function\_n[i-1]/Efield[i-1]);

```

66)

end

```

**Table 5.** The calculation of  $I_{DS}(V_{GS}, V_{DS})$

#### . 4 . . . 1 . . . 1 . . 4 // 101

| // The current calculation |                                                                                                                                                                                                                                              |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| I <sub>DS</sub>            | $=q\mu_{load}\frac{W}{L}\int_{V_{5}}^{V_{5}+V_{0}}\int_{\phi_{1}}^{\phi_{1}}\frac{Q_{free}(\phi,V_{CH}(y))}{Q_{free}(\phi,V_{CH}(y))+Q_{loc}(\phi,V_{CH}(y))}\times\frac{n_{free}(\phi,V_{CH}(y))}{E_{AOS}(\phi,V_{CH}(y))}d\phi dV_{CH}(y)$ |  |  |

| 67)                        | for(i=depth_resolution;i>0;i=i-1)                                                                                                                                                                                                            |  |  |

| 68)                        | begin                                                                                                                                                                                                                                        |  |  |

| 69)                        | depth=depth+q*(W/L)*band_mobility*(Qfreei/(Qfree[0]+                                                                                                                                                                                         |  |  |

|                            | Qloc[0]+Qit))*(potential_x[i-1]-potential_x[i])*(function_n                                                                                                                                                                                  |  |  |

|                            | [i-1]/Efield[i-1]);                                                                                                                                                                                                                          |  |  |

| 70)                        | end                                                                                                                                                                                                                                          |  |  |

| 71)                        | lateral=lateral+depth*itv;                                                                                                                                                                                                                   |  |  |

| 72)                        | if(Vds-Vds_itv<0.1 && Vds-Vds_itv>0)/**********/                                                                                                                                                                                             |  |  |

| 73)                        | begin                                                                                                                                                                                                                                        |  |  |

| 74)                        | itv=Vds-Vds_itv;                                                                                                                                                                                                                             |  |  |

| 75                         | 1 —                                                                                                                                                                                                                                          |  |  |

- 75) end

- 76) else

- 77)

- begin itv=0.1;

- 78)

- 79) end

- 80) end

- depth=0; 81)

- 82) Qfreei=0;

- 83) end

- 84)  $I(D,S) \leq + lateral;$

- 85) end

- 86) endmodule

then the assumed value of  $\phi_{\rm B}$  is adjusted until the relation between  $V_{\rm GS}$  and  $\phi_{\rm S}$  agrees with Eq. (12). In this way, we can find the self-consistent solutions of  $\phi_{\rm B}(V_{\rm GS})$  and  $\phi_{\rm S}(V_{\rm GS})$ . Once  $\phi_{\rm B}(V_{\rm GS})$  and  $\phi_{\rm S}(V_{\rm GS})$  are known, the output current  $I_{\rm DS}(V_{\rm GS}, V_{\rm DS})$  is able to be calculated by Eq. (13).

We have incorporated abovementioned procedures into HSPICE via Verilog-A. Although the source code of Verilog-A is too long to be shown here, we summarize it herein as denoted by following tables [Table  $1\sim5$ ] in which the key procedures implemented via Verilog-A are concisely described in a *high-level language* type.

# IV. A-IGZO TFT INVERTER EXPERIMENTS AND RESULTS

A cross-sectional view of integrated a-IGZO TFTs with the staggered bottom gate structure is shown in Fig. 1(a). The detailed process sequence for a-IGZO TFTs is the same as in [5]. Structural parameters are as follows: the channel length (L)=30 µm, the gate-to-S/D overlap length ( $L_{ov}$ )=5 µm, the thickness of the gate oxide ( $T_{ox}$ )=100 nm, and the thickness of a-IGZO active thin-film ( $T_{IGZO}$ )=50 nm, respectively. As shown in Fig. 1(b), the enhancement load-type a-IGZO TFT-based inverter was integrated. The channel width  $W_{load}/W_{driver}$  was 50/175 µm for the load/driver TFT, and the pads of all nodes in two TFTs were prepared in the inverter layout in order to separately extract subgap DOSs of the load and driver TFTs (five pads as seen in Fig. 1(c)).

The  $g_A(E)$  was experimentally extracted from the multi-frequency response of *C*-*V* characteristics [6]. All a-IGZO DOS parameters are given in Table 6.

By using the 1-D field solver via Verilog-A [i.e., Table

| Table 6. | Used | SPICE | parameters |

|----------|------|-------|------------|

|----------|------|-------|------------|

| parameter                                           | value                |                    | parameter                                         | value              |

|-----------------------------------------------------|----------------------|--------------------|---------------------------------------------------|--------------------|

| parameter                                           | driver               | load               | parameter                                         | value              |

| $N_{\mathrm{TA}}[\mathrm{eV}^{-1}\mathrm{cm}^{-3}]$ | 7.5×10 <sup>18</sup> | 8×10 <sup>18</sup> | $N_{\rm TD}$ [eV <sup>-1</sup> cm <sup>-3</sup> ] | 1×10 <sup>20</sup> |

| $kT_{\rm TA}[{\rm eV}]$                             | 0.08                 | 0.067              | $kT_{\rm TD}[eV]$                                 | 0.06               |

| $N_{\rm DA} [{\rm eV}^{-1} {\rm cm}^{-3}]$          | 3×10 <sup>16</sup>   | 5×10 <sup>16</sup> | $N_{\rm DD} [\mathrm{eV}^{-1} \mathrm{cm}^{-3}]$  | 1×10 <sup>18</sup> |

| $kT_{\rm DA}[{\rm eV}]$                             | 0.8                  | 0.8                | $kT_{\rm DD}$ [eV]                                | 0.55               |

| parameter                                           | value                |                    | parameter                                         | value              |

| parameter                                           | driver               | load               | parameter                                         | value              |

| $N_{\rm D}$ [cm <sup>-3</sup> ]                     | 5×10 <sup>16</sup>   | 5×10 <sup>16</sup> | $N_{\rm C}  [{\rm cm}^{-3}]$                      | 6×10 <sup>18</sup> |

| $V_{\rm FB}[V]$                                     | 0.067                | 0.13               | $\mu_{\rm Band} [{\rm cm}^2/{\rm Vs}]$            | 23.5               |

| W[µm]                                               | 175                  | 50                 | $T_{\rm OX}$ [nm]                                 | 100                |

| <i>L</i> [µm]                                       | 30                   | 30                 | $T_{AOS} = T_{IGZO} [nm]$                         | 50                 |

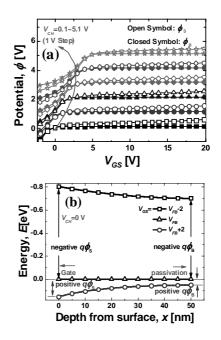

2 and 4] and Eqs. (9-12),  $\phi_{\rm S}(V_{\rm GS})$  and  $\phi_{\rm B}(V_{\rm GS})$  are acquired as seen in Fig. 2(a). Fig. 2(b) also shows the  $V_{\rm GS}$ -modulated energy band around the source region (*i.e.*, y=0), which is calculated from the 1-D field solver. Especially, the floating body effect with  $\phi_{\rm B}$  is clearly reproduced.

The measured device parameters of the driver and load TFTs consisting of a-IGZO inverter are summarized in Table 7. The difference of field-effect mobility ( $\mu_{FE}$ ) is attributed to both the ratio of  $W_{load}/W_{driver}$  and the definition of  $\mu_{FE}$ .

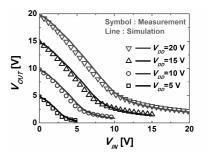

The SPICE simulated transfer and output characteristics based on the extracted  $\phi_s$  and  $\phi_b$  show a good agreement with the measured ones both in the linear and in the log scale, as seen in Fig. 3. It verifies that the proposed DOSbased SPICE model of a-IGZO TFTs is reasonable and very efficient. The used SPICE parameters are also summarized in Table 6.

**Fig. 2.** (a) The self-consistent  $\phi_{\rm S}(V_{\rm GS})$  and  $\phi_{\rm B}(V_{\rm GS})$  solution pair of the driver TFT extracted from the 1-D field solver, (b) The  $V_{\rm GS}$ -modulated energy band diagram of the driver TFT at  $V_{\rm CH}(y=0)=0$  V with definitions of  $\phi_{\rm S}$  and  $\phi_{\rm B}$ .

Table 7. The measured performance parameters

| TFT    | $V_{\mathrm{T}}\left[\mathbf{V}\right]$ | $\mu_{\rm FE}$ [cm <sup>2</sup> /Vs] | SS<br>[V/dec] | $I_{\rm ON}$ [µA]<br>( $V_{\rm GS}$ =20 V,<br>$V_{\rm DS}$ =0.1 V) | $I_{\rm ON}/I_{\rm OFF}$ |

|--------|-----------------------------------------|--------------------------------------|---------------|--------------------------------------------------------------------|--------------------------|

| Driver | 5.42                                    | 19.8                                 | 0.67          | 5.73                                                               | 8.04×10 <sup>5</sup>     |

| Load   | 5.04                                    | 6.39                                 | 0.66          | 1.91                                                               | 6.36×10 <sup>6</sup>     |

**Fig. 3.** (a) The transfer and (b) Output characteristics of a-IGZO TFTs calculated by using Eq. (13), The inset of (a) shows the transfer characteristic in the linear scale. The measured load line curve also agrees well with the simulated one.

The average/maximum error between the measured and simulated transfer characteristic is 3.06/10.1% and 5.73/20% (driver and load TFT, respectively) in Fig. 3(a). Also, the average/maximum error between the measured and simulated output characteristic is 0.33/6.4% and 2.29/3% (driver and load TFT, respectively) in Fig. 3(b). High error value of transfer characteristics is mainly attributed to the subthreshold current regime.

Finally, the VTC of a-IGZO inverter in Fig. 1(c) is measured at a room temperature without photoillumination. The a-IGZO inverter is also simulated by

Table 8. The HSPICE input code for a-IGZO inverter simulation

| //** | //** The simulation of VTC in a-IGZO inverter |  |  |

|------|-----------------------------------------------|--|--|

| 1)   | Inverter simulation                           |  |  |

| 2)   | .hdl 'DeAOTS_DC_Model_inverter.va'            |  |  |

| 3)   | .option post                                  |  |  |

| 4)   | Vg G 0 dc                                     |  |  |

| 5)   | Vd D 0 20                                     |  |  |

| 6)   | Vs S 0 0                                      |  |  |

| 7)   | Xtft1 Vout G S TFT_DRIVER                     |  |  |

| 8)   | Xtft2 D D Vout TFT_LOAD                       |  |  |

| 9)   | .dc Vg 0.0 20 0.5                             |  |  |

| 10)  | .print V(Vout)                                |  |  |

| 11)  | .end                                          |  |  |

Fig. 4. The measured VTC for a-IGZO TFT inverter compared with SPICE simulation. The average error between the measured and simulated VTC is 6% at  $V_{DD}$ =20 V.

using the proposed DOS-based SPICE model. The input code used in HSPICE simulation is shown in Table 8.

Fig. 4 shows that the measured VTC agrees well with the simulated one at various supply voltages ( $V_{DD}$ ). The average/maximum error between the measured and simulated VTC is 6/12.6% at  $V_{DD}$ =20 V. Consequently, the proposed DOS-based SPICE model is found to be efficiently applicable to AOS-based circuit simulation.

# **V. CONCLUSIONS**

The physics-based SPICE model of AOS TFTs is proposed and demonstrated in a-IGZO TFT inverter by using Verilog-A. The DOS-based SPICE model can successfully reproduce the measured I-V characteristics of a-IGZO TFTs and the VTC of a-IGZO inverter very efficiently. Especially, it is noticeable that the proposed SPICE model and the simulation methodology are expected to be very useful in the process optimization as well as the circuit design of AOS TFTs because subgap DOS is the process-controlled parameter. As further study, the C-V model is underway. The physics-based SPICE model via Verilog-A is expected to play a significant role in process optimization and circuit design for innovative AOS TFT-based applications such as display backplane, wearable computers, e-paper, transparent SoC, solar cell, and 3-D stacked memories.

## **ACKNOWLEDGMENTS**

This work was supported by the Mid-career Researcher Program through National Research Foundation of Korea (NRF) grant funded by the Ministry of Education, Science and Technology (MEST) (Grant no. 20100000828). The CAD software was supported by IC Design Education Center (IDEC).

# REFERENCES

- H.-H. Lu et al, "32-inch LCD Panel Using Amorphous Indium-Gallium-Zinc-Oxide TFTs," in *SID Int. Symp. Digest Tech. Papers*, pp.1136-1138, 2010.

- [2] Y. G. Mo et al, "Amorphous Oxide TFT Backplane for Large Size AMOLED TVs," in *SID Int. Symp. Digest Tech. Papers*, pp.1037-1040, 2010.

- [3] H. Yin et al, "High Performance Low Voltage Amorphous Oxide TFT Enhancement/Depletion Inverter through Uni-/Bi-Layer Channel Hybrid Integration," in *IEDM Tech. Dig.*2009, pp.199-202.

- [4] M.-J. Lee et al, "Low temperature grown transition metal oxide based storage materials and oxide transistor for high density nonvolatile memory," *Advanced Functional Materials*, Vol.19, No.10, pp.1587-1593, May, 2009.

- [5] Y. W. Jeon et al, "Subgap Density of States-Based Amorphous Oxide Thin Film Transistor Simulator (DeAOTS)," *IEEE Transactions on Electron Devices*, Vol.57, No.1, pp.2988-3000, Nov., 2010.

- [6] S. Lee et al, "Extraction of Subgap Density of States in Amorphous InGaZnO Thin Film Transistors by Using Multi-Frequency Capacitance-Voltage Characteristics," *IEEE Electron Device. Letters*, Vol.31, No.3, pp.231-233, Mar., 2010.

**Yong Woo Jeon** received the B.S. degree in electrical engineering from the Kookmin University, Seoul, Korea, in 2009, where he is currently working toward the M.S. degree at the Department of Electrical Engineering under the supervision of

Prof. D. M. Kim and Prof. D. H. Kim. His current research mainly focuses on amorphous oxide semiconductor TFTs and their device physics.

**Inseok Hur** received the B.S. degree in electrical engineering from the Kookmin University, Seoul, Korea, in 2011, where he is currently working toward the M.S. degree in the Department of Electrical Engineering under the supervision of Prof. D. M.

Kim and Prof. D. H. Kim. His current research mainly focuses on amorphous oxide semiconductor thin-film transistors and their device physics.

**Yongsik Kim** received the B.S. degree in electrical engineering from the Kookmin University, Seoul, Korea, in 2010, where he is currently working toward the M.S. degree at the Department of Electrical Engineering under the supervision of Prof. D. M.

Kim and Prof. D. H. Kim. His current research mainly focuses on amorphous oxide semiconductor TFTs and their device physics.

**Minkyung Bae** received the B.S. degree in electrical engineering from the Kookmin University, Seoul, Korea, in 2010, where she is currently working toward the M.S. degree in the Department of Electrical Engineering under the supervision of Prof. D. M.

Kim and Prof. D. H. Kim. Her current research mainly focuses on amorphous oxide semiconductor thin-film transistors and their device physics.

**Hyun Kwang Jung** received the B.S. degree in electrical engineering from the Kookmin University, Seoul, Korea, in 2010, where he is currently working toward the M.S. degree at the Department of Electrical Engineering under the supervision of Prof. D. M.

Kim and Prof. D. H. Kim. His current research mainly focuses on amorphous oxide semiconductor TFTs and their device physics.

**Dongsik Kong** received the B.S. degree in electrical engineering from the Kookmin University, Seoul, Korea, in 2010, where he is currently working toward the M.S. degree in the Department of Electrical Engineering under the supervision of Prof. D. M.

Kim and Prof. D. H. Kim. His current research mainly focuses on amorphous oxide semiconductor thin-film transistors and their device physics.

**Woojoon Kim** received the B.S. degree in electrical engineering from the Kookmin University, Seoul, Korea, in 2011, where he is currently working toward the M.S. degree at the Department of Electrical Engineering under the supervision of Prof. D. M.

Kim and Prof. D. H. Kim. His current research mainly focuses on amorphous oxide semiconductor TFTs and their device physics.

**Jaeman Jang** received the B.S. and M.S. degree in 2009 and 2011, respectively, from the Kookmin University, Seoul, Korea, where he is currently working toward the Ph.D. degree in electrical engineering. During his M.S. studies, he has

worked on modeling, characterization and design of nano-scaled memory device including capacitorless 1T DRAM and nano-crystal flash memory device. His current research interest includes design, fabrication, characterization, and modeling of oxide thin film transistors and organic thin film transistors.

**Dong Myong Kim** (S'86–M'88) received the B.S. (magna cum laude) and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1986 and 1988, respectively, and the Ph.D. degree in electrical engineering from

the University of Minnesota, Twin Cities, in 1993. From February 1988 to August 1989, he was with the Division of Electronic Engineering at Korea Institute of Science and Technology (KIST), Seoul, Korea, where he worked on the characterization and modeling of microwave devices and integrated circuits. Since March 1993, he has been with the School of Electrical Engineering, Kookmin University, Seoul, Korea. He is also serving as a Special Lecturer for Semiconductor Physics and Devices at Samsung Electronics Co., Hwasung, Korea since April 2002. His current research interests include design, fabrication. characterization, and modeling of nanostructure silicon devices, thin film transistors, biosensors, III-V compound semiconductor devices, volatile and nonvolatile memories, and CMOS RF circuits

**Jaehyeong Kim** received the B.S. degree in electrical engineering from the Kookmin University, Seoul, Korea, in 2011, where he is currently working toward the M.S. degree at the Department of Electrical Engineering under the supervision of Prof. D. M.

Kim and Prof. D. H. Kim. His current research mainly focuses on amorphous oxide / organic semiconductor TFTs and their device physics.

**Dae Hwan Kim** (M'08) received the B.S., M.S., and Ph.D. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 1996, 1998, and 2002, respectively. From 2002 to 2005, he was with Samsung Electronics Company, Ltd.,

Kyung ki-Do, Korea, where he contributed to the design and development of 92-nm DDR DRAM and 80-nm DDR2 DRAM. In 2005, he joined the School of Electrical Engineering, Kookmin University, Seoul, where he is currently an Associate Professor. He has authored or coauthored more than 170 research publications and patents. His current research interests are nanoscale CMOS devices and integrated circuits, metal oxide and organic thin-film transistors, biosensors devices, exploratory logic and memory devices, energyefficient nano-ICs, and Si quantum devices. He has also worked on the characterization, modeling, and circuit design for reliabilities of CMOS devices, thin-film transistors, display, biosensors, and neuromorphic systems. He is a member of IEEE, Society for Information Display, and Institute of Electronics Engineers of Korea.