# Placement of Defect-Tolerant Digital Microfluidic Biochips Using the T-tree Formulation

# PING-HUNG YUH, CHIA-LIN YANG, and YAO-WEN CHANG National Taiwan University

Droplet-based microfluidic biochips have recently gained much attention and are expected to revolutionize the biological laboratory procedures. As biochips are adopted for the complex procedures in molecular biology, its complexity is expected to increase due to the need of multiple and concurrent assays on a chip. In this article, we formulate the placement problem of digital microfluidic biochips with a tree-based topological representation, called *T-tree*. To the best knowledge of the authors, this is the first work that adopts a topological representation to solve the placement problem of digital microfluidic biochips. We also consider the defect tolerant issue to avoid to use defective cells due to fabrication. Experimental results demonstrate that our approach is more efficient and effective than the previous unified synthesis and placement framework.

Categories and Subject Descriptors: B.7.2 [Integrated Circuits]: Design Aids

General Terms: Algorithms, Performance, Design

Additional Key Words and Phrases: Microfluidics, biochip, placement

#### **ACM Reference Format:**

Yuh, P.-H., Yang, C.-L., and Chang, Y.-W. 2007. Placement of defect-tolerant digital microfluidic biochips using the T-tree formulation. ACM J. Emerg. Technol. Comput. Syst. 3, 3, Article 13 (November 2007), 32 pages. DOI = 10.1145/1295231.1295234 http://doi.acm.org/10.1145/ 1295231.1295234

This article is an extended and revised version of the paper presented at the 2006 IEEE/ACM Design Automation Conference (DAC) @ ACM 2006.

This work was partially supported by the National Science Council of Taiwan under Grant Nos. NSC 95-2752-E-002-008-PAE and NSC 95-2221-E-002-374 and by the Excellent Research Projects of National Taiwan University, 95R0062-AE00-07.

Authors' address: P.-H. Yuh, C.-L. Yang (contact author), Department of CSIE, National Taiwan University, No. 1, Sec. 4, Roosevelt Road, Taipei, Taiwan; email: {r91089, yangc}@csie.ntu.edu.tw; Y.-W. Chang, Graduate Institute of Electronics Engineering and Department of EE, National Taiwan University, No. 1, Sec. 4, Roosevelt Road, Taipei, Taiwan; email: ywchang@cc.ee.ntu.edu.tw. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or direct commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org. © 2007 ACM 1550-4832/2007/11-ART13 \$5.00. DOI 10.1145/1295231.1295234 http://doi.acm.org/ 10.1145/1295231.1295234

## 13:2 • P.-H. Yuh et al.

## 1. INTRODUCTION

Due to the advances in the microfabrication and microelectromechanical systems, microfluidic technology has gained much attention recently. The composite microsystems could perform conventional biological laboratory procedures on a small and integrated system. As a result, microfluidic biochips are used in several common procedures in molecular biology, such as the clinic diagnosis and the DNA sequence analysis.

Most recently, second-generation (digital) microfluidic biochips, which are based on the manipulation of the discrete liquid particles (the *droplets*), have been proposed [tutorgig]. Each droplet can be independently controlled by the electrohydrodynamic forces generated by an electric field. The field can be generated by an individually accessible electrode. Compared with the firstgeneration microfluidic biochips that are based on the continuous fluid flow and contain external pressure sources (e.g., micropumps), the droplets can be moved anywhere in a 2D array to perform the desired chemical reaction and the electrodes can be reprogrammed for different bioassays. With these two properties, digital microfluidic biochips can handle large-scale and complex procedure, since the complex procedure can be built based on a set of fundamental operations, such as droplet generation, mixing of multiple droplets, droplet transportation, droplet dilution, and droplet fission. Moreover, digital microfluidic biochips can be reconfigured for different levels of hierarchy.

As biochips are adopted for complex procedures in molecular biology, the design complexity of digital microfluidic biochips is expected to increase due to the need of multiple and concurrent assays on a biochip. The International Technology Roadmap for Semiconductors (ITRS) clearly points out that the integration of electro-biological devices is one of the major challenges of system integration beyond 2009 [ITRS]. Besides, the increase in the density of assays and area of digital microfluidic biochips may reduce yield. Since we need time to ramp up the yield of biochips, it is desirable to perform a bioassay on a biochip with the existence of defects. How to incorporate the defect tolerant issue in Computer Aided Design (CAD) support becomes an important issue.

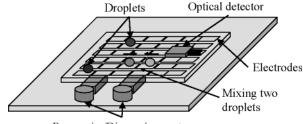

Figure 1 shows the schematic view of a digital microfluidic biochip based on the principle of electrowetting on dielectric (EWOD) [Fair et al. 2003]. There are three major components in a biochip: 2D microfluidic array, reservoirs/dispensing ports, and optical detectors. The 2D microfluidic array consists of a set of basic cells with the same architecture. The 2D microfluidic array is used for the chemical reaction of droplets and droplets transportation. With this 2D array, fundamental microfluidic operations (e.g., mix, dilute, and store) can be performed for different bioassays. The mix operation is to mix two droplets containing analytes and reagents. The two droplets route to the same location and turn around some pivot points for fast mixing process. This operation can be used for preprocessing, sample dilution, or reaction between samples and reagents. The dilution operation is to mix samples with buffers to reduce the sample concentration. The dilution ratio is controlled by a hierarchy of binary mixing phases by mixing samples (or diluted droplets) and buffers. The storage

Placement of Defect-Tolerant Digital Microfluidic Biochips • 13:3

Reservoirs/Dispensing ports

Fig. 2. An example of bioassay execution on digital microfluidic biochips.

operation is to temporarily preserve samples; that is, a droplet containing biological sample is located at a fixed location for a period of time. Note that since droplets can move freely on the 2D array, these operations can be performed anywhere in this 2D array. In other words, a basic cell can perform different operations at different time steps. This property is referred to as the *reconfigurability* of biochips. Moreover, there are different implementations of these operations with different areas and durations. For example, a mix operation can be performed in a  $2 \times 3$  or  $1 \times 4$  region with different mixing times. In this paper, we refer to this type of operations (mix, dilute) as the *reconfigurable operations*. The reservoirs/dispensing ports are responsible for droplets generation while the optical detectors are used for the detection of reaction results. In contrast to the 2D array, these devices have only one functionality. Therefore, in this paper, we call these device as the *non-reconfigurable devices*. The operations (e.g., droplet dispensing/generation and detection) performed on these devices are referred to as *non-reconfigurable operations*.

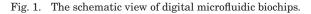

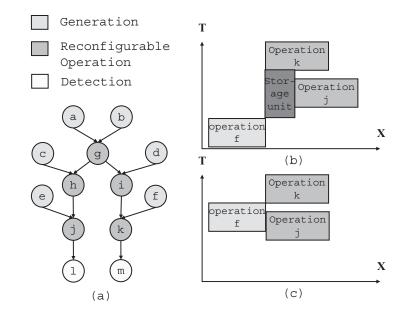

The bioassay is a procedure to determine the strength or activity of a biological sample by comparing its effect with those standard preparations on the living cells. Figure 2 shows the bioassay execution on a biochip. A bioassay is represented as a task graph, where each node represents a fundamental operation and each edge represents the data dependency between two operations. Each fundamental operation (mix, dilution, etc.) occupies a certain area and

## 13:4 • P.-H. Yuh et al.

lasts for a period of time. There are two important characteristics of the execution of a bioassay. First, due to the reconfigurability of biochips, two fundamental operations may share the same area at different time steps. For example, the mix operation b and the mix operation a share the same area. Second, a storage unit is required to temporarily store the intermediate result between two datadependent fundamental operations. For example, although the mix operation ais finished at time 4, the mix operation c cannot immediately start its execution since another input droplet of mix c is not available at that time. Therefore, a storage unit is required to store the result of the mix operation a. The above two characteristics complicates the placement of fundamental operations, since we need to determine not only the physical location but also the starting time of each fundamental operation. Moreover, we also need to determine the number of storages and the locations of them.

Due to the reconfigurability, the placement problem of digital microfluidic biochips includes architectural-level synthesis (i.e., scheduling and resource binding) and physical placement. How to simultaneously perform architecturallevel synthesis and physical placement is the most challenging issue in the placement problem.

## 1.1 Related Works

Architectural-level synthesis and physical placement of digital microfluidic biochips have been addressed in the recent literature. For the architecturallevel synthesis, Ding et al. [2001] proposed an architectural-level modeling and an integer linear programming based optimization method for droplet-based microfluidic biochips. Su et al. [Su and Chakrabarty 2004] used the sequencing graph to represent the bioassay protocol and proposed an integer linear programming based formulation and two heuristics, the modified list scheduling algorithm and the genetic algorithm, to solve this problem. Recently, Ricketts et al. [2006] proposed the hybrid priority scheduling algorithm based on the genetic algorithm. For the physical placement, Su et al. [Su and Chakrabarty 2005a] proposed a simulated annealing-based algorithm for the physical placement problem with given scheduled operations. They also considered the fault tolerance issue by modeling the degree of faults and identifying the empty spaces to recover operations with faulty cells. Recently, Su and Chakrabarty [2005b] presented a unified synthesis and placement flow based on parallel recombinative simulated annealing. Their algorithm consisted of three stages: binding, scheduling, and physical placement. They used the list scheduling algorithm for scheduling and a greedy placement algorithm for physical placement. They also considered the defect tolerant issue for yield enhancement.

The synthesis and physical placement problem of digital microfluidic biochips are closely related to the operations of dynamically reconfigurable FPGAs (DRFPGAs), which have received much attention recently [Bazargan et al. 2000]. The digital microfluidic biochips offers the same partial reconfigurability as the DRFPGAs. Many approaches, such as the graph-theoretic approach [Fekete et al. 2001] and the topological representation based approach [Yuh et al. 2004; Yuh et al. 2004], have been proposed. Among these

approaches, the T-tree [Yuh et al. 2004] representation is the state-of-the-art method for DRFPGAs.

## 1.2 Our Contribution

In this article, we adopt the T-tree topological representation [Yuh et al. 2004] to solve the placement problem of digital microfluidic biochips. Due to the reconfigurability of DRFPGAs, the placement of digital microfluidic biochips is similar to the simultaneous scheduling and placement of DRFPGAs. However, the placement of biochips is more complicated than that of DRFPGAs for two reasons. First, besides reconfigurable operations, biochips also have non-reconfigurable operations. Second, a storage unit is required for two datadependent operations if they are not scheduled at consecutive time steps. To the best knowledge of the authors, our work is the first to apply a topological representation to solve the placement problem of digital microfluidic biochips. We choose the T-tree [Yuh et al. 2004] topological representation over other 3D representations, such as 3D-subTCG [Yuh et al. 2004], Sequence Triplet [Yamazaki et al. 2000], and 3D slicing tree [Cheng et al. 2005], because T-tree is effective and efficient on volume optimization and handling the storage units. We also explore the property of a bioassay to develop a clustering algorithm; since a generation operation and a reconfigurable operation are performed sequentially in a bioassay, we cluster the two operations a priori for better solution quality and less CPU time. Due to the need to perform a bioassay on a biochip with the existence of defects, the proposed placement algorithm handles the defect tolerant issue by modeling each defective cell as an obstacle and not allowing overlaps among operations and obstacles.

We evaluated the proposed placement algorithm on the colorimetric protein assay [Srinivasan et al. 2004] and the multiplexed in-vitro diagnostics [Su and Chakrabarty 2004]. We assumed different design specifications, for example, fixed architecture and limited assay completion time, for each bioassay. The experimental results show that our placement algorithm can satisfy all design specifications for all bioassay while both Su and Chakrabarty [2005b] and the 3D-subTCG based algorithm can satisfy only some of them. Moreover, we can achieve smaller volume than Su and Chakrabarty [2005b] and 3D-subTCG. For example, for the in-virto diagnostics, Su and Chakrabarty [2005b] obtains, on average, 4.07X larger volume than our algorithm. For the defect tolerance, we performed four different sets of experiments (two sets with three and two sets with four defective cells). With the existence of defects, our placement algorithm could achieve a biochip with only 16% increase in the assay completion time compared with that of a nondefective biochip with reasonable CPU time.

The remainder of this article is organized as follows. Section 2 formulates the placement problem of digital microfluidic biochips. Section 3 reviews various 3D floorplan representations and gives the advantages of T-tree over other representations. Section 4 presents the T-tree based formulation for the placement problem. Section 5 describes our temporal floorplanning algorithm. Section 6 demonstrates our defect tolerance approach. Section 7

13:6 P.-H. Yuh et al.

Fig. 3. Overview of the placement problem of biochips.

reports the experimental results. Finally, concluding remarks are given in Section 8.

## 2. PROBLEM FORMULATION

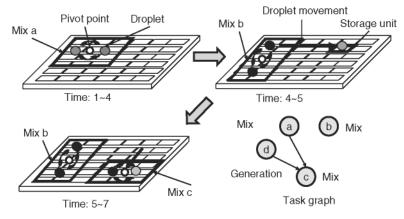

In this section, we give a formal definition about the placement problem of digital microfluidic biochips. Figure 3 shows the overview of the placement problem. There are three inputs to the placement problem. The first one is the sequencing graph  $G = \{V, E\}$  that represents the protocol of a bioassay [Su and Chakrabarty 2004], where  $V = \{v_1, v_2, \dots, v_m\}$  represents a set of *m* assay operations and  $E = \{(v_i, v_j), 1 \le i, j \le m\}$  denotes the data dependencies between two assay operations; i.e., the *precedence constraints*. We may need at most one storage unit for each edge in G to store the intermediate data between two data-dependent operations. Throughout this paper, we use operation and task interchangeably. The second one is the microfluidic module library that contains the basic modules for biochips. Each basic module is characterized by its functionality (i.e., mix, dilution, etc.) and parameters (i.e., width, height, and operation duration). The third one is the design specification, including: (1) the fixed architecture (such as  $10 \times 10$  array) and limited assay completion time (such as 400 seconds) and (2) the maximum number of instances for each type of non-reconfigurable devices; that is, the *resource constraints*.

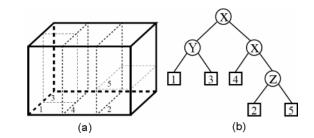

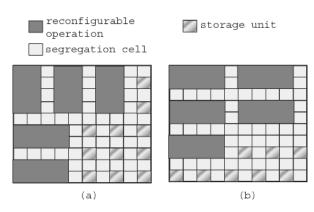

Fig. 4. (a) A 3D placement. (b) Its corresponding 3D-subTCG.

The goal of our algorithm is to simultaneously perform resource binding, scheduling, and physical placement with volume optimization under the design specification. Binding is to map an operation to a functional resource. Note that there may be several functional resources for a given operation. For example, for a reconfigurable operation, such as the mix operation, we can use a  $2 \times 2$ array mixer or a  $2 \times 4$ -array mixer with different mixing times. However, several operations may map to the same functional resource for resource sharing. For example, we may map two detection operations to the same optical detector. After binding, the duration and dimension of each operation is determined. Scheduling is to determine the starting time of each operation under the precedence constraint. For a valid schedule, non-reconfigurable operations that map to the same device cannot execute concurrently. Physical placement is to find the physical location for each reconfigurable operation on the 2D microfluidic array. We also need to determine the locations of optical detectors. On the other hand, we can manually determine the reservoirs/dispensing ports after placement, since they do not affect the area of the biochip [Su and Chakrabarty 2005b]. In this paper, we ignore the time for transporting droplets between different tasks because the movement of droplets is very fast compared with the duration of each task [Fair et al. 2003; Srinivasan et al. 2004]. We also follow Su and Chakrabarty [2005b] in using the segregation cells to wrap each reconfigurable operation, storage unit, and optical detectors for not only providing the transportation path for droplets movement between different operations, but also isolating one operation from another to avoid unexpected cross-contamination.

## 3. REVIEW OF 3D FLOORPLAN REPRESENTATIONS

In this section, we briefly review popular 3D floorplan representations proposed in the recent literature, including 3D-subTCG [Yuh et al. 2004], Sequence Triplet (ST) [Yamazaki et al. 2000], T-tree [Yuh et al. 2004], and 3D slicing tree [Cheng et al. 2005]. Then we point out the advantages of T-tree over other 3D representations.

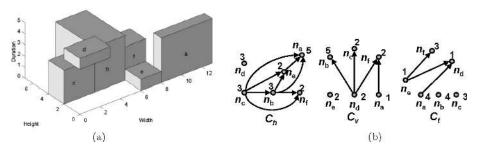

## 3.1 3D-subTCG

3D-subTCG is an extension of the well-known 2D floorplan representation: Transitive Closure Graph (TCG) [Lin and Chang 2001]. 3D-subTCG uses a horizontal transitive closure graph  $C_h$  and a vertical transitive closure graph  $C_v$

13:8 • P.-H. Yuh et al.

Fig. 5. A 3D floorplan; the corresponding Sequence Triplet is (*bca, bac, abc*).

to describe the geometric relations and a *temporal transitive closure graph*  $C_t$  to model the temporal relations among tasks. Figure 4 shows a 3D placement and its corresponding 3D-subTCG. Each node  $n_i$  in a transitive closure graph represents a task  $v_i$ . The value associated with a node in  $C_h$  ( $C_v$  or  $C_t$ ) gives the width (height or duration) of the corresponding task, and the edge  $(n_i, n_j)$  in  $C_h$  ( $C_v$  or  $C_t$ ) represents the horizontal (vertical or temporal) relation of  $v_i$  and  $v_j$ . For example, in Figure 4, since task  $v_c$  ( $v_a$ ) is left to (below)  $v_b$  ( $v_f$ ), there exists an edge  $(n_c, n_b)$  ( $(n_a, n_f)$ ) in  $C_h$  ( $C_v$ ). Similarly, since task  $v_a$  is executed before task  $v_d$ , there exists an edge  $(n_a, n_d)$  in  $C_t$ .

#### 3.2 Sequence Triplet

Sequence Triplet (ST) is a 3D representation extended from the well-known Sequence Pair representation [Murata et al. 1995]. An ST consists of three sequences ( $\Gamma_1$ ,  $\Gamma_2$ ,  $\Gamma_3$ ), where each sequence contains the label of all tasks. Figure 5 shows a simple 3D placement and its corresponding ST. ST defines the relations between two tasks based on the relative positions of this two tasks in the three sequences. The relation between two tasks is defined as follows: (1) if the sequence of two tasks  $v_a$ ,  $v_b$  is the same (from left to right) in ( $\Gamma_1$ ,  $\Gamma_2$ ,  $\Gamma_3$ ), i.e., ( $\Gamma_1$ ,  $\Gamma_2$ ,  $\Gamma_3$ ) = (..a..b.., ..a..b.., ..a..b..), it means that task  $v_b$  is in the  $Y^+$  direction of task  $v_a$ ; (2) if ( $\Gamma_1$ ,  $\Gamma_2$ ,  $\Gamma_3$ ) = (..a..b.., ..a..b.., ..b..a..), it means that task  $v_b$  is in the  $X^-$  direction of task  $v_a$ ; (3) if ( $\Gamma_1$ ,  $\Gamma_2$ ,  $\Gamma_3$ ) = (..a..b.., ..a..b..), it means that task  $v_b$  is in the  $X^+$  direction of task  $v_a$ ; (4) if ( $\Gamma_1$ ,  $\Gamma_2$ ,  $\Gamma_3$ ) = (..a..b.., ..b..a..), ..b..a..), it means that task  $v_b$  is in the  $Z^-$  direction of task  $v_a$ . For example, since the relative positions of tasks  $v_a$  and  $v_b$  satisfy relation (2),  $v_a$  is in the  $X^$ direction of  $v_b$ .

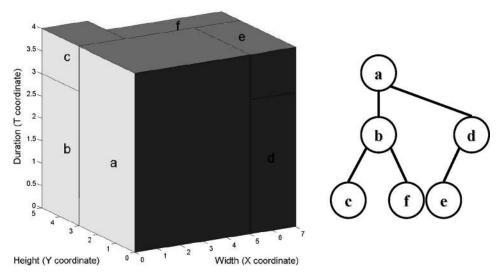

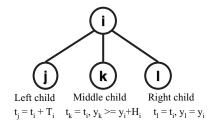

#### 3.3 T-tree

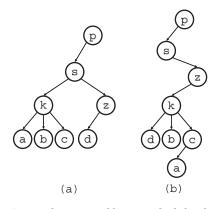

T-trees are a 3-ary tree, where each node corresponds to a unique task and has at most three children to represent the dimensional relationship among tasks. The T-tree is designed to represent a compacted placement where each task cannot move toward the origin. Figure 6 shows a compacted placement and its corresponding T-tree. Given a set of m tasks, let  $W_i$ ,  $H_i$ , and  $T_i$  denote the width, height, and duration of each task,  $1 \le i \le m$ . We use  $(x_i, y_i)$   $((i, y'_i))$  to denote the coordinate of the bottom-left (top-right) corner of a task  $v_i$ , and  $t_i$  $(t'_i)$  the starting (ending) time of task  $v_i$ ,  $1 \le i \le m$ . The T-tree represents the geometric relationship between two tasks as follows. If node  $n_j$  is the left child of node  $n_i$ , module  $v_j$  must be placed adjacent to module  $v_i$  in the  $T^+$  direction, that is,  $t_j = t_i + T_i$ . If node  $n_k$  is the middle child of node  $n_i$ , module  $v_k$  must be placed in the  $Y^+$  direction of module  $v_i$ , with the *t*-coordinate of  $v_k$  equal to

Fig. 6. A compacted placement and its corresponding T-tree.

Fig. 7. The structure of the T-tree.

that of  $v_i$ , i.e.,  $t_k = t_i$  and  $y_k \ge y_i + H_i$ . If node  $n_l$  is the right child of node  $n_i$ , module  $v_l$  must be placed in the  $X^+$  direction of module  $v_i$ , with the *t*- and *y*-coordinates equal to those of  $v_i$ , i.e.,  $t_l = t_i$  and  $y_l = y_i$ . Figure 7 shows the structure of a T-tree.

## 3.4 3D Slicing Tree

The 3D Slicing tree [Cheng et al. 2005] is an extension of the 2D slicing tree representation [Wong and Liu 1986]. A 3D slicing floorplan is a floorplan that consists of a finite number of nonoverlapping rectangles, where these rectangles can be obtained by repetitively subdividing rectangles with the planes that are perpendicular to the X-, Y-, or Z-axis (assume that faces of the 3D blocks are perpendicular to the X, Y, and Z axes). Figure 8(a) shows a 3D slicing floorplan. The 3D slicing tree is an oriented rooted binary tree that represents a 3D slicing floorplan. Figure 8(b) shows the corresponding 3D slicing tree of Figure 8(a). Each leaf node corresponds to a basic 3D task and is labeled by its name. Each internal node represents a supermodule and is labeled by X, Y, or Z. The label X means that the corresponding supermodule is divided into two halves by a plane that is perpendicular to the X-axis. The labels Y and Z are

13:10 • P.-H. Yuh et al.

Fig. 8. (a) The 3D slicing structure. (b) The corresponding 3D slicing tree.

similarly defined. For example, the root of the two tasks  $v_2$  and  $v_5$  represents a supermodule. Since its label is Z, this supermodule is divided by the plane that is perpendicular to the Z-axis. Therefore, task  $v_5$  is in the  $Z^+$  direction of task  $v_2$ .

#### 3.5 Discussion

In this section, we give the advantages of the T-tree over the other representations for the placement problem of digital microfluidic biochips, for which we choose the T-tree representation to solve the problem addressed in this paper:

- (1) T-tree models compacted floorplans whose modules are compacted toward the origin, while the 3D-subTCG and ST model general floorplans and the 3D slicing tree models slicing floorplans. Recall that for the placement problem of digital microfluidic biochips, we need to satisfy the given fixed architecture and limited assay completion time. Therefore, a feasible 3D floorplan must be within the 3D cube defined by the fixed architecture and limited assay completion time. Since the T-tree models a compacted floorplan, it is more suitable for volume optimization, and thereby is more likely to generate solutions that are within the defined 3D cube. Consequently, T-tree is more suitable for the placement problem of digital microfluidic biochips than other 3D representations.

- (2) Recall that we need a storage unit for two data-dependent operations if they are not scheduled at consecutive time steps. Also, the number and duration of these storage units are related to the schedule of operations. Based on the structure of T-tree, we can easily determine the number of storage units and their duration before packing. This process takes only linear time. As for 3D-subTCG and ST, we need, on average,  $O(m^2)$  time to obtain this information with m operations since each transitive closure graph has average  $\frac{m(m-1)}{6}$  edges. For the 3D slicing tree, this information cannot be obtained before packing. Further, the number of storage units varies with different schedules. We may need to delete an unused storage unit or insert a new one during simulated annealing (SA) for packing efficiency. For 3D-subTCG, when deleting an unused storage unit (inserting a new storage unit), we need to delete (insert) an edge from this storage unit to all other tasks, and detect whether the properties of 3D-subTCG are satisfied after deletion (insertion). That is, we need to detect whether the

transitive closure property is satisfied and there exists no cycles in each transitive closure graph. We need O(|E|) time to detect cycles and to maintain the transitive closure property for inserting/deleting one edge, where E is the set of edges in one transitive closure graph. For ST, we need to determine the positions of a storage unit in  $(\Gamma_1, \Gamma_2, \Gamma_3)$  for insertion, since we need to satisfy the requirement of storage units—a storage operation  $v_s$  must be performed after the finish of  $v_i$  if  $v_s$  stores the result of  $v_i$ . This process may need O(km) time, where k is the number of storage units required for insertion. For the 3D slicing tree, it is hard to guarantee that the duration of one storage unit equals the time gap between two data-dependent operations. Therefore, it is harder for a 3D slicing tree to obtain a feasible solution.

(3) As described in Section 1, the size (number of operations) of a bioassay is expected to increase because the design of a biochip will become more complicated to handle concurrent assays on a chip. Therefore, the efficiency of handling large-scale bioassays is one important factor when evaluating the suitability of a 3D representation for the placement problem of biochips. It has been shown [Yuh et al. 2004] that T-tree is more efficient and effective than 3D-subTCG and ST for the simultaneous scheduling and placement problem of DRFPGAs. Since the problem addressed here is closely related to that of the DRFPGAs, we expect the T-tree to also be more efficient and effective than 3D-subTCG and ST.

With these reasons, we decide to choose the T-tree representation to handle the placement problem of digital microfluidic biochips.

# 4. T-TREE BASED BIOCHIP PLACEMENT

In this section, we first present the challenges of solving the placement problem of biochips. Then we demonstrate that the execution of tasks on a biochip can be modeled as the temporal floorplanning problem. Finally, we present how to model each type of tasks with the T-tree formulation and how to handle the design specification in our algorithm.

Due to the reconfigurability of both DRFPGAs and biochips, the placement of digital microfluidic biochips is similar to the simultaneous scheduling and placement of DRFPGAs. At first glance, one may apply the techniques for DRF-PGAs to solve the placement problem of biochips. However, the placement of biochips is more complicated than that of DRFPGAs based on the following two reasons.

(1) In addition to reconfigurable operations, biochips also have nonreconfigurable operations. These non-reconfigurable operations have different characteristics from that of reconfigurable operations. For example, since droplets are generated at the reservoirs/dispensing ports which are on the boundary of the 2D microfluidic array, the generation operations do not occupy the area of the 2D microfluidic array. Another example is the detection operations. Since the detectors are fixed after fabrication, two detection operations using the same detector must have the same physical

#### 13:12 • P.-H. Yuh et al.

Fig. 9. The two placements with the same biochip area and number of reconfigurable operations but with different number of storage units.

location in the 2D microfluidic array. Besides, the total number of nonreconfigurable operations at any time is limited due to the limited number of non-reconfigurable devices. As a result, we require different ways to handle these non-reconfigurable operations.

(2) In digital microfluidic biochips, a storage unit is required for two datadependent operations if they are not scheduled at consecutive time steps. The existence of the storage units complicates the placement problem for two reasons. First, instead of only area estimation as used in Su and Chakrabarty [2004], we need detail physical information of these storage units for accurate biochip area calculation. We use Figure 9 as an example to illustrate this scenario. Figure 9 shows two placements with the same biochip area  $(10 \times 10)$  and the same number of reconfigurable operations (5 operations). Note that for the purpose of functional isolation and droplet transportation, we use the segregation cells to wrap each operation and storage unit. Although these two placements have the same biochip area. they differ in the number of storage units. If no detail physical information of the storage units is provided, we cannot obtain the exact biochip area. We may conclude that the area of Figure 9(a) is larger than that of Figure 9(b), since the number of storage units of Figure 9(a) is larger than that of Figure 9(b) if only area estimation of storage units is used. Second, the number and duration of the storage units are not determined a priori. More importantly, the number and duration of the storage units are related to current schedule of operations. This characteristic makes storage units different from modules in traditional temporal floorplanning problem, where the number of modules and the volume of each module are inputs and remain unchanged during floorplanning. We use Figure 10 as an example to explain this characteristic. In this figure, we model each operation as a 3D box. Figure 10 shows a bioassay with two data-dependent operations. For each operation and storage unit, we model it as a 3D box. As shown in

ACM Journal on Emerging Technologies in Computing Systems, Vol. 3, No. 3, Article 13, Publ. date: November 2007.

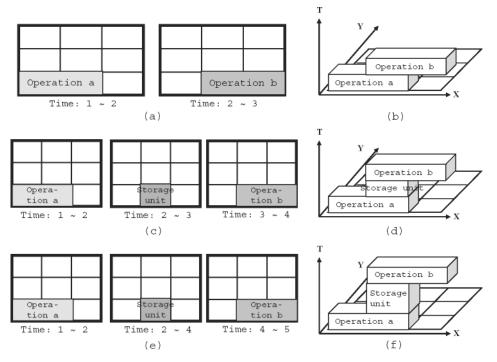

Figure 10(a), since operation  $v_b$  starts right after operation  $v_a$  finishes, we do not need a storage unit. Figure 10(b) shows its corresponding 3D placement with two operations. Now suppose that  $v_b$  starts one time unit after  $v_a$

Fig. 10. Examples to show the characteristics of storage units. (a) Two tasks on a biochip. (b) The corresponding 3D floorplan of (a). (c) Two tasks with a storage unit. (d) The corresponding 3D floorplan of (c). Note that we have three modules in this floorplan. (e) Two tasks with a storage unit. (f) The corresponding 3D floorplan of (e). The duration of the storage unit is increased from 1 to 2 time units.

finishes, as shown in Figure 10(c). In this situation, we need one storage unit to store the intermediate result between  $v_b$  and  $v_a$ . Figure 10(d) shows its corresponding 3D placement. Note that compared with the 3D placement shown in Figure 10(b), we now have three modules corresponding to two operations and one storage unit  $v_s$ . Therefore, the number of storage units is related to the schedule of the data-dependent operations. Figure 10(e) shows another scenario, where  $v_b$  starts two time units after  $v_a$  finishes. Figure 10(f) shows the corresponding 3D placement. Compared with the 3D placement shown in Figure 10(d), the duration of  $v_s$  is increased from one time unit to two time units. This is because the duration of  $v_s$  must cover the time difference between  $v_a$  and  $v_b$ . As a result, the duration of storage units is also related to the schedule of two data-dependent operations. Another observation from Figure 10 is that the starting time of  $v_s$  is equal to the ending time of  $v_a$  and the ending time of  $v_s$  is the same as the starting time of  $v_b$ , as shown in Figures 10(d) and (f). We need to satisfy the above requirements of storage units when solving the placement problem.

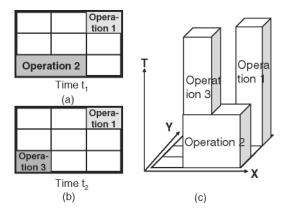

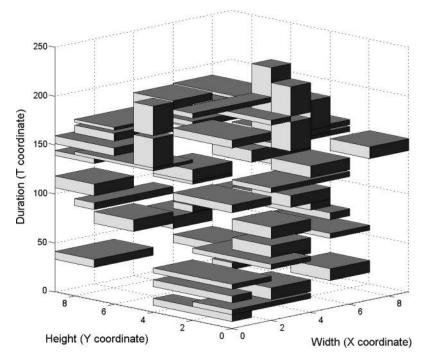

Now we present our T-tree based placement formulation. Due to the reconfigurability of biochips, the execution of a set of tasks can be viewed as a 3D floorplan as shown in Figure 11. The X and Y dimensions give the area of a

## 13:14 • P.-H. Yuh et al.

Fig. 11. (a) Two operations are executed at time t1. (b) At time t2, operation 3 starts to execute at the same physical location as operation 2. (c) The 3D modeling of the execution of the three operations.

biochip while the T dimension represents the duration of a bioassay. Suppose that both operations  $v_1$  and  $v_2$  are executed at time t1, as shown in Figure 11(a). Figure 11(b) shows that at time t2, we can perform operation  $v_3$  at the same physical location as operation  $v_3$  after operation  $v_2$  is finished. The execution of the three operations can be modeled as a set of 3D modules with their widths and heights (X and Y dimensions) representing the physical dimensions occupied by the operations in a biochip and its duration (T dimension) being the execution of a set of operations, as shown in Figure 11(c). Since the execution of a set of operations can be mapped to a 3D floorplan, we can apply the temporal floorplanning techniques to solve the placement problem of digital microfluidic biochips.

For each task in a sequencing graph, we create a unique node in a T-tree. Note that there are both reconfigurable and non-reconfigurable tasks in a biochip. For reconfigurable tasks and detection tasks, since we need to perform this type of tasks in the 2D microfluidic array, we model it as a 3D box. For non-reconfigurable tasks except the detection tasks, since the reservoirs and dispensing ports are outside the 2D microfluidic array as shown in Figure 1, we need only to consider the time aspect for this type of tasks. Therefore, we model it as a 3D line with both its width and height being zero.

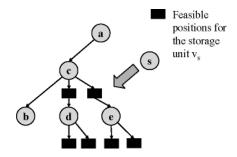

In this paragraph, we describe how we model the storage units. We create a node  $n_s$  for each storage unit  $v_s$ . Since  $v_s$  holds the intermediate data between two data-dependent tasks  $v_i$  and  $v_j$ ,  $v_s$  must satisfy the *storage constraint*. The storage constraint states that the starting time of  $v_s$  must be equal to the ending time of  $v_i$  and the ending time of  $v_s$  must be equal to the starting time of  $v_j$ . Figure 12 illustrates how to find the feasible locations for  $n_s$  in a T-tree to satisfy the storage constraint. Suppose that we want to find the feasible locations for  $n_s$  is the same as the ending time of  $v_i$ . Thus, based on the starting time of  $v_j$  is the starting time of  $v_i$  is the same as the ending time of  $v_i$ . Thus, based on the structure of T-tree, the starting time of  $v_c$  in Figure 12 is the same as the ending time of  $v_a$ , and the starting times of

Fig. 12. An example of finding the feasible locations for a storage unit in a T-tree. Suppose that tasks  $v_a$  and  $v_b$  need a storage unit  $v_s$ .

$v_b$ ,  $v_c$ , and  $v_d$  are the same. Based on above observation, the feasible locations of  $n_s$  are the middle or the right child of nodes  $n_b$ ,  $n_c$ , or  $n_d$ , as the black boxes shown in Figure 12. After placing  $n_s$  in its feasible location, we set the ending time of  $v_s$  as the starting time of  $v_b$ . Note that the duration of  $v_s$  is not fixed; it varies based on the starting time of  $v_b$ .

The design specification describes the fixed architecture, the limited assay completion time, and the resource constraints. We model the fixed architecture and limited assay completion time as the *fixed-cube constraint*. The fixed-cube constraint states that a feasible 3D floorplan must be within a 3D cube. To handle the resource constraints, we introduce the concept of the *virtual* precedence constraints. If two non-reconfigurable tasks are bound to the same non-reconfigurable resource, such as the same dispensing port, these two non-reconfigurable tasks cannot be executed at the same time. Therefore, we add an additional edge between these two tasks in the sequencing graph to satisfy the resource constraint. Note that there is no storage unit requirement in these additional edges.

## 5. THE FLOORPLANNING ALGORITHM

Our algorithm is based on the simulated annealing (SA) method [Kirkpatrick et al. 1983]. We adopt SA instead of genetic algorithm (GA) as our optimization method because it has been shown that SA is typically more efficient and economical than GA for the problems in electronic design automation (EDA). GA needs to maintain a set of solutions, called the population. At each iteration, GA needs to evaluate the fitness function for each solutions in the current population. On the other hand, SA maintains only two solutions—the current solution and the best one. At each iteration, SA needs only to evaluate the current solution. As a result, SA typically needs less CPU time than GA. Moreover, SA uses less memory than GA due to the smaller number of solutions maintained.

Before performing SA, we first cluster one generation operation with one reconfigurable operation to reduce the CPU time and to increase the chance of obtaining more compact 3D floorplans. During SA, given a feasible T-tree, we perturb it to obtain another feasible T-tree through a set of predefined SA operations. After perturbation, we perform a feasibility detection and tree reconstruction process to obtain a feasible topology with respect to the precedence

## 13:16 • P.-H. Yuh et al.

Fig. 13. (a) A sample sequencing graph. (b) A partial floorplan with  $v_f$  being scheduled long before  $v_k$  starts. (c) Another partial floorplan with  $v_f$  being scheduled right before  $v_k$  starts.

constraints and the storage constraints. Finally, a packing procedure that places all operations and optical detectors is invoked to evaluate the solution quality.

#### 5.1 Clustering of Generation and Reconfigurable Operations

In this section, we detail our clustering algorithm. The goal of the clustering algorithm is to obtain a more compact 3D floorplan and to reduce the CPU time by reducing unnecessary storage units. This clustering algorithm is motivated by two observations. First, a generation operation and a reconfigurable operation are always performed in sequence, since we need to first generate a droplet and then to perform reactions. Second, we may improve the solution quality (e.g., volume) and reduce the CPU time by reducing the amount of storage units required via clustering. Recall that we need a storage unit for two data-dependent tasks if they are not scheduled at consecutive time steps. The duration of this storage unit also varies based on the starting and ending times of these two tasks. Since the storage units occupy certain volumes, the number and duration of them have great effect on the total volume of a 3D floorplan. If we can minimize the volume of these storage units, we may obtain a more compact 3D floorplan. We use the sample sequencing graph shown in Figure 13(a) as an example. Figure 13(b) shows a partial floorplan. For simplicity, we only show the X and T dimensions.<sup>1</sup> In this floorplan, since task  $v_f$  finishes much earlier than task  $v_k$  starts, the storage unit  $v_s$  will have a very long duration. Therefore, we may obtain a less compact 3D floorplan due to the non-overlapping requirement among  $v_s$  and other tasks. On the other hand, Figure 13(c) shows another

<sup>&</sup>lt;sup>1</sup>For illustration purpose, in this figure, the width of the generation operation  $v_f$  is not zero.

ACM Journal on Emerging Technologies in Computing Systems, Vol. 3, No. 3, Article 13, Publ. date: November 2007.

partial floorplan. In this floorplan, since  $v_f$  finishes right before  $v_k$  starts, we do not need a storage unit between  $v_f$  and  $v_k$ . By scheduling a generation operation as near as its data-dependent reconfigurable operation, we can effectively minimize the unnecessary volume occupied by a storage unit. In this way, we have a higher chance to obtain a 3D floorplan with smaller area.

The idea of the proposed clustering algorithm is that: given a sequencing graph G, we randomly cluster one generation operation  $v_g$  with one reconfigurable operation  $v_r$  if there exist an edge between  $v_g$  and  $v_r$  in G. After clustering, the ending time of  $v_g$  is the same as the starting time of  $v_r$ . By this method, we do not need the storage unit between  $v_g$  and  $v_r$ . The other advantage is that we can reduce the number of nodes in a T-tree to speed up the packing process. However, one disadvantage is that we may potentially increase the assay completion time. The reason is as follows. Recall that we assign virtual precedence constraints among tasks that are bound to the same non-reconfigurable device. Suppose that there exists a virtual precedence constraint between two generation operations  $v_g$  and  $v_q$ . If we cluster  $v_g$  and  $v_r$ , we merge  $v_g$  and  $v_r$ into a new task  $v_l$ . So now we have a virtual precedence constraint between  $v_l$ and  $v_a$ . This means that  $v_a$  starts after  $v_l$  finishes rather than after  $v_{\sigma}$  finishes. Therefore, the assay completion time is potentially increased due to clustering. In order not to increase the assay completion time, we do not actually cluster  $v_g$  and  $v_r$  into a new task. In our current implementation, we add additional requirement on nodes  $n_g$  and  $n_r$  in a T-tree. We require that  $n_r$  will always be the left child of  $n_g$  in a T-tree. This requirement has the same effect as clustering two tasks, since the ending time of  $v_g$  is the same as the starting time of  $v_r$  if  $n_r$  is the left child of  $n_g$ . In our floorplanning algorithm, if we perform SA operation on  $n_g$ , we also perform the same SA operation on  $n_r$ . We also check if the two clustered nodes are in their correct positions in a T-tree during feasibility detection and tree reconstruction process, which will be presented in Section 5.5.

#### 5.2 Perturbation

The original SA operations defined in Yuh et al. [2004] contain Move, Swap, and Rotation. For the placement of digital microfluidic biochips, we introduce a new type of SA operations, called *Rebind*. Rebind is to bind a task to another functional resource. For a reconfigurable task, such as the mix operation, we randomly select a resource instance for this task. For example, we can change from a  $2 \times 2$ -array mixer to a  $2 \times 4$ -array mixer with different mixing times. For a non-reconfigurable task, we randomly change a task from one instance to another. For example, suppose that we have two optical detectors  $p_1$  and  $p_2$  for detection operations. For a detection operation  $v_d$  that originally uses  $p_1$ , we can rebind it to  $p_2$ . Note that since we add the virtual precedence constraints among tasks corresponding to the same non-reconfigurable resource instance, we modify these virtual precedence constraints after rebinding. For instance, when we bind  $v_d$  from  $p_1$  to  $p_2$ , we delete all virtual precedence constraints of  $v_d$  and add the virtual precedence constraints between all other tasks that are bound to  $p_2$  and  $v_d$ .

## 13:18 • P.-H. Yuh et al.

We now show how to add the virtual precedence constraints between tasks that are bound to the same non-reconfigurable device when performing the Rebind SA operation. We add the virtual precedence constraints among tasks bound to the same non-reconfigurable device based on the *execution level*, or lv(i), of each operation  $v_i$ . The intuition is that if lv(i) is larger than lv(j), then operation  $v_i$  is executed before operation  $v_j$ . We add a virtual precedence constraint from  $v_i$  to  $v_j$  if lv(i) is larger than lv(j). Given a sequencing graph G, we can recursively calculate lv(i) for each task  $v_i$  in G. We first assign lv(i) = 0for all tasks  $v_i$  with zero out-degree in G. For example, in Figure 13(a), lv(l) and lv(m) are both zero. We then delete all assigned tasks and assign lv(i) = 1 for all remaining tasks with zero out-degree in G. For example, in Figure 13(a), lv(j)and lv(k) are both one. The above process repeats until all tasks are assigned its execution level.

We also enhance the original SA operations to handle the fixed-cube constraint. We bias the Move operation based on the probability of violating the fixed-cube constraint in each dimension. Let  $k_w$   $(k_h, k_t)$  be the number of floorplans whose width (height, completion time) exceeds the user-specified width (height, completion time) in the last r iterations. In this paper, we set r equal 500. We bias the selection of the destination of the Move operation based on the values  $k_w/r$ ,  $k_h/r$ , and  $k_t/r$ . For example, a larger  $k_w/r$  implies that it is more difficult to fit the floorplans to the 3D cube in the X direction. Therefore, we should try to place tasks along the Y or T directions to satisfy the fixed-cube constraint.

## 5.3 Placement of Optical Detectors

In this section, we describe how to place the optical detectors in our algorithm. After the chemical reaction among droplets, we need optical detectors to detect the reaction results. We need to determine the locations of these optical detectors during floorplanning. These detectors are fixed after fabrication. Therefore, if two detection operations map to the same optical detector, they should be placed at the same physical location. Note that the segregation cells are also needed for the optical detectors to avoid the optical interference.

Suppose that two detection operations  $v_i$  and  $v_j$  are bound to the same optical detector and we first determine the location of  $v_i$ . The basic idea is that we simultaneously determine the locations of  $v_i$  and  $v_j$ . Once the locations of  $v_i$ and  $v_j$  are determined, the location of the optical detector is also determined. Note that when placing the detection operations, we also warp these operations with the segregation cells. By this method, we can guarantee that the optical detectors are warped with the segregation cells after floorplanning. After determining the location of  $v_i$ , we set  $v_j$  at the same location as  $v_i$ . The original packing algorithm of T-tree maintains a list L to store all tasks whose locations are already determined [Yuh et al. 2004]. Finally, we add  $v_j$  into L to indicate that the location of  $v_j$  is already determined. Note that we need to check if  $v_j$ overlaps with any other tasks in L. If  $v_j$  overlaps with some tasks, we shift both  $v_i$  and  $v_j$  along the X direction to avoid the overlap.

#### 5.4 Cost Function

Our goal is to simultaneously optimize the biochip area and assay completion time under the design specification. Therefore, the cost function  $\Phi$  used in our algorithm is given by

$$\Phi = \alpha V / V_{norm} + \beta S / s_{norm} + \gamma M, \qquad (1)$$

where V is the volume of the 3D floorplan, S is the sum of the volume of all storage units,  $V_{norm}$  is the normalized volume,  $S_{norm}$  is the normalized sum of the volumes of all storage units, and M is the penalty term for fixed-cube constraint.  $\alpha$ ,  $\beta$ , and  $\gamma$  are user-specified constants. M is defined as

$$M = \frac{max(W_{f} - W_{p}, 0) \times W_{f}}{N_{w}^{2}} + \frac{max(H_{f} - H_{p}, 0) \times H_{f}}{N_{h}^{2}} + \frac{max(T_{f} - T_{p}, 0) \times T_{f}}{N_{e}^{2}}, \qquad (2)$$

where  $N_w$   $(N_h, N_t)$  is the normalized width (height, assay completion time),  $W_p$   $(H_p, T_p)$  and  $W_f$   $(H_f, T_f)$  denote the width (height, assay completion time) of the design specification and a 3D floorplan, respectively. Since we must pack all modules into a pre-defined 3D cube, we penalize the excessive width, height, and completion time in the cost function. The rationale behind M is that when SA minimizes the cost function, it automatically minimizes the penalty term. Thus, we can automatically satisfy the fixed-cube constraint.

#### 5.5 Feasibility Detection and Tree Reconstruction

After perturbation, we perform feasibility detection and tree reconstruction to satisfy all precedence constraints and storage constraints. We enhance the feasibility detection and the iterative tree reconstruction process proposed in Yuh et al. [2004] with the consideration of the storage constraints. After obtaining a feasible topology of a T-tree, we invoke the packing procedure to determine the physical locations of all tasks.

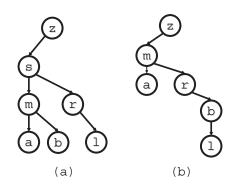

Given a T-tree H, we first check if a clustered node  $n_i$  is the left child of another clustered node  $n_j$ . If not, we Move  $n_i$  to the position of the left child of  $n_j$ . Then we check if every storage unit is in one of its feasible positions. If a storage unit  $n_s$  is not in one of its feasible positions, we Move  $n_s$  to one of its feasible positions. Note that since we modify the topology of H during the tree reconstruction process, the duration of each storage unit may change. To simplify our algorithm, we thus restrict every storage unit not to have its left child. By doing so, the starting time of a task will not be affected by any storage unit during the tree reconstruction process. Next we explain how to remove the left child of a storage unit. Suppose that a storage unit  $v_s$  stores the result of task  $v_a$  and  $n_k$  is the left child of  $n_s$  in H. We perform the move subtree procedure described below to move the subtree rooted by  $n_k$  to another place in H. First we choose one node  $n_z$  in the subtree rooted by  $n_a$  but not in

Fig. 14. The example of moving a subtree rooted by  $n_k$  as the left subtree of  $n_z$ . (a) A T-tree before moving the subtree rooted by  $n_k$ . (b) A T-tree after moving the subtree rooted by  $n_k$  as the left subtree of  $n_z$ .

the subtree rooted by  $n_k$ . Then we randomly move the subtree rooted by  $n_k$  to the positions of the left subtree, middle subtree, or right subtree of  $n_z$  based on the values of  $k_w/r$ ,  $k_h/r$ , and  $k_t/r$  defined in Section 5.2. For example, if  $k_t/r$  is large, then we have lower probability to move the subtree rooted by  $n_k$  to the position of the left subtree of  $n_z$ . Without loss of generality, assume that we move the subtree rooted by  $n_k$  to the position of the left subtree of  $n_z$ . The other two cases can be handled similarly. First, if  $n_z$  has no left child, then we can simply move the subtree rooted by  $n_k$  to the position of the left subtree of  $n_z$ . Second, if  $n_z$  has its left child, we need to consider two situations:

- (1)  $n_k$  has its left child: In this case, we first move the subtree rooted by  $n_z$ 's left child to the position of the left subtree of  $n_k$ . Then we move the subtree originally rooted by  $n_k$ 's left child to the position of the left subtree of  $n_f$ , where  $n_f$  is in the subtree rooted by  $n_k$  with no left child.

- (2)  $n_k$  has no left child: In this case, we can simply move the subtree rooted by  $n_z$ 's left child to the position of the left subtree of  $n_k$ .

Figure 14 gives an example if we move the subtree rooted by  $n_k$  to the position of the left subtree of  $n_z$ . Figure 15 summaries the move subtree procedure.

Once all storage units are in their feasible positions and do not have their left child, we traverse H to obtain the starting time of each task. Next, we check the precedence constraints and reconstruct H if necessary based on the method proposed in Yuh et al. [2004]. The main loop terminates when the topology of H is not changed, which means that all precedence constraints and storage constraints are satisfied. Then we assign the duration of each storage unit and adjust the number of storage units by deleting an unused storage unit and/or inserting a new one.

Note that we need to satisfy all precedence constraints after deleting or inserting a storage unit. It is easy to observe that inserting a new storage unit into one of its feasible positions does not affect the starting time of other operations. Thus, we do not violate the precedence constraints after insertion. However, deleting a storage unit with the Deletion SA operation presented

Placement of Defect-Tolerant Digital Microfluidic Biochips

#### Subroutine: Move Subtree $(H_k, n_z)$

$H_k$ : the subtree rooted by  $n_k$ ;  $n_z$ : the destination node; 1 Determine to make  $H_k$  as the left, middle or right 2 subtree of  $n_z$  based on the values  $k_w/r$ ,  $k_h/r$ , and  $k_t/r$ ; 3 if Make  $H_k$  as the left subtree of  $n_z$ if  $n_z$  has no left child 4 5Make  $H_k$  as the left subtree of  $n_z$ ; 6 else if  $n_z$  has its left child  $n_l$ 7Make  $H_k$  as the left subtree of  $n_z$ ; 8 Make  $H_l$  as the left subtree of  $n_k$ ; 9 **if**  $n_k$  originally has its left child  $n_p$ 10Make  $H_p$  as the left subtree of  $n_f$ , where 11  $n_f$  is in  $H_k$  and  $n_f$  has no left child; 12 else if Make  $H_k$  as the middle or right subtree of  $n_z$ 13// Similar to above method;

Fig. 15. Summary of the Move Subtree subroutine.

in Yuh et al. [2004] may potentially violate the precedence constraints. In the following paragraphs, we present our storage adjustment process and how to modify the Deletion SA operation to satisfy the precedence constraints when deleting a storage unit.

Suppose that we want to delete a storage unit  $n_s$ . It is easy to delete  $n_s$  if  $n_s$  is a leaf or  $n_s$  has only one child. If  $n_s$  has more than one child, the original Deletion SA operation randomly chooses one of  $n_s$ 's child  $n_c$  and place  $n_c$  at the original position of  $n_s$ . Then we choose one of  $n_c$ 's child and place it at the original position of  $n_c$ . The process continues until a leaf node is encountered. After Deletion, the starting time of all nodes in the subtree rooted by  $n_c$  may be changed. Thus, the precedence constraints may be violated.

In this article, we modify the original Deletion SA operation when deleting  $n_s$  with two children.<sup>2</sup> Suppose that  $n_m$  is the middle child and  $n_r$  is the right child of  $n_s$ . When deleting  $n_s$ , instead of the node  $n_m$  itself, we place the *subtree* rooted by  $n_m$  at the original position of  $n_s$ . Then we make  $n_r$  as the right child of  $n_m$ . If  $n_m$  originally has no right child, then we are finished. Otherwise, let  $n_b$  be the original right child of  $n_m$ . We move the subtree rooted by  $n_b$  to the position of the right subtree of  $n_r$  if  $n_r$  has no right child. If  $n_r$  has its right child  $n_l$ , we find a node  $n_f$  in the subtree rooted by  $n_r$  with the same starting time as  $v_r$  and having either no middle or no right child. Then we move the subtree rooted by  $n_l$  to the position of the storage unit  $n_s$  with two children. Finally, Figures 17 and 18 summarize the storage adjustment process and the feasibility detection and tree reconstruction process, respectively.

13:21

$<sup>{}^{2}</sup>n_{s}$  has at most two children since we do not allow  $n_{s}$  to have its left child.

ACM Journal on Emerging Technologies in Computing Systems, Vol. 3, No. 3, Article 13, Publ. date: November 2007.

Fig. 16. The example of deleting a storage unit  $n_s$ . (a) A T-tree before deleting  $n_s$  (b) A T-tree after deleting  $n_s$ .

| Subroutine: Storage Adjustment (H)                      |

|---------------------------------------------------------|

| H: A T-tree;                                            |

| 1 for all storage unit $v_s$                            |

| 2 if $v_s$ is required but $n_s$ is not in $H$          |

| 3 Insert $n_s$ to one of its feasible positions;        |

| 4 else if $v_s$ is not needed but $n_s$ is in $H$       |

| 5 Delete $n_s$ ;                                        |

| 6 <b>if</b> $n_s$ has only one child $n_o$              |

| 7 Place the subtree rooted by $n_o$ at the original     |

| 8 position of $n_s$ ;                                   |

| 9 else if $n_s$ has two children                        |

| 10 Let $n_m$ $(n_r)$ be the middle (right) child        |

| 11 of $n_s$ ;                                           |

| 12 Place the subtree rooted by $n_m$ at the position    |

| 13 of $n_s$ ;                                           |

| 14 Let $n_b$ be the right child of $n_m$ ;              |

| 15 Make the subtree rooted by $n_b$ as the right        |

| 16 subtree of $n_r$ ;                                   |

| 17 <b>if</b> $n_r$ originally has its right child $n_l$ |

| 18 Find a node $n_f$ in the subtree rooted by $n_r$     |

| 19 with $t_f = t_r$ and having either no middle or      |

| 20 no right child;                                      |

| 21 Insert the subtree rooted by $n_l$ as the            |

| 22 middle or right subtree of $n_f$ ;                   |

|                                                         |

Fig. 17. Summary of the storage adjustment process.

## 6. DEFECT TOLERANCE

In this section, we show how to extend the aforementioned temporal floorplanning algorithm to handle the defect tolerant issue. With the standard microfabrication techniques [Fair et al. 2003] and the synthesis result, a digital microfluidic biochip can be fabricated. However, due to the underlying mixing technology, the microfluidic biochips have unique defects and failure mechanism [Su et al. 2006]. The reconfigurability of the biochips can bypass the

#### Algorithm: Feasibility Detection (H)

H: a T-tree;

- 1 Set the durations of all storage units  $v_s$  as zero;

- 2 repeat

- 3 if a clustered node  $n_i$  is not the left child of node  $n_j$

- 4 Move  $n_i$  to the position of the left child of  $n_j$ ;

- 5 **else if** a storage  $n_s$  is not in its feasible position

- Move  $n_s$  to one of its feasible positions;

- 7 else if  $n_s$  has its left child

- 8 Assume that  $v_s$  stores the result of  $v_a$ ;

- 9 Find a node  $n_z$  in the subtree rooted by  $n_a$  but not

- 10 in the subtree rooted by  $n_s$ 's left child  $n_k$ ;

- 11 Move Subtree (the subtree rooted by  $n_k, n_z$ );

- 12 else

$\mathbf{6}$

- 13 Traverse H to obtain the starting time of

- 14 each task;

- 15 Check the precedence constraints and

- 16 reconstruct H;

- 17 **until** the topology of H is fixed

- 18 Determine the duration of all storage units;

- 19 Storage Adjustment(H);

- 20 **Output:** *H* with the feasible topology.

Fig. 18. Summary of the feasibility detection and tree reconstruction process.

defective cells to tolerate the defects due to fabrication. Moreover, the nonreconfigurable device, such as the detectors, may be unavailable due to the existence of the defects. We need to rebind the operations from an unavailable detector to other available detectors. Note that after fabrication, the locations of the non-reconfigurable devices are fixed. We cannot move these detectors during floorplanning.

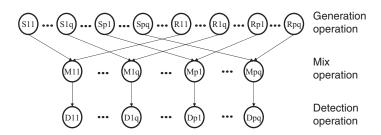

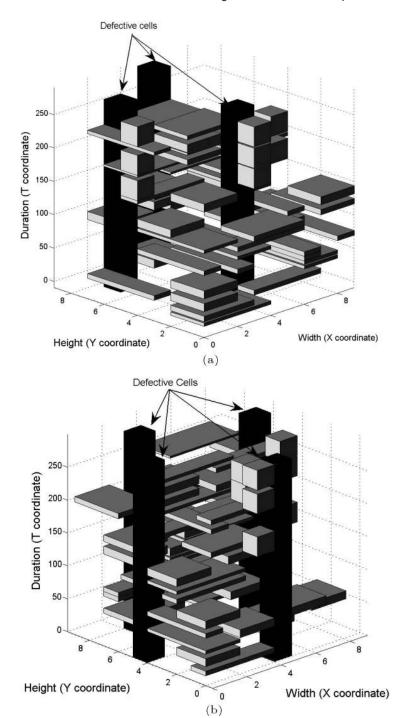

The central idea of our algorithm is that we model each defective cell as an obstacle. If a cell c located at (x, y) becomes faulty, we create an obstacle  $d_c$  located at (x, y) with its duration being the same as the assay completion time. In the packing process, we do not allow the overlap among tasks and obstacles. By this method, we can guarantee that no task will overlap with obstacle  $d_c$ , and thereby avoid to place tasks on defective cells.

We now present our obstacle avoidance algorithm to avoid overlaps among reconfigurable operations and obstacles. As mentioned above, we create an obstacle for each defective cell. During the packing process, we detect if a task  $v_i$ overlaps with any obstacle  $d_c$ . If  $v_i$  overlaps with an obstacle  $d_c$ , we first calculate the X-span  $s_x$  and Y-span  $s_y$ . The X-span (Y-span) represents how far we should shift  $v_i$  along the X (Y) direction to avoid the overlap with  $d_c$ . In this paper, we set  $s_x$  ( $s_y$ ) as the difference between  $x'_c$  and  $x_i$  ( $y'_c$  and  $y_i$ ), where ( $x'_c$ ,  $y'_c$ ) is the up-right coordinate of  $d_c$ . We shift  $v_i$  along the direction that results in smaller movement distance. That is, if  $s_x < s_y$ , we shift  $v_i$  in the X direction; otherwise, we shift  $v_i$  in the Y direction. Figure 19 summaries our obstacle avoidance process.

ACM Journal on Emerging Technologies in Computing Systems, Vol. 3, No. 3, Article 13, Publ. date: November 2007.

13:23

Algorithm: Obstacle Avoidance (v, D)

| -                                         |  |

|-------------------------------------------|--|

| v: a task;                                |  |

| D: set of obstacles;                      |  |

| l repeat                                  |  |

| 2 Scans all obstacles in $D$ ;            |  |

| 3 <b>if</b> $v$ overlaps with $d_c \in D$ |  |

| 4 Let $s_x$ be $ x_v - x_c' ;$            |  |

| 5 Let $s_y$ be $ y_v - y'_c ;$            |  |

| $\delta$ if $s_x < s_y$                   |  |

| 7 Set $x_v$ equal $x'_c$ ;                |  |

| 8 else                                    |  |

| 9 Set $y_v$ equal $y'_c$ ;                |  |

| 10 Update the x-coordinate of $v$ ;       |  |

|                                           |  |

11 until v overlaps no obstacles in D;

Fig. 20. The sequencing graph of colorimetric protein assay [Su and Chakrabarty 2005b].

#### 7. EXPERIMENTAL RESULTS

Our algorithm was implemented in the C++ programming language and run on a 1.066 GHz SUN Blade 1500 machine with 4 GB memory. We implemented the unified synthesis and placement algorithm proposed in Su and Chakrabarty [2005b] and the 3D-subTCG representation on the same machine. For 3D-subTCG, we used the same SA engine as T-tree. We modified the operations of 3D-subTCG to satisfy the storage constraint at each perturbation. We also applied the clustering algorithm proposed in Section 5.1 to 3D-subTCG for fair comparison. For all experiments, we set  $\alpha = \frac{1}{21.5}$ ,  $\beta = \frac{0.5}{21.5}$ , and  $\gamma = \frac{20}{21.5}$ . We also assumed that there exists one segregation cell between any two operations. All experimental results are the best result obtained by simulated annealing.

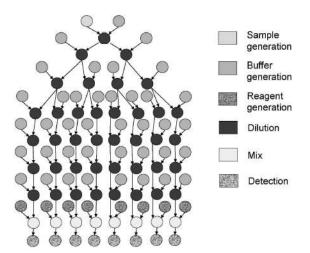

We evaluated our placement algorithm with two bioassays: the colorimetric protein assay [Srinivasan et al. 2004] and the multiplexed in-vitro diagnostics [Su and Chakrabarty 2004]. Figure 20 shows the sequencing graph of the

Fig. 21. The sequencing graph of multiplexed in-virto diagnostics [Su and Chakrabarty 2004].

colorimetric protein assay while Figure 21 shows the multiplexed in-virto diagnostics with p samples (Plasma, Serum, Urine, and Saliva) and q reagents (glucose, lactate, pyruvate, and glutamate). For the colorimetric protein assay, we applied the same design specification (resource constraint) and used the same microfluidic module library as Su and Chakrabarty [2005b]. We assumed that there is only one reservoir/dispensing port for sample fluid, two such ports for buffer fluid, two ports for reagent fluid, and one port for waste fluid. We also assumed that there are at most four optical detectors integrated on the biochip [Su and Chakrabarty 2005b]. For the multiplexed in-virto diagnostics, we used the same design specifications (resource constraint) as Su and Chakrabarty [2004]. We assumed that there is one reservoir/dispensing port for each type of samples and reagents and one optical detector for each enzymatic assay [Su and Chakrabarty 2004]. However, since [Su and Chakrabarty 2004] did not specify the width, height, and duration of each reconfigurable operation, we generated the areas/durations of each type of the mix operations based on the ratio of areas/durations of each reconfigurable operation in Su and Chakrabarty [2005b]. Table I shows the microfluidic module library used for the multiplexed in-vitro diagnostics.

First, we assumed that no defective cells exist. Table II summarizes the result of the colorimetric protein bioassay. Column 2 lists four different design specifications (fixed-cube constraints). We report the resulting volume (area times assay completion time) and CPU time (in seconds). As shown in this table, our algorithm can meet all design specifications (fixed-cube constraints) while both [Su and Chakrabarty 2005b] and 3D-subTCG cannot. More importantly, [Su and Chakrabarty 2005b] (3D-subTCG) requires, on average, 1.68X (1.61X) larger volume and 4.32X (39.96X) longer CPU time than our algorithm. Table III shows the result of the multiplexed in-vitro diagnostics. In this experiment, we used three examples for evaluation. Column 1 shows the number of types of samples and reagents, and column 2 lists the type of samples and reagents used in each example. For each example, we applied three different design specifications, as listed in column 3. We also report the volume and CPU time in this experiment. As shown in this table, our algorithm can meet all design specifications (fixed-cube constraints) while both 3D-subTCG and Su and Chakrabarty [2005b] cannot. Su and Chakrabarty [2005b] obtains larger volumes in all three examples (3.48X, 4.90X, and 3.84X) with longer CPU times (9.71X, 9.81X, and 19.19X, respectively); 3D-subTCG also obtains larger

## 13:26 • P.-H. Yuh et al.

| Operation       | Resource               | Duration (sec.) |

|-----------------|------------------------|-----------------|

| Dispense        | on-chip                | 2               |

| Mix (plasma)    | $2 \times 4$ -array    | 3               |

|                 | 2 	imes 3-array        | 6               |

|                 | $2 \times 2$ -array    | 10              |

|                 | 1	imes 4-linear array  | 5               |

| Mix (Serum)     | $2 \times 4$ -array    | 2               |

|                 | 2 	imes 3-array        | 4               |

|                 | $2 \times 2$ -array    | 6               |

|                 | 1	imes 4-linear array  | 3               |

| Mix (Urine)     | $2 \times 4$ -array    | 3               |

|                 | $2 \times 3$ -array    | 5               |

|                 | $2 \times 2$ -array    | 8               |

|                 | 1 	imes 4-linear array | 4               |

| Mix (Saliva)    | $2 \times 4$ -array    | 4               |

|                 | $2 \times 3$ -array    | 8               |

|                 | $2 \times 2$ -array    | 12              |

|                 | 1	imes 4-linear array  | 6               |

| Opt (glucose)   | LED + Photodiode       | 10              |

| Opt (lactate)   | LED + Photodiode       | 8               |

| Opt (pyruvate)  | LED + Photodiode       | 12              |

| Opt (glutamate) | LED + Photodiode       | 10              |

| Storage         | single cell            | N/A             |

Table I. The Microfluidic Module Library for the In-vitro Diagnostics

Table II. The Experimental Result of the Colorimetric Protein Bioassay

| r                   |                                                          |                                                                                                        |                                          |                                                                       |                                      |  |

|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------|--------------------------------------|--|

|                     |                                                          | [Su and Chakrabarty 2005b]                                                                             |                                          | T-tre                                                                 | ee                                   |  |

|                     | Design                                                   |                                                                                                        | CPU                                      |                                                                       | CPU                                  |  |

| Bioassay            | Spec.                                                    | Volume                                                                                                 | Time (sec.)                              | Volume                                                                | Time (sec.)                          |  |

| Protein             | 10 	imes 10 	imes 400                                    | 10 	imes 10 	imes 349                                                                                  | 275.05                                   | $9 \times 9 \times 241$                                               | 78.03                                |  |

|                     | 10 	imes 10 	imes 360                                    | 9	imes10	imes339                                                                                       | 270.02                                   | $10\times 9\times 211$                                                | 57.27                                |  |

|                     | 11 	imes 11 	imes 320                                    | 10 	imes 11 	imes 313                                                                                  | 266.16                                   | 10 	imes 10 	imes 221                                                 | 68.32                                |  |

|                     | $9\times 9\times 400$                                    | $(9 \times 10 \times 390)^*$                                                                           | 293.21                                   | $9 \times 9 \times 240$                                               | 65.21                                |  |

| Average             |                                                          | 1.68                                                                                                   | 4.32                                     | 1.00                                                                  | 1.00                                 |  |

|                     |                                                          | 3D-subTCG                                                                                              |                                          |                                                                       |                                      |  |

|                     |                                                          | 3D-subT(                                                                                               | CG                                       | T-tre                                                                 | e                                    |  |

|                     | Design                                                   | 3D-subT0                                                                                               | CG<br>CPU                                | T-tre                                                                 | ee<br>CPU                            |  |

| Bioassay            | Design<br>Spec.                                          | 3D-subTO<br>Volume                                                                                     |                                          | T-tre<br>Volume                                                       | -                                    |  |

| Bioassay<br>Protein | U                                                        |                                                                                                        | CPU                                      |                                                                       | CPU                                  |  |

|                     | Spec.                                                    | Volume                                                                                                 | CPU<br>Time (sec.)                       | Volume                                                                | CPU<br>Time (sec.)                   |  |

|                     | $\frac{\text{Spec.}}{10 \times 10 \times 400}$           | $\begin{array}{c} \text{Volume} \\ 10 \times 10 \times 239 \end{array}$                                | CPU<br>Time (sec.)<br>2497.94            | $\begin{array}{c} \text{Volume} \\ 9 \times 9 \times 241 \end{array}$ | CPU<br>Time (sec.)<br>78.03          |  |

|                     | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ | $\begin{tabular}{l} Volume \\ \hline 10 \times 10 \times 239 \\ 10 \times 10 \times 331 \end{tabular}$ | CPU<br>Time (sec.)<br>2497.94<br>2226.71 | Volume $9 \times 9 \times 241$ $10 \times 9 \times 211$               | CPU<br>Time (sec.)<br>78.03<br>57.27 |  |

$Volume = Area \times Completion Time.$  ()\*: the result cannot meet the design specification.

volumes in all three examples (2.50X, 2.05X, and 1.86X, respectively) with longer CPU times (38.52X, 23.89X, and 41.39X, respectively). The two experimental results clearly show the efficiency and effectiveness of our algorithm with different bioassays and design specifications. The results of 3D-subTCG also support our claim in Section 3.5 that the T-tree is a more suitable 3D representation for the placement problem of biochips. Figure 23 shows the placement

|                                                                                                          |                                                                                                                                                |                                                                                                                                                                              | [Su and Chakrabarty 2005b]                                                                                                                                                                                                                                                     |                                                                                                               | T-tree                                                                                                                                                                                                                                                                                                               |                                                                                                  |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|