# Plasma Enhanced Atomic Layer Deposition of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> MIM Capacitors

Dustin Z. Austin, Member, IEEE, Derryl Allman, Member, IEEE, David Price, Member, IEEE, Sallie Hose, and John F. Conley, Jr., Fellow, IEEE

Abstract—Metal–insulator–insulator–metal (MIIM) capacitors with bilayers of  $Al_2O_3$  and  $SiO_2$  are deposited at 200 °C via plasma enhanced atomic layer deposition. Employing the cancelling effect between the positive quadratic voltage coefficient of capacitance ( $\alpha$ VCC) of  $Al_2O_3$  and the negative  $\alpha$ VCC of  $SiO_2$ , devices are made that simultaneously meet the International Technology Roadmap for Semiconductors 2020 projections for capacitance density, leakage current density, and voltage nonlinearity. Optimized bilayer  $Al_2O_3/SiO_2$  MIIM capacitors exhibit a capacitance density of 10.1 fF/ $\mu$ m<sup>2</sup>, a leakage current density of 6.8 nA/cm<sup>2</sup> at 1 V, and a minimized  $\alpha$ VCC of -20 ppm/V<sup>2</sup>.

Index Terms—Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>, metal-insulator-metal capacitors, MIMCAPs, MIIM, plasma enhanced atomic layer deposition, PEALD, quadratic voltage coefficient of capacitance,  $\alpha$ VCC.

## I. INTRODUCTION

**B** ACK end of line (BEOL) metal-insulator-metal capacitors (MIMCAPs) reduce the need for discrete off-board components and have become core passive devices in integrated circuits (IC). Applications of MIMCAPs include analog-to-digital converters, analog noise filters, DC voltage decoupling, and electrostatic discharge protection. According to the 2020 node of the International Technology Roadmap for Semiconductors (ITRS), scaling the area of these devices for analog/mixed-signal ICs will require increasing capacitance density (to greater than 10 fF/ $\mu$ m<sup>2</sup>) while simultaneously maintaining low voltage nonlinearity (less than 100 ppm/V<sup>2</sup>, characterized by the quadratic voltage coefficient of capacitance,  $\alpha$ VCC) and low leakage current density (less than 10 nA/cm<sup>2</sup> at 1V) [1]. In addition to these conflicting performance requirements, BEOL processing allows for temperatures of no more than 400 °C [2].

Increasing capacitance density may be achieved either by decreasing the insulator film thickness or by introducing high dielectric constant ( $\kappa$ ) materials. Simply decreasing the insulator film thickness leads to increased tunneling leakage

Manuscript received February 11, 2015; revised March 10, 2015; accepted March 10, 2015. Date of publication March 16, 2015; date of current version April 22, 2015. This work was supported in part by ON Semiconductor and in part by ONAMI. The review of this letter was arranged by Editor A. Chin.

D. Z. Austin and J. F. Conley, Jr. are with the School of Electrical Engineering and Computer Science, Oregon State University, Corvallis, OR 97331 USA (e-mail: john.conley@oregonstate.edu).

D. Allman, D. Price, and S. Hose are with ON Semiconductor, Technology Development, Gresham, OR 97030 USA.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2015.2412685

as well as increased voltage nonlinearity [3], [4]. On the other hand, most high- $\kappa$  insulators also have drawbacks such as large positive  $\alpha$ VCCs, small metal-insulator barrier heights, and increased conduction through defect levels [5]. Thus, single insulator devices have been unable to simultaneously meet all three performance projections of future ITRS nodes. A promising approach to meeting all of these competing performance needs is to use multi-layer insulator stacks to combine materials with complementary properties (e.g. a high- $\kappa$ , positive  $\alpha$ VCC insulator with a low leakage, negative  $\alpha VCC$  insulator) [6]–[12]. Previous reports of multi-insulator structures that meet or come close to meeting upcoming ITRS projections are listed in Table II. Note however that these previous studies employ either complex or uncommon materials, break vacuum between insulating layers, or are processed outside the specified BEOL temperature limit.

In the present work, Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> bilayers are investigated for potential use in BEOL RF MIMCAPs. Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> are attractive due to their large metal-insulator barrier heights, high dielectric breakdown strength, and common usage in IC fabrication. In addition, SiO<sub>2</sub> is one of the few materials to exhibit a negative  $\alpha$ VCC and thus can be used in combination with the positive  $\alpha VCC$  of Al<sub>2</sub>O<sub>3</sub> to target ultra-low device voltage nonlinearity through  $\alpha VCC$  canceling [7]. Plasma enhanced atomic layer deposition (PEALD) is used to deposit high quality pin-hole free nanolaminate Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> stacks at low temperature without breaking vacuum. The selflimiting reactions of PEALD enable precise control over film thickness, which is critical for optimizing the  $\alpha$ VCC cancelling effect for ultra-thin films. The capacitance density, leakage current density, and aVCC of Al2O3/SiO2 MIIMCAPs are benchmarked against future ITRS projections.

#### II. EXPERIMENTAL

Si/SiO<sub>2</sub>/Ta/TaN substrates with the SiO<sub>2</sub> layer planarized via chemical mechanical polishing were used as the bottom electrodes. PEALD of Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> was performed at 200 °C in a Picosun SUNALE R-200 reactor using alternating N<sub>2</sub>-purge-separated pulses of O<sub>2</sub> and either trimethy-laluminum (TMA) or bis(diethylamino)silane (BDEAS), respectively. TMA was held at 17 °C and BDEAS held at 55 °C. The deposition rates of Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> were approximately 0.10 nm/cycle and 0.11 nm/cycle, respectively. The Al<sub>2</sub>O<sub>3</sub> layer was always deposited first. 250  $\mu$ m diameter evaporated Al dot top contacts with areas of ~0.05 mm<sup>2</sup>

0741-3106 © 2015 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

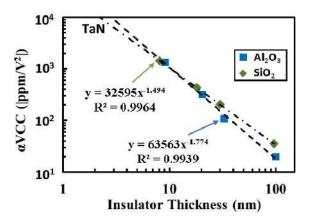

Fig. 1. Plot of  $\alpha$ VCC for Al<sub>2</sub>O<sub>3</sub> (blue squares) and  $|\alpha$ VCC| for SiO<sub>2</sub> (green diamonds) vs. film thickness (d<sub>ox</sub>). Dashed lines indicate power law fits.

were defined via shadow mask. The area of each device was measured and used for area normalizations. The average error in the area measurement is found to be +/-1.8%. Film thickness of select samples was measured using either an FEI Tecnai F20 high-resolution transmission electron microscope (TEM) or a J. A. Woollam M2000 spectroscopic ellipsometer. 100 kHz capacitance vs. voltage (CV) measurements were conducted using an Agilent E4980. Current vs. voltage (IV) measurements were taken using an Agilent B1500A. All electrical tests were conducted with the bottom electrode held at ground and performed in the dark at a controlled 25 °C. CV measurements were swept to approximately one-half breakdown voltage in order to avoid excessive stress during testing. To reduce displacement current, CV and IV measurements were performed at sweep rates of 0.2 V/s.

# **III. RESULTS AND DISCUSSION**

The voltage nonlinearity of MIMCAPs can be described by the quadratic equation,  $\Delta C/C_0 = \alpha V^2 + \beta V$ . Shown in Fig. 1, the  $\alpha VCC$  for Al<sub>2</sub>O<sub>3</sub> and  $|\alpha VCC|$  for SiO<sub>2</sub> are plotted together as a function of single layer insulator thickness. A simple power law was found to fit well the thickness dependence of  $\alpha VCC$ . Combining the power law fits with the capacitive voltage divider equation, approximate layer thicknesses were estimated for Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> bilayers that simultaneously meet ITRS projections for capacitance density and  $\alpha VCC$ .

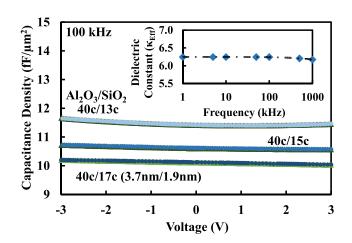

Shown in Fig. 2 are forward/reverse capacitance density vs. voltage sweeps for MIIM devices with 40c of Al<sub>2</sub>O<sub>3</sub> and either 13c, 15c, or 17c of SiO<sub>2</sub>, where "c" represents the number of PEALD cycles. As the difference in thickness between these ultra-thin film stacks is difficult to measure accurately, the number of PEALD cycles is used for identification. The 40c/17c Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> MIIM devices (measured via TEM to be approximately 3.7 nm/1.9 nm) were found to meet the ITRS 2020 projection for capacitance density with 10.1 fF/ $\mu$ m<sup>2</sup> and a minimized  $\alpha$ VCC of -20 ppm/V<sup>2</sup>. Note that optimized  $\alpha$ VCC values are not exactly as predicted by simple theory which considers only "bulk"  $\alpha$ VCC mechanisms [7].  $\alpha$ VCC mechanisms are not well understood [4] and

Fig. 2. Forward (blue) and reverse (green) sweeps of capacitance density vs. voltage for  $TaN/Al_2O_3/SiO_2/Al$  stacks targeting ITRS 2020. Inset: the effective dielectric constant vs. frequency for the 3.7nm/1.9nm device.

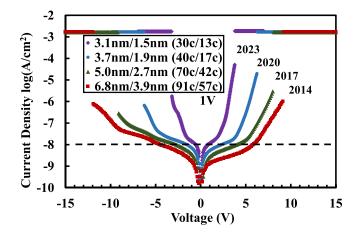

Fig. 3. Current density vs. voltage sweeps for TaN/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/Al stacks targeting various ITRS nodes. The estimated thickness and number of PEALD cycles for each insulator pair are included in the legend.

the discrepancy is likely due to contributions of secondary nonlinearity mechanisms [12] such as electrode effects [13], [14]. As shown in the inset, the effective dielectric constant of these devices shows little frequency dependence up to 1 MHz. A slight negative  $\beta$  can be observed for all of these devices, which might be attributed to the electrode work function difference. The thickness control of PEALD is a clear advantage for minimizing  $\alpha$ VCC. As seen in Fig. 2, the difference between the device with 300 ppm/ $V^2$ (40c/15c) and the device with  $-20 \text{ ppm/V}^2$  (40c/17c), was only 2 PEALD cycles of SiO<sub>2</sub>.

Current density vs. voltage sweeps for Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> stacks targeting future ITRS nodes are shown Fig. 3. The small asymmetry seen between positive and negative polarity likely arises from (i) the work function difference of Al (4.2 eV) vs. TaN (4.6 eV) electrodes and (ii) the presence of deep level defects in the SiO<sub>2</sub> which may enable trap-assisted-tunneling at low bias [5]. The intersection between the vertical and horizontal dashed lines indicates the ITRS maximum leakage limit of 10 nA/cm<sup>2</sup> at 1V. Results are summarized in Table I. The 3.7 nm/1.9 nm (40c/17c) Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> device meets all ITRS 2020 projections with a low  $\alpha$ VCC/C<sub>ox</sub><sup>2</sup> of

αVCC J at 1V J at -1V C/A ITRS Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>  $(ppm/V^2)$  $(A/cm^2)$ Node  $(fF/\mu m^2)$ (nm) $(|A|/cm^{2})$ 2023 3.1 / 1.5 12.8  $1.22 \times 10^{-8}$  $1.43 \times 10^{-8}$ - - -6.79x10<sup>-9</sup> 2020 3.7 / 1.9 10.1 -20  $8.65 \times 10^{-9}$ <u>2.7</u>5x10<sup>-9</sup> 2017 5.0 / 2.7 7.9 20 5.24x10<sup>-9</sup>  $1.34 \times 10^{-9}$   $2.83 \times 10^{-9}$ 2014 6.8/3.9 14 5.6 4 100Normalized Capacitance (%) V L O I V ... 3 +9 MV/cm 75Prohability +8 MV/cm  $\mathbf{50}$ +6.5 MV/cm  $\mathbf{25}$ ⊦4.5 MV/cm 0 8 10 12 14 16 Electric Field ([MV/cm])  $10^{1}$  $10^{2}$ 103  $10^{4}$ 10<sup>5</sup> Seconds (s)

TABLE I Comparison of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> Stacks Meeting Incremental ITRS Nodes

Fig. 4. Capacitance variation vs. positive constant voltage stress time. Inset shows plot of voltage ramped breakdown for positive and negative polarity.

TABLE II

Comparison of Low Voltage Nonlinearity MIIM Capacitors

| Dielectric<br>Stack                                           | Film<br>Thickness<br>(nm) | C <sub>ox</sub><br>(fF/µm <sup>2</sup> ) | αVCC<br>(ppm/V <sup>2</sup> ) | J at 1V<br>(A/cm <sup>2</sup> ) | Deposition<br>Method | Dep/Anneal<br>Temperature<br>(°C) |

|---------------------------------------------------------------|---------------------------|------------------------------------------|-------------------------------|---------------------------------|----------------------|-----------------------------------|

| HfO <sub>2</sub> /SiO <sub>2</sub><br>[7]                     | 12/4                      | 6                                        | 14                            | 2.0x10 <sup>-9</sup>            | ALD/<br>PECVD        | 420                               |

| Sm <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub><br>[8]       | 7.5/4                     | 7.3                                      | -46                           | 1.8x10 <sup>-8</sup>            | Sputter/<br>PECVD    | 420                               |

| Er <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub><br>[9]       | 8.8/3.0                   | 7                                        | -73                           | 4.2x10 <sup>-9</sup>            | Sputter/<br>PEALD    | 400                               |

| STO/ZrO <sub>2</sub><br>[6]                                   | 20/20                     | 11.5                                     | -60                           | 3.5x10 <sup>-8</sup><br>(at 2V) | Sputter/<br>MOCVD    | 550                               |

| STO/Al <sub>2</sub> O <sub>3</sub> /STO<br>[10]               | 25.5/1.0/25.5             | 19.1                                     | 610                           | 1.0x10 <sup>-9</sup>            | ALD                  | 600                               |

| ZTO/BZTO<br>[11]                                              | 17/7                      | 13.4                                     | 14                            | 7.5x10 <sup>-9</sup>            | E-Beam               | 400                               |

| SiO <sub>2</sub> /HfO <sub>2</sub> /SiO <sub>2</sub><br>[12]  | 3/4/3                     | 12.4                                     | 32                            | 1.0x10 <sup>-9</sup>            | ALD                  | 300                               |

| Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub><br>This Work | 3.7/1.9                   | 10.1                                     | -20                           | 6.8x10 <sup>-9</sup>            | PEALD                | 200                               |

| ITRS<br>2020                                                  |                           | 10                                       | < 100                         | < 1.0x10 <sup>-8</sup>          |                      | 400<br>[2]                        |

$0.2 \ \mu m^4/V^2 fF^2$  (a figure of merit proposed in [6]). Targeting film thicknesses to meet the ITRS 2023 capacitance density requirement resulted in leakage current density exceeding the 10 nA/cm<sup>2</sup> limit at 1V. Reduced leakage, which would possibly allow further scaling of this stack, could likely be achieved either by either the use of larger work function electrodes to increase the metal-insulator barrier heights or annealing to reduce defect density. The use of low oxygen affinity ( $-\Delta H_{OX}$ ) metals may also reduce  $\alpha VCC$ . In Fig. 4 the 3.7 nm/1.9 nm (40c/17c)  $Al_2O_3/SiO_2$  device shows little variation with positive constant voltage stress time at fields below 9 MV/cm which, as seen in the inset with voltage ramped breakdown, is close to the breakdown strength of this stack. The difference in breakdown between positive and negative polarities is due to the built-in field of the electrodes. The negative polarity requires higher field to overcome the built-in field.

### **IV. CONCLUSION**

Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> bilayers deposited via PEALD at 200 °C are investigated for applications in MIIM capacitors. An insulator stack consisting of 3.7 nm of Al<sub>2</sub>O<sub>3</sub> and 1.9 nm of SiO<sub>2</sub> demonstrates a capacitance density of 10.1 fF/ $\mu$ m<sup>2</sup>, a leakage current density of 6.8 nA/cm<sup>2</sup> at 1V, and an  $\alpha$ VCC of -20 ppm/V<sup>2</sup>. Benchmarking our results against the ITRS roadmap, it is seen that the Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> stack simultaneously meets the 2020 node for capacitance density, leakage current density, and voltage nonlinearity projections with mainstream materials and low temperature processing.

# ACKNOWLEDGMENT

Devices fabricated at the OSU Materials Synthesis and Characterization (MaSC) Facility.

## REFERENCES

- The International Technology Roadmap for Semiconductors (ITRS), On-Chip Passives Technology Requirements, Semiconductor Industry Association, Washington, DC, USA, 2013.

- [2] A. Farcy *et al.*, "Integration of high-performance RF passive modules (MIM capacitors and inductors) in advanced BEOL," *Microelectron. Eng.*, vol. 85, no. 10, pp. 1940–1946, Oct. 2008.

- [3] M. D. Groner *et al.*, "Electrical characterization of thin Al<sub>2</sub>O<sub>3</sub> films grown by atomic layer deposition on silicon and various metal substrates," *Thin Solid Films*, vol. 413, nos. 1–4, pp. 186–197, Jun. 2002.

- [4] C. Wenger *et al.*, "Microscopic model for the nonlinear behavior of high-*k* metal-insulator-metal capacitors," *J. Appl. Phys.*, vol. 103, no. 10, p. 104103, 2008.

- [5] N. Alimardani *et al.*, "Investigation of the impact of insulator material on the performance of dissimilar electrode metal-insulator-metal diodes," *J. Appl. Phys.*, vol. 116, no. 2, p. 024508, Jul. 2014.

- [6] C. Jorel *et al.*, "High performance metal-insulator-metal capacitor using a SrTiO<sub>3</sub>/ZrO<sub>2</sub> bilayer," *Appl. Phys. Lett.*, vol. 94, no. 25, p. 253502, 2009.

- [7] S. J. Kim *et al.*, "Improvement of voltage linearity in high-κ MIM capacitors using HfO<sub>2</sub>/SiO<sub>2</sub> stacked dielectric," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 538–540, Aug. 2004.

- [8] J.-J. Yang *et al.*, "Effective modulation of quadratic voltage coefficient of capacitance in MIM capacitors using Sm<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> dielectric stack," *IEEE Electron Device Lett.*, vol. 30, no. 5, pp. 460–462, May 2009.

- [9] T. H. Phung *et al.*, "High performance metal-insulator-metal capacitors with Er<sub>2</sub>O<sub>3</sub> on ALD SiO<sub>2</sub> for RF applications," *J. Electrochem. Soc.*, vol. 158, no. 12, p. H1289, 2011.

- [10] J. H. Lee et al., "New metal-insulator-metal capacitor based on SrTiO<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/SrTiO<sub>3</sub> laminate dielectric," in Proc. 10th IEEE Int. Conf. Solid-State Integr. Circuit Technol. (ICSICT), Nov. 2010, pp. 1024–1026.

- [11] C.-C. Lin *et al.*, "MIM capacitors based on ZrTiO<sub>x</sub>/BaZr<sub>y</sub>Ti<sub>1-y</sub>O<sub>3</sub> featuring record-low VCC and excellent reliability," *IEEE Electron Device Lett.*, vol. 34, no. 11, pp. 1418–1420, Nov. 2013.

- [12] S.-U. Park *et al.*, "Analysis of reliability characteristics of high capacitance density MIM capacitors with SiO<sub>2</sub>–HfO<sub>2</sub>–SiO<sub>2</sub> dielectrics," *Microelectron. Eng.*, vol. 88, no. 12, pp. 3389–3392, Dec. 2011.

- [13] K. C. Chiang *et al.*, "High-temperature leakage improvement in metalinsulator-metal capacitors by work-function tuning," *IEEE Electron Device Lett.*, vol. 28, no. 3, pp. 235–237, Mar. 2007.

- [14] C. Vallée et al., "Electrode oxygen-affinity influence on voltage nonlinearities in high-k metal-insulator-metal capacitors," Appl. Phys. Lett., vol. 96, no. 23, p. 233504, 2010.