## **REVIEW ARTICLE**

## Plasma etching: Yesterday, today, and tomorrow

Vincent M. Donnelly<sup>a)</sup> and Avinoam Kornblit<sup>b)</sup>

Department of Chemical and Biomolecular Engineering, University of Houston, Houston, Texas 77204

(Received 19 July 2013; accepted 13 August 2013; published 5 September 2013)

The field of plasma etching is reviewed. Plasma etching, a revolutionary extension of the technique of physical sputtering, was introduced to integrated circuit manufacturing as early as the mid 1960s and more widely in the early 1970s, in an effort to reduce liquid waste disposal in manufacturing and achieve selectivities that were difficult to obtain with wet chemistry. Quickly, the ability to anisotropically etch silicon, aluminum, and silicon dioxide in plasmas became the breakthrough that allowed the features in integrated circuits to continue to shrink over the next 40 years. Some of this early history is reviewed, and a discussion of the evolution in plasma reactor design is included. Some basic principles related to plasma etching such as evaporation rates and Langmuir–Hinshelwood adsorption are introduced. Etching mechanisms of selected materials, silicon, silicon dioxide, and low dielectric-constant materials are discussed in detail. A detailed treatment is presented of applications in current silicon integrated circuit fabrication. Finally, some predictions are offered for future needs and advances in plasma etching for silicon and nonsilicon-based devices. © 2013 American Vacuum Society. [http://dx.doi.org/10.1116/1.4819316]

#### I. INTRODUCTION

Plasmas have been used to etch fine features in Si integrated circuits for nearly 40 years. Without this technology, we would be stuck in the 1970s listening through tinny headphones to disco music on our "small" portable cassette tape player. Carrying laptops around would be more for fitness than for convenience and mobile "smart" phones would require wheels. Today, instead we take these marvelous devices for granted. Among the many important breakthroughs that were required to make this all possible, plasma etching plays a major role in allowing complex circuit patterns printed in a photolithgraphically defined polymer to be transferred to the silicon, silicon dioxide, and metals that make up the integrated circuits at the heart of these devices.

The first commercially available microprocessor, the Intel 4004, was launched in 1971. It was a 4 bit processor, contained 2300 transistors, operated at 1.08 MHz clock-frequency, and a minimum feature size of  $10 \, \mu \text{m}$ . Intel's third generation multicore processors, launched in late 2012, are 64 bit processors, containing  $1.4 \times 10^9$  transistors, operating at roughly 3 GHz clock-frequency and a minimum feature size of 22 nm.<sup>2</sup> Although many factors contributed to the advances in microprocessors' performance, a key element has been the ability to fabricate smaller transistors. This is attributed to advancements in lithography and pattern-transfer methods. The purpose of this review is to cover the advancements in the latter. In the early days of integrated circuit fabrication, pattern-transfer was accomplished by wet etching. However, with time, plasma etching became the preferred method.

Here we attempt to provide a modern review of this field in a comprehensive as possible manner. Given the scope of this undertaking, this is a nearly impossible task. Many important studies will be left out. We also note that there are several earlier books on plasma etching<sup>3,4</sup> as well as more detailed treatments of important aspects such as plasma physics and electrical engineering.<sup>5-7</sup> Instead, the attempt here is to cover in some detail the applications of plasma etching in integrated circuits and to a lesser extent, in microelectromechanical systems (MEMS) devices. The subject is placed in historical perspective and is accompanied by a discussion of mechanisms of plasma etching and selected diagnostics that provide both fundamental insights into plasma etching processes and are in widespread use in manufacturing. An attempt is also made to predict the future needs for plasma etching, looming problems, and possible solutions.

## **II. BRIEF HISTORY**

The use of glow discharges dates back to the late 19th century where sputtering, first discovered by Grove<sup>8</sup> and also observed near the electrodes in vacuum tubes, was used for the production of mirror surfaces.<sup>9</sup> The term "plasma" to designate partially ionized gas is attributed to Irving Langmuir who studied glow-discharges, and according to his colleague and collaborator, Lewi Tonks, <sup>10</sup> coined the term during a discussion between them. The first known use of the term in the literature is dated 1928.<sup>11</sup>

In the early days of integrated-circuit processing, wetetching was used for pattern transfer. With time, however, plasma-based pattern transfer replaced wet chemistry for most if not all the steps. The development of modern plasma-etching equipment for pattern-transfer evolved along

a)Electronic mail: vmdonnelly@uh.edu

b) Electronic mail: avtek0@gmail.com

two paths that eventually merged into the current configuration, where the substrate to be etched is placed on a radio frequency (RF)-powered electrode, with or without an additional plasma-generation source. The two approaches, physical (i.e., sputtering) and chemical, had different goals. The former was needed for pattern transfer that could not be accomplished by wet-chemical means, while the latter was intended to replace wet chemicals in IC fabrication.

The first path, sputtering, was used in the early 1960s for the fabrication of beam-lead devices (beam-leads were an alternate technology to wire-bonding, where gold semirigid cantilevered leads were used to connect the device to the outside world). In the process, developed by Martin Lepselter from Bell Laboratories,  $^{12-14}$  gold leads,  $12.5 \mu m$  in thickness, were electroplated onto a metal stack consisting of an adhesion-promoting layer or a "glue-layer" (titanium or zirconium) and platinum (needed to prevent a chemical reaction between the gold and the glue-layer). The etching of the metal stack below the gold could not be easily accomplished by wet etching. For instance, aqua regia (one part concentrated HCl plus three parts concentrated HNO<sub>3</sub>), one of the few chemicals that will etch platinum, 15 will etch gold about 190 times faster, 16 leading to severe undercutting of the gold. Back-sputtering of the platinum solved the problem, sometimes with the downstream addition of oxygen<sup>17</sup> to increase the selectivity to the glue-layer. In a further development, an RF sputtering method (using an argon plasma) was implemented by Davidse 18,19 from IBM, utilizing a "blocking" capacitor 20 to couple the RF generator to the electrode on which the substrate had been placed. The resulting negative bias led to ion acceleration toward the biased electrode and was used to pattern cermet-film resistors.

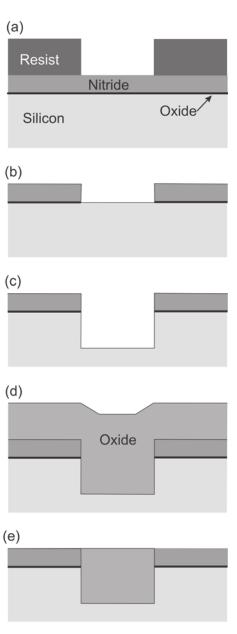

The chemical approach for plasma etching in the semiconductor industry started in the late-1960s when Stephen Irving from Signetics demonstrated the ability to strip photoresist in oxygen plasma. 21-23 The reactor, that had been used to remove organic residues from various substrates by "burning" or "ashing" them, was manufactured by Tracer Labs, a division of LFE Corporation.<sup>24</sup> It consisted of a reaction vessel, where an external coil was used to generate the plasma by an electrodeless discharge [the concept was not new and was used first by Thomson in 1891 (Ref. 25)]. However other issues, such as residues and device damage<sup>23</sup> [associated with ultraviolet (UV) radiation] had to be addressed before plasma-ashing became a viable alternative to wet stripping. Irving recognized the wider implication for etching other materials as well by using either fluorine or chlorine-based compounds to etch SiO<sub>2</sub> or aluminum, respectively.<sup>26</sup> The motivation for use of plasma to clean or pattern semiconductor devices was driven primarily by the need to reduce chemical waste associated with the use of wet etchants, <sup>23,27</sup> but other advantages became apparent as well. As silicon-nitride became the material of choice for the encapsulating layer, there was no wet etchant that could be used to pattern it to form the contact to the aluminum metal layer below.<sup>27</sup> Fluorine based plasmas became the obvious choice to pattern the nitride without eroding the aluminum metal in the contact-pads.

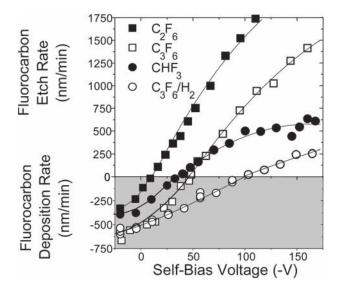

While etching  $SiO_2$  with fluorine-compound based plasma looked attractive, it would not be practical if the selectivity (i.e., the etch-rate ratio of  $SiO_2$  to the underlying substrate) were low. For instance,  $CF_4$  plasmas can etch silicon faster than  $SiO_2$ . The issue of additives (e.g.,  $H_2$ ) or alternative gases ( $C_2F_6$ ,  $C_3F_8$ ,  $CHF_3$ ) to increase selectivity with respect to silicon was discussed extensively by Heinecke.  $^{28,29}$

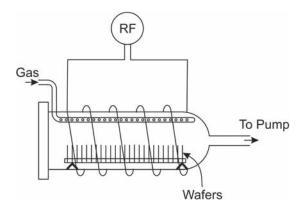

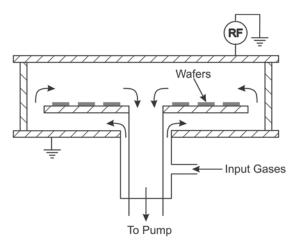

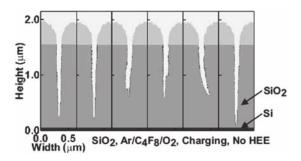

The early plasma reactors were barrel type, where wafers were placed in a quartz chamber with external electrodes<sup>30</sup> (or a coil—Fig. 1). The appropriate gas was introduced into the chamber while RF was applied across the electrodes to generate the plasma. These etchers, while adequate for resist stripping, lacked wafer temperature control and, at least initially, suffered from poor etch uniformity, required for device processing. It was not until the radial-flow reactor was introduced that plasma etching became a viable production alternative to wet etching for patterning. In this reactor (known also as the Reinberg reactor<sup>31</sup>), wafers were placed on the grounded electrode, while RF is applied to the opposite electrode (Fig. 2).

The convergence of the two approaches for plasma etching took place when Hosokawa *et al.*<sup>32</sup> introduced fluorine and chlorine-containing gases (e.g., CF<sub>4</sub>, CCl<sub>3</sub>F, CCl<sub>2</sub>F<sub>2</sub>, etc.) instead of Ar to a RF sputtering apparatus. The motivation was to increase the etch rate of various materials, such as silicon, glass, aluminum, molybdenum, stainless steel, and photoresist. However, there was no discussion of the applicability of the technique to pattern transfer. The technique, now called reactive ion etching (RIE), <sup>33–35</sup> reactive sputter etching (RSE), <sup>36,37</sup> or ion-assisted plasma etching, <sup>38</sup> became the method of choice (with some enhancements that will be discussed in the next section) for patterning devices.

The first all dry-etched device was processed in 1975 by Texas Instruments.<sup>27</sup> The motivation was to reduce the amount of solvents in the processing line as well as the ability to pattern the silicon nitride passivation-layer to access the bond-pads. However, as critical dimensions (CD) became smaller and smaller, vertical dimensions approached and exceeded horizontal dimensions, mask undercutting became intolerable, and anisotropic etching became the primary motivation for using plasmas for pattern-transfer.

Fig. 1. Barrel reactor. Wafers are mounted on a quartz boat inserted through a door (on left) into a quartz tube. After pumpdown, gas flow is initiated followed by RF power applied to a coil wrapping around the quartz tube.

Fig. 2. Reinberg reactor. Wafers are placed on a platen at ground potential. After pumpdown, gases are flowed over the wafers from edge to center, while RF power is applied to the upper electrode.

## III. EQUIPMENT EVOLUTION

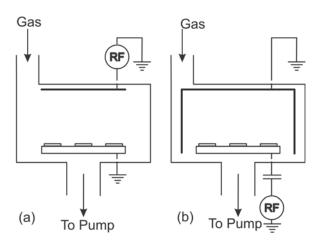

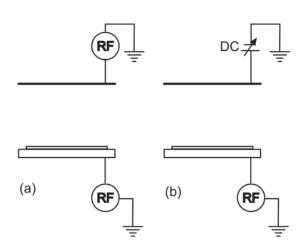

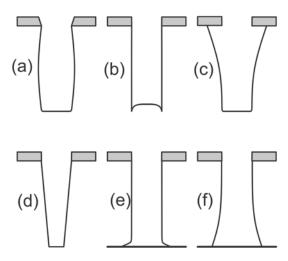

The etching tools used in the early days for pattern transfer were diode reactors with the wafers placed either on the grounded or RF-powered electrode that was capacitively coupled to the plasma with an excitation frequency of 13.56 MHz. Tools with the former configuration were referred to "plasma reactors" while those with the latter configuration were dubbed "reactive-ion-etchers" (RIE) or "reactivesputter etchers" (RSE). The plasma reactors operated at relatively high pressures (hundreds of mTorr) with the two electrodes roughly equal in area [Fig. 3(a)], while reactiveion-etchers operated at lower pressures, with the powered electrode smaller than the grounded electrode [Fig. 3(b)]. The asymmetry of the two electrodes, coupled with the use of a blocking capacitor, yielded a negative dc self-bias voltage on the smaller (usually powered) electrode. The ratio of voltages across the sheaths near the powered and grounded electrodes was originally thought to vary as the ratio of areas of the grounded and powered electrodes to the forth power.<sup>39</sup> While the area ratio dependence was later shown to be much less severe, 40 the smaller electrode was nonetheless found to

Fig. 3. Parallel plate reactors: (a) "Plasma mode"—wafer on grounded electrode; (b) "RIE mode"—Wafer on RF-powered electrode.

obtain a much larger sheath potential than the larger electrode. This causes more energetic ion bombardment of substrates placed on the smaller electrode, enabling anisotropic etching.

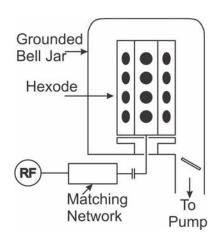

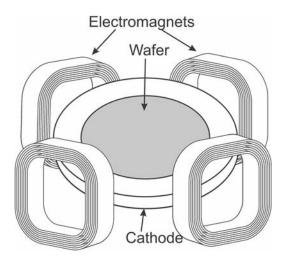

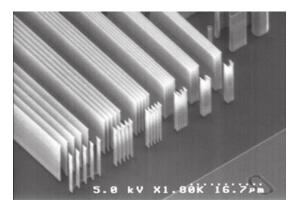

As the industry migrated toward plasma etching processes and replaced wet etching as the preferred method for pattern-transfer, throughput became an important issue. Reactive ion etchers that could process large batches of wafers were the early solution for the problem. <sup>38,41,42</sup> An example is shown in Fig. 4. Although these etchers could handle up to eighteen 150 mm diameter wafers, the challenges were the control of etching uniformity (within a wafer as well as wafer-to-wafer) and wafer handling (automatic loading and unloading). As the industry migrated to 200 mm wafers, with the need to achieve better etching uniformity (both within-wafer as well as wafer-to-wafer), batch reactors became less attractive, and enhanced etching-rate single-wafer-etchers took their place.

The key to high-throughput single-wafer etchers is enhanced etching-rate and the ability to integrate multiple etching chambers on a single platform. Depending on the application, the higher etching rate can be achieved by increased pressure (>100 mTorr), the use of magnetic fields to confine the electrons, referred to as magnetically enhanced RIE (MERIE), or by using inductive coupling or microwave frequencies to achieve high-density plasmas (>10<sup>11</sup> positive ions/cm<sup>2</sup>). In this case, the source is decoupled from power delivered to the stage to allow ion-energy control independent of plasma density.<sup>43</sup>

## A. Magnetic enhanced reactive ion etching

In this method, electrons spiral around imposed magnetic field lines, increasing their trajectory toward the chamber walls. The end result is higher number of collisions per electron, leading to a higher ionization rate. Early MERIE tools utilized either permanent magnets <sup>44</sup> (e.g., MRC MIE-710) or moving magnets behind the wafers <sup>45</sup> (e.g., Tylan/Tokuda HiRRIE 500). The more common designs, however,

Fig. 4. Batch RIE reactor where wafers are mounted on a multifacet cathode. With a six facet cathode (hexode), twenty-four  $100\,\mathrm{mm}$  wafers could be etched simultaneously (or eighteen  $125\,\mathrm{and}\ 150\,\mathrm{mm}$  wafers). The  $200\,\mathrm{mm}$  version (pentode configuration) could accommodate ten  $200\,\mathrm{mm}$  wafers. The electrode ratio for this configuration is greater than 2.

involved magnetic fields generated outside the chamber walls either by rotating magnets (TEL DRM) or rotating magnetic-field generated by varying currents in two sets of perpendicular coils<sup>45</sup> (Applied Materials—a number of models). In the latter case (Fig. 5), the magnetic field could be turned on and off as needed with the additional control of rotation frequency. At low pressures, the magnetic field enhances etching rates—the electrons' path to the chamber wall is longer, leading to higher ionization due to increased collision rate with neutrals. At higher pressures ( $\geq \sim 100$  mTorr), its effects are smaller, as the inelastic mean free path becomes much smaller than the reactor dimensions. Above 200 mTorr, contributions of the magnetic-field to etch rate are negligible.

## B. Multiple-frequency capacitively coupled plasma etchers

The need to decouple plasma generation from ion-energy control was realized as early as 1979. <sup>46</sup> Etchers with dual RF powered electrodes were introduced in the mid-1980s (e.g., Drytek 384T and Tegal 1500). The former had two opposing electrodes powered with the same frequency (13.56 MHz), with a grounded chamber wall and a grid, <sup>47</sup> while in the latter, the two electrodes were powered with different frequencies, with a grounded third electrode. <sup>48</sup> Later generations of the Tegal triode etchers included magnetic confinement <sup>49,50</sup> as well.

In current dual-frequency capacitively coupled plasma (CCP) reactors, marketed by TEL and Lam Research, high-frequency (≥13.56 MHz) is applied to the upper electrode, and the lower electrode that holds the substrate is powered by the lower frequency. In newer configurations, there is the option to couple both frequencies to the lower electrode, with additional hardware to confine the plasma. This minimizes interaction with the chamber wall and facilitates more efficient chamber cleans that can be carried out after every wafer. The exact frequencies will vary by application, manufacturer, and equipment-generation. A schematic of a

Fig. 5. Applied Materials MERIE chamber. The current in the four coils could be varied to generate a rotating magnetic field. The coils are placed outside the chamber walls.

dual-frequency reactor is shown in Fig. 6(a). These reactors normally operate at higher pressures than the high-density reactors discussed below and are usually used for dielectric-etch applications.

More recently, Lam Research has introduced a CCP etcher where three frequencies, 2, 27, and 60 MHz, are utilized. <sup>53,54</sup> In this configuration, the upper electrode is either RF powered with one frequency or grounded. In the former, two frequencies are applied to the lower electrode, while in the latter all frequencies are coupled to the lower electrode. <sup>55</sup>

In another twist, introduced by TEL, the top electrode, in addition or instead of being RF-powered, may be DC-biased, while the lower electrode is RF biased [DC/RF hybrid reactor, <sup>56–60</sup> Fig. 6(b)]. The reason for DC biasing is to generate high-energy ballistic electrons <sup>59</sup> that will accelerate toward the opposite RF powered electrode, with some reported benefits of reduced electron-shading and improved resist integrity. <sup>61</sup>

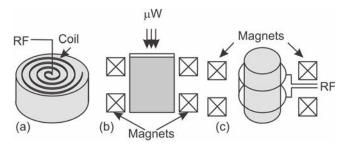

## C. High density etchers

Numerous plasma etchers have been introduced where the plasma is generated by a source that is not capacitively coupled to the plasma. The ion-density in these etchers is generally about an order of magnitude or more higher than in the CCP etchers described above. The wafer is placed on an RF-biased lower electrode, and plasma is generated by a source placed a short distance above the wafer. Common high-density sources are inductive, electron–cyclotron-resonance (ECR), surface-wave-plasma (SWP), and helicon. These and other sources are discussed extensively elsewhere. 43

## 1. Inductively coupled source

In these systems, a coil (or multiple coils to control uniformity) outside the chamber is used for plasma generation. The coil could be planar<sup>62</sup> [Fig. 7(a)] placed on a dielectric window (Lam Research transformer-coupled plasma, or TCP®), three-dimensional bowl shaped (Applied Materials DPS®), or simply a cylindrical coil. The walls are at ground

Fig. 6. Capacitively coupled plasma etcher with the two electrodes powered. In another version, the top electrode is grounded and the two RF generators are coupled to the lower electrode. (a) Both electrodes are RF powered (b) a RF/DC hybrid reactor with the top electrode DC powered.

Fig. 7. Various high-density plasma sources: (a) Inductive—planar coil; (b) ECR; (c) helicon.

potential, but they are usually coated with an insulating, ceramic layer and are often behind an insulating liner. The substrate is placed on the stage that is capacitively coupled to a RF source. As in CCP systems, the small electrode holding the wafer develops a negative dc self bias when RF power is imposed; hence, it can be thought of as a cathode. In some etchers, the plasma is confined by a magnetic field generated by fixed magnets.

Inductively coupled etchers generally operate at pressures of a few mTorr to tens of mTorr and are used for the etching of trenches, gate-electrodes, high- $\kappa$  dielectrics, aluminum and its alloys. There are also special configurations to etch materials that do not form volatile compounds (Hitachi offers such a system), including alloys of nickel and iron, noble metals, lead zirconate titanate (PZT), barium strontium titanate (BST), and others. In these cases, where sputtering is the mechanism for pattern transfer, the by-products accumulate on the chamber walls, which then have to be physically cleaned from time to time. If the etch by-products are conductive, however, they may coat the dielectric window; a capacitively coupled plasma reactor is preferred in these instances.  $^{63}$

## 2. Electron-cyclotron-resonance source

In an ECR plasma,64 radiation is launched through a dielectric window into a low-pressure volume containing the gas to be ionized [Fig. 7(b)]. The frequency of the radiation in commercial etchers is typically in the microwave regime (2.45 GHz), but UHF (450 GHz) was used in some etchers as well mainly for dielectric etch applications. 65 The electrons generated are confined by a magnetic field generated by a few magnets and are forced to move in a circular motion. The frequency of rotation (cyclotron frequency) is given by  $\nu = (1/2\pi)(eB/m)$ , where e and m are the electron charge and mass, respectively, and B is the magnetic flux density. At resonance, the right-hand side equals the excitation frequency, and therefore  $B = 0.0875 \,\mathrm{T}$  (875 G) and 0.0161 T (161 G) for  $\nu = 2.45 \, \text{GHz}$  and 450 MHz, respectively. The chamber below the resonance cavity is typically surrounded by magnets for improved uniformity. Currently, the main applications of ECR etchers are silicon or aluminum etching.

#### 3. Helicon source

Helicon sources<sup>66</sup> are not currently used in mainstream commercial etchers. The source utilizes a specially designed

antenna and operates at frequencies in the megahertz range in the presence of an axial magnetic field, producing bounded whistler waves. <sup>67</sup> Depending on the antenna design, different modes of excitation are possible. Early helicon sources for plasma etching operated in the m=1 mode, <sup>68–70</sup> but the one that eventually gained presence in the commercial market operated at the m=0 mode <sup>71</sup> (MORI source, first marketed by PMT and subsequently by Trikon). The former is characterized by electrical field lines that do not change their pattern with position but the pattern rotates along the direction of the B field, while the latter exhibits field lines that change direction from radial to azimuthal, depending on position. The etch chamber is often magnetically confined. The MORI source has been used for etching silicon, metal, as well as dielectrics.

#### 4. Surface wave plasma source

This source uses microwaves to generate a high density discharge without the presence of a DC magnetic field. These type of etchers were first commercialized in the early 1990s (e.g., Sumitomo SW4010), but never became widely used. However, recently TEL has introduced a SWP etch chamber with a radial-line slot antenna, utilizing a 2.45 GHz microwave source. It has been reported that the electron energy distribution function (EEDF) in the plasma-generation zone is non-Maxwellian,  $^{73,74}$  and therefore no unique electron temperature,  $T_e$ , can be assigned. Away from the plasma generation zone the bulk of the EEDF approaches a Maxwellian distribution with  $T_e$  around 1 eV. The intensity of vacuum ultraviolet (VUV) radiation near the wafer, linked to device damage,  $^{75,76}$  is reported to be considerably lower than the radiation associated with inductive sources.

## D. Downstream etchers

In these systems, plasma is generated in a remote chamber (either by a microwave or an inductive source), in a manner that does not expose the wafer to UV radiation, which can lead to device damage (e.g., threshold shift).<sup>23</sup> In addition, due to the long length of tubing between the source and the substrate, no charged particles reach the etching chamber and the substrate is exposed only to neutrals. These etchers are used for isotropic etching processes. The main application is for resist-stripping (ashing) with O atoms at elevated temperature (200-300 °C). The formation of nonreactive, ground state O2 is suppressed by the addition of other gases such as N<sub>2</sub>.<sup>77</sup> N<sub>2</sub>/H<sub>2</sub> mixtures can also be used for resist stripping, albeit at a lower rate.<sup>78</sup> This mixture is useful when oxidation of the exposed substrate (e.g., TiN film, or low- $\kappa$  dielectrics) is to be avoided. 78,79 Another application is the soft etch of silicon by atomic fluorine resulting from the dissociation of gases such as NF3 or CF4 at room temperature. Substrate heating, when necessary, is accomplished either by a heated chuck or lamp. Depending on the tool, wafers can be etched either by resting on the chuck, or on the lift-pins. In the latter configuration, both front and back-sides of the wafer can be etched simultaneously. The chuck can often be RF powered to initiate the etch by removing a hard-to-etch film on top of the layer to be removed, such as the crust formed on top of photoresist during ion implantation.

#### E. Temperature control

In all applications where photoresist is used as the mask, there is a need to keep the wafer temperature low enough to prevent the resist from flowing or reticulating. Both temperature and UV radiation generated by the plasma are the causes of the latter, and in fact act in synergy. 80 In other cases, temperature is a critical parameter in determining the rate of the etch process (e.g., aluminum etching) and it must be controlled. In earlier generations of etchers, this was accomplished by placing the wafer on the chuck, sometimes with force applied at the periphery of the wafer placed on a domed pedestal. Later generation etchers have utilized helium heatexchange gas, pressurizing the gap between the wafer and the chuck. This pressure is typically between 4 and 30 Torr, and the gap is within or below the mean-free-path of helium at the operating pressure (roughly 0.01 mm at 10 Torr and 40 °C). Under these conditions, the heat transfer coefficient does not vary much with variations in the gap dimensions.<sup>81</sup> Although in principle other gases may be used for heat exchange, helium is preferred because of its high heattransfer coefficient and high ionization potential (i.e., the He leaking into the plasma does not perturb it). With the introduction of electrostatic chucks (ESC), the He leak-up rate into the chamber is used to monitor wafer clamping and the health of the ESC. Warped wafers (especially ones that are bowed upwards as a result of a highly tensile film on the front of the wafer) can lead to high helium leak-up rate and inadequate clamping or "chucking."

Both heated (T > 150 °C) and cryogenically cooled chucks are used in some applications. The former is used in to increase the vapor pressure of the etch by-products (e.g., high- $\kappa$  etching), while the latter is used in limited applications to minimize lateral etching (e.g., silicon etching with SF<sub>6</sub> in a non-Bosch process).

## F. Endpoint detection

At most etching levels, some endpoint detection is needed, first to ensure that etching is complete, and second to avoid excessive etching time that may erode the underlying layer. There are numerous methods that have been used over the years in research laboratories and production environment, such as interferometry, <sup>82</sup> ellipsometry, <sup>83–85</sup> and optical emission spectroscopy (OES). <sup>86–90</sup>

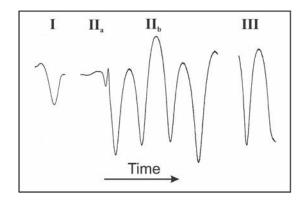

While ellipsometry is a useful research tool, it has not found much use in production. Interferometry was widely used in batch etchers, but with the transition to single wafer etchers, optical-emission monitoring became the preferred method for endpoint detection, due to its relative simplicity in terms of hardware and software implementation. Interferometry is still useful in some applications, where etching steps are to be changed based on depth of material etched (see discussion below and example in Fig. 8).

The interferometric method relies on interference between light beams reflected from the top and the bottom

surface being etched. If the imaginary component, k of the refractive index, n+ik, is small, a periodic reflected signal will be observed, with periodicity corresponding to  $\Delta d = \lambda/(2\sqrt{n^2 - \sin^2\theta_i})$ , where  $\Delta d$  is the thickness associated with a period,  $\theta_i$  is the angle of incidence with respect to the surface normal, and  $\lambda$  is the wavelength of the light-source being used. The light source could be external [laser or UV (Ref. 91)] or even internal, i.e., the plasma glow itself. <sup>92,93</sup> In the latter case, it could be used to monitor the etching process over the entire wafer. From the periodicity of the reflected light, etch rates can be determined, and endpoint is realized when the reflected signal becomes flat (Fig. 8, end of trace I).

The monitoring of reflectance can also be used to detect endpoint of an absorbing layer (high imaginary refractive index, *k*) on top of another by monitoring the change in reflectance. For example, this method was used to monitor the etching of aluminum in a batch reactor, using a He-Ne laser as the light source. <sup>94</sup> A large change in reflectance occurs when the metal is cleared. <sup>94</sup> A similar approach was used in the fabrication of x-ray masks to monitor the etching of tungsten sandwiched between two layers of Cr on top of a polysilicon membrane. <sup>95</sup>

In a slight modification of the method, it can be used for endpoint prediction. <sup>78,96–98</sup> For example, reflectivity changes have been used in etching of polysilicon gates to stop on less than 1 nm of thermal oxide, by initiating a selective overetch step before the polysilicon cleared. In this case, the wavelength of the external light source was chosen to yield a change in reflectance 10–20 nm before endpoint, which triggered the overetch step. <sup>96</sup>

The technique most commonly used for endpoint determination is OES (Sec. IV A), where a particular wavelength in the plasma is monitored throughout the etch process for any change associated with the removal of the film being etched. It can be associated with an etch by-product, like CO emission in oxide etching (which leads to the signal decline at endpoint), or reactant, such as Cl or  $\text{Cl}_2$  in polysilicon etching (which leads to a signal rise at endpoint). The

Fig. 8. Reflected light recorded during etching of a TaSi<sub>x</sub>/polysilicon gate stack with an antireflecting coating (ARC), showing periodicity associated with interference. I: ARC etch (with Cl<sub>2</sub>). II: TaSi<sub>x</sub> and the bulk of the polysilicon (with CFCl<sub>3</sub>/O<sub>2</sub>); steps IIa and IIb correspond to the etching of TaSi<sub>x</sub> and polysilicon, respectively. III: Etching of the remainder of the polysilicon with Cl<sub>2</sub>/O<sub>2</sub>. A long overetch step (not shown) with a low-bias Cl<sub>2</sub>/O<sub>2</sub> plasma was carried out to clear residual polysilicon resulting from the topography associated with these device.

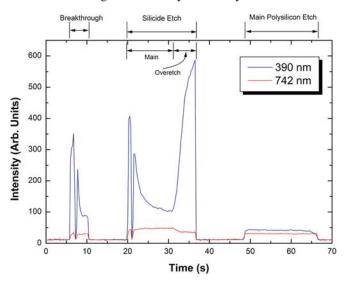

appropriate monitoring wavelength is either selected by a filter, photomultiplier tube, or an optical multichannel array. In the latter case, it is possible to monitor multiple wavelengths simultaneously. In cases where a rotating magnetic-field is used, some averaging of the signal over one or more rotation-periods is required to produce a meaningful signal. An example of an emission trace used to monitor WSi<sub>x</sub>/poly-silicon gate etching is shown in Fig. 9. While OES is a powerful technique for endpoint detection, it is not sensitive enough in cases where the exposed area is very small, such as in contact and via etching.

Both reflectivity and OES techniques require an access windows on the chamber that must remain clean to obtain stable signals of sufficient intensity. Typically, a heated quartz window is used to prevent polymer buildup.

Other endpoint detection methods, such as pressure change, bias change, and mass spectrometry are discussed elsewhere. 94 These are not used in production due to their complexity and/or lack of sensitivity.

#### IV. DIAGNOSTICS AND MECHANISMS

## A. Some basic considerations in ion-assisted etching

Anisotropic plasma etching is made possible by the perpendicular bombardment of the surface by positive ions that are accelerated by a sheath potential that develops on surfaces exposed to the plasma. Within this simple classification of ion-assisted etching, many types of reactions can occur. Anisotropic etching requires a combination of energetic ions and reactive neutral species. The flux of neutral species should preferably be much larger than the positive ion flux, so that the etching rate is mainly limited by the ion flux. This

Fig. 9. (Color online) Emission signals associated with a multistep  $WSi_x/V$  polysilicon gate etching process. Two wavelengths, 390 and 742 nm were used to monitor the process in a Lam 9400 etcher. **Breakthrough**: Highbias  $Cl_2$ . **Silicide etch**:  $Cl_2/O_2$ . **Polysilicon etch**:  $Cl_2/HBr/O_2$ . **Overetch (not shown)**:  $HBr/O_2$ . The intensity fluctuations at the beginning of the breakthrough and the silicide etch reflect instability of the RF power associated with the matching network of the source. The 390 nm trace rises at endpoint of the  $WSi_x$  etch step while the 742 nm trace falls. The 390 nm emission line is used to determine endpoint of the main polysilicon etch (the fall of the 742 nm trace is associated with RF power being turned off).

allows the fastest etching rates to be obtained with minimum dependence on the feature aspect ratio and the area of exposed material.

#### 1. Vaporization of products

It is advantageous if the etching gas is able to form a volatile compound with the film or silicon substrate that is being etched. Although it is possible to obtain useable etching rates with some sputtering processes, including with reactive gases that aid in breaking substrate bonds but generate nonvolatile products, these products will redeposit on the wafer and coat the reactor surfaces, causing many feature-scale and reactor scale problems. Also such processes are not very selective.

For a compound to be sufficiently volatile, its evaporation rate should be much higher than the desired etching rate. The maximum evaporation rate is computed by the principle of detailed balance: at equilibrium, the forward and reverse rates of every elementary process are equal. Consequently, for a gaseous species at a number density, n, in equilibrium with its liquid or solid state in a closed system, its evaporation rate equals its impingement rate on the solid or liquid. The impingement rate or flux (molecules-cm<sup>2</sup>s<sup>-1</sup>) of species onto a surface is

$$f_i = \frac{nv}{4}. (1)$$

The thermal speed, v (in cm/s), is given by

$$v = \left(\frac{8kT}{\pi m}\right)^{1/2},\tag{2}$$

where k is the Boltzman constant  $(8.314 \times 10^7 \text{ erg K}^{-1} \text{ mole}^{-1})$ , T is the temperature in Kelvin, and m is the mass in grams/mole. For an ideal gas at pressure p (expressed as dyne-cm<sup>-2</sup> [1 dyne-cm<sup>-2</sup> = 0.1 Pa =  $7.502 \times 10^{-5}$  Torr]), the impingement rate can be expressed as

$$f_i = \frac{p}{\sqrt{2\pi mkT}}. (3)$$

The equilibrium vapor pressure,  $p_V$ , is described by the Clausius–Clapeyron equation:

$$p_V = p_0 \exp\left(\frac{-\Delta H}{RT}\right),\tag{4}$$

where  $\Delta H$  is the heat of vaporization and  $p_0$  is a constant of integration. Consequently, at equilibrium, the evaporation rate (equals the impingement rate) is given by

$$f_e = f_i = \frac{p_V}{\sqrt{2\pi mkT}}. ag{5}$$

The evaporation rate is given by the right side of Eq. (5), regardless if the system is closed or open and far from equilibrium.

For the most common materials used in silicon microelectronics devices, the etching products in halogen, carbon, hydrogen, and oxygen-containing plasmas are SiF<sub>4</sub>, SiF<sub>2</sub>, SiCl<sub>4</sub>, SiCl<sub>2</sub>, SiBr<sub>4</sub>, SiBr<sub>x</sub>H<sub>y</sub>, SiCl<sub>x</sub>Br<sub>y</sub>H<sub>z</sub>, SiOF<sub>2</sub>, CO, CO<sub>2</sub>,

O<sub>2</sub>, COF<sub>2</sub>, metal halides, and metal oxy-halides. These are not necessarily the primary etching products leaving the surface, but are nonetheless the predominant stable products that are pumped away. With the exception of some refractory metal compounds and Si-dihalides, the evaporation rates for these products are many orders of magnitude larger than typical etching rates, hence these stable products will never reach an appreciable coverage on surfaces and etching of these materials is *never* limited by the evaporation rate, even in the case of Si etching in an HBr plasma, where SiBr<sub>4</sub> is the *least* volatile product possible. Hence, even though it is true that SiBr<sub>4</sub> is less volatile than SiCl<sub>4</sub>, Si etching in a HBr plasma is not slower than that in a Cl<sub>2</sub> plasma because the product is less volatile.

For a species to be present on the surface during etching, it must be strongly adsorbed. The rate of thermal desorption is given by

$$k_d = \nu_0 \exp(-E_a/RT), \tag{6}$$

where  $\nu_0$  is the pre-exponential or so-called attempt frequency and  $E_a$  is the activation energy for desorption, or binding energy for the adsorbate. The pre-exponential factor is often simply assumed to be equal to a typical vibrational frequency of  $\sim 10^{13} \,\mathrm{s}^{-1}$ , although it is in fact equal to kT/htimes the ratio of partition functions of the transition state for desorption to that of the reactant state and can vary from typically  $10^8$  to  $10^{15}$  s<sup>-1</sup>. Like  $\nu_0$ , the binding energy can also span a wide range of values, reflecting the complex nature of the surface layer and the multitude of bonding configurations. Using a value of  $10^{13} \, \mathrm{s}^{-1}$  for  $\nu_0$ , it can be seen from Eq. (6) that a species must have a binding energy of 16 kcal/mol  $(0.69\,\mathrm{eV})$  at room temperature to have a  $\sim 0.1\,\mathrm{s}$  lifetime on the surface, comparable to the time required to etch 1 monolayer. This binding energy exceeds physisorption energies for most adsorbate-substrate combinations, but is less than most chemical bonds; consequently, any chemisorbed species will likely live indefinitely on the surface, while products like SiBr<sub>4</sub> will desorb nearly instantaneously after being formed.

Therefore, surfaces are covered with chemisorbed species during and after etching. It is mostly plasma radicals that will adsorb and form this chemisorbed layer, but feed gases can sometimes also react (e.g., Cl<sub>2</sub> with Si and Al). Once this chemisorbed layer forms, containing atoms from the etching gas and (usually) the substrate, it must be removed (after perhaps being further "activated") for etching to proceed. This is usually accomplished by ion bombardment. In one notable exception, Al etching at higher pressures, ion bombardment is not necessary, and the chemisorbed layer formed by reactions of Cl<sub>2</sub> and Cl spontaneously converts to a physisorbed AlCl<sub>3</sub> layer that rapidly desorbs. In most cases, however, it is the ion-stimulated removal of the chemisorbed layer that makes anisotropic etching possible.

## 2. Adsorption and etching by neutrals

A few reactions of neutrals with materials used in microelectronics devices have been studied. These experiments measure sticking coefficients, the reaction coefficients, and recombination coefficients. In an oversimplified treatment, the sticking coefficient can be defined by the Langmuir–Hinshelwood adsorption model, which, using Cl adsorption on Si as an example, can be described as

$$Cl + Si \rightarrow Cl - Si,$$

(7)

where Si· is an adsorption site. The relative density of such adsorption sites is defined as  $\theta$ , which can range from 0 to 1. The probability for adsorption is given by

$$k_{\text{ads}} = S(1 - \theta), \tag{8}$$

where S is the sticking coefficient (or probability) at Si. When all sites are occupied, the probability for adsorption is zero. Most etching processes operate near this limit.

Even on clean, perfect crystalline surfaces, adsorption is more complicated and often occurs by a precursor-mediated mechanism in which an adsorbate has a high sticking coefficient, even on an adsorbate-covered surface. The weakly bound adsorbate diffuses along the surface until it either finds a vacant site for adsorption (Si in the example above), reacts, or desorbs. On rough surfaces that are present during etching, the adsorption and diffusion processes are more complicated, with a range of differing adsorption sites and rates.

Although sticking coefficients are often treated as adjustable parameters in models, some measured values have been reported. These parameters usually do not correspond to the Langmuir–Hinshelwood sticking coefficient at a vacant site, as defined above, and instead are either reaction coefficients that lead to generation of products that desorb or incorporate into a growing film.

A reaction coefficient for etching,  $\varepsilon_{X(S)}$ , can be defined as the probability that an impinging neutral will react with an atomic or molecular material, S, in the absence of ion bombardment or other sources of energetic particles, to generate a volatile product that promptly desorbs. <sup>99</sup> It is given by

$$\varepsilon_{X(S)} = \frac{(x/y) N_A \rho_S R_{X(S)}}{M_S (n_X v_X/4)}, \tag{9}$$

where  $R_{X(S)}$  is the etching rate,  $N_A$  is Avogadro's number,  $\rho_S$  and  $M_S$  are the density and mass of the substrate, and x/y is the average stoichiometry of the  $SX_x$  etching products that desorb, divided by the  $X_y$  stoichiometry of the etchant (e.g., y = 2 for  $Cl_2$ ).

Reaction coefficients have been measured for some relevant etchants and materials and are important for determining isotropic etching rates and so degree of undercutting. The etching rate of substrate S by species X is often given in the form of an Arrhenius expression

$$R_{X(S)} = A T_g^n n_X \exp\left(-E_a/RT_S\right), \tag{10}$$

where A and  $E_a$  are the Arrhenius pre-exponential factor and activation energy, respectively,  $n_X$  is the number density of X at gas temperature  $T_g$ , and  $T_S$  is substrate temperature, and

n is either 0.5 or 0, depending on whether the dependence of the impingement rate on  $T_g$  is separated from or included in the activation energy. For n-type Si etching, the dopant level affects the pre-exponential. In these cases, A can be expressed as  $^{100}$

$$A = A_0 N_e^{\gamma}, \tag{11}$$

where  $N_e$  is the *n*-type carrier concentration and  $\gamma$  is an empirical factor.

## 3. Ion induced etching reactions

The etching rate for many materials during simultaneous exposure to ion and neutral fluxes is much faster than the sum of the sputtering and chemical etching rates (plasma etching's version of the "whole is greater than the sum of its parts"  $^{101}$ ). The details of this process are extremely complicated. Several distinct mechanisms have been identified. Although ion bombardment sometimes aids in removing a passivating species from horizontal surfaces that would otherwise slow or stop etching, in virtually all cases ion bombardment enhances the reaction between the neutrals and substrate that leads to the formation of a volatile product. This is true even in the case of etching of Si in fluorine-atom-generating plasmas such as  $SF_6/O_2$ , where the etching rate by F atoms is quite high.

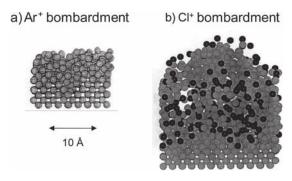

The details of ion-assisted etching reactions have been reviewed previously.<sup>5,102,103</sup> Coburn, Winters, and coworkers have show that for Ar<sup>+</sup>-assisted etching of a fluorinated Si surface, the process occurs by a "chemical sputtering" process in which ion bombardment causes chemical reactions to occur that lead to the formation of products that then desorb. These reactions are generally assumed to happen on a very short time scale (~1 ps)<sup>104</sup> in the collision cascade created by the transfer of momentum from the impacting, neutralized ion to the substrate and reactant atoms in the near-surface region. Product desorption can take much longer, but is usually not rate-limiting.

#### 4. Other plasma-surface reactions

Plasma interactions with surfaces other than those being etched also affect the plasma etching process, though indirectly. Species in the plasma stick on the walls and masked portions of the substrate and can lead to the growth of a film, or the formation of a product that desorbs. These processes modify the plasma species concentrations and can lead to changes in etching rates, profile shapes, selectivities, and other figures of merit. Therefore, surface reaction coefficients are of interest for conditions as close as possible to real etching plasmas.

Fisher and co-workers have measured sticking coefficients and reaction coefficients of selected radicals under conditions close to those in the plasma. <sup>105–107</sup> Beams of SiH, OH, NH, NH<sub>2</sub>, CF, and CF<sub>2</sub> radicals generated in various plasmas were directed at substrates such as SiO<sub>2</sub> and fluorocarbon films in a differentially pumped chamber, and detected by laser-induced fluorescence (LIF) as they impinge on a surface and reflect

from the surface. An image of the path of the incoming and outgoing radicals is captured, hence the technique is called "imaging of radicals interacting with surfaces." Sticking and/ or reaction coefficients can be obtained with this method. For CF<sub>2</sub> scattering off SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Si, stainless steel, and photoresist substrates, the flux of scattered CF<sub>2</sub> exceeds its incident flux, indicating that this product is formed by a surface reaction of other impinging species (e.g., CF and/or CF<sub>3</sub>) that are also present in the plasma beam source. <sup>108</sup>

# B. Selected diagnostic techniques for etching plasmas

It is beyond the scope of this article to review the many diagnostic methods that are available to characterize processing plasmas, including electrical probe methods to determine ion and electron number densities and electron energy distributions. Instead we will highlight a few selected techniques that are useful for understanding and monitoring etching processes. These can be divided into gas-phase and surface probes.

The gas phase plasma contains mostly neutrals. These are stable feed gas species, radicals formed by the decomposition of the feed gas, stable etching products, and radicals that can be primary products or product fragments that are formed by electron impact. In some cases, a complete determination of the plasma neutral composition is desired for a deeper understanding of plasma chemistry. In other cases, one or several species are monitored to sense endpoints when thin films have been etched away.

There is also an important need to monitor the chemical and physical nature of surfaces immersed in plasmas. This includes not only the surfaces of wafers being etched, but also the plasma chamber wall surfaces. Controlling the latter is essential for maintaining stable processing conditions, since the composition of radicals in the plasma is greatly affected by heterogeneous reactions that are in turn dependent on the nature of the chamber wall surface. Ellipsometry and infrared absorption spectroscopy are in situ methods that have been used to monitor species on surfaces in real time. The chemical composition of surfaces immersed in plasmas can also be investigated by electron spectroscopy methods [mostly x-ray photoelectron spectroscopy (XPS)] that require the sample to be transferred from the plasma chamber to the analysis chamber without exposure to air. Recently advances have been made in a "spinning wall" technique in which a small portion of the chamber wall is rapidly rotated such that the surface can be analyzed by Auger electron spectroscopy and desorption mass spectrometry. 109,110

## 1. Mass spectrometry

Mass spectrometry is the broadest gas-phase diagnostic method, capable of detecting any neutral or charged species in the plasma. In practice, however, this is anything but straightforward. In a "residual gas analysis" mode, mass spectrometry can be used to routinely monitor stable species that leave the plasma, and/or form in downstream regions on the way to the mass spectrometer. This can be used to infer

which radicals may be present in the plasma (e.g.,  $C_2F_6$  formation downstream from a  $CF_4$  plasma is likely a result of  $CF_3$  recombination). Etching products can also be detected by mass spectrometry, and can be used in end-point detection, although such an approach is almost never used because optical emission spectroscopy is simpler and more sensitive.

To detect reactive neutrals, a small aperture needs to be installed in the wall of the plasma chamber. Line-of-sight detection of species passing through the aperture and entering the input of the mass spectrometer ionizer is of course essential but not sufficient. Two stages of differential pumping are required and the product beam must be chopped to distinguish the beam signal from the background gas in the mass spectrometer chamber. Only when the neutral mean free path,  $\lambda_n$ , is comparable to the reactor radius, R (almost never the case), does mass spectrometry monitor species with similar efficiency at the center and edge of the plasma. Under typical conditions of R > 15 cm diameter chambers, and  $\lambda_n < 1$  cm (for gas pressures of > 5 mTorr), the method is highly biased toward species near the walls.

Another shortcoming with mass spectrometry is that it is difficult to assign peaks to a particular species. Occasionally, this is due to a coincidence in mass (e.g., Si and CO), but more commonly, the issue is distinguishing parents from daughter ions that are formed in the ionizer of the mass spectrometer. Cracking patterns for stable species such as SiCl<sub>4</sub> can be measured to help unravel the connection between the detection of daughter fragments and the number densities of the parent and daughter neutral species. Signal intensities can also be recorded as a function of the mass spectrometer electron impact ionizer energy. Such appearance potential measurements can help to separate the signals originating in daughter fragments from those corresponding to the parent ion of radicals. <sup>111–113</sup>

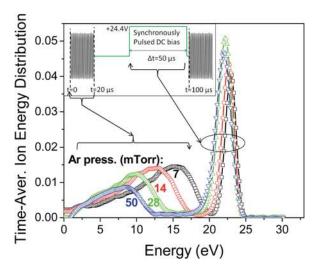

Ions can also be directly detected with a mass spectrometer, with the ionizer switched off. 113 An energy analyzer between the ion input region and the detector can energyselect the ions and by sweeping the pass energy, an ion energy distribution (IED) can be obtained with respect to ground potential (assuming the mass spectrometer is grounded). In CCPs and inductively coupled plasmas (ICPs) with no Faraday shield, the IED is governed by the electron temperature and the product of the ion transit time across the sheath and the frequency of oscillations in the sheath potential (i.e., the applied RF). When it takes many RF cycles for the ion to cross the sheath, and no collisions occur, ions will impinge on grounded surfaces with a nearly monoenergetic IED and an energy of the mean sheath potential. Knowing the composition of impinging ions and taking into account the influence of substrate bias, mass spectrometer measurements of ions impacting grounded surfaces at the edge of the plasma can be used to infer what happens at the RF-biased substrate.

## 2. Optical, gas phase techniques

Practical diagnostic methods for plasma etching must be nonintrusive. Optical techniques satisfy this requirement. Plasma-phase (as opposed to surface) optical diagnostics techniques include (in roughly decreasing order of usage) optical emission spectroscopy, LIF, UV absorption, infrared (IR) absorption, and laser-Raman scattering. Application of these spectroscopic techniques for thin film materials processing has been reviewed. 114

a. Optical emission spectroscopy. OES is the most widely used diagnostic technique in plasma etching. It was first used in an etching application by Harshbarger *et al.* in 1977 to study a  $CF_4/O_2$  plasma during Si etching in parallel plate plasma. They identified F, O, Si, and CO emissions and showed that F and Si emission exhibited a maximum as a function of  $O_2$  addition to  $CF_4$ .

The vast majority of optical emission in etching plasmas is a result of electron-impact excitation. Most atomic and diatomic species can be monitored by OES. Some triatomic molecules such as CF<sub>2</sub>, SiCl<sub>2</sub>, NH<sub>2</sub>, and CO<sub>2</sub><sup>+</sup> can also give rise to optical emission, but emission from larger molecules is either lacking because of low-lying, nonradiative bound and dissociative states or is broad and featureless because of the large density of vibrational states. Because of the complexity of the excitation mechanism, OES is usually a qualitative technique. This does not hamper the main application for OES: endpoint detection. It does, however, make it difficult (but not impossible) to determine quantitative, relative, and absolute species number densities by this method (see below).

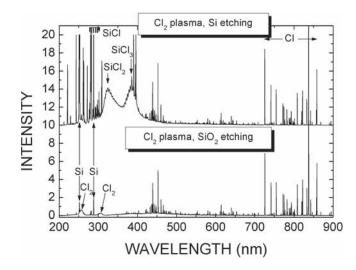

Typical optical emission spectra of a chlorine plasma during fast etching of Si and slow etching of SiO<sub>2</sub> are shown in Fig. 10. The spectra are dominated by emission from Cl, and, when large areas of Si are present and the substrate stage is RF-biased, from Si, SiCl, SiCl<sub>2</sub>, and SiCl<sub>3</sub> (and/or SiCl<sub>3</sub><sup>+</sup>). The Si and SiCl emissions are typically used to sense the endpoint of the etching of a thin film of Si in chlorine-containing plasmas. SiBr emission can also be used in HBr-containing plasmas. Emission from Cl<sub>2</sub> is also apparent in the spectrum recorded during etching of SiO<sub>2</sub>. Cl<sub>2</sub> emission near 305 nm is

Fig. 10. Plasma induced emission spectra of a  $\text{Cl}_2$  ICP system described elsewhere (Ref. 456) during etching of Si (top) and  $\text{SiO}_2$  (bottom, intensities multiplied by 4.33 before being plotted).

attributed to electron impact excitation of an ion pair state of Cl<sub>2</sub> at 8.4 eV, or possibly to one at 9.2 eV. 116

$$Cl_2 + e \rightarrow Cl_2^* + e, \tag{12}$$

$$Cl_2^* \rightarrow Cl_2 + h\nu,$$

(13)

where the superscript "\*" indicates the electronically excited state(s) and  $h\nu$  is a photon of frequency  $\nu$  (= 9.84 × 10<sup>14</sup> s<sup>-1</sup> for a wavelength of 305 nm). It has been shown that the Cl emissions are mostly a result of electron impact excitation of Cl atoms <sup>116–118</sup>

$$Cl + e \to Cl^* + e, \tag{14}$$

$$Cl^* \rightarrow Cl + h\nu.$$

(15)

This makes detection of Cl emission useful for measuring endpoints as well; as a material that consumes Cl is etched away, Cl emission increases.

For more quantitative determination of even relative Cl number densities, it is necessary to consider that Cl\* is also excited to a smaller extent from dissociation of Cl<sub>2</sub>. <sup>118</sup>

$$Cl_2 + e \rightarrow Cl + Cl^* + e. \tag{16}$$

Hence, Cl emission intensity depends on both Cl and Cl<sub>2</sub> number density. O emission behaves similarly, originating from both O and O<sub>2</sub> in oxygen plasmas. The dissociative excitation of O emission is relatively much more important in O<sub>2</sub> plasmas compared to Cl in Cl<sub>2</sub> plasmas because of the stronger O<sub>2</sub> bond relative to Cl<sub>2</sub>, and generally higher electron temperatures in O<sub>2</sub> plasmas. <sup>119</sup> If the plasma contains large fractions of SiCl<sub>x</sub> etching products and not much Cl, then production of Cl emission from dissociative excitation of SiCl<sub>x</sub> may also need to be included, but the strong SiCl<sub>x</sub> bond should make this a minor process, except for extreme conditions.

Emission from  $\mathrm{SiCl_x}$  indicates that these species are present in the plasma. Of course, some of these emissions could be the result of dissociative excitation of higher Si-chlorides, such as  $\mathrm{SiCl_3} + e \to \mathrm{SiCl_2}^* + \mathrm{Cl} + e$ . This does not matter for endpoint detection but does prevent OES from providing anything more than a qualitative indicator of ground state number densities of these species. It is much better to detect these species directly by UV absorption spectroscopy or mass spectrometry. 121,122

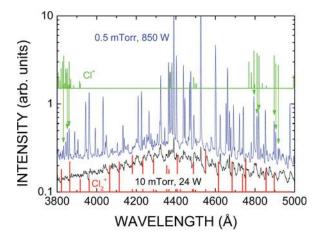

Weak emission from  $\mathrm{Cl}^+$  in the UV and visible regions is also observed in high-density  $\mathrm{Cl}_2$  plasma emission spectra, as shown in the expanded spectrum in Fig. 11 (blue, upper trace). Emission from  $\mathrm{Cl}_2^+$  between 400 and 550 nm can also be found in the spectrum at high power and low pressure in Fig. 11 (blue, upper trace), but it is relatively much more prominent in lower density plasmas, as shown in the example in Fig. 11 (black, bottom trace). Electronically excited ions such as  $\mathrm{Cl}_2^+$  can be produced by a one-step electron impact excitation from the ground state of neutral  $\mathrm{Cl}_2$

$$Cl_2 + e \rightarrow Cl_2^+(A^2\Pi_u) + 2e,$$

(17)

Fig. 11. (Color online) Low power (24 W)–high pressure (10 mTorr), and high power (850 W)–low pressure (0.5 mTorr)  ${\rm Cl_2}$  ICPs.  ${\rm Cl_2}^+$  bandhead and  ${\rm Cl}^+$  line positions and intensities are represented by the "stick spectra" at the top and bottom.

$$Cl_2^+(A^2\Pi_u) \to Cl_2^+(X^2\Pi_g) + h\nu.$$

(18)

If little emission is detected from  $\operatorname{Cl}_2^+$  and strong emission is observed from  $\operatorname{Cl}^+$ , then  $\operatorname{Cl}^+$  is likely the dominant ion, as it was at  $0.5\,\mathrm{mTorr}$  and  $850\,\mathrm{W}$ . When the converse is true, then  $\operatorname{Cl}_2^+$  is the dominant positive ion, as it is in the example of  $10\,\mathrm{mTorr}$  and  $24\,\mathrm{W}$ . This is also consistent with direct measurements of  $\operatorname{Cl}_2^+$  by LIF in a  $\operatorname{Cl}_2$  plasma: when the reactor was operated in a low-power CCP mode,  $\operatorname{Cl}_2^+$  emission was relatively strong,  $\operatorname{Cl}^+$  emission was weak and LIF measurements taken together with Langmuir probe measurements showed that  $\operatorname{Cl}_2^+$  was the dominant ion, while in the high-power ICP mode,  $\operatorname{Cl}^+$  emission was strong and  $\operatorname{Cl}_2^+$  was barely detectable in either emission or by LIF, hence the dominant ion was  $\operatorname{Cl}^+$ .  $^{123,124}$

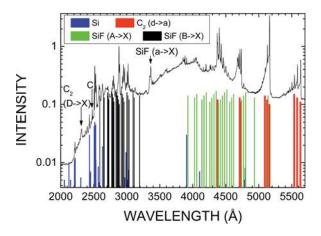

A sample emission spectrum of a fluorocarbon plasma  $(C_2F_6)$  during etching of  $SiO_2$  and Si is shown in Fig. 12. The spectrum contains features that can be assigned to  $C_2$ , Si, SiF, and C. In addition, emission from F was found in the

Fig. 12. (Color online) Emission spectrum of a  $C_2F_6$  inductively coupled plasma during etching of  $SiO_2$  and Si. The "stick" spectra indicate the positions of known emissions from Si, SiF, C, and  $C_2$ . The heights of the "sticks" are of no significance.

red/near-infrared region (not shown). Because of the presence of a heated "silicon roof" in the reactor used to obtain this spectrum, the plasma was depleted of F atoms, hence fluorine is contained in  $SiF_x$  species and not as much is available to form  $CF_2$  and  $CF_3$ . Emission from these species tends to dominate lower density plasmas. In high density fluorocarbon plasmas depleted of fluorine, the radical  $C_2$  appears to be a dominant species. The polymer layer that deposits under these conditions is depleted in fluorine.

b. Actinometry. If an excited state (k) of species X is populated solely by electron impact excitation from its ground state (i) then its absolute ground state number density  $(n_X)$  can, in principle, be obtained from the intensity  $(I_{X,i,j,k})$  of emission at wavelength  $\lambda_{X,j,k}$  accompanying the transition  $X_k \to X_j$ , and the relationship<sup>5</sup>

$$I_{X,i,j,k} = 4\pi a(\lambda_{X,j,k}) n_X Q_{X,k} b_{X,j,k} \int_0^\infty \sigma_{X,i,k}(v) v^3 f_e(v) dv,$$

(19)

where  $\alpha(\lambda_{X,j,k})$  is the spectrometer sensitivity at  $\lambda_{X,j,k}$ ,  $\sigma_{X,i,k}(v)$  is the cross section at electron speed v for electron impact excitation of  $X_k$  from  $X_i$ ,  $f_e(v)$  is the electron speed distribution function  $4\pi v^2 f_e(v) dv$  (the number of electrons with speeds between v and v+dv),  $Q_{X,k}=\tau^{-1}/(\tau^{-1}+k_qP)$  is the quantum yield for emission by  $X_k$ , where  $\tau$  and  $k_q$  are the radiative lifetime and quenching rate constant for  $X_k$  by all species at total pressure P, and  $b_{X,j,k}$  is the branching ratio for the transition  $X_k \to X_j$ .

The electron speed distribution and the proportionality constant are difficult to determine. Consequently rare gas actinometry is often used to convert emission intensities into quantitative, relative number densities. This technique was first applied in plasmas by Coburn and Chen. <sup>125</sup> In this approach, a small amount of a rare gas, A, with an excited state  $A_k$  that has an energy close to that of  $X_k$  is added to the discharge. The energy levels of the rare gases span the range from 9.7 eV for Xe to 23 eV for He. Assuming that rare gas emissions are caused solely by electron impact excitation of the ground state, an expression analogous to Eq. (19) relates emission from the rare gas to its known number density

$$I_{A,i,j,k} = 4\pi a(\lambda_{A,j,k}) n_A Q_{A,k} b_{A,j,k} \int_0^\infty \sigma_{A,i,k}(v) v^3 f_e(v) dv.$$

(20)

It is usually assumed that the relative energy dependence of the cross section for electron impact excitation of the species of interest is the same as that of the rare gas, i.e.,  $\sigma_{A,i,k}(v) \propto \sigma_{X,i,k}(v)$  at any v. Consequently, the  $n_X$  can be simply expressed as

$$n_X = a_{X,A} n_A (I_{X,i,i,k}/I_{A,i,i,k}),$$

(21)

where  $a_{X,A}$  is a proportionality constant. Relative densities of atoms (F, Cl, H, and O), and small molecules (Cl<sub>2</sub>, CF, CF<sub>2</sub>,

BCl) have been determined in a wide variety of plasmas by this method. In a few cases, absolute number densities have also been measured through several calibration methods.

Actinometry is a simple method that, when carefully applied, can provide valuable quantitative measurements of species concentrations in commercial plasmas with limited optical access. Perhaps the most common and most reliable use of actinometry is for measurement of F atom densities in fluorine-containing plasmas. Fluorine atom actinometry, using the 750.4 nm line of Ar, was first reported by Coburn and Chen for CF<sub>4</sub>/O<sub>2</sub> plasmas<sup>125</sup> and was later used by many researchers, including d'Agostino *et al.*<sup>126</sup>,127 in CF<sub>4</sub>/O<sub>2</sub> and SF<sub>6</sub>/O<sub>2</sub> plasmas, Donnelly *et al.*<sup>128</sup> in CF<sub>4</sub>/O<sub>2</sub> and NF<sub>3</sub>/Ar plasmas, Schabel *et al.*<sup>129</sup> in C<sub>2</sub>F<sub>6</sub>/Ar ICPs, and Karakas *et al.*<sup>130</sup> in CH<sub>3</sub>F/O<sub>2</sub> plasmas.

Atomic oxygen emission actinometry has also been reported,  $^{131,132}$  with verification by LIF.  $^{132}$  When divided by Ar emission at 750.4 nm, it was found that O emission at 844.6 nm  $(3p^3P \rightarrow 3s^3S)$ , tracked  $n_O$  reasonably well, while O emission at 777.4 nm  $(3p^5P \rightarrow 3s^5S)$  did not. The latter was attributed to dissociative excitation of  $O_2$ , as verified by linewidth measurements. As mentioned above, the O 844.6 nm line also suffers from dissociative excitation of  $O_2$ , even in a high density ICP. This is because O atom densities are usually less than those of  $O_2$  (if oxygen is not being largely consumed by reactions with materials or feed gas components), a result of the large  $O_2$  bond strength (5.11 eV).

Actinometry has also been widely used for measurement of relative number densities of Cl-atoms. Often the Ar 750.4 nm line is used, even though it is not such a good energy match for the Cl emitting levels. Using the Xe 828.0 or 834.7 nm line provides a much better energy match to the Cl emitting levels, and more consistent tracking of Cl number density. In addition, dissociative excitation of  $Cl_2$  [reaction (16)] is a source of Cl emission at low  $n_{Cl}$ . Direct evidence for this was observed in  $Cl_2$  plasmas.

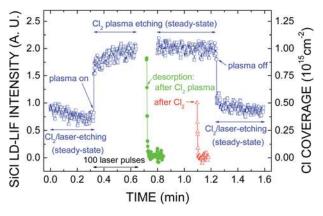

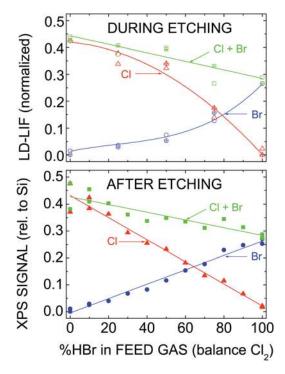

## 3. Surface techniques

Analysis of plasma-exposed surfaces can be carried out in a number of ways. It is far easier to perform the analysis by moving the sample (usually under vacuum) to a chamber equipped with a standard analysis method such as XPS. This method is discussed in some detail in the next section. In some cases, it is of interest to analyze surfaces while they are immersed in the plasma. Several approaches have been demonstrated. Aydil and co-workers have used total internal reflection, Fourier-transform infrared absorption to monitor adsorbates on a GaAs sample mounted near the reactor wall. 133,134 This technique provides quantitative analysis for many species with monolayer detection, but requires IRtransparent substrates and relatively long times. In the laser desorption-laser induced fluorescence (LD-LIF) technique, a pulsed laser heats the surface, causing desorption of adsorbates that are detected by LIF, excited by the tail of the same laser pulse. 135-139 This method has very high sensitivity for some species (e.g., <1% of a monolayer of SiCl and SiBr) and fast (ns) time response, but the interpretation is more difficult and it is limited to a relatively few species, and thermally robust surfaces. Another approach, called the "spinning wall" method inserts a cylindrical substrate into the reactor wall. 109,121,122,140–146 Part of the cylinder is in the plasma while another section is in a differentially pumped chamber with a mass spectrometer and Auger electron spectrometer (AES) facing the surface. By rapidly rotating the substrate, portions of the surface that were in the plasma as little as 1 ms ago can be diagnosed. Weakly bound species and heterogeneous reaction products can be observed with the mass spectrometer and strongly bound species can be detected by AES.

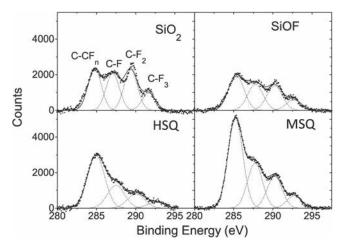

a. Vacuum-transfer XPS. Electron spectroscopy techniques such as XPS and Auger electron spectroscopy are extremely useful for quantitative identification of species on surfaces, and especially for XPS, chemical bonding, and structural information. The plasma environment does not allow these techniques to be used in real time; therefore, analysis of plasma-etched materials is carried out after etching by transferring the sample to a separate analysis chamber. If this is done by bringing the sample out into the air, then the surface layer will be oxidized in most cases. Of course, characterization of air-exposed wafers is often of interest for long-term reliability reasons, but if studying the plasma-surface interaction is the prime motivation, then air exposure must be avoided.

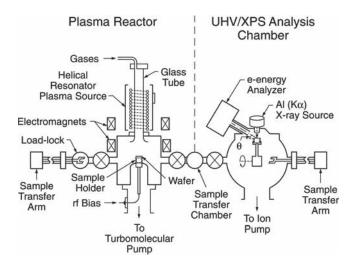

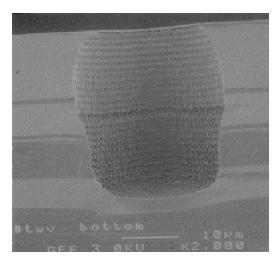

Several research groups have constructed integrated plasma etching/surface analysis machines that allow samples to be moved under vacuum from the etching chamber to the analysis chamber. <sup>147–154</sup> This is usually done by moving the sample through a loadlock chamber with linear transfer devices. One such system is shown in Fig. 13. One obvious question is how does the surface change between the instant when the plasma is extinguished and when analysis begins, a delay of at least several minutes after etching? Chemisorbed

Fig. 13. Schematic of an inductively coupled (helical resonator) plasma reactor attached to a sample transfer chamber that is connected to an ultrahigh vacuum (UHV) chamber equipped with XPS. The take-off angle  $\theta$  is the angle between the axis of the photoelectron collection lens and the wafer plane (Ref. 115).

species will not desorb, but physisorbed species present at low coverages during etching will react and/or desorb before analysis can be carried out. Weakly adsorbed species, though often important for etching reactions, are not expected to be present at high concentrations. The chemisorbed layer is also very important, since ion bombardment causes reactions in this layer that lead to etching. The vacuum transfer surface analysis method provides valuable insights into the nature of this layer, which is stable and long lived in the absence of air or ion bombardment.

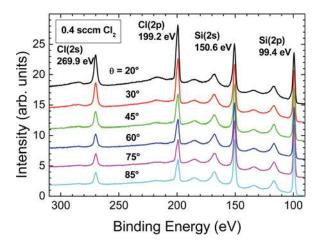

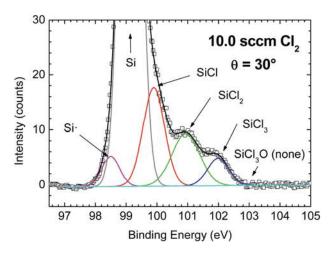

Si etching in F and Cl-containing plasmas has been studied in some detail. Low resolution spectra of unpatterned Si after etching in a chlorine ICP are shown in Fig. 14. Si(2p), Si(2s), Cl(2p), and Cl(2s) peaks are readily identified, along with O(1s) and C(1s) contamination in some cases. Loss features at multiples of the bulk Si plasmon resonance are also observed. The plasmon features to the high binding energy side of the Cl(2p) and Cl(2s) peaks indicate that some Cl has penetrated rather deep into the Si. When the "take-off" angle is small (the angle between the electron collection direction and the surface), XPS is more surface sensitive. The Cl peaks become more intense relative to Si, indicating that Cl is near the surface. From further analysis of the take-off angle dependence of the intensities in the spectra in Fig. 14, the thickness of the chlorinated layer can be derived  $(\sim 2 \text{ nm})$ . This subject is expanded upon below in the section on the nature of the Si surface layer.

# C. Mechanistic studies of etching of selected materials

All anisotropic etching processes involve one (or both) of the above mechanisms. In most cases, no reaction takes place between the neutrals and the material to be etched, despite the fact that a volatile product can form and the reaction between the atomic etchants (e.g., Cl atoms) and the substrate (e.g., Si) is exothermic to produce the gaseous product (SiCl<sub>4</sub>). In this case, energetic ion bombardment speeds up the rate of reactions that generate gaseous products and anisotropic etching occurs. In a few cases, such as

Fig. 14. (Color online) Low resolution XPS spectra as a function of takeoff angle for blanket Si etched in a high density  $\text{Cl}_2$  ICP, under conditions described in a previous publication (Ref. 115).

in etching of Al in a chlorine-containing plasma, spontaneous fast etching occurs in the absence of ion bombardment and this process is stopped by depositing a very thin layer on the sidewalls. This protective layer is sputtered away faster than it can deposit on horizontal surfaces, allowing anisotropic etching to be obtained. Selected examples are now presented in some detail.

#### 1. Si etching in halogen-containing plasmas

Coburn and Winters were the first to show conclusively that the etching rate of a material (Si), normally slow when exposed to either neutral etchants (XeF<sub>2</sub>) or ion bombardment (Ar<sup>+</sup>), was greatly accelerated in the simultaneous exposure to both. This classic experiment was carried out with beams of XeF<sub>2</sub> and Ar<sup>+</sup> in a high-vacuum chamber, thus avoiding the complex plasma environment. Many variations on this experiment have contributed to our understanding of ion-assisted etching processes. A summary of some of this work is presented in Table I of Vitale *et al.* 156

Early work by the IBM group focused on ion-enhanced etching of Si by  $XeF_2$ , partly because etching of Si in  $CF_4$ -containing plasmas was one of the first plasma etching processes developed. F-atoms are the active etchant for Si in this plasma, as well as in  $SF_6$  plasmas that are used to etch Si at faster rates. Most anisotropic etching of silicon is carried out in Cl and/or Br-containing plasmas, however, because isotropic chemical etching by Cl and Br is much slower than etching by F-atoms. Most, but not all of the technologically relevant combinations of ions  $(Cl_2^+, Cl^+, \text{and } Ar^+)$  and neutrals  $(Cl_2$  and Cl) have been investigated.

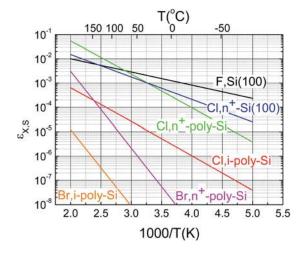

Isotropic etching of Si can also occur as a result of chemical reactions with F, Cl, or Br atoms to form volatile products. These processes are described by the reaction probabilities,  $\varepsilon_{X(S)}$ , defined above. Etching rates and reaction probabilities for Si by F atoms have been reported by Flamm *et al.* <sup>99</sup> Values for Cl atoms have been given by Ogrzylo *et al.* <sup>100</sup> and Walker and Ogrzylo. <sup>157</sup> These researchers also measured reaction coefficients for Br atoms with Si. <sup>158</sup> Using a density of 2.33 for Si, and assuming that the etching products are SiF<sub>4</sub> for F, and an equal mixture of the di-halide and tetra-halide (so x = 3) for Cl and Br, reaction probabilities from these studies are reproduced in Fig. 15 as a function of substrate temperature.

Several general conclusions can be drawn from the data in Fig. 15. At room temperature, chemical etching of Si by halogen atoms follows the trend F > Cl > Br, expected from the Si-halogen bond strengths (140, 90, and 80 kcal/mol, respectively). The dopant type and level strongly affects the Cl and Br reactivity. Highly doped n-type Si (n<sup>+</sup>-Si) etches much faster than lightly doped n-type or p-type Si. This dopant dependence has been attributed to the shift in the Fermi level, making formation of Cl<sup>-</sup> favored. Cl<sup>-</sup> is drawn through the SiCl<sub>x</sub> surface layer by the resulting electric field. The formation of F<sup>-</sup> has also been invoked to explain the smaller enhancement in the etching of n<sup>+</sup>-Si by F-atoms. Isotropic etching of Si by F is fast enough to be a concern for anisotropic etching in high density plasmas that generate

Fig. 15. (Color online) Reactions coefficients for F, Cl, and Br atoms with Si, generated from data and expressions given in published studies (Refs. 99, 100, 157, and 158).

large percentages of F atoms (e.g.,  $CF_4/O_2$ ,  $SF_6/O_2$ , or  $NF_3$ ). To slow isotropic etching by F atoms, it is often necessary to add a species that coats the sidewall and slows lateral etching. Thermally activated isotropic etching can also be slowed, relative to ion assisted etching, by cooling the substrate. At low partial pressures of Cl atoms ( $<10\,\text{mTorr}$ ), isotropic etching by Cl and Br atoms is very slow for all levels of p-type, intrinsic, and lightly to moderately doped n-type Si. Highly doped n-type Si will exhibit a large degree of undercutting at Cl partial pressures of only a few mTorr. Under these cases, some sidewall protection scheme is necessary.

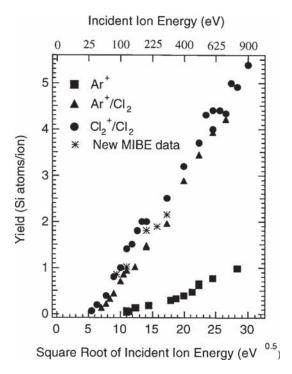

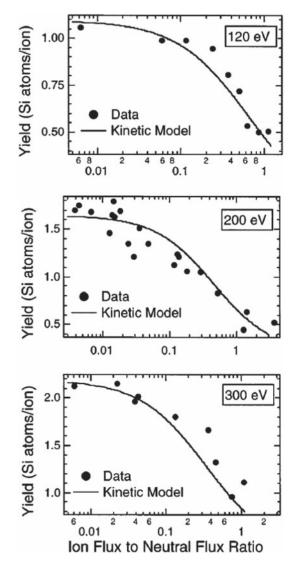

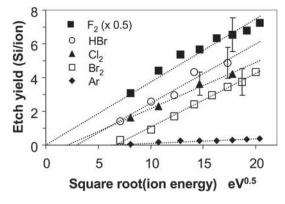

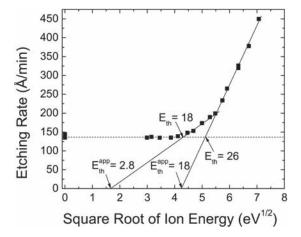

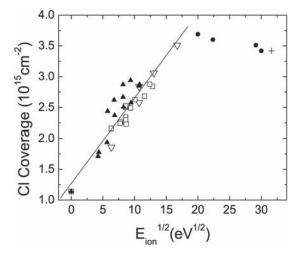

For anisotropic etching, the ion-assisted etching rate must greatly exceed the etching rate by neutral species. The fundamental parameter of interest is the ion-assisted etching yield, defined as the number of substrate atoms or molecules removed per incident ion. Figure 16 presents measurements by Levinson et al. 160 of Si yields as a function of the square root of ion energy for Cl<sub>2</sub> and either Ar<sup>+</sup> or Cl<sub>2</sub><sup>+</sup>, carried out in the limit of a high neutral-to-ion flux ratio. A simple linear square root relationship was found, with a threshold energy below which ion assisted etching ceases, as has been observed in many etching investigations.<sup>161</sup> At higher energies, the nature of the ion (reactive Cl<sub>2</sub><sup>+</sup> versus unreactive Ar<sup>+</sup>) plays only a small role in determining the yield. For example, near  $500 \,\mathrm{eV}$ , the yields are only  $\sim 5\%$  higher for Cl<sub>2</sub><sup>+</sup>/Cl<sub>2</sub> than for Ar<sup>+</sup>/Cl<sub>2</sub>, while at 60 eV, the yields for  $\text{Cl}_2^+/\text{Cl}_2$  are  $\sim 50\%$  higher than for  $\text{Ar}^+/\text{Cl}_2$ .  $^{160}$  Yields extrapolate to 0 at about 25 and 35 eV for  $\text{Cl}_2^+/\text{Cl}_2$  and Ar<sup>+</sup>/Cl<sub>2</sub>, respectively; hence, near threshold, the nature of the ion becomes important. The Ar<sup>+</sup>/Cl<sub>2</sub> yield at 100 eV is in good agreement with the value of 0.7 reported by Chang et al. 162 for the same conditions.

Yields have been measured as a function of the Ar<sup>+</sup>-to-Cl<sub>2</sub> flux ratio (Fig. 17) and have been found to saturate at a low ratio, indicating ion-flux-limited etching and a small sticking coefficient by Cl<sub>2</sub> on the ion-bombarded/chlorinated surface. At high ion-to-neutral flux ratios (not usually obtainable in plasma etching processes unless the halogen fraction in the feed gas is very low), the surface is mostly free of

Fig. 16. Si ion-assisted etching yields as a function of the square root of ion energy, measured with high neutral-to-ion beam flux ratios. Reproduced with permission from Levinson *et al.*, J. Vac. Sci. Technol. A **15**, 1902 (1997). Copyright 1997, American Vacuum Society.

adsorbed Cl and the sticking coefficient is much higher [0.5 (Ref. 163)].

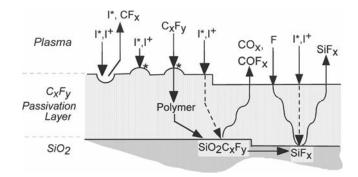

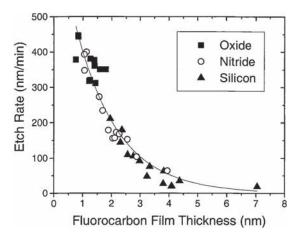

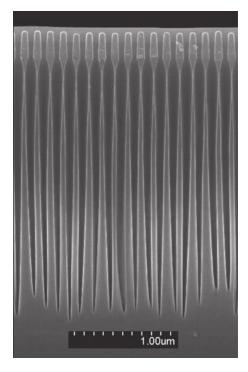

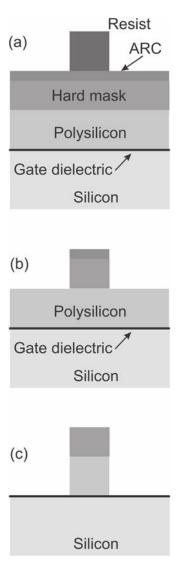

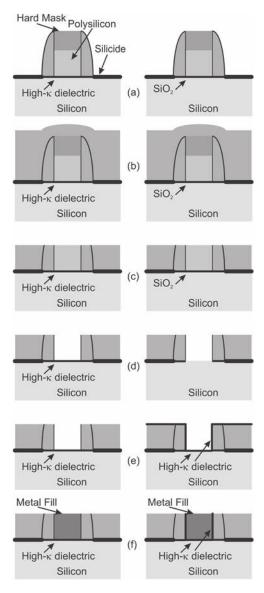

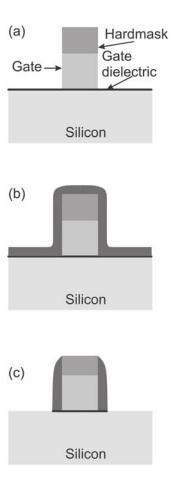

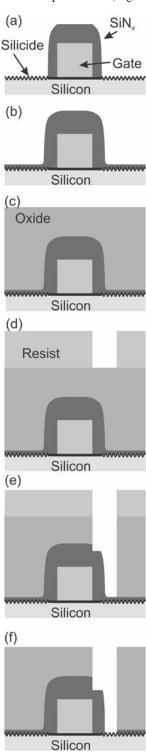

Argon ion-assisted etching by Cl-atoms has also been reported. Two to five times higher ion yields are found when the surface is chlorinated with Cl instead of Cl<sub>2</sub>. <sup>162</sup> The enhancement for Cl vs Cl<sub>2</sub> is smaller (about two-fold) with Cl<sup>+</sup>, compared to Ar<sup>+</sup>. <sup>164</sup> These results indicate that when ion-bombarded Si is exposed to Cl, it forms a more heavily chlorinated surface layer than when it is instead exposed to Cl<sub>2</sub>, but that some of the Cl comes from Cl<sup>+</sup> (and presumably Cl<sub>2</sub><sup>+</sup>) in a chlorine plasma. This results agrees with LD-LIF studies (see Fig. 18), where the Cl areal density on Si exposed to a chlorine ICP was about twice that on Si exposed to Cl<sub>2</sub> gas with the plasma off.