# POEMS: End-to-End Performance Design of Large Parallel Adaptive Computational Systems

Vikram S. Adve, *Member*, *IEEE*, Rajive Bagrodia, *Senior Member*, *IEEE*, James C. Browne, *Member*, *IEEE*, Ewa Deelman, *Member*, *IEEE*, Aditya Dube, Elias N. Houstis, John R. Rice, *Member*, *IEEE*, Rizos Sakellariou, *Member*, *IEEE*, David J. Sundaram-Stukel, Patricia J. Teller, *Member*, *IEEE*, and Mary K. Vernon, *Member*, *IEEE Computer Society*

Abstract—The POEMS project is creating an environment for end-to-end performance modeling of complex parallel and distributed systems, spanning the domains of application software, runtime and operating system software, and hardware architecture. Toward this end, the POEMS framework supports composition of component models from these different domains into an end-to-end system model. This composition can be specified using a generalized graph model of a parallel system, together with interface specifications that carry information about component behaviors and evaluation methods. The POEMS Specification Language compiler, under development, will generate an end-to-end system model automatically from such a specification. The components of the target system may be modeled using different modeling paradigms (analysis, simulation, or direct measurement) and may be modeled at various levels of detail. As a result, evaluation of a POEMS end-to-end system model may require a variety of evaluation tools including specialized equation solvers, queuing network solvers, and discrete-event simulators. A single application representation based on static and dynamic task graphs serves as a common workload representation for all these modeling approaches. Sophisticated parallelizing compiler techniques allow this representation to be generated automatically for a given parallel program. POEMS includes a library of predefined analytical and simulation component models of the different domains and a knowledge base that describes performance properties of widely used algorithms. This paper provides an overview of the POEMS methodology and illustrates several of its key components. The methodology and modeling capabilities are demonstrated by predicting the performance of alternative configurations of Sweep3D, a complex benchmark for evaluating wavefront application technologies and high-performance, parallel architectures.

**Index Terms**—Performance modeling, parallel system, message passing, analytical modeling, parallel simulation, processor simulation, task graph, parallelizing compiler, compositional modeling, recommender system.

### 1 Introduction

DETERMINING the performance of large-scale computational systems across all stages of design enables more effective design and development of these complex software/hardware systems. Toward this end, the Performance Oriented End-to-end Modeling System (POEMS) project is creating and experimentally evaluating a problem solving

V. Adve is with the Computer Science Department, University of Illinois at Urbana-Champaign, Urbana, IL 61801. E-mail: vadve@cs.uiuc.edu.

Manuscript received 18 Apr. 1999; revised 29 Dec. 1999; accepted 15 Mar. 2000

Recommended for acceptance by A. Cheng, P. Clementes, and M. Woodside. For information on obtaining reprints of this article, please send e-mail to: tse@computer.org, and reference IEEECS Log Number 111938.

environment for end-to-end performance analysis of complex parallel/distributed systems, spanning application software, operating system (OS) and runtime system software, and hardware architecture. The POEMS project leverages innovations in communication models, data mediation, parallel programming, performance modeling, software engineering, and CAD/CAE into a comprehensive methodology to realize this goal. This paper presents an overview of the POEMS methodology, illustrates the component models being developed in the POEMS project by applying them to analyze the performance of a highly-scalable application, and finally, describes preliminary work being performed in integrating multiple different models for a single application using the POEMS methodology.

The key innovation in POEMS is a methodology that makes it possible to compose multidomain, multiparadigm, and multiresolution component models into a coherent system model. Multidomain models integrate component models from multiple semantic domains; in the case of POEMS, these domains are application software, OS/runtime software, and hardware. Multiparadigm models allow the analyst to use multiple evaluation paradigms—analysis, simulation, or direct measurement of the software or hardware system itself—in a single system model. To facilitate the integration of models from

R. Bagrodia and E. Deelman are with the Computer Science Department, University of California at Los Angeles, Los Angeles, CA 90095-1596.

E-mail: {rajive, deelman}@cs.ucla.edu.

J.C. Browne and A. Dube are with the Department of Computer Science, University of Texas at Austin, Austin, TX 78712-1188.

E-mail: {browne, dube}@cs.utexas.edu.

E. Houstis and J. Rice are with the Computer Science Department, Purdue University, West Lafayette, IN, 47907-1398.

E-mail: {jrr, enh}@cs.purdue.edu.

R. Sakellariou is with the Computer Science Department, University of Manchester, Manchester M13 9PL, UK. E-mail: rizos@cs.man.ac.uk.

D. Sundaram-Stukel and M. Vernon are with the Computer Science Department, University of Wisconsin-Madison, Madison, WI 53706.

E-mail: {sundaram, vernon}@cs.wisc.edu.

P. Teller is with the Department of Computer Science, The University of Texas at El Paso, El Paso, TX 79968. E-mail: pteller@cs.utep.edu.

different paradigms, the specification and implementation of POEMS models is accomplished through formulating component models as compositional objects with associative interfaces [11], [12]. Associative module interfaces extend conventional interfaces to include complete specification of component interactions. A specification language (the POEMS Specification Language or PSL) for specification of multidomain, multiparadigm, multiresolution performance models has been designed and a compiler for this language is under development.

The POEMS project is building an initial library of component models, at multiple levels of granularity, for analyzing both nonadaptive and adaptive applications on highly-scalable architectures. POEMS supports analytical models, discrete-event simulation models at multiple levels of detail, and direct execution. The analytical models include deterministic task graph analysis [1], the LogP [15] family of models including LogGP [5] and LoPC [18], and customized Approximate Mean Value Analysis (AMVA) [36]. Simulation models include validated stateof-the-art processor and memory hierarchy models based on SimpleScalar [14], interconnection network models using the PARSEC parallel simulation language [9], large-scale parallel program simulations using the MPI-Sim simulator [28], [10], and parallel I/O system simulators [8]. A unified application representation based on a combination of static and dynamic task graphs has been developed that can serve as a common workload representation for this wide range of performance models.

Ongoing research within POEMS is developing techniques to integrate subsets of two or more of these component models, as a first step towards automatic integration of models within the POEMS framework. One such effort is integrating a compiler-generated analytical model based on the static task graph with the MPI-Sim simulator. This integrated model has the potential to increase greatly the size of problems and systems that can be simulated in practice. In addition, it can be expanded to include detailed processor simulation (e.g., with the SimpleScalar simulator), ideally for a small subset of the computational tasks. Another effort is examining the integration of MPI-Sim, LogGP, and SimpleScalar models. These ongoing efforts are described briefly in Section 6.

The project also is building a knowledge base of performance data, gathered during the modeling and evaluation process, which can be used to estimate, as a function of architectural characteristics, the performance properties of widely used algorithms. The knowledge base, along with the component models, application task graphs, and formal task executions descriptions (called TEDs), is stored in the POEMS database, an integral part of the POEMS system.

POEMS development is being driven by the design evaluations of highly-scalable applications executed on parallel architectures. The first driver application is the Sweep3D [22] program that is being used to evaluate advanced and future parallel architectures at Los Alamos National Laboratory.

Section 2 presents an overview of the Sweep3D application, which is used to illustrate the POEMS methodology

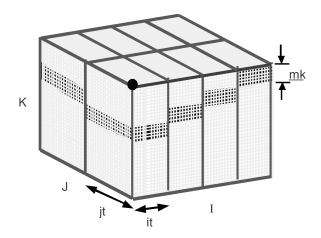

Fig. 1. One wavefront of Sweep3D on a 2×4 processor grid.

and performance prediction capabilities. Section 3 describes the conceptual elements of the POEMS methodology and illustrates it with an example. Section 4 presents the suite of initial POEMS performance tools and the initial library of component models that are under development for Sweep3D. Section 5 presents results of applying these models to provide performance projections and design results for Sweep3D. Section 6 describes ongoing research on the development and evaluation of integrated multiparadigm models in POEMS. Section 7 discusses related work. Conclusions are presented in Section 8.

# 2 POEMS DRIVER APPLICATION: SWEEP3D

The initial application driving the development of POEMS is the analysis of an ASCI kernel application called Sweep3D executed on high-performance, parallel architectures such as the IBM SP/2, the SGI Origin 2000, and future architectures. The Sweep3D application is an important benchmark because it is representative of the computation that occupies 50-80 percent of the execution time of many simulations on the leading edge DOE production systems [19]. Our analysis of this application has three principal goals. One goal is to determine which of the alternative configurations of the Sweep3D application has the lowest total execution time on a given architecture. A related, second goal is to provide quantitative estimates of execution time for larger systems that are expected to be available in the near future. The third goal is to predict the quantitative impact of various possible architectural and/or OS/runtime system improvements in reducing the required execution time. This section contains a brief description of this application; Sections 4 and 5 discuss how the POEMS methodology is being applied to obtain the desired performance projections for Sweep3D.

The Sweep3D kernel is a solver for the three-dimensional, time-independent, neutron particle transport equation on an orthogonal mesh [22]. The main part of the computation consists of a *balance* loop in which particle flux out of a cell in three Cartesian directions is updated based on the fluxes into that cell and other quantities such as local sources, cross section data, and geometric factors.

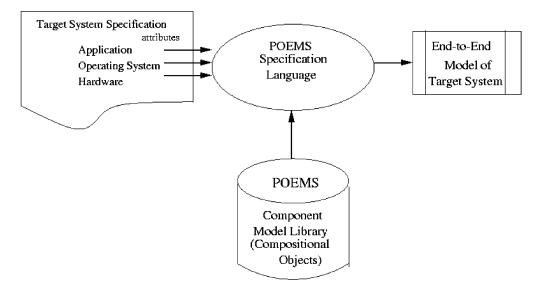

Fig. 2. Overview of the POEMS environment.

Fig. 1 illustrates how the three-dimensional computation is partitioned on a 2×4 two-dimensional processor grid. That is, each processor performs the calculations for a column of cells containing J/2  $\times$  I/4  $\times$  K cells. The output fluxes are computed along a number of directions (called angles) through the cube. The angles are grouped into eight octants, corresponding to the eight diagonals of the cube (i.e., there is an outer loop over octants and an inner loop over angles within each octant). Along any angle, the flux out of a given cell cannot be computed until each of its upstream neighbors has been computed, implying a wavefront structure for each octant. The dark points in the figure illustrate one wavefront that originates from the corner marked by the circle. The processor containing the marked corner cell is the first to compute output fluxes, which are forwarded to the neighboring processors in the *i* and j dimensions, etc. In order to increase the available parallelism, the wavefront is pipelined in the k dimension. That is, a processor computes the output fluxes for a partial column of cells of height mk, as shown in the figure, and then forwards the output fluxes for the partial column to its neighboring processors before computing the next partial block of results. (Since the octant starts in the marked upper corner of the cube, the next partial block of cells to be computed is below the dark shaded partial block in each column.) The computation is pipelined by groups of mmi angles, not shown in the figure. Therefore, the amount of computation for each "pipelined block" is proportional to  $it \times jt \times mk \times mmi$ , where it and jt are the number of points mapped to a processor in the i and j dimensions, mk is the number of points in the k dimension per pipeline stage and mmi is the number of angles per pipeline stage.

The inputs to Sweep3D include the total problem size (I, J, K), the size of the processor grid, the k-blocking factor (*mk*), and the angle-blocking factor (*mmi*). Two aggregate problem sizes of particular interest for the DOE ASCI program are one billion cells (i.e., I=1000, J=1000, K=1000) and 20 million cells (i.e., I=255, J=255). Key configuration questions include how many processors

should be used for these problem sizes, and what are the optimal values of *mk* and *mmi*.

## 3 POEMS METHODOLOGY

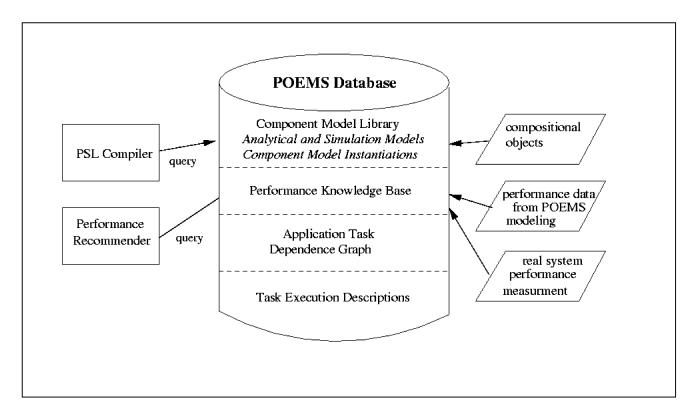

Using POEMS, a performance analyst specifies the workload, operating system, and hardware architecture for a system under study, henceforth referred to as the target system. In response, as depicted in Fig. 2, the completed POEMS system will generate and run an end-to-end model of the specified software/hardware system. The target system is defined via an integrated graphical/textual specification language (the POEMS Specification Language or PSL) for a generalized dependence graph model of parallel computation. Section 3.1 describes the process of component model composition and evaluation tool interfacing. The generalized dependence graph model of parallel computation is described in Section 3.2. The PSL is briefly introduced and illustrated in Section 3.3.

The nodes of the dependence graph are models of system components, i.e., instances of component models in the application, OS/runtime, and hardware domains. In specifying the target system, the analyst defines the properties of each system component in the context of and in terms of the attribute set of its semantic domain. For example, for a hardware component, the analyst defines the design parameters, the modeling paradigm, and the level of detail of the component model. As discussed in Section 3.3, the component models are implemented as compositional objects, i.e., "standard objects" encapsulated with associative interfaces [11], [12], [16] specified in the PSL. These component models, together with application task graphs, and performance results, are stored in the POEMS database, described in Section 3.6. POEMS also includes a knowledgebased system, called Performance Recommender, to assist analysts in choosing component models. The Performance Recommender is sketched in Section 3.5. As described in Section 3.2, the application domain represents a parallel computation by a combination of static and dynamic task graphs, which are specialized forms of generalized

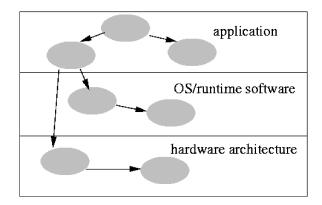

Fig. 3. Multidomain dependence graph.

dependence graphs. Generalized dependence graphs can be used in the operating system domain to model process and memory management, interprocess communication, and parallel file systems. In the hardware domain, the nodes of a graph are associated with models of hardware components. Fig. 3 is a schematic of a generalized dependence graph model spanning multiple domains.

When specifying the target system, the analyst selects the components that are most appropriate for the goals of her/ his performance study. As discussed in Section 3.4, model composition is facilitated by task execution descriptions (TEDs), which characterize the execution of components of the task graph on particular hardware domain components, e.g., processors, memory hierarchies, and interconnection networks. It also relies on the models being implemented as compositional objects and on data mediation methods. The performance knowledge base of the POEMS database may provide guidance to the analyst in the selection of components. The compiler for the POEMS specification language will access the specified component models from the POEMS database, when appropriate component models are present and will incorporate them into the system model.

## 3.1 Component Model Composition and Evaluation Tool Integration

As noted earlier, POEMS composes its system models from component models of different types ranging from simple analytical models such as LogGP to detailed simulation models of instructions executing on modern processor/cache architectures. Each component model can be characterized as a "document" that carries an *external interface* defining its properties and behavior. Successful composition requires that this interface specifies the properties and behavior of the component models with which the given component model can be composed successfully.

Evaluation of the multiparadigm system models requires interfacing and integration of evaluation tools for each component model type. Each evaluation tool also can be characterized as a processor that "understands" and acts upon information supplied for the component model it is evaluating. Each tool evaluates the behavior of the component model types it "understands." The input to each tool must be in the types set it "understands." Interfacing and integration of tools requires that the output

of one tool be the input of another tool. Successful interfacing and integration of tools, each of which "understands" different type sets, requires that the output of a source tool (which will be in the type set it "understands") must be mapped to the type set "understood" by its target tool. The information necessary to support these mappings must be defined in the external interfaces from which the tools are invoked.

Manual composition of component models to create system models is now accomplished on an ad hoc basis by humans reading documentation and applying their experience and knowledge to select component models with properties and behaviors such that the components can be integrated. Manual interfacing of evaluation tools that utilize different representations of components is now accomplished by manual specification of mappings from outputs to inputs and hand coding of these mappings. Design and implementation of these mappings is often a very laborious and error-prone process, sufficiently so that these tasks are seldom attempted. A major reason for the difficulty of these tasks is that there is no consistent specification language in which to describe the properties and behaviors of either components or tools. The human system model composer and evaluation tool integrator must resolve the ambiguities and inconsistencies of mappings among languages with different semantics on an ad hoc, case-by-case basis. Automation of component model composition and tool interfacing and integration will require that the interfaces of component models and evaluation tools be specified in a common representation with semantics sufficiently precise to support automated translations.

The POEMS Specification Language (PSL) [16] is the representation used in POEMS to specify the information necessary to support composition of component models and interfacing and integration of evaluation tools. PSL is an interface specification language. Components and tools are treated as objects and each is encapsulated with a PSL-specified interface. PSL-specified interfaces, called associative interfaces, are a common language for expressing both component model composition and mappings across evaluation tool interfaces. An object encapsulated with an associative interface is called a compositional object. Associative interfaces and compositional objects are defined and described in Section 3.3.2. An example of PSL specifications is given in Section 3.3.4.

A compiler for PSL-specified interfaces that has access to a library of component models and evaluation tools can automatically compose a set of component models selected by a performance engineer into a system model and generate the mappings among the outputs and inputs of the evaluation tools. The compiler for PSL programs will generate an instance of the generalized hierarchical dependence graph defined in Section 3.2. A feasibility demonstration prototype of a PSL compiler has been developed [16] and a more capable version of the PSL compiler is under development.

PSL-specified associative interfaces also facilitate manual composition and integration processes since they provide a systematic framework for formulation of component model

and evaluation tool interfaces. The applications of the POEMS methodology to performance studies of Sweep3D given in Sections 5 and 6 are manually executed examples of the model composition and evaluation tool interfacing methods and concepts defined and described in this section and in Sections 4 and 5.

### 3.2 General Model of Parallel Computation

Given a PSL program, the PSL compiler generates an instance of a generalized hierarchical dependence graph. This model of parallel computation and its use in POEMS system modeling are described in this section after introducing some basic definitions and terminology.

# 3.2.1 Definitions and Terminology

Generalized Hierarchical Dependence Graph. A general graphical model of computation in which each node represents a component of the computation and each edge represents a flow of information from node to node. The graph is hierarchical in that each node can itself be an interface to another generalized dependence graph. Each edge in such a graph may represent either a dataflow relationship or a precedence relationship. For each node, an extended firing rule (that may include local and global state variables in addition to input data values) specifies when each node may begin execution. For a precedence edge, the node at the head of the edge may not begin execution until the node at the tail has completed.

**Dynamic Task Graph**. An acyclic, hierarchical dependence graph in which each node represents a sequential task, precedence edges represent control flow or synchronization, and dataflow edges (called communication edges) represent explicit data transfers between processes.

Static Task Graph. A static (symbolic) representation of the possible dynamic task graphs of a program, in which each node represents a set of parallel tasks and each edge represents a set of edge instances. Unlike the dynamic task graph, this graph includes loop and branch nodes to capture logical control flow (and hence the graph may contain cycles).

### 3.2.2 Dependence Graph Model of Parallel Systems

The POEMS representation of a parallel system is a hierarchical dependence graph in which the nodes are instances of compositional objects and the edges represent flows of information from node to node. As shown in Fig. 3, the nodes may be defined in different domains and a node in one domain may invoke nodes in both its own and implementing domains. For example, the implementing domains for an application are the OS/runtime system and hardware domains.

The graph model is executable, where an execution represents a model solution for the specified application software and system configuration. The nodes and edges may be instantiated during execution, thus defining a dynamic instance of the graph that captures the behavior of the entire system during the execution being modeled. This dynamic graph may or may not be constructed explicitly at runtime, depending on the specified solution methods.

A node executes when the computation reaches a state in which its associated "firing rule" evaluates to true. A firing rule is a conditional expression over the state of the input edges and the local state of a node. Each edge has associated with it a data type specification, which is called a transaction. Clock-driven execution is obtained by adding to the data dependence relationships (and specifications of the firing rules for the nodes) an edge between each source sink node pair carrying the current time of each source node. Each node executes the Lamport [23] distributed clock algorithm to determine the current time.

# 3.2.3 Common Application Representation

The POEMS application representation is designed to provide workload information at various levels of abstraction for both analytical and simulation models. More specifically, the representation is designed to meet four key goals [3]. First, it should provide a common source of workload information for the various modeling techniques envisaged in POEMS. Second, the representation should be computable automatically using parallelizing compiler technology. Third, the representation should be concise and efficient enough to support modeling terascale applications on very large parallel systems. Finally, the representation should be flexible enough to support performance prediction studies that can predict the impact of changes to the application, such as changes to the parallelization strategy, communication, and scheduling. The design of the representation is described in more detail in [3] and is summarized briefly here.

The application representation in POEMS is based on a combination of *static* and *dynamic* task graphs. As defined earlier, the static task graph (STG) is a compact, symbolic graph representation of the parallel structure of the program. The nodes represent computational tasks, CPU components of communication, or control flow. The graph also includes extensive symbolic information in order to capture symbolically the structure of the parallel computation as a function of parameters such as the number of processors and relevant program input variables. For example, each static task node contains a symbolic integer set that describes the set of task instances that are executed at runtime (e.g., the following set can be used to denote a task node with *P* instances:

$$\{[i]: 0 \le i \le P-1\}$$

).

Each edge between parallel task nodes contains a symbolic integer mapping that describes the edge instances connecting task instances (e.g., the mapping

$$\{[i \rightarrow j] : 1 \le j \le P - 1 \land j = i + 1\}$$

denotes P-1 edge instances connecting instance i of the node at the tail to instance i+1 of the node at the head). Finally, control-flow nodes contain symbolic information about loop bounds or branching conditions. Together, this information enables the STG to capture the parallel structure of the program while remaining independent of program input values. In addition, each computational task also has an associated scaling function describing how the computational work for the task scales as a function of relevant

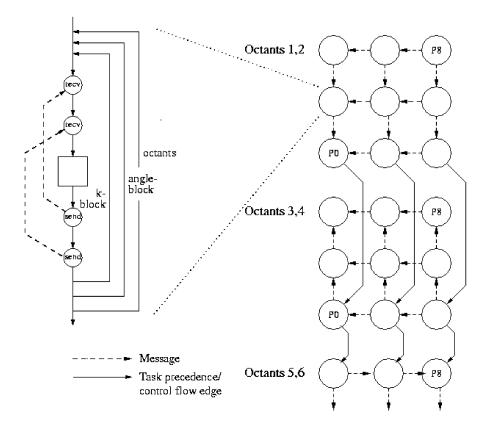

Fig. 4. Static task graph for Sweep3D and the dynamic communication structure on a 3x3 processor grid.

program variables. For example, this information can be used to support simple extrapolation of performance metrics as a function of input size.

The dynamic task graph, which is instantiated from the static task graph, is a directed acyclic graph that captures the precise parallel structure of an execution of the application for a given input [1]. The dynamic task graph is important for supporting detailed and precise modeling of parallel program behavior. For many modeling techniques, however, the dynamic task graph need not be instantiated explicitly but the same information can be obtained by traversing the static task graph at model runtime. This is a key capability already available in the graph-based runtime system on which the POEMS implementation will be based.

#### 3.2.4 Sweep3D Task Graph

The task graph concepts are illustrated by the static task graph for the sweep phase of Sweep3D, shown on the left-hand side of Fig. 4. This task graph was generated manually and is a simplified version of the graph that would be generated using the task graph synthesis techniques in the dHPF compiler, described in Section 4.1. (The actual static task graph differs mainly in that there are additional small computational tasks between the communication tasks and the k-block actually consists of several computation and a few control-flow nodes.)

The right hand side of Fig. 4 shows the dynamic communication pattern of the sweep phase that would be realized assuming a  $3\times3$  processor grid. This shows four of the eight octants in each time step of Sweep3D and the

computation and communication tasks performed by each processor for each octant can be seen on the left. An illustration of the dynamic task graph and a more detailed description can be found in [3].

### 3.3 Modeling Using Compositional Objects

The interfaces of compositional objects carry sufficient information to enable compiler-based integration of multidomain, multiparadigm, multiresolution component models into a system model. Section 3.3.1 defines compositional objects. Section 3.3.2 defines the interfaces of compositional objects. Section 3.3.3 describes how compositional objects are incorporated into the dependence graph model of computation and Section 3.3.4 illustrates compositional modeling with an example from Sweep3D.

### 3.3.1 Compositional Objects

The POEMS Specification Language and programming environment enable creation of performance models as instances of the general dependence graph model of parallel computation. The nodes of the graph are instances of compositional objects that represent components. Compositional objects are defined in the context of an application semantic domain, an OS/runtime semantic domain, and/or a hardware semantic domain. The properties of objects are defined in terms of the attribute set of the appropriate semantic domain.

Each component is specified by a set of attributes. A component model is an instantiation of a component. There may be many instances of a given component model each with the same set of attributes, but with different values bound to these attributes.

#### 3.3.2 Associative Interfaces

An associative interface is an extension of the associative model of communication [11], [12] used to specify complex, dynamic interactions among object instances. An associative interface specifies the functions it implements, domain-specific properties of the functions it implements, the functions it requires, and the domain-specific properties of the functions it requires.

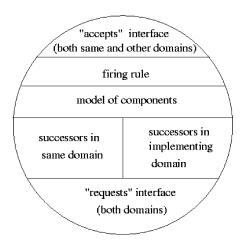

An associative interface has two elements: an "accepts" interface for the services that the component model implements and a "requests" interface that specifies the services the component model requires. Interfaces are specified in terms of the attributes that define the behavior and the states of standard objects [13], [31], [33]. An object that has associative interfaces is said to be a compositional object and an object that interacts through associative interfaces is said to have associative interactions.

An "accepts" interface consists of a profile, a transaction, and a protocol. A profile is a set of name/value pairs over the attributes of a domain. An object may change its profile during execution. A transaction is a type definition for a parameterized unit of work to be executed. A protocol specifies a mode of interaction such as call-return or data flow (transfer of control) and/or a sequence of elementary interactions. A "requests" interface consists of a selector expression, a transaction, and a protocol. A selector expression is a conditional expression over the attributes of a domain. The selector references attributes from the profiles of target objects. When evaluated using the attributes of a profile, a selector is said to match the profile whenever it evaluates to true. A match that causes the selector to evaluate to true selects an object as the target of an interaction. The parameters of the transaction in the match should either conform or the POEMS component model library must include a routine to translate the parameters of the transaction in the requests interface instance to the parameters of the transaction in the matched accepts interface and vice versa. A compositional object may have multiple accepts and requests in its associative interface. Multiple accepts arise when a component model implements more than one behavior. A component model may have a request instance for a service from an implementing domain and a request instance for continuation of execution in its own domain.

# 3.3.3 Mapping of Compositional Objects to Dependence Graphs

POEMS compositional objects are defined by encapsulating "standard objects" [13], [31], [33] with associative interfaces and data-flow execution semantics. Fig. 5 shows the structure of a POEMS compositional object. The edges of the generalized dependence graph defined in Section 3.2 are derived by matching request interfaces with accepts interfaces. The selector must evaluate to true and the transaction must be conformable for an edge to be created. Transactions are conformable if the parameters of the transaction can be mapped to one another. The requirement for the mapping of parameters arises when component models in a system model either are defined at different levels of resolution or use different paradigms for evaluation. The POEMS compiler uses a library of domain-aware type coercions to implement mappings when required. The

Fig. 5. A node of a dependence graph as a compositional object.

firing rule for a component model is derived by requiring that all of the parameters in the transaction in the interface be present on its input edges. Requests and accepts interfaces can be matched when a system model is compiled or at runtime.

The matching of *selectors* in *requests* to *profiles* in *accepts* thus composes a dynamic data flow graph and controls the traversal of the graph that models the execution behavior of the system.

Note that a component model at the application or OS/runtime level may have dependence arcs to and from its own and implementing levels.

# 3.3.4 Illustration of Compositional Modeling for Sweep3D

As an example of compositional modeling, the specification of two of the component models that are composed to create an end-to-end model of Sweep3D are illustrated in Figs. 6 and 7. The target hardware system is an IBM SP/2, except that the memory hierarchy of the 604e processors is modeled as being different from that of the SP/2. (This modification is particularly relevant because measurements have shown that Sweep3D utilizes only about 20–25 percent of the available cycles on a single processor in high-performance systems [34].)

This example assumes that the Sweep3D application being modeled is represented by the task graph of Fig. 4 with "recv" nodes, "k-block" nodes, and "send" nodes. It also is assumed that the analyst has specified that execution of the compute operations be modeled using detailed instruction-level simulation, including a detailed simulation of memory access, and that the execution of communication and synchronization operations be modeled using MPI simulation.

This example involves the application domain, the OS/runtime domain, and the hardware domain. (In the interest of brevity and clarity, the syntax is a simplified form of the actual syntax of PSL.) In the example that follows, the PSL interfaces for a "k-block" node of the dependence graph and the first "send" node after a "k-block" node are specified. In the specification for the "k-block" component model the profile element "domain = application[Sweep3D]" specifies that this component is

```

Accepts:

Profile = {domain = application[Sweep3D], node type = k-block, evaluation mode = simulation[SimpleScalar] };

Transaction = { k-block(k-block-code) };

Protocol = dataflow;

```

### Body:

/\* Invocation of the SimpleScalar simulator to execute the instructions that comprise the computation of this k-block. The instructions for the k-block (and the other nodes) have been previously loaded into SimpleScalar's data space as the memory contents of the processor/memory pair being simulated. Initialization of SimpleScalar is done using an initialization component in the POEMS database. The parameter of the transaction is a pointer to the base address in memory for the instructions. \*/

#### Requests:

```

Selector = {domain = hardware [processor/memory],

node type = N/A, evaluation mode = simulation

[SimpleScalar]};

Transaction = {avacute code block(k block code);

```

Transaction = {execute\_code\_block(k-block-code};

Protocol = call-return;}

Fig. 6. Specification of compositional objects: An example using the representation of a "k-block" node of the Sweep3D task graph.

from the Sweep3D application. "Evaluation mode = simulation[SimpleScalar]" specifies that the evaluation of this component will be done by the SimpleScalar simulator. In this case, the "k-block" is a sequence of instructions to be executed by the SimpleScalar simulator. The PSL compiler composes these component model specifications into an instance of the generalized hierarchical dependence graph defined in Section 3.2.1.

The *accepts* interface for the compositional object representing the k-block node is straightforward. The k-block node has been generated by the task graph compiler and belongs to the application domain. The identifier "k-block" specifies a set of instructions that are to be executed. The *requests* interface for the k-block node has two request instances, one for the implementing (hardware) domain for the k-block and a second request instance continuing the flow of control to the next send node in the application domain.

The first request in the *requests* interface selects the SimpleScalar simulator to execute the instructions of the k-block node and evaluate the execution time of the code for the k-block node. The transaction associated with the first selector invokes an execute code block entry point defined for SimpleScalar. The protocol for this selector is call-return since SimpleScalar must complete its execution and return control to the k-block node before the k-block node can transfer the computed data to the send node and send node execution can be initiated. SimpleScalar has

```

Accepts:

Profile = { domain = application[Sweep3D], node type =

send, evaluation mode = simulation[MPI-Sim] };

Transaction = {MPI-send(destination, message,

mode)};

Protocol = dataflow;

Body:

/* Invocation of the MPI-Sim simulator to simulate the

modified MPI send operation specified in the transaction.

Requests:

Selector={ domain = runtime, node type = N/A,

evaluation mode = simulation[MPI-Sim] };

Transaction ={MPI-send(destination, message, mode) };

Protocol = call-return;

Selector = { domain = Application[Sweep3D], node type

= send, evaluation mode = simulation[MPI-Sim] };

Transaction = {MPI-send(destination, message, mode)};

Protocol = dataflow;

```

Fig. 7. Specification of compositional objects: An example using the representation of a "send" node of the Sweep3D task graph.

been encapsulated in the POEMS library as a single node dependence graph in the hardware domain.

The second selector in the requests interface selects the send node immediately following the k-block instance in the task graph to continue execution of the system model. The transaction in this request invokes the MPI-Sim simulator to evaluate the execution time of the MPI-send function defined in MPI-Sim. The protocol is the "data-flow" protocol for data-flow graphs; in this case, the control follows the data along the arc that is defined by the matching of the request and the accept interfaces. Note that even though MPI-Sim is in the runtime domain we have assigned the send node to the application domain. This choice was made because the send node is constructed as a part of the application by the task graph compiler (See Section 4.1 for a description of the task graph compiler.) This is the most direct translation of the task graph into a data-flow graph. MPI-Sim is encapsulated in the POEMS component model library as a single-node graph. MPI-Sim is invoked from the send node of the application send node with call-return semantics. This encapsulation of the runtime domain MPI-Sim node in the application node allows the send node to pass control to its successor send node as soon as the MPI-Sim simulator has completed execution.

For this example, the representation of the first "send" node following the k-block node in the task graph for Sweep3D is given in Fig. 7. As shown, the profile in the *accepts* interface of the send component model specifies that it derives from the Sweep3D application, is a "send" node, and is to be evaluated using MPI-Sim. The transaction specifies an entry point of MPI-Sim.

The selector in the first request instance matches the MPI-Sim simulator and the transaction specifies the entry point for the MPI-send operation. The protocol is call-return because MPI-Sim must complete execution and return control to the application before this send node can transfer

control to the next send node. The selector of the second request instance identifies the next node to which control should be transferred.

The accepts and requests interfaces of each compositional object or task graph node direct the search of the POEMS database by the POEMS compiler to identify appropriate component models to be used to instantiate components and link them to generate this segment of the system model. (The current version of the POEMS Specification Language compiler [16] does not yet interface to the POEMS database. It accesses component models from a Unix file system.) This database search provides a link to the code that implements an instance of the specified component model. In this case, the code that implements the k-node component model is the SimpleScalar simulator and the code that implements the send node is MPI-Sim. (See Section 4 for a description of SimpleScalar and MPI-Sim.) The accepts and requests interfaces, the link to the code implementing the instance of a component model, and other parameters associated with the component model will be stored in a Task Execution Description (TED) (see Section 3.4) in the POEMS database.

To execute the specified system model, SimpleScalar and MPI-Sim execute as processes on a host processor. SimpleScalar runs as the executing program for which MPI-Sim is modeling communication. SimpleScalar takes as input the executable file of the k-block node, which is stored in simulated memory. At the conclusion of executing the "k-block" node, the POEMS environment invokes the MPI-send module of MPI-Sim. A special built-in interface procedure that links SimpleScalar and MPI-Sim copies the data to be transmitted from the simulated memory of SimpleScalar into the real memory of the host, which allows MPI-Sim to model the communication operation.

### 3.4 Task Execution Descriptions (TEDs)

Considerable information is needed to characterize the behavior and properties of each component and different instances of each component model will have different attribute values. For example, there may be two instances of a component, one that is analytically evaluated and one that is evaluated by simulation. Analytical modeling may require parameter values that specify task execution time, while simulation of a single task requires either an executable representation of the task or its memory address trace. As a result, these two instances of the same component require different modes of integration into a system model. The information necessary to accomplish these integration functions must be associated with each component instance. POEMS will use a Task Execution Description (TED) to describe the modeled execution of a task; a TED is associated with each node of a task graph.

In addition, a TED contains the attributes required to define the method used to model single-task execution. The methods that are being evaluated for simulating individual tasks are instruction-driven, execution-driven, and trace-driven simulation. For example, a TED would define the input parameters for SimpleScalar that would enable the creation a particular instantiation of the SimpleScalar component model.

### 3.5 Performance Recommender

The POEMS Performance Recommender system facilitates the selection of computational parameters for widely used algorithms to achieve specified performance goals. For example, in the Sweep3D context, the system is used to obtain the parameters of the algorithm (e.g., grid size, spacing, scattering order, angles, k-blocking factor, convergence test), system (e.g., I/O switches), and machine (e.g., number and configuration of processors). Capturing the results of system measurement as well as modeling studies (discussed in Section 5), this facility can provide insight into how interrelationships among variables and problem features affect application performance. It functions at several levels ranging from the capture of analytical and simulation model results to those of the measured application.

POEMS is using a kernel (IFESTOS), developed at Purdue [29], that supports the rapid prototyping of recommender systems. IFESTOS abstracts the architecture of a recommender system as a layered system with clearly defined subsystems for problem formulation, knowledge acquisition, performance modeling, and knowledge discovery. The designer of the recommender system first defines a database of application classes (problems) and computation class instances (methods). The data acquisition subsystem generates performance data by invoking the appropriate application (e.g., Sweep3D). The performance data management subsystem provides facilities for the selective editing, viewing, and manipulation of the generated information. Performance analysis is performed by traditional attribute-value statistical techniques, and "mining" this information produces useful rules that can be used to drive the actual recommender system. This approach has been demonstrated successfully for problem domains in numerical quadrature and elliptic partial differential equations [29]. Currently it is being applied to the Sweep3D application.

### 3.6 POEMS Database

The volume and complexity of the data environment for POEMS make the POEMS database a critical component of the project. In fact, POEMS as a tool could not be built without a database as a searchable repository for a wide spectrum of model and performance data. The POEMS database will be the repository for:

- a. The component model definitions as compositional objects and component model definitions as instances of the component models.

- b. Static task graphs for the applications, generated by the extended dHPF compiler.

- c. The Task Execution Descriptions, which characterize each component model, as discussed in Section 3.3.4.

- d. The knowledge base, which will guide analysts and designers in the development of total systems.

- Measurements of performance in several formats included measurements and predictions of execution time.

The POEMS Specification Language compiler will be interfaced to the database as will the Performance Recommender. Fig. 8 is a schematic of the role of the database in POEMS.

Fig. 8. Overview of the POEMS Database.

# 4 THE INITIAL POEMS PERFORMANCE ANALYSIS TOOLS

Currently, several performance analysis tools are being integrated in POEMS. These include the following tools, which are described briefly in this section: an automatic task graph generator [3], the LogGP [5] and LoPC [18] analytic models, the MPI-Sim simulator [28], and the SimpleScalar instruction-level, processor/memory architecture simulator [14]. Each tool contains capabilities for modeling the application, OS/runtime, and hardware domains. Together, these tools provide the capability to analyze, with a fairly high degree of confidence, the performance of current and future applications and architectures, for very large and complex system configurations. As a prerequisite to developing multiparadigm models, each of these tools has been used to develop a single-paradigm, multidomain model of Sweep3D. This has allowed us to understand the unique role that each paradigm can play in total system performance analysis.

### 4.1 Automatic Task Graph Generator

A comprehensive performance modeling environment like POEMS will be used by system designers in practice only if model construction and solution can be largely automated. For an existing application, one critical step towards this goal is to automatically construct the application representation described in Section 3.2. Data-parallel compiler technology from the dHPF compiler project [2] has been extended to compute the task-graph-based application representation automatically for High Performance Fortran (HPF) programs. In normal use, the dHPF compiler

compiles a given HPF program into an explicitly parallel program in SPMD (Single Program Multiple Data) form, for message-passing (MPI), shared-memory (e.g., pthreads), or software distributed shared-memory (TreadMarks [6]) systems. The synthesized task graphs represent this explicitly parallel program. In the future, the task graph synthesis will be extended to handle existing message-passing programs as well.

There are three key innovations in the compiler support for task graph construction:

- The use of symbolic integer sets and mappings. These are critical for capturing the set of possible dynamic task graphs as a concise, static task graph. Although this is a design feature of the representation itself, the feature depends directly on the integer set framework technology that is a foundation of the dHPF compiler [2]. The construction of these sets and mappings for an STG is described in more detail in [3].

- Techniques for condensing the static task graph. The construction of static task graphs in dHPF is a two-phase process [3]. First, an initial static task graph with fine-grain tasks is constructed directly from the dHPF compiler's internal program representation and analysis information. Second, a pass over the STG condenses fine-grain computational tasks (e.g., single statements) into coarse-grain tasks (e.g., entire loop iterations or even entire loop nests). The degree of granularity clearly depends on the goals of the modeling study, and can be controlled as discussed below.

Integer set code generation techniques for instantiating a

dynamic task graph for a given input. Although this

step is conceptually performed outside the compiler,

it can be done in a novel, highly efficient, manner for

many programs using dHPF's capability of generating code to enumerate the elements of an integer set

or mapping. This also is explained further below.

The goal of condensing the task graph is to obtain a representation that is accurate, yet of a manageable size. For example, it may be appropriate to assume that all operations of a process between two communication points constitute a single task, permitting a coarse-grain modeling approach. In this case, in order to preserve precision, the scaling function of the condensed task must be computed as the symbolic sum of the scaling functions of the component tasks, each multiplied by the symbolic number of iterations of the surrounding loops or by the branching probabilities for surrounding control-flow, as appropriate. Note, however, that condensing conditional branches can introduce fairly coarse approximations in the modeling of task execution times. The compiler, therefore, takes a conservative approach and does not collapse branches by default. Instead, it is desirable to allow the modeler to intervene and specify that portions of the task graph can be collapsed even further (e.g., by inserting a special directive before control flow that can be collapsed). Even in the default case, however, the compiler can increase the granularity of tasks further in some cases by moving loop-invariant branches out of enclosing loops, a standard compiler transformation. For example, this would be possible for a key branch within the k-block of Sweep3D.

Constructing the DTG for a given program input requires symbolic interpretation of the parallel structure and part of the control flow of the program. This interpretation must enumerate the loop iterations, resolve all dynamic instances of each branch, and instantiate the actual tasks, edges, and communication events. For many regular, nonadaptive codes, the control flow (loop iterations and branches) can be determined uniquely by the program input, so that the DTG can be instantiated statically. (Again, in some cases, a few data-dependent branches may have to be ignored for approximate modeling, under the control of the modeler as proposed above.) To instantiate parallel tasks or edges, the elements of the corresponding integer set or mapping must be enumerated. The key to doing this is that, for a given symbolic integer set, the dHPF compiler can synthesize code to enumerate the elements of that set [2]. (Any mapping can be converted into an equivalent set for code generation.) We exploit this capability and generate a separate procedure for each set, parameterized by the symbolic program variables that appear in the set; typically these are process identifiers, program input variables, and loop index variables. Then this generated code is compiled separately and linked with the program that performs the instantiation of the DTG. When instantiating dynamic task instances for a given static task, the code for that task's symbolic set is invoked and is provided with the current values of the symbolic parameters at this point in the interpretation process. This directly returns the required index values for the task instances. Edge instances of a static

edge are instantiated in exactly the same manner, from the code for the integer set mapping of that static edge.

In some irregular and adaptive programs, the control flow may depend on intermediate computational results of the program and the DTG would have to be instantiated dynamically using an actual or simulated program execution. The DTG for a given input can be either synthesized and stored offline for further modeling with any model, or instantiated on the fly during model execution for modeling techniques such as execution-driven or instruction-driven simulation. Both these approaches will be key for multiparadigm modeling of advanced adaptive codes.

The automatic construction of the static task graph has been exploited directly in integrating a task-graph-based model with MPI-Sim for improving the scalability of simulation, as described in Section 6.1. The automatic construction of the dynamic task graph makes it possible to do automatic analytical modeling of program performance, using deterministic task graph analysis [1].

# 4.2 LogGP/LoPC

The task graph for a given application elucidates the principal structure of the code, including the interprocessor communication events, from which it is relatively easy to derive the LogGP or LoPC model equations. The approach is illustrated by deriving the LogGP model of the Sweep3D application that uses blocking MPI send and receive primitives for communication. The task graph for the sweep phase of this application is given in Fig. 4.

The LogGP model of the Sweep3D application is given in Fig. 9. The hardware domain is modeled by three simple parameters: L, G, and  $W_g$ , which are defined below. The first six equations, (1a) through (3b), model the runtime system components used by the Sweep3D application. That is, these equations model the MPI communication primitives as they are implemented on the SP/2 that was used to validate the model. Equations (4) through (8) model the execution time of the application as derived from the dynamic task graph.

Equations (1a) through (3b) reflect a fairly precise, yet simple, model of how the MPI-send and MPI-receive primitives are implemented on the SP/2. Information about how the primitives are implemented was obtained from the author of the MPI software. For messages smaller than four kilobytes, the cost of a send or receive operation is simply the LogGP processing overhead (o) parameter. The total communication cost for these messages (3a) is the sum of the send processing overhead, the message transmission time (modeled as the network latency (L), plus the message size times the gap per byte (G) parameter), and the receive processing overhead.<sup>1</sup> A subscript on the processing overhead parameter denotes the value of this parameter for messages smaller  $(o_s)$  or larger  $(o_l)$  than one kilobyte. When the subscript is omitted, the appropriate value is assumed. For messages larger than four kilobytes (3b), an additional handshake is required. The sending processor sends a short message to the receiving processor, which is acknowledged

<sup>1.</sup> The communication structure of Sweep3D is such that we can ignore the LogGP gap (g) parameter, since the time between consecutive message transmissions is greater than the minimum allowed value of intermessage transmission time.

$$Send \; (message \; length < 4KB) = o \qquad (1a)$$

$$Send \; (message \; length \geq 4KB) = o_s + L + o_s + o_s + L + o_l \qquad (1b)$$

$$Receive \; (message \; length < 4KB) = o \qquad (2a)$$

$$Receive \; (message \; length < 4KB) = o_s + L + o_l + (message\_size \times G_l) + L + o_l \qquad (2b)$$

$$Total \; Comm \; (message \; length < 4KB) = o + (message\_size \times G) + L + o \qquad (3a)$$

$$Total \; Comm \; (message \; length \geq 4KB) = o_s + L + o_s + o_s + L + o_l + (message\_size \times G_l) + L + o_l \qquad (3b)$$

$$W_{i,j} = W_g \times mmi \times mk \times it \times jt \qquad (4)$$

$$StartP_{i,j} = max \; (StartP_{i-1,j} + W_{i-1,j} + Total\_Comm + Receive, StartP_{i,j-1} + W_{i,j-1} + Send + Total\_Comm) \; (5)$$

$$T_{5,6} = startP_{1,m} + 2[(W_{1,m} + Send_E + Receive_N + (m-1)L) \times \#k - blocks \times \#angle-groups] \qquad (6)$$

$$T_{7,8} = startP_{n-1,m} + 2[(W_{n-1,m} + Send_E + Receive_N + (m-1)L + (n-2)L) \times \#k - blocks \times \#angle-groups] + Receive_N + W_{n,m} \qquad (7)$$

$T = 2 (T_{5,6} + T_{7,8})$

Fig. 9. LogGP model of MPI communication and the Sweep3D application.

by a short message from the receiving processor when the receive system call has been executed and the buffer space is available to hold the message. After that, the message transfer takes place. In this case, the Send cost (1b) or Receive cost (2b) is the duration of the communication event on the processor where the corresponding MPI runtime system call occurs. Further details about the accuracy of these communication models and how the parameter values were measured are given in [35].

The equations that model the MPI communication primitives might need to be modified for future versions of the MPI library, or if Sweep3D is run on a different message-passing system or is modified to use nonblocking MPI primitives. The equations illustrate a general approach for capturing the impact of such system modifications.

Equations (4) through (8) model the application execution time, taking advantage of the symmetry in the Sweep3D task graph (see Fig. 4). For simplicity, the Sweep3D application model presented here assumes each processor in the  $m \times n$  Sweep3D processor grid is mapped to a different SMP node in the SP/2. In this case, network latency, L, is the same for all (nearest-neighbor) communication in Sweep3D. As explained in [35], the equations that model communication can be modified easily for the case when 2x2 regions of the processor grid are mapped to the same SMP node.

Equation (4) models the time required for a single task to compute the values for a portion of the grid of size  $mmi \times mk \times it \times jt$ . In this equation,  $W_g$  is the measured time to compute one grid point and mmi, mk, it, and jt are the Sweep3D input parameters that specify the number of angles and grid points per block per processor.

Equation (5) models the precedence constraints in the task graph for the sweeps for octants 5 and 6, assuming the processors are numbered according to their placement in the two-dimensional grid, with the processor in the upper

left being numbered (1,1). Specifically, the recursive equation computes the time that processor  $p_{i,j}$  begins its calculations for these sweeps, where i denotes the horizontal position of the processor in the grid. The first term in (5) corresponds to the case where the message from the west is the last to arrive at processor  $p_{i,j}$ . In this case, due to the blocking nature of the MPI primitives, the message from the north has already been sent but cannot be received until the message from the West is processed. The second term in (5) models the case where the message from the north is the last to arrive. Note that  $StartP_{1,1} = 0$  and that the appropriate one of the two terms in (5) is deleted for each of the other processors at the east or north edges of the processor grid.

**(8)**

The Sweep3D application makes sweeps across the processors in the same direction for each octant pair. The critical path time for the two right downward sweeps is computed in (6) of Fig. 9. This is the time until the lower-left corner processor  $p_{\rm l,m}$  has finished communicating the results from its last block of the sweep for octant 6. At this point, the sweeps for octants 7 and 8 (to the upper right) can start at processor  $p_{\rm l,m}$  and proceed toward  $p_{\rm n,1}$ . The subscripts on the Send and Receive terms in (6) are included only to indicate the direction of the communication event, to make it easier to understand why the term is included in the equation.

Since the sweeps from octants 1 and 2 (in the next iteration) will not begin until processor  $p_{n,1}$  is finished, the critical path for the sweeps for octants 7 and 8 is the time until all processors in the grid complete their calculations for the sweeps. Due to the symmetry in the Sweep3D algorithm, captured in the task graph, the time for the sweeps to the northeast is the same as the total time for the sweeps for octants 5 and 6, which is computed in (7) of the figure. Due to the symmetry between the sweeps for octants 1 through 4 and the sweeps for octants 5 through 8, the total

execution time of one iteration is computed as in (8) of Fig. 9. Equation (6) contains one term [(m-1)L], and the (7) contains two terms [(m-1)L] and (n-2)L], that account for synchronization costs, as explained in [35].

The input parameters to the LogGP model derived above are the L, o, G, P, and W<sub>g</sub> parameters. The first three parameters were derived by measuring the round-trip communication times for three different message sizes on the IBM SP system, and solving equations (3a) and (3b) with the derived measures (see [35] for details). The Wi,j parameter value was measured on a 2x2 grid of processors so that the work done by corner, edge, and interior processors could be measured. In fact, to obtain the accuracy of the results in this paper, Wi,i for each perprocessor grid size was measured to account for differences (up to 20 percent) that arise from cache miss and other effects. Since the Sweep3D program contains extra calculations ("fixups") for five of the twelve iterations, W<sub>i,j</sub> values for both of these iteration types were measured. Although this is more detailed than the creators of LogP/LogGP may have intended, the increased accuracy is substantial and needed for the large-scale performance projections in Section 5. In the future, other POEMS tools will be used to obtain these input parameters, as explained in Section 6.3.

The LogGP model of the SP/2 MPI communication primitives is shown to be highly accurate in [35]. Selected validations and performance projections of the LogGP model of Sweep3D are presented in Section 5.

### 4.3 MPI-Sim: Direct Execution-Driven System Simulation

POEMS includes a modular, direct execution-driven, parallel program simulator called MPI-Sim that has been developed at UCLA [10], [28]. MPI-Sim can evaluate the performance of existing MPI programs as a function of various hardware and system software characteristics that include the number of processors, interconnection network characteristics, and message-passing library implementations. The simulator also can be used to evaluate the performance of parallel file systems and I/O systems [8]. Supported capabilities include a number of different disk caching algorithms, collective I/O techniques, disk cache replacement algorithms, and I/O device models. The parallel discrete-event simulator uses a set of conservative synchronization protocols together with a number of optimizations to reduce the time to execute simulation models.

MPI-Sim models the application and the underlying system. An application is represented by its local code blocks and their communication requirements. The local code block model is evaluated by direct execution. MPI programs execute as a collection of single threaded processes and, in general, the host machine has fewer processors than the target machine. (For sequential simulation, the host machine has only one processor). This requires that the simulator supports multithreaded execution of MPI programs. MPI-LITE, a portable library for multithreaded execution of MPI programs, has been developed for this purpose.

The MPI communication layer, which is part of the runtime domain, is simulated by MPI-Sim in detail; buffer

allocation and internal MPI synchronization messages are taken into account. The simulator does not simulate every MPI call, rather all collective communication functions are first translated by the simulator in terms of point-to-point communication functions and all point-to-point communication functions are implemented using a set of core nonblocking MPI functions. Note that the translation of collective communication functions in the simulator is identical to how they are implemented on the target architecture. A preprocessor replaces all MPI calls by equivalent calls to corresponding routines in the simulator. The physical communications between processors, which are part of the hardware domain are modeled by simple end-to-end latencies, similar to the communication latency parameter in the LogP model.

For many applications, these runtime domain and hardware domain communication models are highly accurate [10], [28]. MPI-Sim has been validated against the NAS MPI benchmarks and has demonstrated excellent performance improvement with parallel execution against these benchmarks [28]. As shown in Section 5, it also is highly accurate for the Sweep3D application and the simulation results (which reflect fairly detailed modeling of the runtime domain) greatly increase confidence in the scalability projections of the more abstract LogGP model.

### 4.4 Instruction-Level Simulation

As stated above, the system model provided by MPI-Sim is based on direct execution of computational code and simulation of MPI communication. As a result, the processor/memory architecture of the target system to be evaluated must be identical to that of the host system.

To provide performance evaluation of applications on alternative (future) processor and memory subsystem designs, the POEMS component model library includes processor, memory, and transport component models that are evaluated using instruction-level, discrete-event simulation. These models are in the process of being composed with MPI-Sim to predict the performance of programs for proposed next-generation multiprocessor systems. The results of the more abstract task graph, LogGP/LoPC, and MPI-Sim analyses can be used to identify the most important regions of the design space to be evaluated with these, more detailed, hardware component models. The detailed hardware models can be used to validate the more abstract models, and can provide parameter values for future processor/memory architectures needed in the more abstract models.

In order to provide this kind of modeling capability, a simulator that models instruction-level parallelism is essential. The "sim-outorder" component of the SimpleScalar tool set [14] meets this requirement for simulating complex modern processor/memory architectures. As a result, it is being integrated in the POEMS environment. sim-outorder can be used to model state-of-the-art superscalar processors, which support out-of-order instruction issue and execution. The processor attributes of these hardware processor/memory subsystem component models include the processor fetch, issue, and decode rates, number and types of functional units, and defining characteristics of the branch predictor. Currently, its

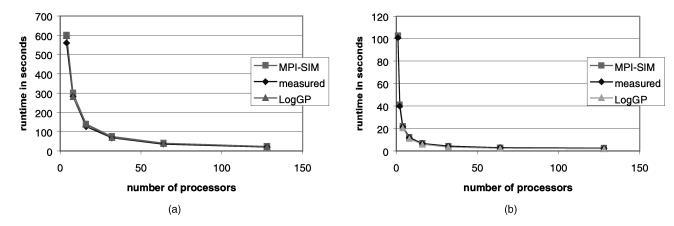

Fig. 10. Validation of LogGP and MPI-Sim. (a) Validation for problem size 150×150×150. (b) Validation for problem size 50×50×50.

integrated memory components include level-one and level-two instruction and data caches, a translation-lookaside buffer, and main memory. The simulator is fairly portable and customizable with reasonable effort.

Currently, the MPI-version of Sweep3D successfully executes on multiple instantiations of sim-outorder, each executed by a separate MPI process. This simulation produces estimates of the parameter value called  $W_{i,j}$  in the LogGP model, thus enabling the LogGP model to predict the performance of Sweep3D on alternative processor-cache architectures. This simulation capability also demonstrates a proof-of-concept for integrating the sim-outorder and MPI-Sim modeling tools. The future integration of MPI-Sim and sim-outorder will support detailed simulation of both the OS/runtime domain and the hardware domain.

# 5 APPLICATION OF POEMS TO PERFORMANCE ANALYSIS OF SWEEP3D

The goal of the POEMS performance modeling system is to enable complete end-to-end performance studies of applications executed on specific system architectures. To accomplish this, the system must be able to generate information that can be used to identify and characterize performance bottlenecks, analyze scalability, determine the optimal mapping of the application on a given architecture, and analyze the sensitivity of the application to architectural changes. This section presents a representative sample of the results obtained in modeling Sweep3D. These results are for the IBM SP system.

### 5.1 Model Validations

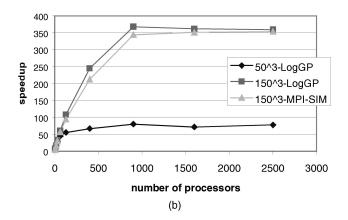

We first demonstrate the accuracy of the performance models described above. Both MPI-Sim and LogGP model Sweep3D accurately for a variety of application parameters such as the mk and mmi parameters that define the size of a pipelined block, different total problem sizes, and number of processors. Figs. 10a and 10b present the measured and predicted execution time of the program for the  $150^3$  and  $50^3$  total problem sizes respectively, as a function of the number of processors. For these results, the k-blocking factor (mk) is 10 and the angle-blocking factor (mmi) is three. Both the MPI-Sim and LogGP models show excellent agreement

with the measured values, with discrepancies of at most seven percent. The next section shows that these two problem sizes have very different scalability, yet Fig. 10 shows that the LogGP and MPI-Sim estimates are highly accurate for both problem sizes.

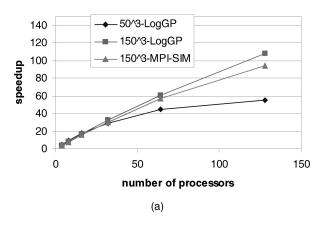

### 5.2 Scalability Analysis

It is important to application developers to determine how well an application scales as the number of processors in the system is increased. On today's systems, the user could conduct such studies by measuring the runtime of the application as the number of processors is increased to the maximum number of processors in the system, e.g., 128 (see Fig. 11a). The figure clearly shows that the small problem size  $(50^3)$  cannot efficiently exploit more than 64 processors. On the other hand, the larger problem size shows excellent speedup up to 128 processors. However, due to the system size limitation, no information about the behavior of larger problem sizes on very large numbers of processors is available to the user. Modeling tools enable users to look beyond the available multiprocessor systems. Fig. 11b shows the projections of LogGP and MPI-Sim to hardware configurations with as many as 2500 processors. Although the application for the 1503 problem size shows good performance for up to 900 processors, it would not perform well on machines with a greater number of processors.

Fig. 11 also demonstrates the excellent agreement between the analytical LogGP model and the MPI-Sim simulation model. Each model was independently validated for a variety of application configurations on as many as 128 processors and the good cross-validation between the models for up to 2,500 processors increases our confidence in both models.

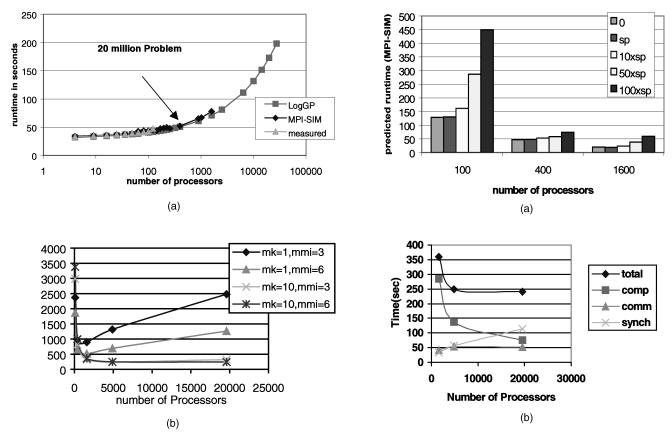

Fig. 12a demonstrates the projective capability of the simulation and analytical models. This figure shows the measured and estimated performance as a function of the number of processors, for a fixed per-processor grid size of  $14\times14\times255$ . For this per-processor grid size the total problem size on 400 processors is approximately 20 million grid points, which is one problem size of interest to the application developers. Obviously, measurement is limited to the size of the physical system (128 processors). The maximum problem size that can be measured, with the per-processor grid size of  $14\times14\times255$  is 6.4 million cells.

Fig. 11. Projected Sweep3D speedup. (a) Speedup for up to 128 processors. (b) Speedup for up to 2,500 processors.

MPI-Sim can extend the projections to 1,600 processors (80 million cells) before running out of memory because the simulator needs at least as much aggregatememory as the application it models. (In Section 6.1, we describe compiler-based techniques that eliminate the memory bottleneck for simulation of regular programs such as Sweep3D and, thus, greatly increase the system and problem sizes that can be simulated.) Finally, LogGP can take the projections to as much as 28,000 processors (i.e., for the given application configuration parameters, a 1.4 billion problem size).

One important issue addressed in the figure is the validity of the model projections for very large systems. In particular, the close agreement between measurement and the MPI-Sim and LogGP models for up to 128 processors and the close agreement between MPI-Sim and LogGP for up to 1,600 processors greatly increases our confidence in the projections of MPI-Sim and LogGP for large problem sizes of interest to the application developers.

The mutual validation between the two different models is one key way in which simulation and analytical modeling complement each other. Furthermore, the two models have complementary strengths. The key strength of MPI-Sim is that it can be used to study program performance by users with little or no modeling expertise and can be used to study the performance impact of detailed changes in the design of Sweep3D or in the implementation of the MPI communication primitives. The key strength of the LogGP model is that it can project the performance of design changes *before* the changes are implemented and for the largest problem sizes of interest.

### 5.3 Application Mapping

For applications such as Sweep3D, which allow varying the degree of pipelining, it is often important to explore not only how many resources are needed to achieve good results, but also how best to map the application onto the machine. Fig. 12b shows how LogGP explores the parameter space for the 20 million-cell Sweep3D problem on up to 20,000 processors. Here, the k- and angle-blocking factors are varied, which results in various degrees of pipelining in the algorithm. The graph shows that for a small number of processors (less than 400) the choice of blocking factors is not very important. However, as more processors are used

and the grid size per processor decreases, the degree of pipelining in the k-dimension has a significant impact, resulting in poor performance for the smallest blocking factor (mk=1). For this blocking factor, the performance of the application also is sensitive to the angle-blocking factor. However, when the k-blocking factor is properly chosen (mk=10), the impact of the mmi parameter value is negligible. The results also indicate that the optimal operating point for this total problem size is perhaps one or two thousand processors; increasing the number of processors beyond this number leads to greatly diminished returns in terms of reducing application execution time. This projected optimal operating point is a key design question that was unanswered prior to the POEMS analysis.

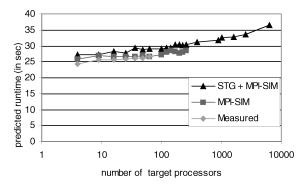

# 5.4 Communication Requirements Analysis

Another issue of interest is the application's performance on a system with upgraded communication capability. A related issue is the application's performance on high-performance tightly-coupled multiprocessor systems versus its performance on a network of loosely-coupled work-stations. Both simulation and analytical models can be used to study these issues by modifying their communication components to reflect changes in the communication latency of the system.