#### POLYCHRONY\* FOR SYSTEM DESIGN

### PAUL LE GUERNIC JEAN-PIERRE TALPIN JEAN-CHRISTOPHE LE LANN<sup>†</sup>

Inria project Espresso<sup>‡</sup> Irisa, Campus de Beaulieu, 35042 Rennes, France

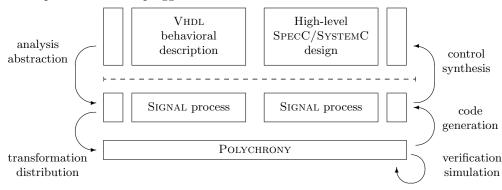

Rising complexities and performances of integrated circuits and systems, shortening time-to-market demands for electronic equipments, growing installed bases of intellectual property (IP), requirements for adapting existing IP blocks with new services, all stress high-level design as a prominent research topics and call for the development of appropriate methodological solutions. In this aim, system design based on the so-called "synchronous hypothesis" consists of abstracting the non-functional implementation details of a system and lets one benefit from a focused reasoning on the logics behind the instants at which the system functionalities should be secured. With this point of view, synchronous design models and languages provide intuitive (ontological) models for integrated circuits. This affinity explains the ease of generating synchronous circuits and verify their functionalities using compilers and related tools that implement this approach. In the relational mathematical model behind the design language SIGNAL, this affinity goes beyond the domain of purely synchronous circuits, and embraces the context of complex architectures consisting of synchronous circuits and desynchronization protocols: globally asynchronous and locally synchronous architectures (GALS). The unique features of the relational model behind Signal are to provide the notion of polychrony: the capability to describe circuits and systems with several clocks; and to support refinement: the ability to assist and support system design from the early stages of requirement specification, to the later stages of synthesis and deployment. The SIGNAL model provides a design methodology that forms a continuum from synchrony to asynchrony, from specification to implementation, from abstraction to concretization, from interfaces to implementations. Signal gives the opportunity to seamlessly model circuits and devices at multiple levels of abstractions, by implementing mechanisms found in many hardware simulators, while reasoning within a simple and formally defined mathematical model. In the same manner, the flexibility inherent to the abstract notion of signal handled in the synchronous-desynchronized design model of Signal invites and favors the design of correct by construction systems by means of well-defined transformations of system specifications (morphisms) that preserve the intended semantics and stated properties of the architecture under design. The aim of the present article is to review and summarize these formal, correct-by-construction, design transformations. Most of them are implemented in the POLYCHRONY tool-set, allowing for mixed bottom-up and top-down design of embedded hardware-software system using the SIGNAL design language.

<sup>\*</sup>From the Greek "poly chronos" to mean multiple clocks  $^{\dagger}$  Present affiliation: Thomson Multimedia R&D France

$<sup>^{\</sup>ddagger}\mathrm{URL}$  http://www.irisa.fr/espresso

#### 1 Introduction

High-level design and modeling of hardware and embedded hardware/software systems have gained prominence in the face of rising technological complexity, increasing performance requirements and shortening time to market demands for electronic equipments. Today, the installed base of intellectual property (IP) further stresses the requirements for adapting existing IPs with new services within complex integrated architectures, calling for appropriate mathematical models and methodological approaches to integrate systems.

Over the past decade, numerous programming models, languages, tools and frameworks have been proposed to design, simulate and validate heterogeneous systems within abstract and rigorously defined mathematical models. Formal design frameworks provide well-defined mathematical models that yield a rigorous methodological support for the trusted design, automatic validation, and systematic test-case generation of systems.

However, they are usually not amenable to direct engineering use and not seem to satisfy the present industrial demand. As a matter of fact, the attention of the EDA industry tends to shift to modeling frameworks based on general-purpose programming language variants, in response to a growing industry demand for higher abstraction-levels in the system design process and an attempt to fill the so-called industrial productivity qap.

Whereas abstract frameworks are ways to unambiguously model the essence of hardware software systems, to help understand the design, implement formal correctness proofs and predict performances and other metrics; general-purpose languages facilitate programming, encourage reuse and gain from the popularity of C-like and Java-based languages.

At present, a possibility of widening existing divergences between formal methods and industrial practices is perceivable. It seems that any useful methodology cannot avoid the industrial trend of using emerging programming languages. This contrasted picture calls for an effort toward the convergence between the theory of formal methods and the industrial practice and trends in system-design.

The present article aims at this convergence by considering the formal modeling framework Polychrony (as one of many formal design frameworks proposed over the past decade). It invites to a reflection on the implementation of present industrial practices and trends in such a framework by considering the required definition of proper methodological approaches and its implementation by means of effective program analysis and transformation techniques.

#### 1.1 A polychronous design model

Despite the overwhelming advance of Electronic Design Automation (EDA), existing techniques and tools merely provide *ad-hoc* solutions to challenging issues. The pressing demand for design tools has sometimes hidden the need to lay mathematical

foundations below design languages. Many illustrating examples can be found: one of the most striking examples is the variety of very different formal semantics found in hardware description languages (HDLs), even between the most widely used ones, VHDL or Verilog. Even thought these design languages benefit from decades of programming practice, they still give rise to some diverging interpretations of their semantics.

The need for higher abstraction-levels and the rise of stronger market constraints in the EDA industry now make the need for unambiguous design models more obvious. For instance, HDL simulators now need to accelerate the execution through cycle-based and compiled code strategies to support the simulation of chips that score millions of gates.

This challenge requires models and methods to reason on the translation of concurrent processes into purely sequential ones, to implement high-level, non-trivial optimizations such as process folding. Another example is sub-micronic technology, which requires designers to reason about logic optimizations in an entirely different way (wires can now be viewed as connected by gates). Even worth mentioning is that these examples even exhibit apparent contradictions in terms of modeling requirements: the first tends to abstract away from low-level details, while the second states that logic and time are indeed dependent.

In the context of such a contrasted picture, co-design becomes the central activity, instead of just being the interface between distinct hardware and software activities. In the co-design activity, communications between processes is central, interoperability between heterogeneous models and languages is central. All the leverages in system design call for the need to clearly identify Models of Computation (MoC) and develop adequate techniques based on formal computational models and design methods.

In this aim, system design based on the so-called "synchronous hypothesis" has focused the attention of many academic and industrial actors of the EDA community. The synchronous paradigm consists of abstracting the non-functional implementation details of a system and lets one benefit from a focused reasoning on the logics behind the instants at which the system functionalities should be secured. With this point of view, synchronous design models and languages provide intuitive (ontological) models for integrated circuits. This affinity explains the ease of generating synchronous circuits and verify their functionalities using compilers and related tools that implement this approach.

In the relational mathematical model behind the design language Signal, this affinity goes beyond the domain of purely synchronous circuits and embraces the context of complex architectures consisting of synchronous circuits and desynchronization protocols: globally asynchronous and locally synchronous architectures (Gals).

This unique feature is obtained thanks to the fundamental notion of *polychrony*: the capability to describe systems in which components obey to multiple clock rates. It provides a mathematical foundation to a notion of *refinement*: the ability

to model a system from the early stages of its requirement specifications (relations, properties) to the late stages of its synthesis and deployment (functions, automata).

The notion of polychrony goes beyond the usual scope of a programming language, allowing for specifications and properties to be described. As a result, the Signal design methodology draws a continuum from synchrony to desynchronization, from specification to implementation, from abstraction to concretization, from interfaces to implementations. Signal gives the opportunity to seamlessly model circuits and devices at multiple levels of abstraction while reasoning within a simple and formally defined mathematical model.

The inherent flexibility of the abstract notion of signal handled in the synchronous/desynchronized design model of Signal invites and favors the design of correct-by-construction systems by means of well-defined transformations of system specifications (morphisms) that preserve the intended semantics and stated properties of the architecture under design.

Plan In the present article, we propose to examine the mathematical concept of polychrony and define the corresponding relational design model. This model yields the definition of the Polychrony synchronous programming environment. Based on this implementation, we develop top-down (refinement-based) and bottom-up (component-based) methodological approaches to system design. We put this method to work for modeling and synthesizing hardware devices, thereby demonstrating the effectiveness and flexibility of our model and method.

The outline of our presentation starts in section 2 with the exposition of a rationale on the model of Signal. It starts with a highlight on the peculiar design choices of the model, and an informal tutorial presentation of its syntax with key examples. It continues with a formal specification of the underlying mathematical model (section 3). Section 4 assesses the appropriateness of the Signal model for designing complex Gals architectures. This assessment includes a formal presentation of traditional properties as reactivity or determinism, and more specific formal properties such as endochrony, flow-invariance, latency-insensitivity.

Section 5 puts the expression capabilities of our mathematically well-founded model to work by spelling out its methodological consequences. We define both a top-down design engineering method, based on the classical notion of refinement (section 6.1) and then a bottom-up design method, based on the principles of component-based engineering (section 6.2). The introduction of these notions is exemplified by studying the case of the progressive design of an even-parity checker. Section 5.4 presents the static resolution and dynamic model-checking techniques that come with the Polychrony environment to check that the refinement of a design is not regressive and that the integration of components verify the intended functional requirements of the system.

Section 7 probes the usefulness of Signal for engineering circuits further by describing optimization techniques which greatly improve simulation by making use of symbolic transformation methods implemented in the Signal compiler. These

transformations consists of the desynchronization of elementary synchronous components, that, once recombined, allow to produce optimized control paths and generate optimized simulation (C) code. At last, section 8 recapitulates the results implemented in the Polychrony environment (see the Espresso project web-pages (http://www.irisa.fr/espresso for more detail) and makes some conclusive remarks.

# 2 Polychrony

The synchronous approach provides an unambiguous notion of time: time is seen as a chronology, instead of a chronometry, as in traditional HDLs. However, it is not always clear up to what extent synchronous languages are suitable tools to address the various levels of a design; how an implementation can be derived from a specification, and how the latter can proved correct against the former.

### 2.1 Rationale for a polychronous model

Synchronous design and synchronous languages share a common point of view: the propagation time of signals along combinational paths is always considered as much smaller than the sampled time interval between two observations. Because of the simplicity and popularity of this concept, the synchronous approach is usually subject to the *a priori* that it only applies for the design of purely synchronous circuits.

**Polychrony and over-sampling** This argument does not (at least) hold in the case of Signal. The polychronous mathematical model associates individual clocks (set of instants, also called time sets) to signals.

Over-sampling (i.e. adding an arbitrary yet inductive number of instants between two clock cycles) enables the specification of constraints between inputs and outputs in such a way that no further input may occur as long as the given constraints are not meet by the (intermediate) calculations of the output.

Over-sampling is an example of flow-preserving transformation or refinement which consists of specifying the internal reactions of a given system component as fast enough to stabilize until new values occur on input and results occur along outputs (in particular, over-sampling does not loose any input value).

The abstract notion of absence (of values) between two occurrences of <u>useful</u> values along a signal is flexible enough to enable reasoning on the successive refinements and transformations of the description of a system. Typically, absence allows to model asynchronous loops in hardware design (e.g. RS latches).

**Polychrony and flow-graphs** A control-data flow graph (CDFG) is a commonly used representation to capture sequentiality, conditional branching and control loop constructs (in its control-flow portion of the CDFG), and operations on data (in its

data-flow portion of the CDFG). In our model, a clock is associated to every signal; this notion of clock (or time set) generalizes to actions as well as to sequences of actions, providing a uniform way to support data and control transformations on what we name a conditional flow graph.

Abstraction and refinement The notion of over-sampling clearly renders the multiple levels of abstraction and the multiple granularities of time that prevail at the successive architecture levels of a circuit or system. Over-sampling is also very useful to reproduce typical synchronization patterns encountered at system-level between complex components, as well as typical simulation mechanisms that emulate flows of data between loosely coupled domains.

As a result, polychrony exhibits a continuum between the dual notions of abstraction and refinement which is central to decompose, understand and integrate the design of a system at its successive architectural levels of its components. Signal allows the description of properties and behaviors, of interfaces and implementations, of abstractions and refinements within the same formal design model.

Furthermore, the notion of polychrony naturally yields a partial order relation of implementation: a behavior implements a property (or another, more general, behavior), a component implements an interface, a refinement implements an abstraction. This implementation relation can easily be built by means of formal simulation relations and related model-checking and static-checking techniques.

**Polychrony and state machines** In Signal, model-checking is preferably implemented by mean of the resolution of polynomial dynamical system of equations expressed over the ring  $\mathbb{Z}/3\mathbb{Z}$  (using ternary decision diagrams), where absence is interpreted as 0. The main advantage of this representation is that, making explicit use of operations on ideals and variety of  $\mathbb{Z}/3\mathbb{Z}$  avoids the enumeration the state-space of a given specification, and additionally enables control-synthesis.

Model-checking Signal specifications could also be implemented using more conventional data-structures, such as boolean decision diagrams or automata. However, experiments shows that such representations significantly increase the number of variables.

In Signal, static-checking is implemented by means of the inference and resolution of invariants between signals, which describe their synchronization, serialization and causality relations: the *clock calculus*. Synchronization and causality relations play a central role for the compilation, optimization and transformation of programs. They are of most interest to statically check the implementation relation: a component implements an interface if the synchronization and causal relations of the interface are implied by those of the component.

### 2.2 An informal introduction to core-Signal

In Signal, a process P consists of the simultaneous composition of equations over signals. A signal  $x \in \mathcal{X}$  describes a possibly infinite flow of timed values (we write x for a sequence of names and assume an infinite set of signal names  $\mathcal{X}$ ). We first introduce the abstract syntax used in this paper and then give some guidelines to read the examples written in Signal.

**Abstract syntax** An equation x = fy describes a relation between a sequence of operands y and a sequence of results x by a process  $f \in F$ . We write  $v, w \in \mathcal{V}$  for a value and t and t for the boolean constants true and false.

The synchronous composition  $P \mid Q$  of the processes P and Q consists of simultaneously considering a solution of the equations in P and Q at any time. The abstract syntax of a process P in core-Signal is defined by the inductive grammar:

$$\begin{array}{cccc} P & ::= & \boldsymbol{x} = f \, \boldsymbol{y} & & \text{(equation)} \\ & | & P \mid Q & & \text{(composition)} \\ & | & P / x & & \text{(restriction)} \end{array}$$

SIGNAL requires three primitive processes: pre (to reference the previous value of a signal in time), when (to sample a signal) and default (to deterministically merge two signals). It also requires the following primitive boolean functions: negation not, equality eq and identity id. pre cab be considered as a register whilst when and default are related to control.

$$f \in F \supseteq \{ \operatorname{pre} v \mid v \in \mathcal{V} \} \cup \{ \operatorname{when}, \operatorname{default}, \operatorname{not}, \operatorname{eq}, \operatorname{id}, \ldots \}$$

The equation  $x = \operatorname{pre} v y$  initially defines x by the value v and then by the previous value of y in time. It requires x and y to be synchronous (i.e. to be present at the same time).

$$y: (t_1,v_1) \, (t_2,v_2) \, \, (t_3,v_3) \dots$$

pre  $v\,y: (t_1,v) \, \, (t_2,v_1) \, \, (t_3,v_2) \dots$

The equation x = y when z defines x by y when z is true.

The equation x = y default z defines x by y when y is present and by z otherwise.

```

\begin{array}{c} y: & (t_2,v_2) \, (t_3,v_3) \, \dots \\ z: (t_1,v_1) & (t_3,w_3) \dots \\ y \text{ default } z: (t_1,v_1) \, (t_2,v_2) \, (t_3,v_3) \, \dots \end{array}

```

Concrete syntax of Signal If P (resp. exp or f(x1,...,xn)) is a concrete Signal process, we write P (resp. exp or f(y)) to denote its abstract syntax.

- (x1,...,xn) := f(y1,...,yn) is the concrete syntax for an equation x = f(y);

- The expressions not c, x when c, x default y and P | Q have identical concrete and abstract syntax. Delay is written x:=y\$1 init v in the concrete syntax and  $x = \operatorname{pre} v y$  in the abstract syntax;

- The declaration P where t x defines the type t of the signal x and becomes P/x in the abstract syntax. The type event is the subtype  $\{t\} \subset \mathbb{B}$ .

- The equations c := (exp1 = exp2) and x := y in the concrete syntax correspond to the statements c = eq(exp1, exp2) and y = idx in the abstract syntax;

- The equation x := v (for v a constant) is equivalent to x := x\$1 init v and

x := when c to x := true when c.

Further notations of the concrete syntax can similarly be expanded into primitive expressions. Examples are x = y, to mean that x and y are synchronous; x + y, to mean that either x or y are present.

We exemplify the equational design model of Signal by considering examples (written in the concrete syntax) that unveil the key features of its primitive operators and help understanding the peculiarities of the mathematical model to be presented next.

**Example 1 (counter).** To start with, let us consider putting the three primitive operators together by designing a rudimentary increasing counter that can be reset to 0. The process Count accepts an input reset signal and delivers the integer output signal val. The local variable counter is initialized to 0 and stores the previous value of the signal val (equation counter := val\$1 init 0). When an input reset occurs, the signal val is reset to 0 (expression (0 when reset)). Otherwise, the signal val takes an increment of the variable counter (expression (counter + 1)).

Notice that the activity of the process Count is governed by the clock of its output val which differs from that of its input reset. Count is a polychronous process. If the signal val is solicited by the environment, then either reset is absent and Count increments val, or reset is present and Count sets val to 0. Hence, the process Count is reactive and deterministic.

**Example 2 (sampler).** It can be used in different contexts in order to provide the required behaviors. For instance, in the process Sampler, the process Count is wrapped by additional input and output signals in order to implement a counter modulo N (an integer constant parameter) and can still be reset to 0 upon receipt of the reset event. Had we written val := Count(alarm) instead of val := Count(reset default alarm), we would have defined a modulo function instead.

```

process Sampler = {integer N} (? event reset, tick ! integer val; event alarm)

(| val

:= Count(reset default alarm)

:= (val = N-1)$1 init true

mod

alarm := when mod

val ^= reset ^+ tick

|) where boolean mod;

end:

observable events

tick

tt

tt

tt

tt

tt

reset

tt

tt

tt

alarm

2 \ 3 \ 4 \ 0

2

3

0

val | 1 0 1

1

counter \mid 0 \quad 1 \quad 0 \quad 1 \quad 2 \quad 3 \quad 4

0 1

```

The rate of execution is now governed by two input signals tick and reset. An alarm signal is generated each time the count val is reset to 0 (i.e. if the previous output of Count was N-1, expression mod := (val = N-1)\$1 init true).

In this example, we also introduce synchronization relations. To ensure a correct synchronization of the signal val with the reset and tick events, we need to specify the relation val ^= reset ^+ tick, which means that val is present (and activates the counter) iff either reset or tick is present.

**Example 3 (clock).** We may use the sampler to modularly design a clock (with a reset capability) by composing four instances of the parameterized Sampler process to count seconds, minutes and hours given an input base signal and the constant number N of bases within a second.

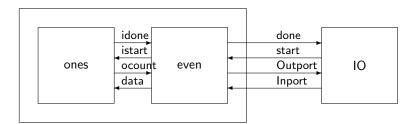

**Example 4 (over-sampling).** We now consider more advanced modeling techniques by considering the design of a true piece of hardware and exercise elementary methodological notions by considering the refinement of this design and its implementation, making use of the unique feature of over-sampling, that characterizes the Signal model.

In Signal, one may want to design a process making internal iterative (and finite) computations (just as for counting seconds), but sometimes, one would appreciate to just have to care about the result of the iteration and not to have to explicitly activate that process to perform an iteration. It is not necessary to do so in Signal, by contrast with related synchronous languages.

As an example, consider the following expression which checks a particular byte-level property (sub-process IsEven) of an integer signal num. At this level of design, one just expects IsEven to return an event when the property is satisfied (hence, the boolean output of IsEven is down-sampled, using when, to the instants at which it holds the value true).

```

even := true when IsEven(num)

```

Now, suppose that the property implemented by the process IsEven consists of checking teh condition that the number of bits of the input is an even number. Although the computation of this property can be done in a bounded number of iterations, it requires the activation of a sub-clock every time an input count is passed to the process IsEven. To implement it in Signal, one uses an internal, variable over-sampling.

```

process IsEven = (? integer num ! boolean parity)

(| num

^= start

| start := when (done$1 init true)

| parity := flip when done

done

:= mask=0

(| curmask := rshift (mask$1 init 0)

l mask

:= num default curmask

|) where integer curmask

end

(| tick

:= when (xand (mask, 1) = 1)

\mid resetFlip := (xand (num, 1) = 0)

:= resetFlip default ((not flop) when tick) cell ^done

| flip

| flop

:= flip$1 init true

|) where event tick;

boolean resetFlip, flop

end

|) where event start;

boolean done, flip;

integer mask;

function rshift = (? integer x ! integer y);

function xand = (? integer x, y ! integer z);

end;

```

The process IsEven is initially in standby. It starts when an input num value is

present (expression num ^= start). It returns in standby after termination (expression start := when done\$1 init true). The process terminates when the internal variable mask reaches 0, meaning that there are no remaining bits to count (expression done := mask=0).

The variable mask is calculated every time the process is active and until the termination condition holds (meaning that a fix-point is reached). It is initialized to the input signal num when the process starts. Then, every time the process is active, it is shifted right curmask := rshift (mask\$1 init 0).

A tick occurs when a bit in the mask is set. This is determined by performing a logical-and between the mask and 1. If a tick occurs, a boolean flip signal commutes. The variable flop holds its previous value and is initially true. The operator cell allows to write a register cell at the clock-rate of the sub-expression (not flop) when tick and read it at the (different) clock-rate of the signal done. When the process stops, the parity is true iff that signal is true. This example makes use of external function declarations (rshift and xand).

| $observable\ events$           |    |          |    |    |    |          |          |    |    |    |    |    |

|--------------------------------|----|----------|----|----|----|----------|----------|----|----|----|----|----|

| num                            | 5  |          |    |    | 4  |          |          |    | 0  | 3  |    |    |

| parity                         |    |          |    | tt |    |          |          | ff | tt |    |    | tt |

| $additional\ internal\ events$ | 1  |          | •  | 1  | 1  |          |          | I  | 1  | 1  |    | 1  |

| done                           | ff | $f\!\!f$ | ff | tt | ff | $f\!\!f$ | ff       | tt | tt | ff | ff | tt |

| mask                           | 5  | 2        | 1  | 0  | 4  | 2        | 1        | 0  | 0  | 3  | 1  | 0  |

| tick                           | tt |          | tt |    |    |          | tt       |    |    | tt | tt |    |

| flip                           | ff | ff       | tt | tt | tt | tt       | $f\!\!f$ | ff | tt | ff | tt | tt |

#### 3 A model for polychronous systems

Starting from the model of tagged signals of Lee and Sangiovani <sup>19</sup>, we define a tagged model of polychronous signals. This yields a structure of polychronous processes that is used to give the formal trace semantics of core-Signal. We then assess the generality and expressive power of the formal semantics and design model of core-Signal by spelling out its algebraic properties.

### 3.1 A tagged model of polychronous processes

We consider a set of boolean and integer values  $v \in \mathcal{V} = \mathbb{B} + \mathbb{Z}$  to represent the operands and results of a computation. A tag t, used to denote synchronization, is an element of a set  $\mathbb{T}$  equipped with a partial order relation  $\leq$ ; the partial order represents causality. A chain  $C \in \mathbb{T}$  is a totally ordered subset of  $\mathbb{T}$ .

**Definition 1 (partial-order of tags).** The partially ordered set  $(\mathcal{T}, \leq)$  of a given process is a subset  $\mathcal{T} \subset \mathbb{T}$  that satisfies the following properties:

```

\mathcal{T} is countable \mathcal{T} has a lower bound 0 for \leq the partial-order \leq on \mathcal{T} is well-founded

```

Let  $\mathcal{C}$  be the set of chains C in  $\mathcal{T}$ . Then, for a tag  $t \in C$ , we write  $\min(C)$ ,  $\max(C)$  and  $\operatorname{pred}_C(t)$  for the minimum, maximum and immediate predecessor of t in C.

**Definition 2 (event, signal and behavior).** An event  $e \in \mathcal{E} = \mathcal{T} \times \mathcal{V}$  is a relation between a tag and a value. A  $signal\ s \in \mathcal{S} = \mathcal{T} \rightharpoonup \mathcal{V}$  is a partial function defined on a chain of tags to a set of values. We write tags(s) to denote the domain of s. A  $behavior\ b \in \mathcal{B} = \mathcal{X} \rightharpoonup \mathcal{S}$  is a partial function from signal names  $x \in \mathcal{X}$  to signals  $s \in \mathcal{S}$ . We write vars(b) to denote the domain of b and  $tags(b) = \bigcup_{x \in vars(b)} tags(b(x))$  to denote its tags. Hence, the informal sentence "x is present (at t in b)" can be formally defined by  $t \in tags(b(x))$ .

Figure 1: A behavior b: from signal names to partially ordered tags and values

We write  $b|_X$  for the projection of a behavior b on a set  $X \subset \mathcal{X}$  of names (i.e.  $\operatorname{vars}(b|_X) = X$  and  $\forall x \in X, b|_X(x) = b(x)$ ) and  $b_{/X}$  for the projection of b on the complementary of X in  $\operatorname{vars}(b)$  (i.e.  $b_{/X} = b|_{\operatorname{vars}(b) \setminus X}$ ). We write  $\lambda$  to denote the empty signal and  $0|_X = \{(x, \lambda) \mid x \in X\}$  to associate  $X \subset \mathcal{X}$  to the empty signal.

**Definition 3 (process).** A process  $p \in \mathcal{P} = \mathcal{P}(\mathcal{B})$  is a set of behaviors that have the same domain X (we write it vars(p)). The synchronous composition  $p \mid q$  of two processes p and q is defined by the set of behaviors that extend a behavior  $b \in p$  by the restriction  $c_{vars(p)}$  of a behavior  $c \in q$  provided that the projections of b and c on  $vars(p) \cap vars(q)$  are equal.

$$p \mid q = \left\{ b \uplus c_{/\text{vars}(p)} \mid (b, c) \in p \times q, \ b|_{\text{vars}(p) \cap \text{vars}(q)} = c|_{\text{vars}(p) \cap \text{vars}(q)} \right\}$$

Figure 2: Synchronous composition  $p \mid q$ : matching behaviors along common signals

$<sup>\</sup>S$  or, equivalently,  $b/\text{vars}(q) \uplus b|_{\text{vars}(p) \cap \text{vars}(q)} \uplus c/\text{vars}(p)$  since b and c coincide on  $\text{vars}(p) \cap \text{vars}(q)$

Notes Notice that a process p consists of an inductive number of behaviors, and that a behavior consists of a finite number of tag chains. Each chain is infinite and countable. Hence, the set of tags in a process is at most countable. In the present model, a signal is a partial function from a set of tags  $\mathcal{T}$  to a set of values  $\mathcal{V}$ . An alternative approach would be to define it as a total function on  $\mathcal{T}$  to  $\mathcal{V}$  completed by  $\bot$ . In <sup>19</sup>, a more general definition of process is given by considering an unordered set of tags and a set of value completed with a special mark  $\bot$  to denote the absence of a value at a given time tag. This generality is not required to model synchronous processes. Synchronous structures <sup>21</sup> also constitute a more general model, where the so-called imaginary signals (i.e. signals in which tags are not totally ordered) can also be modeled.

#### 3.2 Scalable design

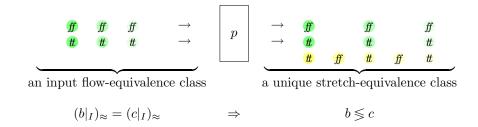

A key concept for defining systems and reusable components in a smooth design process is the concept of scalable observation. For instance, when defining the instruction set of a component, the various micro steps of the execution of an instruction don't have to be known, and the instruction is seen as a process that takes arguments and (simultaneously, or at the next step) does an atomic action; the designer of the circuit will actually implement a finer clocked process. A single virtual circuit can be implemented using various internal architectures and various clock frequencies. A technical support for allowing time scalability is given in our model by the so called stretch-closure property, strongly related to stuttering invariance in models with silent events.

Figure 3: Stretching b allows for a scalable c and refinement d

The intuition behind this relation is to consider a signal as an elastic with (ordered) marks on it (the tags). If we stretch the elastic, the marks remain in the same order, but we may now add more marks between two stretched marks. If we unstretch the elastic, all marks will be closer to one another and some of them not distinguishable, but they will still remain in the same order. The same holds for a set of elastics: a behavior. If we equally stretch each elastic, the partial order between each mark will remain the same.

**Definition 4 (stretching).** A behavior c is a stretching of b, written  $b \leq c$ , iff vars(b) = vars(c) and there exists a bijection  $f: \mathcal{T} \to \mathcal{T}$  that

```

is order-preserving, i.e. \forall t, u \in \mathcal{T}, t < u \Leftrightarrow f(t) < f(u)

is increasing, i.e. \forall C \in \mathcal{C}, \forall t \in C, t \leq f(t)

satisfies tags(c(x)) = f(tags(b(x))) for all x \in vars(b)

satisfies b(x)(t) = c(x)(f(t)) for all x \in vars(b) and all t \in tags(b(x))

```

The relation of stretching  $\leq$  is a partial-order relation on behaviors. It gives rise to an equivalence relation between behaviors. Both relations are extended to processes.

**Definition 5 (stretch-equivalence).** The behaviors b and c are stretch-equivalent, written  $b \le c$ , iff there exists a behavior d s.t.  $d \le b$  and  $d \le c$ .

It is appealing to consider the relation between processes and the partial order of stretching. In particular, it is interesting to consider the class of processes which contain all possible stretches of a given behavior.

**Definition 6 (stretch-closure).** A process p is stretching-closed iff for all  $b \in p$  and all  $c \in \mathcal{B}$ ,  $c \leq b \Rightarrow c \in p$ .

A non-empty, stretching-closed process p admits a set of strict behaviors, written  $(p)_{\leqslant}$ , s.t.  $(p)_{\leqslant} \subset p$  (for all  $b \in p$ , there exists a unique  $c \in (p)_{\leqslant}$  s.t.  $c \leqslant b$ ).

### 3.3 Denotation of core-Signal

The denotation  $[\![P]\!]$  of a process P consists of the largest set of behaviors accepted by P. It is defined by induction on the structure of P. For each equation,  $\mathbf{x} = f\mathbf{y}$  and by induction hypothesis, the function  $[\![]\!]$  defines the relation between the signals involved in an equation by considering the chain of tags that supports it.

**Denotation function**  $\llbracket p \rrbracket$  The equation  $x = \operatorname{pre} v \, y$  initially defines x by the value v and then by the previous value of y in time. Suppose that the value of the input signal y is w at a given tag t. The output signal x loads the value v and the process evolves as  $x = \operatorname{pre} w \, y$ , storing the value w of y. The meaning of the equation  $x = \operatorname{pre} v \, y$  is to define the signals x and y along that same chain of tags  $C \in \mathcal{C}$  and define the value of x at a given tag x by the value of x at the immediate predecessor of x in x. Notice that this requires x and y to be synchronous (i.e. to share the same tags x).

$$\llbracket x = \operatorname{pre} v \, y \rrbracket = \{ \mathbf{0}|_{x,y} \} \cup \left\{ b \in \mathcal{B}|_{x,y} \, \middle| \, \underset{\forall t \in C \, \backslash \, \min(C), \ b(x)(t) = b(y)(\operatorname{pred}_C(t))}{\operatorname{tags}(b(x)) = \operatorname{tags}(b(y)) = C \in \mathcal{C} \, \backslash \, \emptyset, \ b(x)(\min(C)) = v \right\}$$

The equation x = y when z defines x by y when z is true. Let us consider the tag t at which this happens. There are four cases to consider:

```

\begin{split} &\text{if } t \notin \operatorname{tags}(y) \text{ then } t \notin \operatorname{tags}(x) \\ &\text{if } t \notin \operatorname{tags}(z) \text{ then } t \notin \operatorname{tags}(x) \\ &\text{if } t \in \operatorname{tags}(y) \text{ and } t \in \operatorname{tags}(z) \text{ and } z(t) = \mathit{ff} \text{ then } t \notin \operatorname{tags}(x) \\ &\text{if } t \in \operatorname{tags}(y) \text{ and } t \in \operatorname{tags}(z) \text{ and } z(t) = \mathit{ft} \text{ then } t \in \operatorname{tags}(x) \text{ and } x(t) = y(t) \end{split}  \|x = y \text{ when } z\| = \left\{ b \in \mathcal{B}|_{x,y,z} \, \middle| \, \begin{array}{l} \operatorname{tags}(b(x)) = \{t \in \operatorname{tags}(b(y)) \cap \operatorname{tags}(b(z)) \, | \, b(z)(t) = \mathit{tt} \} \\ \forall t \in \operatorname{tags}(b(x)), \, b(x)(t) = b(y)(t) \end{array} \right\}

```

The equation x = y default z defines x by y when y is present and by z otherwise. At a given tag t, there are three cases to consider:

```

if t \in \operatorname{tags}(y) then t \in \operatorname{tags}(x) and x(t) = y(t)

if t \notin \operatorname{tags}(y) and t \in \operatorname{tags}(z) then t \in \operatorname{tags}(x) and x(t) = z(t)

if t \notin \operatorname{tags}(y) and t \notin \operatorname{tags}(z) then t \notin \operatorname{tags}(x)

```

$$\llbracket x = y \operatorname{default} z \rrbracket = \left\{ b \in \mathcal{B}|_{x,y,z} \left| \begin{array}{c} \operatorname{tags}(b(y)) \cup \operatorname{tags}(b(y)) = \operatorname{tags}(b(x)) = C \in \mathcal{C} \\ \forall t \in C, \ b(x)(t) = \left\{ \begin{array}{c} b(y)(t), \quad t \in \operatorname{tags}(b(y)) \\ b(z)(t), \quad t \not \in \operatorname{tags}(b(y)) \end{array} \right. \right\}$$

Figure 4: Delay, sampling and merge

The meaning of the synchronous composition  $P \mid Q$  is the synchronous composition  $\llbracket P \rrbracket \mid \llbracket Q \rrbracket$  of the denotations  $\llbracket P \rrbracket$  and  $\llbracket Q \rrbracket$ .

$$[\![P \,|\, Q]\!] = [\![P]\!] \,|\, [\![Q]\!]$$

From the denotation of [P | Q], one easily infers the following property:

#### **Property 1.** Composition is commutative and associative

The meaning of restriction P/x (restricting the scope of the signal x to the process P) consists of all behaviors c that are stretch-equivalent to a behavior b/x from  $[\![P]\!]$ . Notice that the restriction of b over x is not enough to obtain all stretch-equivalent behaviors (see example 5). Therefore, one needs to define the meaning of  $[\![P/x]\!]$

as all  $c \leq b/x$  for all  $b \in [P]$ . Using the same symbol for syntactic and semantic restriction we define:

$$[P/x] = [P]/x$$

and  $p/x = \{c \mid b \in p \land c \le (b/x)\}$

**Example 5.** For instance, let  $b = ((x, s_1), (y, s_2))$  with  $s_1 = \{(t_1, 1), (t_2, 2), (t_3, 3)\}$  and  $s_2 = \{(t_1, t), (t_3, t)\}$  and consider the process  $p = \{c \ge b\}$ . The signal  $s_2$  is stretch equivalent to  $s'_2 = \{(t_1, t), (t_2, t)\} \le s_2$ . Hence,  $s'_2$  should be in the restriction of p over x, but it is not contained in  $\{c_x \mid c \in p\}$ .

The denotation of processes defined by the function  $[\![P]\!]$  satisfy the requirements for a scalable design. Namely, a process P can be used at different time scales because its denotation is closed for the stretch-equivalence relation.

**Property 2.** For all Signal processes P,  $[\![P]\!]$  is stretch-closed.

# 3.4 Algebraic properties

We now introduce the algebraic structure of processes in core-Signal. We first consider some remarkable processes: the process 1 s.t.  $vars(1) = \emptyset$  is neutral w.r.t. synchronous composition; the process  $0 = \{(x, \lambda)_{x \in X} \mid X \subset \mathcal{X}\}$  is absorbent w.r.t. synchronous composition. Let us note vars(P) (resp. out(P)) for the set of (output) signals in P and define  $in(P) = vars(P) \setminus out(P)$  for the input signals of P.

$$\begin{array}{ll} \operatorname{vars}(\pmb{x} = f\pmb{y}) = \pmb{x} \cup \pmb{y} & \operatorname{out}(\pmb{x} = f\pmb{y}) = \pmb{x} \\ \operatorname{vars}(P \mid Q) = \operatorname{vars}(P) \cup \operatorname{vars}(Q) & \operatorname{out}(P \mid Q) = \operatorname{out}(P) \cup \operatorname{out}(Q) \\ \operatorname{vars}(P/x) = \operatorname{vars}(P) \setminus \{x\} & \operatorname{out}(P/x) = \operatorname{out}(P) \setminus \{x\} \end{array}$$

A key property regards the containment of local signals. It is central to establish the algebraic structure of polychronous processes. It stipulates that a process P is equivalent to the projection of the composition  $P \mid Q$  on the signals vars(P) iff the projection of Q on the signals vars(P) is contained in the projection of P on vars(Q). This observation yields the algebraic structure of  $[\![P]\!]$ .

**Property 3.** For all processes

$$P$$

and  $Q$  s.t.  $vars(P) = A$  and  $vars(Q) = B$ ,

$$\begin{vmatrix} ( \llbracket P \rrbracket \rrbracket | \llbracket Q \rrbracket ) |_A \subset \llbracket P \rrbracket \\ ( \llbracket P \rrbracket | \llbracket Q \rrbracket ) |_B \subset \llbracket Q \rrbracket \\ \llbracket P \rrbracket = ( \llbracket P \rrbracket | \llbracket Q \rrbracket ) |_A \text{ iff } \llbracket Q \rrbracket |_{A \cap B} \supset \llbracket P \rrbracket |_{A \cap B}$$

The syntactic containment properties give rise to the structural equivalence laws between processes of  $[\![P]\!]$ .

Corollary 1 (laws of composition). For all processes P, Q and R, we have

absorbent:  $[\![P]\!] \mid \emptyset = \emptyset$  idempotent:  $[\![P]\!] \mid [\![P]\!] = [\![P]\!]$

monotonous:  $[\![P]\!] \subset [\![Q]\!] \Rightarrow [\![P]\!] \, | \, [\![R]\!] \subset [\![Q]\!] \, | \, [\![R]\!]$

neutral:  $[\![P]\!] | 1 = [\![P]\!]$

$\mathrm{vars}(P) = \mathrm{vars}(Q) \Rightarrow \llbracket P \rrbracket = \llbracket P \rrbracket \, | \, \llbracket Q \rrbracket \Leftrightarrow \llbracket P \rrbracket \subset \llbracket Q \rrbracket$

Hence the algebraic structure of  $\llbracket P \rrbracket$ :

**Property 4.** ([P], [1, 1) is a commutative monoid.

#### 3.5 Flow relations

Stretching defines an equivalence relation that preserves the simultaneousness and the ordering of events within a behavior, i.e. stretched behaviors possess the same synchronization relations. We introduce a weaker relation which discards the actual synchronization relations between signals and allows for comparing behaviors w.r.t. the sequences of values that signals hold. For this purpose we define a relaxation relation which allows to individually stretch the signals of a behavior, and the corresponding flow-equivalence relations between behaviors.

Figure 5: Asynchrony as the relaxation of synchronization relations

**Definition 7 (relaxation).** A behavior c is a relaxation of b, written  $b \sqsubseteq c$ , iff vars(b) = vars(c) and for all  $x \in vars(b)$ ,  $b_{|x} \le c_{|x}$ .

The relation of relaxation  $\sqsubseteq$  is a partial-order relation on behaviors. It gives rise to the flow-equivalence relation between behaviors. Two behaviors are flow-equivalent iff they have the same domain and their signals hold the same values in the same order.

**Definition 8 (flow-equivalence).** The behaviors b and c are flow-equivalent, written  $b \approx c$ , iff there exists a behavior d s.t.  $d \sqsubseteq b$  and  $d \sqsubseteq c$ .

Since the equivalence class of a behavior b is a semi-lattice, it admits a strict behavior, written  $b_{\approx}$ .

# 3.6 Sampling

Stretching defines an equivalence relation that preserves simultaneousness and ordering of all events, i.e. the stretched behavior is isomorphic to the original one. It mainly addresses the problem of using a component in various contexts. Relaxation defines an equivalence that preserves flows. This relation is useful for modeling the distribution of a process on an asynchronous architecture. The refinement of a system specification consists of transforming its abstract behaviors into more concrete ones that make intermediate computational steps explicit. Conversely, the abstraction of a behavior consists of discarding some intermediate calculations and the related intermediate events. Hence, it is necessary to device an *implementation relation* that takes the notion of time refinement into account for comparing behaviors. For that purpose we define the notions of *sampler* and *sampling* (w.r.t. a sampler). These definitions are the basis for hardware implementation in POLYCHRONY.

```

Definition 9 (sampler). A signal c is a sampler of a signal x iff

```

```

\forall t \in \operatorname{tags}(c), c(t) \in \mathbb{B}\operatorname{tags}_{tt}(x) \subset \operatorname{tags}_{tt}(c) \subset \operatorname{tags}(x) \subset \operatorname{tags}(c)

```

where  $\operatorname{tags}_{tt}(c) = \{t \in \operatorname{tags}(c) \mid c(t) = tt\}$ . A sampler c of a signal x is a  $\operatorname{clock}$  of x iff  $\operatorname{tags}(x) = \operatorname{tags}_{tt}(c)$ . A clock of x is a  $\operatorname{pure} \operatorname{clock}$  of x iff  $\operatorname{tags}(c) = \operatorname{tags}_{tt}(c)$ .

**Definition 10 (signal sampling).** The sampling of x by c, a sampler of x, consists in "removing" x occurrences from tags on which c is not equal to t. The result is the signal  $y = when_c(x)$  such that

```

\begin{aligned} & \operatorname{tags}(y) = \operatorname{tags}_{tt}(c) \\ \forall t \in \operatorname{tags}(y), & x(t) = y(t) \end{aligned}

```

We extend these definitions to behaviors and processes. This requires the definition of a *sampler system*.

**Definition 11 (sampler system).** Let b a behavior, and A=vars(b). A sampler system of b is a function  $\kappa: A \to A$  s.t.

```

\kappa

is acyclic

\forall a \in \text{dom}(\kappa), \ b(\kappa(a))

is a sampler of b(a)

```

A sampler system  $\kappa$  is a clock system iff for all  $a \in \text{dom}(\kappa)$ ,  $b(\kappa(a))$  is a clock of b(a). These definitions are extended to processes. A function  $\kappa$  is a sampler system (a clock system) for a process p iff it is a sampler system (a clock system) for every behavior b of p. We can define the notion of sampling.

**Definition 12 (sampling).** The sampling of a behavior b by a sampler system  $\kappa$  is the behavior  $b' = \mathcal{S}_{\kappa}(b)$  s.t. vars(b) = vars(b') and for all  $x \in vars(b)$ ,  $b'(x) = \mathcal{S}^*b(x)$  where  $\mathcal{S}^*$  is recursively defined by

```

if \kappa is not defined on x then S^*(b(x)) = b(x)

if \kappa is defined on x then S^*(b(x)) = when_{S^*(b(\kappa(x)))}(x)

```

This definition is extended to processes. The sampling of (a process) p by  $\kappa$ , a sampler system of p, is the process  $p' = \{S_{\kappa}(b) | b \in p\}$

**Example 6.** For instance,  $\kappa = \{(x,c)\}$ , with c a boolean signal, is a sampler system for the Signal processes  $x^=c$  and  $x^=$ when c. It is a clock system for the equation  $x^=$ when c that is itself a sampling of  $x^=c$  by  $\kappa$ .

# 4 Polychronous design properties

In this section, we intend to assess the generality and expressive power of the formal semantics and design model of core-Signal and demonstrate to what extent it encompasses and completes models considered in related works.

Synchronous programming is commonly associated to the notion of reactivity. If a real-time system has to immediately react to some high prioritized events, it is not required to do so for all events. The POLYCHRONY model allows to design reactive systems and "proactive" ones. Determinism is a key property for critical program execution. Nevertheless, specification level, property description, abstractions need non determinism resulting from partial descriptions. In the POLYCHRONY framework, one can design such non deterministic behaviors.

Synchronous programming was initially widely publicized using the idealized model of zero-time computation and instantaneous broadcast communication. Distributed systems do not, however, obey this idealized picture of perfect synchrony: computations and communications take time, interaction topologies evolve during service. As a matter of fact, synchrony and asynchrony are usually perceived as fundamentally different concepts in nature.

Asynchrony (as a model of concurrency) is traditionally relevant for reasoning on distributed algorithms and for modeling non-determinism, failure, mobility. It meets a natural implementation by networked point-to-point communication. Synchrony is largely understood as specific to the design of reactive systems and digital circuits. In this context, timeless logical concurrency and determinism are suitable hypothesis.

On the flip side, a synchronous design hypothesis consists usually of assuming that communications and computations are instantaneous between the successive execution steps of a system. Making this hypothesis is beneficial for design. It allows the designer to focus on the logics of the system, characterized by synchronization and causal relations between events, and abstract away timing issues until a later stage of the design (its deployment on a given architecture).

However, an everyday broader range of software development areas requires reasoning on a combination of synchronous and asynchronous interaction at the different architectural levels of the system under design. Relevant practical examples are co-designed hardware-software architectures, reconfigurable embedded devices, multi-threaded reactive systems components on real-time virtual machines and operating systems, distributed and reactive telecommunication applications on fault-tolerant middle-ware. In summary, every system whose design requires robustness to latency, to threading, to distribution.

# 4.1 Process properties

**Reactivity** Signal allows the specification of either reactive or non-reactive yet constrained processes. Following the approach of Berry, we define reactivity w.r.t. a set of signals I (usually, the set of inputs) as the ability of the process to react to each configuration of I in all states.

**Definition 13 (configuration).** A configuration on  $I \subset \mathcal{X}$  is a partial function from signal names  $x \in I$  to values  $v \in \mathcal{V}$ .

A process p of variables X = vars(p) is reactive on a given set  $I \subset X$  of inputs iff, for all strict behaviors  $b \in p$ , for all tags  $t \in \text{tags}(b)$ , for all configurations s on I (including the empty signal), there exists at least a behavior c that has the same prefix as b up to pred(t) and such that  $c_t = s$ . For a signal s (resp. behavior s), we write  $s|_{s}$  the prefix of s until the tag s0 i.e.  $s|_{s}$ 1 = {s1, s2 i.e. s3.

**Definition 14 (reactive).** A process p is reactive (strictly reactive) on  $I \subset \text{vars}(p)$  iff, for all  $b \in (p)_{\leq}$ , for all  $t \in \text{tags}(b)$ , for all configurations (all non empty configurations) s on I there exists  $c \in (p)_{\leq}$  s.t.:

$$(c)|_{\leq \operatorname{pred}(t)} = (b)|_{\leq \operatorname{pred}(t)}, c_t = s$$

A process that is reactive on a not empty I is (obviously) strictly reactive on I. We say that a process is reactive (strictly reactive) if it is reactive (strictly reactive) on its input signals.

Example 7. The equations z:=x default y and z:=x when y as well as all basic SIGNAL equations with a single input signal are strictly reactive processes. The

processes Sampler and Clock are further examples of strictly reactive processes. By contrast, the process Count is (only) reactive (see example 1).

On the opposite, the process z:=x and y is not reactive at all (in the sense of definition 14). The following program implements an and combinator that is "maximally" reactive on x and y.

```

(| a := x default (a$1 init false)

| b := y default (b$1 init false)

| z := a and b

|) where integer a, b;

```

To obtain a strictly reactive event driven and operator, we additionally need to add the synchronization constraint  $z = x^+ y$ . One may also want to extend the operator and to have a "minimal" and strictly reactive behavior (i.e. that does nothing as soon as one of its input signals is absent).

```

z := (x when ^y) and (y when ^x)

```

To get a reactive and whose output signal zz only changes when both input signals are present, one can simply add the equation zz := z default (zz\$1 init false). Last, but not least, the processes IsEven (example 4) is not strictly reactive. It accepts inputs only in standby (initially) or if its previous computation is terminated.

As a matter of comparison, ESTEREL programs are reactive by design. Depending upon the semantics of its step interpretation, a STATECHART may, or may not, be reactive. Finally, LUSTRE programs are usually not strictly reactive; they are never reactive.

**Determinism** An automaton is deterministic if, in all of its states, each event corresponds to at most one transition. In our model, a process p s.t. X = vars(p) is deterministic on a given set  $I \subset X$  of signals iff two strict behaviors b and c of p, that have the same projection on I up to a tag t, have the same behaviors (on X) up to t.

**Definition 15 (determinism).** A process p is deterministic on a (possibly empty) subset  $I \subset \text{vars}(p)$  iff, for all  $c_1, c_2 \in (p)_{\leq}$ , for all  $t \in \text{tags}(c_1) \cap \text{tags}(c_2)$ :

$$(c_1|_I)|_{\leq t} = (c_2|_I)|_{\leq t} \Rightarrow (c_1)|_{\leq t} = (c_2)|_{\leq t}$$

We say that a process is deterministic if it is deterministic on its input signals.

**Example 8.** The process x := y\$1 init v is deterministic as well as all other basic Signal equations (on distinct signals). The process Count of example 1 is deterministic. By contrast, the process x := a default x is not deterministic. When a is absent the value of x is free. Thus x is partially defined by this equation. In Signal, one can specify such a partial definition of x by write x := a in place

of x := a default x. Several partial definitions of a signal x can appear in a program, provided that these definitions are compatible (i.e. the composition  $x := a \mid x := b$  requires a and b to hold the same value when they have the same tag). Fortunately, non-deterministic specifications can be composed to form a deterministic program when some suitable synchronization constraints are added. This is, however, not always possible. For instance, the following process (which makes use of Count, example 1) is intrinsically non deterministic (actually the signal out may be every sequence of positive or null integers):

```

(| val := Count(reset) | out := val when request |) where integer val;

```

The reason why it is definitely not deterministic is that, whatever the context is, there is no way to synchronize the internal clock of val and thus the activity rate of this occurrence of Count.

As a matter of comparison, ESTEREL and LUSTRE programs are deterministic by design. Most StateChart interpretations are usually non deterministic. Signal capability to express non deterministic behaviors makes this language suitable for defining partial specifications, for modeling process or program abstractions, for modeling non deterministic devices, etc.

**Endochrony** The property of endochrony is a key property for system design, and specially component based system design. It can be seen as the equivalence between the internal (synchronous) and external (asynchronous) observations of a process. A process is said to be endochronous on I iff, given an external (asynchronous) stimulation of I, it is capable of reconstructing a unique synchronous behavior (up to stretch-equivalence).

This means that it can be implemented as a process which is mostly insensitive to (internal and) external propagation delays. This implementation and its context have to agree on activation starts (for instance a physical clock, an external triggering, a procedure call, etc) and on the availability of data, but not necessarily on the presence of signals at the current execution step. This task is controlled by the process that samples continuous signals or select significant values among parameters, read in file or memory, get values in a FIFO or a mailbox, etc.

Figure 6: An endochronous design

**Definition 16 (endochrony).** A process p is endochronous on a (possibly empty) subset  $I \subset \text{vars}(p)$  iff

$$\forall b, c \in p, (b|_I)_{\approx} = (c|_I)_{\approx} \Rightarrow b \leq c$$

We say that a process P is endochronous if it is endochronous on its input signals in (P). Notice that endochrony implies determinism.

**Property 5.** An endochronous process is deterministic.

**Example 9.** The processes z := x default y and z := x when y are not endochronous. The equation x := y\$1 init v and all other basic Signal equations (with variables being all distinct) denote endochronous processes.

The processes Count (Example 1), Sampler (Example 2), Clock (Example 3) are not endochronous. Conversely, and despite the fact that its greatest clock is not available from its interface, and that this clock depends upon values, IsEven is endochronous.

We can extend a deterministic and non-endochronous process by adding boolean signals and clock constraints. For instance, the following process yields an endochronous extension for z := x default y.

```

(| z := x default y

| cx ^= cy

| x ^= when cx

| y ^= when cy |)

```

Endochrony generally requires some clock constraints to be satisfied. Thus, ESTEREL programs or STATECHART are not endochronous. A LUSTRE program is endochronous by design and so are its internal nodes. In this model, a (possibly partial) data-flow function p can be defined as a process satisfying

$$\forall b, c \in p, (b|_I)_{\approx} = (c|_I)_{\approx} \Rightarrow (b)_{\approx} = (c_{\approx})$$

where  $I \subset \text{vars}(p)$  is the set of input signals. Thus an endochronous process is a data-flow function and the converse is false.

By *exochrony*, we denote the dual of endochrony: input configurations are mastered by the context of the process. An exochronous process is by definition a reactive deterministic process. ESTEREL programs are exochronous.

### 4.2 Composition properties

**Asynchrony** We use the partial order relation of relaxation to define the semantics of the asynchronous composition  $p \parallel q$  of synchronous processes p and q. Notice that  $p \parallel q \subseteq p \parallel q$ .

**Definition 17 (asynchrony).** Given a behavior b of p s.t. X = vars(p) and a behavior c of q s.t. Y = vars(q), the parallel composition of  $p \parallel q$  admits the behaviors d that are the relaxations of signals common to b and c (i.e.  $I = X \cap Y$ ).

$$p \parallel q = \left\{ d \mid \exists (b,c) \in p \times q, d_{|X \setminus Y} \leq b_{|X \setminus Y} \land b|_{I} \sqsubseteq d|_{I} \land d_{|Y \setminus X} \leq c_{|Y \setminus X} \land c|_{I} \sqsubseteq d|_{I} \right\}$$

**Flow-invariance** The relation of flow-equivalence offers the appropriate criterion for checking the refinement of a system with communication protocols correct. It is, for instance, the property considered in  $^4$  for the refinement-based design of the LTTA protocol in SIGNAL. Flow-invariance consists of ensuring that the refinement of a synchronous specification  $p \mid q$  by an asynchronous implementation  $p \mid q$  preserves the flow of values along signals for any given behavior.

**Definition 18 (flow-invariance).** The composition of p and q is flow-invariant iff, for all  $b \in p \mid q$ , for all  $c \in p \parallel q$ ,  $(b|_I)_{\approx} = (c|_I)_{\approx}$  implies  $b \approx c$  for I the input signals of  $p \mid q$ .

Moreover, flow-invariance is compositional and, as demonstrated in <sup>4</sup>, directly amenable to verification using model-checking.

Figure 7: A flow-invariant design

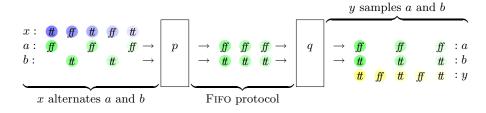

Endo-isochrony The implementation of globally asynchronous and locally synchronous (GALS) architectures in Signal amounts to model a system as a set of endochronous components that communicate endo-isochronously. Particular protocols such as patient processes or one-place Fifo buffers fall into this category and can be expressed in Signal (see example 10), thanks to polychrony and to the property of stretch and relaxation closure. Endo-isochrony is a much stronger requirement than flow-invariance, derived from the property of endochrony, and is amenable to static verification (as shown section 5.3).

**Definition 19 (endo-isochrony).** Two processes p and q are endo-isochronous iff p, q and  $(p|_I)|_{(q|_I)}$  are endochronous (with  $I = \text{vars}(p) \cap \text{vars}(q)$ ).

The properties of endochrony and endo-isochrony allow for the compositional design of distributed designs starting from polychronous specifications.

**Property 6 (endo-isochrony).** If p and q are endo-isochronous then the composition of p and q is flow-invariant.

**Example 10.** The following process implements an alternating input/output one-place buffer protocol (it is parameterized over the type t of the data and over the initial value i stored in the buffer's register).

It is implemented in two steps. The sub-process Current (modeling memory requirements) stores any value incoming from x and loads it into y upon demand (i.e. at the clock of y). The sub-process Alternate (modeling protocol constraints) alternates the clocks of x and y by synchronizing them to the different values of a boolean flip-flop signal b. Notice that the input x and the output y of the process Buffer are isomorphic.

### 4.3 Related works

The first formal address of desynchronization can be found in <sup>10</sup>, where precise relations between well-clocked synchronous functional programs and the subset of Kahn-networks are established, and shown to be amenable to buffer-less evaluation. In <sup>11</sup>, the author considers the distribution of synchronous automata on asynchronous networks using FIFO-buffered broadcast communications. In <sup>8</sup>, a model for the distribution of synchronous programs on distributed architectures is introduced which uses low-level non-blocking one-place buffers. In <sup>2</sup>, the transformation of synchronous designs on distributed architecture is further developed in the context of Signal. In <sup>3</sup>, an analysis of the links between synchrony and asynchrony is presented in the context of synchronous transition systems (STS) and the compositional property of isochrony introduced (a pair of processes is isochronous iff its synchronous and asynchronous compositions admit the same traces). Notice that flow-invariance implies isochrony.

The semantics of asynchrony of definition 17 is of comparable expressive power to that proposed in <sup>3</sup> for synchronous transition systems. It is expressed within the

tagged model of computation of  $^{19}$  and, unlike  $^3$ , equipped with partial order and equivalence relations that provide a structure of semi-lattice. It encompasses finite FIFO buffer implementations, as considered in  $^{10,11}$ , as well as low-level non-blocking one-place buffers implementations, a considered in  $^8$ .

In <sup>9</sup>, a theory of latency-insensitive protocols (Lip) is presented as a foundation of a new methodology to design very large digital systems by assembling blocks of existing *intellectual property* (Ip). It is appealing to cast the tagged model of polychronous signals in the theory of Lip to demonstrates how correct-by-construction polychronous designs can be implemented in this framework.

In the theory of LIP, a process p may accept  $stall\ moves$  (a stall move consists of stretching a signal s of a given behavior b by one logical instant) and respond by the appropriate procrastination effect (the other signals s' of the behavior b will respond to the delay of s by making coordinated stall moves).

The mechanism of causally related stall moves is made explicit (and generalized to polychronous signals) in the relation of stretching  $\sqsubseteq$  (definition 4). A stretch corresponds to a slide of tags in a given behavior: if an event e is stalled, then all other events e', causally related to e by the partial order relation  $\leq$ ) will slide. As a result, Signal processes are *patient*, in the sense of  $^9$ .

**Definition 20 (patience** <sup>9</sup>). A patient process p is a process such that, for all behaviors  $b \in p$ , for all and for all signals  $x \in \text{vars}(b)$  s.t.  $b(x) = (t_j, v_j)_{j>0}$ , if a signal  $s' = (t'_k, v_k)_{k>0}$  differs from s by one stall move (i.e. there exists l > 0 s.t.  $t_j = t'_k$  for all j = k < l and  $t_l \le t'_l$ ) then there exists  $b' \in p$  such that b'(x) = s'.

The (multi-clocked) notion of flow-equivalence relates to the (single-clocked) notion of latency-equivalence of Carloni et al.  $^9$ . Two signals are latency-equivalent iff they present the same values in the same order.

**Definition 21 (latency-equivalence** <sup>9</sup>). Let  $(t_i)_{i>0}$  and  $(t'_i)_{i>0}$  be two chains of  $\mathcal{T}$  s.t. for all j, k > 0,  $j \leq k$  iff  $t_j \leq t_k$  and  $t'_j \leq t'_k$ . The signals  $s = (t_i, v_i)_{i>0}$  and  $s' = (t'_i, v'_i)_{i>0}$  are latency equivalent iff for all i > 0,  $v_i = v'_i$ .

Notice that, if  $s \approx s'$  then s and s' are latency equivalent. Flow-equivalence extends the property of latency-equivalence to multi-clocked systems: the theory of LIP considers synchronous processes equipped with totally ordered time tags (i.e. single-clocked systems). This hypothesis corresponds to the low-level behavior of circuits (where silence, i.e.  $\tau$  events, corresponds to stall moves or "don't care" moves). The tagged model of polychronous signals considers a more general structure of partially ordered semi-lattice.

In Signal, the implementation communication media proposed in <sup>9</sup>: buffers, equalizers and relay processes; allows for the correct-by-construction design of latency-insensitive processes starting from endochronous (patient) IP blocks.

# 5 System design with polychrony

The Signal model provides a design methodology which encompasses compilation and distribution. The implementation of Signal supports this broad spectrum of utilization by providing accurate data-structures and algorithms to manipulate and transform the model of an application, from the specification of early requirements and property to the generation of sequential and distributed code.

The media for reasoning on a system under design in Signal consists of a synchronization relations, represented as clock hierarchies (section 5.1), and causality relations, represented by conditional dependency graphs (section 5.2).

These tools and the analysis and transformation techniques exposed in present section yield a seamless methodology that capture system design from its early specification stages (requirements can be expressed by synchronization and causality properties in Signal) down to late deployment stages (hierarchized and serialized designs can be expressed in Signal).

## 5.1 Synchronization relations

In Signal, the presence of a value along a signal x at a given tag is denoted by its clock  $\hat{x}$ . Referring to the tagged model of polychronous signals (section 3.1), the clock of a signal represents the set of tags at which the signal holds a value. This object can easily be represented in the syntax of Signal. For a given signal x, we write event x or  $\hat{x}$  for the signal that holds the value true iff x is present: its clock.

$$\begin{array}{c} x:\left(t_{1},v_{1}\right)\left(t_{2},v_{2}\right)\,\left(t_{3},v_{3}\right)\dots\\ \mathrm{event}\,x:\left(t_{1},t\!\!t\right)\,\left(t_{2},t\!\!t\right)\,\left(t_{3},t\!\!t\right)\,\dots\end{array}$$

Notice that both a system specification and its clock abstraction are objects which can both be represented and manipulated in Signal in order to produce and represent successive design transformation, from early requirement specifications to late sequential and distributed code generation. For instance, the process event can be defined in Signal as follows.

```

process event = (? x ! y) (| y = (x=x) |)

```

A synchronization relation is described by an equation between signal clocks. Given two signals x and y, we write synchro xy (or  $\hat{x}=\hat{y}$ ) to synchronize them. The process synchro can itself be defined in Signal as follows.

```

process synchro = (? x, y !) (| (event x)=(event y) |)

```

In order to enable reasoning on control in a system, we write [x] for the clock at which a boolean signal x (resp.  $[\neg x]$  holds the value true (resp. false). We naturally have the following relations between boolean signal clocks. These relations can themselves be represented in Signal. We write 0 for the empty clock. The grammar

of clock expressions h and clock relations H is defined by induction as follows.

$$h ::= 0 | \hat{x} | [x] | [\neg x] | h \hat{\times} h' | h \hat{+} h' | h \hat{-} h' \quad \text{(clocks)}$$

$$H ::= \emptyset | h = h' | h < h' | D \cup H' | \exists x.H \quad \text{(equations)}$$

The domain of clocks  $(\mathcal{H}, \hat{+}, \hat{\times}, \hat{-}, 0)$  forms a semi-lattice of union operator  $\hat{+}$ , intersection  $\hat{\times}$ , difference  $\hat{-}$  and neutral element 0. In particular, we have the following remarkable properties between clocks and sampling that  $\hat{x} = [x]\hat{+}[\neg x]$  and that  $[x]\hat{\times}[\neg x] = 0$  for all signal names x.

In the Signal compiler, clock relations are reconstructed from a given specification by making use of the following clock inference procedure. Note that existential quantifiers can be eliminated by replacing equations, e.g.  $\exists x. \{\hat{y} = \hat{x} + \hat{z}\}$ , by inequations, e.g.  $\{\hat{y} \geq \hat{z}\}$ .

$$\begin{split} x &= \operatorname{pre} v \, y : \{ \hat{x} = \hat{y} \} \\ x &= y \text{ when } z : \{ \hat{x} = \hat{y} \hat{\times} [z] \} \\ x &= y \operatorname{default} z : \{ \hat{x} = \hat{y} \hat{+} \hat{z} \} \\ P \mid Q : H \cup H' & \text{iff } P : H \text{ and } Q : H' \\ P / x : \exists x . H & \text{iff } P : H \end{split}$$

In order to establish the property that assesses the correctness of the inference system P:H, we define an interpretation of the set of clock relations H by the set of behaviors that satisfy these relations. We write this interpretation  $[\![H]\!]$ . A clock expression h is interpreted as the set of tags that characterize it for a given behavior b, written  $b|_{h}$ .

$$\forall b \in \mathcal{B}, \quad b|_{\hat{x}} = \left\{ \begin{array}{ll} \operatorname{tags}(b(x)), & x \in \operatorname{vars}(b) \\ \emptyset, & x \not \in \operatorname{vars}(b) \\ b|_{[x]} = \left\{ \begin{array}{ll} \operatorname{tags}(b(x)), & x \in \operatorname{vars}(b) \\ \emptyset, & x \not \in \operatorname{vars}(b) \\ \emptyset, & x \notin \operatorname{vars}(b) \end{array} \right. \quad \begin{array}{ll} b|_{[\neg x]} = b|_{\hat{x}} \setminus b|_{[x]} \\ b|_{h \hat{\times} h'} = b|_h \cap b|_{h'} \\ b|_{h \hat{+} h'} = b|_h \cup b|_{h'} \\ b|_{h \hat{\wedge} h'} = b|_h \setminus b|_{h'} \end{array} \right.$$

Then, a set of clock relations H is interpreted by the set  $[\![H]\!]$  that contains all the behaviors which satisfy it.

$$\begin{split} \llbracket h &= h' \rrbracket = \{ b \in \mathcal{B} \, | \, b|_h = b|_{h'} \} \\ \llbracket h &< h' \rrbracket = \{ b \in \mathcal{B} \, | \, b|_h \subset b|_{h'} \} \\ \llbracket H \cup H' \rrbracket = \llbracket H \rrbracket \cup \llbracket H' \rrbracket \\ \llbracket \exists x. H \rrbracket = \llbracket H \rrbracket_{/x} \end{split}$$

We show that the behaviors  $[\![P]\!]$  of a process P are contained in the interpretation  $[\![H]\!]$  of its clock constraints H.

**Property 7.** If

$$P:H$$

then  $\llbracket P \rrbracket \subseteq \llbracket H \rrbracket$

**Hierarchization** The Signal compiler uses the data structure of clock relations H to built a hierarchy of clocks. This hierarchy, which can be informally seen as

a forest of trees, renders the partial order relations between the clock of all signals defined in a given specification. Two signals x and y appear at the same node of the hierarchy iff they are synchronous, i.e.  $\hat{x} = \hat{y}$ . A signal x is placed in a branch under a signal y iff it is a down-sampling of y, i.e.  $\hat{x} < \hat{y}$ .

The construction of the hierarchy of clocks, introduced by Amabegnon et al. in  $^1$ , constitutes the core of the Signal compiler. It consists of first building elementary trees and then of merging the root of those trees according to clock relations specified in the remainder of the constraint set H. The hierarchization algorithm proposed by Amabegnon et al. in  $^1$  possesses a couple of remarkable properties:

- It produces a canonical representation of the clock constraint set C.

- It determines whether a design is endochronous (see definition 16): if the hierarchy of a process forms a tree then the order of evaluation of the equations of P is recursively determined by the clocks from top to the bottom of the tree

A sufficient condition for the existence of a canonical representation of H for a given design p is the existence of a master clock x for p, i.e., a signal x such that H implies  $\hat{x} > \hat{y}$  for all other signals y of p. Indeed, in a (deterministic) Signal design, output signal clocks are defined modulo the input signal clocks (for pre,  $\hat{x} = \hat{y}$ ; for pre,  $\hat{x} = \hat{y} + \hat{z}$ ; for pre,  $\hat{x} = \hat{y} \times [z]$ ). Therefore, the existence of a master x guarantees the computability of all output clocks starting from the input clocks.

**Example 11.** In order to give an informal assessment of this result (formalized section 5.3), let us reconsider the process  $\mathsf{Sampler}$  (example 1) and determine its synchronization relation using the inference system P:H. The  $\mathsf{SIGNAL}$  compiler produces the following synchronization constraints for the process  $\mathsf{Sampler}$ .

Its interpretation is that the clock of val is the union of the reset and tick signal clocks (expression CLK\_val := reset ^+ tick). The inferred clock CLK\_1 (defined by the expression CLK\_1 := reset ^+ alarm) is that at which the counter val is reset to 0. The inferred clock CLK\_2 (defined by the expression CLK\_2 := CLK\_val ^- CLK\_1) is that at which the counter val is incremented. The process is endochronous since we have that val = mod,  $val \ge tick$ ,  $val \ge reset$  and  $val \ge alarm$ .

```

(| CLK_val := reset ^+ tick

| CLK_1 := reset ^+ alarm

| CLK_2 := CLK_val ^- CLK_1

```

#### 5.2 Causality relations

A complementary feature provided by Signal allows to express control flow. The conditional data-flow graph in the Signal compiler handles this control flow as causal relations between signals at given clocks: the relation  $x \to b$  y specifies that

x is a cause of y at the clock of h. Causal relations are transitive and distributive w.r.t. clocks.

$$G ::= \emptyset \mid x \to^h y \mid G \cup G' \mid G \cap G' \mid G \setminus G' \mid \exists x.G$$

The conditional data-flow graph of a process is subject to the following distribution rules, which allow to construct its closure  $\overline{G}$ .

$$\forall x, y \, \forall h, h' \quad x \to^h y \cup y \to^{h'} z \quad \Rightarrow \quad x \to^{h \, \hat{\times} \, h'} z \\ x \to^h y \cup x \to^{h'} y \quad \Rightarrow \quad x \to^{h \, \hat{+} \, h'} y$$

In the Signal compiler, the data-structure of conditional data-flow graph G is used to schedule and serialize the equations of a design into elementary operations so as to produce optimized sequential code (for an acyclic graph) or distributed code (for a clustering of this graph into acyclic sub-graphs).

The presence of a cycle in the data-flow graph renders a causality loop of fixed-point equation that cannot be implemented by a single operation (e.g. x = x + 1 defines the immediate value of x by the solution of a fixed-point equation).