**DTU Library**

# Power and Thermal Management of System-on-Chip

Liu, Wei

Publication date:

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA): Liu, W. (2011). Power and Thermal Management of System-on-Chip. Technical University of Denmark. IMM-PHD-2011-250

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Power and Thermal Management of System-on-Chip

Wei Liu

Kongens Lyngby 2011 IMM-PHD-2011-250

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk

IMM-PHD: ISSN 0909-3192

# **Summary**

With greater integration of VLSI circuits, power consumption and power density have increased dramatically resulting in high chip temperatures and presenting a heat removal challenge. To effectively limit the high temperature inside a chip, thermal specific approaches, besides low power techniques, are necessary at the chip design level.

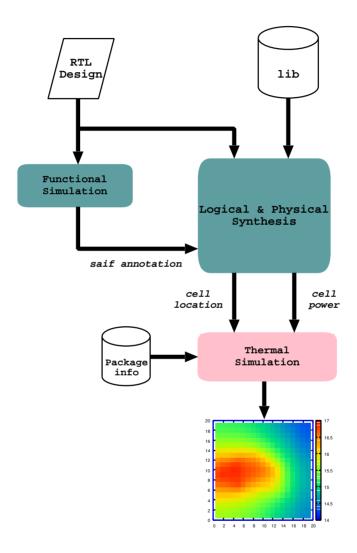

In this work, we investigate the power and thermal management of System-on-Chips (SoCs). Thermal analysis is performed in a SPICE simulation approach based on the electrical-thermal analogy. We investigate the impact of interconnects on heat distribution in the substrate and present a way to consider temperature dependent signal delay in global wires at early design stages.

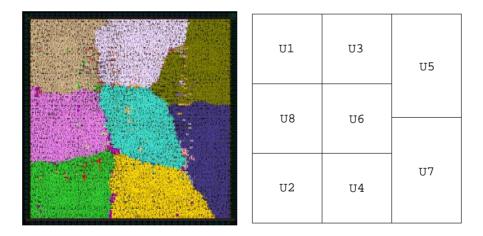

With the aim of reducing high local power density in hotspots, we propose two placement techniques to spread hot cells over a larger area. The proposed methods are compared in terms of temperature reduction, timing and area overhead to the general method, which enlarges the circuit area uniformly.

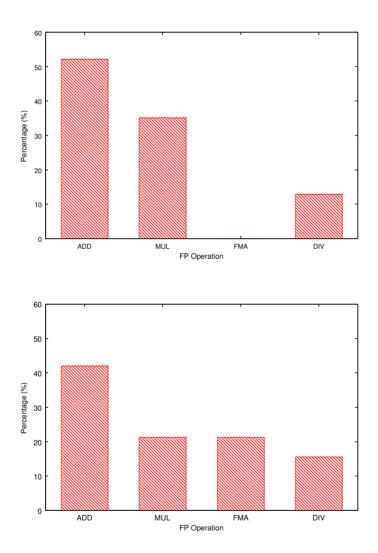

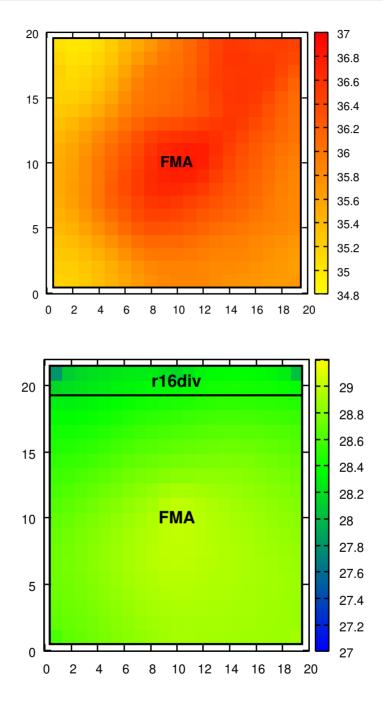

A case study analyzes the design of Floating Point Units (FPU) from an energy and a thermal perspective. For the division operation, we compare different implementations and illustrate the impact of power efficient dividers on the energy consumption and thermal distribution within the FPU and the on-chip cache. We also characterize the temperature dependent static dissipation to evaluate the reduction in leakage obtained from the decrease in temperature.

# Resumé

Ved øget integration af VLSI kredsløb øges effektforbrug og effekttæthed dramatisk med højere temperaturer på chippen til følge. Dette forhold gør fjernelse af energi en design udfordring. På chip design niveau er termisk specifikke metoder nødvendige for effektivt at begrænse temperaturen på chippen.

I dette arbejde undersøges metoder for styring af effekt og temperatur for System-on-Chips (SoCs). Termisk analyse baseres på SPICE simuleringer af elektriske ækvivalentkredsløb for det termiske system. Indflydelsen af ledningsforbindelser for temperaturfordelingen i substratet undersøges, og en metode for estimering af temperaturafhængige signalforsinkelser på et tidligt stadie af design præsenteres.

Med målsætningen om at reducere punkter med høj lokal effekttæthed (hotspots) foreslås to placeringsteknikker for fordeling af hotspots over større areal. De foreslåede metoder sammenlignes med den generelle metode, hvor kredsløbsarealet øges uniformt, med hensyn til opnået temperaturreduktion samt omkostninger i form af øget forsinkelse og areal.

I et case study analyseres design af enheder til beregninger med flydende tal (Floating Point Units, FPU) med hensyn til energi og temperatur. For divisionsoperationen sammenlignes forskellige implementationer, og betydningen af energi-effektive divisionskredsløb illustreres ved energiforbrug og temperaturfordeling inden for FPU og i on-chip cache-lagre. Endelig karakteriseres det temperatur-afhængige statiske effektforbrug for at beregne reduktion i lækstrømme som følge af den lavere temperatur.

# **Preface**

This thesis was prepared at the Department of Informatics and Mathematical Modelling, the Technical University of Denmark in partial fulfillment of the requirements for acquiring the degree of Doctor of Philosophy in engineering.

The thesis deals with power and thermal management of System-on-Chips. The main focus is on investigating thermal behaviors within VLSI circuits, reducing peak temperature in hotspots and optimizing energy and leakage consumption.

The thesis is self-contained and relies on the work done in a number of research papers written during the period 2007–2010.

Lyngby, December 2010

Wei Liu

# **Acknowledgements**

First and foremost, I would like to thank my supervisor, Alberto Nannarelli, for his persistent encouragement and guidance over the years. I am deeply grateful for his confidence in me and for having the opportunity to work with him. I would also like to thank my co-supervisor, Jan Madsen, for providing great insight in state of the art of research and the way to conduct successful PhD study.

Part of the work was carried out during my external stay at the Electronic Design Automation group at Politecnico di Torino. I would like to express thanks to Professor Enrico Macii and Professor Massimo Poncino for hosting me at Polito and also to Andrea Calimera who worked closely with me on the project. Our discussions gave me great insight in the area of design automation and inspired many ideas that were later put down in this work.

I would also like to thank all the colleagues in the Embedded Systems Engineering section at DTU Informatics, for creating a great atmosphere to exchange ideas and opinions.

Finally, the greatest thanks go to my parents and my girlfriend for their enduring encouragement, support and love.

# Curriculum Vitae

### Wei Liu

| 2005    | Bachelor in Engineering, Zhejiang University (China)                                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2006-07 | Student Assistant, Center for Biological Sequence Analysis,<br>Technical University of Denmark                                                                       |

| 2007    | MSc in Engineering, Technical University of Denmark                                                                                                                  |

| 2009    | Visiting Student, Electronic Design Automation Group, Politecnico di Torino (Italy)                                                                                  |

| 2011    | PhD in Engineering, Technical University of Denmark<br>Dissertation: Power and Thermal Management of System-on-Chip<br>Supervisor: Alberto Nannarelli and Jan Madsen |

#### **PUBLICATIONS**

W.Liu and A.Nannarelli, "Power Dissipation in Division", *Proc. of 42nd Asilo-mar Conference on Signals, Systems and Computers*, pp. 1790-1794, Oct. 2008

W.Liu and A.Nannarelli, "Net Balanced Floorplanning Based on Elastic Energy Model", *Proc. of 26th Norchip Conference*, pp. 258-263, Nov. 2008

W.Liu, A.Calimera, A.Nannarelli, E.Macii and M.Poncino, "On-Chip Thermal Modeling Based on SPICE Simulation", *Proc. of 19th International Workshop on Power And Timing Modeling, Optimization and Simulation*, pp. 66-75, Sept. 2009

W.Liu, A.Nannarelli, A.Calimera, E.Macii and M.Poncino, "Post Placement Temperature Reduction Techniques", *Proc. of 2010 Design, Automation Test in Europe Conference Exhibition*, pp. 634-637, Mar. 2010

W.Liu and A.Nannarelli, "Power Dissipation Challenges in Multicore Floating-Point Units", *Proc. of 21st IEEE International Conference on Application-specific Systems Architectures and Processors*, pp. 257-264, Jul. 2010

W.Liu and A.Nannarelli, "Temperature Aware Power Optimization for Multicore Floating-Point Units", *Proc. of 44th Asilomar Conference on Signals, Systems and Computers*, pp. 1134-1138, Nov. 2010

# **Contents**

| 51                 | ımm   | ary                                                           | 1   |

|--------------------|-------|---------------------------------------------------------------|-----|

| R                  | esum  | ıé                                                            | iii |

| P                  | refac | е                                                             | v   |

| A                  | ckno  | wledgements                                                   | vii |

| 1                  | Inti  | roduction                                                     | 1   |

| <b>2</b>           | Pov   | ver Dissipation and Heat Transfer in CMOS VLSI circuits       | 5   |

|                    | 2.1   | Power Dissipation in CMOS circuits                            | 6   |

|                    | 2.2   | Design for Low Power                                          | 9   |

|                    | 2.3   | Heat Transfer and Distribution                                | 13  |

|                    | 2.4   | Technology Scaling and Thermal Issues                         | 17  |

|                    | 2.5   | Thermal Management Techniques                                 | 19  |

| 3                  | Floa  | ating Point Units                                             | 23  |

|                    | 3.1   | Floating-Point Representation                                 | 24  |

|                    | 3.2   | Floating-Point Addition                                       | 26  |

|                    | 3.3   | Floating-Point Multiplication                                 | 28  |

|                    | 3.4   | Floating-Point Fused Multiply-Add                             | 30  |

|                    | 3.5   | Floating-Point Division                                       | 33  |

| 4 Thermal Modeling |       | ermal Modeling                                                | 45  |

|                    | 4.1   | A SPICE Simulation Based Thermal Modeling Method              | 46  |

|                    | 4.2   | Wire Delay Estimation under Substrate Temperature Variation . | 59  |

|                    | 4.3   | Summary                                                       | 68  |

xii CONTENTS

| 5 | Pow  | ver Density Reduction in Hotspots                        | 69  |

|---|------|----------------------------------------------------------|-----|

|   | 5.1  | Motivation                                               | 70  |

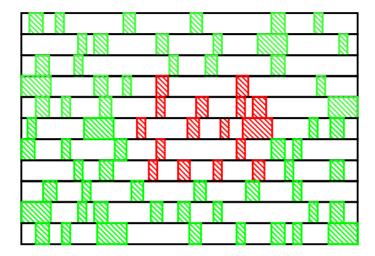

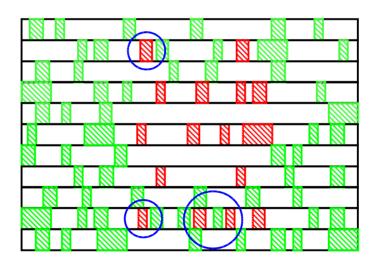

|   | 5.2  | Design Methodology                                       | 73  |

|   | 5.3  | Experiment Results                                       | 81  |

|   | 5.4  | Summary                                                  | 85  |

| 6 | Ene  | rgy and Thermal Aware Design in FPU                      | 87  |

|   | 6.1  | Energy Metrics                                           | 88  |

|   | 6.2  | Implementation of the FP-units                           | 89  |

|   | 6.3  | Energy Consumption in FP-operations                      | 91  |

|   | 6.4  | Thermal Analysis                                         | 94  |

|   | 6.5  | Leakage Optimization in Caches                           | 96  |

|   | 6.6  | Summary                                                  | 100 |

| 7 | Pers | spective                                                 | 103 |

|   | 7.1  | Thermal Aware Planning and Routing for Global Wires      | 103 |

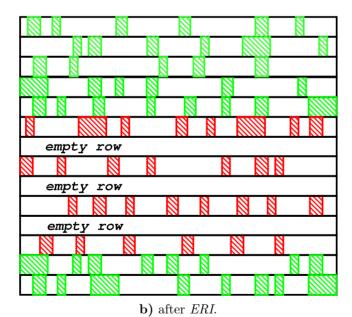

|   | 7.2  | Delay Overhead Optimization in ERI and HSD Methods       | 104 |

|   | 7.3  | NBTI Analysis with Detailed Spatial Thermal Distribution |     |

| 8 | Con  | clusion                                                  | 107 |

| Α | Sou  | rce Code for the Thermal Simulation Tool                 | 119 |

|   | A.1  | SPICE Subcircuit Model for Thermal Cells                 | 120 |

|   | A.2  | Mapping from Standard Cells to Thermal Cells             | 121 |

|   | A.3  | Generating SPICE Netlist for the RC Equivalent Circuit   | 125 |

|   | A.4  | Auxiliary Scripts                                        | 131 |

| В | Syn  | opsys Commands in the $ERI$ and $HSD$ Methods            | 133 |

|   | B.1  | Floorplanning in Synopsys' IC Compiler                   | 133 |

|   | B.2  | Commands for Information Retrieval and Cell Movement     | 134 |

|   | B.3  | Scripts for the <i>Empty Row Insertion</i> Method        | 135 |

|   | B.4  | Scripts for the HotSpot Diffusion Method                 | 137 |

# Chapter 1

# Introduction

Over the past few decades, the semiconductor industry has seen a revolutionary increase in computing performance, which is largely achieved through doubling the number of transistors on a chip almost every two years. This trend of technology scaling was already predicted by Intel's co-founder Gordon Moore as early as 1965, and often referred to as Moore's Law. In 2010, the industry has passed the two billion transistor milestone with the release of several high end server processors.

The dramatic increase in the degree of integration has allowed the design of more and more powerful systems, ranging from large mainframe servers constituting backbones of the Internet to portable handheld devices, which enable people to be connected at anytime from anywhere. The advancement in manufacturing technology and design methodology makes it possible to put an entire System on a Chip (SoC), integrating all components of an electronic system into a single Integrated Circuit (IC).

The increasing performance of Very Large Scale Integration (VLSI) circuits is accompanied by the increasing power and power density, which exhibit themselves in the form of heat and present a cooling challenge. The cost of cooling solutions is a nonlinear function of power and to a large extent limits the maximum amount of power that can be dissipated in a chip. This is also referred to as the *Power Wall* of commodity processors, which makes power and thermal

2 Introduction

management both a technical and an economic challenge.

Heat generated at transistor junctions flows towards the heat sink and the ambient environment mainly through the substrate and the chip package. Analogous to electrical resistance in current flow, thermal resistance can be defined as well, which is dependent on the dimension and the material used in the chip. To contain the peak junction temperature, a circuit has to operate within its thermal design power (TDP) so that heat generation does not outpace heat dissipation in the cooling system.

High temperature has a negative impact on many aspects of a Complementary Metal Oxide Semiconductor (CMOS) circuit, such as transistor performance, power consumption and system reliability. Thermal management is not only the task of package designers but also of the chip designers. To effectively limit the high temperature in a chip equipped with a cost-effective cooling system, thermal specific approaches, besides low power techniques, are necessary at the chip design level.

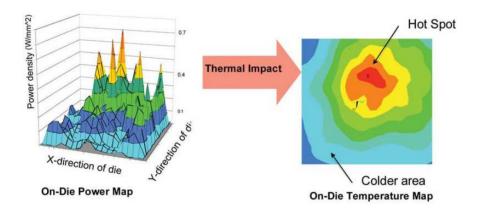

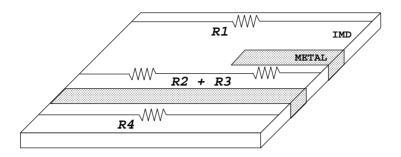

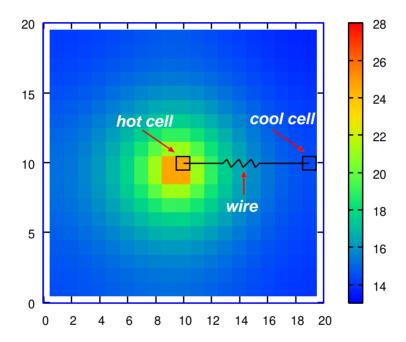

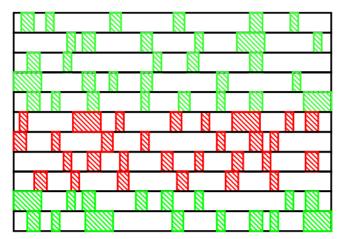

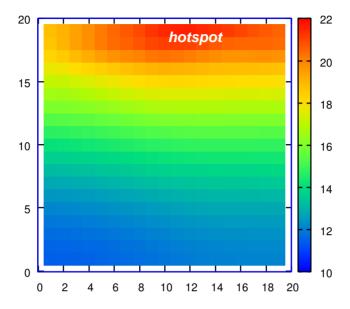

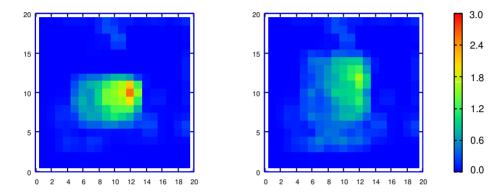

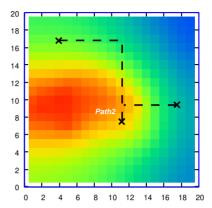

Figure 1.1: A typical power map and the corresponding thermal map (from [1]).

Figure 1.1 illustrates the correlation between the power profile and the corresponding thermal map, which schematically shows the temperature rise at different locations in the chip. The non-uniformity of power consumption can cause a much higher local power density (typically referred to as hotspots). In microprocessors, regions on the die with a temperature higher than 85 °C are usually called hotspots. Temperatures in the hotspots rise much faster than the full chip heating and can in the worst case cause severe damage to the chip.

In this work, we investigate the power and thermal management of SoCs. To

study the thermal distribution within a circuit, we implement a thermal simulator that numerically analyzes the power-temperature relationship. The thermal simulation provides valuable insights and forms the basis for characterization and optimization of thermal behaviors. We also studied the thermal impact on interconnect in terms of delay since the electrical resistance in metal is temperature dependent. The results give the perspective that wire planning at early design stages should take thermal impact into account to optimize for delay and reliability.

With the purpose of reducing power density in hotspots, we propose two placement techniques that spread cells in the hotspots over a larger area. Increasing the area occupied by the hotspot directly reduces its power density. We compare the proposed methods in terms of temperature reduction, timing and area overhead to the general method, which enlarges the circuit area uniformly.

In addition, as a case study we analyze the design of Floating Point Units (FPU) from both an energy and thermal perspective. We compare different implementations for the division operation and illustrate the impact of power efficient dividers on thermal profiles within the FPU and on-chip cache. The decrease in average temperature can reduce the power consumption in cache and any other leakage dominate circuit blocks. We provide a quantitative evaluation of the leakage and the total power reduction obtained from the decrease in temperature.

The rest of the chapters in this work is organized as follows. Chapter 2 describes power consumption and heat transfer within a CMOS VLSI circuit. Chapter 3 introduces floating-point (FP) number representations and describes algorithms and implementations for FP operations. Chapter 4 presents a thermal simulation method, which we use to analyze steady-state thermal profile within a circuit. In Chapter 4, we also describe a method to model temperature dependent wire delay during the early design stages. Chapter 5 presents two temperature reduction techniques that we propose to reduce the power density in hotspots. Chapter 6 discusses power consumption in FPUs and compares energy savings and peak temperature reductions from alternative implementations of FP division. Chapter 7 highlights some of the perspectives that can extend this work and finally Chapter 8 draws the conclusions.

4 Introduction

# Chapter 2

# Power Dissipation and Heat Transfer in CMOS VLSI circuits

Power consumption has become a primary design constraint as CMOS manufacturing technology scales down to deep sub-micron geometries.

Traditionally, static CMOS circuits are very power efficient as they nearly dissipate zero power while idle. This is a compelling advantage over bipolar processes and allows much more CMOS transistors to be integrated onto a single die. Since the 1980s CMOS processes were widely adopted and are nowadays used for nearly all digital logic applications.

According to the constant field scaling theory [2], both the dynamic power and the area of a transistor scales to  $1/S^2$  (S is the process scaling factor) when moving to a new process node. As a result, for the same die area designers can put  $S^2$  times more transistors in a new process while maintaining the same power density.

In practice, however, power density has skyrocketed because clock frequencies have increased much faster and supply voltage remains higher than classical scaling would predict. The increasing power density results in higher junction temperature, which affects many aspects of a semiconductor device. In high end processors, the performance is becoming increasingly limited by the maximum amount of power that can be dissipated by the cooling system without exceeding the maximum junction temperature. Increasing the volume of heat sinks or using more advanced cooling systems can permit more power dissipation. However, the cost of cooling systems is a nonlinear function of total chip power dissipation which makes using more powerful cooling system a non sustainable solution. In commodity microprocessors, a shift from high frequency single core designs to moderate frequency multi-core designs has already taken place because of the excessive cooling cost.

The emergence of new technologies can offer a one time solution to the heating problem, such as the displacement of bipolar technology by CMOS technology. However, at the moment no clear successor to the CMOS technology has emerged yet. Power consumption and power density will remain as the key design bottleneck as the degree of integration increases with each new process node. Consequently, it has become ever more important to build power efficient and thermal aware solutions at all design levels.

Many research work has been carried out in the past decades to design power efficient circuit but in recent years thermal issues quickly arose to become one of the potential show-stoppers to future CMOS scaling. In this chapter, we will first review the mechanisms of power dissipation in CMOS circuits and describe the methods to model and estimate on-chip temperature distribution. Then we will discuss about thermal trends with technology scaling and how temperature affect various properties of CMOS circuits. Finally, we briefly summarize the related work in the area of power and thermal management.

# 2.1 Power Dissipation in CMOS circuits

Power dissipation in CMOS circuits comes from two components [2]:

- Dynamic dissipation due to charging and discharging of load capacitance and to the short-circuit current.

- Static dissipation due to leakage current and other current drawn continuously from the power supply.

### 2.1.1 Dynamic Dissipation

The dominant component in dynamic power dissipation is due to the charging of the load capacitance  $C_L$ . In standard cell designs,  $C_L$  for a certain cell is the total gate capacitance on the driven cells  $C_g$  and the total capacitance contributed from the interconnecting wires to the driven cells  $C_w$ . In nanometer technologies, for long wires (longer than several tens of micrometer),  $C_w$  can dominate  $C_g$  and contribute the most to  $C_L$  in a standard cell.

$$C_L = C_q + C_w (2.1)$$

The average dynamic power dissipation can be expressed as the average instantaneous energy dissipation:

$$P_{dynamic} = \frac{1}{T} \int_{0}^{T} i_{DD}(t) V_{DD} dt = \frac{V_{DD}}{T} \int_{0}^{T} i_{DD}(t) dt$$

(2.2)

where  $i_{DD}(t)$  is the transient current drawn from the power supply and  $V_{DD}$  is the supply voltage. The integral is the total amount of charges delivered during the time interval T. During each transition, the load capacitance is charged to  $V_{DD}$  or discharged to ground and the amount of charges delivered Q is therefore equal to  $C_LV_{DD}$ . Assuming a nodal activity of  $\alpha$  on the load and a clock frequency of f, the total number of transitions amounts to  $\alpha Tf$ . Therefore, Eq. (2.2) simplifies to:

$$P_{dynamic} = \frac{V_{DD}}{T} \alpha T f C_L V_{DD} = \alpha C_L V_{DD}^2 f$$

(2.3)

$\alpha C_L$  is also called effective switching capacitance as it is the part of total capacitance that contributes power consumption.

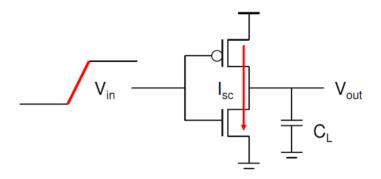

Short circuit power dissipation occurs when both pull-up and pull-down network in a CMOS gate are partially ON during the input signal transition (as illustrated in Figure 2.1). This results in a current pulse directly from  $V_{DD}$  to GND in a short period of time. The short circuit power depends on the transition time, the peak current and the supply voltage. However, the derivation of an exact formula for the short circuit power is not easy and by making simplifying assumptions closed-form expressions have been proposed in [3, 4, 5]. To reduce short circuit power dissipation, it is desirable to make the edge slope of transition as sharp as possible, e.g. by increasing the size of the driving gate.

Figure 2.1: Short circuit power dissipation in an inverter.

### 2.1.2 Static Dissipation

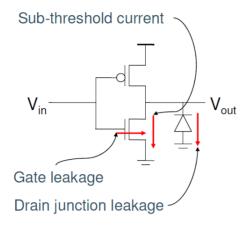

Static dissipation is caused by secondary effects (as illustrated in Figure 2.2) such as sub-threshold conduction, gate oxide tunneling, reversed biased diode leakage, etc. which lead to small amounts of current flowing through an OFF transistor. In 130 nm processes and beyond, the static power (a.k.a leakage power) has rapidly become a primary design issue which increases exponentially as process moves to finer technologies. This is primarily due to the scaling of threshold voltage  $V_{th}^{-1}$  resulting in orders of magnitudes increase in transistor's leakage current.

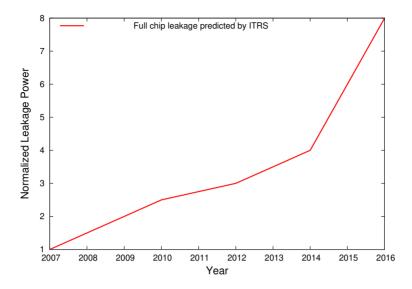

According to the International Technology Roadmap for Semiconductors (ITRS) [6], various low power techniques such as dynamic  $V_{th}$ , multiple  $V_{th}$  transistors, power domains/voltage islands, body bias, etc. will mitigate leakage until 2012. As the use of high- $\kappa$  dielectric<sup>2</sup> brings gate leakage under control, sub-threshold leakage is going to dominate and limit performance. Figure 2.3 shows the ITRS prediction of leakage in 2007 for the next decade.

The sub-threshold leakage current density, i.e. the current per unit transistor area, can be expressed by [7]:

$$J_{sub} = \frac{W}{L_{eff}} \mu \sqrt{\frac{q\epsilon_{si} N_{cheff}}{2\phi_s}} v_T^2 \exp\left(\frac{V_{gs} - V_{th}}{\eta v_T}\right) \left[1 - \exp\left(\frac{-V_{ds}}{v_T}\right)\right]$$

(2.4)

<sup>&</sup>lt;sup>1</sup>Threshold voltage is the voltage at which there are sufficient carriers to make a conducting path between source and drain of a transistor.

<sup>&</sup>lt;sup>2</sup>The silicon dioxide gate dielectric is replaced by a material with a higher dielectric constant  $\kappa$  (such as hafnium-based materials), which allows further device miniaturization.

Figure 2.2: Static power dissipation in an inverter.

where W is the width of the transistor,  $L_{eff}$  is the effective channel length,  $N_{cheff}$  is the effective channel doping,  $\phi_s$  is the surface potential,  $\eta$  is the subthreshold swing, and  $v_T$  is the thermal voltage.  $v_T$  is given by kT/q where k is the Boltzmann's constant, q is the electrical charge, and T is the junction temperature.

From Eq. (2.4), we can see that sub-threshold leakage current is an exponential function of the junction temperature T. At high operating temperatures, static dissipation can contribute a significant amount to the total power dissipation in CMOS circuits. In cache and other circuit components, where signal switching only occurs to a small portion of transistors at a time, static power can dominate over dynamic power. Reports indicate that 40% or even a higher percentage of the total power consumption in 90 nm process technology is due to leakage [8] and this percentage is expected to increase with technology scaling.

# 2.2 Design for Low Power

Design for low power has been one of the main research subjects in VLSI design for the past decades. Many proposed low power techniques are quite effective and over the years major library providers and Electronic Design Automation (EDA) tool vendors have integrated these techniques into their products. Standards for power intent specification such as Unified Power Format [9] (UPF) and

Figure 2.3: Full-chip leakage normalized to leakage power in 2007.

Common Power Format [10] (CPF) allow the specification of implementationrelevant power information in power aware design flows. Some of these techniques are general in nature and can be applied to most situations. Others require circuit designers to make decisions based on careful analysis of the various interacting factors. Low power techniques can be divided into those that reduce dynamic power and those that reduce static power.

### 2.2.1 Dynamic Power Reduction

The dynamic dissipation is governed by Eq. (2.3) and is reduced by decreasing the effective switching capacitance, the power supply or the operating frequency.

Clock gating [11, 12] is an effective method in reducing switching capacitance, which disables any changes to input registers of the idle part of a circuit. Clock gating can be applied at different granularities. Fine grained clock gating controls a small number of registers or even a single register and the area overhead due to extra control hardware can be high. On the other hand, coarse grained clock gating is applied to a large number of registers, probably also to portions of the clock tree since the clock tree itself consumes a significant amount of power due to the large activity factor. The disadvantage of coarse grained clock

gating is that it can only be applied when all the gated registers are idle, which can be infrequent in general.

Synthesis tools can also perform many power reduction techniques during logic synthesis such as operand isolation, logic restructuring and resizing, pin swapping, etc. to minimize the effective switching capacitance [13].

Intuitively, the most effective way of optimizing dynamic power would be to decrease the supply voltage  $V_{DD}$  as the reduction can be quadratic. A lower supply voltage can be used for cells not in the critical path without compromising a circuit's performance [14]. At the chip level, different blocks can have different speed requirements (e.g. peripheral interfacing circuitry can operate at a slower speed than the data processing circuitry) allowing effective power reduction through multiple supply voltages with no performance overhead. However, multivoltage design does introduce complexities especially for layout. Additional pins are required to connect all the supply voltages to the chip. The power grid has to distribute each of the power supplies separately to the appropriate blocks. The interfacing between different power domains has to ensure the correct signal levels by using level shifters.

Another technique that involves lowering supply voltage is dynamic voltage scaling (DVS) [15], which varies the speed of a circuit dynamically according to the timing requirement. A similar technique is dynamic frequency scaling (DFS) [16], which adjusts the clock frequency in order to save power. DVS and DFS are combined in some designs into dynamic voltage and frequency scaling (DVFS) [17].DVS and DFS can both be implemented either in hardware through circuit delay monitoring and matching or in software through operating system scheduling.

#### 2.2.2 Static Power Reduction

The static dissipation, unlike dynamic dissipation, is very much dependent on the manufacturing process (e.g. channel length, doping profile, etc.) and the operating environment (e.g. temperature, supply voltage, etc.). As can be seen from Eq. (2.4), at the circuit design level, the static dissipation can be reduced by increasing the threshold voltage  $V_{th}$  or decreasing the gate to source voltage  $V_{gs}$  (decreasing the drain to source voltage  $V_{ds}$  is impractical since static CMOS swings from rail to rail).

Transistor threshold voltage  $V_{th}$  is dependent on several parameters such as body doping profile, gate oxide thickness, body voltage, temperature, etc. Standard cell libraries usually offer more than one cells to implement each logic function,

each using a different transistor threshold voltage. Cells with a low threshold voltage (LVT cells) have a faster transition time but leak more sub-threshold current. Cells with a high threshold voltage (HVT cells) have less leakage but also a slower speed. Thus, leakage optimization can proceed in such a way that LVT cells are used sparingly in timing critical paths and HVT cells are used elsewhere to save standby power [18].

Alternatively, the threshold voltage can be controlled at runtime through applying a variable biasing voltage to the body from a control circuitry [19]. Reverse body bias (RBB) can be applied to increase the threshold voltage and thus reduce leakage when the circuit is in standby mode. During active mode, forward body bias (FBB) can be applied to speed up the circuit to match timing requirement. In this way, the circuit can be seen as implemented in transistors with adaptable or variable threshold voltages. In fact, the technique is also known as variable threshold CMOS (VTCMOS). The advantage of adaptive body biasing is that dynamiclly tuning the threshold voltage allows leakage reduction also at runtime. However, the technique requires a triple well process to achieve different body bias levels at different regions of the chip, which is quite expensive.

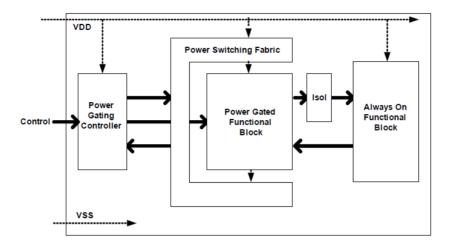

Another technique to reduce idle time leakage is power gating, also known as multiple threshold CMOS (MTCMOS), which cuts off power supply entirely to the idle part of a circuit [20]. Power gating uses low  $V_{th}$  transistors for computation and high  $V_{th}$  transistor as switches to disconnect the power supply during idle mode. Power gating is suitable for runtime behaviors with quite long idle periods (e.g. millions of clock cycles) and is very effective in reducing leakage power since the path from power supply to the ground is "cut-off".

Figure 2.4 illustrates a power gating design, where the controller controls the sequences when switching between power ON and power OFF mode. The power gated block is disconnected from supply rails by the power switching fabric. The isolation block insures any signal connected to the always-on block does not stay at intermediate signal levels when the power gated block is in OFF mode.

The technique also imposes several requirements to the design of standard cell libraries and physical implementation tools. For example, isolation cells and always-on cells have to be provided by the library in order to ensure signal integrity on the interface with non power gated domains. Any useful state information in memory elements (e.g. registers) has to be preserved during power down and correctly restored upon power on, which is usually accomplished by using state retention registers. State retention register is embedded with an always on low leakage shadow register that keeps the content of the main register during power gating. At the physical implementation stage, cells in the same power gating domain can be clustered in the layout as much as possible in order to minimize the number of switch cells, which are usually large area. Power

Figure 2.4: Block diagram of a SoC with Power Gating (from [21]).

gating also introduces virtual supply rails and complicates the design of power networks.

### 2.3 Heat Transfer and Distribution

The dissipated power in a VLSI circuit is manifested in the form of heat. In the context of a MOSFET, when a signal transition occurs, the applied voltage leads to a lateral electric field, which accelerates the charge carriers to move from source to drain. The charge carriers that gained kinetic energy release part of the energy whenever colliding with other carriers and atoms causing vibrations of these particles and consequently a rise in the temperature. In this way, electrical energy due to power consumption in CMOS circuit is transformed to heat.

Two sources of heat generation exist in a CMOS circuit: cells and interconnects. Power consumption in cells is composed of dynamic and static dissipation as described in the previous section. Power consumption in interconnects is caused by the flow of a small amount of current that charge and discharge the parasitic capacitance in the interconnect during signal transition.

The small amount of current flow can result in significant temperature rise in

metal wires, which is widely known as self-heating, due to the low- $\kappa$  dielectric materials used in modern processes. However, self-heating is less related to substrate temperature distribution than reliability issues in metal wires such as electromigration. Due to the much smaller electrical resistance in interconnects, the major source of heat generation is the power dissipation in cells on the device layer.

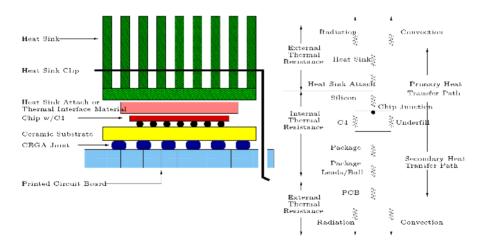

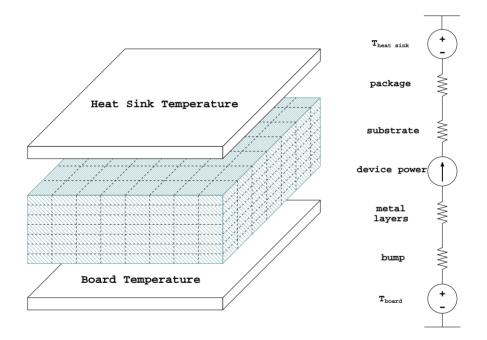

For a flip-chip design<sup>3</sup>, most of the heat generated from the transistor junctions is dissipated to the ambient environment through the heat sink attached to the back side of the substrate, which constitutes the primary heat transfer path. A small amount of heat is also conducted through interconnect layers and pads to the packaging and printed circuit boards (PCB). Figure 2.5 shows a typical flip chip design with a cross-sectional view of the PCB, packaging and a heat sink. The heat sink is attached to the backside of the substrate through thermal interface materials (TIM) and the wire leads are connected to the PCB through C4 and CBGA Joint. The system is modeled as a network of thermal resistors which shows the major heat dissipation paths. The heat is mainly transferred through conduction within the system and through radiation and convection to the ambient.

Figure 2.5: Heat dissipation paths of a chip (from [22]).

To describe the relationship between power consumption and junction temper-

<sup>&</sup>lt;sup>3</sup>Flip-chip, also called Controlled Collapse Chip Connection (C4), is a method where the surface of the chip is covered with an array of pads on the top of metal. The chip is flipped upside down and in nearly direct contact with the package, eliminating the inductance associated with the bond wires [2].

ature, a first order expression can be expressed as:

$$T_j = T_a + P_{chip} \times R_{ja} \tag{2.5}$$

where  $T_a$  is the temperature of ambient environment (e.g. temperature of air in side the chassis of a desktop computer),  $P_{chip}$  is the total power consumption inside the chip,  $R_{ja}$  is the junction to ambient thermal resistance and  $T_j$  is the derived junction temperature. As illustrated in Figure 2.5,  $R_{ja}$  can be modeled as the series resistance from junction to ambient in different parts of the chip. Analogous to electrical resistance, thermal resistance can be defined as:

$$R = \frac{L}{k \times A} \tag{2.6}$$

where k is the material's thermal conductivity, L is the length and A is the cross-sectional area of the conducting path.

Substituting Eq. (2.6) into Eq. (2.5), we get:

$$T_j = T_a + P_{chip} \times \frac{L}{k \times A} \tag{2.7}$$

To a circuit designer, L and k are process and package dependent parameters and  $T_a$  is determined by the operating environment. Consequently,  $T_j$  is closely related to the ratio between  $P_{chip}$  and A which defines the power density of the chip.

Due to the large variation of power density in different regions on the die, significant temperature difference between different regions (typically referred to as thermal gradients) usually exists on the substrate layer. The one dimensional first order expression in Eq. (2.5) is incapable to capture the temperature difference within the chip.

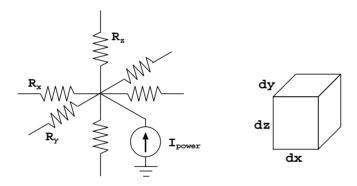

In general, the heat diffusion equation is used to describe the rate of heat conduction in a chip:

$$q = -k_t \nabla T \tag{2.8}$$

which states that heat flux, q (in  $W/m^2$ ), is proportional to the negative gradient of temperature, T (in K), with the constant of proportionality corresponding to the thermal conductivity of the material,  $k_t$  (in W/(mK)).  $k_t$  is in general temperature dependent, however the variation is not significant. For on chip thermal analysis,  $k_t$  can be treated as constant for each type of material.

The divergence of q is the difference between the power generated and the time rate of change of heat as described in Eq. (2.9),

$$\nabla \cdot q = -k_t \nabla \cdot \nabla T = -k_t \nabla^2 T = g(\mathbf{r}, t) - \rho c_p \frac{\partial T(\mathbf{r}, t)}{\partial t}$$

(2.9)

where  $\mathbf{r}$  is the spatial coordinate of the point at which the temperature is being determined, g is the power density of the heat source (in  $W/m^3$ ),  $c_p$  is the heat capacity of the material (in J/(kgK)) and  $\rho$  is the density of the material (in  $kg/m^3$ ). This heat diffusion equation(Eq. (2.9)) can be rewritten as,

$$\rho c_p \frac{\partial T(\mathbf{r}, t)}{\partial t} = k_t \nabla^2 T + g(\mathbf{r}, t)$$

(2.10)

Eq. (2.9) is subject to the boundary condition,

$$-k_t \frac{\partial T(\mathbf{r}, t)}{\partial n} = h_c (T_{\mathbf{r}, t} - T_a)$$

(2.11)

which states that the heat generated inside the chip equals the heat dissipated to the ambient.

The time constant of on-chip heat conduction is in milliseconds, which is much larger than the clock periods in nanoseconds. This means transient currents with short time constants do not have significant impact on temperature distribution. If the power profile of a circuit does not change within an extended period of time, steady-state analysis can capture the thermal behavior of the circuit accurately [22]. Steady state thermal analysis determines temperature distribution when power density distribution does not change over time, which is sufficient for applications with stable power profiles or periodically changing power profiles that cycle quickly [23]. Thus to obtain steady state temperature profile, single average power for different location of the circuit can be used.

Eq. (2.10) can be solved numerically using one of several solution frameworks for partial differential equations. The Finite Difference Method (FDM) and the Finite Element Method (FEM) both discretize the chip and form a system of linear equations relating the temperature distribution to the power distribution. Many research work based their optimization on thermal simulators using the FDM or the FEM methods [24, 25, 26, 27]. The work in [28] proposed a compact thermal model for architectural thermal analysis, which based on the electrical-thermal analogy creates a coarse grained RC network of functional blocks and the package. The resulting matrix equations are then solved using LU decomposition to obtain a steady-state thermal analysis.

For full chip thermal analysis, in order to achieve high resolution the number of linear equations resulted from the FDM discretization can be huge. The multigrid algorithm was successfully used in [23, 29] to solve the problem and shown to be more efficient than other methods such as Gauss-Seidel iteration, conjugate gradient method, etc. The multigrid method follows a hierarchical approach and is based on the observation that an iterative solver is usually

more effective in removing high frequency solution errors in a FDM mesh than low frequency errors. Therefore, a hierarchy of mesh grids with multilevel granularities are constructed. The method starts with iterating over the finest grid and once the convergence deteriorates due to low frequency errors it changes to the coarser grid where the low frequency errors are removed through coarse grid correction. Once the solution to the coarser grid is obtained, it is mapped back to the finer grid through interpolation. The overall runtime is observed to be linear with the number of nodes in the finest mesh grid.

An alternative to the FDM and FEM methods is a boundary element method using Green functions [30, 31]. In this method, only layers of heat sources or layers of thermally interest are analyzed, thus resulting in a smaller problem size than FDM and FEM. However, the method is based on the assumption that chip materials are layer-wise uniform and consequently is more suitable for early stage analysis where efficiency is more in favor than accuracy. An improved method in [32] reduces the complexity in Green function based methods by recognizing the bottleneck corresponds to a convolution operation.

# 2.4 Technology Scaling and Thermal Issues

Eq. (2.5) shows that junction temperature depends on power consumption and thermal resistance. With manufacturing process scaled to finer geometries, power consumption in a single transistor decreases. Thermal resistance for a single transistor, on the other hand, increases due to the reduction in the transistor's geometrical size [33]. Transistor's temperature in a new process is thus dependent on the relative rate of changes of the two parameters.

To estimate full chip temperature increase in a new process, one also has to take into account the increase in transistor density. In [22], the authors using industrial technology data and ITRS prediction for future technologies showed that the normalized temperature increase of a chip is significantly elevated when CMOS technology scaled from 350 nm to 90 nm. The estimated junction temperature of a 90 nm process CMOS chip is about 4.5 times higher than that of a 350 nm process CMOS chip.

The rapid increasing junction temperature can affect several aspects of circuit design as many CMOS circuit parameters are temperature dependent. The carriers mobility of a transistor decreases with increasing temperature which lowers the drive current and leads to increased delays. On the contrary, transistor's threshold voltage decreases with temperature which improves transistor switching time. The performance of a transistor is therefore dependent on which of the

two factors dominate. The unit resistance of a wire segment increases with temperature, which makes the delay on wires especially global wires very sensitive to high temperature [34].

The unevenly distributed heat caused by large spatial variations in power consumption at different locations can make performance analysis difficult. Thermally induced device mismatch is a major concern in high speed and high precision IC design such as clock distribution networks, Arithmetic Logic Units (ALU), data converters, amplifiers, etc. Containing temperature and thermal gradient is also critical to the design of mixed signal and analog ICs as they are more sensitive to temperature.

Sub-threshold leakage, as described in Section 2.1 has an exponential dependence on temperature [7]. It has been shown in [35] that for every 30 °C increase in temperature, the amount of leakage more than doubles. The induced leakage in turn increases total power consumption and causes further temperature rise. If the cooling system is inadequate to remove the generated heat fast enough, the positive feedback loop between temperature and leakage will eventually cause thermal runaway and burn down the chip.

Temperature is a vital factor in microelectronics system's reliability [36]. Higher junction temperature reduces mean time to failure (MTTF) for the devices, which has a direct impact on the overall system reliability. It is reported in [37] that a small increase in operating temperature  $(10-15\,^{\circ}\mathrm{C})$  can decrease the lifespan of devices by 2 times. Many physical effects that cause reliability degradation are thermally activated processes [38, 39, 40]. Negative Biased Temperature Instability (NBTI) and Hot Carrier Injection (HCI) effects, which are strongly dependent on temperature, degrade the performance of transistors in an irreversible manner over time. These effects reduce a circuit's lifetime and cause timing violations eventually. Other failure mechanisms such as electromigration, stress migration and dielectric breakdown are accelerated by high temperature and temperature gradients and cause permanent device failures [41]. According to ITRS [6], the junction temperature of a semiconductor device must be kept at 85 °C or lower to ensure long term reliability.

All these factors dictate that the excessive heat generated from the circuit must be dissipated to the ambient at a reasonable speed and the circuit should be operated within a specified temperature range.

# 2.5 Thermal Management Techniques

Although the elevated temperature is caused by the increasing power consumption in a chip, effective power management methods may not be as useful for thermal management. The key differences between power reduction techniques and temperature reduction techniques can be classified into several aspects.

First, power dissipation is in general spatially nonuniform across a chip and thus temperature in local hotspots can increase much faster than full chip heating. If the high power density in hotspots is effectively reduced, a chip can dissipate the same amount or even more total power at a lower peak temperature. Power management performs a *minsum* optimization, which monitors full chip power consumption and attempts to lower the total energy consumed over an entire application run. In contrast, thermal management is a *minmax* optimization problem, where peak temperature at specific localized hotspots and full chip thermal gradient are of main concern.

Second, heat distribution within a circuit evolves over timescales of hundreds of microseconds while power dissipation changes every clock cycle, which is in nanoseconds. Consequently, low power techniques that reduce power dissipation at a very short timing granularity do not have effect in reducing temperature.

Although a vast literature on techniques to reduce power does exist, as we have seen in Section 2.2, not all low-power design solutions are effective for reducing temperature. For this reason, recent research has focused on specific solutions for *thermal management* ([42, 43, 44, 45, 46]), in which temperature and not power is the actual metric.

To perform thermal management within a circuit, techniques explicitly targeting the spatio-temporal thermal behavior are needed. Thermal management can be divided into design time and run time techniques based on the timing of activation.

# 2.5.1 Design Time Solutions

Design time thermal management involves the spatial arrangement of circuit structures in such a way that the maximum local power density is reduced. These structures are functional blocks at the chip level and individual gates at the block level. Placing high power consumption structures away from each other can reduce the thermal coupling and flatten out the die's thermal profile.

In [47], an isothermal logic partitioning technique was proposed. This method iteratively optimizes the thermal profile of a placed netlist by building isothermal logical clusters and then partitioning the hottest clusters into two parts. In this way, hotspots are split apart and can be placed close to cool cells. For standard cell based synthetic benchmarks, the algorithm achieved on average 5.54% and 9.9% in peak temperature reduction with a timing overhead of 5% and 10% respectively.

Many thermal aware floorplanning and placement algorithms were also proposed, typically using peak temperature as one component of the cost function when evaluating the quality of a candidate solution. In [48], a system level leakage aware floorplanner (LEAF) was proposed. The method also models the positive feedback loop between temperature and leakage in a simulated annealing based floorplanning algorithm. For each type of transistor in the library, a temperature leakage correlation table is generated from SPICE simulation. Within the annealing, an initial estimate of the leakage is used to determine the temperature, which in turn updates the leakage. The feedback loop between the leakage and the temperature continues until steady-state temperature is reached. The new floorplan is evaluated in terms of total leakage power and other metrics such as area and total wirelength.

In recent years, temperature variation induced clock skew in the clock distribution network has become prominent. In [49, 50], the authors described design time clock tree synthesis algorithms to take counter measures against nonuniform substrate thermal profile. While in [51], the optimal insertion of tunable delay buffers into clock trees, to adjust at run time the delay of clock distribution paths that are more susceptible to temperature variations, is discussed. Thermal aware global routing algorithms for improving reliability are also proposed in [52, 53].

The advantage of design time techniques is that they are applied during the physical implementation stage and the incurred performance overhead can usually be optimized. On the other hand, the solution is static and does not adapt to changes in thermal behaviors such as the shifting of locations of hotspots at run time.

#### 2.5.2 Run Time Solutions

Run time thermal management is also called dynamic thermal management (DTM) as they are performed dynamically when applications are running. DTM monitors chip temperature through thermal sensors and triggers response mechanisms. Reactive DTM activates responsive mechanisms once the peak temperature.

ature or thermal gradient exceeds predefined thresholds, while the timing of activation in proactive DTM is based on predictions of future temperatures. Response mechanisms include dynamic power reduction techniques like DVFS, power gating and clock gating as described in Section 2.2, and architectural adaptation methods like clock throttling, limiting the issue width in multiple issue processors, task migration in multicore systems, etc.

In [54, 55, 56], the authors studied the reductions in hotspots and spatialtemporal thermal gradients using static and dynamic task scheduling methods. The DTM schemes considered in [55] are thread migration and voltage scaling and the proposed scheduler is compared against load balancing schedulers, which are typically found in multi-core operating systems. To avoid significant performance degradation a probabilistic policy (Adaptive-Random) determines between load balancing and DTM schemes. The results showed that the proposed methods can effectively reduce hotspots with a performance overhead between 2.4% and 15.0% for different approaches. In [56], the authors proposed a proactive thermal management approach, which can estimate future temperature based on a moving window of temperature history. The robustness and accuracy of the method are achieved through adapting the model parameters according to the dynamic workload and temperature measurements at runtime. In [57], the authors proposed a thermal balancing policy specifically designed for multiprocessor stream computing applications. The experiment results showed that the proposed policy achieved thermal balance between cores at a performance cost less than general DTM schemes such as DVFS, Stop&Go, etc.

The advantage of run time thermal management is that it can adapt to dynamic thermal behaviors and is suitable for applications where the workload on blocks varies overtime as in the case of a microprocessor. The disadvantage is that these techniques are usually complex to implement and the performance overhead due to the triggering of DTM can be significant. For example, DVS requires to stall between 10 - 50  $\mu$ s for the resynchronization of the clock's phase-locked loop [58]. Furthermore, aggressive DTM might introduce additional thermal stress-relax cycles that cause mechanical stress and impact system reliability and thus requires careful analysis.

# **Floating Point Units**

Floating-point units (FPU) could be a good case study for power and thermal aware design. FPUs are found in a wide variety of processors ranging from server and desktop microprocessors, graphic processing units (GPU), to digital signal processors (DSPs), mobile Internet devices and embedded systems. In NVIDIA's latest CUDA architecture Fermi, each streaming multiprocessor contains 32 FPUs totaling 512 of them in a single GPU. Floating-point operations are much more complex than their integer and fixed-point counterparts. Consequently, FPUs usually occupy a significant amount of silicon area and can consume a large fraction of power and energy in a chip. For scientific and graphics intensive applications, the high power consumption in FPU can make it the hotspot on the die.

In this chapter, we give a brief overview of the floating-point representation and the arithmetic operations on floating-point numbers, namely add/subtract, multiply, fused multiply-add and divide. For each operation, we illustrate the basic steps necessary to perform the operation in hardware and an example implementation. In particular, the division operation is implemented using several alternative algorithms. In Chapter 6, we compare the different implementations of division in terms of power and energy consumption and discuss FPU design from an energy and a thermal perspective.

# 3.1 Floating-Point Representation

A floating-point representation is used to represent real numbers in a finite number of bits. Since the set of real numbers is infinite, it is only possible to exactly represent a subset of real numbers in the floating-point representation. The rest of the real numbers either fall outside the range of representation (overflow or underflow) or are approximated by other floating-point numbers (roundoff). The most used representation is sign-and-magnitude, in which case a floating-point number x is represented by a triple  $(S_x, M_x, E_x)$ :

$$x = (-1)^{S_x} \times M_x \times b^{E_x} \tag{3.1}$$

where  $S_x \in \{0, 1\}$  is the sign,  $M_x$  denotes the magnitude of the significand, b is a constant called the base and  $E_x$  is the exponent.

A floating-point representation system involves many parameters and historically many floating-point processors were designed using a variety of representation systems. To avoid incompatibilities between different systems, the IEEE Floating-point Standard 754 was developed, which is followed by most floating-point processors today. The latest version of the standard (IEEE 754-2008 [59]) defines the arithmetic formats of binary and decimal floating-point numbers as well as arithmetic and other operations that perform on these numbers. We briefly summarize the main components of the IEEE Standard 754 for binary numbers in this section.

#### 3.1.1 Formats

The magnitude of the significand  $M_x$  is represented in radix 2 normalized form with one integer bit:

where F is called the fraction and the leading 1 is called the hidden bit. The exponent  $E_x$  is base 2 and in biased representation with

$$B = 2^{e-1} - 1$$

where e is the number of bits of the exponent field. Denormalized numbers  $(E_x = 0 \land F \neq 0)$  do not have a leading 1 in the hidden bit. Consequently, the value of a normal floating-point number represented in the IEEE format can be obtained as:

$$x = (-1)^{S_x} \times 1.F_x \times b^{E_x - B} \tag{3.2}$$

The three components are packed into one word with the order of the fields in S, E and F. The system defines three basic binary floating-point formats:

- binary16 (Half): S(1), E(5), F(10).

- binary32 (Single): S(1), E(8), F(23).

- binary64 (Double): S(1), E(11), F(52).

## 3.1.2 Rounding

The standard defines five rounding algorithms:

- Round to nearest: Round to nearest, ties to even (default); Round to nearest, ties away from zero.

- Directed: Round toward 0 (truncated); Round toward  $+\infty$ ; Round toward  $-\infty$ .

## 3.1.3 Operations

Required operations include:

- Numerical: add, subtract, multiply, divide, remainder, square root, fused multiply-add, etc.

- Conversions: floating to integer, binary to decimal (integer), binary to decimal (floating), etc.

- Miscellaneous: change formats, test and set condition flags, etc.

# 3.1.4 Exceptions

The standard defines five exceptions, each of which sets a corresponding status flag when raised and by default the computation continues.

- overflow (result is too large to be represented).

- underflow (result is too small to be represented).

- division by zero.

- inexact result (result is not an exact floating-point number).

- invalid operation (when a Not-A-Number result is produced).

In the following sections, we describe the algorithm and implementation for floating-point operations. In specific, the operations described are: add/subtract, multiply, fused multiply-add and divide. Of all these operations, division is more complex and we will present several algorithms and implementations for the division operation.

For each operation, we first present a high level description of the steps to be performed in generic form. We assume the operands and results are represented in the triple (S, M, E) as described in the previous section. To simplify the description of algorithms, let  $M^* = (-1)^S M$  represent the signed significand. A hardware implementation of the operation is then given to illustrate the execution of different algorithms.

# 3.2 Floating-Point Addition

The addition/subtraction is described in the following expression:

$$z = x \pm y$$

The high level description of this operation is composed of the following steps:

1. Add/subtract significands and set exponent.

$$M_z^* = \begin{cases} (M_x^* \pm (M_y^* \times b^{(E_y - E_x)})) \times b^{E_x} & \text{if } E_x \ge E_y \\ \\ ((M_x^* \times b^{(E_x - E_y)}) \pm M_y^*) \times b^{E_y} & \text{if } E_x < E_y \end{cases}$$

$$E_z = \max(E_x, E_y)$$

- 2. Normalize significand and update exponent.

- 3. Round, normalize and adjust exponent.

- 4. Set flags for special cases.

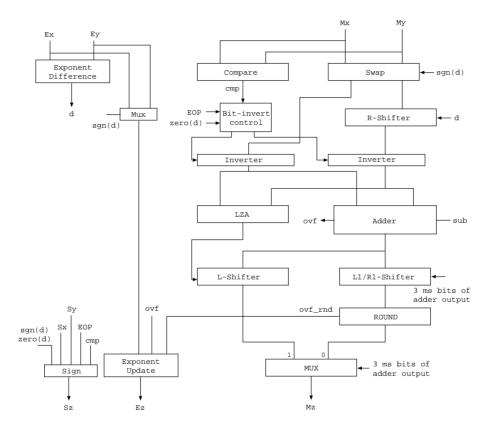

A single path implementation of the floating-point add operation is shown in Figure 3.1 from [60], where a more detailed description of the unit is given. To

Figure 3.1: Single path floating-point addition.

avoid having two alignment shifters, the operands are swapped according to the sign of the exponent difference. A two's complement adder performs the sign-and-magnitude addition in step 1. When the effective operation is subtraction (determined by the operation and the signs of the operands), the smaller operand is complemented by bit-inversion plus carry-in to the adder. This is to avoid complementing the output of the adder when the result is negative. The leading zero anticipation (LZA) unit determines the position of the leading one in the result in parallel with the addition.

In the normalization step, two cases can occur. In the first case, the effective operation is subtraction and the output of the adder has many leading zeros, which requires a massive left shift of the result and no roundup is necessary since the exponents difference is less than 2 and no initial massive right shift was performed. In the second case, the output of the adder contains only one leading zero or has an overflow due to addition. In this case, a shifting of only one position to the left or to the right is required and subsequently a roundup is necessary. The two cases can be designed into separate paths in order to reduce the latency in both paths [61].

# 3.3 Floating-Point Multiplication

The multiplication of two floating-point numbers x and y is defined as:

$$z = x \times y$$

The high level description of this operation is composed of the following steps:

1. Multiply significands and add exponents.

$$M_z^* = M_x^* \times M_y^*$$

$$E_z = E_x + E_y + B$$

- 2. Normalize  $M_z^*$  and update exponent.

- 3. Round.

- 4. Determine exception flags and special values.

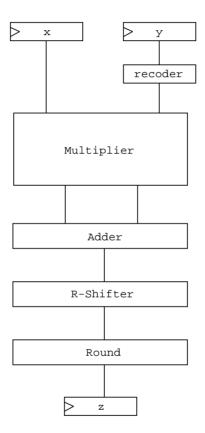

The basic implementation of floating-point multiplication is shown in Figure 3.2. For the sake of simplicity, we only show the data paths for the significands in

Figure 3.2: Implementation of floating-point multiplication (significands only).

block diagrams. Parallel multiplication (combinational) is a three steps computation [60]. We indicate with

$$z = x \times y$$

the product z (n + m bits) of a n-bit operand x and a m-bit operand y.

1. First, m partial products

$$z_i = 2^i x \cdot y_i \qquad i = 0, \dots, m - 1$$

are generated. Because  $y_i = \{0, 1\}$ , this step can be realized with a  $n \times m$  array of AND-2 gates<sup>1</sup>

2. Then, the m partial products are reduced to 2 by an adder tree

$$\sum_{i=0}^{m-1} 2^i x \cdot y_i = z_s + z_c \ .$$

3. Finally, the carry-save product  $z_s$ ,  $z_c$  is assimilated by a carry-propagate adder (CPA).

$$z = z_s + z_c$$

.

The delay in the adder tree and its area depend on the number of addends to be reduced (m:2). By radix-4 recoding the multiplier y, often referred as Booth's recoding, the number of partial products is halved  $\frac{m}{2}$ . As, a consequence the multiplier's adder tree is smaller and faster. However, in terms of delay, the reduction in the adder tree is offset by a slower partial product generation, due to the recoding [60]. On the other hand, the reduction in area is significant, and the power dissipation is reduced as well due to both the reduced capacitance (area) and the nodes' activity because sequences of 1's are recoded into sequences of 0's resulting in less transitions.

The significand of the product might have an overflow in which case it is necessary to shift the result one position to the right and increment the exponent. Finally, rounding is performed according to the specified mode.

# 3.4 Floating-Point Fused Multiply-Add

The fused multiply-add (FMA) operation is a three operand operation defined by the following expression:

$$z = a + b \times c$$

<sup>&</sup>lt;sup>1</sup>Shifting  $(2^i)$  is done by hard-wiring the AND-2 array's output bits.

The high level description of this operation is composed of the following steps:

- 1. Multiply significands  $M_b^*$  and  $M_c^*$ , add exponents  $E_b$  and  $E_c$ , and determine the amount of alignment shift of a.

- 2. Add the product of  $M_b^* \times M_c^*$  and the aligned  $M_a^*$ .

- 3. Normalize the adder output and update the result exponent.

- 4. Round.

- 5. Determine exception flags and special values.

The multiply-add operation is fundamental in many scientific and engineering applications. Many commercial processors include a FMA unit in the floating-point unit to perform double precision floating point fused multiply-add operation as a single instruction. The main advantages of the fused implementation over the separate implementation of multiplication and addition are:

- The high occurrence of expressions of that type in scientific computation, and the consequent reduction in overhead to adjust the operands from the IEEE format to the machine internal representation (de-normalization, etc.).

- Improvement in precision, as the result of multiplication is added in full precision and the rounding is performed on  $a + b \times c$ .

The drawback is that if a large percentage of multiply and add cannot be fused, the overhead in delay and power is large especially for addition.

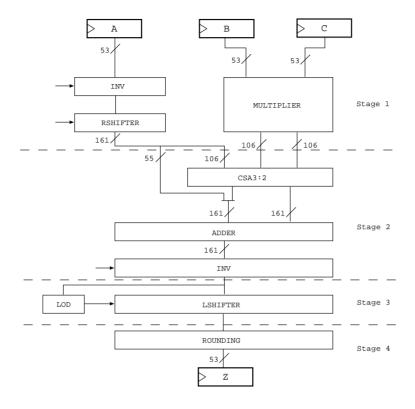

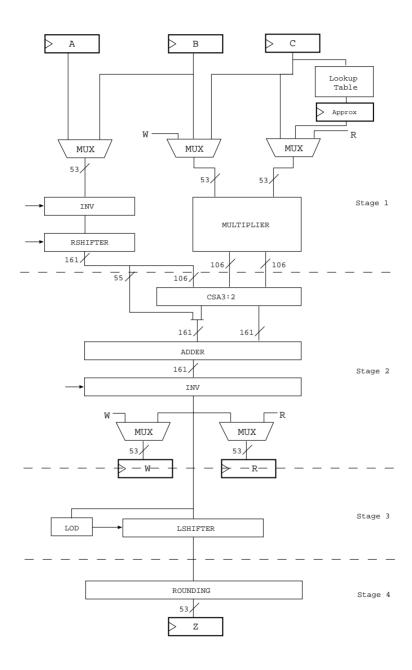

The architecture of an FMA unit for binary64 (double precision) significands, shown in Figure 3.3, is derived from the basic scheme in [60] and [62]. Registers A, B and C contain the input operands and register Z contains the final result. To prevent shifting both a and the product of b and c, a is initially positioned two bits to the left of the most significant bit (MSB) of  $b \times c$  so that only a right shift is needed to align a and the product. The zero bits inserted in the two least-significant (LS) positions are used as the guard and round bits when the result significand is a. The amount of shift depends on the difference between the exponents of a and  $b \times c$ . Moreover, a is conditionally inverted when the effective operation is subtraction.

A Booth encoded tree multiplier computes the product of b and c and the result is output in carry-save format to be added with the shifted a. Since the product

Figure 3.3: Scheme of an FMA unit (significands only).

has 106 bits, only the 106 LSBs of the shifted a are needed in the carry-save adder (CSA). The 55 MSBs of the shifted a are concatenated with the sum of the CSA to form input to the adder. Since the carry in the output of the CSA has 106 bits, only one of the input to the adder has 161 bits.

Consequently, the leftmost 55 bits portion of the adder is implemented as an incrementer with the carry-out of the lower part as the increment input. The adder also performs end-around-carry adjustment for effective subtraction. As the result might be negative, an array of inverters is required at the output of the adder.

Once the result of the addition is obtained, the amount of normalization shift is determined by the leading one detector (LOD). No right shift for normalization is required due to the initial position of a.

To increase throughput, the FMA unit is implemented in a four-stage pipeline. The position of the pipeline registers is indicated with dashed horizontal lines in Figure 3.3.

The FMA unit can be used to perform floating point addition by making b = 1 (or c = 1) and multiplication by making a = 0.

# 3.5 Floating-Point Division

The division operation is defined by the following expressions:

$$x = q \cdot d + rem$$

and

$$|rem| < |d| \cdot ulp$$

and  $sign(rem) = sign(x)$

where the  $dividend\ x$  and the  $divisor\ d$  are the operands and the results are the  $quotient\ q$  and the  $remainder\ rem$ .

The high-level description of the floating-point division algorithm is composed of the following steps:

1. Divide significands and subtract exponents.

$$M_a^* = M_r^* / M_d^*$$

$$E_q = E_x - E_d - B$$

- 2. Normalize  $M_q^*$  and update exponent accordingly.

- 3. Round.

- 4. Determine exception flags and special values.

Division is implemented in hardware in all general purpose CPUs and in most processors used in embedded systems. Several classes of algorithms exist to implement the division operation in hardware, the most used being the digit recurrence method, the multiplicative method and various approximation methods.

In the following we briefly review these algorithms and implementations. Due to the differences in the algorithms, a comparison among their implementation in terms of performance and precision is sometimes hard to make. In Chapter 6, we will use power dissipation and energy consumption as metrics to compare among these different classes of algorithms.

# 3.5.1 Division by Digit Recurrence

The digit-recurrence algorithm [63] is a direct method to compute the quotient of the division

$$q = \frac{x}{d} + rem$$

The radix-r digit-recurrence division algorithm is implemented by the residual recurrence

$$w[j+1] = rw[j] - q_{j+1}d$$

$j = 0, 1, ..., n$

with the initial value w[0] = x. The quotient-digit  $q_{j+1}$ , normally in signed-digit format to simplify the selection function, provides  $\log_2 r$  bits of the quotient at each iteration. The quotient-digit selection is

$$q_{j+1} = SEL(d_{\delta}, y)$$

$q_{j+1} \in [-a, a]$

where  $d_{\delta}$  is d truncated after the  $\delta$ -th fractional bit and the estimated residual,  $y = rw[j]_t$ , is truncated after t fractional bits. Both  $\delta$  and t depend on the radix and the redundancy (a). The residual w[j] is normally kept in carry-save format to have a shorter cycle time.

The divider is completed by a on-the-fly convert-and-round unit [63] which converts the quotient digits  $q_{j+1}$  from the signed-digit to the conventional representation, and performs the rounding based on the sign of the remainder computed by a sign-zero detect (SZD) block. The conversion is done as the digits are produced and does not require a carry-propagate adder.

The digit-recurrence algorithm is quite a good choice for the hardware implementation because it provides a good compromise between latency, area and power and rounding is simple (the remainder is computed at each iteration). A radix-4 division scheme is implemented in Intel Pentium CPUs [64], in ARM processors [65] and in IBM FPUs [66].

## Radix-4 Division Algorithm

We now briefly summarize the algorithm for radix-4 with the quotient digit selected by comparison [65]. The radix-4 recurrence is

$$w[j+1] = 4w[j] - q_{j+1}d$$

$j = 0, 1, ..., n$

with  $q_{j+1} = \{-2, -1, 0, 1, 2\}.$

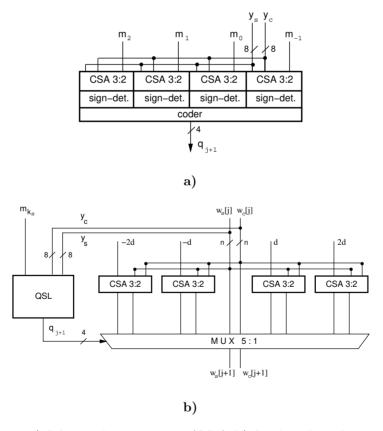

The quotient-digit  $q_{j+1}$  is determined by performing a comparison of the truncated residual  $y = \widehat{4w[j]}$  (carry-save) with the four values  $(m_k)$  representing the boundaries to select the digit for the given d. That is,

This selection can be implemented with a unit (QSL) similar to that depicted in Figure 3.4.a where four 8-bit comparators (sign-det.) are used to detect in which range y lies. The coder then encodes  $q_{j+1}$  in 1-out-4 code which is suitable to drive multiplexers.

Figure 3.4: a) Selection by comparison (QSL). b) Single radix-4 division stage.

In parallel, all partial remainders  $w^k[j+1]$  are computed speculatively (Figure 3.4.b), and then one of them is selected once  $q_{j+1}$  is determined.

The critical path of the unit in Figure 3.4 is

$$t_{REG} + t_{CSA}^{QSL} + t_{8b-CPA}^{QSL} + t_{buffer} + t_{MUX}$$

#### Intel Penryn Division Unit

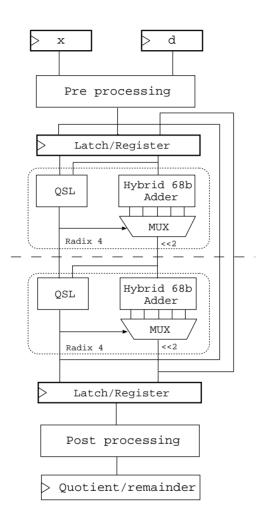

The division unit implemented in the Intel Core2 (Penryn) family is sketched in Figure 3.5 [64]. It implements IEEE binary32/binary64 compliant division, plus extended precision (64 bits significand) and integer division. The unit consists of three main parts: the pre-processing stage necessary to normalize integer operands to ensure convergence; the recurrence stage; and the post-processing stage where the rounding is performed.

The recurrence is composed of two cascaded radix-4 stages synchronized by a two-phase clock to form a radix-16 stage (4 bits of quotient computed) over a whole clock cycle. Each radix-4 stage is realized with a scheme similar to that of [65] shown in Figure 3.4.

This scheme was selected by Intel because of the reduced logical depth. However, the speculation on the whole w-word (54 bits for [65], 68 bit for the Core2 format) is quite expensive in terms of area and power dissipation.

According to [64], a maximum of 6+15=21 cycles are required to perform a division on binary64 (double-precision) operands.

#### Radix-16 by Overlapping Two Radix-4 Stages

An alternative to the Penryn solution, is to have a radix-16 divider obtained by overlapping (and not cascading) two radix-4 stages. In this scheme, the speculation is applied to the narrower y-path as explained next. Examples of radix-16 dividers by radix-4 overlapping are reported in [63] and [67].

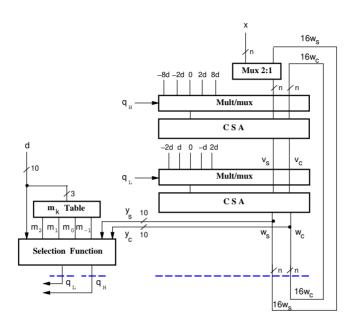

The radix-16 retimed recurrence, illustrated in Figure 3.6.a, is

$$v[j] = 16w[j-1] - q_{Hj}(4d)$$

$w[j] = v[j] - q_{Lj}d$

with  $q_{Hj} \in \{-2, -1, 0, 1, 2\}$ ,  $q_{Lj} \in \{-2, -1, 0, 1, 2\}$ , and w[0] = x (eventually shifted to ensure convergence). In Figure 3.6.a, the position of the registers is indicated with a dashed horizontal line. The recurrence is retimed (the selection function is accessed at the end of the cycle) to increase the time slack in the

Figure 3.5: Architecture of Penryn divider (significands only).

bits of the wide w-path (at right) so that these cells can be redesigned for low power [67].

The block QSL in Figure 3.6.b is the same as that of Figure 3.4.a. In this case, while  $q_H$  is computed, all five possible outcomes of  $q_L$  are computed speculatively. Therefore the computation of  $q_L$  is obtained with a small additional delay.

The total number of iteration to compute a binary64 division, including initialization and rounding, is 18.

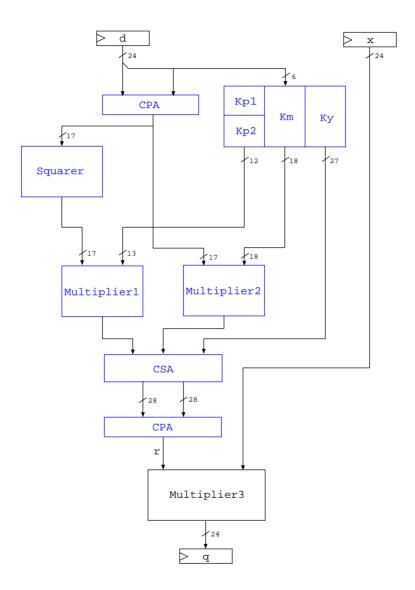

# 3.5.2 Division by Multiplication

The quotient q of the division can also be computed by multiplication of the reciprocal of d and the dividend x

$$q = \frac{1}{d} \cdot x$$

This is implemented by the approximation of the reciprocal R = 1/d, followed by the multiplication  $q = R \cdot x$ .

By determining R[0] as the first approximation of 1/d, R can be approximated in m steps by the Newton-Raphson (NR) approximation [60]

$$R[j+1] = R[j](2 - R[j]d)$$

$j = 0, 1, ..., m$

Each iteration requires two multiplications and one subtraction. The convergence is quadratic and the number of iterations m needed depends on the initial approximation R[0], which is usually implemented by a look-up table.

Once R[m] has been computed, the quotient is obtained by an additional multiplication  $Q = R[m] \cdot x$ . To have rounding compliant with IEEE standard, extra iterations are required to compute the remainder and perform the rounding according to the specified mode [60]:

- rem = Qd x

- q = ROUND(Q, rem, mode).

The NR algorithm for binary64 division (m=2) with an initial approximation of 8 bits is summarized below.

2d

CSA

\* \*

QSL

M<sub>Ks</sub> y<sub>s</sub> y<sub>c</sub> -2d -d d

10 10 10

8 8 8 CSA CSA

QSL QSL QSL QSL

b)

**a**)

Figure 3.6: a) Recurrence radix-16. b) Overlapped selection function.

MUX

4

q<sub>L</sub>

```

R[0] = LUT(d);

FOR i := 0 T0 2 LOOP

W = 2 - d * R[i];

R[i+1] = R[i] * W;

END LOOP;

Q = x * R[3];

rem = x - d * Q;

q = ROUND(Q,rem,mode);

```

Although division by iterative multiplication is expensive in power, it has been chosen to implement division in AMD processors [68], NVIDIA GPUs [69], and in Intel Itanium CPUs utilizing the already existent FMA unit.

To implement the NR algorithm using the existing FMA instruction, the lookup table for the initial approximation has to be performed in software. Subsequently, the NR iterations can be executed directly in the FMA unit in Figure 3.3. An extra clock cycle is required to forward the result from the output register to the input register between each FMA instruction. Thus, excluding the initial approximation a total of  $8 \times 5 + 1 = 41$  cycles is required to implement division in software.

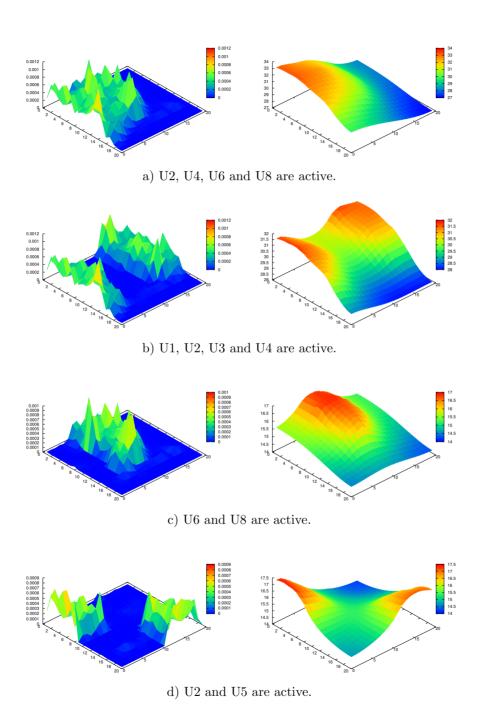

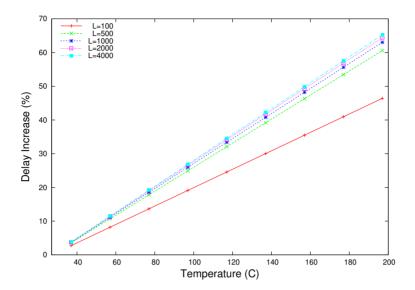

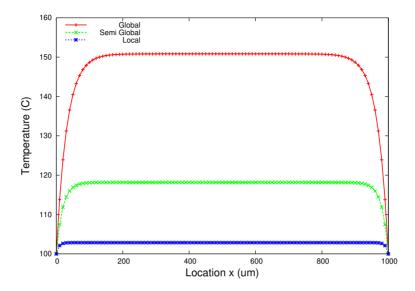

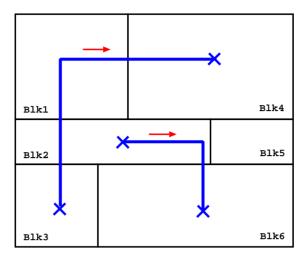

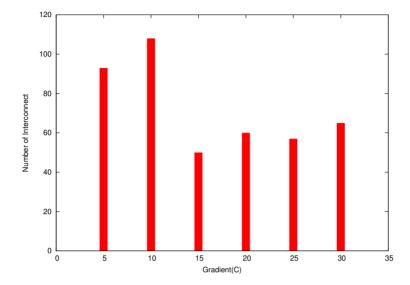

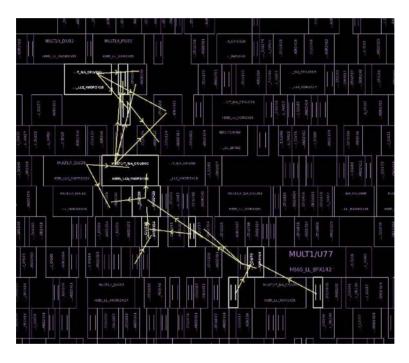

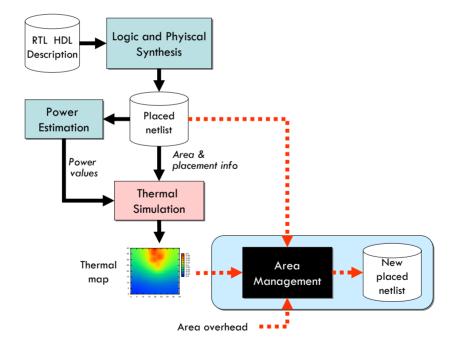

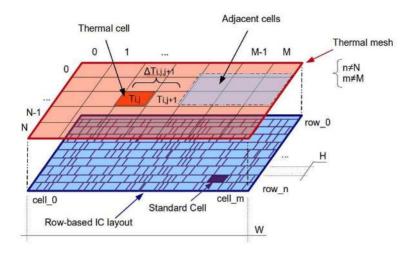

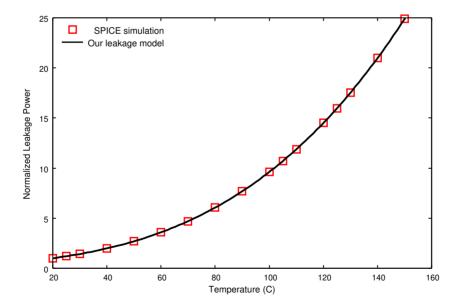

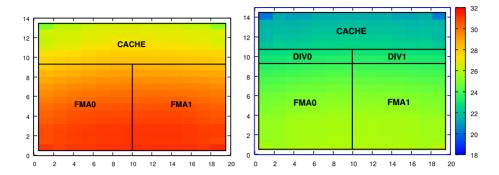

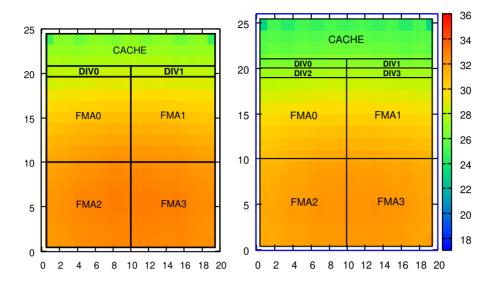

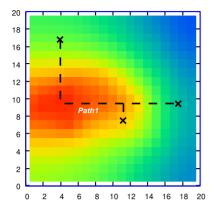

As can be seen, the latency of software implementation is quite long. In the following, we illustrate how to implement the NR algorithm in hardware based on the FMA unit shown in Figure 3.3. In order to achieve the initial approximation and implement the NR algorithm, the FMA unit in Figure 3.3 needs to be augmented with a look-up table and several multiplexers and registers to bypass intermediate results. The implementation of the multiplicative method based on a FMA unit is shown in Figure 3.7.