## Predictable embedded multiprocessor architecture for streaming applications

Citation for published version (APA):

Moonen, A. J. M. (2009). Predictable embedded multiprocessor architecture for streaming applications. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR642808

DOI:

10.6100/IR642808

Document status and date:

Published: 01/01/2009

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 23. Aug. 2022

# **Predictable Embedded Multiprocessor Architecture for Streaming Applications**

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 15 juni 2009 om 16.00 uur

door

Arnold Joannes Maria Moonen

geboren te Weert

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr.ir. R.H.J.M. Otten

en

prof.dr. H. Corporaal

#### © Copyright 2009 Arno Moonen

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright owner.

Cover design: Seph Rademakers

Printed by: Universiteitsdrukkerij Technische Universiteit Eindhoven

A catalogue record is available from the Eindhoven University of Technology Library

ISBN: 978-90-386-1811-1

# **Abstract**

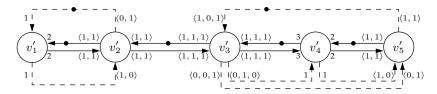

# Predictable Embedded Multiprocessor Architecture for Streaming Applications

The focus of this thesis is on embedded media systems that execute applications from the application domain *car infotainment*. These applications, which we refer to as jobs, typically fall in the class of streaming, i.e. they process on a stream of data. The jobs are executed on heterogeneous multiprocessor platforms, for performance and power efficiency reasons. Most of these jobs have firm real-time requirements, like throughput and end-to-end latency. Car-infotainment systems become increasingly more complex, due to an increase in the supported number of jobs and an increase of resource sharing. Therefore, it is hard to verify, for each job, that the real-time requirements are satisfied. To reduce the verification effort, we elaborate on an architecture for a *predictable system* from which we can verify, at design time, that the job's throughput and end-to-end latency requirements are satisfied.

This is achieved by starting with an architecture where processors have private local memories and execute tasks in a static order, so that the uncertainty in the temporal behaviour is minimised. As an interconnect, we use a network that supports guaranteed communication services so that it is guaranteed that data is delivered in time. The architecture is extended with shared local memories, run-time scheduling of tasks, and a memory hierarchy.

Dataflow modelling and analysis techniques are used for verification, because they allow cyclic data dependencies that influence the job's performance. Shown is how to construct a dataflow model from a job that is mapped onto our predictable multiprocessor platforms. This dataflow model takes into account: computation of tasks, communication between tasks, buffer capacities, and scheduling of shared resources. The job's throughput and end-to-end latency bounds are derived from a self-timed execution of the dataflow graph, by making use of existing dataflow-analysis techniques. It is shown that the derived bounds are tight, e.g. for our channel equaliser job, the accuracy of the derived throughput bound is within 10.1%. Furthermore, it is shown that the dataflow modelling and analysis techniques can be used despite the use of shared memories, run-time scheduling of tasks, and caches.

# Acknowledgments

Writing this chapter means that my thesis formally comes to an end. This chapter allows me to show my gratitude to all people that directly or indirectly contributed to or supported my research.

Support for my research was provided by NXP semiconductors, who gave me the facility to conduct my research and supported my PhD financially from 2004 until 2008. In this period, I divided my working time between NXP Research in Eindhoven (System-On-Chip Architectures and Infrastructure group), NXP semiconductors in Nijmegen (Business-Line Car Infotainment), and Eindhoven University of Technology (Electronic Systems group). I have been very lucky to have, on one hand, the facilities of an excellent research environment, and, on the other hand, the possibility to put research ideas on trial within a development team.

I would like to thank Jef van Meerbergen, from Eindhoven University of Technology, for giving me the opportunity to work on the challenging research topic of predictable embedded multiprocessor architectures. I am very grateful for his encouragement and guidance throughout my PhD journey.

I also want to thank Ralph Otten for accepting to be promotor at my PhD defense and for his support as a group leader of the Electronic Systems group. My thanks also extends to Henk Corporaal as being my second promotor and for his valuable feedback during our discussions at the University. Furthermore, I owe much gratitude to all members of my PhD committee for reading my thesis, giving useful feedback and for participating in my defence session.

I am indebted to my supervisors Marco Bekooij, from NXP research, and René van den Berg, from NXP semiconductors, for their outstanding support, advice, and guidance in my daily work. With Marco, I had many brainstorm sessions and a lot of in-depth discussions that were very useful and from which I have learned a lot. I was greatly inspired by René who is a system architect within Business-Line Car Infotainment, and who participated in our technical discussions and gave feedback to my work. Besides being good supervisors, Marco and René are pleasant people to work with.

Within the System-On-Chip Architectures and Infrastructure group in Eindhoven, my research was part of the Hijdra project. Unfortunately, I cannot mention everyone who helped me, but I would like to mention the Hijdra members for the valuable discussions and for getting the opportunity to work in such a team of enthusiastic and talented researchers.

I also want to thank all people with whom I have worked within the Business-Line Car Infotainment, for creating a nice working environment, for supporting my research, and for giving constructive feedback. I really enjoyed being part of the soccer team *FC BION* for the sportive relaxation after work.

My thanks also extend to my colleagues at the Electronic Systems group, for the nice working environment. A special thanks goes out to the members of the PreMaDoNa project for the technical discussions and for providing valuable feedback on my research.

Finally, I wish to thank my family and friends. My parents have always believed in me and helped me to reach my goals. The love and encouragement of my girlfriend Esther allowed me to finish this journey. Finally, I would like to dedicate this work to my lost father, Wiel Moonen, who left us too soon.

Arno Moonen April 2009

# **Contents**

|   | Abs  | tract                                                         | i   |  |  |  |

|---|------|---------------------------------------------------------------|-----|--|--|--|

|   | Ack  | nowledgments                                                  | iii |  |  |  |

| 1 | Intr | oduction                                                      | 1   |  |  |  |

|   | 1.1  | Car-infotainment domain                                       | 1   |  |  |  |

|   | 1.2  | Reactive and real-time systems                                | 4   |  |  |  |

|   | 1.3  | Platform-based design                                         | 6   |  |  |  |

|   |      | 1.3.1 Existing platforms                                      | 7   |  |  |  |

|   |      | 1.3.2 Platform trends                                         | 9   |  |  |  |

|   |      | 1.3.3 Design-time versus run-time mapping                     | 10  |  |  |  |

|   |      | 1.3.4 Verification of real-time constraints                   | 11  |  |  |  |

|   | 1.4  | Problem definition                                            | 12  |  |  |  |

|   | 1.5  | Approach                                                      | 14  |  |  |  |

|   | 1.6  | Contributions                                                 | 16  |  |  |  |

|   | 1.7  | Thesis outline                                                | 17  |  |  |  |

|   | Part | I: Design rules for a predictable multiprocessor architecture | 19  |  |  |  |

| 2 | Stre | Streaming application domain                                  |     |  |  |  |

|   | 2.1  | Characteristics of streaming                                  | 21  |  |  |  |

|   | 2.2  | Job's real-time constraints                                   | 24  |  |  |  |

|   | 2.3  | Sample-rate conversion                                        | 25  |  |  |  |

|   | 2.4  | Jobs and use cases in the infotainment nucleus                | 26  |  |  |  |

|   |      | 2.4.1 Generation three                                        | 27  |  |  |  |

|   |      | 2.4.2 Generation four                                         | 29  |  |  |  |

| 3 | Mu   | tiprocessor architecture for streaming applications           | 31  |  |  |  |

|   | 3.1  | Requirements for a predictable architecture                   | 31  |  |  |  |

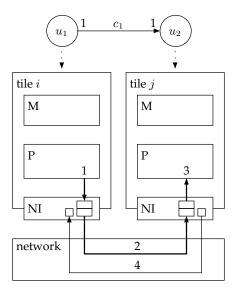

|   | 3.2  | Multiprocessor architecture                                   |     |  |  |  |

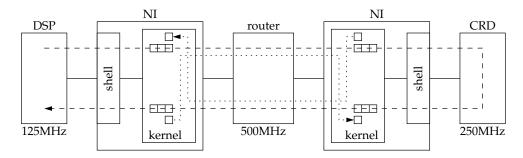

|   |      | 3.2.1 Æthereal network-on-chip                                | 34  |  |  |  |

vi Contents

|   | 3.3  | Communication and synchronisation between tasks                      | 37 |  |  |  |  |

|---|------|----------------------------------------------------------------------|----|--|--|--|--|

|   | 3.4  | Static-order scheduling of tasks                                     | 40 |  |  |  |  |

|   | 3.5  | Concluding remarks                                                   | 41 |  |  |  |  |

| 4 | Ana  | llysing real-time performance                                        | 43 |  |  |  |  |

|   | 4.1  | Modelling a job that is mapped to the platform                       | 43 |  |  |  |  |

|   | 4.2  | Dataflow model preliminaries                                         | 44 |  |  |  |  |

|   | 4.3  | Dataflow model construction                                          | 47 |  |  |  |  |

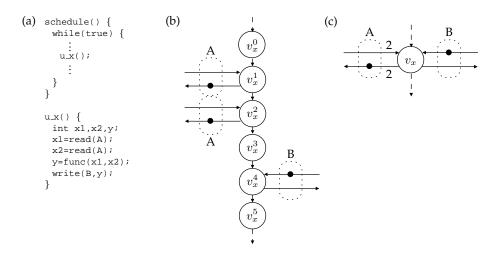

|   |      | 4.3.1 Absence of the firing rule in the implementation               | 49 |  |  |  |  |

|   |      | 4.3.2 Modelling static-order schedules                               | 53 |  |  |  |  |

|   | 4.4  | Dataflow analysis techniques                                         | 56 |  |  |  |  |

|   | 4.5  | Concluding remarks                                                   | 58 |  |  |  |  |

| 5 | Cas  | e study: comparison of Æthereal network and interconnects in SAF7780 | 59 |  |  |  |  |

|   | 5.1  | Car-infotainment generation three                                    | 59 |  |  |  |  |

|   |      | 5.1.1 Reference design                                               | 59 |  |  |  |  |

|   |      | 5.1.2 Communication requirements                                     | 60 |  |  |  |  |

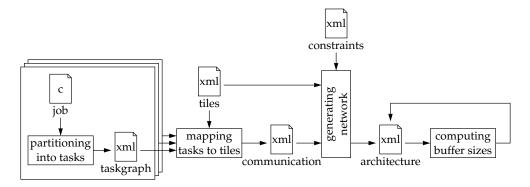

|   | 5.2  | Design flow and tools                                                | 62 |  |  |  |  |

|   |      | 5.2.1 Estimating the network area                                    | 63 |  |  |  |  |

|   | 5.3  | Comparison design-space exploration and reference design             | 65 |  |  |  |  |

|   |      | 5.3.1 Network cell area                                              | 65 |  |  |  |  |

|   |      | 5.3.2 Network communication latency                                  | 68 |  |  |  |  |

|   | 5.4  | Concluding remarks                                                   | 69 |  |  |  |  |

| 6 | Cas  | e study: analysing real-time performance of a channel equaliser      | 71 |  |  |  |  |

|   | 6.1  | Channel equaliser implementation                                     | 71 |  |  |  |  |

|   | 6.2  | Performance analysis via a dataflow model                            |    |  |  |  |  |

|   | 6.3  | Performance comparison with simulation                               | 76 |  |  |  |  |

|   | 6.4  | Sources of inaccuracy                                                | 78 |  |  |  |  |

|   | 6.5  | Concluding remarks                                                   | 80 |  |  |  |  |

|   | Part | II: Multiprocessor architecture extensions                           | 81 |  |  |  |  |

| 7 | Sha  | red memory architecture and remote write accesses                    | 83 |  |  |  |  |

|   | 7.1  | Inter-tile communication via a shared memory                         | 83 |  |  |  |  |

|   |      | 7.1.1 Address-less versus address-based communication                | 84 |  |  |  |  |

|   |      | 7.1.2 Implementation of inter-tile communication                     | 85 |  |  |  |  |

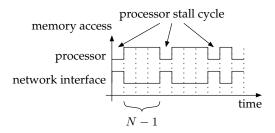

|   | 7.2  | Upper bound on processor stall cycles                                | 90 |  |  |  |  |

|   |      | 7.2.1 Processor stall cycles due to remote write accesses            | 90 |  |  |  |  |

|   |      | 7.2.2 Processor stall cycles due to local memory sharing             | 92 |  |  |  |  |

|   | 7.3  | Run-time scheduling of task executions                               | 94 |  |  |  |  |

|   | 7.4  | Dataflow model construction                                          | 96 |  |  |  |  |

| <u> </u> | • • |

|----------|-----|

| Contents | VII |

| Contents | ¥11 |

|          |     |

|                                                                        |      | 7.4.1   | Modelling run-time scheduling of tasks                     | . 96           |

|------------------------------------------------------------------------|------|---------|------------------------------------------------------------|----------------|

|                                                                        |      | 7.4.2   | Modelling inter-tile communication                         | . 97           |

|                                                                        | 7.5  | Case s  | tudy: MP3 playback                                         | . 100          |

|                                                                        |      | 7.5.1   | Upper bounds on processor stall cycles                     | . 101          |

|                                                                        |      | 7.5.2   | Latency-rate server representation of the MP3-decoder      | . 103          |

|                                                                        | 7.6  | Conclu  | ading remarks                                              | . 104          |

| 8                                                                      | Cacl | ne-base | d multiprocessor architecture                              | 105            |

|                                                                        | 8.1  | Multip  | processor architecture with external memory                | . 105          |

|                                                                        |      | 8.1.1   | Inter-tile communication via external memory               | . 107          |

|                                                                        | 8.2  | Optim   | istically-estimated versus conservatively-estimated bounds | . 109          |

|                                                                        | 8.3  | Cache   | -miss reduction techniques                                 | . 111          |

|                                                                        | 8.4  | Cache   | -aware mapping of streaming jobs                           | . 113          |

|                                                                        |      | 8.4.1   | Execution scaling                                          | . 114          |

|                                                                        |      | 8.4.2   | Computation of the execution scaling factor                | . 116          |

|                                                                        |      | 8.4.3   | Example of execution scaling in a dataflow model           | . 117          |

|                                                                        | 8.5  | Case s  | tudy: Digital-Radio-Mondiale receiver                      | . 118          |

|                                                                        | 8.6  | Conclu  | ading remarks                                              | . 122          |

| 9                                                                      | Con  | cluding | g remarks                                                  | 125            |

| A Modelling static-order schedules: Relation between phase $f'$ and po |      |         |                                                            | ı q <b>129</b> |

|                                                                        | Bibl | iograpl | ny                                                         | 131            |

|                                                                        | Curi | riculum | ı Vitae                                                    | 137            |

|                                                                        | List | of pub  | lications                                                  | 139            |

|                                                                        |      |         |                                                            |                |

viii Contents

# Chapter 1

## Introduction

#### 1.1 Car-infotainment domain

The target application domain, in this thesis, is the application domain from business-line *car-infotainment solutions* at NXP semiconductors. This business line has more than seventeen years of experience in designing digital signal processing chips for car radios.

A car is a uniquely challenging environment that combines entertainment (e.g. audio and video) with information (e.g. weather, news, and traffic information). We refer to this combination as *car infotainment*. The main application areas are: radio, audio, video, and navigation.

In the past, radio was only analog terrestrial radio reception, like Amplitude Modulation (AM), Frequency Modulation (FM), and Weather Band (WB). Currently, digital satellite radio and digital terrestrial radio are emerging rapidly. An example of digital satellite radio is Satellite Digital Audio Radio Service (SDARS). SDARS is a popular type of digital radio in the United States of America (USA) and it is operated by XM-Radio and Sirius. Examples of digital terrestrial radio are Digital Radio Mondiale (DRM), Digital Audio Broadcast (DAB), and Hybrid Digital (HD) radio.

Examples of audio processing are playback compressed and uncompressed audio, streaming audio from a portable media player, audio post processing for enhanced audio quality, and encoding audio to a storage device. Current car radios support various kinds of interfaces for connecting the car radio to portable media players, mobile phones, and storage devices. Furthermore, the number of supported compression formats is increasing rapidly. Examples of currently used compression formats are MPEG-1 audio layer 3 (more commonly referred to as MP3) and Microsoft's Windows Media Audio (WMA).

Currently, video processing is mainly video playback for rear-seat entertainment. The video source can be a mass storage device (e.g. DVD or hard disk) or digital radio (e.g. SDARS). Finally, there is navigation processing with, for example, road access services and eSafety. In this thesis, our focus will be mainly on application areas radio and audio, because these areas are the main focus of business-line car-

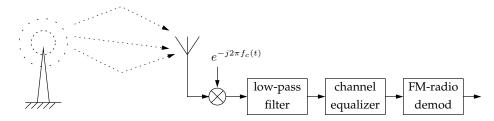

**Figure 1.1:** Multi-path reception is just one of the issues that has to be addressed.

infotainment solutions at NXP semiconductors. The individual functions in an application are referred to as jobs, like an MP3 decoder job and FM-radio demodulation job. Note that most of the jobs process on streams of data, like radio, audio, or video streams.

The car is a living room on wheels, which is a uniquely challenging environment. A car is a moving object driving at speeds up to  $200 \, \mathrm{km/h}$  (causing doppler effect), autonomously following a radio station, in a continuous changing environment with temperature variation, high voltage/current peeks, multi-path reception (as depicted in Fig. 1.1), and background noise. At the same time, the user expects a high quality audio. Therefore, a number of quality enhancement features are added, like *RDS-follow-me* for autonomously switching frequencies for following a radio station, channel equalising for cancelling distortion coming from multi-path reception, two reception antennaes enabling an improved reception with *phase diversity*, and noise reduction and echo cancellation algorithms for making hands-free phone calls.

The development of the car-infotainment market is not uniform across different regions in the world. For example, terrestrial digital radio and (particularly) satellite digital radio are growing strongly in the USA, while terrestrial digital radio is emerging in Europe. In the Japanese market, video is already widespread (often integrated into the head units) and navigation is well advanced, both in terms of adoption and technology (three dimensional view and integrated hard-disc devices). The European market has the strongest adoption of *Bluetooth* (BT) for connecting personal devices to their car infotainment and the main focus in Asia today are low-end car radios. Therefore, platforms should be flexible and programmable so that they can cover multiple regions.

Next to these technical challenges, the car environment has also non-technical challenges. For example, car manufacturers aim for zero field returns. Therefore, the system should have zero bugs and it should handle abnormal conditions well. No system is totally bug free, but a robust system will not lock up, cause damage to data, or let the user wait forever. Field returns are typically expensive and they harm the brand's image. That is why car manufacturers require from their suppliers that they are automotive qualified. To pass the automotive qualification, the system is exposed to extensive field tests and it should behave according to its specified behaviour during these tests. New platforms need to be algorithmic upward compatible with existing platforms, because current algorithms are already proven in the field and algorithmic changes need again extensive field tests, which are time consuming and

Figure 1.2: Simplified car-infotainment system.

costly. Therefore, they increase the development risks for new platforms.

There are some important differences between the life cycles in the automotive, consumer electronics, and personal computer domain, like time for introduction of new applications, and life time of applications and devices. For automotive products the planning and development of a new device takes about three years (two years for design and one year for validation and automotive qualification) and the life cycle is about eight to ten years. For products in consumer electronic, the planning and development time is six to nine months and the life cycle is about one and a half year. For the personal computer world this is even faster (several months). To survive the automotive life cycle, car-infotainment platforms should support flexibility and upgrade possibilities. For example, in October 2001 Apple launched its portable media-player *iPod* that became a hype in the following years. Car radios that are sold in 2003 contain digital signal processing platforms that are developed at least three years earlier. Therefore, they had to be flexible in such a way that the iPod could be connected to a car radio. Furthermore, when looking at the development of the car radio of today, can a *digital right management* solution survive an entire car life cycle?

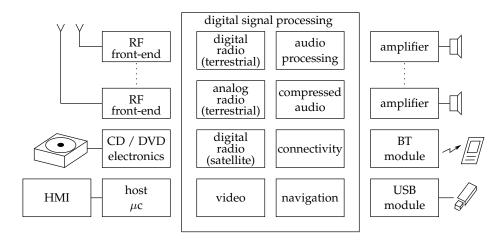

A simplified block diagram of a car-infotainment system is depicted in Fig. 1.2. The application areas, such as analog terrestrial radio, digital terrestrial radio, digital satellite radio, audio processing, compressed audio, video, and navigation, have been considered as largely distinct in building car-infotainment systems. But future systems will be increasingly characterised by convergence of these application areas. The main digital signal processing platforms of business-line *car-infotainment solutions* at NXP semiconductors, support a nucleus of infotainment functionality. An infotainment nucleus consists of common and stable jobs from the areas radio, audio, video, as well as navigation. One chip or chip-set, including software, will be the heart of an integrated infotainment system, where cost, quality and application life time are balanced. Standard interfaces, to interconnect multiple chips, enable high-end application implementations for early market penetration, because we are never sure what jobs we can expect in future generations (e.g. speech recog-

|            | supported                |                  |                  | supported                 |              |            |              |

|------------|--------------------------|------------------|------------------|---------------------------|--------------|------------|--------------|

| generation | areas                    |                  |                  |                           | modes        |            |              |

|            | analog terrestrial radio | audio processing | compressed audio | digital terrestrial radio | single media | dual media | triple media |

| one        | •                        | •                |                  |                           | •            |            |              |

| two        | •                        | •                |                  |                           | •            | •          |              |

| three      | •                        | •                | •                |                           | •            | •          |              |

| four       | •                        | •                | •                | •                         | •            | •          | •            |

Table 1.1: Overview of current infotainment-nucleus generations.

nition [22], audio spotlight [66], or anti sound [96]). Furthermore, it enables prototyping to capture requirements. An overview of the four generation digital signal processing platforms is shown in Table 1.1. Currently (generation four), the number of supported media streams is three, one for front-seat audio and two for rear-seat audio. Future generations will support even more than three streams. For example, for ripping audio streams to a hard disk (e.g. streams received from multiple radio stations). Furthermore, we expect that future infotainment-nucleus generations will increase to integrate additional jobs from the areas digital satellite radio, video and navigation, in a single chip. The increase in the number of jobs, increase in the number of active media streams, and increase in quality enhancement algorithms contribute to an rapid increase of possible set of simultaneously active jobs. This rapid increase will result in an increase of complexity and the demand for new design and verification methods to come to a robust and cost-efficient system implementation.

A short summary of characteristics in the car-infotainment domain is given below:

- Most jobs fall in the class of streaming, i.e. they process on a stream of data.

- Increasing demand for flexibility, e.g. supporting multiple digital-radio standards and multiple compression formats.

- The supported number of jobs and number of media streams is increasing.

- The possible number of simultaneously active jobs is increasing rapidly.

### 1.2 Reactive and real-time systems

The streaming jobs in the car-infotainment domain, typically need to react on their environment within certain timing constraints. Reactive systems [41, 6] have to react to an environment which cannot wait. Reactive systems maintain a permanent

**Figure 1.3:** Example of jobs performance contribution function for different types of requirements.

interaction with their environment and have externally defined timing constraints. Radio reception is an example where the system should keep up with its environment, because the radio transmitter cannot be held up.

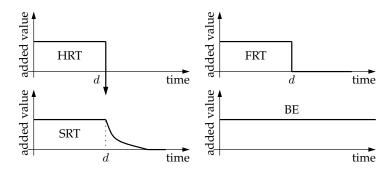

In [14], computing systems that must react within precise timing constraints to events in its environment, are called real-time systems. As a consequence, the correct behaviour of these systems depends not only on the value of the computation but also on the time at which the results are produced. Streaming media applications typically have such *real-time constraints*, i.e. deadlines. By contrast, non-real-time or *best-effort* (BE) systems are systems for which there are no deadlines, even if fast response or high performance is desired. Depending on the consequences that may occur when missing a deadline, real-time requirements are usually distinguished in three classes: (i) *hard real-time* (HRT), (ii) *soft real-time* (SRT), and (iii) *firm real-time* (FRT) [14].

- (i) A job has hard real-time requirements if missing its deadline may cause catastrophic consequences on the environment (e.g. may result in the loss of life or in large damage). Therefore, in case of a hard real-time job, it is not allowed to miss any deadline. A hard real-time job contributes to its performance if it completes its function within its deadline d, as depicted in Fig. 1.3. Completing its function after its deadline, would jeopardise the behaviour of the system, therefore, its quality contribution can be seen as minus infinity. Systems that typically have hard real-time constraints, due to the potentially severe outcome of missing a deadline, are safety critical systems.

- (ii) A job has soft real-time requirements if meeting its deadline is desirable for performance reasons, but missing its deadline does not cause serious damage to the environment and does not jeopardise correct system behaviour. If a soft real-time job completes its function after its deadline, it still contributes to the quality, but this contribution may decrease over time. Soft real-time jobs are typically those used where there is a need to keep a number of results up to date with changing situations. An example of a job with soft real-time constraints is navigation, dropping frames while displaying a map is hardly noticeable by a user as long as the deadline misses are sporadic.

- (iii) A job has firm real-time requirements if missing its deadline results in no contri-

Figure 1.4: Platform-based design paradigm.

bution to its performance, but missing its deadline does not cause serious damage to the environment and does not jeopardise correct system behaviour. Audio and radio processing are examples of jobs with firm real-time requirements. Missing a deadline, when processing an audio stream, will result in a steep quality degradation. For example, missing deadlines at a digital-to-analog converter can cause hiccups in the audio, or missing a deadline in the digital radio path can result in loss of synchronisation. In both examples there are severe quality losses, but there are no catastrophic consequences on the environments. In this thesis, we will focus on jobs with firm real-time requirements, because our focus is up to infotainment-nucleus generation four, which exclude video and navigation jobs.

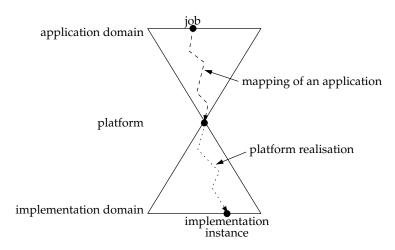

### 1.3 Platform-based design

The growing complexity of current and future embedded systems leads to a demand for new design paradigms. The car-infotainment domain consists of an increasing number of jobs, as described in Section 1.1. Implementing these jobs in a system-on-chip that meets the functional and non-functional constrains, is a large design problem. Platform-based design [24, 47] is an example of a design paradigm in which the design complexity is split into two, by specifying a platform specification in the middle as depicted in Fig. 1.4. The platform is targeting multiple jobs from a specific domain. The platform specification allows software engineers to map their jobs to the platform at the same time as the hardware engineers realise an implementation instance that meets the platform specification. Furthermore, a platform design increases the reuse between different products from the same application domain. This also reduces the non-recurrent engineering cost and time-to-market in developing a new product.

A system platform consists of a high-level architecture specification for hardware as well as software. For this high-level architecture, services are defined that can be

allocated to a job, which is mapped onto the platform. Mapping a job to the platform is challenging for meeting its real-time constraints like throughput and end-to-end latency. At the bottom in Fig. 1.4, there are possible implementations of the platform that comply to the high-level architecture specification and that are able to deliver the specified services. Realisation of a platform implementation is challenging for meeting cost constraints in terms of silicon area and energy consumption. In this thesis, we propose an architecture and design rules for building a platform that is optimised for infotainment-nucleus generation four and beyond.

#### 1.3.1 Existing platforms

This section evaluates existing platforms within the car-infotainment domain and it elaborates on the platform trends. From a consumer perspective, we divide current NXP's car-infotainment platforms into four generations, as described in Table 1.1.

The design of the first generation car-infotainment chip SAA7701, started in the early nineties. It supported analog terrestrial-radio reception and audio post-processing functionality. The radio input signal was coming from a tuner chip and the radio signal was demodulated by a dedicated hardware Intellectual Property (IP) module. Beside the radio input, the chip had capability for two analog and two digital input signals. This chip integrated one Digital Signal Processor (DSP) (which belongs to the EPICS family [72]) that was able to process one audio stream at a time. The main task of the processor was audio post processing. Derivatives of the SAA7701 included a hardware accelerator for extra audio features, like equalisation, and they supported up to five analog and three digital input signals. As the chips were implemented in smaller process technologies, the processors were able to execute with higher clock frequencies and supporting more features with an increasing sound quality. The processor has a local on-chip memory that is used by only the processor.

The second generation car-infotainment platform supports processing single and dual media stream, for independent front-seat and rear-seat audio. The first chip that supported this was SAA7706, which was also the first car-infotainment system that integrated two DSPs instead of one. The chip SAA7724 was the first chip capable of processing two independent analog terrestrial-radio streams. It integrated three special purpose processors, for demodulating the two radio input streams, together with two DSPs, for sample-rate conversion and audio post processing. The chip SAF7730 [71] is also capable of processing two radio input signals and it consists of five DSPs and five hardware accelerators. Three DSPs in combination with the five hardware accelerators are used to demodulate two radio streams. The two remaining processors are used for sample-rate conversion and audio post processing. Next to dual-radio processing, the SAF7730 is also capable of single-radio reception with phase diversity, which is an advanced algorithm for improved radio reception. The interconnect of the chip SAF7730 is as follows. There are hardwired point-to-point connections between a processor and hardware IP modules like accelerators or peripherals. The interconnect between the processors is implemented with circular buffers that are stored in dual-ported memories. Next to these inter-processor communication memories, the processors have local memories for storing instructions, coefficients and data.

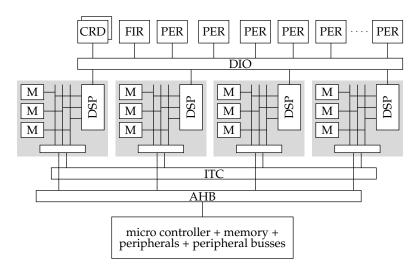

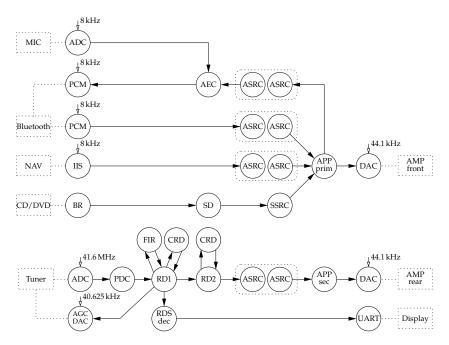

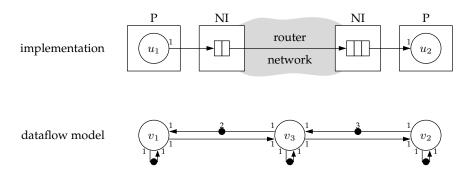

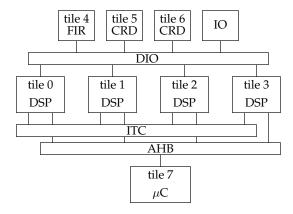

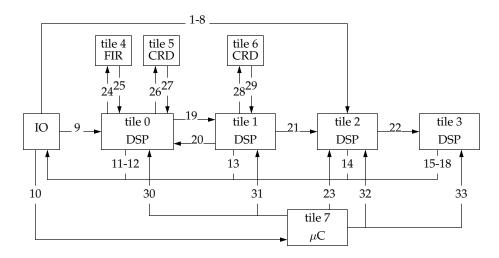

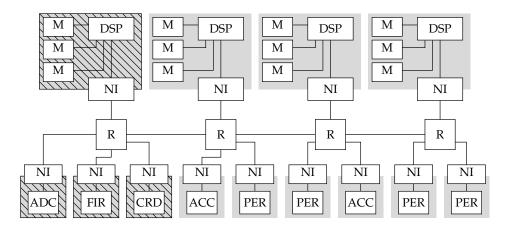

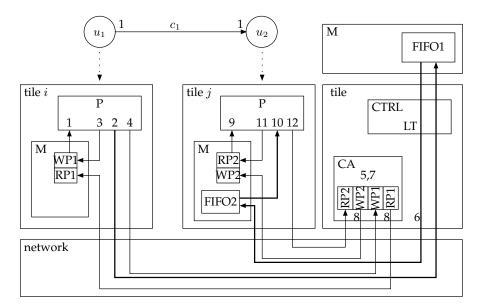

Figure 1.5: Hardware architecture generation three (SAF7780).

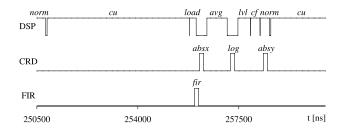

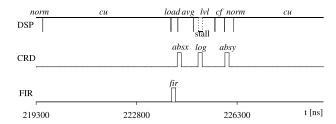

In the first two generations, the digital signal processing chips are controlled and monitored by a host micro controller ( $\mu$ c) that is connected to these chips. The micro controller can program the chip's parameters, like control parameters and filter coefficients. Such a micro controller is integrated in the third generation car-radio chip SAF7780 [88, 8]. Furthermore, it supports analog terrestrial-radio reception, playback compressed audio (MP3 and WMA), and connectivity to portable devices in different user modes, like single-media versus dual-media audio. Although it supports dual media, it can demodulate only one radio-input stream at the same time. This chip is composed of four DSPs, one micro controller (which can be used as host), three hardware accelerators (one Finite-Impulse-Response (FIR) filter and two Coordinate-Rotation-Digital computer (CRD) accelerators), and a number of input and output peripherals (PER), as depicted in Fig. 1.5. The radio demodulation is performed by two DSPs in combination with the three hardware accelerators. The two other DSPs perform sample-rate conversion, compressed-audio decoding, and audio post processing. As interconnect, the platform uses a multi-layer bus (AHB) in the micro-controller subsystem, a crossbar switch (ITC) between the DSPs, and a crossbar switch (DIO) between the DSPs and the accelerators/peripherals. The DSPs make use of local memories (M) for instructions, coefficients and data. In contrast with generation one and two, these processors make use of shared local memories instead of private local memories, i.e. a processor can also write to the local memory of another processor.

The fourth generation car-infotainment platform is currently under development and it will support analog as well as digital terrestrial-radio reception and decoding as well as encoding compressed audio (various formats). Compared to previous generations, this platform will support processing up to three independent media streams, one for front-seat and two for rear-seat audio. The platform will include a number of DSPs, a Very-Long-Instruction-Word (VLIW) processor, a micro controller, and a number of hardware accelerators and peripherals. The interconnect of

the chip will consist of a number of multi-layer busses that are connected via bridges. Such an interconnect is a first step towards a network-on-chip. The memory architecture is as follows. There will be an off-chip memory because the memory footprints (e.g. for the digital radio jobs) are considered to be too expensive to store on-chip. The processors will have local shared memories as well as caches to hide the large latencies in accessing the off-chip memory.

#### 1.3.2 Platform trends

By investigating existing car-radio platforms, we observed the following trends. The first generation platforms contain only one processing core. Next generation platforms contain multiple processing cores. For cost and power-efficiency reasons, we see that heterogeneous multiprocessor systems are used that combine various types of processors with configurable hardware accelerators. The trend of an increase in the number of processing cores is expected to continue in the future. It is also visible in other application domains. For example in the CELL processor from IBM, which combines one PowerPC core with eight synergetic processors [46]. Another example is coming from Intel. Instead of still increasing the clock frequency, Intel shifts its strategy to increasing the number of processors. Currently, they shift from single-core to multi-core systems, and later on they expect to shift from multi-core towards many-core systems, which consist of more than hundred processing cores [10].

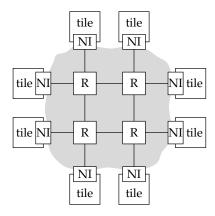

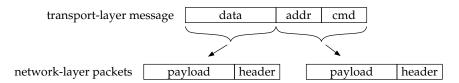

The integration of different types of cores into a working system is a major challenge. Currently multiple busses and custom interconnects (point-to-point, crossbar switches) are used and they are interconnect to each other via bridges. However, with an increasing number of cores, designed in technologies with decreasing dimension, they do not sufficiently address hardware problems (deep sub-micron VLSI design) and software problems (application programming). Networks-on-chip tackle these problems and, therefore, are a better answer to the integration challenges. From a hardware perspective, they structure the top level wires in a chip, and facilitate modular design [74]. Structured wiring results in predictable electrical parameters, such as crosstalk. Network interconnects are segmented and multihop. The advantage of segments is that only those segments are activated that are actually used in the communication, so only those segments dissipate power. Multihop is needed because the transport delay from source to destination can become longer than the clock period. From a software perspective, networks can reduce the programming effort by defining proper transport-level services. The bottleneck in single-processor architectures is computation, whereas the bottleneck in multiprocessor architectures shifts from computation towards communication. Getting the right data at the right place at the right time will dominate the architecture. Networks that offer *guaranteed-communication services* make systems easier to program, easier to design [34], and more robust.

The first two generation car-infotainment platforms have only processors with private local memories. Although there is a C-compiler available, most of the code is written in assembly for performance and legacy reasons. Software algorithms that are written in assembly code are typically more efficient in terms of required processor cycles and memory usage compared to compiled C-code. The disadvantages of assembly code are that it is much harder to write, read, and maintain compared to

C-code and it is only applicable for the targeted processor. The trend is that processors become faster, larger, and more complex. Furthermore, software tasks become also larger and more complex in contrast to the small tasks as in the first platform generations. Therefore, the trend is larger memory footprints and more variation in the temporal behaviour. From small tasks in combination with predictable memory access latencies, we are able to derive conservatively-estimated upper bound on the execution times of these tasks, as we will describe later. For such a system, worst-case design is achievable because conservatively-estimated bounds (e.g. on the required number of processor cycles) are not far from the typical case. In current and future generation platforms, the local memories are shared, the code will be off-loaded to an off-chip memory, and caches will be introduced to prevent that every memory access will receive a large memory access latency. In such a memory hierarchy, the access latency from a processor to the external memory can vary, because of an unknown state of the cache, possible contention in the communication infrastructure, and possible contention at the external memory. Therefore, the distance between the typical-case and worst-case memory access latency will increase. The uncertainty of the required number of processor cycles increases and worst-case design can become too expensive, if the worst case is an order of magnitude different from the typical case. This increase of uncertainty makes it a challenge to build cost-efficient platforms with worst-case design methodologies.

#### 1.3.3 Design-time versus run-time mapping

A platform consists of a high-level architecture for which platform services (or resources) are defined that can be allocated to a job. Mapping a job is defined as allocating resources to a job and finding scheduling settings in case of resource sharing. The main challenge that is discussed in this thesis, is mapping a job so that the job's real-time requirements are met.

There are trade-offs between run-time and design-time mapping of a job. Design-time mapping has a few advantages. First of all, the scope is typically larger than in case of run-time mapping, i.e. with design-time mapping the designer can make decisions based on knowledge over a large number of iterations, e.g. gathered via profiling during simulation, via static code analysis, or via knowledge from the application domain. Furthermore, design-time mapping can be more complex than run-time mapping, because computation is not time critical. The main advantage of run-time mapping is a more precise knowledge about the system load. For example, it is known in which scenario [30] or mode the job is executed and it is known which resources are actually used. However, at run-time the scenario or resource usage can change rapidly. Furthermore, computing a specific mapping will occupy a processor, takes time, and consumes energy. Therefore, run-time mapping algorithms should be simple.

In this thesis, we combine design-time and run-time mapping in the following way. Every possible set of simultaneously activated jobs, which we refer to as a use case, is investigated separately at design time. Each job in a use case is mapped to our platform, one by one. Tasks from a job are bound to the processing tiles. The required resource budgets and scheduler settings are computed so that the real-time requirements are met. At run-time, the jobs are started and stopped by loading a

predefined mapping.

#### 1.3.4 Verification of real-time constraints

To verify that the job's real-time requirements are met, we need a performance analysis technique to analyse the temporal behaviour of a job. We identify two categories for existing analysis techniques, namely (i) simulation and (ii) exhaustive analysis.

(i) Extensive simulation is often used for analysing the temporal behaviour of a job and to verify that its throughput and end-to-end latency requirements are satisfied. The simulation tools accompanying the modelling language SystemC [44] and POOSL [85], for example, are used to simulate transaction level models [21]. Transaction level models trade-off accuracy for running time. However simulation can be performed at different levels of abstraction, simulation of all operation modes for a large set of input stimuli is time consuming. From cycle-accurate simulation, we can derive an optimistic estimate on the minimum throughput, because the throughput observed during simulation is only valid for the given set of input stimuli. A larger set of input stimuli can increase the accuracy, however, we are unable to guarantee that throughput requirements are met for all possible input stimuli and starting states.

Assuming that the parameters in a model (e.g. worst-case execution times) are conservative, proper analysis techniques, such as exhaustive analysis, are able to guarantee that no deadlines are missed, i.e. can guarantee a minimum throughput and maximum end-to-end latency.

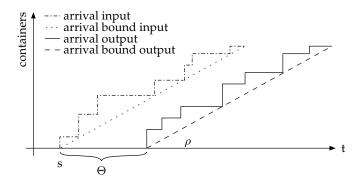

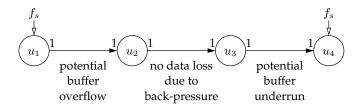

(ii) Exhaustive analysis techniques are based on min-plus algebra [11] or max-plus algebra [3]. Network calculus [17], real-time calculus [53, 87], and event-models [45] have their roots in the min-plus algebra [5]. These analysis techniques bound the data traffic between tasks with (piece-wise) linear bounds. The analysis is based on the assumption that the bounds for each pair of communicating tasks can be given the same average slope. The slope of a bound can be adapted by, for example, changing the settings of run-time schedulers or by regulating arrival of data by introducing traffic shapers. An important drawback of this analysis approach is that it has problems with cyclic data dependencies that affect the temporal behaviour. The reason is that the linear bounds on the traffic are considered an input of the problem and not an outcome of the analysis. More precisely, the linear bounds are derived for each task in isolation. For acyclic graphs the end-to-end temporal behaviour can be computed given these bounds. However, for cyclic graphs incorrect results can be obtained because cyclic dependencies can affect these bounds and, therefore, can influence the job's temporal behaviour. Cyclic dependencies can be caused by functional dependencies (e.g. in the case of feedback loops), schedule dependencies (e.g. in the case of static-order scheduling), and back-pressure (to prevent buffer overflow). In our car-infotainment system, we have such cyclic dependencies. Therefore, we should be able to cope with them.

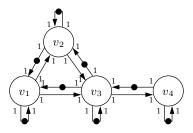

Dataflow-analysis techniques [51, 76, 91] have their roots in max-plus algebra [5]. Multiple dataflow models are described in literature, each with a different trade-off between expressivity and analysability. The best well known dataflow models are Single Rate DataFlow (SRDF) [9], Multi-Rate DataFlow (MRDF) [9, 50], Cyclo-Static

**Figure 1.6:** Ordering of dataflow models according to their expressivity.

DataFlow (CSDF) [9, 64], Boolean DataFlow (BDF) [13], and Dynamic DataFlow (DDF) [63]. Marked graphs [16] and Weighted Marked Graphs, which are a subclass of timed Petri Net theory, have the same expressiveness as SRDF and MRDF graphs, respectively. SRDF and MRDF are also known as Homogenous Synchronous DataFlow (HSDF) [76] and Synchronous DataFlow (SDF) [50], respectively. MRDF and CSDF graphs can be transformed into equivalent SRDF graphs, but the number of actors of the equivalent SRDF graphs can be large. Therefore, for a one-to-one relation between tasks in the implementation and actors in the model, Fig. 1.6 shows the ordering of SRDF, MRDF, and CSDF models according to their expressivity [9]. These models do not support data dependent input and output behaviour of tasks, as is supported in the by BDF and DDF models. But in these models, throughput and end-to-end latency cannot be derived for an arbitrary graph. Some generalisations of dataflow models have been proposed, i.e. techniques to allow input data dependent input and output behaviour of tasks [93, 84, 7], and that maintain the full potential for analysis. Another generalisation on dataflow models is scenario awareness, which is referred to as a Scenario-Aware DataFlow (SADF) model [86]. This model uses a dataflow model to represent a specific scenario and it uses a stochastic approach to model the order in which scenarios occur. The underlying model is a Markov chain that can be analysed using exhaustive or simulation-based techniques.

An important advantage of dataflow-analysis techniques [76, 28] is that it allows cyclic data dependencies that influence the temporal behaviour. Therefore, also back-pressure is supported by the dataflow model. This allows execution-time estimates of tasks, in case conservatively-estimated upper bounds are not available, as will be described in Chapter 8.

#### 1.4 Problem definition

A car-infotainment system consists of a hardware platform on which the application software is executed. The application consists of a number of jobs that process on streams of data. For performance and power efficiency reasons, these jobs are executed on a heterogeneous multiprocessor architecture. Furthermore, the jobs have real-time constraints, like throughput and end-to-end latency. To reduce the verification effort, the job as well as the hardware platform should have a predictable temporal behaviour. This allows the designer to verify, at design time, that the job's real-time requirements are met. In the literature, also composable systems [49, 5, 37] are proposed to reduce the verification effort in integrating multiple jobs to a hard-

Problem definition 13

ware platform. In a composable system, the temporal behaviour of one job cannot be affected by another job while they are both executed on the same platform. Therefore, in a composable system the job's real-time requirements can be verified in isolation. The isolation of temporal behaviour is realised with fixed resource budgets for jobs. In a predictable system, in contrast with a composable system, jobs have a minimum resource budget and not a fixed resource budget. A composable system is especially useful in case jobs (e.g. soft real-time jobs) can have an overload. In a composable system, this overload cannot affect the performance of other jobs (e.g. firm real-time jobs), because the temporal behaviour of one job cannot affect the temporal behaviour of another job. Therefore, composability will ease the system's performance-verification effort, because an overload of a job will only affect the performance of the misbehaving job. Predictable and composable architectures are orthogonal to each other and they can be combined in one system, as is shown in [37]. In this thesis, we only focus on a predictable system on which firm real-time jobs are executed. A predictable system is necessary to be able to guarantee that the job's real-time requirements are met.

Definition of a predictable system:

**Definition 1** (Predictable system). A system is predictable if we can verify at design time whether temporal constraints are satisfied for the respective condition to hold.

The temporal constraints are expressed as repetitive deadlines at source or sink tasks, as will be described in next chapter. On the one hand, deadlines can be derived from a task's throughput constraint or end-to-end latency constraint. On the other hand, if we can guarantee an upper bound on end-to-end latency that is lower than the end-to-end latency constraint, and if we can guarantee a lower bound on throughput that is higher than the required throughput, then it is sure that no deadlines will be missed. Therefore, we should be able to derive an upper bound on end-to-end latency and a lower bound on throughput for every job. Furthermore, these bounds should be tight to enable a cost-efficient implementation of the system.

For a job with hard real-time requirements, no data can be lost. When mapping a job with hard real-time requirements on a hardware platform, the condition of a predictable system is as follows:

**Definition 2** (Condition for hard real-time). A hard real-time system must satisfy the temporal constraints for any input stream and any initial state of the system.

A system with hard real-time constrains must keep up with its environment in any circumstance. Therefore, for a hard real-time system, we must derive a conservatively-estimated upper bound on end-to-end latency and a conservatively-estimated lower bound on throughput for every job. These bounds must hold for any possible set of input stimuli and for any possible initial state of the hardware platform (e.g. initial state of a time-division-multiplex scheduler or cache).

For a job with firm real-time requirements, no data should be lost and the system should keep up with its environment. Not keeping up with the system environment does not jeopardise correct system behaviour, because it has firm real-time requirements instead of hard real-time requirements. When mapping a job with firm real-time requirements on a hardware platform, the condition of a predictable system is as follows:

**Definition 3** (Condition for firm real-time). A firm real-time system must satisfy the temporal constraints for a set of input streams and any initial state of the system. Furthermore, a firm real-time system must have a fall-back mechanism to recover from deadline misses.

For a firm real-time system with a specific set of input stimuli, we can derive an upper bound on end-to-end latency and a lower bound on throughput for every job. Notice that the derived bounds are optimistic estimates, because they are not guaranteed for every possible set of input stimuli. If the job exceeds our optimistically-estimated bounds on end-to-end latency or throughput, it can miss a deadline. When the set of input stimuli is representative, we are confident that the system exceeds a deadline only sporadically. It is not catastrophic if the job sporadically misses a deadline due to firm real-time requirements. Not keeping up with the system environment must not jeopardise correct system behaviour, so it must have a fall-back mechanism in case of a deadline miss. An example of a fall-back mechanism is reusing a previous computed audio sample.

When mapping a job with soft real-time requirements on a hardware platform, the condition of a predictable system is as follows:

**Definition 4** (Condition for Soft real-time). A soft real-time system has a target for its average behaviour but does not have temporal constraints. Furthermore, a soft real-time system must have a fall-back mechanism to recover from deadline misses.

For jobs with soft real-time requirements it is desirable that the system keeps up with its environment, but missing a deadline does not cause serious damage to the environment since there is a fall-back mechanism. In a soft real-time system, it is allowed to derive an estimated end-to-end latency and estimated throughput instead of optimistically-estimated bounds as in case of firm real-time. Therefore, the target temporal behaviour is typically average case. In this thesis, we only focus on hard and firm real-time systems and we do not investigate systems with soft real-time requirements. Furthermore, all active jobs are equally important.

We now arrive at the main problem statement of this thesis:

**Problem statement.** Develop a multiprocessor architecture for a predictable firm real-time system that is optimised for infotainment-nucleus generation four. Furthermore, show that a job, which is mapped on the architecture, can be represented in a dataflow model, so that existing dataflow-analysis techniques can be used to verify that the system satisfies the real-time constraints.

In next section, we elaborate on our approach in dealing with this problem.

### 1.5 Approach

A system consists of multiple jobs executed on a hardware platform. In order to come to a predictable system, we need (i) jobs from which we are able to reason about the temporal behaviour, (ii) a platform architecture from which we are able to

Approach 15

reason about the temporal behaviour, and (iii) a model of a job that is mapped on the platform in order to reason about the temporal behaviour of the total system.

- (i) When a job complies to our model of computation, we are able to reason about its temporal behaviour at design time. Chapter 2 formulates the characteristics of such a job. A job can be represented in a task graph, where tasks are represented by nodes and inter-task communication channels are represented by edges. The main characteristics in order to bound the temporal behaviour are bounded execution times, bounded production behaviour, and bounded consumption behaviour of tasks. The bounds on execution times should be conservatively estimated in case of hard real-time requirements, or they can be optimistically estimated in case of firm real-time requirements.

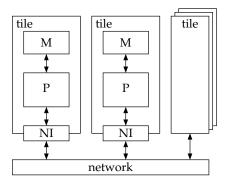

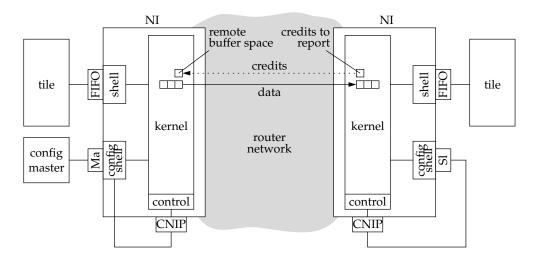

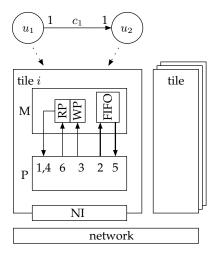

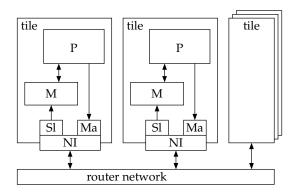

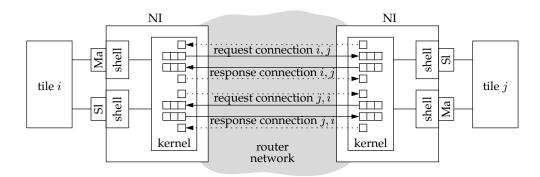

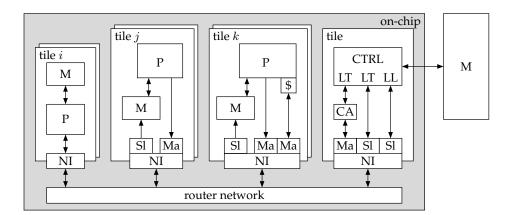

- (ii) We are able to reason about the temporal behaviour of the following platform architectures. First, we start by defining a multiprocessor architecture with limited resource sharing, to limit the uncertainty in the temporal behaviour. Predictable memory-access latencies are achieved with a local private memory for each processor, i.e. a processor only accesses its local memory and this memory is not accessed by another processor. Furthermore, each processor executes only tasks from the same job and these tasks are executed in a static order. As an interconnect between the processors, we make use of a network-on-chip that supports network connections with guaranteed communication services. For such a system, we are able to derive conservatively-estimated bounds on throughput and end-to-end latency for each job. The architecture has limitations in terms of the supported sizes for memory footprint and data containers. Furthermore, the supported number of communication channels and the supported buffer capacities for inter-tile communication, are fixed at design time. This architecture is only applicable for jobs coming from infotainment-nucleus generation one and two, because these jobs make use of sample-based processing.

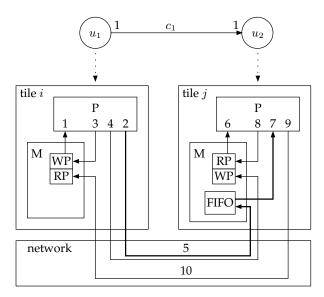

Next, this multiprocessor architecture is extended with shared local memories between processors. This allows us to communicate via circular buffers that are stored in the local memory of a processor. The main advantages of these circular buffers is a cost-efficient implementation of large buffers and that the buffer capacities are programmable at run time. The number of supported communication channels is also programmable at run time. Furthermore, the use of circular buffers enables checking of available space or data, which in its turn enables the use of run-time scheduling of tasks that belong to different jobs. This sharing of memory and processor resources will increase the uncertainty in the temporal behaviour of the system. However, conservatively-estimated bounds on throughput and end-to-end latency can still be derived. The architecture has still the limitation in the supported memory footprint, because tasks are assumed to fit in the local memories of the processors. Therefore, this architecture is only applicable for jobs up to infotainment-nucleus generation three.

Finally, the multiprocessor architecture is extended with an off-chip memory that is shared between the processors. This is required in case the memory footprint of tasks is considered to be too large to store on-chip. The access latencies to an off-chip memory are larger than the access latencies of local memories. Therefore, processors will use level one caches to hide these larger access latencies. This thesis does not elaborate on explicitly (software controlled) pre-fetching of the task's program code

and working data set into a local memory, but it is seen as future work. The introduction of caches will introduce additional uncertainty in the temporal behaviour of the system. In practice, for such an architecture, optimistically-estimated bounds on throughput and end-to-end latency are used instead of conservatively-estimated bounds. This architecture is applicable for jobs from infotainment-nucleus generation four.

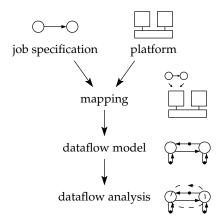

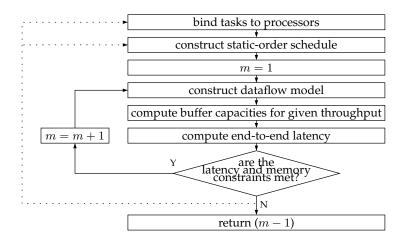

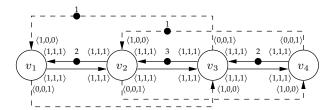

(iii) In order to reason about the temporal behaviour, we require a model that accurately represents the temporal behaviour of a job that is executed on the platform. For such a model, we make use of dataflow models. First, the job's task graph will be transformed into a dataflow graph. Next, the job will be mapped to the platform and after every mapping step additional constraints are added to this dataflow model. For every extension in the architecture, we need to represent the temporal behaviour in a dataflow model. Finally, the job's real-time requirements are verified by making use of existing dataflow-analysis techniques. Furthermore, buffer capacities and scheduler settings can be derived for given throughput and end-to-end latency constraints.

#### 1.6 Contributions

This thesis makes several contributions to develop a predictable and cost-efficient system for streaming jobs.

Main contribution of this thesis

• Introduction of a network-based multiprocessor system that is predictable. This is achieved by starting with an architecture where processors have private local memories and execute tasks in a static order, so that the uncertainty in the temporal behaviour is minimised. This architecture is extended with shared local memories, run-time scheduling of tasks, and a memory hierarchy. After each extension, it is shown that the temporal behaviour can still be modelled in a dataflow model and, hence, we are still able to verify that the job's throughput and end-to-end latency requirements are met.

Contributions in Part I of this thesis

- We show that tasks, which are executed in a static order, can be represented

with one actor despite the absence of the firing rule in the implementation. An

algorithm is introduced for generating a CSDF graph that models tasks that

are executed on processors with static-order schedules. Earlier versions of this

work were published in [58, 57].

- For an industrial case study, we compare the Æthereal network-on-chip with the traditional interconnects for infotainment-nucleus generation three. For this generation, we conclude that it is feasible to replace the traditional interconnects by an Æthereal network and still meet the communication requirements. We conclude that the network-area cost is mainly determined by the number of connections (translating to a number of buffers) and the network

Thesis outline 17

topology (affecting the number of routers, the slot table and the sizes of the buffers). Earlier versions of this work were published in [60, 55].

• For an industrial case study, we investigate the tightness of a conservatively-estimated lower bound on the throughput for a job mapped onto our multiprocessor platform. The conservatively-estimated throughput bound is computed from a dataflow model and it is compared with the optimistically-estimated throughput bound that is measured with cycle-accurate simulation. The difference is only 10.1% for our job, which is a channel equaliser for FM radio. The difference is small because of tight conservatively-estimated bounds on execution times (each processor has a private local memory) and communication latencies (due to guaranteed-throughput services and a small slot table in the network). Finally, we identify three causes for the difference between a throughput bound that is computed from a dataflow model and a throughput bound that is measured with cycle-accurate simulation. An earlier version of this work was published in [57].

#### Contributions in Part II of this thesis

- For address-based communication, we introduced a formula to compute an upper bound on the number of processor stall cycles, which can be translated in a lower bound on the processor utilisation. For our industrial case study, which is an MP3 decoder, we have shown that the bound on the processor utilisation has an accuracy of at least 6%. Furthermore, in case of sharing of a network connection between multiple communication channels, it is shown that larger network-interface buffers can lead to larger buffer requirements for the circular buffers in the memory. An earlier version of this work was published in [56].

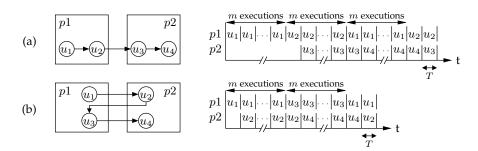

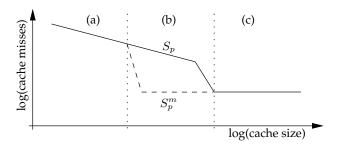

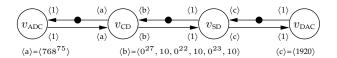

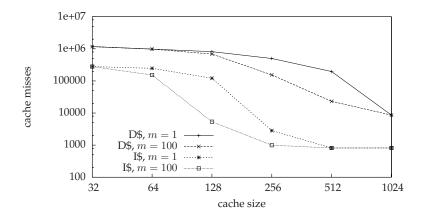

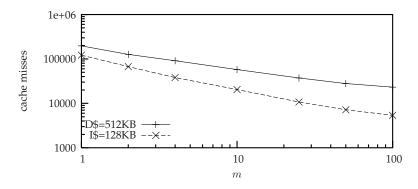

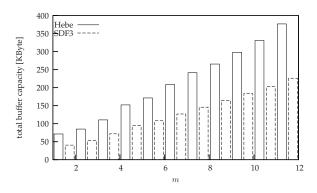

- We proposed a novel cache-aware mapping technique that reduces the number of instruction and data cache misses for streaming jobs that are mapped onto a multiprocessor system. This technique is based on a technique [73] that executes tasks multiple times in a loop before executing another task. It is shown that it is only beneficial if the individual tasks fit in the instruction and data cache, and the set of tasks, which are executed on a processor, do not fit simultaneously. We use a dataflow model for representing an application that is mapped onto a multiprocessor with a specific number of successive task executions. From this dataflow model we derived the maximum number of successive task executions by making use of existing dataflow-analysis techniques. For our industrial case study, which is a Digital-Radio-Mondiale receiver, we reduce the number of cache misses by a factor 4.2. This work was published in [58].

#### 1.7 Thesis outline

This thesis is divided into two parts. In part I, we introduce design rules for a predictable multiprocessor system-on-chip. In part II, these concepts are extended to-

wards a multiprocessor architecture for jobs up to infotainment-nucleus generation four.

Part I: In the next chapter, we first formulate a streaming job and describe its characteristics. For these streaming jobs we define, in Chapter 3, a scalable heterogeneous multiprocessor architecture that consists of tiles which communicate via a network-on-chip. In Chapter 4, we describe dataflow modelling and analysis for verifying the real-time requirements of our streaming jobs. This chapter also describes how such a model can be constructed, so that it captures the temporal behaviour of a job mapped onto a multiprocessor platform. In Chapter 5, the network cost is investigated in terms of area and latency for a number of automatically generated network instances and this is compared to traditional interconnects from car-infotainment platform SAF7780. Chapter 6 evaluates the practical use and tightness of dataflow modelling and analysis for our channel-equaliser case study.

Part II: In Chapter 7, we extend the multiprocessor architecture with shared on-chip memories and run-time scheduling of tasks. For these extensions, it will be shown that the real-time constraints can still be verified by dataflow modelling and analysis. In Chapter 8, the multiprocessor architecture is extended with a shared off-chip memory. It introduces a cache-aware mapping technique for streaming applications, because an efficient use of the memory hierarchy is important for current and future multiprocessor systems. Finally, Chapter 9 concludes this thesis and gives recommendations for future work.

Part I: Design rules for a predictable multiprocessor architecture

# **Chapter 2**

# Streaming application domain

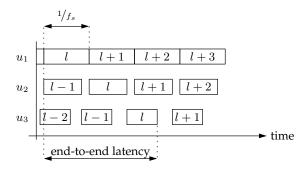

The jobs in the infotainment nucleus, typically process streams of input data and generate streams of output data. Furthermore, they have real-time constraints, for example caused by a periodic source (e.g. analog-to-digital converter), periodic sink (e.g. digital-to-analog converter), or both periodic source and sink. These jobs are called streaming jobs in this thesis. The characteristics of streaming jobs are described in the following section. In Section 2.2, we elaborate on the real-time requirements of these jobs. Jobs with sample-rate conversion are described in Section 2.3. Finally, Section 2.4 gives some examples of streaming jobs in the car-infotainment domain.

### 2.1 Characteristics of streaming

Streaming jobs are common in the embedded domain and they encompass a broad spectrum of applications, including media encoding and playback. Every possible set of simultaneously activated jobs is called a use case. Jobs can be started and stopped by the user. The user can start or stop jobs while others continue. Furthermore, the mode of a job can be changed by the user. Muting an audio stream or changing its volume are examples of mode changes where switching between use cases is not necessary. A switch between use cases is a dynamic process, which must be handled at run time. The number of use cases is increasing rapidly, because of the increasing number of supported jobs. For example, if there are N jobs and each job can be active or inactive, then the number of use cases is theoretically  $2^N$ . Obviously, jobs can only be started if enough resources are available.

Streaming jobs are characterised by concurrent computation processes, which we refer to as tasks, that process potentially infinite sequences of data provided by the environment. A task represents a function transformation that has one or more inputs and outputs. Furthermore, tasks execute independently and they can have state that contains all the information necessary to execute. They are repeatedly executed and thus have explicit start and finish times. After a task started its execution, it will continue to execute until it is finished. In case of run-time scheduling, tasks can also

**Figure 2.1:** Example of a streaming job represented as a task graph.

be interrupted, as we will see in Part II of this thesis. Once a task finished its execution, it can start to execute its next iteration. Tasks are executed by, for example, a processor or hardware accelerator. A scheduler repetitively enables tasks to start executing. Of course, when the user stops the job, the tasks are not enabled anymore.

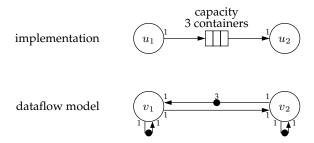

For each task, it is made explicit which data is private to a task (state) and which data is shared between tasks (communication). A task has random access to its private data. Shared data is communicated from one task to another task via a communication channel. Containers are used for the synchronisation between tasks, i.e. tasks communicate containers via First-In First-Out (FIFO) buffers. A fixed amount of data can be stored in a container and they can be full or empty. Containers are also useful for memory management, namely for allocating and releasing space in a memory. Examples of containers are audio stereo samples, MP3 frames, video pixels, video lines, or video frames. A task can have random access within a container, despite the FIFO synchronisation between containers. The number of containers that can be stored in a communication channel is fixed, i.e. the FIFO buffer capacity is fixed. During one execution of a task, it consumes a number of full data containers from its input channels and it produces a number of containers to its output channels.

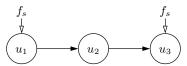

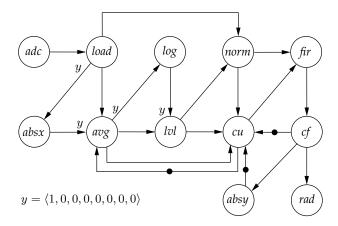

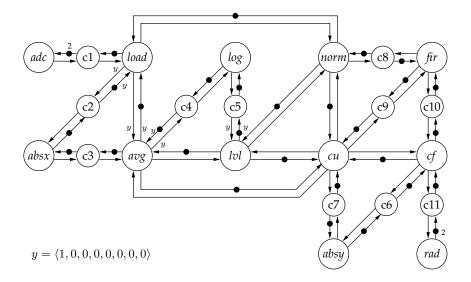

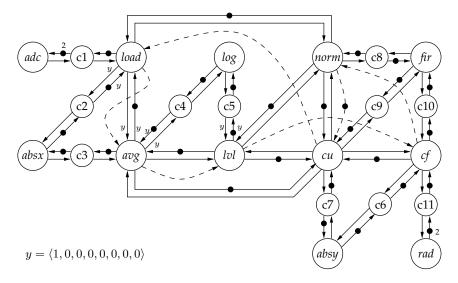

It is natural to express a streaming job as a graph, where the nodes represent independent tasks and the edges represent communication channels between these tasks. Such a task graph H=(U,C) consists of a finite set of tasks U and a finite set of communication channels C. Fig. 2.1 shows an example of a task graph that represents a streaming job that consists of three tasks and two communication channels.

A communication channel  $c_k = (u_i, u_j)$  connects an output of task  $u_i$  to an input of task  $u_j$  with  $u_i, u_j \in U$  and  $c_k \in C$ . Task  $u_i$  produces data containers on this channel and tasks  $u_j$  consumes data containers from this channel. The maximum number of containers that can be stored in a channel  $c_k$  is bounded and it is denoted with  $d(c_k)$ .

After a task started its execution, it will continue until it is finished. The start time of the l th execution of task  $u_i$  is denoted by  $s(u_i,l)$ . The time that task  $u_i$  finished its l th execution, is denoted by  $f(u_i,l)$ . After one execution of task  $u_i$ , the number of data containers that are produced on channel  $c_k$  is denoted by  $\mu(u_i,c_k)\in\mathbb{N}^+$ . The number of data containers that task  $u_j$  consumes from channel  $c_k$  is denoted by  $\lambda(u_i,c_k)\in\mathbb{N}^+$ . In this thesis, we assume that the number of consumed and produced containers are known at design time and cyclo static.

Every task has an execution time that is defined as:

**Definition 5** (Execution time). The execution time of task  $u_i$  is defined as the difference between the time this task started its execution and the time this task finished its execution, i.e.  $f(u_i, l) - s(u_i, l)$ , assuming that sufficient filled containers are available at all its inputs, sufficient empty containers are available at all its outputs, and this task is the only task executed on a processor and the processor is the only master

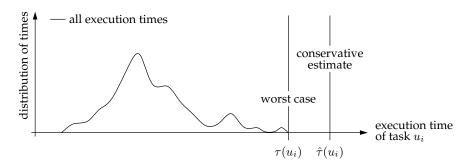

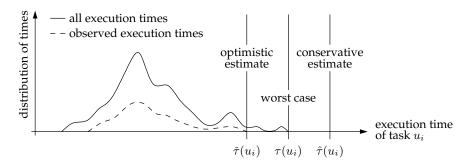

**Figure 2.2:** The definition of worst-case executions time and a conservatively estimated upper bound on the execution time.

that is accessing the memories.

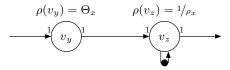

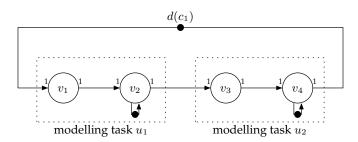

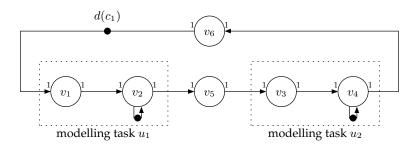

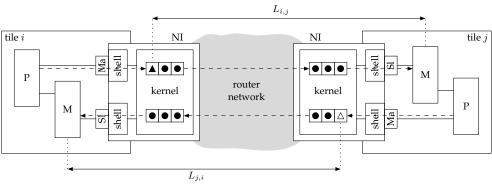

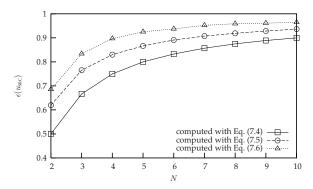

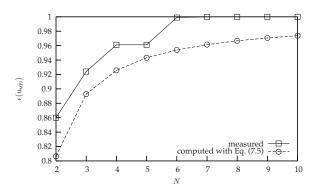

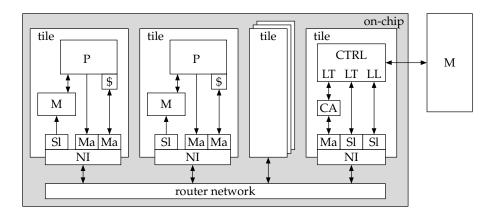

This execution time does not include the time a task has to wait for input data and output space. It does also not include the time a task has to wait before it is scheduled and it does not include the interference time caused by interrupting tasks. Furthermore, execution time does not include processor stall time caused by arbitration at shared memories and cache misses. Therefore, task execution times do not include dependencies between resource and tasks.