## Preliminary Candidate

## Advanced Avionics

System for

## General Aviation

Prepared for

Ames Research Center National Aeronautics and Space Administration

by

Southern Illinois University Under Contract No. NAS2-9310 Distribution of this report is provided in the interest of information exchange. Responsibility for the contents resides in the author or organization that prepared it.

# NATIONAL AERONAUTICS AND SPACE ADMINISTRATION , AMES RESEARCH CENTER MOFFETT FIELD, CALIFORNIA 94035

REPLY TO

NAS 2-9310 AT:241-12-09

November 8, 1977

NASA Representative Scientific and Technical Information Facility P. O. Box 8757 Baltimore/Washington International Airport, Maryland 21240

Subject:

Transmittal of Contractor Report: "Preliminary Candidate Advanced Avionics System for General Aviation," by T. M. McCalla, F. L. Grismore, S. E. Greatline, and L. M.

Birkhead, dated July 1977

Reference: Program Code - 512-52-01

The subject report prepared under Contract NAS 2-9310 has been reviewed at Ames and is recommended for release in STAR as CR-152025.

Paul Bennett

Chief, Technical Information Division

Enclosure:

1 cy subject report

cc:

NASA Hqrs., Code KSI (w/o enc.)

## PRELIMINARY CANDIDATE ADVANCED AVIONICS

SYSTEM FOR GENERAL AVIATION

FINAL REPORT

by .

T. M. McCalla Principal Investigator, SIU

F. L. Grismore Principal Investigator, SIU

S. E. Greatline Investigator, CAC

L. M. Birkhead Investigator, SIU

SOUTHERN ILLINOIS UNIVERSITY Carbondale, Illinois

July, 1977

Prepared under Contract No. NAS2-9310

for

Ames Research Center National Aeronautics and Space Administration Moffett Field, California 94035

#### ABSTRACT

This contract resulted in the design of an advanced integrated avionics system for general aviation aircraft. Although the design in most cases did not proceed to the level of detailed circuitry and actual software, sufficient investigation was performed to achieve a high degree of confidence in the system concepts. In the opinion of the research team, the system described is a good approach to use in building a practical integrated avionics system for general aviation. To further prove this point, and refine the system design, it will be necessary to proceed through the steps of building and testing one or more prototype systems.

Some question exists as to the minimum configuration required to prove out the system concept. This would seem to depend on the eye of the beholder to a considerable degree. We feel that in addition to the triple bus, several team processors, at least one display, a com, a nav, and part of the flight following capability, some of the sensor actuator subsystem should also be included. In one sense, a computer could exercise the bus with a few team processors. But to actually fly the system, and get a hands on feel for its performance and potential, some of each of the subsystems should be included. Voice recognition, engine diagnostics, and other advanced concepts should ultimately be possible. Voice generation should be included in the system now. Hopefully funds will permit NASA to pursue exploration of this new technology

#### ACKNOWLEDGMENTS

In addition to the project team listed on the title page, several other people have played an important role in this study.

Mr. George Callas, of NASA, has on numerous occasions sought out information that helped the team to nail down particular points. He has always been available and a positive motivation. Dr. Dallas Denery, and those who work for him have contributed to this report at various stages by their remarks, and helpful criticisms. Working with the NASA-Ames Guidance and Navigation Branch has been a good experience.

Ms. Janice Jacobsen, the project part time secretary, has endured our many drafts and changes, while also pushing through the seeming endless paperwork.

Graduate students, Mr. Jayakumar, Mr. Ming-Cheng Chen, and Mr. Neng-Huang Sheng performed valuable work in the area of the system processor and bus systems. Work on the GASP PL/I CPS simulation has been performed by Mr. Jayakumar.

Mrs. R. Williams has been a constant help. First, by typing the initial proposal for the project, and later continuing to help us whenever we got into a bind.

Thanks to you all.

T. M. McCalla, Jr. Project Manager, SIU

#### TABLE OF CONTENTS

|           | Pag                                                   | ,e |

|-----------|-------------------------------------------------------|----|

| Section 1 | Introduction                                          | 1  |

|           | Background                                            | 1  |

|           | Purpose                                               | 1  |

|           |                                                       | ī  |

|           | Design Philosophy                                     | 2  |

|           | Significance                                          | 2  |

|           | Digiti tealice                                        | ۷. |

| Section 2 | A Pilot's Perspective                                 | 5  |

|           | Cockpit Philosophy                                    | 5  |

|           | Cessna 402 Panel                                      | 5  |

|           | Flight Scenarios                                      | 7  |

|           |                                                       | 7  |

|           |                                                       | 9  |

|           |                                                       | 9  |

|           |                                                       |    |

| Section 3 | Hardware Description                                  | .0 |

|           | Design Introduction                                   | 0. |

|           | Bus System                                            |    |

|           | Configuration                                         |    |

|           | Bus Interface Modules                                 |    |

|           | Central Processor                                     |    |

|           | Team Architecture                                     |    |

|           | Central Processor Subsystem                           |    |

|           |                                                       | 30 |

|           | Creation Organization                                 | 30 |

|           |                                                       |    |

|           |                                                       | 31 |

|           |                                                       | 37 |

|           | Sensors/Actuators                                     |    |

|           | System Configuration Without Remote Service Modules 6 |    |

|           | Display Subsystem 6                                   |    |

|           |                                                       | 57 |

|           | Operational Features 6                                | 7  |

|           | Functional Capabilities of Display Modes 6            | 8  |

|           | Map Displays                                          | 7  |

|           |                                                       | 8  |

|           |                                                       | 9  |

|           |                                                       | 33 |

|           |                                                       | 39 |

|           |                                                       | 39 |

|           |                                                       | 0  |

|           | Navigation subsystem #1                               |    |

|           | Navigation Subsystem #2                               |    |

|           | Communication Subsystem Design                        |    |

|           | Introduction                                          | .1 |

|           | Controller                                            |    |

|           | Flight Following Subsystem                            |    |

|           | Storm Avoidance Subsystem                             |    |

|           | Hardware                                              | 9  |

| Section 3 | (Continued) Page                         |  |

|-----------|------------------------------------------|--|

|           | Voice Generation Subsystem               |  |

|           | Message Assembly                         |  |

|           | Articulatory Model                       |  |

|           | Vocabulary                               |  |

|           | Power Control Subsystem                  |  |

|           | Protect/Regulator Circuit                |  |

|           | System Packaging                         |  |

|           | Audio Unit And Special Function Keyboard |  |

|           | General                                  |  |

|           | Audio Unit                               |  |

|           |                                          |  |

|           | Manual Special Keypad                    |  |

|           | Mass Memory                              |  |

| Section 4 | System Modeling                          |  |

|           | Reasons For Simulation                   |  |

|           | Simulation Objectives                    |  |

|           |                                          |  |

|           | The Language Chosen                      |  |

|           |                                          |  |

|           | Simulation Plan                          |  |

|           | Sensor Actuator Subsystem Simulation     |  |

|           | Compute Data Source Address              |  |

|           | Transfer Data to Memory                  |  |

|           | Test                                     |  |

|           | Process Algorithm                        |  |

|           | Bus Interrogation                        |  |

|           | Simulation Code                          |  |

|           | CPS Subsystem Simulation                 |  |

|           | Conclusions                              |  |

|           | References                               |  |

| Section 5 | System Tradeoffs                         |  |

|           | Overall Tradeoffs                        |  |

|           | Tradeoff Comparisons                     |  |

| Section 6 | Modularity                               |  |

|           | Definition                               |  |

|           | Advanced Avionics System                 |  |

|           | Recoling System 189                      |  |

•

|           | Pa                                                   | ge  |

|-----------|------------------------------------------------------|-----|

| Section 7 | Reliability                                          | 83  |

|           | Introduction                                         | 83  |

|           | Failure Modes                                        | 83  |

|           | Catastrophic Failure                                 |     |

|           | Hazardous Failures                                   |     |

|           | Nuisance Failures                                    |     |

|           | Analytical Techniques and Modeling                   |     |

|           | Probability Density Function                         |     |

|           | Mission Time                                         |     |

|           | Models                                               |     |

|           | Component Failure Rates                              | -   |

|           | Evaluation of Specific Failure Probabilities 1       |     |

|           | · Bus Failures · · · · · · · · · · · · · · · · · · · |     |

|           | Central Processor Subsystem Failure                  |     |

|           | Sensor Actuator Subsystem Failures                   |     |

|           | Communications Failures                              |     |

|           | Navigation Subsystem Failures                        |     |

|           | Flight Following (Transponder) Failures              |     |

|           |                                                      |     |

|           | Power System Failures                                |     |

|           | Composite Failure Probabilities                      |     |

|           | Catastrophic Failure                                 |     |

|           | Reliability References                               | 16  |

| Section 8 | System Installation And Maintenance                  | .17 |

|           | Introduction                                         | 17  |

|           | System Level Service                                 |     |

|           | Installation                                         |     |

|           | Calibration                                          |     |

|           | Maintenance                                          |     |

|           | Subsystem Repair                                     |     |

|           | Scheduled Avionics Maintenance                       |     |

|           | Avionic Maintenance Cost                             |     |

|           | Avionic maintenance dost                             | 23  |

| Section 9 | System Cost                                          | 27  |

|           | Cost Model                                           |     |

|           | Cost Analysis Sample                                 |     |

|           | Cost Estimates Assumptions                           |     |

|           | Typical System Cost                                  | 30  |

|           | Full Implementation (IFR Cessna 402) 2               | .30 |

|           | Single Engine New Installation                       |     |

|           | Partial Retrofit, Single Engine                      |     |

|           | Conclusion                                           |     |

|            |                                   |      |      |     |    |     |     |   |   |   | F | Page |

|------------|-----------------------------------|------|------|-----|----|-----|-----|---|---|---|---|------|

| Section 10 | Risk Analysis                     | •    |      |     | •  |     |     | • | • | • | • | 232  |

|            | Introduction ,                    |      |      |     |    |     |     |   |   |   |   | 232  |

|            | System Information Buses          |      |      |     |    |     |     |   |   |   |   | 232  |

|            | System Central Processor          |      |      |     |    |     |     |   |   |   |   |      |

|            | Sensor Actuator Subsystem         |      |      |     |    |     |     |   |   |   |   |      |

|            | Display Subsystem                 |      |      |     |    |     |     |   |   |   |   |      |

|            | Navigation Subsystem              |      |      |     |    |     |     |   |   |   |   |      |

|            | Communication Subsystem           |      |      |     |    |     |     |   |   |   |   |      |

|            | Flight Following Subsystem        |      |      |     |    |     |     |   |   |   |   |      |

|            | Storm And Terrain Avoidance Subsy | ste  | n.   |     |    |     |     |   |   | • | ٠ | 235  |

|            | Voice Generation Subsystem        |      |      |     |    |     |     |   |   |   |   |      |

|            | System Power                      |      |      |     |    |     |     |   |   |   | • | 235  |

|            | Audio Unit And Special Function K | (eyb | oard | 1 8 | ub | sys | te  | m |   |   | ٠ | 235  |

|            | Mass Memory Subsystem             | •    |      | •   | •  |     | •   | ٠ | • | • | • | 236  |

| Section 11 | Results and Conclusions           |      |      | ٠   | •  | • • | • • | • | • | • | • | 237  |

| Appendix   | Acronyms and Abbreviations        |      |      |     |    |     |     |   |   |   |   | 238  |

#### - SECTION 1

#### INTRODUCTION

#### BACKGROUND

Recent technological innovations in the area of microelectronics has provided the possibility for significant improvements in the efficiency and safety of general aviation aircraft. The inclusion of computer deduction in the implementation of totally integrated aircraft electronics, provides a tool of much greater capability than the unaided pilot who must manually scan and mentally integrate the total aircraft system. NASA has recognized the need to provide leadership in exploring new areas of system integration to help weed out approaches which are not direct lines to a profitable product.

#### **PURPOSE**

The purpose of the candidate advanced avionics system design for general aviation aircraft is to begin to understand the practicality of utilizing advanced microprocessor technology to make significant improvements in the safety and utility of general aviation aircraft. Techniques have been used which are markedly beyond what the general aviation industry is presently funding in the magnitudes required to bring this technology to the point where it will be routinely applied in the general aviation fleet.

#### SCOPE

Efforts have been made in this candidate system design to identify the overall approach and structure which the system should have to meet the desired integration, reliability, modularity, and cost objectives. Some of the subsystems were looked at in depth. One such in depth study was made of the system busing. Much effort was expended in looking at the various alternative busing approaches available. The military 1553A bus system was judged too elaborate and expensive for general aviation needs. The short confines of the system box and the motherboard concept suggested that a parallel etched bus system would be satisfactory since the data must eventually be used in this form. When distances suggest a simpler serial approach for the cabling, it seems that a differential driver-receiver pair would be sufficient. In fact a test was run in an aircraft using such a simple bus. Despite efforts to induce failure, no noise failures were in fact observed during the test flight. (See section 10 on risk analysis).

The preliminary system specification as well as the final system specification included information which indicated the risk of the technologies, which was also discussed during the three oral reviews. A conservative approach has been taken in providing for the computational power needed by the system. The central processor subsystems may be

judged more powerful than are needed for this application, but jobs for a computer have a way of growing when the computer power is available.

Retrofit to older aircraft, availability of this system to the single engine 2 place aircraft, in addition to such aircraft as the Cessna 402 twin specifically targeted for this design, have been continually considered.

Initially, ways were sought just to make the system work; with some hope of achieving the reliability, cost, power, and weight requirements. As the design has progressed from the top down, more specific detail in some areas has caused a redesign of portions of the system. This will no doubt continue as the system enters into the even more detailed design phases. So far, it has always been possible to do this redesign within the framework laid out for this system. There is no reason why this should not continue to be the case for future prototype work.

### DESIGN PHILOSOPHY

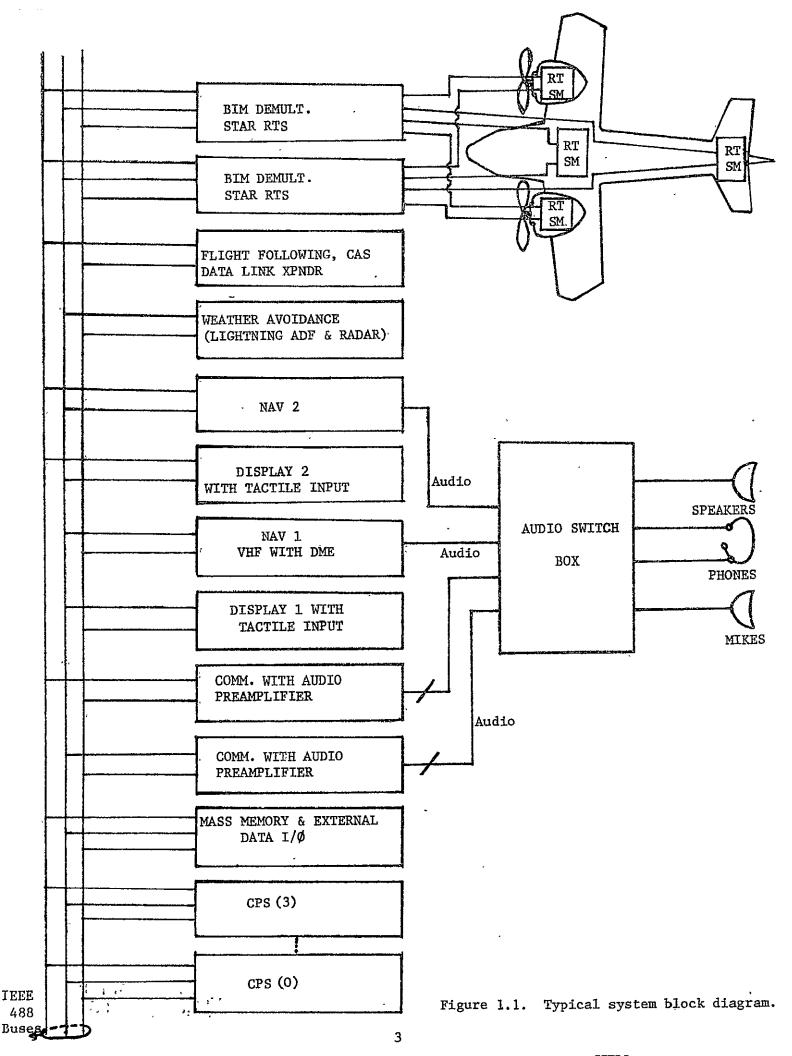

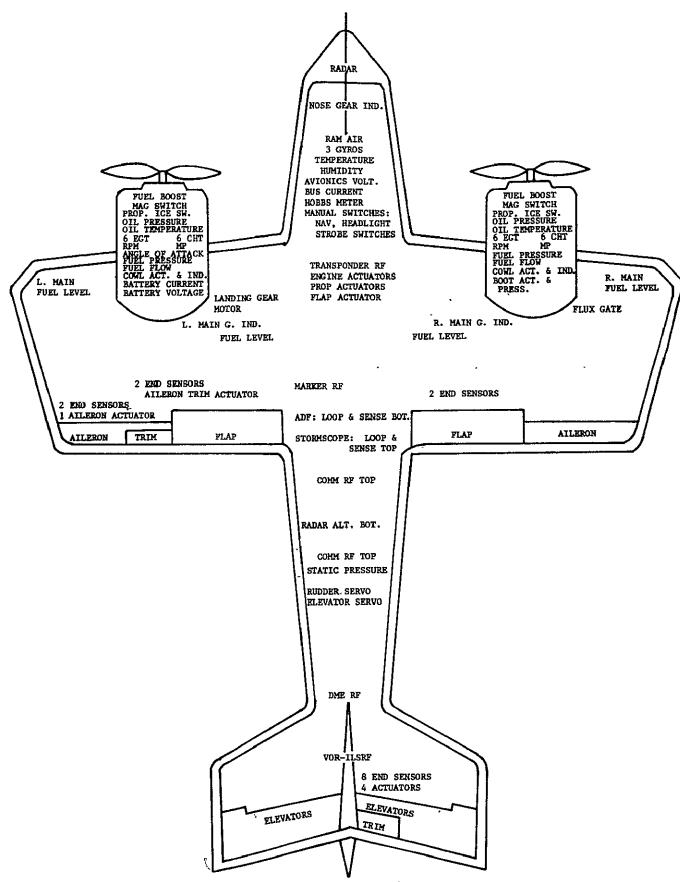

The structure of the candidate system has been chosen to expedite its changing role. An attempt has been made to keep the structure modular so that the configuration and content of the system may be readily modified as aircraft owner and airway system requirements change. Minimization of the ultimate system cost has been observed, while keeping in mind the reliability, modularity, and maintainability required of this system. Features have been rejected which were considered to be cost extravagent for the eventual system to posses. Useful extra features that will be available because the future hardware makes them very cheap to possess, have at times been included. The design has received much attention in the hardware and software areas which are critical to aircraft safety. The pilot has been considered to be a vital part of this system, and has final authority over system operations. The system performs actions by itself, but these can always be ultimately overruled by the pilot. In some cases the system is most invaluable as a source of rapidly accessible data and alternatives for pilot decision making. A block diagram of the advanced avionics system is shown in figure 1.1. Some appreciation of the magnitude of the integration task is gleaned by considering figure 1.2.

#### SIGNIFICANCE

This integrated avionics design offers a radical change from the way things are done now in a general aviation aircraft. As the airways become more crowded with those using this time efficient mode of transportation, the potential for improvements in the margins of safety and efficiency are immense. This design provides a framework within which engine reliability, weather avoidance, pilot assistance, precision navigation, and efficient fuel management may be greatly improved over what now is possible by the average pilot in the average aircraft. The new avionics coupled with airframe and engine developments should help aviation fulfill its needed role as one of the important forms of transportation in this country.

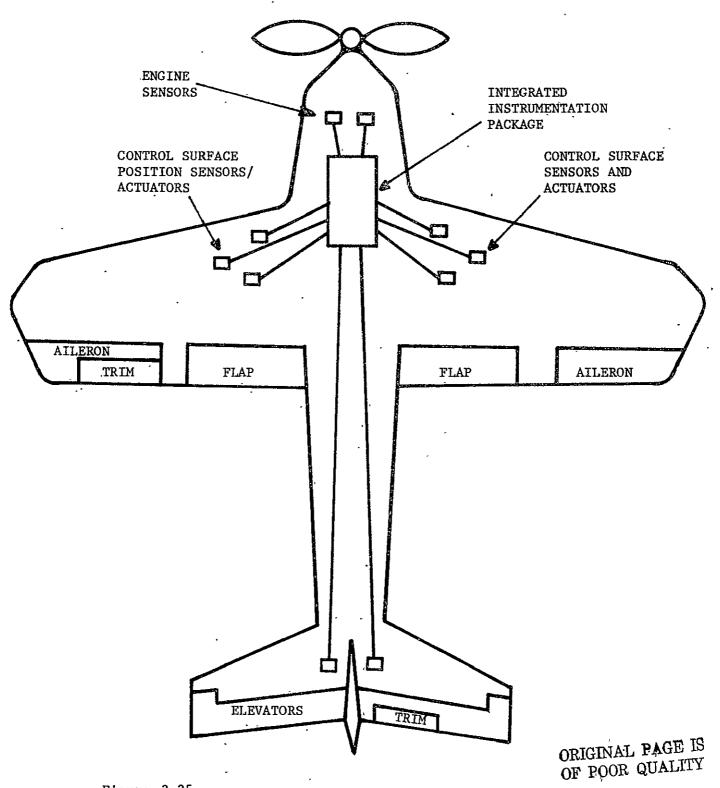

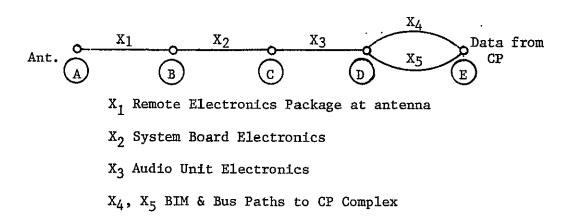

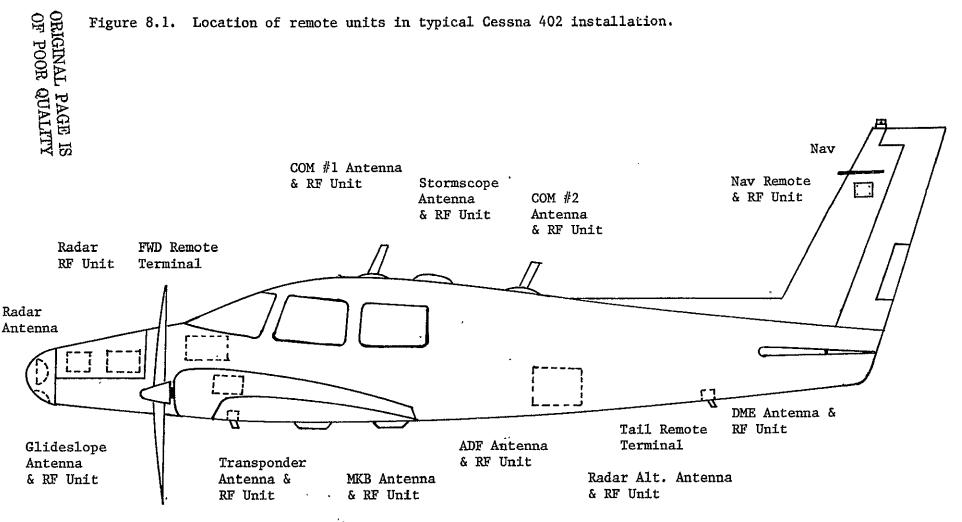

Figure 1.2. Cessna 402 sensor/actuator, antenna distribution.

#### SECTION 2 A PILOTS PERSPECTIVE OF THE SYSTEM

#### COCKPIT PHILOSOPHY

The pilot is always in command. This system assists the pilot in scanning the many instrumentation pickoffs in the aircraft, and rapidly calculates interrelated quantities for the pilot to use. Situation factors and possible decision consequences are rapidly available to the pilot for perusal before making a decision. The system can become a valuable tool, in fact assistant, to be supervised by the pilot.

The cockpit has been laid out for single pilot operation. If both parts of the main display fail, then the backup and/or number two display is placed for relatively easy viewing by the pilot. Autopilot controls can be overriden by the pilot using manual force or by logical entry to the system. Displays are meant to help the pilot in the simplest possible way, and reduce confusion and distraction of attention to the minimum. The system can even be told to prompt occassionally, in case there is a possibility that the pilot needs help to keep alert. How much machine—human interaction occurs, is totally determined by what the pilot instructs the system to do.

#### CESSNA 402 PANEL

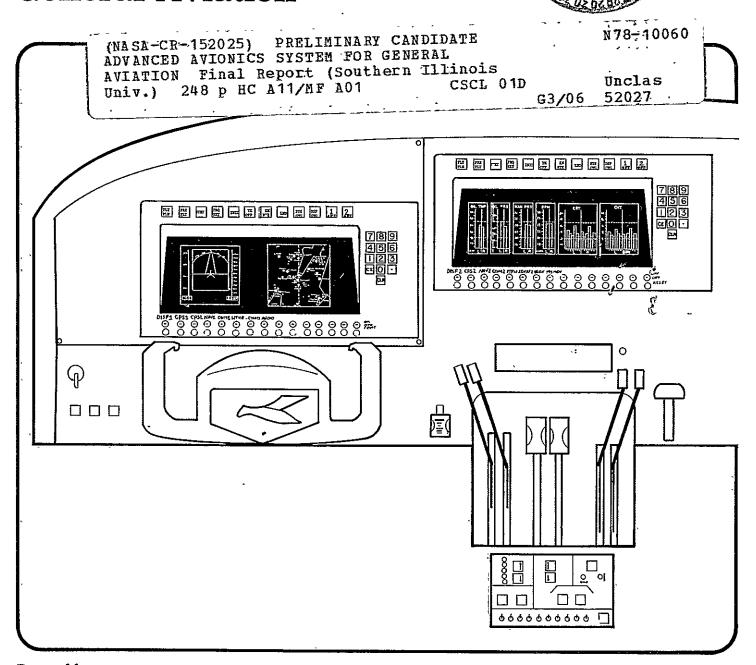

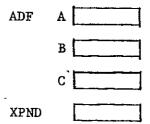

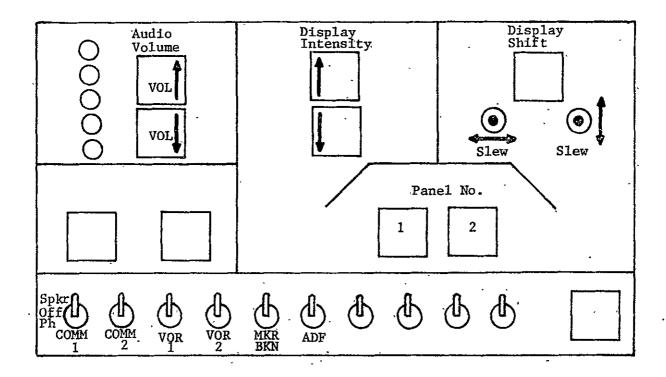

Figure 2.1 shows an IFR equipped Cessna 402 single pilot front panel. Both of the dual redundant displays can be used from the left seat. Below the center display is the mass memory cassette which holds navigation information. Above each display is a set of dedicated pushbuttoms that can be used to call up standard display formats. These are titled from left to right, FPLAN, PFLT, START, FSET, INIT, TKOFF, ENROUTE, LAND, SYSCNG which are nemonics for flight plan, preflight, start, frequency set, initialization, takeoff, enroute, landing, system change, and display change respectively. Below the flat display panels are switches with indicators that may be used to turn off, force on, reset, or assign to automatic operation any of the subsystems. A numeric input pad with entry clear is to the right of each display. Data is also entered by touching the face of the displays to indicate choices among displayed alternatives. The force overridable engine control quadrant resides in the usual location to the right of the pilot. Below the control quadrant is a control panel for adjusting audio level, display positioning, setting up the headphonespeaker audio paths, etc. An elapsed time meter used to make entries in the airframe engine, and avionics logs is at the lower righthand corner of the panel.

The left display is recessed into the panel while the central display projects out above the engine quadrant. This provides room behind the central display for the system avionics box.

Figure 2.1. Advanced Avionics System Panel Layout for Cessna 402.

#### FLIGHT SCENARIOS

#### Sample VFR Flight

In this scenario, to show the flavor of a "typical" VFR flight, all of the equipment for an IFR flight is presupposed, although it may not be redundant. For a less well equipped aircraft, just delete the help received from a particular piece of equipment.

Master power is applied by tossing the switch at the lower left of the instrument panel to bring to life those elements which are not always kept at the low trickle power level. Orange letters on the black panel background announce the time and date, while reminding the pilot to preflight the aircraft, and check the weather, if not already done. The pilot has already conferred about the weather, and runs through the lists available by touching PFLT to verify that the loading of the aircraft is in limits and that nothing else was missed during the preflight.

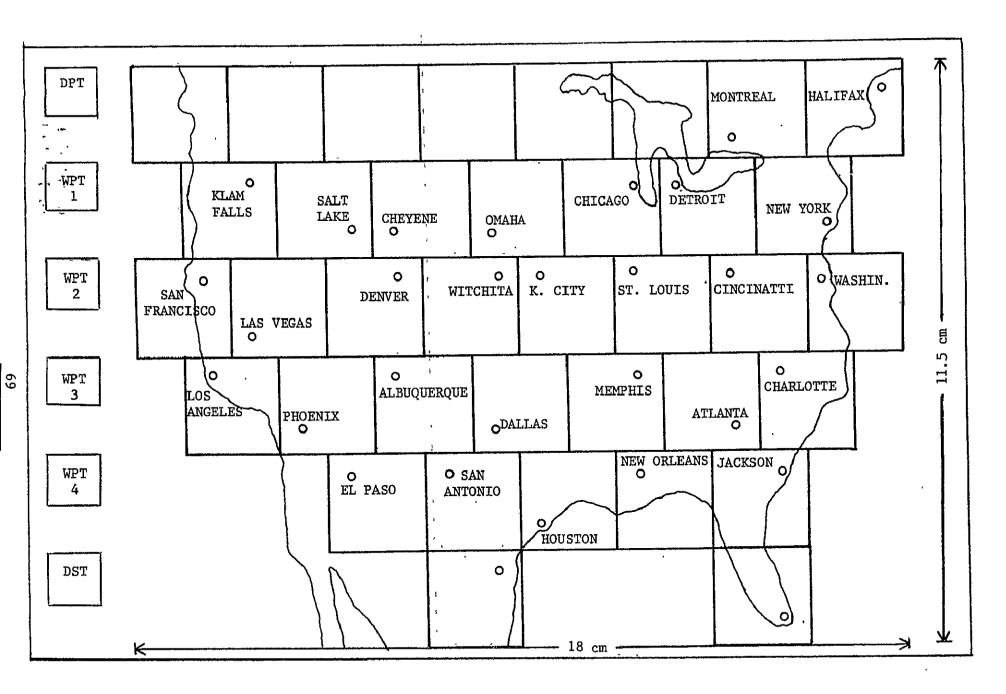

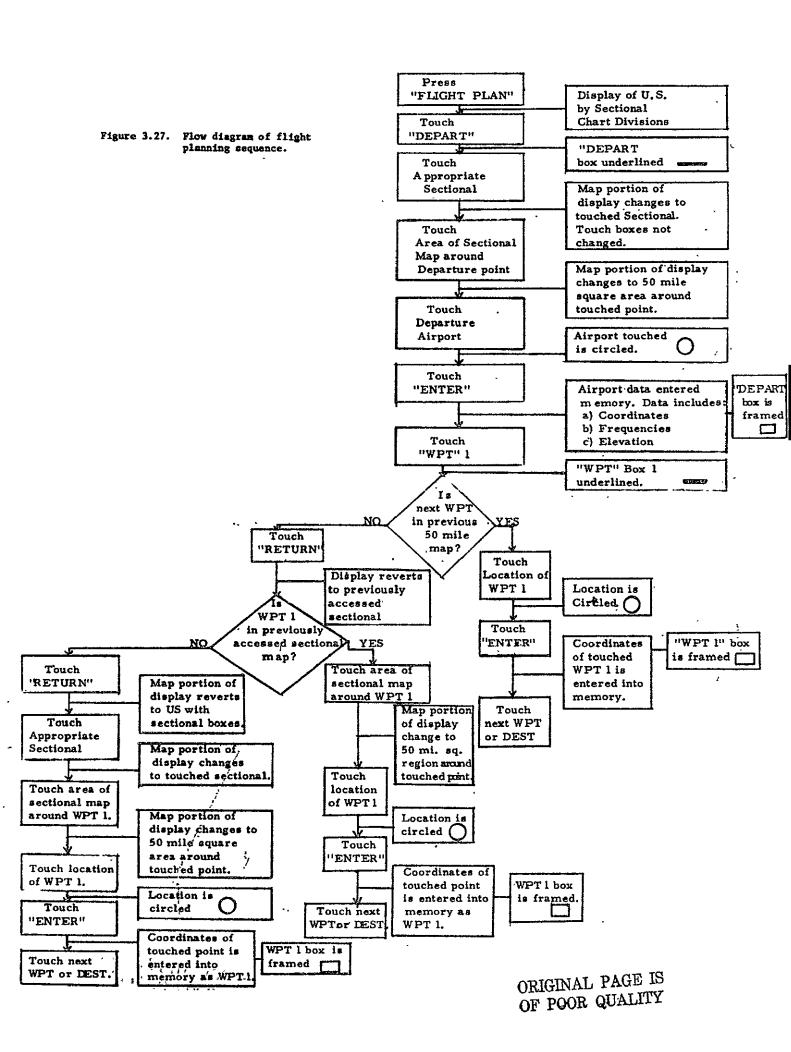

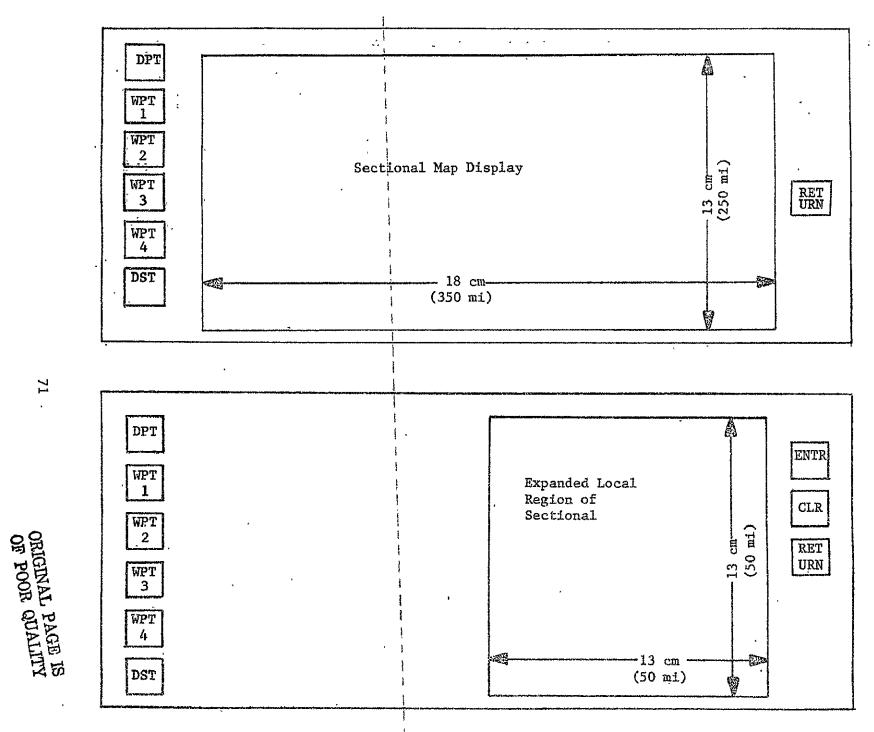

A push of the FPLAN button above the display in front of the pilot brings up a map of the United States at the same time the pilot presses the left engine start button. The engine roars to life and is adjusted to best idle speed with the right hand. Six taps of the left forefinger selects the departure and destination points on the three levels of electronic maps which are presented in sequence.

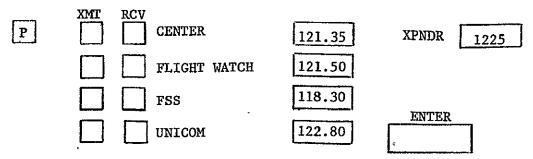

Navigational aids are selected from the mass storage tape. An appropriate route avoiding all restricted and prohibited areas is plotted on the map, now spanning the entire region of the planned flight. A map of the airport taxiways and runways may be called up by tapping the TKOFF button. The density altitude and the go-stop takeoff runway length is displayed on the airport taxiway-runway map. This button also makes available an enlarged (third level) map containing the airport as used in the FPLAN display. In addition the taxi and takeoff checklists are available in this mode of display at a tap of a finger. ATIS, ground, Cpt, tower and departure frequencies have been selected from the weekly updated navigation tape, which most VFR pilots purchase every six months. ATIS is tapped to obtain the airport departure information, which is too loud. Volume is adjusted to a lower level by holding down the level reduce button, located on the center pedestal below the engine control quadrant. A tap of Cpt, and acknowledgement by the voice in the speaker, leads the pilot to transmit destination, aircraft type and desired altitude. A transponder squawk is assigned. This is easily entered into the buttons to the right of the panel and each number is echoed back to the pilot by the voice generation subsystem and also accumulatively displayed in the entry verification box as it is depressed. One number was wrong. A push of the CE button, and the entry is quickly corrected on the keypad. Transponder is selected by tapping a spot on the display panel. Similarly the altimeter setting could be provided to the system for a check with that obtained automatically by the dual barometric pressure transducers and the stored airport altitude. disagreement between the barometric pressure transducers produces a request by the system for an external altimeter setting from the pilot. Entry via the right hand keyboard and touching the corresponding box of the display

allows the system to conclude that barometric pressure sensing component set #1 is not functioning properly and the #2 set is within limits. is next tapped switching the communications frequency to this value. A press of the yoke transmit button and a few words clears the pilot to taxi to runway 36R with tower frequency 118.2. This is different than most aircraft use for this airport so the pilot taps a spot on the panel selecting this choice of frequency rather than the one brought up as the (All possibilities are displayed with a dot showing which automatic choice. has been selected). The usual frequencies for an airport departure are made conveniently available on the TKOFF display for a mass memory stored But any frequency in the system is easily set by pressing the FSET button, which causes all the different frequency set devices in the system to come up on the display. After the righthand keypad has been used to key in values, each number dutifully echoed both aurally and at a spot on the display, the appropriate box is touched. The display acknowledges by filling in the box, and the sound system says "tower" or whatever. The aural system can be turned off like any other system, of course.

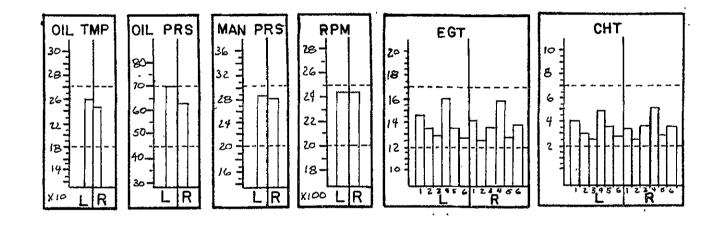

The usual pretakeoff tests were made by the system during taxi and will be continued at the start of the takeoff roll. Upon nearing the runway the pilot touches "tower" on the display and presses the yoke button to announce that the aircraft is ready for takeoff on runway 36R. Tower clears for takeoff. During rollout the system checks to see if the takeoff should be aborted. After flying speed is reached the display switches from runway layout to departure map. This may be forced by pushing ENROUTE, selecting U.S. map, and areas like in the FPLAN display. On the left side of the display in front of the pilot is a vertical situation display. An engine monitoring display is usually placed in the center display above the engine quadrant. The map and VSI can be switched by pressing the slew toggle which can shift the wrap around display in either direction. The ENROUTE button gives a detail of the enroute segment about the aircraft, and is obtained initially when the button is pressed. ENROUTE thus makes available all of the departure, enroute, and arrival maps that the pilot might care to study. But, mostly this button is used to select the enroute map about the aircraft's current position.

Soon after departure the display begins to shift as the aircraft proceeds along the route. It was not necessary to press ENROUTE since the avionics knows that the local traffic area display has become invalid. Since this pilot likes to keep flying skills sharp, the automatic pilot has not been engaged and the pilot hand flies the aircraft over the countryside occasionally glancing at the map display for pilotage landmarks to observe. The map and the scenery agree as the approximate planned route is followed. Nearing the destination, the airport and its frequencies become available on the map. Music has been tuned in on the ADF broadcast band, but the pilot now sets the upcoming approach control frequency into the priority position of the audio control box. Shortly the music is interrupted as another pilot calls the airport, and is answered. Any of the various communication functions can be assigned priorities in any order desired. This is done by pressing the P on the display the number of times that entries will be made, and then touching functions in the order of priority. Approach is touched and the yoke mike keyed to report the aircraft. A sequence similar to, but in reverse is followed as the aircraft moves through the sequence ending with a taxi to the ramp and shutdown.

If the autopilot has been engaged, then the route would have been followed precisely and the pilot alerted when the airport approach control zone neared. All of the pilot's time could be used for scanning. Inclusion of fool-proof collision avoidance will remove even this requirement.

Departure and arrival at noncontrolled airports are even simpler. Only the unicom frequencies come up on the display with the taxiways and airport layout. Of course radar frequencies along the route are provided for the pilot to use if this service is desired.

Instrument Flight Rules.

IFR flight could start similarly to the VFR flight, but would have the following differences:

- 1. The switch to departure frequency or ARTCC must be made.

- Constant radio communication would be maintained and an exact flight path would be flown, probably on autopilot.

On both VFR and IFR flights potential weather problems would be overlaid on the map enroute display from data obtained using radar or electrical activity detection.

#### Emergency Procedures

During a rushed departure and takeoff the left engine fails before single engine speed is reached in the Cessna 402. The aural system states "nose down" while the panel airspeed flashes to indicate insufficient airspeed has been attained. Excessive yaw causes the right engine power to be reduced as corrective rudder is applied and the transponder squawks an emergency. 'Calculations are instantly provided the pilot to show the available options, i.e.: to land on the runway ahead, circle back, or try to stop straight ahead, based on speed, altitude, weight, runway length and wind-providing the pilot entered any required additional information prior to takeoff! This data had been entered in haste by the rushed pilot.

At higher altutudes the alternate airport possibilities can be provided to the pilot as well as landing or ditching procedures when time permits preparation.

Failure of portions of the system are brought to the attention of the pilot and alternative reconfigurations suggested along with the possible consequences. These are worked out with deliberation and by experts for rapid use by the pilot during an emergency.

In this case the pilot is skillful at engine out procedures in general and quickly dips the aircraft to attain single engine speed and climbs to pattern altitude as full power is resumed in the right engine. (Next time, back to more conservative takeoff speeds!) At left base the left half of the main display becomes blank. A quick push of the left slew button restores the VSD and returns the system to pilot messages normally presented on the right half of the display. At this point the right engine sputters also and the system announces that the fuel flow is below limits. One suggested cure is to turn on the fuel selector valve to the right inboard fuel tank. This quickly revives the engine. Nevertheless the pilot has been informed that the field is within gliding distance. Next time, the pilot resolves to use the optional preflight check list IN FULL.

#### HARDWARE DESCRIPTION

#### DESIGN INTRODUCTION

This integrated avionics system design has been carried out to the level which indicates subsystem function, and the methods of overall system integration. Sufficient detail has been included to allow identification of possible system component technologies, and to perform reliability, modularity, maintainability, cost, and risk analysis upon the system design. In addition the organizational detail is adequate to serve as a starting point for a detailed system design and analysis based upon the adopted system approaches.

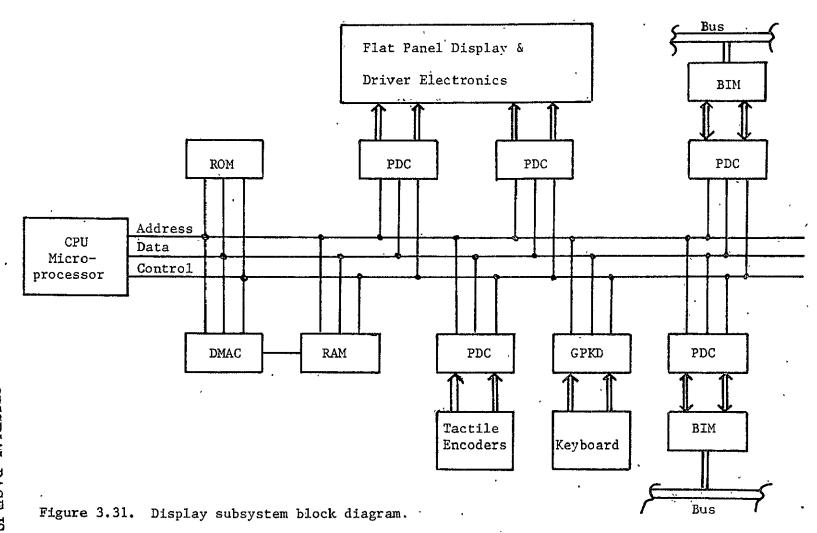

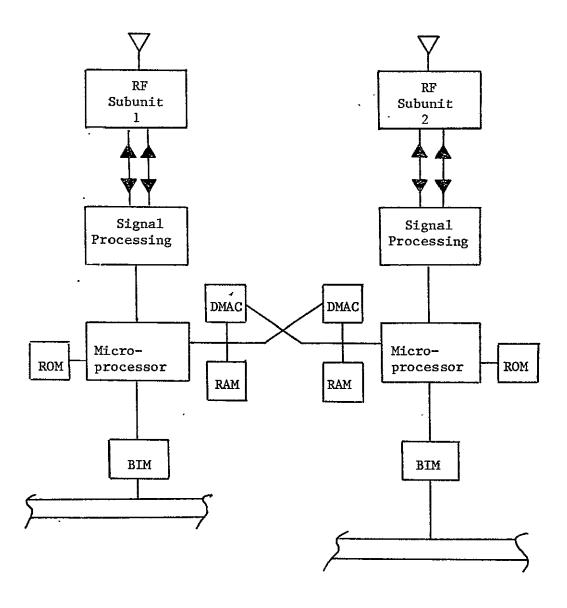

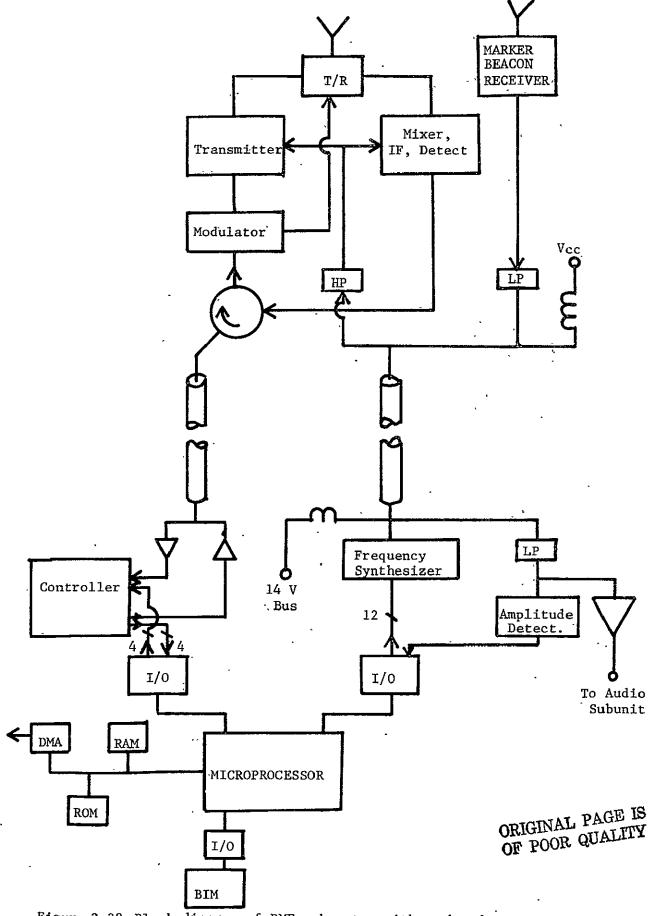

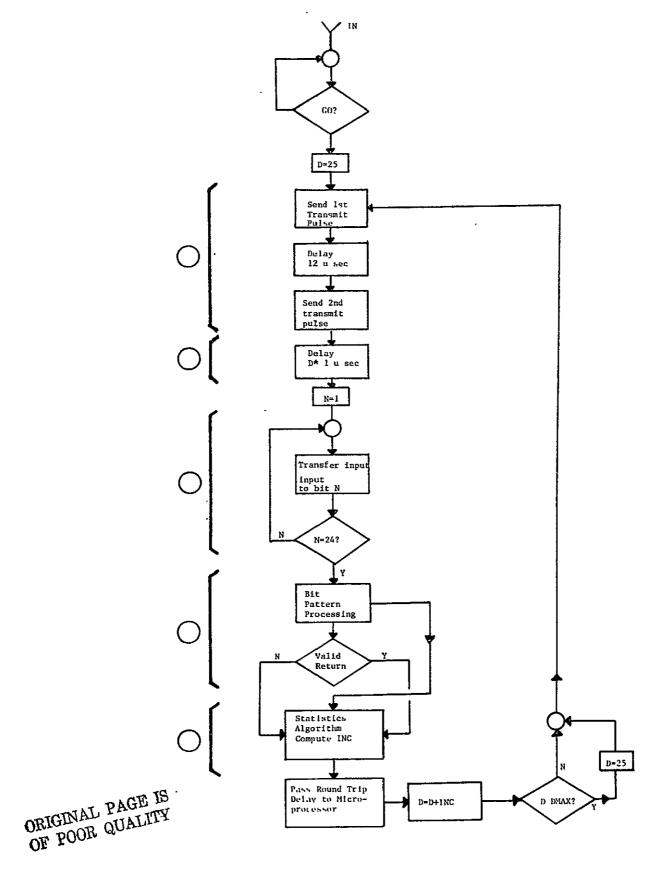

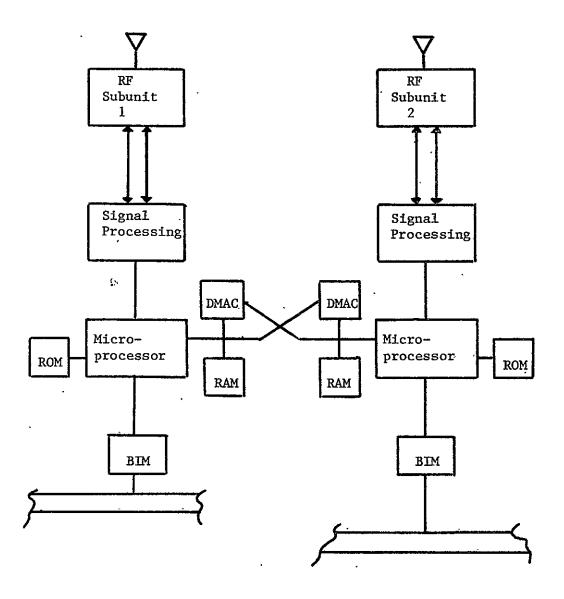

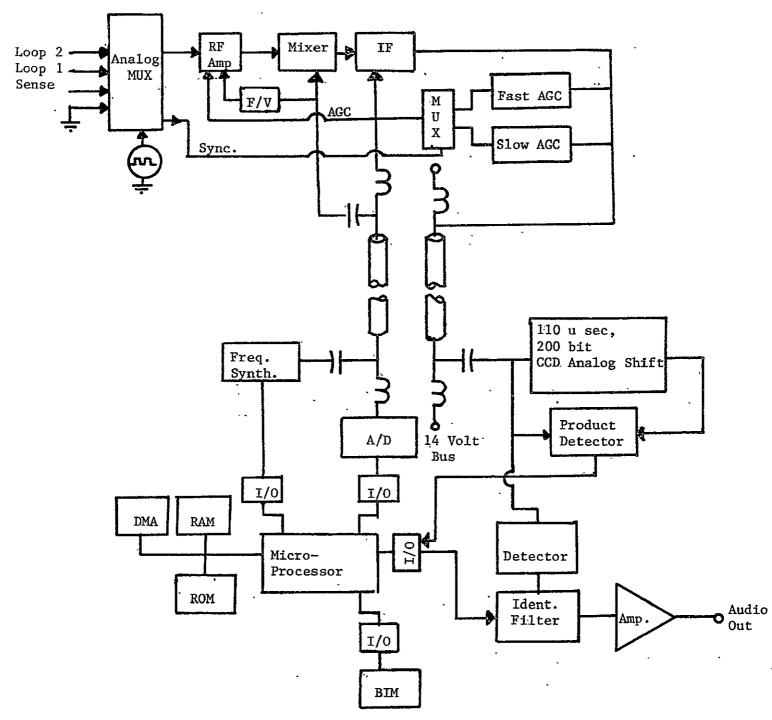

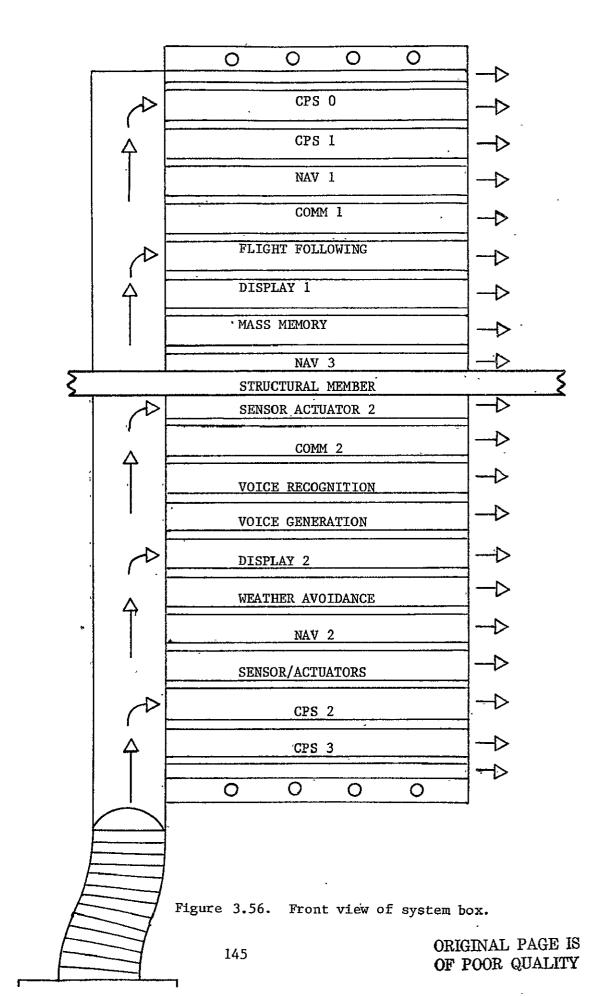

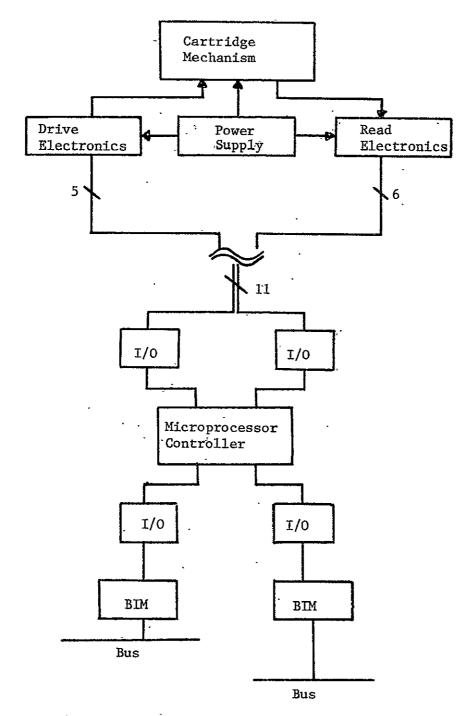

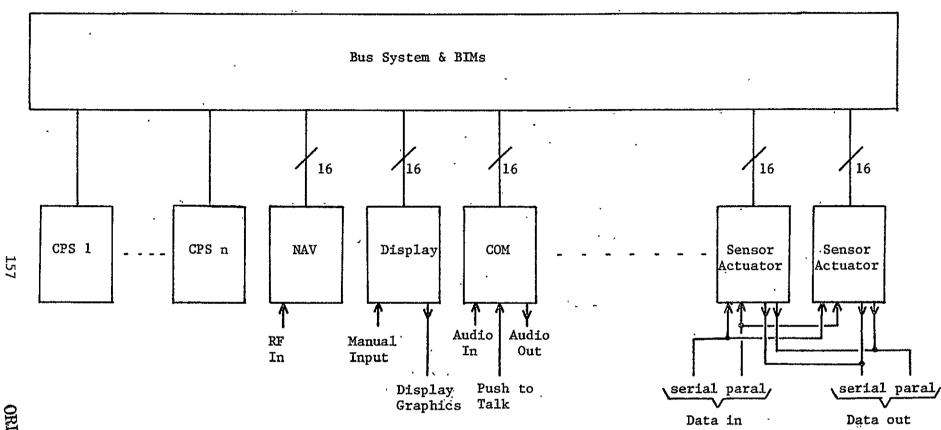

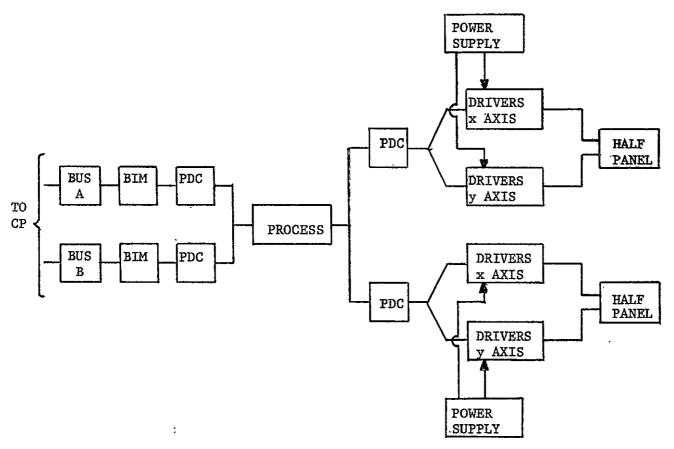

A high reliability team architecture for the Central Processor along with a triple redundant parallel IEEE-488 bus system comprises the heart of the system organizational approach. Subsystems are plugged into slots located in a single integrated system box. In twin engine aircraft, serial bussed service modules may be located remotely to serve groups of sensors and actuators. Normally two flat panel displays provide output to the pilot, while input is provided via dedicated buttons, the touch sensitive flat panels, and a separate keyboard. Figure 2.1 depicts the front panel for a Cessna 402 aircraft. Sensors are distributed about the aircraft, as well as the actuators for the control surfaces, and the quadrant engine control actuators. The sensor-actuator-antenna distribution is shown in figure 1.2. All aircraft system functions are integrated including navigation, communication, aircraft attitude, display, etc. as shown in block diagram form in figure 1.1.

Triple redundant IEEE-488 instrumentation buses along with a redundant team architecture central processor form the system framework. Versatile sensor-actuator and display subsystems exploit this new integrated approach along with advanced navigation, communication, flight following and weather avoidance subsystems as described in the following pages.

#### BUS SYSTEM

The bus system consists of three redundant sets of 16 conductors each. Communication between subsystems takes place only over these conductors. The characteristics of the lines, the drivers and receivers, and the protocol are described in IEEE Std. 488-1975. This system design adopts the standard completely except for several small points. They are:

- a) Each receiver shall be designed so that if the line voltage, V, is  $\leq 0.4$  volts, the input current, I, must be greater than  $\sim 0.4$  ma.

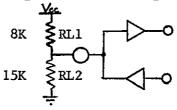

- b) In addition to (a) above, the composite bus tie point resistance (receiver input, terminating resistors and driver leakage) must be such that if V > 0.4 volts, I must be > -1.5 ma. With the receiver specification given above this implies an increase of termination resistors to RL1 = 8K and RL2 = 15K. See figure 3.1

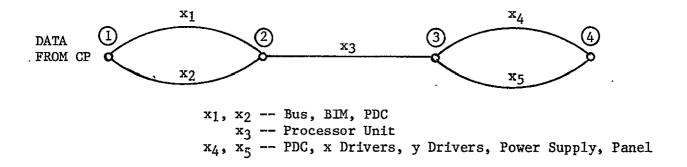

Figure 3.1 Bus tiepoint diagram

This is compared to the 3K and 6.2K values used in IEEE 488-1975, page 51.

c) The mechanical specifications, section 4 of IEEE 488-1975, are not applicable to this design.

The effect of these modifications is that total subsystem count can be increased from 15 to 31 without increasing driver capacity.

The receiver characteristics identified above are easily met with low power Schottky  $T^2L$ , MOS, or CMOS circuitry.

#### Configuration

The bus structure will be etched onto one layer of a multi-layer system mother board. The layers are:

- 1) Bus and signal lines

- 2) Ground Plane

- 3) System Power (14/28 volts)

The bus lines are to be 1.0 mm wide lines on 2 mm centers. Line thickness shall be plated up to 0.125 mm. A cover flash of electroless gold followed by a silicon elastomer conformal coat is used to provide environmental protection. Connection to the bus is carried out with miniature connectors, similar to the Elco 8000 series, soldered to the conductors and riveted at end parts. Connections to power and ground planes will be made by use of plated through holes.

#### Bus Interface Modules.

The system makes use of two types of commercially available BIMs. These units are designed to provide all bus protocol operations and actual data transfer.

The BIM used with the CP subsystems is similar to the Zia Tech 80. It is a microprocessor-memory unit which carries out bus related activities via program control. This BIM implements all 488 defined state diagrams and can pass and receive the control attribute. Memory of these BIMs is an extension of subsystem memory and hence it becomes an integral part of the computer subsystem.

The BIM block used on all other subsystem cards is similar to the Motorola 68488 LSI device. (Actual availability of the 68488 is scheduled for last quarter 77). These devices provide the Talker, Listener, Acceptor Handshake and Source Handshake functions but not controller. Since only the CPS units can be controllers this is no limitation. These single chip devices are fabricated in MOS technology and integrated into the subsystem cards simply as an extended I/O modual.

The bus interface module is an inter-system compatable standalone unit which will carry out the direct decoding and communication

associated with the parallel bus protocol. (See IEEE Std. #488-1975

for specific requirements). It must respond to queries, recognize

primary and secondary addresses, perform all "handshake" functions,

transmit "requests for service" signals, and act as a channel for

data flow from bus to subsystem. The BIM will be a general low

cost LSI circuit capable of being used at any bus interface location.

It will be capable of being "programmed" to any of 31 addresses

through the use of 5 external strap pins which will be returned

to either Vcc or ground.

Communication over a 488 bus takes place using two 8 bit bidirectional line sets. One set will be restricted to transmission of data bytes, secondary addresses, and status bytes. The other line set is to carry local interface messages.

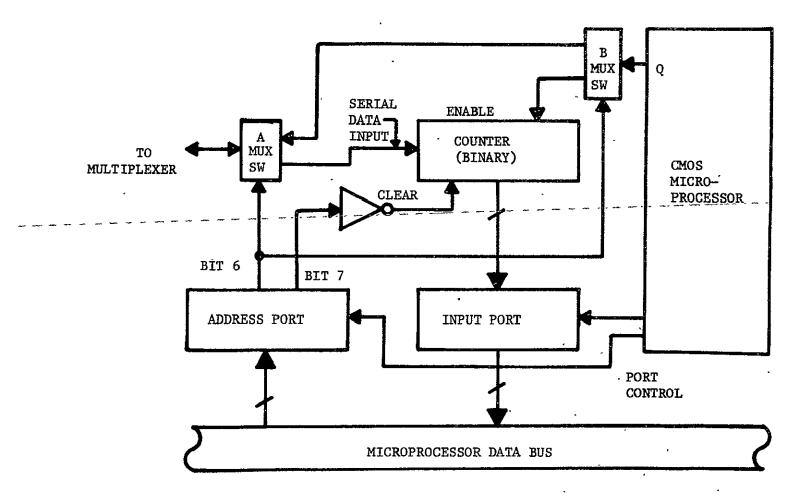

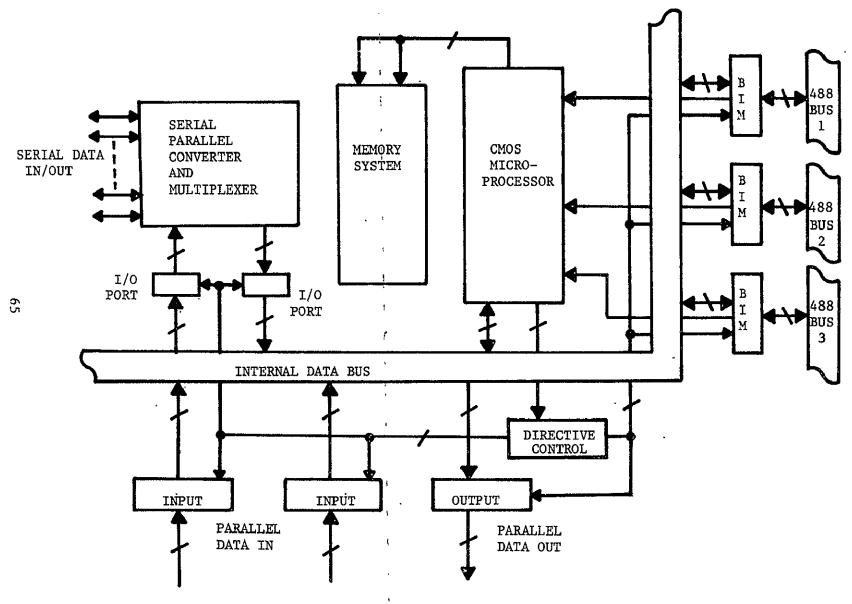

#### CENTRAL PROCESSOR

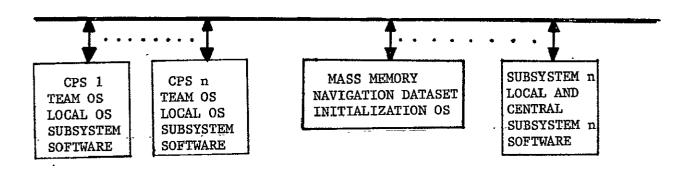

The central processor (CP) controls all major interchanges of data between subsystems, system modification actions, and generally anything of a system supervisory nature. One to four or more central processor subsystems (CPSs) in a team architecture, along with a mass memory device comprises the overall CP. Communication between the CP and other subsystems, as well as interchanges between individual CPSs is all performed via three system IEEE-488 information buses. Software for the system is distributed among the individual subsystems, the CP mass memory, and the CPS team members as shown in figure 3.2 System time is kept by each CPS.

Figure 3.2. Distribution of software in system.

ORIGINAL PAGE IS OF POOR QUALITY

#### Team Architecture

The team architecture is a combination of a hardware configuration and a software configuration. When the system is provided with multiple Central Processor Subsystems, the structure provides for continued system operation as long as at least one CPS and one bus is operational. The team operating system (TOS), comprised largely of a collection of tables and software for modifying those tables, with the 488 bus system, provides a means of efficiently carrying out a cooperative effort on the system CP work load. The team architecture has no single critical element such as a common voter element to determine CPS operational validity. On the other hand, each CPS is connected to each 488 bus via a pilot resetable time out circuit (TOC). All hardware and software used during flight by the CP is repeated in each of the CPS team members. Sufficient capabity for emergency operation of the aircraft under IFR flight conditions is present in each CPS.

This design of the team architecture uses:

MULTIPLE 488 BUSES

MULTIPLE SELF SUFFICIENT CENTRAL PROCESSOR SUBSYSTEMS

MULTIPLE SETS OF CENTRAL PROCESSOR SOFTWARE

MULTIPLE SETS OF TIME OUT CIRCUITS

MULTIPLE PILOT OVERRIDE CAPABILITY

These components of the system are discussed separately elsewhere. This portion of the design description will thus conclude with a description of one possible TOS structure as shown in figure 3.3.

ID#

LEVEL

NEXT TASK REGISTER (NTR)

Figure 3.3. Team operating system tables.

Three tables and a next task word are used in this approach to the team OS. These are identified as the task table (TTBL), and the task que table (TQTBL), level table (LTBL), and the next task word. CPS RAM holds the TTBL and TQTBL as these do not normally change often during aircraft operation in a teamwork fashion. One exception is the dynamic modification of the software configuration due to hardware failure. In this case one bit in each word of the TQTBL must be altered in all the RAMs collectively. All other changes to these tables is a local CPS affair. On the other hand both the LTBL and the NTR are changed frequently by the team OS and so these tables are located in the memory of every BIM for every CPS.

Task (TTBL). The TTBL contains as many entries as there are CP programs which could be executed. The tasks may be placed in the TTBL in any order, but once placed, the position of the task defines its ID number. To elaborate, the first entry in the TTBL has the ID number 1, the second entry has the ID number 2, etc. Since each CPS is a sixteen bit machine, a single word contains sufficient capacity for each entry in the TTBL. The first bit in each entry is used to indicate whether the remaining 15 bits specify the starting location in RAM for the task or whether the software still resides in the CPS mass memory, and the task must yet be fetched under the label given by the remaining 15 bits. We arbitrarily will select 1 to indicate a starting address and 0 to specify a label for a program in mass memory.

Task Que Table (TQTBL). The Task Que Table like the TTBL has as many entries as there are CP programs which could be executed. The arrangement of tasks in this table is according to the ID number as defined for the task by its placement in the TTBL. The TQTBL is a linked list of task IDs such that all tasks at the same priority level will collectively form a circle linkage. Each entry is divided into two eight bit bytes. The high order byte specifies the ID number of the task which follows this task at the same priority level. Usually there are several priority levels in the system, and the software in each level will be linked in a closed chain by the TQTBL. The low order byte contains job flags, one for each bit, of which the last bit is defined to be the task Operational Status Bit (OSB). This bit specifies whether the task at that entry is to be executed or not. The system is generally free running and cycles among the tasks at each level. As a task is examined for execution in the TQTBL, this last bit specifies whether the software is to be executed in this transit of the circle of jobs at this task level. This bit is used to include or exclude tasks from running and allows rapid automatic reconfiguration of the system according to prestored bit

patterns. Arbitrarily we specify that when this bit is 0, it Indicates this task is not to be run, and when this last bit is 1, this task is to be executed when its turn comes up. A diagnostic routine is included by setting its OSB to 1, and software is deleted as equipment is shut down by setting the corresponding operational status bits to 0. Note that bits which are used frequently in the TTBL and TQTBL are located at the end of the word for ease of testing with bit shift programming.

Level Table (LTBL). The Level Table has as many entries as the system has priorities. The order of entries in the LTBL is according to priority, with tasks needing the most frequent service in the first level, which is designated level 0. Those tasks needing less frequent service are placed in level 1, etc. Each LTBL entry uses four eight bit bytes of the 2K bytes in each BIM. The first and second byte contain the ID number of the first task in this level to be executed, and the next task to be executed in this level respectively. The first task is left fixed once the OS is installed, while the next task is constantly changed according to the value in the TOTBL as software is executed. The third byte contains the level limit number (LLN). This LLN specifies how many times. the full circle of tasks at this level is to be executed, before operation transfers to the next level, for execution of one task from that level, before returning. The fourth byte contains the total number of times the circle of tasks at that level has thus far been executed. When the LLN is reached a task is run from the next level and the fourth byte reset to zero.

Next Task Register (NTR). These two bytes of BIM memory contains the ID number of the next task to be executed in the entire multiprocessor system. The first byte is used for the next task and the second byte stores the level from which the task was obtained.

Typically the system will start off with the table entries placed by an initialization OS (IOS) which configures the software system each time the aircraft electronics are modified. The team operating system will initialize certain entries each time the electronics are turned on. The tasks will have normal flight software specified for execution in the TQTBL (OSB =1) and all Lever Counter (LC) entries will be zero. The system begins execution at level 0 and selects the task stored in the second byte of the first entry of the LTBL. CPS#1 is initialized to the task in the high order byte of the level 0 LTBL, while CPS#2 is initialized to the task which follows

this in the TQTBL. CPS#3 then is initialized in its byte 2 of the LTBL to the task which follows the task given to CPS#2 as specified by the TQTBL, etc. The next task register is initialized to the next task in the linked circle of the TQTBL, which has not yet been assigned to a CPS.

When one of the CPSs finishes it's task it then looks at the NTR to find what to do next. The team OS in this free CPS then looks in the TQTBL to find what task follows the task it is about to perform. This is located in the first byte of the entry in the TQTBL which corresponds to the number yet in the NTR. The free CPS then places this number in both the next task register and the LTBL by becoming first the bus controller for all working buses, and then a talker on all working buses while commanding the BIMs for the other CPSs to be listeners. The LTBL and NTR are located in the portion of CPS memory that is part of the 2K BIM memory and so this operation does not necessarily interfere with the operation of the other CPSs. The 2K of BIM memory serves as a cache memory for each bus and CPS.

When the final entry in a level is reached, this will be noted by all zeros in the next task entry in the TQTBL. The team OS of a free CPS will then increment the LC for this level, and compare the LC with the LLN. If the LC is less than the LLN, the team OS will then select the next task as the number stored in the first byte of that level in If the LLN and the LC numbers are the same, then the team OS will select the task from the second byte of the next larger numbered level in the LTBL and place this in the NTR along with the higher task level number, for all of the CPSs in the BIM cache memories. In addition the first task in the first byte of the LTBL in the level which is about to complete a cycle, will be placed also in the second byte position of that level entry in the LTBL. These operations then set up all entries for all CPSs so that the next task will be properly selected by the next free team processor.

The length of time taken to run software, the size of the various LLN numbers, the level in which software is run, and the number of tasks in each of the levels all determine how often various tasks are executed. Crudely speaking, tasks in different levels tend to be run at an order of magnitude slower as levels increase.

This software timing design was performed to show that a method did exist for setting up the team OS. There is little doubt that other team structures can be devised but they have not been labored at for this contract.

#### Central Processor Subsystem (CPS)

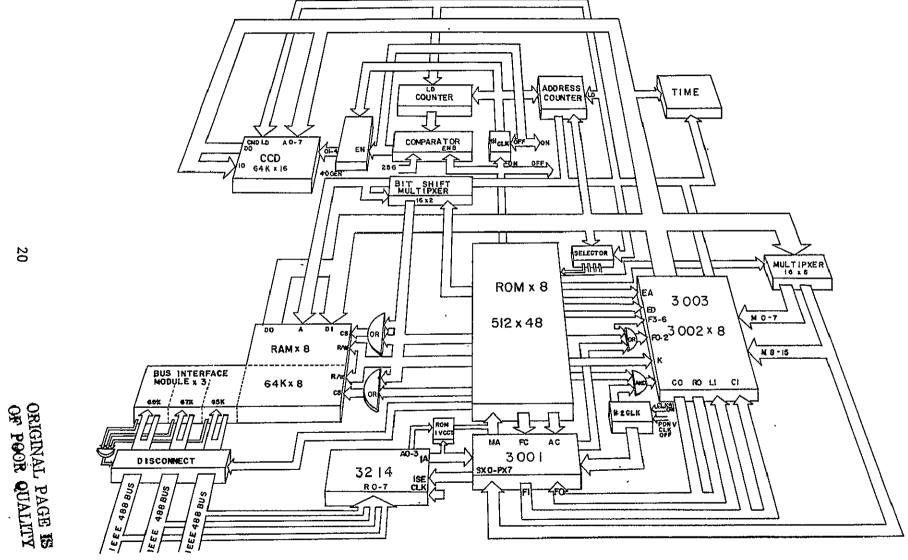

Each CPS is a total computer capable of independent operation of an emergency portion of the integrated avionics system as specified to the pilot in a placard and then available in detail electronically from the system. All components for each CPS, including memory, are mounted on a single printed circuit board which plugs into a single slot inside the system box. Each CPS accesses all three 488 buses through a Bus Interface Module (BIM) and a Time Out Circuit (TOC). None of the CPSs are specialized or dedicated to any other subsystem support function except as may be handled on a rotational basis by any team CPS. See figure 3.4.

Microprocessor. Each microprocessor is constructed utilizing mostly Intel 3000 computing elements and some additional ROM, OR, and multiplexer chips. In particular eight Central Processing Element (CPE) chips, one Microprogram control Unit (MCU) chip, one Interrupt Control Unit (ICU) chip, 64 Read Only Memory (ROM) chips, two multiplexers and a multiple OR gate chip are used. The microprocessor uses Random Access Memory (RAM) and Charge Coupled Device (CCD) memory to be described later. The macroprograms written by use of assembly or higher level languages, are stored in machine language form in the RAM for execution, and CCD for later retrieval and execution in Each macroinstruction in RAM causes one or more microinstructions to be performed as directed by the permanent microcode stored in ROM. Interpretive microcode for several different machines is stored in the ROM and can be selected from RAM merely by setting the bits of a latch multiplexer. In this system, code written for a Motorola M6800, a DEC PDP-8, or a DEC PDP-11 was written.

A microprogram contained in control memory initializes the machine when power is first turned on and supervises the fetching of a first macroinstruction from RAM. Each macroinstruction is decoded by a combination of MCU addressing and microcode deduction. This is obtained by the macroinstruction sending the MCU to a first ROM address where operations are performed which determine the next ROM address etc. Simultaneously, ROM bits are used to control the CPE chips, the memory, and whatever else the processor designer desires. When the microprogram flows through address row 0 and column 15, the interrupt strobe enable line of the MCU is raised. The interrupt system responds by disabling the row address outputs of the MCU, and by forcing the row entry address of the microprogram interrupt sequence onto the row address bus. This operation is normally performed just before each macroinstruction is fetched.

Figure 3.4. System Central Processor.

Eight CPE chips are connected to construct a 16 bit processor. The CPE array provides the arithmetic, logic and register functions under the control of seven microfunction bus input lines, designated FO-F6. These lines are decoded internally to select the arithmetic/logic section (ALS) function, generate the scratch pad address and control the internal multiplexers.

M-bus inputs are used to bring data from the RAM and CCD into the CPE array. Data on the M-bus is multiplexed internally for input to the ALS. The scratch eleven internal registers designated RO through R9 and T. The output of the scratch pad is multiplexed internally for input to the ALS. A variety of arithmetic and logic operations may be performed in the ALS including 2's complement arithmetic, incrementing, decrementing, logical AND, inclusive OR, exclusive NOR, and logic complement. The result of an ALS operation may be stored in the accumulator or one of the scratch pad registers. Separate left input and right output lines, designated LI and RO, are available for use in right shift operations. Carry input and carry output lines, designated CI and CO are provided for ripple carry propogation. The K-bus is used to mask memory inputs and to supply constants to the CPE from the microprogram.

The MCU controls the sequence in which microinstructions are fetched from the ROM, and provides for the storing of CO and the control for CI for the CPE array. Microinstruction sequences are mostly designated by using codes supplied to the MCU by a portion of the ROM words themselves. The MCU decodes these words by using the bit \_\_patterns\_to\_determine\_which is to\_be\_the next\_microprogram\_\_\_\_ address. Each address control function of the MCU is specified by an encoding of the lines designated ACO-AC6. Data on the macroinstruction bus, PX4-PX7, can be tested by the JPX function to determine the next microprogram address. Data on the secondary instruction bus, SXO-SX3, is synchronously loaded into the PR latch while data on the PX-bus is being tested. During a subsequent cycle, the PR latch may be tested by the JPR, JLL, or JRL functions to determine the next microprogram address. Flag logic control inputs FCO-FC3 are used to cross switch the C and Z flags with the flag logic input, FI, and the flag logic output, The interrupt strobe enable of the MCU is available on the output line designated ISE and is used to enable the interrupt control unit (ICU). This line is placed in the active high state whenever the location, row 0 and column 15, is selected as an address. The ICU in turn may respond to an interrupt on one of it's lines by pulling down the enable row address (ERA) input line of the MCU to override

any present ROM selected next row address. An alternative next row address is gated onto the ROM address lines to vector interrupt the microprogram and force it to enter a handling routine for whichever device requested the interrupt.

To aid in performing the macroinstructions from diverse machines, multiplexers are used to rearrange the bit patterns of the macroinstructions. At any one time, only one of the several rearrangements is enabled. Which rearrangement is in effect is selected by bits of the ROM stored microinstruction.

Microcode is stored in three groups of ROM. Each group of ROM is dedicated to the microcode required to perform the macrocode of a particular processor. In this system macrocode for the Motorola M6800, DEC PDP-8A, and PDP-11 were investigated. Each of the three groups of ROM are organized into 1024 addresses by 48 bits. A 2:4 latch demultiplexer and one ROM bit is used to help the MCU select the particular ROM group and address in that group for the current microinstruction.

The ROM microinstructions include the following fields:

| ACO-AC6             | (7 bits)  | Controls the next address logic for the MCU.      |

|---------------------|-----------|---------------------------------------------------|

| FCO-FC3             | (4 bits)  | Controls the flag logic of the MCU.               |

| LD                  | (1 bit)   | When this is in the active high state, the next   |

|                     |           | address logic of the MCU loads the data on the    |

|                     |           | instruction bus into the microprogram address     |

|                     |           | register.                                         |

| F0-F6               | (7 bits)  | The micro-function bus controls the CPE ALS       |

|                     |           | function and register selection.                  |

| K0 <del>-</del> K16 | (16 bits) | These mask bus inputs provide a separate          |

|                     |           | input port to the CPE for the microprogram        |

|                     |           | to allow mask or constant values to be injected   |

|                     |           | into the program.                                 |

| EA                  | (1 bit)   | Used to enable the address from the CPE to        |

|                     |           | the address bus.                                  |

| ED                  | (1 bit)   | Used to enable the data from the CPE to the       |

|                     | •         | data bus.                                         |

| CLK                 | (1 bit)   | It selects which of the two CPS clocks is active. |

| MPX                 | (3 bits)  | Used to select one of 8 multiplexer bit           |

|                     | •         | rearrangements.                                   |

| RW                  | (1 bit)   | Determines whether data is to be read or          |

| · •                 |           | written in memory.                                |

| CS                  | (2 bits)  | Used to select which or both bytes of RAM used.   |

|                     | ·/        |                                                   |

The additional 4 bits in each ROM word are free for future assignment in the detailed design of the control of the BIM or local mass memory, etc.

Local Instruction Memory. The active avionics macroprograms and the operating systems are stored in the 64K x 8 bit RAM/ROMs. Both the macroprogram RAM and ROM are random accessible. But the RAM portion can both be read from and written on while the ROM portion is only used for reading. Permanent portions of the OS and the routines used by it are stored in the ROM. Macroprograms used in the avionics subsystems, especially those stored on the CCD memory, and those programs which are dynamically altered, as well as data from the 488 buses may be temporarily stored in RAM. Most of this portion of the memory is expected to be RAM, but the exact proportions are a matter for the detailed system design. Normally both 8 bit bytes are selected for reading or writing from the microprocessor as designated by the RW bit of the ROM microcode. Another two bits of ROM are used for the chip select (CS) input of each RAM to enable byte or full word operation. Three hundred nanosecond RAM has been chosen as a companion to the 150 nanosecond microcode cycle time.

A section of denser mass memory is also included in this system design. This memory could be bubble memory to take advantage of the nonvolitility property. It is not clear at this time which will be the best to use ten years in the future. CCD memory is expected to be secure in this system because of the backup power supplies used. CCD memory avoids some of the additional electronics needed to support bubble memory.

As seen in figure 3.4the CCD memory is 16 bits in. width. The device is configured as 16 chips each with 64K bits of memory. The chips are arranged into 256 tracks of 256 bits on each track. A track is merely a 256 bit CCD shift register. The local OS loads one of the 256 addresses into AO-A7, selecting a track on each of the 16 CCD chips. CE is decoded in the CMD register (CR) loaded from the A bus and the addresses are latched from the D bus. In addition, a starting memory address is loaded into the address counter by decoding a command from the A bus to load the actual address from the D bus. Data is read into the CCD or taken from CCD in block of 256 words. microinstruction uses a bit from the microcode ROM to turn on the CCD clock and turn off the main clock labeled #2 in the figure. The read/write bit will be set to control the RAM information direction of flow. Similarly the Write" Enable (WE) line of the CR will have been latched to the proper value at the same time the tracks were selected. The address

to the RAM is provided by the counter, and is incremented for each word read out of the CCD or written into it. So 256 contiguous words are either read from RAM into the CCD or are read from the CCD into the RAM. When 256 words have been counted, the comparator notes this fact and shuts down clock #1 and restarts clock #2. Thus the CPS does no computation, and is interrupted during these data transfers. Data can be transferred at the rate of clock #2. The system can be made much faster and of lower power by adding the hardware to scan the 256 tracks on the 16 CCDs instead of shifting down one track to transfer the words. But in this design, only little used diagnostic and system reconfiguration software is placed on the CCD. For this reason speed is sacrificed to save some hardware.

Cache Memory. The 2K x 8 RAM associated with each BIM provides the cache memory for each CPS. This memory is dual ported and so the BIM can place data in these locations without significantly interfering with the operation of the CPS. This is important since the operation of telling the other CPSs what the next task is, is fairly often recurring, and increases with the number of CPSs.

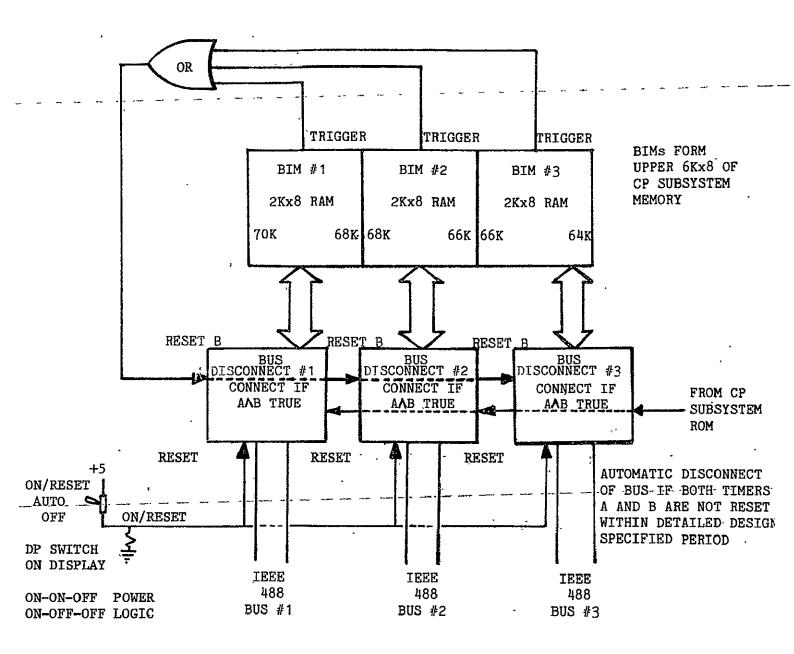

Time Out Connection (TOC). Each CPS is connected to all three system 488 information buses with a TOC. See figure 3.5. The TOC serves to disconnect the CPS from the bus should a specified period of time elapse both it and one other CPS resets the timing circuit. Thus for an individual TOC to be connecting the CPS to an individual 488 bus, the CPS itself has run a program which resets the TOC timer and another CPS has run a program which resets the timer. Of course the TOCs are powered up in the connected mode. The pilot has a switch for each CPS with separate circuits for each TOC, that allows for manual reset—on or off. All three TOCs are resettable from a single 488 bus or from a single CPS instruction. The time needed between resets before a time out disconnect occurs is a matter for the detailed design.

CP Mass Memory. A common mass memory unit which has access to all three 488 buses provides the following information to the CPSs. The location of electronic fixes, geographic features of the overflown area, and a copy of the initialization OS. These first two libraries are on a common An IOS tape is provided when the integrated avionics system is acquired. The IOS could also be ROM mounted on the mass memory subsystem card.

Figure 3.5. CENTRAL PROCESSOR SUBSYSTEM DISCONNECT TOC

Operating System OS. Three operating systems are used in this design. Each CPS uses a local operating system to fetch and run programs from the local mass memory as well as handle the bus I/O and local software linkages. For two or more CPSs in the CP, each CPS also has the team OS to coordinate the multiprocessing teamwork of the CP. In addition a third, initialization OS, is required to configure the CPS software at subsystem installation time. This last OS fetches system software stored in the individual subsystem memories, performs various system compatibility checks, and configures a local OS, team OS, and system software package for the CPSs. The distribution of software in the system is shown in figure 3.2.

<u>CP Functions</u>. Software performs the following functions in a fully implemented integrated avionics system.

The 488 buses will be supervised by the CP to grant access to the bus by all non CPS subsystems. In addition, for a CPS to have talker access to a bus, it must be a controller for that bus.

The CP shall dynamically supervise the actions of all subsystems to the degree they have been constructed to receive such supervision.

Flexible task slave subsystems shall be given their function by the CP. Such tasks shall remain fixed for a subsystem until changed by the CP. Similarly for multi-task subsystems.

The CP shall designate to subsystems the destination for all data transfers. These designations may be for single items or data blocks, and may be part of a task assignment.

The CP shall designate to all subsystems the source for all system bus acquired data. These designations may be part of a task assignment.

The CP shall perform the major part of the system verification checks for proper system operation.

The CP shall perform checks, automatically, to verify that the operation of the CP is correct. The pilot shall be notified of any CP malfunction detected. Tasks shall automatically adjust the CP operation to maintain system integrity when any CP malfunction is detected, as reasonably feasible.

The CP shall perform checks, automatically, to verify that each subsystem within the system configuration is performing properly. The pilot shall be notified, and the system software reconfigured to maintain system operation whenever any malfunction is detected.

The CP shall collect sensor data and compute suitable display and/or actuator commands for aircraft equipped with a flight director or autopilot.

The CP shall provide suitable display commands to enable the pilot to hand fly the aircraft relative to preset attitudes, altitudes, and airspeeds. If the aircraft is navigationally coupled, then visual, and/or oral commands will be issued to the pilot so as to enable the aircraft to be maintained on a 4-D flight plan.

The CP shall provide navigational computation for the system.

The CP shall with the assistance of electronic fixes stored in the common CP mass memory, and tactile input from the pilot, compute a flight plan for the pilot in accordance with prescribed ATC procedures. This flight plan shall be automatically transmitted and updated through the CP, which shall maintain a record of said plan, if the system, including ATC, is so equipped with direct digital link.

The CP shall have available a library of all electronic position fixes, for which the system is equipped to receive. The CP shall automatically command the navigational subsystems to both receive these fixes and compute appropriate coordinates.

The CP shall have available a library of terrain features which it relates to the aircraft flight path. The CP shall compute safe altitudes and issue warnings if a danger is detected. The CP or a designated subsystem processor will be responsible for all coupling and computation between the navigational subsystems and the flight director and/or autopilot capabilities.

The CP or a designated subsystem processor shall be responsible for monitoring the condition of all aircraft systems and flight parameters and providing timely warning to the pilot of any discrepancies detected from normal or designated conditions.

The integrated avionics system shall provide assistance to the pilot in performing tasks including but not limited to the following: weight and balance, passenger briefing, preflight inspection, start of engines, taxi check, pre-take-off check, flight planning and entering, flight plan alteration.

Helps will be primarily lists, aural system responses, and graphic displays. Automatic condition monitoring will be utilized as appropriate, including any other information the system possesses about the situation, to aid the pilot. In the prototype system some of these items may be loaded by tape cartridge into system memory.

The advanced avionics system shall have provision for assisting the pilot to act in coping with emergencies including but not limited to the following:

electrical power loss impending engine loss engine loss structural ice fuel low relative to specified destination and margins loss of any aircraft system lack of pilot input for more than a specified period impending impact with ground loss of ground to air following pilot sick (or totally incapacitated - passenger instructions) overheating of engine engine icing impending collision with another aircraft (dependent on ARTC implementation of DABS) hijack lost

Table 3.1. PROCESSOR SUBSYSTEM PARTS TABLE

| Description                                   | No. Chi<br>Hybrid<br>Groups | ips<br>Size<br>in <sup>2</sup> |         | Power<br>Total | Technology                 |

|-----------------------------------------------|-----------------------------|--------------------------------|---------|----------------|----------------------------|

| 2 bit Central Processing Element              | 87                          |                                | 1       | 8              | Schottky Bipolar           |

| Microprogram Control Unit                     | 1                           | 2                              | 1       | 1              | Schottky Bipolar           |

| Interrupt Control Unit                        | 1                           |                                | .5      | 1              | Schottky Bipolar           |

| Time Crystal (with counter in hybrid package) | 1                           |                                | .1      | .1             | MOS                        |

| 150 ns clock #2 (gated output, capacitor      | ) 1                         | .5                             | .2      | 1.0            | Bipolar                    |

| 600 ns clock #1 (countdown from #2)           | 1                           | .5                             | .1      | .1             | MOS                        |

| 64K x 1 Random Access Memory, 300 ns (proj.)  | 16]                         | 1                              | .5      | 8.0-           | 1 <sup>2</sup> L           |

| 1024 x 8 Read Only Memory, 100 ns (proj.      | ) 18                        | 9                              | .75 est | : 13.5         | Bipolar                    |

| 8 Input x 1 Line Multiplexer                  | 16]                         | 1                              | .25     | 4.0            | Schottky Bipolar<br>Hybrid |

| 2 Input x 4 Line Multiplexer                  | 4                           | 2                              | .25     | 1.0            | Schottky Bipolar           |

| Quad 2 Input OR                               | 2                           | 1                              | .25     | .5             | Schottky Bipolar           |

| Hex Inverter                                  | 1                           | .5                             | .25     | .25            | Schottky Bipolar           |

| 4 Bit Demultiplexer                           | 1                           | .5                             | .125    | .13            | Schottky Bipolar           |

| 8 Bit Counter                                 | 2                           | 1                              | .1      | .2             | Mos                        |

| 8 Bit Comparator                              | 1                           | .5                             | :1      | .1             | MOS .                      |

| 256K x 1 CCD                                  | 16]                         | 1                              | .25 est | : 4            | Mos                        |

| 4 Phase Clock Generator                       | 1                           | .5                             | .1      | .1             | Mos                        |

| BIM                                           | 3                           | 1.8                            | 2 est   | : 6            | MOS Hybrid                 |

| Bus Disconnect                                | 3                           | 1.5                            | .2      | .6             | Mos                        |

| Voltage Regulator                             | ,                           | 2                              | 80% eff | 55.98          | Total                      |

The chips given in the table are placed in hybrid assemblies, which are in turn mounted on the processor subsystem printed circuit card. Total chip and hybrid area approximately  $27 \text{ in}^2$ .

Total power requirement approximately 60 watts, or 6.5 amps from avionics bus.

<sup>]</sup> indicates these chips are in a common hybrid package.

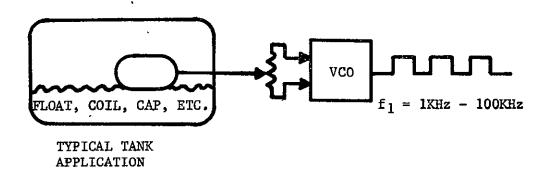

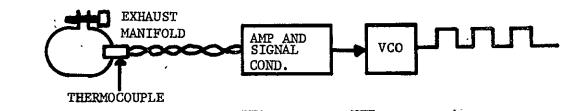

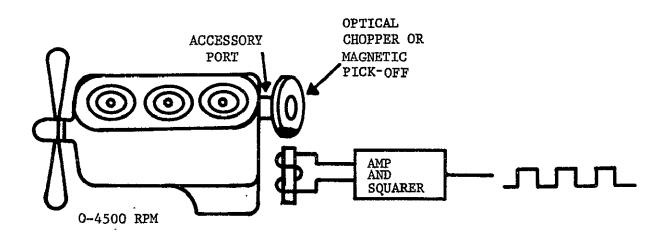

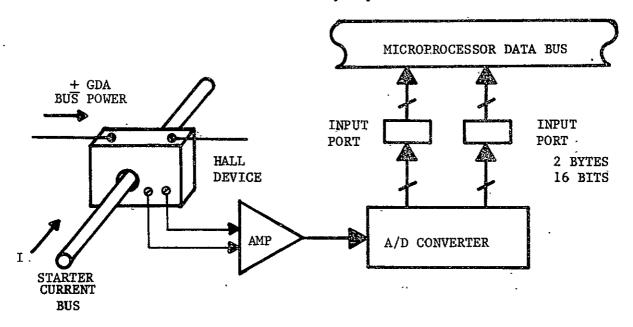

## SENSOR ACTUATOR SUBSYSTEM

# Subsystem Overview

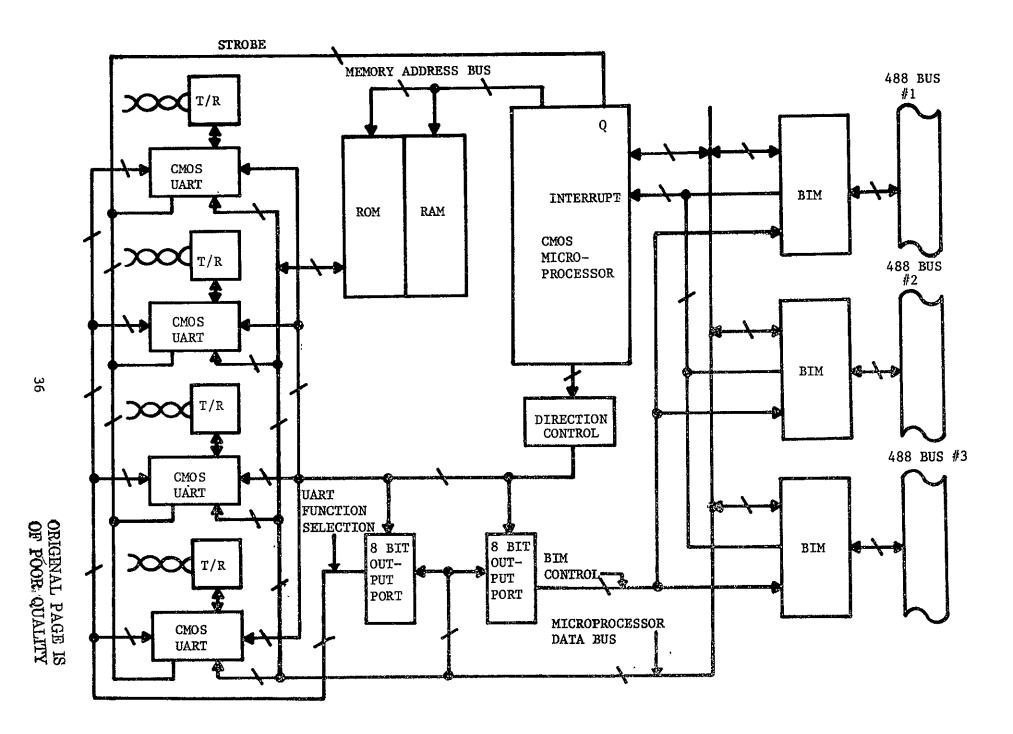

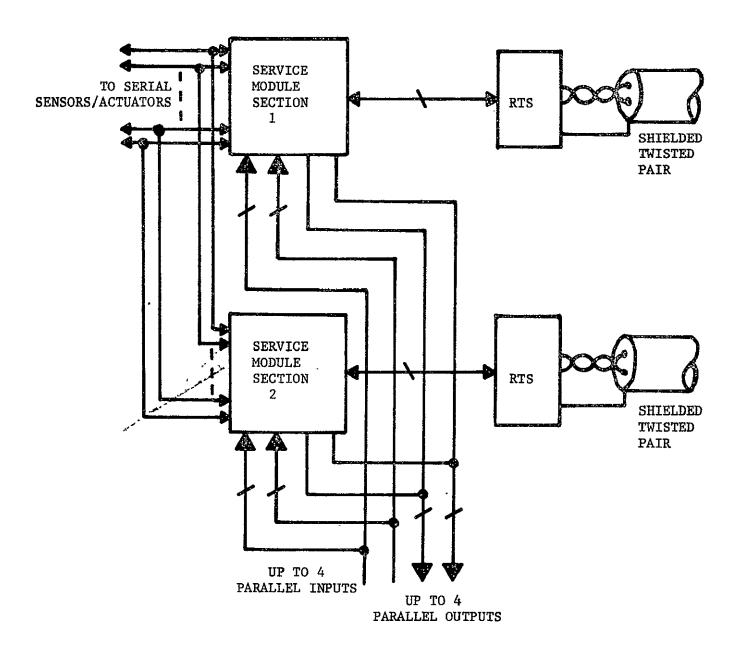

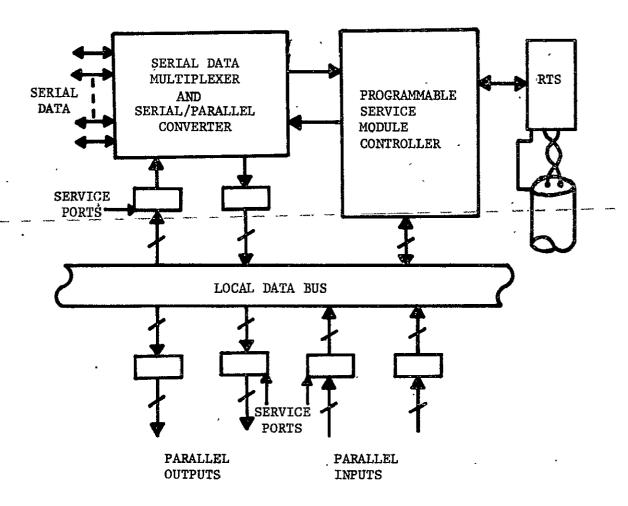

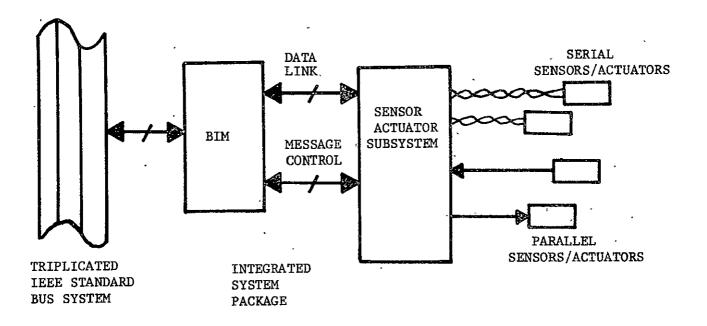

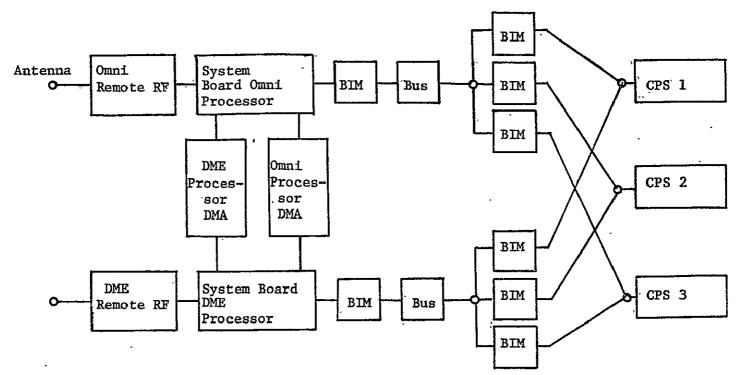

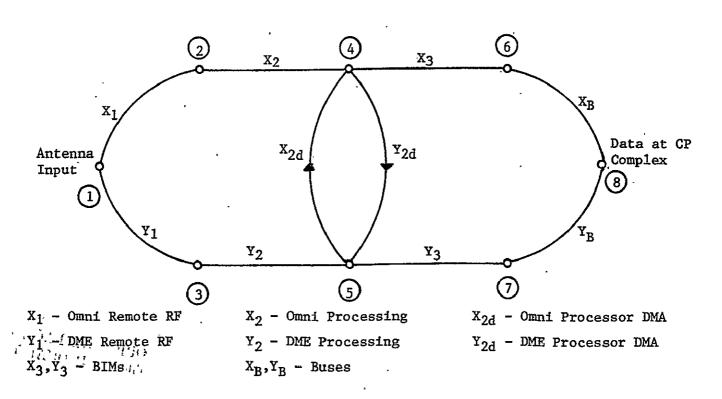

The Sensor Actuator Subsystem is a multiply redundant sub-system which is connected to all three IEEE standard 488 parallel integrated system buses, and resides within the integrated system package. External conversation with sensors or actuators will occur: (a) via a receiver transmitter system over a shielded twisted pair to a remote service module or (b) directly with the sensors or actuators themselves. Each subsystem will be modularly constructed and built up to the degree of complexity required by the aircraft in which it will be installed.

The most complex form will consist of:

- a) Bus Interface Modules (BIMs)

- b) Actuator preprocessor and subsystem controller

- c) Receiver/transmitter systems

- d) Remote transmitter/receiver

- e) Remote service modules

- f) Serial and parallel digital transducers

- g) Star connected serial transmission buses.

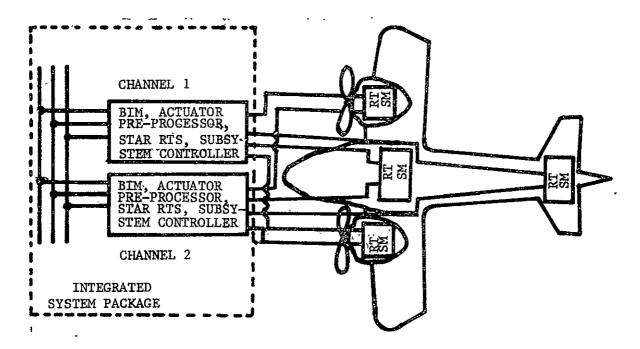

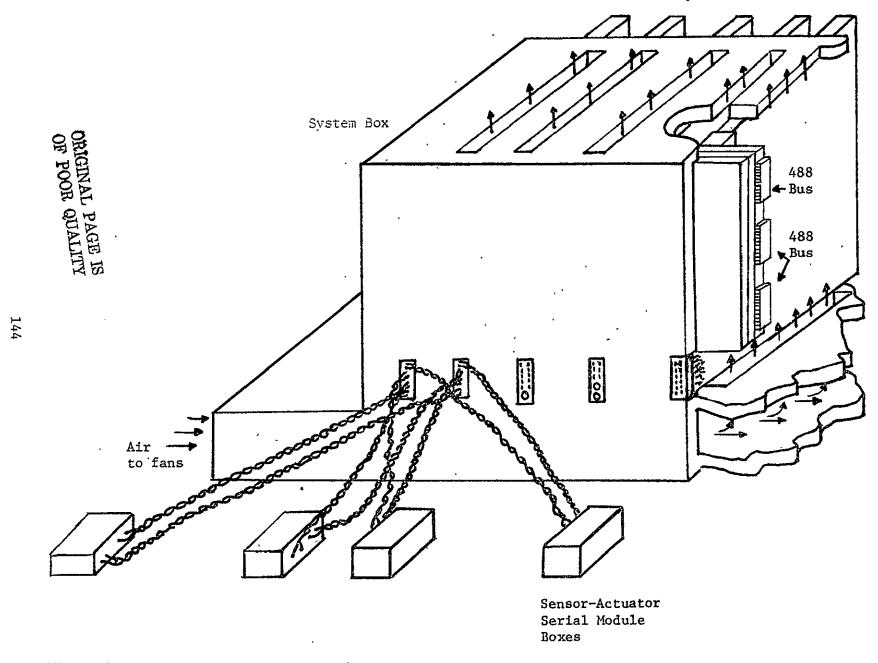

A typical system installation, showing maximum capability as well as suggested remote station locations is shown in figure 3.6. The system is multiply redundant and each microprocessor controlled service channel is capable of providing complete critical sensor/actuator data to the CP via one of three internal busing routes.

Figure 3.6. Typical system installation.

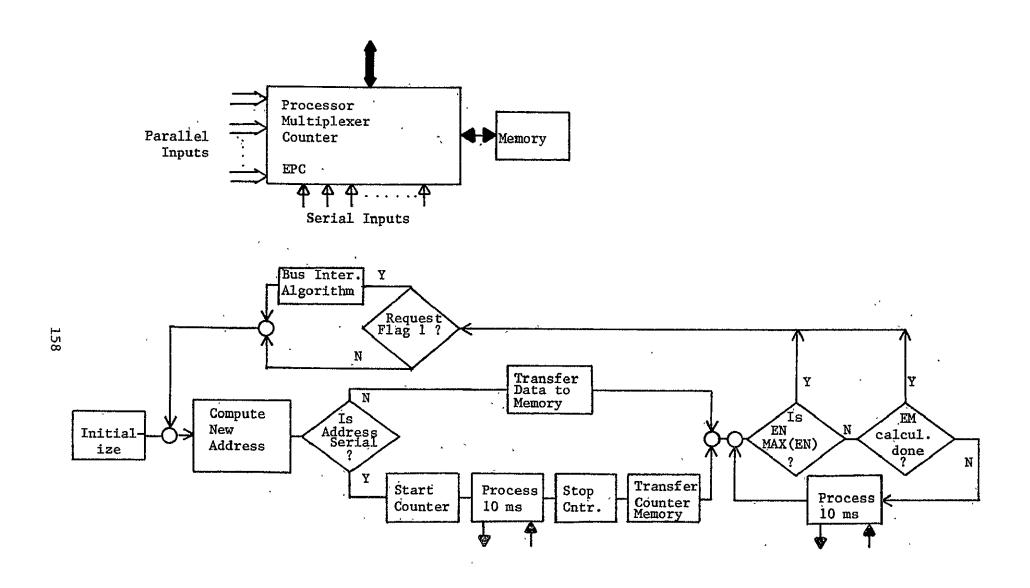

## Integrated System Package (ISP)

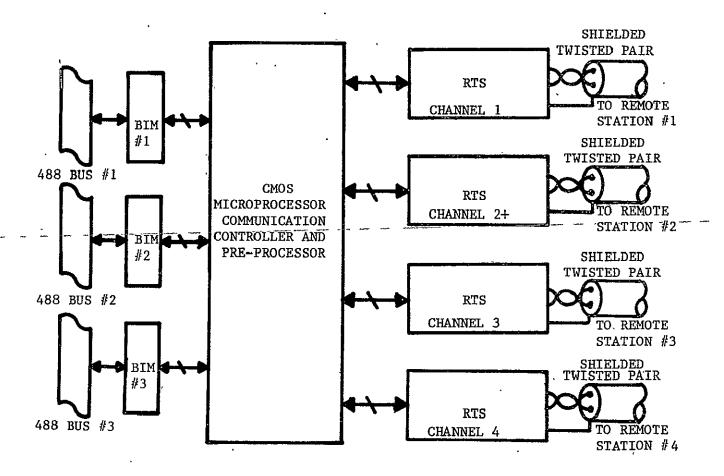

In order to maintain bus integrity and thus insure a high order of reliability for the CP team, all activity which relates to devices outside the integrated system package will occur through highly reliable, buffered, pre-processing units. Figure 3.7 shows the structure of one channel of the sensor/actuator subsystem components that resides within the integrated system package (ISP).

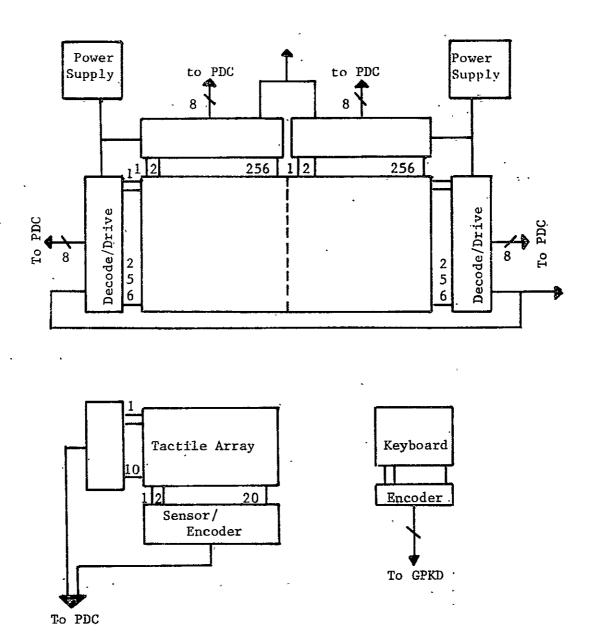

A maximum of four remote stations will be served by each of the two sensor actuator channels in the ISP. Dedicated lines to each individual remote station form a star configuration from the ISP. See figure 3.7. In order to minimize the program complexity, storage space and processor speed, a hardware rather than software approach will be used for the parallel to serial conversion and communication line protocol.

Figure 3.7. One channel of the sensor/actuator subsystem.

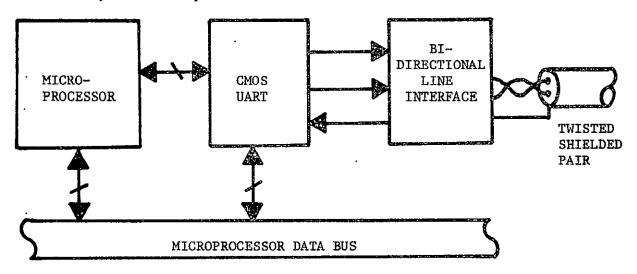

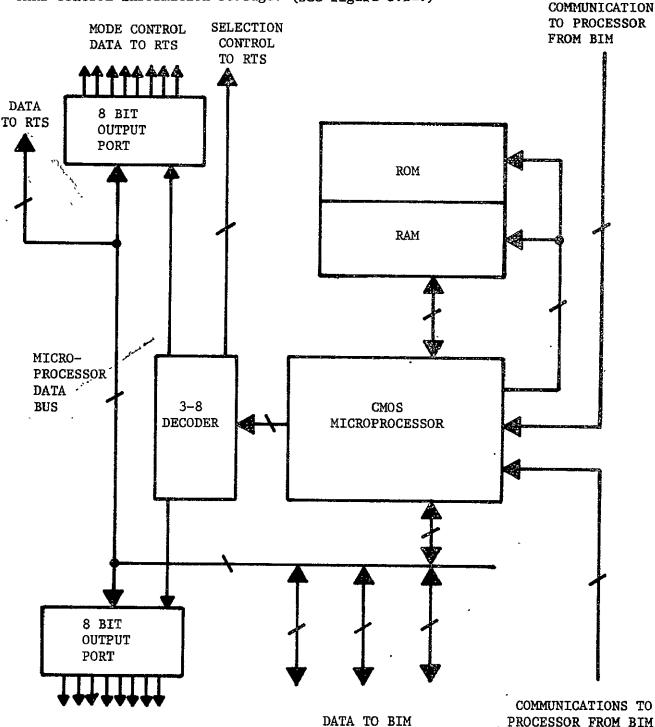

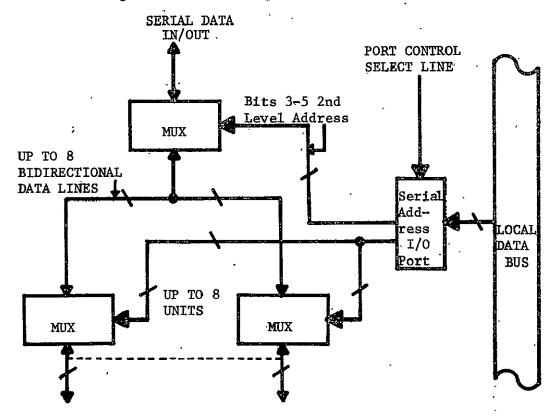

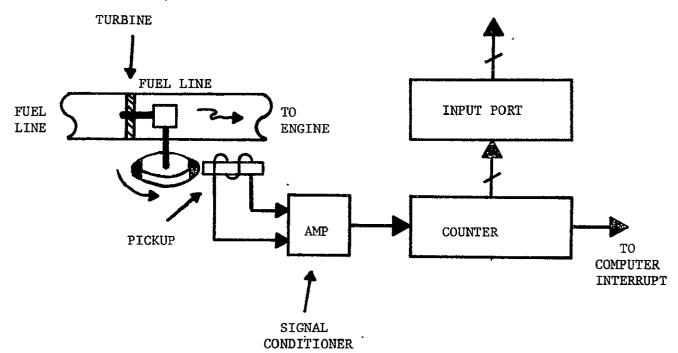

Receiver Transmitter System (RTS). Interface to remote sensor actuator service modules will be accomplished through bidirection data transfer over a serial data bus via a universal asynchronous receiver transmitter (UART) and a bidirectional transmission line interface, will accomplish the actual data transfer. (See figure 3.10).

Figure 3.8. Receiver transmitter system (RTS).

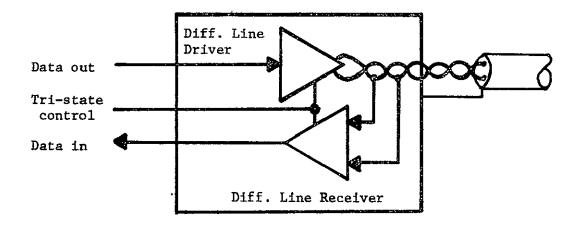

Transmission line interface: Communication to the remote stations is handled in a simple command-response mode. Should an out of limit condition occur, the CP will be made aware during routine data delivery by the system. Therefore no complicated protocol need be implemented at the remote station communication level. This allows all remote stations to reside in a listen mode (i.e. transmitters disconnected) until a request to transmit is received. The transmission line interface is therefore no more than a differential line driver with a tri-state output control, and a standard differential line receiver. See figure 3.9.

Figure 3.9. Transmission line interface.

Universal asynchrous receiver transmitter (UART): The UART consists of a receiver and transmitter designed to provide the necessary formatting and control for interfacing serial asynchrous data to and from the bidirectional transmission line interface. The receiver-transmitter is capable of full duplex operation and is externally programmable.

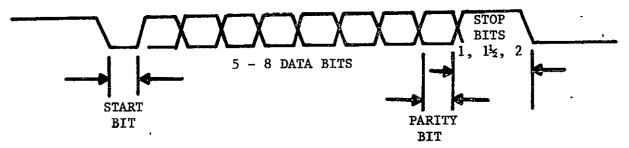

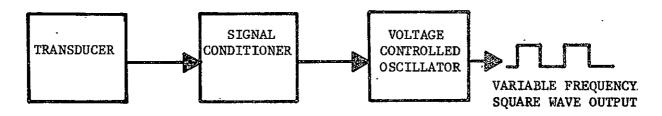

The transmitter converts parallel data to a serial block containing the data, (5-8 bits), a start bit, a parity (optional) bit and a stop bit  $(1, 1\frac{1}{2}, \text{ or } 2)$ . (See figure 3.10.)

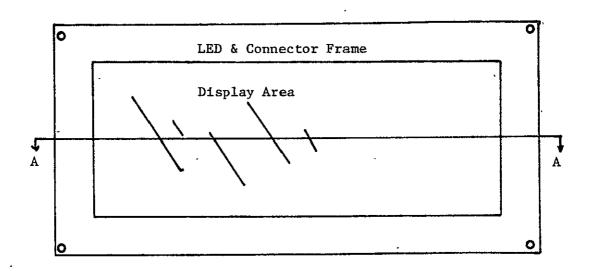

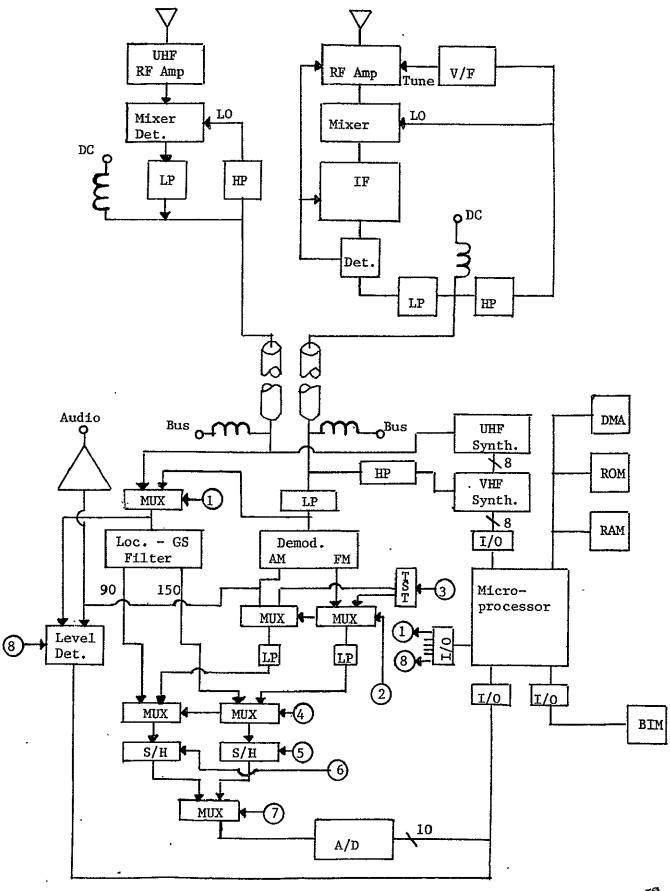

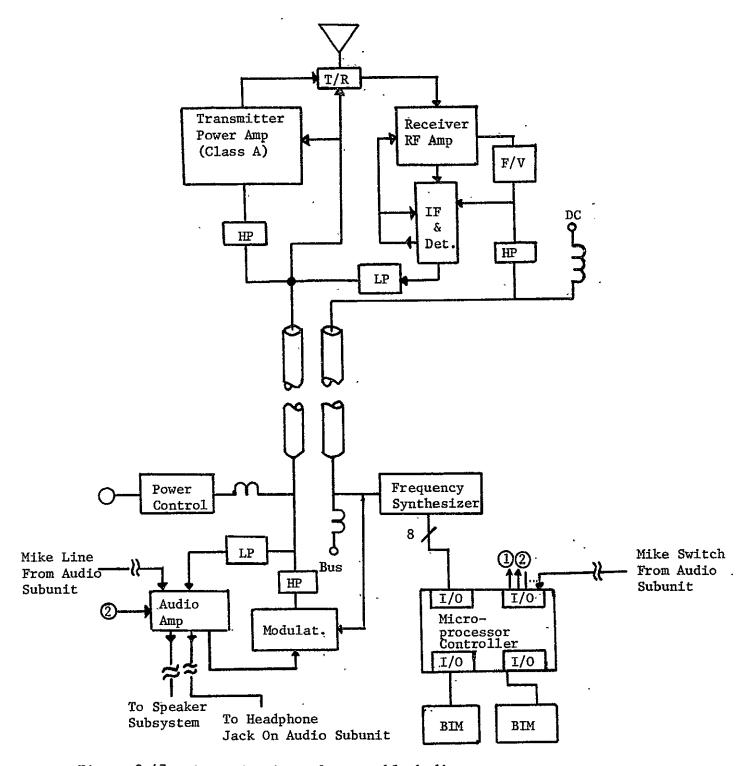

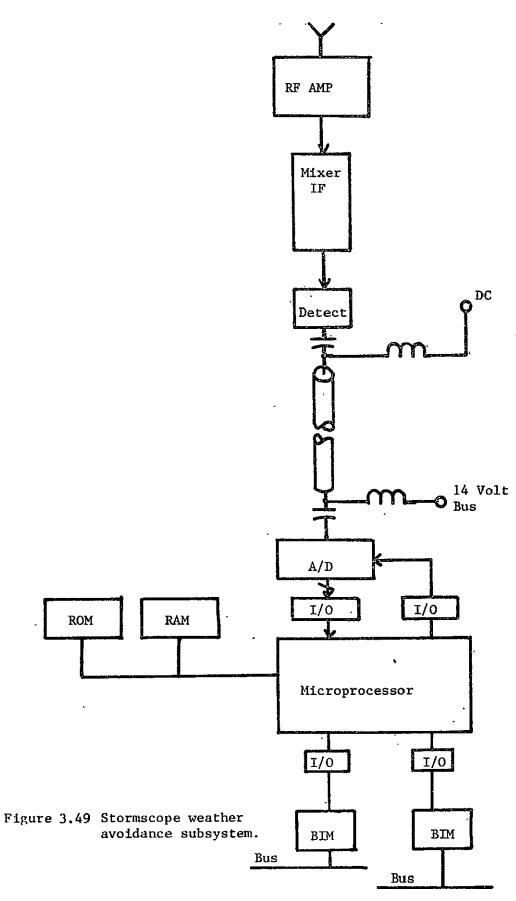

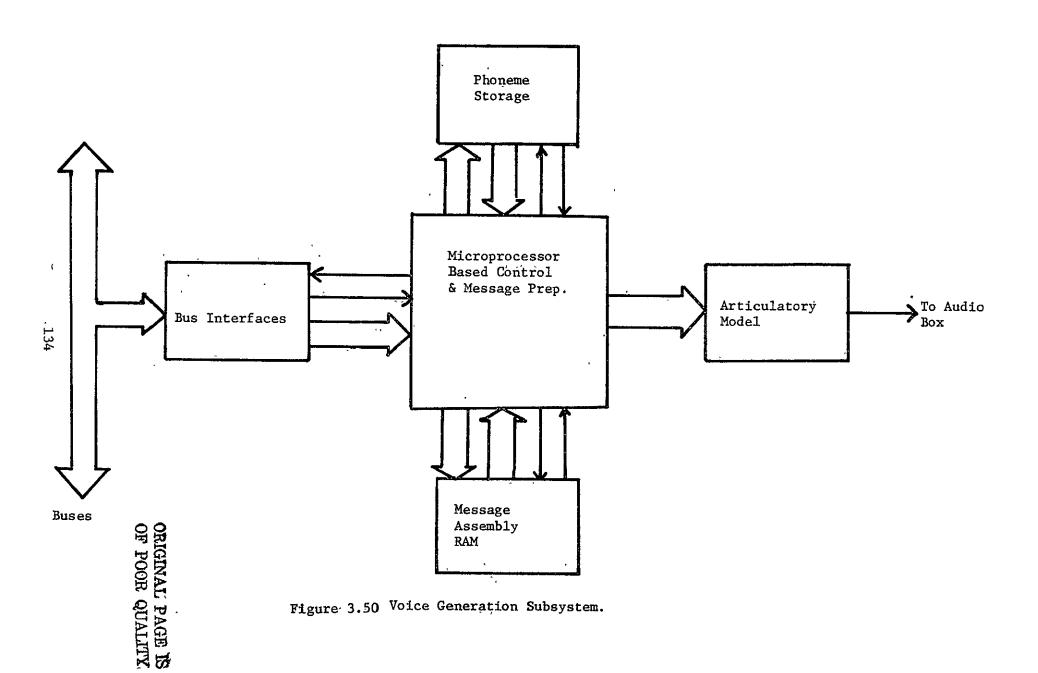

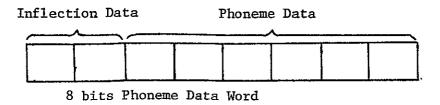

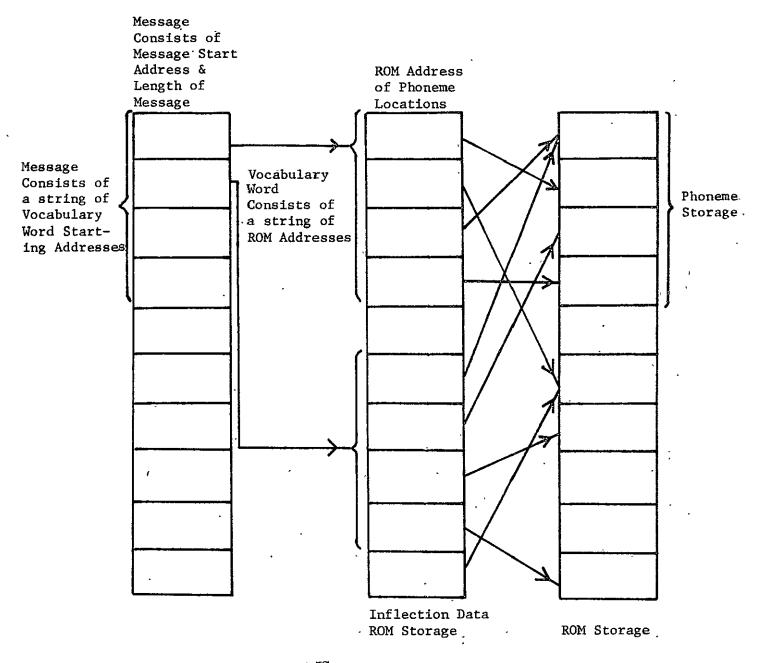

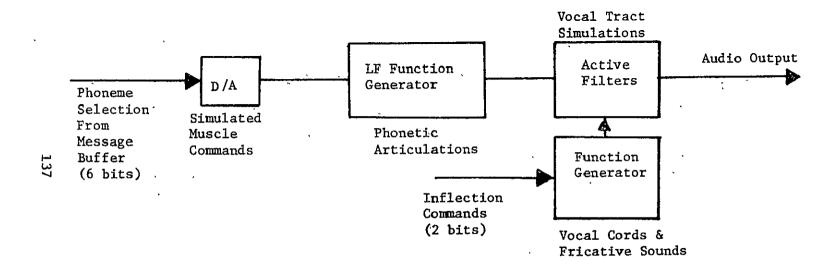

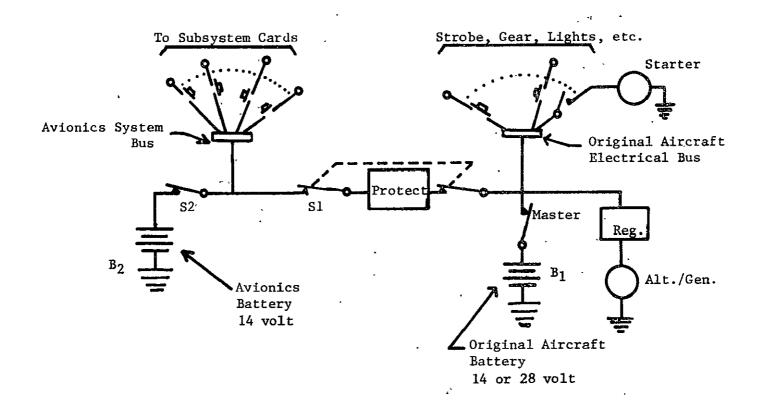

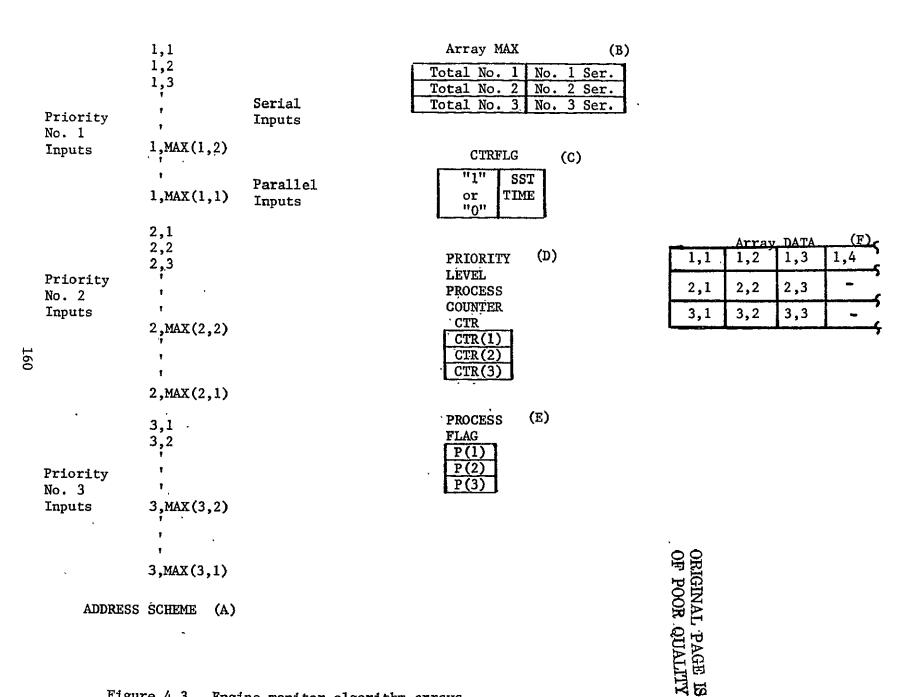

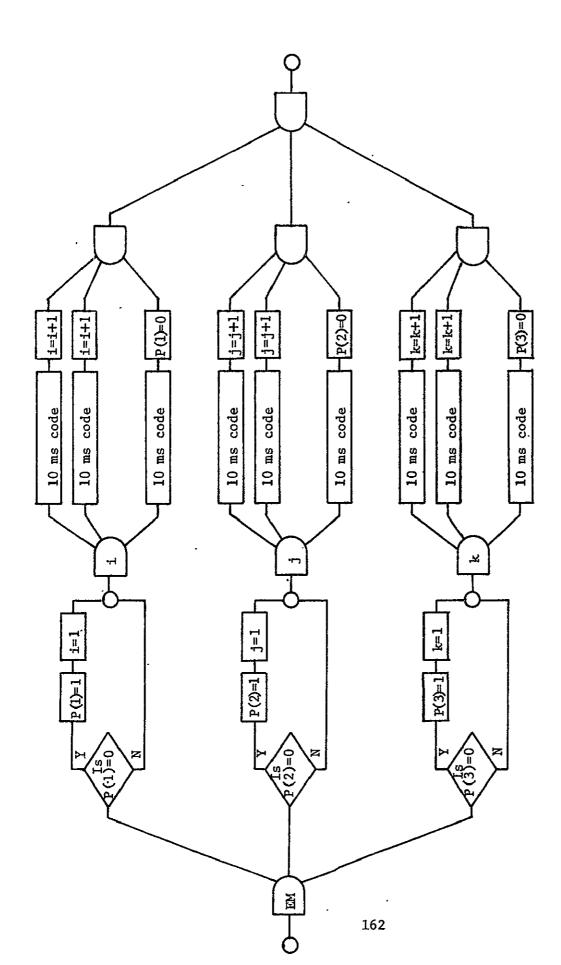

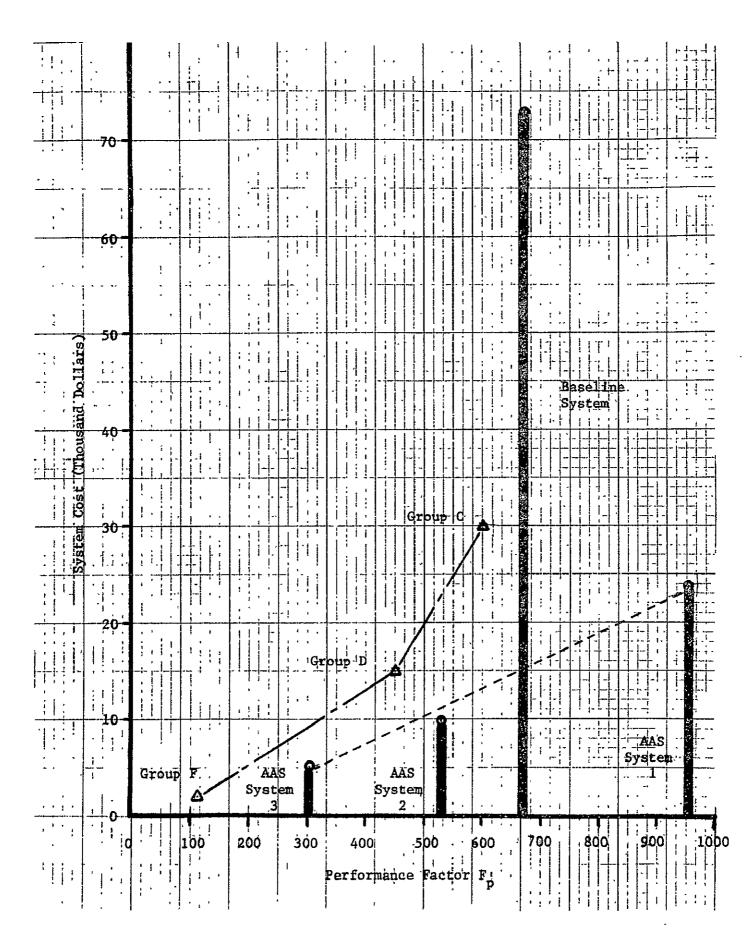

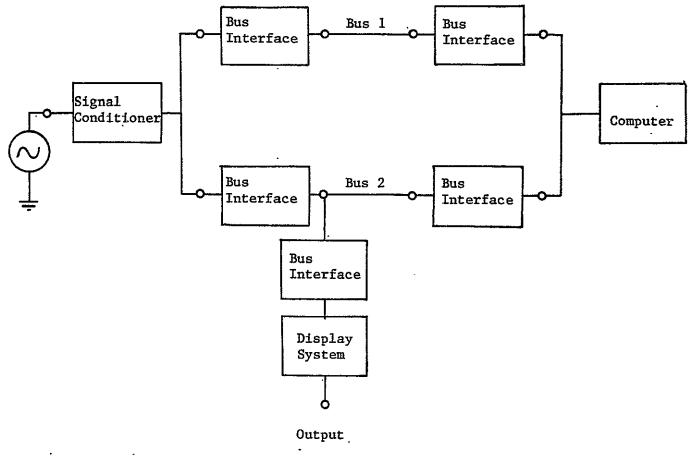

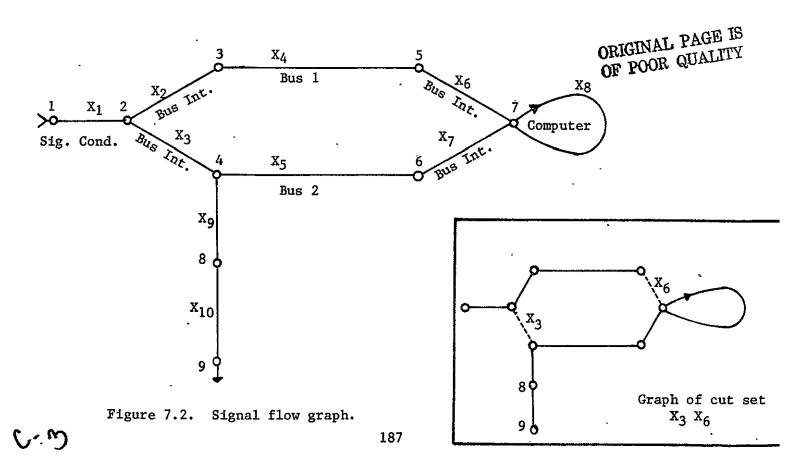

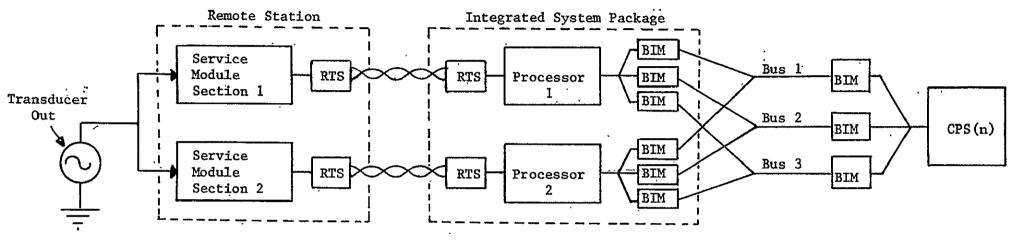

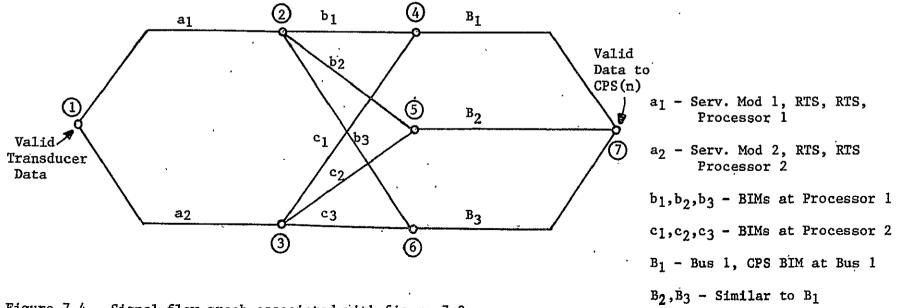

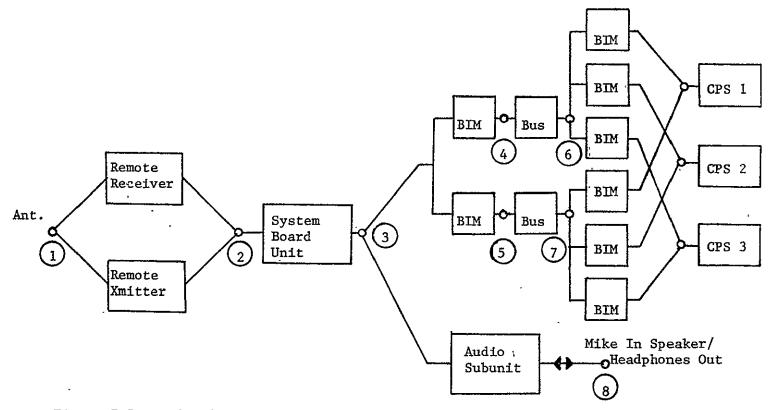

Figure 3.10. Serial data transmission.