## Preparation of Ohmic contacts to GaAs/AlGaAs-core/shell-nanowires

S. Wirths, M. Mikulics, P. Heintzmann, A. Winden, K. Weis et al.

Citation: Appl. Phys. Lett. **100**, 042103 (2012); doi: 10.1063/1.3678639 View online: http://dx.doi.org/10.1063/1.3678639 View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v100/i4 Published by the American Institute of Physics.

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/ Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded Information for Authors: http://apl.aip.org/authors

## ADVERTISEMENT

## Preparation of Ohmic contacts to GaAs/AlGaAs-core/shell-nanowires

S. Wirths, <sup>1,2</sup> M. Mikulics, <sup>1,2</sup> P. Heintzmann, <sup>1,2</sup> A. Winden, <sup>1,2</sup> K. Weis, <sup>1,2</sup> Ch. Volk, <sup>1,2</sup> K. Sladek, <sup>1,2</sup> N. Demarina, <sup>1,2</sup> H. Hardtdegen, <sup>1,2</sup> D. Grützmacher, <sup>1,2</sup> and Th. Schäpers<sup>1,2,a</sup>) <sup>1</sup>Peter Grünberg Institute (PGI-9), Forschungszentrum Jülich GmbH, 52425 Jülich, Germany <sup>2</sup>JARA-Fundamentals of Future Information Technology, Forschungszentrum Jülich GmbH, 52425 Jülich, Germany

(Received 13 December 2011; accepted 3 January 2012; published online 24 January 2012)

Ohmic contacts to GaAs/AlGaAs core/shell nanowires are prepared by using a Ni/AuGe/Ni/Au layer system. In contrast to Ohmic contacts to planar GaAs/AlGaAs layer systems here, relatively low alloying temperatures are used in cylindrical geometry. Lowest resistances are found for annealing temperatures of 320 °C and 340 °C. For annealing temperatures exceeding 360 °C, the nanowires degraded completely. Nanowires annealed under optimized conditions preserved their Ohmic characteristics even down to temperatures of 4 K. © 2012 American Institute of Physics. [doi:10.1063/1.3678639]

In recent years, III-V semiconductor nanowires experienced an increasing interest in the quest of finding solutions in shrinking the size and increasing the speed of electronic devices.<sup>1,2</sup> In this respect, GaAs is an interesting candidate owing to the relatively small effective electron mass and the resulting expected high mobility. However, due to the surface depletion layer, GaAs is not suitable for single material nanowires. An elegant solution of this problem is to epitaxially coat the nanowire by a shell semiconductor with a higher energy band gap.<sup>3–10</sup> Here, AlGaAs is the perfectly suitable shell material as it supplies charge carriers to the GaAs core by modulation doping<sup>10–12</sup> as well as preserves the carriers from the direct influence of the surface defects without additionally introduced strain due to the lattice matching between GaAs and AlGaAs.

In order to use GaAs/AlGaAs core/shell nanowires in electronic devices, electron transport through the wire has to be accomplished. A serious challenge in this respect is the access to the conductive GaAs/AlGaAs interface, since it is isolated by the AlGaAs shell layer. In this letter, we report on transport measurements of modulation-doped GaAs/ AlGaAs core/shell nanowires. In order to gain Ohmic contacts, we used an Ni/AuGe/Ni/Au layer system, <sup>13,14</sup> which is common for contacting 2-dimensional electron gases based on GaAs/AlGaAs layer systems.<sup>15,16</sup> During the contact annealing, Ge diffuses into the semiconductor and occupies Ga vacancies leading to an effective *n*-type doping.<sup>14</sup> Regarding GaAs/AlGaAs core/shell nanowires, one has to be cautious, since NiAs(Ge,Ga) and Au(Ga,As) phases might extend into the nanowire during the annealing process and short-circuit two closely spaced contacts. In order to prevent extensive diffusion at the interface, we alloyed our contacts at relatively low temperatures in the range of 300 °C and 370 °C, which is considerably lower than the commonly used annealing temperatures around 430 °C. However, as reported by Werthen,<sup>17</sup> the formation of Ohmic contacts can already be expected at temperatures as low as 275 °C.

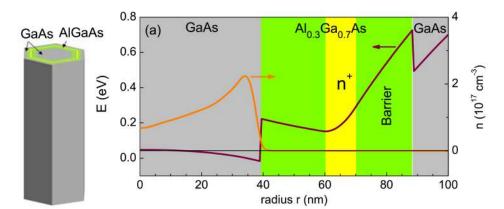

The growth of modulation-doped GaAs/AlGaAs core/ shell nanowires consists of two steps.<sup>10</sup> First, GaAs nanowires were grown at 750 °C on a GaAs (111)B substrate by selective area metal-organic vapor phase epitaxy using trimethylgallium and arsine (AsH<sub>3</sub>) as precursors in an N<sub>2</sub> ambient. Subsequently, the GaAs nanowires were covered by conformal overgrowth of Al<sub>0.3</sub>Ga<sub>0.7</sub>As and GaAs at 690 °C, using triethylgallium and dimethylethylamin alane. The structure of the modulation-doped GaAs/AlGaAs core/shell nanowires consists of an 80 nm thick GaAs core, a 20 nm thick intrinsic Al<sub>0.3</sub>Ga<sub>0.7</sub>As-layer, a 10 nm thick doped  $(n_d = 2 \times 10^{18} \text{ cm}^{-3})$  Al<sub>0.3</sub>Ga<sub>0.7</sub>As-layer, a 20 nm thick intrinsic Al<sub>0.3</sub>Ga<sub>0.7</sub>As layer, and finally a 10 nm thick GaAs cap layer. The length of the as-grown nanowires was 1.4  $\mu$ m. In Fig. 1(a), the conduction band profile and the electron density along the radial direction calculated by a selfconsistent Schrödinger-Poisson solver are shown. As can be seen here, the carriers are expected to be confined close to the inner GaAs/AlGaAs interface within the GaAs core. The expected carrier concentration at the interface GaAs/AlGaAs is  $2.8 \times 10^{11} \,\mathrm{cm}^{-2}$ .

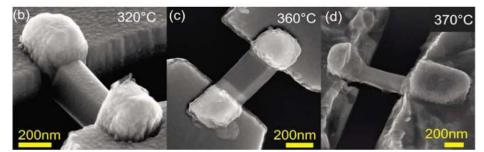

For the preparation of Ohmic contacts, the nanowires were transferred onto an *n*-type doped Si (100) wafer covered by a 100-nm-thick SiO<sub>2</sub> layer. By means of electron beam lithography and lift-off, contact fingers to the nanowires were defined. The contact layer system consisted of 5 nm Ni, 90 nm AuGe of eutectic composition (12 wt. % Ge), 25 nm Ni, and 100 nm Au. Afterwards, the contacts were annealed in a rapid thermal processing (RTP) furnace under N2 flow. The distance of the contacts was between 400 and 900 nm. Five different annealing temperatures  $T_a$  were investigated, i.e., 300°C, 320°C, 340°C, 360°C, and 370°C. For each annealing temperature, six to nine contacted nanowires were studied. The annealing time  $t_a$  was increased in steps of 5 s or 10 s. Due to the different annealing results for certain annealing temperatures, the total maximum annealing time varied from 75 s ( $T_a = 320$  °C) to 140 s (300 °C). In Figs. 1(b)-1(d), typical scanning electron micrographs (SEM) are shown for samples annealed at different temperatures. While for the sample annealed at 320 °C, no degradation of the nanowire was observed [cf. Fig. 1(b)]; brighter areas of the nanowire surface are visible at the boundary of the contact fingers at 360°C [cf. Fig. 1(c)]. A complete

<sup>&</sup>lt;sup>a)</sup>Electronic mail: th.schaepers@fz-juelich.de.

Appl. Phys. Lett. 100, 042103 (2012)

FIG. 1. (Color online) (a) Simulation of the conduction band profile and the electron density of a modulation-doped GaAs/ AlGaAs core/shell nanowire in radial direction. (b)-(d) SEM images of contacted GaAs/AlGaAs-core/shell-nanowires after annealing at 320 °C for 75 s, at 360 °C for 105 s, and at 370 °C for 10 s, respectively.

degradation of the GaAs/AlGaAs core/shell nanowire was observed at an annealing temperature of 370 °C, which is above the eutectic temperature of AuGe (361 °C).

The current-voltage (I-V) characteristics of the annealed contacts were measured in a two-terminal configuration after each annealing step. For the room-temperature measurements, a semiconductor probe station was employed, while the low temperature measurements were performed in a He-4 flow cryostat. Due to the small length of the nanowires, the usual transmission-line method could not be employed. Since only two contact fingers could be placed on the nanowire, information on the contact properties was gained from two-terminal measurements, i.e., the additional contribution of the nanowire resistance is included. Without annealing, all measured wires had a resistance larger than 1 G $\Omega$ .

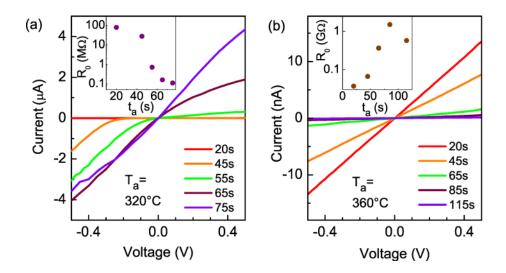

Figures 2(a) and 2(b) exemplarily show the resulting characteristics for annealing temperatures of 320 °C and 360 °C, at 5 different annealing times, respectively. For both temperatures, a single nanowire was investigated, respectively. In between each annealing step, the I-V characteristic was measured. As can be seen in Fig. 2(a), after a short annealing time of 20s at 320°C, only a small current of less than 10 nA is measured at 0.5 V. If the annealing time is increased up to 45 s, a diode-like behavior is observed, i.e., the I-V characteristics are asymmetric with respect to bias voltage reversal. Presumably, only for one of the contacts a sufficient amount of Ge-atoms diffused into the nanowire underneath the contact area. Further increase of the annealing time up to 75 s finally leads to an almost linear I-V characteristic in the complete bias voltage range. Now, both contacts are annealed sufficiently, and Ohmic contacts are achieved. A possible reason for this behavior might be connected to the area of the nanowire, which is covered by the contact metal. On AlGaAs/GaAs layer systems it has been shown that for a larger contact area, the contact resistance decreases.<sup>18</sup> In our case, this relation could not clearly be verified. Due to the small dimensions of the nanowires, we did not succeed in processing equally sized contact areas on both sides of the

FIG. 2. (Color online) (a) *I*-*V* characteristics of a GaAs/AlGaAs nanowire annealed at 320 °C, for different annealing times. The inset shows the corresponding resistance  $R_0$ at zero bias. (b) Corresponding measurements for an annealing temperature of 360 °C, with  $R_0$  shown in the inset.

Downloaded 14 May 2013 to 134.94.122.141. This article is copyrighted as indicated in the abstract. Reuse of AIP content is subject to the terms at: http://apl.aip.org/about/rights\_and\_permissions

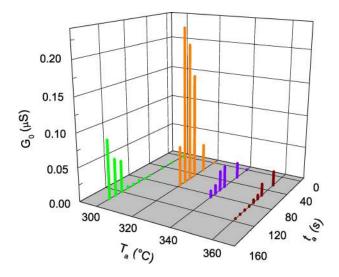

FIG. 3. (Color online) Conductance  $G_0$  for a set of nanowires for different annealing times  $t_a$  and temperatures  $T_a$ .

nanowire. Because of the small wire dimensions, we also cannot distinguish which type of diffusion, i.e., from the surface through the layer system or from the wire terminals, has a larger impact on the contact resistance. The zero-bias twoterminal resistance  $R_0$  of this nanowire is plotted in Fig. 2(a) (inset). As shown here,  $R_0$  decreases by almost three orders of magnitude from a value of 80 M $\Omega$  after an annealing time of 20 s to 110 k $\Omega$  after 75 s.

As can be seen in Fig. 2(b) for the sample annealed at  $360 \,^{\circ}$ C, the opposite behavior compared to the sample annealed at  $320 \,^{\circ}$ C is observed, i.e., with increasing annealing time, the resistance increases, as indicated by the decreasing slope of the *I-V* characteristics. All *I-V* characteristics are Ohmic. At short annealing times of 25 s and 45 s, a resistance below 100 M $\Omega$  is found, whereas at longer times, the resistance increases to the order of 1 G $\Omega$ .

In Fig. 3, the two-terminal zero-voltage conductance  $G_0 = 1/R_0$  at different annealing times and temperatures of different samples is compared. A homogeneous coverage of the contact fingers on the nanowires still has to be achieved, in order to get more congruent results for different samples with equal annealing parameters. This would be a condition

precedent to achieve reliable statistic values from our measurements. Thus, here, we present the conductance of 4 different nanowires exhibiting representative characteristics of GaAs/AlGaAs core/shell nanowires for the presented times and temperatures. For each annealing temperature, one nanowire was measured at incremental annealing times. As can be seen in Fig. 3, the best results are achieved for an annealing temperature of 320 °C and an annealing time of 65 s. For annealing temperatures lower or higher than 320 °C, somewhat lower maximum conductance values are obtained. Interestingly, the annealing time for the obtained maximum conductance is decreasing with increasing annealing temperature. The maximum conductance of the samples annealed at 300 °C is found at a relatively long annealing time of around 120 s, while for the samples annealed at 360 °C, the maximum conductance is gained already after 45 s. The observation that, for an annealing temperature of 360 °C, a lower conductance is measured probably is concerned with the partial degradation of the nanowire, as can be seen in Fig. 1(c). Indeed, for samples annealed at 370 °C, a very low resistance in the order of  $k\Omega$  was measured, which indicates that the metal diffusion into the nanowire short-circuited the contact fingers [cf. Fig. 1(d)].

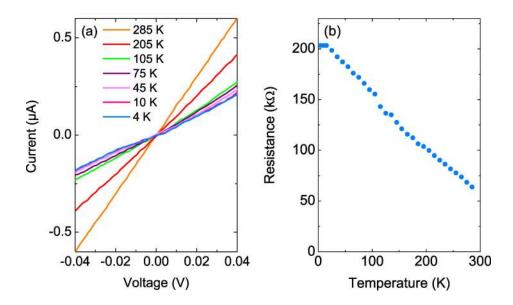

A crucial question is whether or not the contacts to the GaAs/AlGaAs core/shell nanowires are still Ohmic at low temperatures. Since the AlGaAs layer serves as a barrier, it has to be shown that the carriers are not mainly transferred to the core by thermionic emission, which should be considerably reduced at low temperatures. In Fig. 4(a), the I-V characteristics of a nanowire annealed at 320 °C for 55 s are shown for different temperatures. Even at 4 K, an Ohmic behavior is observed. The corresponding resistance determined from a linear fit of the I-V characteristics increases by about a factor of three when the temperature is decreased from room temperature to 4 K [cf. Fig. 4(b)]. Since four-terminal measurements could not be performed due to the short nanowire length, it is not possible at this stage to assign the temperature dependence of the resistance to the intrinsic properties of the nanowire or to thermal excitation at the metal/semiconductor interface. However, it can be excluded that extensive diffusion into the nanowire occurred, since in this case a

FIG. 4. (Color online) (a) *I-V* characteristics of a GaAs/AlGaAs core/shell nanowire with a contact separation of 900 nm at various temperatures. (b) Resistance as a function of temperature.

Downloaded 14 May 2013 to 134.94.122.141. This article is copyrighted as indicated in the abstract. Reuse of AIP content is subject to the terms at: http://apl.aip.org/about/rights\_and\_permissions

metal-type temperature dependence, opposite to the one found here, would be expected. Furthermore, control experiments were performed on nanowires consisting of only the GaAs core. Here, the resistance was extremely high in the G $\Omega$  range, which confirms that the carriers in our GaAs/AlGaAs nanowires are supplied by the dopants in the AlGaAs shell.

In summary, by systematically varying the annealing time and temperature, optimal parameters to achieve low resistive Ohmic contacts to a modulation-doped GaAs/ AlGaAs core/shell nanowire were determined. The results found here can be regarded as an important step towards nanowire devices based on modulation-doped GaAs/AlGaAs core/shell structures. Based on the results obtained here, it might be interesting for future studies to investigate the sizedependence of the contact resistance and to get a deeper understanding of the diffusion.

- <sup>3</sup>Z. Zanolli, L. Froberg, M. Björk, M. Pistol, and L. Samuelson, Thin Solid Films **515**, 793 (2006).

- <sup>4</sup>X. Jiang, Q. Xiong, S. Nam, F. Qian, Y. Li, and C. M. Lieber, Nano Lett. 7, 3214 (2007).

- <sup>5</sup>J. W. W. van Tilburg, R. E. Algra, W. G. G. Immink, M. Verheijen, E. P. A. M. Bakkers, and L. P. Kouwenhoven, Semicond. Sci. Technol. 25, 024011 (2010).

- <sup>6</sup>L. Samuelson, C. Thelander, M. T. Björk, M. Borgström, K. Deppert, K. A. Dick, A. E. Hansen, T. Mårtensson, N. Panev, A. I. Persson *et al.*, Physica E (Amsterdam) **25**, 313 (2004).

- <sup>7</sup>J. Noborisaka, J. Motohisa, S. Hara, and T. Fukui, Appl. Phys. Lett. **87**, 093109 (2005).

- <sup>8</sup>L. V. Titova, T. B. Hoang, H. E. Jackson, L. M. Smith, J. M. Yarrison-Rice, Y. Kim, H. J. Joyce, H. H. Tan, and C. Jagadish, Appl. Phys. Lett. 89, 173126 (2006).

- <sup>9</sup>L. Ouattara, A. Mikkelsen, N. Sköld, J. Eriksson, T. Knaapen, E. Cavar, W. Seifert, L. Samuelson, and E. Lundgren, Nano Lett. **7**, 2859 (2007).

- <sup>10</sup>K. Sladek, V. Klinger, J. Wensorra, M. Akabori, H. Hardtdegen, and D. Grützmacher, J. Cryst. Growth **312**, 635 (2010).

- <sup>11</sup>D. Spirkoska, A. Fontcuberta i Morral, J. Dufouleur, Q. Xie, and G. Abstreiter, Phys. Status Solidi (RRL) **5**, 353 (2011).

- <sup>12</sup>D. Lucot, F. Jabeen, J.-C. Harmand, G. Patriarche, R. Giraud, G. Faini, and D. Mailly, Appl. Phys. Lett. 98, 142114 (2011).

- <sup>13</sup>N. Braslau, Solid-State Electron. 10, 381 (1967).

- <sup>14</sup>T. S. Kuan, P. E. Batson, T. N. Jackson, H. Rupprecht, and E. L. Wilkie, J. Appl. Phys. 54, 6952 (1983).

- <sup>15</sup>T. K. Higman, M. A. Emanuel, J. J. Coleman, S. J. Jeng, and C. M. Wayman, J. Appl. Phys. **60**, 677 (1986).

- <sup>16</sup>G. S. Saravanan, K. M. Bhat, K. Muraleedharan, H. P. Vyas, R. Muralidharan, and A. P. Pathak, Semicond. Sci. Technol. 23, 025019 (2008).

- <sup>17</sup>J. G. Werthen, J. Appl. Phys. **52**, 1127 (1981).

- <sup>18</sup>O. Göktaş, J. Weber, J. Weis, and K. von Klitzing, Physica E (Amsterdam) 40, 1579 (2008).

<sup>&</sup>lt;sup>1</sup>C. Thelander, P. Agarwal, S. Brongersma, J. Eymery, L. Feiner, A. Forchel, M. Scheffler, W. Riess, B. Ohlsson, U. Gösele, and L. Samuelson, Mater. Today **9**, 28 (2006).

<sup>&</sup>lt;sup>2</sup>W. Lu and C. M. Lieber, J. Phys. D: Appl. Phys. 39, R387 (2006).