# ARTICLE

Received 18 May 2015 | Accepted 27 Jul 2015 | Published 3 Sep 2015

DOI: 10.1038/ncomms9181

**OPEN**

# Projected phase-change memory devices

Wabe W. Koelmans<sup>1</sup>, Abu Sebastian<sup>1</sup>, Vara Prasad Jonnalagadda<sup>1</sup>, Daniel Krebs<sup>1</sup>, Laurent Dellmann<sup>1</sup> & Evangelos Eleftheriou<sup>1</sup>

Nanoscale memory devices, whose resistance depends on the history of the electric signals applied, could become critical building blocks in new computing paradigms, such as braininspired computing and memcomputing. However, there are key challenges to overcome, such as the high programming power required, noise and resistance drift. Here, to address these, we present the concept of a projected memory device, whose distinguishing feature is that the physical mechanism of resistance storage is decoupled from the information-retrieval process. We designed and fabricated projected memory devices based on the phase-change storage mechanism and convincingly demonstrate the concept through detailed experimentation, supported by extensive modelling and finite-element simulations. The projected memory devices exhibit remarkably low drift and excellent noise performance. We also demonstrate active control and customization of the programming characteristics of the device that reliably realize a multitude of resistance states.

<sup>&</sup>lt;sup>1</sup>IBM Research—Zurich, Säumerstrasse 4, 8803 Rüschlikon, Switzerland. Correspondence and requests for materials should be addressed to W.W.K. (email: wko@zurich.ibm.com).

e are entering the era of cognitive computing, which holds great promise in deriving intelligence and knowledge from huge volumes of data<sup>1</sup>. Today's cognitive computers are based on the Von Neumann architecture, in which logic and memory are separated. Cognitive computing is inherently data-centric, and high-speed data transport between memory and processing units consumes much power. Thus, in efficient cognitive computers, logic and memory should coexist, like in brain-inspired neuromorphic computing<sup>2</sup> and memcomputing<sup>3,4</sup>. The critical element in these fascinating new computing paradigms is a high-density, lowpower, variable-state, programmable and non-volatile nanoscale memory device<sup>5-10</sup>. However, key challenges, such as the high programming power required, noise and resistance drift, must be overcome.

Phase-change memory devices are currently well-positioned to be used in the exploration of neuromorphic and memcomputing applications owing to the multi-level storage capability, proven large-scale manufacturability and good understanding we have of the underlying physical mechanisms and state dynamics<sup>11</sup>. In a conventional phase-change device, a nanometric volume of phase-change material is sandwiched between two metal electrodes. On application of electrical pulses, the phase-change material reversibly changes from the crystalline to the amorphous phase. The resistance change induced by varying the structural phase configuration is used to store information. Key in this conventional approach is that the phase-change material is used both for writing information, by undergoing a phase transition, and for retrieving the information stored, by reading its low-field electrical resistance. The drawback in this approach is that although phase-change materials have excellent phase-transition properties, that is, they can undergo phase transitions on the nanosecond timescale<sup>12,13</sup> and down to nanoscale dimensions<sup>12</sup>, their highly disordered nature and high defect density make them susceptible to highly undesirable electrical effects, such as noise and drift<sup>14,15</sup>. This leads to the difficult challenge of having to optimize the phase-change properties and the electrical properties in one and the same material.

A resistive memory device concept that can overcome this crucial challenge would be a game changer for this technology. A promising step in this direction was the recent introduction of memory cells with electrically conducting surfactant layers to partially mitigate resistance drift<sup>16,17</sup>.

In this article, we expand on this idea by proposing a radical rethinking of the memory cell design, namely, the projected memory cell, and present a thorough experimental evaluation of this new concept. First, we introduce the projection concept. Next, we present the design, fabrication and simulation of projected phase-change memory devices. This is followed by experimental results, where we show almost complete elimination of drift and 1/f noise characteristics, thereby proving the efficacy of this concept.

## Results

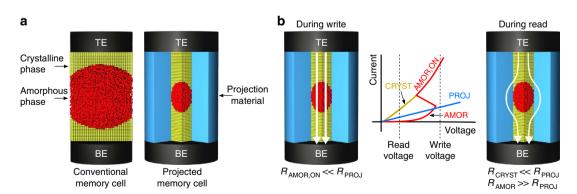

The concept of projection. In a projected memory device, the essential idea is to design the device in such a way that the physical mechanism of information storage is decoupled from the information-retrieval process<sup>18</sup>. The projected memory device or cell comprises a carefully designed segment consisting of a non-insulating material (projection segment) that is parallel to the phase-change segment (Fig. 1a). The resistance of this projection segment is judiciously chosen such that it has only a marginal influence on the write operation (during which the phase transition occurs), but a significant influence on the read operation (Fig. 1b). This is indeed possible because electrical transport in amorphous phase-change materials is highly nonlinear. At high fields, the amorphous material undergoes the so-called electronic threshold switching, leading to a low-resistive state (ON state)<sup>19</sup>. Thus, if during the high-field write process the resistance of the projection component is significantly higher than the ON-state resistance of the amorphous region, most of the current will flow through the phase-change segment. During the low-field read process, however, the current bypasses the highly resistive amorphous region and flows through that part of the projection segment that is parallel to it. Hence, the resistance of the device is dominated by the resistance of that part of the projection segment, and thus is a good measure of the amorphous/crystalline phase configuration. The information that typically is stored into the length of the amorphous region is in a sense projected onto the projection component. Note that even though the projection segment is present during both read and write operations, the 'projection' is designed to occur only during the read process.

**Figure 1 | The concept of a projected memory device. (a)** A convential phase-change memory cell (left) and a projected phase-change memory cell (right). TE and BE indicate the top and bottom electrodes, respectively. The crystalline and amorphous phases are shown schematically. The projected memory cell has an additional segment with projection material. (b) The desired *I*-*V* characteristics corresponding to the phase-change and projection segments are shown schematically. The phase-change section in the amorphous phase is denoted as AMOR with the corresponding resistance,  $R_{AMOR}$ , and in the crystalline phase denoted as CRYST with resistance  $R_{CRYST}$ . The projection segment is denoted as PROJ with resistance  $R_{PROJ}$ . In write mode, the write voltage exceeds the threshold voltage, and the amorphous section goes into the ON-state with a resistance  $R_{AMOR,ON}$  that is lower than  $R_{PROJ}$ . This ensures that most of the current flows through the phase-change segment, resulting in Joule heating and subsequent phase transition. In read mode, because  $R_{PROJ}$  is chosen to be much lower than  $R_{AMOR}$  at low fields, the current preferentially flows through the section of the projection segment that is parallel to the amorphous section. Elsewhere, the current will preferentially flow through the crystalline section.

This decoupling of the information-retrieval task from the phase-change task paves the way for a complete rethinking of the memory cell design. For example, to reduce the power needed to programme a cell, the phase-change component can be made as small as or as resistive as possible, as long as the phase change (that is, the structural re-organization of atomic configurations) is facilitated. Moreover, the amorphous phase-change material can have undesirable electrical properties as long as the projection material has excellent electrical characteristics. The projection component can have very innovative geometries and resistance variations to facilitate both fabrication and multi-level storage. Furthermore, it can act as a thermal shield to prevent inter-cell interference. The cell design is guided by clear 'design rules' under which the concept works, imposed by the highly nonlinear fielddependent electrical transport properties of phase-change materials. The projection concept is a generic concept that can be extended to certain classes of non-phase-change resistive memories, possibly in the redox class<sup>20,21</sup>.

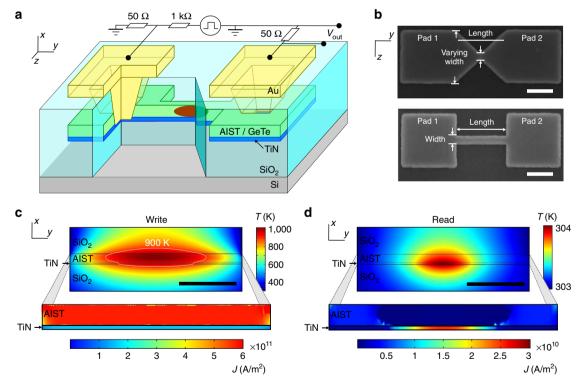

To demonstrate the concept of projection, several projected phase-change memory devices with a lateral cell geometry were fabricated (Fig. 2a). The lateral cell geometry was chosen for the demonstration of the concept because it offers more flexibility to explore different designs and better inspection access to the cell (during and after fabrication). However, the concept can easily be extended to commercially more viable vertical cell designs<sup>18</sup>. When viewed from the top, these devices possess different geometric shapes, such as tapered or rectangular (Fig. 2b). The devices consist of a 2.8-nm-thick TiN projection component and a phase-change component of either 15-nm-thick AgInSbTe (AIST) or 30-nm-thick GeTe, initially in the crystalline phase. Two different phase-change materials were used to show the versatility of the concept. Crystal growth-dominated phase-change materials GeTe<sup>22</sup> and AIST<sup>23</sup> were chosen to ensure the formation of well-defined amorphous regions within the crystalline matrix. Moreover, the crystalline resistivity of GeTe and AIST is advantageous for the design of cells in conjunction with a relative low-resistance projection material such as TiN. Other phase-change materials may necessitate a more resistive projection material, such as TaN.

We conducted extensive finite-element (FE) simulations to investigate the electrical and thermal characteristics of these devices. To derive the parameters for electrical transport associated with the various materials, we fabricated devices with only a projection layer or a phase-change layer and conducted field- and temperature-dependent transport measurements (see Methods). The FE simulations clearly showed the feasibility of forming substantial amorphous regions in the crystalline matrix by creating temperatures in excess of 900 K in the device, which is the typical melting temperature of phase-change materials (Fig. 2c). During writing, the current density was uniformly higher in the phase-change material than in the projection material. During reading, the amorphous region was circumvented by the current (Fig. 2d).

**Figure 2 | Projected memory devices.** (a) Schematic 3D view of projected phase-change memory devices with lateral geometry. They consist of a TiN projection layer and a phase-change layer of either AIST or GeTe. These layers are surrounded by  $SiO_2$  for electrical and thermal insulation. The device has two electrical connections to the top level. (b) SEM images (top view) of a device with tapered and one with rectangular geometry during fabrication. The device length in both cases is 400 nm, and the width of the rectangular device is 50 nm. Scale bar, 200 nm. (c) The write process simulated by FE modelling. (top) Temperature map of the device (side view). The contour indicates the 900-K isotherm, inside which the phase-change material is assumed to be amorphous after the melt-quench process. Scale bar, 100 nm. (bottom) Current-density map (side view) during write, not drawn to scale. The current density is uniform and highest in the phase-change material. (d) The read process simulated by FE modelling. (top) Temperature map (side view) of the device (side view) and the width of the read current is negligible ( $\approx$ 1K). Scale bar, 100 nm. (bottom) Current-density map of the device (side view) during read, not drawn to scale. The current largely circumvents the amorphous region created by the write process of **c**, and predominantly flows through the projection component.

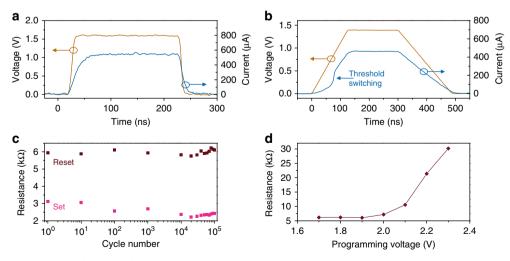

Experimental results. Resistive switching experiments were conducted on the projected devices. First, we present reset (increases the device resistance) and set (reduces the device resistance) experiments on a device with tapered geometry. As-fabricated, the phase-change component (AIST) was in the crystalline state with a resistance of 2.6 k $\Omega$ . A reset pulse was applied with a characteristic short trailing edge (Fig. 3a). A part of the phase-change component melted because of Joule heating, and the short trailing edge ensured a fast quench process. The resulting glass transition created an amorphous region within the crystalline matrix, which caused the device resistance to increase to 8.0 k $\Omega$ . From the simulations, we estimate that the amorphous region parallel to the projection component was about 30 nm long. Next, a set pulse with a long trailing edge was applied to crystallize. To visualize the threshold switching, we chose a set pulse that also had a long rising edge (Fig. 3b). Prior to threshold switching, the current flowing through the device was substantially lower, with little contribution from the amorphous region. At about 80 ns, the amorphous region underwent threshold switching, and a sharp rise in current was observed. This led to significant Joule heating and crystal growth, and the cell was brought back to  $2.6 \text{ k}\Omega$ .

The device endurance was tested by applying a set of shorter pulses than those shown in Fig. 3a,b to not unnecessarily stress the device. The reset and set pulses were chosen to be 100 and 350 ns long, respectively. The resistance levels are well separated for more than 10<sup>5</sup> cycles (Fig. 3c). The shape of the pulses was not changed during the endurance experiment.

Second, we present almost analogue storage in the projected memory devices. The rectangular-shaped devices are particulary well suited for this. By increasing the amplitude of the reset pulse, we progressively increased the size of the amorphous region and hence the resulting device resistance. Such a relation between the programmed resistance level and the reset pulse amplitude is typically referred to as a programming curve (Fig. 3d).

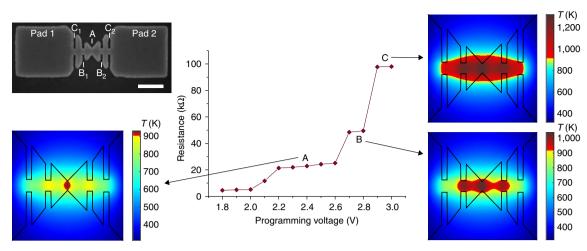

By introducing a geometric modulation, we can influence and control the shape of the programming curve to facilitate multilevel storage. Figure 4 shows a device with spatial variations in the width. The device, containing here GeTe as the phase-change material, is characterized by several narrow constrictions designed to create hot spots and thus contain the amorphous regions. FE simulations were used to visualize the shape of the amorphous regions being created during programming. Consistent with the findings from the FE simulations, the experimental measurements showed distinct resistance plateaus in the programming curve (Fig. 4). First, the amorphous region fills the centre of the cell, as shown in the FE simulation corresponding to plateau A. If only a little more power is sent to the cell, the amorphous region grows, but will not reach the constrictions to the left  $(B_1)$  and right  $(B_2)$  of the centre vet. However, when the power is sufficiently high the amorphous region fills  $B_1$  and  $B_2$  at the same time. Further up, constrictions  $C_1$  and  $C_2$  will be filled, corresponding to plateau C of the graph in Fig. 4. Such programming curves are particularly well suited for multi-level storage in which distinct resistance levels need to be achieved in a highly reliable manner.

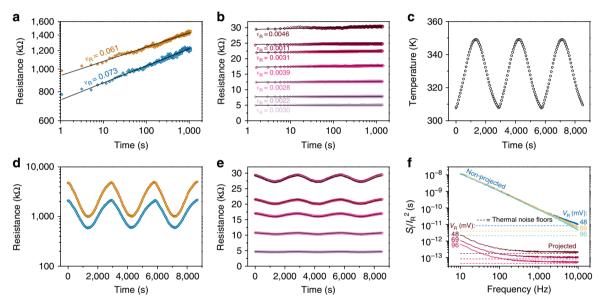

Next, we explore the variation in the resistance levels, a key challenge in resistive memories. To conduct a direct comparison with non-projected devices, we characterized identical lateral devices without the projection layer. The AIST-based devices were programmed to several resistance levels, and at each level the resistance of the device was monitored for 1,400 s. The temporal evolution of two programmed resistance levels in a non-projected device is shown in Fig. 5a. At constant ambient temperature, the resistance versus time is characterized by  $R(t) = R(t_0)(t/t_0)^{v_R}$ , where  $R(t_0)$  is the resistance measured at any time  $t_0$  greater than a few hundreds of nanoseconds after programming<sup>24,25</sup>. The drift coefficient,  $v_{\rm R}$ , was measured to be  $\approx 0.067$ , which is typical of amorphous AIST<sup>26</sup>. In contrast, the projected memory device exhibited a drift coefficient of only  $\approx$ 0.0030 (Fig. 5b). This remarkable, 22-fold drift reduction occurs because the majority of the current flows through the projection component rather than the amorphous region.

Because electrical transport in amorphous phase-change materials is thermally activated ( $E_A$  is typically in the range of 0.2–0.4 eV), the programmed resistance levels in a conventional phase-change device exhibit a significant temperature dependence. We studied the temperature dependence of the resistance levels in both a projected memory device and a non-projected device with identical geometries. At each programmed state, we

**Figure 3** | **Programming of projected memory devices.** (a) Voltage and subsequent current flowing through the device when a reset pulse is applied. The melt-quench process results in the creation of a higher resistance state that corresponds to an amorphous length of  $\approx$  30 nm. (b) Voltage and subsequent current when a set pulse is applied. The onset of threshold switching can clearly be seen in the initial part of the pulse. This pulse results in the crystallization of the amorphous region that was created by the reset pulse, and the resistance of the device drops to 2.6 k $\Omega$ . (c) Device endurance after periodic set and reset pulses. (d) Programming curve corresponding to a device with rectangular geometry. By increasing the amplitude of the reset pulse, the size of the amorphous region and hence the device resistance can be progressively increased to achieve almost analogue storage.

**Figure 4 | Controlled shape of the programming curve of a memory device.** (top left) SEM image (top view) of the geometrically modulated memory device that has constrictions A,  $B_1$ ,  $B_2$ ,  $C_1$  and  $C_2$  to control the growth of the amorphous region. Scale bar, 200 nm. The graph shows a programming curve with distinct plateaus A, B and C caused by the constrictions. Heat maps (top view) created by FE simulation show snapshots of the phase configuration at each plateau. The yellow to red crossover at a temperature of 900 K is indicative of the crystalline to amorphous crossover.

**Figure 5 | Time and temperature dependence of the resistance levels and noise characteristics. (a)** The programmed states in a phase-change device without projection component exhibit significant temporal resistance drift at constant temperature with a drift coefficient,  $v_R$ , determined by a fit to a power law (black line), of  $\approx 0.067$  that is characteristic of the AIST phase-change material. (b) The programmed states in a projected memory device exhibit strongly reduced temporal resistance drift at constant ambient temperature. The black lines are fits to a power law. (c) Applied temperature to investigate the temperature dependence of the programmed states. (d) Resistance variations corresponding to two different programmed states in a non-projected memory device when the ambient temperature is varied as shown in c. (e) Resistance variations corresponding to five different programmed states in a projected memory device when the ambient temperature is varied as shown in c. The black lines show the resistance variation predicted by FE simulations. (f) Normalized spectral density of the current noise for both a projected resistive memory device and an identical phase-change device without projection component. The measurements are obtained for three different read voltages ( $V_R$ ). The projected memory cell is programmed to a resistance of 24 k $\Omega$  and the non-projected cell is programmed to 1.1 M $\Omega$ , both corresponding to amorphous regions of about 90 nm in length. The dashed lines show the thermal noise floors for each bias voltage and each resistance.

varied the ambient temperature in a sinusoidal manner between 307 and 350 K (Fig. 5c). The resulting resistance variations for the non-projected and projected memory devices are depicted in Fig. 5d,e. The resistance variations are significantly lower in the projected memory devices. In Fig. 5e, also the result of a FE simulation matching the experimental scenario is plotted. There is remarkable agreement between experiment and simulation.

Besides the time/temperature dependence of the resistance levels, another key challenge in conventional phase-change devices is that of noise. When a bias voltage,  $V_R$ , was applied to

read back the resistance levels, significant fluctuations on top of the mean current,  $I_{\rm R}$ , were observed. This relatively low-frequency noise reduces the signal-to-noise ratio and poses significant challenges for applications of phase-change devices.

We therefore also measured the normalized power spectral density of the current noise for the projected and the non-projected devices as a function of  $V_{\rm R}$  (Fig. 5f). The non-projected device showed the characteristic  $V_{\rm R}$  independent, and normalized current spectral density,<sup>27</sup>  $S_{\rm I}/I_{\rm R}^2$ , with a 1/f frequency dependence<sup>28</sup> at frequencies <10 kHz, substantially

higher than the thermal noise floor for a 1.1-M $\Omega$  resistor. The projected device, in contrast, exhibited a noise level comparable to the thermal noise floor of a 24-k $\Omega$  resistor and the current noise is independent of  $V_{\rm R}$ . In addition, the lower absolute resistance value, for the same phase configuration, allows any readout circuitry to operate at a higher bandwidth. These experiments clearly show the merits of the projection concept for countering the highly undesirable properties of resistance variations, temperature sensitivity and noise.

### Discussion

To summarize, we have presented the concept of projection in resistive memory devices, whereby the physical mechanism of storage is decoupled from the information-retrieval process. We designed, fabricated and characterized projected memory devices based on the phase-change storage mechanism in a lateral cell geometry. For the first time, the concept was convincingly demonstrated in a combination of simulations and experimental measurements. Moreover, we also showed the significant advantages such a concept could bring in overcoming the key challenges of resistance variations and noise in conventional resistive memory devices. The prospects are fascinating: this new cell architecture opens up an alternative dimension in research on resistive memory devices in the form of projection materials. A variety of metallic, semi-metallic or even semiconducting projection materials could be explored. Moreover, instead of geometric modulation of the complete device the projection segment could be designed to have spatial geometric variations as well as variations in resistivity, for example, semiconducting projection materials could be doped locally. With all these benefits, projected memory devices are likely to provide significant impetus to the field of resistive memories and could play a key role in future non-Von Neumann computing systems.

#### Methods

Device fabrication. The devices were fabricated on a silicon substrate with a thermally grown 100-nm-thick SiO<sub>2</sub> top layer for thermal and electrical insulation. Next, a layer stack consisting of the projection material (2.8 nm of TiN, only for the projected memory devices), the phase-change material (15 nm of Ag<sub>4</sub>In<sub>3</sub>Sb<sub>67</sub>Te<sub>26</sub> or 30 nm of Ge<sub>50</sub>Te<sub>50</sub>) and a capping layer (5 nm of (ZnS)<sub>80</sub>-(SiO<sub>2</sub>)<sub>20</sub>) was deposited. The layer stack was then patterned into the cell design desired using an e-beam-lithography process with hydrogen silsesquioxane (HSQ) resist and an ion milling step. To avoid sidewall oxidation of the phase-change material, the patterned cell was immediately passivated with 20 nm of sputtered SiO<sub>2</sub>. All scanning electron microscopy (SEM) images shown were recorded at this stage of the fab rication process. Electrical connections to the cell were created by first ion milling holes into the SiO<sub>2</sub> passivation layer in another e-beam lithography step and then sputtering tungsten connections in a lift-off process using a third e-beam lithography step. The tungsten was then encapsulated with a layer of 60-nm-thick sputtered SiO<sub>2</sub>. Finally, using optical lithography and a reactive ion etch, probe pads (200 nm of sputtered gold) were connected to the tungsten.

**Simulations**. Simulations using the FE method were performed with Comsol 4.3b and 5.1 (COMSOL, Inc.) using the built-in Joule heating model. The cell geometries were rebuilt in 3D from the design values and SEM images where needed. The thermal conductivities of the projection material, the insulator (SiO<sub>2</sub>) and the phase-change material were chosen to be 12–15, 1.4 and 2 W m<sup>-1</sup> K<sup>-1</sup>, respectively. SiO<sub>2</sub> was assumed to be a perfect insulator. To derive the parameters for electrical transport, we fabricated devices with only a projection layer (TiN) or a phase-change layer (AIST). Field- and temperature-dependent transport measurements were conducted to obtain the parameters related to electrical transport.

The TiN projection material was found to exhibit a weak temperature dependence and almost no field dependence. The resistivity of TiN as a function of temperature fits  $\rho_{\rm PM} = \rho_{\rm PM,0}[1 + \alpha_{\rm PM}(T - T_0)]$ , where  $\alpha_{\rm PM} = -4.2 \times 10^{-4} {\rm K}^{-1}$ ,  $T_0 = 303 {\rm K}$ ,  $\rho_{\rm PM,0} = 3.6 \times 10^{-5} {\rm \Omega}m$  and *T* denotes the temperature, see Supplementary Fig. 1. The resistance decrease with temperature is consistent with previous studies on TiN thin films at the nanometer scale<sup>29</sup>.

Regarding AIST, the crystalline phase exhibits a weak temperature dependence and negligible field dependence. The resistivity of c-AIST was well captured by  $\rho_{c-AIST} = \rho_{c-AIST,0}[1 + \alpha_{c-AIST}(T - T_0)]$ , where  $\alpha_{c-AIST} = -5.9 \times 10^{-4} \text{ K}^{-1}$ ,  $T_0 = 303 \text{ K}$  and  $\rho_{c-AIST,0} = 9.9 \times 10^{-6} \Omega \text{m}$ , see Supplementary Fig. 2a. The resistivity of the amorphous AIST (a-AIST) material is simulated by  $\rho_{a-AIST} = \rho^* e^{(E_a - \beta E)/k_B T}$ , where *E* is the electric field,  $\rho^* = 1.3 \times 10^{-7} \Omega m$ ,  $E_A = 0.29 \text{ eV}$  and  $\beta = 5.7 \text{ meV MV}^{-1} m$  (see Supplementary Note 1 and Supplementary Figs 2b and 3a,b). Beyond a certain electric field,  $E_{th} = 10 \text{ MV m}^{-1}$ , the threshold-switching phenomenon will cause the resistivity of the amorphous phase to drop to a value almost identical to that of the crystalline phase, see Supplementary Fig. 3c.

Regarding GeTe, the crystalline phase exhibits a weak temperature dependence and negligible field dependence. The resistivity of c-GeTe was well captured by  $\rho_{c-GeTe} = \rho_{c-GeTe,0}[1 + \alpha_{c-GeTe}(T - T_0)]$ , where  $\alpha_{c-GeTe} = 4.3 \times 10^{-4} \text{ K}^{-1}$ ,  $T_0 = 303 \text{ K}$  and  $\rho_{c-GeTe,0} = 1.1 \times 10^{-5} \Omega \text{m}$  (see Supplementary Fig. 4a). The resistivity of the amorphous GeTe (a-GeTe) was well captured by  $\rho_{a-GeTe} = \rho^* e^{(E_A/k_BT)}$ , where  $\rho^* = 2.2 \times 10^{-6} \Omega \text{m}$  and  $E_A = 0.28 \text{ eV}$  at a GeTe thickness of 30 nm (see Supplementary Fig. 4b).

Electrical characterization. A custom-made electrical characterization platform with integrated heating stage was used for electrical measurements. The sample was mounted on an invar block with two embedded tungsten heaters. The temperature was measured using a thermocouple inserted into the invar block and controlled via a Eurotherm 2416 temperature controller. The temperature on top of the memory device chip was calibrated using an Omega silicon diode sensor. The measurement temperature was 303 K unless specified otherwise. For the annealing steps and the temperature-dependent transport measurements, the tungsten heaters were used. The ambient temperature variation experiment of Fig. 5d was performed after 150 min of annealing up to 350 K. To stabilize the resistance state, this annealing was done for each of the states programmed. Full crystallinity of the phase-change materials in the devices fabricated was verified by resistivity measurements and ensured by annealing steps if required. The devices were electrically contacted using a high-frequency Cascade Microtech Dual-Z probe. A Keithley 2400 SMU was used for DC voltage or current outputs and the measurements of the corresponding current or voltage at the device. The cell resistance was read at a constant read voltage of 0.1 V. Device programming was done using an Agilent 81150A Pulse Function Arbitrary Generator. The AC voltage and current signals were measured with a Tektronix DPO4104B oscilloscope. Mechanical relays were used to switch between AC and DC measurements.

#### References

- 1. Kelly, III J. E. & Hamm, S. Smart Machines: IBM's Watson and the Era of Cognitive Computing (Columbia Univ. Press, 2013).

- Merolla, P. A. et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 345, 668–673 (2014).

- Borghetti, J. et al. 'Memristive' switches enable 'stateful' logic operations via material implication. Nature 464, 873–876 (2010).

- Di Ventra, M. & Pershin, Y. V. The parallel approach. Nat. Phys. 9, 200–202 (2013).

- Chua, L. Resistance switching memories are memristors. Appl. Phys. A 102, 765–783 (2011).

- Strukov, D. B., Snider, G. S., Stewart, D. R. & Williams, R. S. The missing memristor found. *Nature* 453, 80–83 (2008).

- Wright, C. D., Hosseini, P. & Diosdado, J. A. V. Beyond von-Neumann computing with nanoscale phase-change memory devices. *Adv. Funct. Mater.* 23, 2248–2254 (2013).

- Kuzum, D., Yu, S. & Wong, H. P. Synaptic electronics: Materials, devices and applications. *Nanotechnology* 24, 382001 (2013).

- Burr, G. W. et al. in Proceedings of the IEEE International Electron Devices Meeting 697–700 (IEEE, Piscataway, NJ, USA, 2014).

- Eryilmaz, S. B. *et al.* Brain-like associative learning using a nanoscale non-volatile phase change synaptic device array. *Front. Neurosci.* 8, 205 (2014).

- 11. Wong, H. P. et al. Phase change memory Proceedings of the IEEE 98, 2201-2227 (2010).

- Xiong, F., Liao, A. D., Estrada, D. & Pop, E. Low-power switching of phasechange materials with carbon nanotube electrodes. *Science* 332, 568–570 (2011).

- Sebastian, A., Le Gallo, M. & Krebs, D. Crystal growth within a phase change memory cell. *Nat. Commun.* 5, 4314 (2014).

- Boniardi, M. & Ielmini, D. Physical origin of the resistance drift exponent in amorphous phase change materials. *Appl. Phys. Lett.* 98, 243506 (2011).

- Beneventi, G. B., Calderoni, A., Fantini, P., Larcher, L. & Pavan, P. Analytical model for low-frequency noise in amorphous chalcogenide-based phase-change memory devices. J. Appl. Phys. 106, 054506 (2009).

- Kim, S. et al. in Proceedings of the IEEE International Electron Devices Meeting 762–765 (IEEE, Piscataway, NJ, USA, 2013).

- 17. Kim, S., Krebs, D., Lam, C. H. & Pozidis, C. Phase-change memory cells. US patent application US 2014/0369114 (filed 5 June 2014).

- Krebs, D. & Sebastian, A. Phase-change memory cells. US patent US9,087,987 (filed 17 June 2014, and issued 21 July 2015).

- Adler, D., Shur, M. S., Silver, M. & Ovshinsky, S. R. Threshold switching in chalcogenide-glass thin films. J. Appl. Phys. 51, 3289–3309 (1980).

- 20. Waser, R., Dittmann, R., Staikov, G. & Szot, K. Redox-based resistive switching memories-nanoionic mechanisms, prospects, and challenges. Adv. Mater. 21, 2632-2663 (2009)

- 21. Eleftheriou, E. S., Krebs, D. & Sebastian, A. Resistive random-access memory cells. US patent application US 2015/0003144 (filed 16 June 2014).

- 22. Raoux, S., Cheng, H. Y., Caldwell, M. A. & Wong, H. P. Crystallization times of Ge-Te phase change materials as a function of composition. Appl. Phys. Lett. 95, 071910 (2009).

- 23. Salinga, M. et al. Measurement of crystal growth velocity in a melt-quenched phase-change material. Nat. Commun. 4, 2371 (2013).

- 24. Ielmini, D., Sharma, D., Lavizzari, S. & Lacaita, A. Reliability impact of chalcogenide-structure relaxation in phase-change memory (PCM) cells - part I: Experimental study. IEEE Trans. Electron Dev. 56, 1070-1077 (2009).

- 25. Sebastian, A., Krebs, D., Le Gallo, M., Pozidis, H. & Eleftheriou, E. in Proceedings of the IEEE International Reliability Physics Symposium (IEEE, Piscataway, NJ, USA, 2015).

- 26. Wimmer, M., Kaes, M., Dellen, C. & Salinga, M. Role of activation energy in resistance drift of amorphous phase change materials. Front. Phys. 2, 75 (2014).

- 27. Fantini, P., Pirovano, A., Ventrice, D. & Redaelli, A. Experimental investigation of transport properties in chalcogenide materials through 1/f noise measurements. Appl. Phys. Lett. 88, 263506 (2006).

- 28. Close, G. F. et al. in Proceedings of the IEEE International Electron Devices Meeting 660-663 (IEEE, Piscataway, NJ, USA, 2010).

- 29. Wang, J. M., Liu, W. G. & Mei, T. The effect of thermal treatment on the electrical properties of titanium nitride thin films by filtered arc plasma method. Ceramics Int. 30, 1921-1924 (2004).

#### Acknowledgements

We thank C. Rossel, M. Lantz and H. Pozidis for fruitful discussions; A. Athamanathan for help with the FE simulations; M. Le Gallo for experimental help; and U. Egger and W. Häberle for technical assistance. We thank C. Lam and S. Kim for useful discussions.

We also thank T. Tuma and J. Engelen for assistance with the artwork; and C. Bolliger for help in the preparation of the manuscript. Finally, we thank our collaborators at RWTH Aachen, particularly M. Salinga and M. Rütten, for assistance with deposition of the phase-change materials.

#### Author contributions

A.S., D.K. and E.E. initiated the work. W.W.K., V.P.J. and L.D. designed and fabricated the devices. W.W.K. and D.K. performed the FE simulations. W.W.K. and A.S performed the experiments, analysed the data and co-wrote the manuscript with input from all other authors. E.E. supervised the work.

### Additional information

Supplementary Information accompanies this paper at http://www.nature.com/ naturecommunications

Competing financial interests: The authors declare no competing financial interests.

Reprints and permission information is available online at http://npg.nature.com/ reprintsandpermissions/

How to cite this article: Koelmans, W.W. et al. Projected phase-change memory devices. Nat. Commun. 6:8181 doi: 10.1038/ncomms9181 (2015).

This work is licensed under a Creative Commons Attribution 4.0 ۲ International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/