Received 5 September 2018; revised 7 October 2018; accepted 9 October 2018. Date of publication 15 October 2018; date of current version 1 March 2019. The review of this paper was arranged by Editor A. G. U. Perera.

Digital Object Identifier 10.1109/JEDS.2018.2875976

# Proton Conductor Gated Synaptic Transistor Based on Transparent IGZO for Realizing Electrical and UV Light Stimulus

WEIJUN CHENG<sup>®</sup><sup>1</sup>, RENRONG LIANG<sup>1</sup>, HE TIAN<sup>®</sup><sup>1</sup>, CHUANCHUAN SUN<sup>®</sup><sup>2</sup>, CHUNSHENG JIANG<sup>®</sup><sup>3</sup>, XIAWA WANG<sup>1</sup>, JING WANG<sup>1</sup>, TIAN-LING REN<sup>®</sup><sup>1</sup>, AND JUN XU<sup>1</sup>

Institute of Microelectronics, Tsinghua University, Beijing 100084, China

Beijing Institute of Control Engineering, Beijing 100094, China

Microsystem and Terahertz Research Center, China Academy of Engineering Physics, Chengdu 610200, China

CORRESPONDING AUTHORS: R. LIANG AND H. TIAN (e-mail: liangrr@tsinghua.edu.cn; tianhe88@tsinghua.edu.cn)

This work was supported in part by the National Key Research and Development Program of China under Grant 2016YFA0302300 and Grant 2016YFA0200400, and in part by the National Natural Science Foundation of China under Grant 61306105. This paper has supplementary downloadable material available at http://ieeexplore.ieee.org, provided by the author.

**ABSTRACT** Synaptic transistors mimicking the biological synapse's short term plasticity and short-term memory property were demonstrated using the amorphous indium–gallium–zinc oxide channel in combination with the nanogranular SiO<sub>2</sub> as the gate oxide. The lowest energy consumption was  $\sim 1.08$  pJ per pulse activity and the operating voltage was within 100 mV. The device's plasticity and memory characteristics can be explained by the movement of protons in the insulating layer. The proton relaxation was revealed by two ways of dual sweeping: continuous and discontinuous sweepings. We observed that the excitatory postsynaptic current (EPSC) rose as the voltage decreased anomaly during the backward sweeping process. In the electrical stimulus, both the short-term potentiation and depression were observed for this proposed device. The amplitude of the EPSC changed with the pulse number following a saturating exponential function. For the electrical stimulus under constant illumination, the UV light wavelength, intensity and duration time were found to have little effect on the paired pulse facilitation. While in the light stimulus, the light frequency promoted the paired pulse facilitation and had more effect on the synapse's plasticity than the other light pulse parameters including intensity, numbers and width.

**INDEX TERMS** Synaptic transistor, transparent oxide, IGZO, nanogranular SiO<sub>2</sub>, UV light.

#### I. INTRODUCTION

The human brain has a huge advantage of handling a complicated problem over the conventional computers because of the complex neural network that consists of about 100 billion neurons connected by biological synapses [1]. Extensive researches have been carried out to study the mechanism of biological synapses and mimic their functions using electronic devices in hope to realize the parallelism, structural plasticity and robustness of a human brain [2], [3]. Many kinds of two-terminal devices, such as memristors, resistive switches and proton-conducting devices [4]–[7] and threeterminal devices, such as ionic/electronic, proton conductor oxide and organic materials devices [8]–[14], have been used to simulate the biological synapses. Three-terminal synapse transistors can realize the transmission by the semiconductor channel and the learning by adjusting the interaction between the channel and the insulating layer simultaneously, but the two-terminal devices cannot. The EPSC values vary as the gate signal changes in the width, frequency and amplitude, which is similar to how the brain controls the neurons responding to environmental change. Some synaptic transistors have been reported to mimic the human brain to learn and remember by tuning the stimulus' pulse property or being given a series of rehearsals [15], [16].

Amorphous indium–gallium–zinc oxide ( $\alpha$ -IGZO) is a transparent conducting oxide with excellent electron transport properties. It has an energy bandgap of around 3.3 eV and can be easily formed at room temperature [16], [17]. IGZO-based synaptic transistors are very promising to realize energy-efficient synaptic operations [18], [19]. Aixal *et al.*  found that the SiO<sub>2</sub> dielectric films deposited at room temperature by plasma-enhanced chemical vapor deposition (PECVD) method had a special microporous structure with a huge electric-double-layer capacitance, making it possible to realize synaptic plasticity [20]-[22]. Recently, synaptic transistors with HfO<sub>x</sub> insulating layer/IGZO channel layer or nanogranular SiO<sub>2</sub> insulting layer/Si channel layer have been fabricated and realized the LTD [16] or the short-term potentiation (STP)behavior [20], but not simultaneously. However, the mechanism of the memory property hasn't been analyzed in detail in the aforementioned SiO<sub>2</sub>-based synaptic transistors researches that have largely ignored the proton relaxation in the SiO<sub>2</sub>. Moreover, as moderate UV exposure can enhance the brain's learning, object recognition and memory ability by promoting a novel glutamate biosynthetic pathway in the brain [23], it is urgent now to study the UV light effects on the synaptic transistors in detail [24], [25].

In this work, a synaptic thin film transistor combining nanogranular SiO<sub>2</sub> with IGZO was fabricated. Both the STP and the short depression (STD) were observed. It was shown that the amplitude of the EPSC changes with the pulse number following a saturating exponential function. In addition, the ionic charge relaxation in the nanogranular SiO<sub>2</sub> was revealed by two ways of dual sweeping: continuous and discontinuous sweepings. Furthermore, in addition to the gate, source and drain terminals, UV light was found to be another effective controlling terminal of the synaptic transistor in the light stimulus. The frequency of the light pulse had an obvious effect on the synaptic transistor's plasticity and promoted the paired pulse facilitation (PPF) and the EPSC gain. In this work, the device was made to work under 0.1 V, the drain to source voltage (V<sub>DS</sub>) was 1 mV and the energy consumption was  $\sim 1.08$  pJ per pulse activity.

## **II. DEVICE FABRICATION AND EXPERIMENTAL SETUP**

The proton conductor gated synaptic transistors were fabricated on p-type Si wafers. First, microporous SiO<sub>2</sub> film of thickness 65 nm and 1 µm were deposited at room temperature using the ORION III PECVD system [16], [26]. At a pressure of 250 mTorr and an RF power of 100 W, reactive gases SiH<sub>4</sub>, O<sub>2</sub>, and Ar passed through the chamber at flow rates of 60 sccm, 10 sccm, and 10 sccm, respectively. Secondly, a 40-nm-thick  $\alpha$ -IGZO film was deposited on the SiO<sub>2</sub> film by RF sputtering via a LAB-18 system at room temperature. During the IGZO deposition process, the concentration of O<sub>2</sub>, pressure and RF power were 2%, 5 mTorr and 180 W, respectively [27]. Then, the active regions of the device were patterned by the UV lithography followed by a diluted hydrochloric acid (HCl) solution etching. Lastly, the source and drain electrodes were formed by lifting-off a 140 nm Mo metal layer by the LAB-18 with 250 W power in a 5 mTorr Ar atmosphere. The typical channel width and length were 80 µm and 10  $\mu$ m, respectively. The device's electrical properties were measured by a semiconductor parameter analyzer Keithley

B1500A at room temperature. The surface topography of the nanogranular SiO<sub>2</sub> was observed by a scanning electron microscope (SEM). The cross-section of the fabricated device was investigated using a high-resolution transmission electron microscopy (HRTEM, FEI Talos F200). A UV LED source with full intensity of 158.62 mW/cm<sup>2</sup> and three different wavelengths (365 nm, 395 nm and 405 nm) was used to illuminate the synaptic transistors in the light-related measurements.

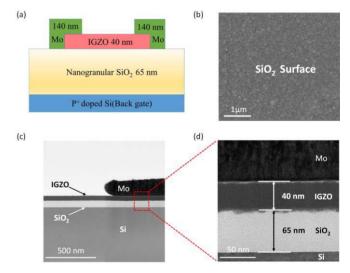

Fig. 1(a) depicts the bottom-gate top-contact structure of the nanogranular SiO<sub>2</sub>/IGZO synaptic transistor. Fig. 1(b) shows a typical SEM image of the surface of 65nm-thick nanogranular SiO<sub>2</sub>on Si substrate. The microporous structure is observed clearly. Fig. 1(c) illustrates a crosssectional HRTEM image of the nanogranular SiO<sub>2</sub>/IGZO synaptic transistor with a 65 nm gate oxide layer and Fig. 1(d) shows the zoom-in image. The thicknesses of the IGZO and SiO<sub>2</sub> are measured to be around 40 nm and 65 nm, respectively. The In, Ga, Zn, and O elements are uniformly distributed in the channel layer, as shown in Fig. S1, in the supplementary material. Moreever, it is interesting to note that the In element is precipitated from the IGZO layer and becomes crystallized at the SiO<sub>2</sub>/IGZO interface, as shown in Fig. S2, in the supplementary material.

**FIGURE 1.** Schematic and microstructure images of the fabricated transistor. (a) Schematic diagram of the proposed nanogranular SiO<sub>2</sub>/IGZO synaptic transistor. (b) The SEM image of the nanogranular SiO<sub>2</sub> surface. (c) The cross-sectional TEM image of the fabricated synaptic transistor. (d) The enlarged TEM image of the area marked by the red rectangle in Fig. 1(c).

### **III. RESULTS AND DISSCUSSION**

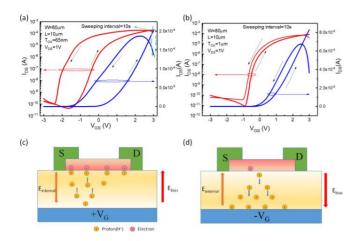

Different from a conventional transistor, a synaptic transistor has a memory capability that the threshold voltage is affected by the mobile charges in the insulting layer. As shown in the Fig. 2(a), the threshold voltage of the backward sweeping becomes smaller than that of the forward sweeping. The interval between the forward and back sweeping is 10 s. The threshold voltage is defined as the gate voltage at which the drain current reaches 10 nA [28]. For the current-voltage

FIGURE 2. Transfer curve of the fabricated transistor with different polarity gate bias. (a, b) Dual sweeping I-V data of the nanogranular Si02/IGZO synaptic transistor with (a) 65-nm-thick gate oxide and (b) 1- $\mu$ m-thick gate oxide at V<sub>DS</sub> = 1 V, the red line for the logarithmic coordinates and the blue line for the linear coordinates. The forward and backward sweeping directions are indicated by arrow heads on the curves. (c, d) Schematic of electric-double-layer structures when the voltage applied on the bottom gate is (c) positive and (d) negative.

(I-V) sweeping, the gate voltage ranges from -3 V to 3 V with the drain to source voltage (V<sub>DS</sub>) fixed at 1 V. The forward and backward sweeping directions are indicated by the arrow heads on the curves. The red line is shown in logarithmic coordinates and the blue line in linear coordinates. The device with a 65 nm gate oxide film shows a clear anticlockwise hysteresis due to the mobile ionic charges. The calculated memory window, i.e., the change of threshold voltage, is up to 1.48 V. The drain current on/off ratio and subthreshold swing of the device are  $4.3 \times 10^6$ and 120 mV/decade, respectively. Fig. 2(b) shows the dual sweeping transfer curves of another device with 1-µm-thick gate oxide. The measured memory window width is 0.165 V, much smaller than that of the device with a 65 nm-thick gate oxide. The anticlockwise hysteresis of the devices can be explained as follows. When a positive gate voltage is applied to the bottom gate, electrons will be induced in the IGZO channel as the mobile protons drift to the interface and accumulate, as shown in Fig. 2(c). Hydrogen dissociated from SiH<sub>4</sub> during the PECVD process can enter the nanogranular SiO<sub>2</sub> matrix as Si–OH<sup>+</sup> and formed the protons [18]. When a negative gate voltage is applied, the protons will be pulled away from the interface, as shown in Fig. 2(d). As the electric field strength is inversely proportional to the oxide thickness under a constant gate voltage, less protons drift to the insulator/channel interface inside the 1-µm-thick gate oxide in comparison to the 65-nm-thick one. As a result, the memory window of the device with a  $1\mu m$  gate oxide is narrower than that of the device with a 65 nm gate oxide. In this paper, all the measurements referred below are based on the 65 nm-thick nanogranular SiO<sub>2</sub> device unless specially stated.

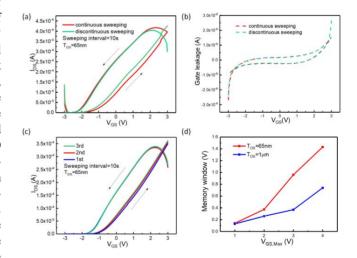

To find whether the protons move away from the insulator/channel interface to their equilibrium position, two different sweepings were used: continuous sweeping and discontinuous sweeping. In a continuous sweeping, the gate voltage was swept from -3 V to 3 V (forward) and back to -3 V (backward) without any interval. Whereas for the discontinuous sweeping, there is a 10 s break. As shown in Fig. 3(a), the starting drain current reduced in the magnitude and the drain current first rose as the gate voltage during the discontinuous sweeping. During the interval, the protons will move to their equilibrium positions naturally, which is called the protons relaxation and it makes the electrons in the channel reduces. That's why the starting drain current of backward sweeping is smaller than the ending drain current of forward sweeping. As the gate voltage is swept back, the electric field pushes more protons to the interface when the gate voltage is still positive. Thus, the current increases as the gate voltage decreases until the impact of voltage reduction surpasses the impact of protons induction on the channel. As shown in Fig. 3(b), the gate leakage is within 3 nA during the two different sweeping process. Fig. 3(c) shows that the nanogranular  $SiO_2$  based synaptic transistor has a good stability after three times of the discontinuous sweeping with an interval of 30 s by using a new fresh device to measure. The dependence of the memory window on the gate sweeping range is shown in Fig. 3(d). For the device with a 65-nm-thick gate oxide, the memory window is 0.14 V within a sweeping rang of -4 V to 1 V and changes to 1.43 V within a sweeping rang of -4 V to 4 V. The larger the  $V_{GS}$  is, the more protons accumulate near the nanogranular SiO<sub>2</sub>/IGZO interface.

FIGURE 3. Electrical performance of the fabricated transistor. (a) Comparison of the I-V curves between the discontinuous sweeping and continuous sweeping for the 65-nm-thick gate oxide device. (b) The gate leakage during the continuous and discontinuous sweeping. (c) Three times of discontinuous I-V sweeping for the 65-nm-thick gate oxide device. (d) The relation between the threshold voltage change (i.e., memory window) and the gate voltage sweeping range. All the measurements are with V<sub>DS</sub> of 1 V.

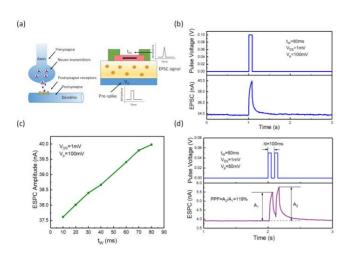

Fig. 4(a) depicts the analogy between a biological synapse and a nanogranular  $SiO_2$  based synaptic transistor: the bottom gate is similar to the presynapse, the protons in the

**FIGURE 4.** Excitatory postsynaptic current triggered by electrical pulses. (a) An analogy between the biological synapse and the artificial synaptic device in this work. The post-synapse's strength is decided by the amount of the neuro-transmitters for the biological synapse while the strength is affected by the protons in the insulator for the synaptic transistor. (b) EPSC (bottom panel) triggered by a presynaptic spike (100 mV, 80 ms) (top panel). The EPSC is measured with V<sub>DS</sub> of 1 mV. (c) The relation between the EPSC amplitude and the presynaptic spike width, measured with a pulse voltage of 100 mV and V<sub>DS</sub> of 1 mV. The amplitude of the pulse voltage is defined as V<sub>p</sub>. (d) A pair of presynaptic pulses and the EPSC triggered by the pulses, with a pulse width of 50ms, pulse voltage of 50 mV, V<sub>DS</sub> of 1 mV and pulse interval of 100 ms. A<sub>1</sub> and A<sub>2</sub> represent the amplitudes of the first and second EPSC, respectively.

insulator are equivalent to the neuro-transmitters in the synapse cleft, and the source electrode /channel/ drain electrode corresponds to the postsynapse. To verify the device's synaptic function, a pre-spike pulse (100 mV, 80 ms) was applied on the bottom gate with a V<sub>DS</sub> of 1 mV, as shown in Fig. 4(b). The pulse width and voltage amplitude are defined as t<sub>W</sub> and V<sub>p</sub>, respectively. The EPSC through the channel is from 33.8 nA to 39.8 nA at the end of the spike, after which the current decays slowly due to the proton relaxation described by an exponential relation [3]. The calculated energy dissipation of a single spike event is  $\sim$ 3.18 pJ, which is much lower than that of the reported nanogranular SiO<sub>2</sub>-based proton conductor gated synaptic transistors(~160 pJ) [16] and zinc oxide based synaptic devices ( $\sim$ 35 pJ) [9]. The energy dissipation per spike is calculated by  $E = I_{peak} \times t_W \times V_{DS}$ , where E is the energy dissipation per spike, Ipeak is the spike peak current, tw is pulse width and  $V_{DS}$  is the drain to source voltage. Fig. 4(c) shows that the EPSC amplitude increases with the presynaptic spike width, measured with a  $V_{DS}$  of 1 mV and  $V_p$  of 100 mV. As the spike width (t<sub>W</sub>) varies from 10 ms to 90 ms, the EPSC amplitude changes from 37.6 nA to 40 nA correspondingly. The number of the protons accumulated at the IGZO/SiO<sub>2</sub> interface is positively related to the time of gate spike and the number of the electrons induced in the IGZO channel increases as the pulse width linearly before the protons get saturated. So that the ESPC amplitude increase with the spike width linearly. This linearity may help build an analytical model of the ESPC amplitude with gate spike

input parameters in a single spike activity. Another important property widely concerned with the synaptic transistor is the paired pulse facilitation (PPF) in which the EPSC triggered by the second pulse will be enhanced by the first pulse due to the memory effect [29]. A pair of pulses were added to the bottom gate with the pulse width of 50 ms, pulse voltage of 50 mV, interval of 100 ms and V<sub>DS</sub> of 1 mV. As shown in Fig. 4(d), the PPF ( $A_2/A_1$ ) reaches 119%, where  $A_1$  and  $A_2$  represent the amplitudes of the first and second EPSC, respectively.

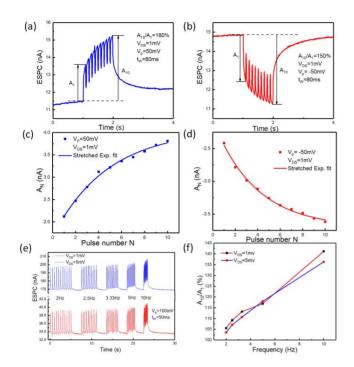

To observe the PPF effect better, a train of 10 pulses was taken to investigate the PPF phenomenon with the V<sub>DS</sub> of 1 mV, pulse width of 80 ms and pulse interval of 100 ms. As shown in Fig. 5(a), the current pulse EPSC was larger than the previous one, which corresponds to the short-term potentiation. The amplitude of the tenth EPSC signal and the amplitude of the first post synaptic signal were defined as A<sub>10</sub> and A<sub>1</sub> and their ratio reaches 180%. It could be found that when the V<sub>p</sub> was reduced to 50 mV, the least energy consumption of a single spike even dropped to 1.08 pJ, calculated by  $E = I_{peak} \times t_W \times V_{DS} = 13.5 \text{nA} \times 80 \text{ms} \times 1 \text{mV} =$ 1.08pJ. As explained above, the protons near the insulator/channel interface will relax to their equilibrium positions. However, there is a relaxation time and part of the protons induced by the prior pulse still exists near the interface, which results in an enhanced EPSC when the next pulse comes. The short-term depression of the synaptic device was also observed. As shown in Fig. 5(b), the EPSC reduced as the pulse train went, measured with a  $V_p$  of -50 mV because the proton reduced near the interface under the negative gate voltage. This measurement was taken with a device after proton accumulation. As shown in Fig. 5(c), 5(d), the amplitude of the spike current changed with the pulse number can be described using a saturating exponential function:

$$A_{N} = A_{0} + r \bullet \exp(-\frac{N}{N_{0}}) \tag{1}$$

where  $A_N$  represents the Nth amplitude of the spike current, N is the pulse number in the pulses train,  $A_0$  is the final current which the EPSC is expected to reach, r is a constant current increment and  $N_0$  is a constant. Fig. 5(e) describes the relation between the excitatory post synaptic current and the pre-spike frequency. Five groups of ten constant  $t_W$  (50 ms) pulses were applied on the device successively with different frequency (2, 2.5, 3.3, 5, 10 Hz) with a V<sub>p</sub> of 100 mV and V<sub>DS</sub> of 1 mV, 5 mV. The EPSC potentiation was positively correlated to the pre-spike frequency as indicated in Fig. 5(f). The current gain, defined as  $A_{10}/A_1$ , increases with the prespike frequency, but is not affected by the amplitude of V<sub>DS</sub>. This indicates that the structure fabricated has a potential to be used as a high-pass filter for information transmission.

Up to now, most reported synaptic transistors have been stimulated with electrical signals while few have concerned the light stimulus, which may have a much wider bandwidth and no RC delay for signal transmission [30]. It is urgent now to study the light effects on the electrical transistors

**FIGURE 5.** Excitatory postsynaptic current triggered by a pulse train. (a) The EPSC measured with the synaptic transistor using 10 presynaptic pulses (50 mV, 80 ms) train with pulse interval of 100 ms. (b) The EPSC measured using 10 presynaptic pulses (-50 mV, 80 ms) train with pulse interval of 100 ms. (c), (d) The relationships between the EPSC amplitude and the gate spike pulse numbers, measured with (c) a positive pulse voltage V<sub>p</sub> = 50mV, (d) a negative pulse voltage V<sub>p</sub> = -50mV, extracted from Fig. 5(a), 5(b). Results from analytical model using a saturating exponential function are also plotted. (e) The EPSC with a constant pulse width of 50 ms where frequency is varied from 2 to 10 Hz at V<sub>DS</sub> = 1 mV, 5 mV. (f) The EPSC versus pre-spike frequency where A<sub>10</sub> represents the amplitude of the 10th EPSC signal and A<sub>1</sub> represents the amplitude of the first post synaptic signal, extracted from Fig. 5(e).

in detail [31]. Another reason to explore the transistor's response to the UV light is that the biological synapse responds to the UV stimulus and moderate UV exposure contributes to the brain's improved learning, object recognition and memory ability [23].

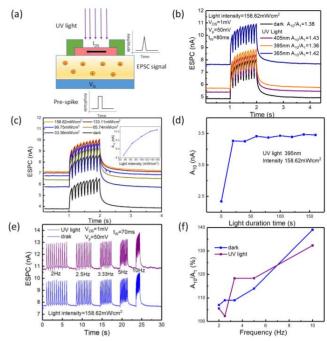

In this work, the UV light is used as the assisting terminal to study the impact of the electrical stimulus and then the light is employed as the control terminal to investigate its influences on the synapse transistors. The band gap of the  $\alpha$ -IGZO is about 3.36 eV and the synaptic transistor proposed in this paper should respond to the ultraviolet light. An ultraviolet LED (full intensity of 158.62 mW/cm<sup>2</sup>) was used to illuminate the synapse, depicted in Fig. 6(a). UV light sources with three different wavelengths (365 nm, 395 nm and 405 nm) were used to measure the synapse sensitivity to wavelength and the results are shown in Fig. 6(b). The synapse's weight was strengthened by the UV light and the drain current increased most responding to the UV light of 365 nm from 4.85 nA to 7.61 nA with a  $V_{DS}$  of 1 mV,  $V_p$  of 50 mV and t<sub>W</sub> of 80 ms. In the electrical stimulus, constant UV light illumination can promote the device's conductance around 56%, but does not impact the EPSC gain, which

**FIGURE 6.** Excitatory postsynaptic current by electrical pulses under the light illumination. (a) Schematic of the ultraviolet light illuminating the synaptic transistor. (b) The device's response to different wavelengths UV light using a ten pulse pre-spikes, measured with a pulse voltage of 50 mV, pulse width of 80 ms,  $V_{DS}$  of 1 mV and light intensity of 158.62mW/cm<sup>2</sup>. (c) The EPSC signal under different light intensity and the inset figure depicts the relation between the  $A_{10}$  and the light intensity. Each intensity measurement is taken after 180 s illumination for the device to achieve steady state. (d) The tenth amplitude of the EPSCs signal versus the light illumination duration time with a 395 nm UV light and full intensity (158.62 mW/cm<sup>2</sup>). (e) The EPSC signals with different frequency pulses under the 395 nm full intensity UV light. (f) The relation between the EPSC gain ( $A_{10}/A_1$ ) and the frequency under the 395 nm full intensity UV light.

remained at about 1.40 for the three kinds of wavelengths. Fig. 6(c) shows that the EPSC signal increases with the light intensity and the inset figure depicts the relation between the tenth amplitude of the EPSC and the light intensity. As the intensity increases, the EPSC grows fast first and then gradually levels off. Each light intensity measurement is taken after 180 s illumination for the device to achieve steady state. The response of the synapse to the light illumination time is shown in Fig. 6(d) and is similar to its response to the light intensity. Fig. 6(e), 6(f) show that the UV light does not influence the synapse transistor's relation between PPF index and the electrical pulse' frequency. The light wavelength, intensity and duration time show little effect on the synapse's plasticity with a constant illumination in the electrical stimulus. Next, the UV light will be an independent control terminal without electrical spikes to study the light's impact on the synapse transistor's plasticity.

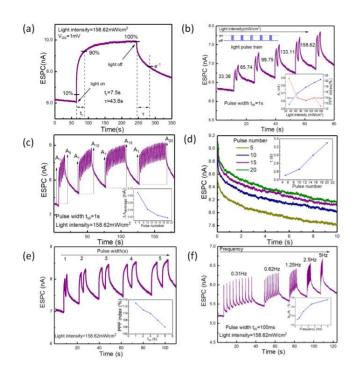

In order to study the light terminal's influence on the synapse' plasticity, a light pulse was applied on the channel surface. As shown in Fig. 7(a), the EPSC increased rapidly after the light was turned on and decayed slowly after the light was turned off. Unless otherwise stated, the following

FIGURE 7. Excitatory postsynaptic current triggered by light pulses. (a)The synapse's response to the UV light using the light as the control terminal with the gate floating,  $V_{DS}$  of 1 mV and light intensity of 158.62mW/cm<sup>2</sup> (b) The EPSC spikes triggered by the ten light pulse train with five kinds of light intensity with pulse width of 1 s. The figure inset of (b) depicts the relation between the A1, PPF (A2/A1) and light intensity. (c) The EPSCs triggered by light pulses train with different pulse number (5, 10, 15, 20), measured with light intensity of 158.62 mW/cm<sup>2</sup> and pulse width of 1 s. The figure inset of (c) depicts the relation between the average spike amplitude change and the section's pulse number. (d) The channel EPSC signal decays after applying different numbers of light pulse sections, extracted from Fig. 7(c). The inset of Fig. 7(d) depicts the relation between the retention time and the section's pulse number. (e) The EPSCs triggered by light pulses train with five sections of different pulse width, measured with a light intensity of 158.62 of mW/cm<sup>2</sup>. The figure inset of (e) depicts the relation between the PPF and pulse width. (f) The EPSCs triggered by light pulses train with different pulse frequency, measured with light intensity of 158.62 mW/cm<sup>2</sup> and pulse width of 100 ms. The figure inset of (e) depicts the relation between the EPSC gain and pulse frequency.

measurements were using the full intensity 395 nm UV light with the gate floating and  $V_{DS}$  of 1 mV. The time for the current to rise from 10% to 90% of the whole dynamic range (t<sub>r</sub>) was measured to be 7.5 s. The decaying characteristic after the light was turned off can be described by Equation (2) [30]:

$$\mathbf{I} = (\mathbf{I}_0 - \mathbf{I}_{int}) \cdot \exp\left[-\left(\frac{\mathbf{t} - \mathbf{t}_0}{\tau}\right)^{\beta}\right] + \mathbf{I}_{int}$$

(2)

where  $I_0$  is the current recorded immediately after the light pulse,  $I_{int}$  is the device's current before any light illumination,  $t_0$  is the time when the UV light is turned off,  $\tau$  is the retention time, and  $\beta$  is an index between 0 and 1. After 180 s UV light illumination, the EPSC rose from 6 nA to 10 nA and  $\tau$  was 43.6 s. The current growth rate became smaller as the illumination time extended. The PPF effect was observed in the light stimulus, where a four-section train of pair pulses with different light intensity was applied on the synapse transistor, as shown in Fig. 7(b). One probable explanation of the synapse's plasticity is due to the inherent persistent photoconductivity (PPC) characteristic of the amorphous IGZO and the neutralization of ionized oxygen vacancies may take a long period, leading to the current decaying slowly after the light off [25]. As shown in the inset figure of Fig. 7(b), A1 increased with the light intensity from 0.56 nA to 0.88 nA while the PPF  $(A_2/A_1)$  slightly decreased with the intensity. Fig. 7(c) describes the relation between the EPSC and the pulse number by using a foursection pulse train with 5, 10, 15, 20 pulses, respectively. The inset figure shows that the average amplitude-change decreased with the pulse number. Fig. 7(d), extracted from the Fig. 7(c), shows that the EPSC decayed with time after each light pulse section was finished. It is worth noting that the  $\tau$  increases with the pulse number from 2.51 s to 3.30 s as the pulse number rises from 5 to 20, as shown in the inset of Fig. 7(d). Although the growth rate is small, after a 180 s illumination,  $\tau$  can rise to 43.6 s according to Fig. 7(a). The ability to expand the feature time by adding pulse width and number is very important for synapse learning because this means that the STM (short term memory) to the LTM (long term memory) transition can be achieved by a series of rehearsal just like human learning and remembering activity. As shown in Fig. 7(e) and the inset figure, the PPF index slightly decreased with pulse width, measured with pairpulse train with t<sub>W</sub> of 1 s, 2 s, 3 s, 4 s, 5 s, respectively. Fig. 7(f) describes the EPSC triggered by a ten-pulse train with five kinds of frequency. When the frequency was 0.31, 0.62, 1.25, 2.5, 5 Hz, the EPSC gain (A<sub>10</sub>/A<sub>1</sub>) was 126%, 128%, 135%, 143%, 148%, respectively, with a maximum of 17.5% increase. The higher the frequency is, the shorter the off-period of UV light is and more carriers accumulate in the channel layer. The important finding is that the frequency has more obvious effect on the synapse's plasticity than the other light pulse parameters including intensity, numbers and width.

#### **IV. CONCLUSION**

In summary, a nanogranular SiO<sub>2</sub>-based proton conductor sgated thin film synaptic transistor using IGZO was proposed in this paper. The synaptic transistor mimicked the biological synapse's short term plasticity and short term memory property. In addition to realizing electrical control of the synaptic transistor, the UV light is found to be another effective control terminal and this is important for the synaptic transistor network and system to realize the complex functions are existing challenges. It is promising to investigate the synaptic transistor's plasticity with multiple presynaptic inputs and using organic wearable insulator. Nevertheless, the work here shows that the nanogranular SiO<sub>2</sub>/IGZO structure is attractive for the potential applications in synaptic electronics.

## REFERENCES

- D. A. Drachman, "Do we have brain to spare?" *Neurology*, vol. 64, no. 12, pp. 2004–2005, 2005.

- [2] D. Kuzum, S. Yu, and H.-S. P. Wong, "Synaptic electronics: Materials, devices and applications," *Nanotechnology*, vol. 24, no. 38, 2013, Art. no. 382001.

- [3] L. Q. Zhu, C. J. Wan, L. Q. Guo, Y. Shi, and Q. Wan, "Artificial synapse network on inorganic proton conductor for neuromorphic systems," *Nat. Commun.*, vol. 5, p. 3158, Jan. 2014.

- [4] H. Yuan *et al.*, "Hydrogenation-induced surface polarity recognition and proton memory behavior at protic-ionic-liquid/oxide electricdouble-layer interfaces," *J. Amer. Chem. Soc.*, vol. 132, no. 19, pp. 6672–6678, 2010.

- [5] S. Yu, Y. Wu, R. Jeyasingh, D. Kuzum, and H.-S. P. Wong, "An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2729–2737, Aug. 2011.

- [6] Z. Q. Wang et al., "Synaptic learning and memory functions achieved using oxygen ion migration/diffusion in an amorphous InGaZnO memristor," Adv. Funct. Mater., vol. 22, no. 13, pp. 2759–2765, 2012.

- [7] K. Xu, "Integrated silicon directly modulated light source using P-well in standard CMOS technology," *IEEE Sensors J.*, vol. 16, no. 16, pp. 6184–6191, Aug. 2016.

- [8] A. Daus *et al.*, "Ferroelectric-like charge trapping thin-film transistors and their evaluation as memories and synaptic devices," *Adv. Electron. Mater.*, vol. 3, no. 12, 2017, Art. no. 1700309.

- [9] P. B. Pillai and M. M. De Souza, "Nanoionics-based three-terminal synaptic device using zinc oxide," ACS Appl. Mater. Interfaces, vol. 9, no. 2, pp. 1609–1618, Jan. 2017.

- [10] Q. Lai et al., "Ionic/electronic hybrid materials integrated in a synaptic transistor with signal processing and learning functions," Adv. Mater., vol. 22, no. 22, pp. 2448–2453, 2010.

- [11] Y. H. Liu, L. Q. Zhu, P. Feng, Y. Shi, and Q. Wan, "Freestanding artificial synapses based on laterally proton-coupled transistors on chitosan membranes," *Adv. Mater.*, vol. 27, no. 37, pp. 5599–5604, 2015.

- [12] J. Shi, S. D. Ha, Y. Zhou, F. Schoofs, and S. Ramanathan, "A correlated nickelate synaptic transistor," *Nat. Commun.*, vol. 4, no. 4, p. 2676, 2013.

- [13] P. Gkoupidenis, N. Schaefer, B. Garlan, and G. G. Malliaras, "Neuromorphic functions in PEDOT:PSS organic electrochemical transistors," *Adv. Mater.*, vol. 27, no. 44, pp. 7176–7180, 2016.

- [14] G. I. Wirth, J. Koh, R. D. Silva, R. Thewes, and R. Brederlow, "Modeling of statistical low-frequency noise of deep-submicrometer MOSFETs," *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1576–1588, Jul. 2005.

- [15] C. J. Wan, L. Q. Zhu, J. M. Zhou, Y. Shi, and Q. Wan, "Memory and learning behaviors mimicked in nanogranular SiO<sub>2</sub>-based proton conductor gated oxide-based synaptic transistors," *Nanoscale*, vol. 5, no. 21, pp. 10194–10199, 2013.

- [16] J. Wang, Y. Li, C. Yin, Y. Yang, and T.-L. Ren, "Long-term depression mimicked in an IGZO-based synaptic transistor," *IEEE Electron Device Lett.*, vol. 38, no. 2, pp. 191–194, Feb. 2017.

- [17] Y.-H. Kim *et al.*, "Flexible metal-oxide devices made by roomtemperature photochemical activation of sol-gel films," *Nature*, vol. 489, no. 7414, pp. 128–132, 2012.

- [18] M. J. Liu *et al.*, "Nanogranular SiO<sub>2</sub> proton gated silicon layer transistor mimicking biological synapses," *Appl. Phys. Lett.*, vol. 108, no. 25, 2016, Art. no. 253503.

- [19] C. J. Wan et al., "Short-term synaptic plasticity regulation in solutiongated indium-gallium-zinc-oxide electric-double-layer transistors," ACS Appl. Mater. Interfaces, vol. 8, no. 15, pp. 9762–9768, Apr. 2016.

- [20] J. Zhou, N. Liu, L. Zhu, Y. Shi, and Q. Wan, "Energy-efficient artificial synapses based on flexible IGZO electric-double-layer transistors," *IEEE Electron Device Lett.*, vol. 36, no. 2, pp. 198–200, Feb. 2015.

- [21] A. Lu, J. Sun, J. Jiang, and Q. Wan, "Microporous SiO<sub>2</sub> with huge electric-double-layer capacitance for low-voltage indium tin oxide thin-film transistors," *Appl. Phys. Lett.*, vol. 95, no. 22, p. 2457, 2009.

- [22] L. Q. Zhu, J. Sun, G. D. Wu, H. L. Zhang, and Q. Wan, "Selfassembled dual in-plane gate thin-film transistors gated by nanogranular SiO<sub>2</sub> proton conductors for logic applications," *Nanoscale*, vol. 5, no. 5, pp. 1980–1985, 2013.

- [23] H. Zhu *et al.*, "Moderate UV exposure enhances learning and memory by promoting a novel glutamate biosynthetic pathway in the brain," *Cell*, vol. 173, no. 7, pp. 1716–1727, 2018.

- [24] S. Dai et al., "Light-stimulated synaptic devices utilizing interfacial effect of organic field-effect transistors," ACS Appl. Mater. Interfaces, vol. 10, no. 25, pp. 21472–21480, Jun. 2018.

- [25] M. Lee *et al.*, "Brain-inspired photonic neuromorphic devices using photodynamic amorphous oxide semiconductors and their persistent photoconductivity," *Adv. Mater.*, vol. 29, no. 28, 2017, Art. no. 1700951.

- [26] T. Goto, K.-I. Sato, Y. Yabuta, S. Sugawa, and S. Hara, "New compact electron cyclotron resonance plasma source for silicon nitride film formation in minimal fab system," *IEEE J. Electron Devices Soc.*, vol. 6, no. 1, pp. 512–517, Nov. 2018.

- [27] W. Zhang *et al.*, "Demonstration of α-InGaZnO TFT nonvolatile memory using TiAlO charge trapping layer," *IEEE Trans. Nanotechnol.*, to be published.

- [28] K. Xu, "Monolithically integrated Si gate-controlled light-emitting device: Science and properties," J. Opt., vol. 20, no. 2, 2018, Art. no. 024014.

- [29] J. Wang, Y. Li, Y. Yang, and T.-L. Ren, "Top-gate electric-double-layer IZO-based synaptic transistors for neuron networks," *IEEE Electron Device Lett.*, vol. 38, no. 5, pp. 588–591, May 2017.

- [30] H. K. Li *et al.*, "A light-stimulated synaptic transistor with synaptic plasticity and memory functions based on InGaZnO<sub>x</sub>-Al<sub>2</sub>O<sub>3</sub> thin film structure," *J. Appl. Phys.*, vol. 119, no. 24, 2016, Art. no. 244505.

- [31] K. Xu et al., "Light emission from a poly-silicon device with carrier injection engineering," Mater. Sci. Eng. B, vol. 231, pp. 28–31, May 2018.

- [32] Y. Liu *et al.*, "Ultra-sensitive near-infrared graphene photodetectors with nanopillar antennas," *Nanoscale*, vol. 9, no. 44, pp. 17459–17464, 2017.

- [33] W. Chen, R. Liang, J. Wang, S. Zhang, and J. Xu, "Enhanced photoresponsivity and hole mobility of MoTe<sub>2</sub> phototransistors by using an Al<sub>2</sub>O<sub>3</sub> high-κ gate dielectric," *Sci. Bull.*, vol. 63, no. 15, pp. 997–1005, Aug. 2018.

**WEIJUN CHENG** received the B.S. degree in microelectronics from Jilin University, Changchun, China, in 2016. He is currently pursuing the Ph.D. degree in electronic science and technology with the Department of Microelectronics, Tsinghua University, China.

His current research interests include synaptic devices, hafnia-based ferroelectric thin film transistor, and 2-D material-based novel devices.

**RENRONG LIANG** received the Ph.D. degree in electronics science and technology from Tsinghua University, Beijing, China, in 2008, where he has been an Assistant Professor with the Institute of Microelectronics since 2010. His current research interests are concerned with fabrication and simulation of SiGe and 2-D materials-based devices, transport models and optimization of low-power nanoscale MOS devices, such as strained Si MOSFETs, FinFETs, tunneling FETs and negative capacitance FETs, and device physics.

**HE TIAN** received the Ph.D. degree from the Institute of Microelectronics, Tsinghua University in 2015, where he is currently an Assistant Professor. He has co-authored over 100 papers and has over 2900 citations. He has been researching on various 2-D material-based novel nanodevices. He was a recipient of the IEEE EDS Ph.D. Student Fellowship and Tsinghua University Top-Ten Scholarship in 2013.

**CHUANCHUAN SUN** received the Ph.D. degree from the Institute of Microelectronics, Tsinghua University in 2018. He is currently an Engineer with the Beijing Institute of Control Engineering.

**JING WANG** received the Ph.D. degree from the General Research Institute for Nonferrous Metals. He is an Associate Professor with the Institute of Microelectronics, Tsinghua university. His current research interests are concerned with fabrication and simulation of Si, Ge, and SiGe-based devices.

**CHUNSHENG JIANG** received the B.S. degree in microelectronics from Xidian University, Xi'an, China, in 2013. He is currently pursuing the Ph.D. degree in EE with Tsinghua University, Beijing, China. He is currently a visiting student with Purdue University, West Lafayette, IN, USA.

His current research interests include device physics, compact models, and circuit simulation for negative capacitance transistor, and junctionless transistor.

**TIAN-LING REN** received the Ph.D. degree in solid-state physics from the Department of Modern Applied Physics, Tsinghua University, Beijing, China, in 1997, where he has been a Full Professor with the Institute of Microelectronics since 2003. His main research interests include 2-D-material-based devices and novel nanoelectronic devices, intelligent sensors and integrated microelectromechanical systems, and critical technology for advanced microand nano-electronics.

**XIAWA WANG** received the Ph.D. degree in electrical engineering from the Massachusetts Institute of Technology in 2017. She is currently a Post-Doctoral Researcher with Tsinghua University, Beijing, China.

Her research interests are novel photonics and semiconductor devices and their applications in industry.

**JUN XU** received the B.S., M.S., and Ph.D. degrees in electrical engineering in 1986, 1989, and 1994, respectively. He is a Full Professor with Tsinghua University. His research interests are in the area of nano-scale high performance CMOS devices and technology.