# Quality-driven model-based design of multi-processor accelerators : an application to LDPC decoders

*Citation for published version (APA):* Jan, Y. (2012). *Quality-driven model-based design of multi-processor accelerators : an application to LDPC* decoders. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR732195

DOI: 10.6100/IR732195

#### Document status and date:

Published: 01/01/2012

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Quality-driven Model-based Design of Multi-processor Accelerators

An Application to LDPC Decoders

# PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op dinsdag 29 mei 2012 om 16.00 uur

door

Yahya Jan

geboren te Charsadda, Pakistan

Dit proefschrift is goedgekeurd door de promotor:

prof.dr. J. Pineda de Gyvez

Copromotor: dr. L. Jóźwiak

Quality-driven Model-based Design of Multi-processor Accelerators An Application to LDPC Decoders / by Yahya Jan. - Eindhoven : Eindhoven University of Technology, 2012. A catalogue record is available from the Eindhoven University of Technology Library ISBN 978-90-386-3136-3 NUR 959 Keywords: embedded systems / electronic design automation / highly-demanding applications / multi-processor accelerators / massively parallel systems.

# Quality-driven Model-based Design of Multi-processor Accelerators An Application to LDPC Decoders

Committee:

prof.dr. J. Pineda de Gyvez (promotor, TU Eindhoven) dr. L. Jóźwiak (co-promotor, TU Eindhoven) prof.dr.ir. R.H.J.M. Otten (TU Eindhoven) prof.dr. K. Bertels (TU Delft) dr. M. Duranton (Institute CARNOT CEA LIST France) dr.ir. T.J. Tjalkens (TU Eindhoven)

The work reported in this thesis is supported by HEC (Higher Education Commission Pakistan) in collaboration with NUFFIC (Netherlands organization for international cooperation in higher education) and Eindhoven University of Technology.

<sup>©</sup> Yahya Jan 2012. All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Cover Design: Edwin van Drunen Printing: Printservice Eindhoven University of Technology

# Abstract

The recent spectacular progress in nano-electronic technology has enabled the implementation of very complex multi-processor systems on single chips (MPSoCs). However in parallel, new highly-demanding complex embedded applications are emerging, in fields like communication and networking, multimedia, medical instrumentation, monitoring and control, military, etc., which impose stringent and continuously increasing functional and parametric demands. The high demands of these applications cannot be satisfied by systems implemented on general purpose processors (GPP). For these applications increasingly complex and highly optimized application-specific MPSoCs are required to perform real-time computations to extremely tight schedules, when satisfying high demands regarding the energy, area, cost and development efficiency. High-quality MPSoCs for these highly-demanding applications can only be constructed through adequate usage of efficient application-specific system architectures exploiting adequate concepts of computation, storage and communication, as well as, usage of efficient design methods and electronic design automation (EDA) tools for synthesizing the actual high-quality hardware platforms implementing the architectures.

Some of the representative examples of these highly-demanding applications include the based-band processing in wired/wireless communication (e.g. the upcoming 4G wireless systems), different kinds of encoding/decoding in communication, image processing and multimedia, 3D graphics, ultra-high-definition television (UHDTV), and encryption applications, etc. These applications require to perform complex computations with a very high throughput, while at the same time demanding low energy and low cost. The decoders of the low density parity check (LDPC) codes, adopted as an advance error-correcting scheme in the newest wired/wireless communication standards, like IEEE 802.11n, 802.16e/m, 802.15.3c, 802.3an, etc., for applications as digital TV broadcasting, mm-wave WPAN, etc., can serve as a representative example of such applications. These standards, for instance the IEEE 802.15.3c, specify as high as  $5\sim 6$  Gbps throughput for the upcoming wireless communication systems. For the realization of the throughput as high as several Gbps, massively parallel multi-processor accelera-

i

tors are indispensable.

These modern highly-demanding applications involve massive parallelism of various kinds (e.g. task, data and functional, etc) and complex interrelationships among the data and computing operations. Therefore, an adequate accelerator design for such highly-demanding applications requires a careful exploration and exploitation of various kinds of parallelism and the resolution of complex interrelationships between the data and computing operations. More precisely, the accelerator design for such kind of applications has to involve adequately the combined micro- and macro-architecture design for the processors, and the corresponding adequate memory and communication architectures design. Since the processor's micro-/macro-architecture and the memory and communication architectures are strongly interrelated and cannot be designed in separation, complex mutual tradeoffs have to be resolved among the processor parallelism at the two levels, and the corresponding memory and communication architectures, as well as, among the performance, power and area. For the design of hardware accelerators, high-level-synthesis (HLS) methods and tools are often used. However, the HLS methods and tools only support the micro-architecture synthesis of a single processing unit, while not taking into account the macro-architecture, memory and communication synthesis and not accounting for the relationships and tradeoffs among these design aspects, which is necessary in the design of hardware accelerators for highly-demanding applications.

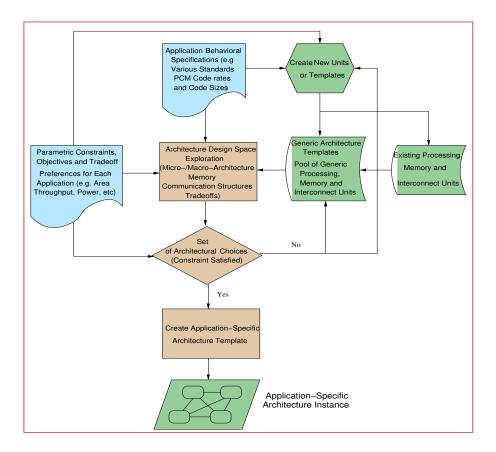

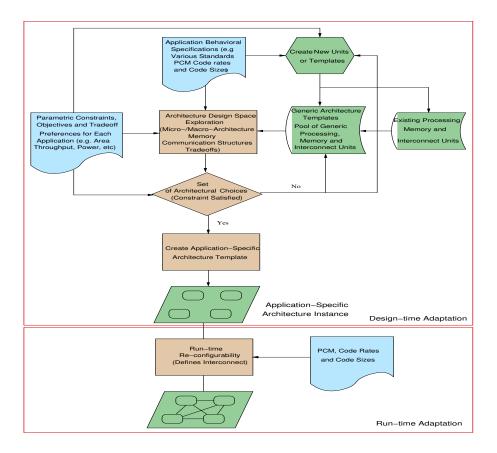

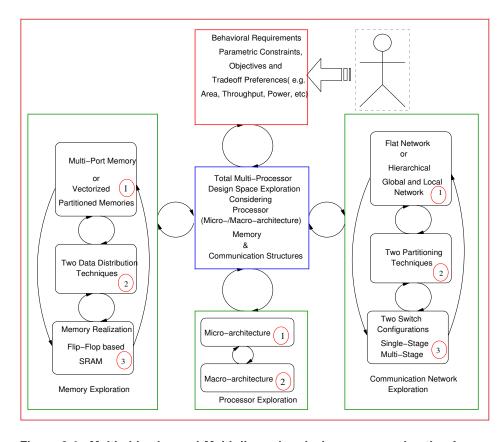

To address the issues highlighted above and to resolve the mutual tradeoffs effectively and efficiently, a novel quality-driven model-based hardware multiprocessor design methodology and the related design space exploration (DSE) approach is proposed in this thesis that jointly consider the processor, memory and communication architectures, and the possible mutual tradeoffs among them.

For the ultra-high throughput requirements that demand massively parallel hardware multi-processor architectures, the communication and memory have usually a dominating influence on all the most important design aspects such as delay, area and power. The additional performance gains expected from an increased parallelism will end up in diminished returns, when exploding the interconnect or memory complexity. Although some research results on the memory and communication architectures can be found in the literature, these results are for programmable on-chip multi-processor systems that utilize the time-shared communication resources, such as shared buses or Network on Chip (NoC). Such communication resources are however not adequate to deliver the data transfer bandwidth required for the massively parallel multi-processor accelerators. Therefore, in the research reported in this thesis, several promising generic scalable communication and memory architectures are proposed that satisfy the required data transfer bandwidth of the high-end multi-processor accelerators. The proposed generic hierarchical partitioned communication and memory architectures ensure the scalability when applied for massively parallel hardware multi-processor accelerators.

The proposed design methodology makes it possible to perform an effective

and efficient exploration and exploitation of the various tradeoffs between the processing parallelism at the micro- and macro-architecture level and the corresponding memory and communication architectures, as well as, among the performance, power and area, to arrive at high-quality accelerator architectures. Several novel scheduling, processing parallelism exploration, and the memory and communication architecture exploration strategies are incorporated into the proposed architecture design space exploration framework.

To analyze and evaluate the proposed design methodology and its related design space exploration framework, a series of extensive case studies are performed through implementing and applying the methodology for industrial-strength applications of the LDPC decoding for the latest communication system standards. These case studies involved extensive architecture synthesis experiments with the LDPC decoder designs for IEEE 802.15.3c LDPC codes. In particular, the results of the experiments clearly demonstrate that neither the fully-serial nor the fullyparallel micro-architectures are adequate to satisfy the ultra-high performance requirements. The extreme fully-serial and fully-parallel micro-architectures are also not appropriate from the viewpoint of the area and power consumption. To satisfy the ultra-high performance or ultra-low power requirements, the combined micro-/macro-architecture exploration is necessary which explores and exploits various partially-parallel architecture combinations.

The results of the experiments confirmed that without considering the processor's micro- and macro-architecture design, as well as, the communication and memory architecture design in combination, it is very difficult to arrive at an adequate high-quality accelerator. They confirmed that the proposed design methodology adequately supports the design of complex multi-processor hardware accelerators, while taking into account the numerous complex tradeoffs.

To our knowledge, despite a more than a decade of research on the hardware accelerators for the highly-demanding applications, no similar holistic qualitydriven design approach has been proposed. In the proposed design method, all the design components are taken jointly as a single design task and the mutual tradeoffs among them, as well as, among different design objectives are considered. Finally, using the method, it is possible to implement various high-quality complex multi-processor hardware accelerators for the highly-demanding applications (e.g. LDPC decoders of practical importance for the newest upcoming wireless communication standards) very quickly. iv

# Acknowledgments

There are many people who contributed directly or indirectly to the work reported in this thesis and I would like to express my gratitude to all of them.

First of all, I would like to thank Prof. Jose Pineda de Gyvez, my promoter. His detailed reviews and constructive remarks significantly improved the quality and overall organization of this thesis.

Next, I would like to thank my co-promoter and direct supervisor Dr. Lech Jóźwiak who provided me the opportunity to perform research in the electronic systems group. His guidance and consistent involvement in all phases of my PhD research project is truly remarkable. During my PhD, we had many and often long technical meetings that helped me a lot in my work. His way of thinking, perception of things and his quality concepts have much improved my theoretical knowledge and understanding of systems. He also helped me in resolving several financial and other issues.

I would also like to thank all the members of my PhD promotion committee for their time and feedback on my thesis. My special thanks go to Dr. Marc Duranton and Dr. Tjalling J. Tjalkins for their collaboration and support during the initial phase of my PhD project.

It was a great and pleasant experience for me to work in the electronic system group. It took me almost no time to settle down in the working environment of the group. I enjoyed my work and the company of my colleagues. I would like to thank them all. I would like to thank Prof. Ralph Otten for accepting me in the group, and Ahsan Shabbir for his help on many issues both technical and nontechnical, when we were together in the electronic systems group. Special thanks to our secretaries Marja and Rian for their guidance regarding all administrative issues, filling out forms written in Dutch, and for their always happy and friendly attitude. I would like to thank my family, my mother Sarhad Bibi, my brothers Daud Jan, Ayub Jan, Easa Khan, and my sister Nighat Ara. I believe that without their support and encouragement, it would be difficult to achieve this result. Many many thanks to Easa Khan for his support, company and visits to Netherlands, when he was studying in Italy. I regret for being away from my family on two important occasions. First, the wedding ceremony of my sister in 2008, and then another important event in my family, the wedding ceremony of my two elder brothers, Daud Jan and Ayub Jan in early 2012. It was very hard for them to accept my absence, especially for my mother, no words to express. Therefore, I dedicate this thesis to my family including the cute Hassan Ahmad, son of my sister.

I would like to thank my friends from Netherlands. Special thanks go to Edwin and Ilinca for helping me in many ways. We spent many weekends together, whether it was cooking a meal together, watching a movie, going on biking trips. I never felt alone in Eindhoven due to their company, God bless them. I would also like to thank Karen and her family having lived with them for a long time. Finally, I would like to thank all of my Pakistani friends living in Netherlands. Especially, I would like to thank all of my friends living in Delft for entertaining me many times during holiday visits to Delft. I am grateful for the exceptional reception. A fantastic time with all of them, *thanks to all*.

Yahya Jan

# Contents

| $\mathbf{A}$ | Abstract i                                                  |                                                                 |    |  |  |  |

|--------------|-------------------------------------------------------------|-----------------------------------------------------------------|----|--|--|--|

| A            | Acknowledgments                                             |                                                                 |    |  |  |  |

| 1            | Intr                                                        | oduction                                                        | 1  |  |  |  |

|              | 1.1                                                         | Modern Highly-demanding Applications                            | 3  |  |  |  |

|              | 1.2                                                         | Main Challenges of Accelerators Design for Highly-demanding Ap- |    |  |  |  |

|              |                                                             | plications                                                      | 5  |  |  |  |

|              | 1.3                                                         | The Aim and Key Contributions of this Thesis                    | 8  |  |  |  |

|              |                                                             | 1.3.1 Design Methods and EDA Tools                              | 8  |  |  |  |

|              |                                                             | 1.3.2 Architecture Design                                       | 9  |  |  |  |

|              |                                                             | 1.3.3 Better Understanding of Architecture Design Problems for  |    |  |  |  |

|              |                                                             | Highly-demanding Applications                                   | 10 |  |  |  |

|              | 1.4                                                         | Thesis Organization                                             | 11 |  |  |  |

| <b>2</b>     | Problem Analysis, Research Task Formulation and Related Re- |                                                                 |    |  |  |  |

|              | sear                                                        | •                                                               | 13 |  |  |  |

|              | 2.1                                                         | Issues of Hardware Accelerator Design for Highly-demanding Ap-  |    |  |  |  |

|              |                                                             | plications                                                      | 14 |  |  |  |

|              | 2.2                                                         | Accelerator Design for LDPC Decoders                            | 20 |  |  |  |

|              | 2.3                                                         | Requirements of an Adequate Accelerator Design                  | 24 |  |  |  |

|              | 2.4                                                         | Research Task Formulation                                       | 25 |  |  |  |

|              | 2.5                                                         | The Proposed Design Approach                                    | 26 |  |  |  |

|              | 2.6                                                         | Related Research                                                | 28 |  |  |  |

|              |                                                             | 2.6.1 Application Analysis and Parallelization                  | 29 |  |  |  |

vii

|          |                                                               | 2.6.2  | High-Level-Synthesis                                          | 33        |  |  |  |  |  |  |

|----------|---------------------------------------------------------------|--------|---------------------------------------------------------------|-----------|--|--|--|--|--|--|

|          |                                                               | 2.6.3  | Overview of Hardware Accelerator Designs for Highly-demand    | ing       |  |  |  |  |  |  |

|          |                                                               |        | Applications                                                  | 37        |  |  |  |  |  |  |

|          | 2.7                                                           | Concl  | usions                                                        | 40        |  |  |  |  |  |  |

| 3        | Quality-driven Model-based Multi-processor Accelerator Design |        |                                                               |           |  |  |  |  |  |  |

|          | Met                                                           | thodol |                                                               | <b>43</b> |  |  |  |  |  |  |

|          | 3.1                                                           |        | ty-driven Model-based Multi-processor Accelerator Design Meth |           |  |  |  |  |  |  |

|          |                                                               |        |                                                               | 44        |  |  |  |  |  |  |

|          | 3.2                                                           |        | sion to (Re-)configurable Multi-processor Accelerator Design  | 52        |  |  |  |  |  |  |

|          | 3.3                                                           |        | -objective, Multi-dimensional Design Space Exploration        | 55        |  |  |  |  |  |  |

|          | 3.4                                                           |        | tecture Design Space Exploration and Synthesis Algorithm .    | 59        |  |  |  |  |  |  |

|          | 3.5                                                           |        | ntages of the Proposed Design Method                          | 73        |  |  |  |  |  |  |

|          | 3.6                                                           |        | n Decision Space and Search Complexity                        | 74        |  |  |  |  |  |  |

|          | 3.7                                                           |        | Study: Hardware Multi-processor LDPC Decoder Design $\ . \ .$ | 77        |  |  |  |  |  |  |

|          | 3.8                                                           | Concl  | usions                                                        | 78        |  |  |  |  |  |  |

| 4        | Implementation of the Design Methodology for its Application  |        |                                                               |           |  |  |  |  |  |  |

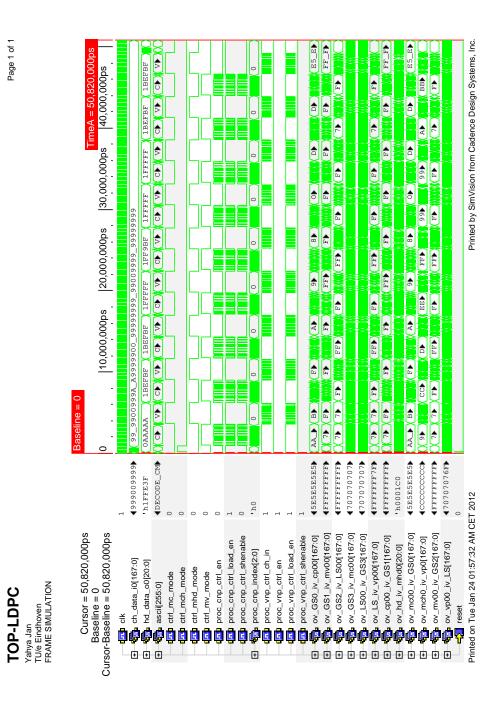

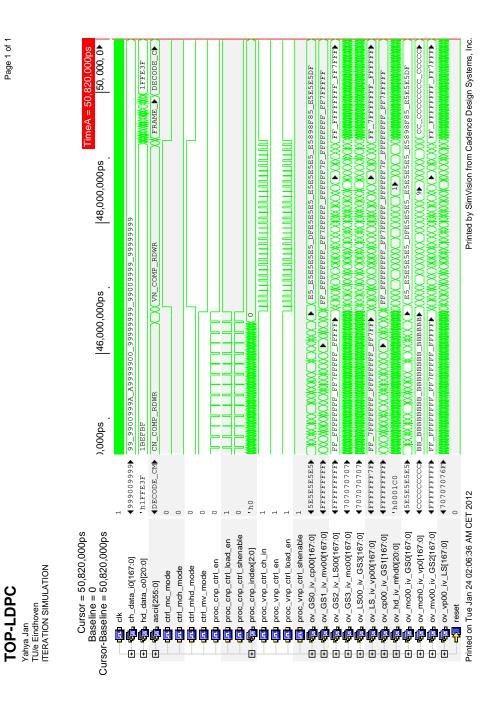

|          | to I                                                          |        | Decoding                                                      | <b>79</b> |  |  |  |  |  |  |

|          | 4.1                                                           |        | Decoder Design Considerations                                 | 80        |  |  |  |  |  |  |

|          | 4.2                                                           |        | Decoding Algorithms                                           | 81        |  |  |  |  |  |  |

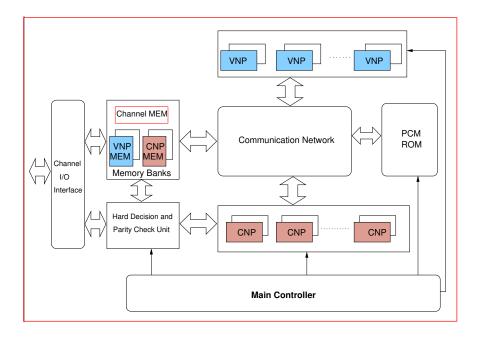

|          | 4.3                                                           |        | Decoder Architecture Template and Template Features           | 84        |  |  |  |  |  |  |

|          | 4.4                                                           | Desig  | n of Generic Component Library                                | 87        |  |  |  |  |  |  |

|          |                                                               | 4.4.1  | Processing Elements Design and Characterization               | 88        |  |  |  |  |  |  |

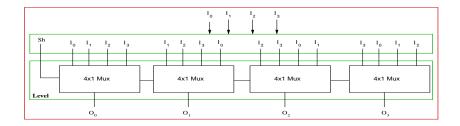

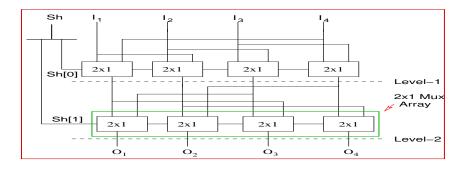

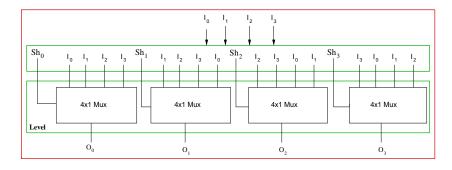

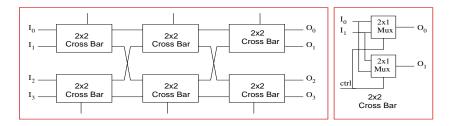

|          |                                                               | 4.4.2  |                                                               | 107       |  |  |  |  |  |  |

|          |                                                               | 4.4.3  | Communication Elements Design and Characterization            | 108       |  |  |  |  |  |  |

|          |                                                               | 4.4.4  | Sequencer/Controller Design for LDPC decoder                  | 110       |  |  |  |  |  |  |

|          | 4.5                                                           |        | cation of the Design Space Exploration and Synthesis Ap-      |           |  |  |  |  |  |  |

|          |                                                               |        |                                                               | 115       |  |  |  |  |  |  |

|          | 4.6                                                           |        | 1 1 1 0                                                       | 123       |  |  |  |  |  |  |

|          | 4.7                                                           |        |                                                               | 124       |  |  |  |  |  |  |

|          | 4.8                                                           | Concl  | usions                                                        | 125       |  |  |  |  |  |  |

| <b>5</b> | Mic                                                           | ,      | I I I I I I I I I I I I I I I I I I I                         | 127       |  |  |  |  |  |  |

|          | 5.1                                                           |        | 1                                                             | 129       |  |  |  |  |  |  |

|          | 5.2                                                           |        | i i                                                           | 131       |  |  |  |  |  |  |

|          | 5.3                                                           |        | ,                                                             | 132       |  |  |  |  |  |  |

|          |                                                               | 5.3.1  | · ·                                                           | 134       |  |  |  |  |  |  |

|          |                                                               | 5.3.2  | Fixed Macro-parallelism and Various Micro-parallelism         | 141       |  |  |  |  |  |  |

|          |                                                               | 5.3.3  | 0                                                             | 145       |  |  |  |  |  |  |

|          | 5.4                                                           |        | 0                                                             | 148       |  |  |  |  |  |  |

|          | 5.5                                                           | -      | tion Scheduling Influence on Performance and Communica-       |           |  |  |  |  |  |  |

|          | <b>.</b> -                                                    |        | nd Memory                                                     |           |  |  |  |  |  |  |

|          | 5.6                                                           | Concl  | usions                                                        | 154       |  |  |  |  |  |  |

viii

| 6  | Communication and Memory Architecture Exploration |                                                                 |      |  |  |

|----|---------------------------------------------------|-----------------------------------------------------------------|------|--|--|

|    | 6.1                                               | Issues of Communication and Memory Architecture Design for Mas- |      |  |  |

|    |                                                   | sively Parallel Hardware Multi-processors                       | 158  |  |  |

|    | 6.2                                               | Communication and Memory Architecture Design for High-end       |      |  |  |

|    |                                                   | Multi-processors                                                | 164  |  |  |

|    | 6.3                                               | Case Study: Communication and Memory Architectures of LDPC      |      |  |  |

|    |                                                   | Decoders                                                        | 168  |  |  |

|    |                                                   | 6.3.1 Data Distribution Based Communication Partitioning        | 177  |  |  |

|    |                                                   | 6.3.2 Data Identification Based Communication Partitioning      | 178  |  |  |

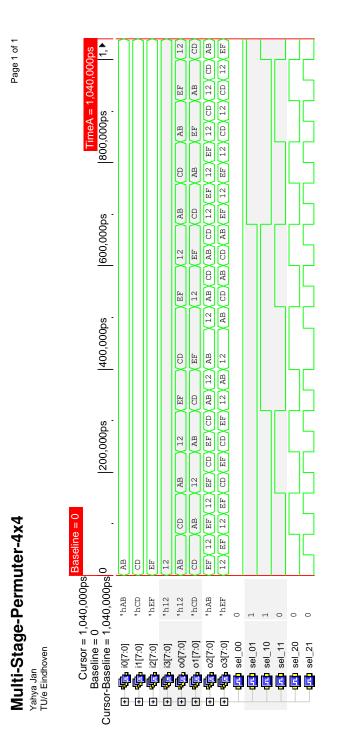

|    |                                                   | 6.3.3 Single-stage versus Multi-stage Switches for Communica-   |      |  |  |

|    |                                                   | tion Network                                                    | 181  |  |  |

|    |                                                   | 6.3.4 Experimental Results Discussion                           | 183  |  |  |

|    | 6.4                                               | Comparison of LDPC Decoder Architectures from Related Re-       |      |  |  |

|    |                                                   | search and our Method                                           | 186  |  |  |

|    | 6.5                                               | Conclusions                                                     | 190  |  |  |

| 7  | Cor                                               | clusions and Future Work                                        | 193  |  |  |

|    | 7.1                                               | Conclusions                                                     | 193  |  |  |

|    | 7.2                                               | Future Work                                                     | 198  |  |  |

| A  | ppen                                              | dix-A                                                           | 201  |  |  |

| A  | Appendix-B                                        |                                                                 |      |  |  |

| Bi | Bibliography                                      |                                                                 |      |  |  |

|    |                                                   |                                                                 | 0.51 |  |  |

| G  | lossa                                             | ry                                                              | 251  |  |  |

| Cı | Curriculum Vitae                                  |                                                                 |      |  |  |

| Li | List of Publications                              |                                                                 |      |  |  |

х

# CHAPTER 1

# Introduction

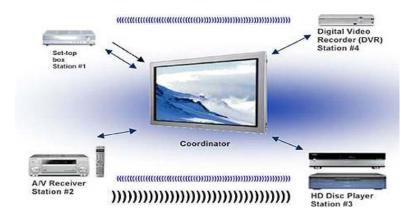

During the last decade, a big progress and remarkable innovations have been made in various embedded system fields, like telecommunications, multimedia, consumer electronics, medical instrumentation, avionics, navigation and transportation, etc. Many new modern ways of information processing, communication and presentation have emerged. For example, the communications systems and standards that were originally developed for voice services have evolved to support extensive video, data and multi-media services with a high availability, reliability, speed and quality-of-service (QoS), as shown in Figure 1.1. Similarly, in the entertainment domain, the video processing/broadcasting systems of the past have been replaced by the current High-Definition (HD) systems and are in a transition-phase to the ultra-high-definition systems (UHDTV) with a rich set of new and innovative services such as video-on-demand (VoD) and youtube, etc, for example. The future wireless video local area network (WVLAN) can also serve as a very good example of such an advanced application with a mix of substantial innovation in video and communication, as shown in Figure 1.2. In the WVLAN all the video sources such as HD disc player, set-top boxes, audio/video (A/V) receiver, etc, communicate with the coordinator (digital display system). This communication involves exchange of huge video contents at extremely high speed among the different video sources and the display system. Also, the different video sources such as HD disc player, set-top boxes, etc, require to process (encoding/decoding) huge amounts of video data at extremely high speeds. All these innovations were possible due to the tremendous advancements in the nanoelectronic and information technologies during the last decade. However, what

still needs improvements are the adequate design methods and electronic design automation (EDA) tools to effectively and efficiently design such kinds of complex and highly-demanding systems. This thesis addresses this need.

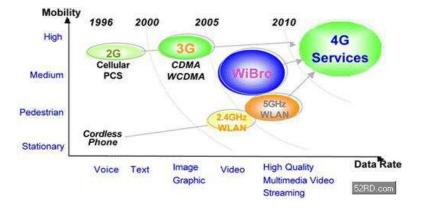

Figure 1.1: Example of innovation in communications systems

Figure 1.2: Example of wireless video LAN (WVLAN) for HD video applications (image: https://www.wirelesshd.org/)

The rest of this chapter is organized as follows. Section 1.1 discusses the highly-demanding applications. Section 1.2 briefly discusses the design, automation and implementation challenges in the design of hardware accelerators for the highly-demanding modern applications as those briefly considered above. Section 1.3 introduces the aim of the research reported in this thesis and lists the key contributions of this research. Section 1.4 presents the overall thesis organization.

#### 1.1 Modern Highly-demanding Applications

The recent spectacular progress in nano-electronic technology has enabled the implementation of very complex multi-processor systems on single chips (MP-SoCs) for high-performance (embedded) applications. On the other hand, however, new highly-demanding complex embedded applications are emerging, in fields like communication and networking, multimedia, medical instrumentation, monitoring and control, military, etc., which impose stringent and continuously increasing functional and parametric demands. The high demands of these applications cannot be satisfied by systems implemented on general purpose processors (GPP). For these highly-demanding applications increasingly complex and highly optimized application-specific MPSoCs are required. They have to perform realtime computations to extremely tight schedules, when satisfying high demands regarding the energy, area, cost and development efficiency, and often to be highly flexible to support different product versions, quickly changing standards, adaptability to changing operation conditions, design reuse and computational sharing, development and fabrication effort re-use, etc. High-quality MPSoCs for these highly-demanding applications can only be constructed through adequate usage of efficient application-specific system architectures and circuit implementations exploiting adequate concepts of computation, storage and communication, as well as, usage of efficient design methods and electronic design automation (EDA) tools for synthesizing the actual high-quality hardware platforms implementing the architectures, and for efficient mapping of applications onto the hardware platforms [1].

Some of the representative examples of these highly-demanding applications include the based-band processing in wired/wireless communication (e.g. the upcoming 4G wireless systems), different kinds of encoding/decoding in communication, image processing and multimedia, 3D graphics, ultra-high-definition television (UHDTV), and encryption applications, etc. These applications require to perform complex computations with a very high throughput, while at the same time demanding low energy and low cost. Moreover, they often require design-time and/or run-time (re-)configurability to support the new evolving and competing standards, and different data transmission rates. The decoders of the low density parity check (LDPC) codes [2], adopted as an advance errorcorrecting scheme in the newest wired/wireless communication standards, like IEEE 802.11n, 802.16e/m, 802.15.3c, 802.3an, etc., for applications as digital TV broadcasting, mm-wave WPAN [3], etc., can serve as a representative example of such applications. These standards specify ultra-high throughput figures in the range of Gbps [3]. Such ultra-high performance cannot be achieved using general purpose processors (GPPs), digital signal processors (DSPs) [4] or general purpose graphic processing units (GPGPUs) [5]. For example, an implementation of LDPC decoders on the famous Texas Instruments TMS320C64xx fixed point DSP processor running at 600 MHz delivers a throughput of only 5 Mbps

[4]. Similarly, implementations of LDPC decoders on the multi-core architectures, results in throughputs in the order of  $1\sim 2$  Mbps on the general-purpose x86 multi-cores, and ranging from 40 Mbps on the GPU to nearly 70 Mbps on the CELL Broadband Engine (CELL/B.E) as reported in [5]. For the realization of the throughput as high as several Gbps, while also remaining in the energy budget, massively parallel multi-processor accelerators are indispensable. Even for sub-stantially lower performance levels the programmable processor based solutions are usually inadequate from the viewpoint of energy consumption.

Real-time high-end video processing (encoding/decoding) is another interesting and representative example of such demanding applications. To satisfy the real-time performance demands of many modern multimedia applications, like: video conferencing, video telephony, camcoders, surveillance, medical imaging, and especially HDTV and new emerging UHDTV in video broadcasting domain, ultra-high performance computational platforms are required. The problem is amplified by the quickly growing requirements of higher and higher quality, especially in the video broadcast domain, what results in a huge amount of data processing for the new standards of digital TV, like UHDTV that requires a resolution of  $(7680x4320) \sim 33$ Megapixel with a data rate of 24 Gbps [6]. Additionally, the latest standards video coding algorithms are much more complex due to the digital multimedia convergence and specifically access of multimedia through a variety of networks and different coding formats used by a single device, as well as, the slow vanishing of the old video coding standards (e.g. MPEG-2) and widespread adaptation of the new standards (e.g. H.264/AVC, VC1 etc). Often, the computational platforms for multimedia are also required to be (re-)configurable, to enable their adaptation to various domains, accessing networks, standards and work modes. Application-specific multi-processors are required to constitute the kernels of such (re-)configurable high-performance platforms. The Context-based Adaptive Binary Arithmetic Coding (CABAC), entropy encoder/decoder of H.264/AVC encoder/decoder can serve here as a one more example. Its purely software-based implementation on a general purpose computing engine results in an unsatisfactory performance even for a quite low quality and resolution (e.g. 30-40 cycles are required on average for a single bin decoding on DSP [7]). The situation is much worse for the High Definition (HD) video as the maximum bin rate requirement of HD (level 3.1 to 4.2) in H.264/AVC, averaged across a coded picture, ranges from 121 Mbins/s to 1.12 Gbins/s [8]. This makes the software solution inadequate to achieve the real-time performance for HD video as a multi-giga hertz general purpose processor would be required for HD encoding in real-time [9]. Moreover, the serial nature of CABAC paralyzes the other processes in video codec that could otherwise be performed in parallel, making CABAC a bottleneck in the overall codec performance. Consequently, to achieve the required performance, flexibility, low cost and low energy consumption, a sophisticated (re-)configurable hardware accelerator for CABAC is necessary.

Above, several examples are given of the high-end applications and their highperformance demands, as well as, the performances achieved for them on the state-of-the-art programmable processors. There are many more such applications in various fields that require hardware acceleration to satisfy their high real-time performance demands. The orientation scores (OS) based image analvsis in medical imaging field is another example of such demanding applications [10]. They involve massively parallel complex image orientation (filtering) and enhancement kernels for image analysis. The filters are the well-known convolution filters that extract some image features utilizing the neighboring pixel information. The unique feature of the filtering operation is the large filter kernel sizes involved in the computation of a single pixel. To adequately satisfy their performance demands, parallelism have to be exploited on a massive scale. For instance, the convolution filter (kernel size of  $15 \times 15$ ) of the orientation scores algorithm requires to process pixels at a rate of 125 MPixel/s with 8-bits/Pixel results in the throughput of 1 Gbps. The convolution filter requires 225 multiplications and 224 additions per clock cycles to compute a single pixel of a single orientation for a kernel of size  $15 \times 15$ . The total number of orientations to investigate is from 12 to 32 and the kernel sizes in the range from 9 to 41. This requires a huge amount of computational resources to compute all the orientations in real-time. Other similar kind of operations are the various kinds of transforms such as fast fourier transform (FFT), discrete cosine transform (DCT), inverse discrete cosine transform (IDCT) and operations on matrix (multiplication, addition), etc, that are used extensively in various application fields, such as DCT/IDCT in H.264/AVC video encoder/decoder. Depending on the application, these operations are implemented with adequate parallelism in hardware at different performance points. Yet another application area where hardware accelerator is often required is the area of encryption applications.

The highly-demanding applications, as those briefly discussed above, may have different computation characteristics and requirements. The next section discusses the features, implementation challenges, and the kind of design approach needed to effectively and efficiently design high-performance hardware accelerators for such applications.

# 1.2 Main Challenges of Accelerators Design for Highlydemanding Applications

In the previous section, several application classes are discussed that require hardware acceleration, because their processing speed requirements are beyond the capabilities of today's programmable processors. In this section, the accelerator design and implementation challenges for the highly-demanding applications are briefly analyzed. As outlined in the previous section, the high physical and economic demands of many modern applications result in many different design issues and challenges that have to be adequately addressed during the accelerator design process. Although all these applications require hardware acceleration to perform their computations with the required speed, they can be quite different regarding the character of computation and communication involved, and some other features.

For example, consider the transform and filtering based applications. All these applications have in common that they mainly involve functional parallelism and a simple local or regular communication. They either do not require (global) memory accesses, because they directly process the incoming stream of data, or they require relatively simple and regular, limited in space and time local memory accesses between which relatively large portions of computations are performed. The design of hardware accelerators for such kind of applications that do not involve complex communication or complex irregular memory accesses is usually limited to the micro-architecture RTL-level exploration and synthesis, and is reasonably supported by the existing methods of "application analysis and parallelization" (APP) and "high-level-synthesis" (HLS) [11–19], and the new emerging commercial HLS tools [20–26]. The HLS tools are often able to automatically produce a reasonable RTL-level representation of the required hardware from a high-levellanguage (HLL) design description, such as C/C++, SystemC, MATLAB, etc. The micro-architecture of such a processing unit is composed of interconnected register-transfer-level (RTL) data-path resources (such as, adders, multipliers, registers and multiplexers, etc) and a controller.

The limitation of HLS to only the micro-architecture exploration and synthesis of a single processing unit, as well as, some other limitations cause that it alone is inadequate for the design of high-performance complex multi-processor hardware accelerators for many modern applications, specifically applications involving complex relationships between the data and computing operations, as considered in this thesis (see Chapter 2 for details). The salient computation, storage and communication character of these applications in addition to the ultra-high performance, lead to many new challenges that have to be addressed, when designing hardware accelerators for these applications. The application features and related design challenges are briefly discussed below.

Many modern applications involve massive parallelism of various kinds, such as task, data and functional parallelism, as well as, complex interrelationships among the data and computing operations at the task level and complex inter-task data dependencies. To satisfy the ultra-high performance of these applications, parallelism has to be exploited on a massive scale. Therefore, to adequately serve these applications, the accelerator design for such applications require a careful exploration and exploitation of various kinds of parallelism and the resolution of complex interrelationships between the data and computing operations. In particular, the accelerator design for such kind of applications has to account for both the micro- and macro-architecture design for processors, and for the corresponding adequate memory and communication architectures design. Moreover, the processor's micro- and macro-architecture and the memory and communication architectures are strongly interrelated and cannot be designed in separation. Complex mutual tradeoffs have to be resolved among the processor parallelism at the two levels, i.e. between the micro- and macro-architecture, and the corresponding memory and communication architectures, as well as, among the performance, power consumption and area. However, the existing HLS methods [11–19] and tools [20–26] as discussed earlier are limited in their scope to the synthesis of a single processing unit. They do not support the total complex design process of such high-end multi-processor accelerators that involves the combined exploration and synthesis of the adequate micro-/macro-architectures for processors, and the corresponding memory and communication architectures, as well as an adequate resolution of the mutual tradeoffs among these design aspects. New architecture design methods and supporting EDA tools are necessary to address the above challenges and to adequately support the design process of such high-end multi-processor accelerators.

The second major challenge is related to the bandwidth and scalability of the communication and memory architectures of the massively parallel hardware multi-processors that are necessary for the implementation of highly-demanding applications. For the massively parallel hardware multi-processors, the traditionally used flat communication architectures and multi-port memories do not scale well, and the memory and communication network influence on both the throughput and circuit area dominates the processors influence. The additional performance gains expected from an increased parallelism will end up in diminished returns, while exploding the communication or memory complexity. Although some research works related to the memory and communication architectures can be found in the literature [27–33] in the context of programmable on-chip multiprocessor systems, the memory and communication architectures were proposed there for the much larger and much slower programmable processors (see Chapter 6 for details). They are not adequate for the small and ultra-fast hardware processors of the massively parallel multi-processor accelerators, due to a much too low bandwidth and scalability issues. These issues being of crucial importance for the massively parallel multi-processor accelerators are not adequately addressed by the state-of-the-art research [27-33] on the memory and communications architectures.

Moreover, similar applications can target different market segments imposing different requirements. For instance, let us consider the video decoding application. The same kind of video decoding can be used in a low power and area mobile device or a laptop, or a high-definition television (HDTV) from low through moderate to extremely high performance levels. Therefore, to quickly arrive at an adequate design quality, for a particular application with all its particular constraints, objectives and tradeoff profiles, an adequate multi-objective architecture design space exploration (DSE) is indispensable taking into account the various design objectives, constraints and tradeoffs. This is not supported by the current accelerator design methods [11–19] and tools [20–26], as they usually accept a few constraints, like only the clock speed constraint.

When this research was started, no adequate design methodology was in place for such kind of accelerators for the highly-demanding applications. Lack of an adequate design methodology resulted in a large number of ad-hoc proposed solutions in the form of various particular ad-hoc point architectures for various problem instances with different throughput requirements. For instance, despite a more than a decade of research on the hardware accelerators for the LDPC decoding, only some partial proposals from a fragmented research on the processor, memory or communication part of the total accelerator design are available or ad-hoc implementations<sup>1</sup> for specific requirements.

The research work reported in this thesis provides solutions to the discussed above serious issues in the design of hardware multi-processor accelerators for highly-demanding applications. In the next section, the main aim of the research reported in this thesis is presented and the summary of its contributions.

#### **1.3** The Aim and Key Contributions of this Thesis

The general aim of the research reported in this thesis was to analyze the issues and requirements of hardware accelerator design for modern highly-demanding applications, as well as, to propose, implement, analyze and evaluate an adequate semi-automatic design method addressing the issues and satisfying the requirements.

In the previous section, some of the main hardware accelerators design challenges for highly-demanding applications are briefly discussed. Here, the key contributions of the research reported in this thesis are listed. Addressing these design challenges requires contributions in both the design methods and EDA tools, as well as the architecture design. Additionally, some contributions are made towards a better understanding of design problems for highly-demanding applications. In the following, some of the major contributions are discussed in each sub-category.

#### 1.3.1 Design Methods and EDA Tools

The contributions to this area are in the form of a new architecture design method and tool to address the design challenges of the accelerator design for highlydemanding applications that are not addressed by the previous research efforts. The contributions are as follows:

- analysis of several different highly-demanding modern applications and the design issues related to these applications; specifically, of the issues that can not be resolved using the traditional methods for design of hardware accelerator architectures

- formulation of requirements for an adequate hardware accelerator design method for the highly-demanding applications based on the results of the analysis

$<sup>^1100{\</sup>sim}150$  research articles on LDPC decoder implementation up till now

- proposal of a novel multi-processor design method that adequately addresses the issues and satisfies the requirements, and is based on the quality-driven model-based system design approach proposed by Jóźwiak [1, 34–37]

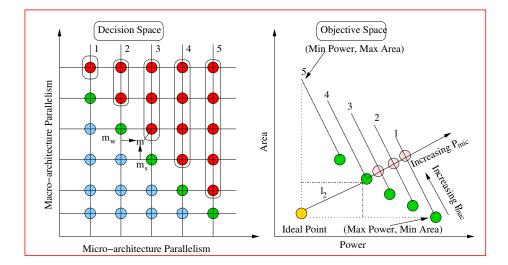

- proposal of a novel multi-objective and multi-dimensional design space exploration (DSE) framework that performs the exploration and exploitation of various tradeoffs between the processing parallelism at the micro- and macro-architecture level, and the corresponding memory and communication architectures, as well as, among the performance, power consumption and area (PPA), to quickly arrive at high-quality accelerator architectures

- two novel operation scheduling techniques, the so-called tight scheduling (TS) and relaxed scheduling (RS), that are proposed to tradeoff the processors cost against the memory and communication structure costs based on whether the processors costs dominates or the memory and communication costs, respectively

- two novel performance and power optimization approaches based on the consideration of the micro-/macro-architecture level parallelism in combination; these approaches are much better than the traditional power and performance optimization methods for multi-processor systems

- application of the proposed multi-processor accelerator design method and implementation of the related DSE framework with all its core activities for the application field of LDPC decoders as a case study to evaluate the proposed design method

- semi-automatic design of numerous different LDPC decoder architectures and exploration of the tradeoffs among the various architectures for the newest communication system standards using the design method, and the related automatic DSE framework

#### 1.3.2 Architecture Design

The second set of main contributions is the architecture scalability problem analysis and design of scalable memory and communication architectures for the massively parallel hardware multi-processor systems. The memory and communication architectures proposed in the past [27–33] for programmable on-chip multiprocessors systems are not adequate for the massively parallel hardware multiprocessor accelerators due to the data transfer bandwidth and scalability issues. Therefore, several novel application-specific memory and communication architectures are proposed in this thesis. The contributions to architecture design are as follows:

• analysis of the communication and memory architecture design and scalability issues for the massively parallel hardware multi-processors

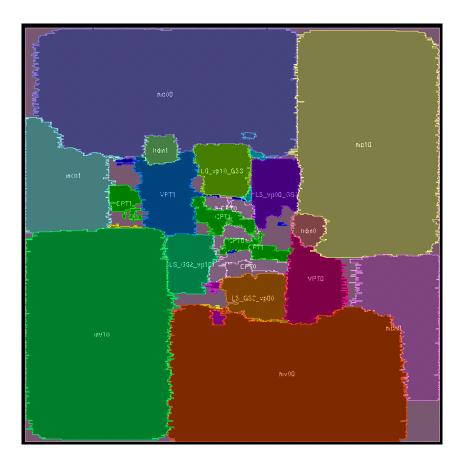

- proposal of several novel generic hierarchical partitioned communication and memory architectures that ensure the scalability when applied to massively parallel hardware multi-processors, as well as, their application method to the memory and communication architecture design of massively parallel LDPC decoders

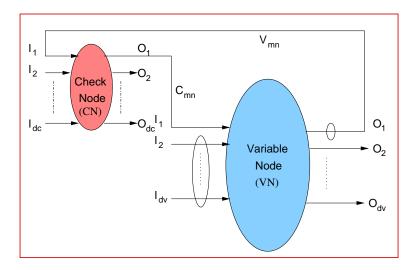

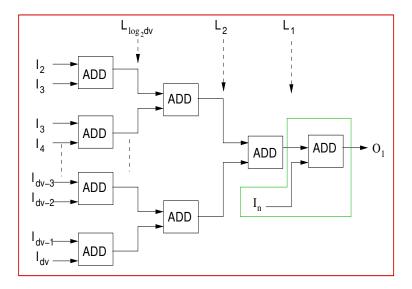

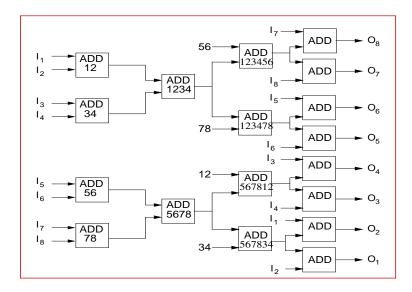

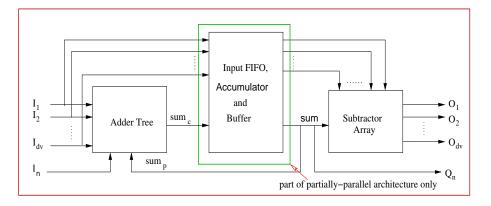

- design and implementation of novel generic check node processor (CNP) and variable node processor (VNP) micro-architectures for the LDPC decoders that span the full range of micro-architectures from the fully-serial, through the partially-parallel, to the fully-parallel

- a novel classification of the multi-processor architectures based on the processing parallelism to evaluate and compare the various architectural solutions

#### **1.3.3 Better Understanding of Architecture Design Problems** for Highly-demanding Applications

Using the proposed multi-processor accelerator design method and its application for a real-life application of LDPC decoding, a large series of architecture synthesis experiments were performed that not only confirmed adequacy of the design method, but also resulted in several findings of high importance for better understanding of architecture design problems for highly-demanding applications. The most important of them are listed below.

- demonstration of the numerous mutual complex tradeoffs between the microand macro-architecture levels and their influence on design parameters like, performance, power consumption and area, etc, to make adequate decisions on the number and type of processors

- demonstration that neither the fully-serial nor the fully-parallel micro-architectures are adequate to satisfy the ultra-high performance or low power requirements, but the partially-parallel architectures have to be explored and exploited

- demonstration that the ultra-high performance and low power requirements can only be satisfied on a reasonable cost through the combined micro-/macro-architecture, as well as, communication and memory architecture exploration

- demonstration that pipelining for performance enhancement is not the best approach in many cases, and may specifically not be suitable for the architectures exploiting massive parallelism at both architecture levels

To our knowledge, despite more than a decade of research on the hardware accelerator design, no similar holistic quality-driven design approach has been proposed. In the design approach proposed in the scope of the research reported in this thesis, all the design components are considered in combination, their combined design forms a single design task, and the mutual interrelationships and tradeoffs among them and their various characteristics are analyzed and adequately resolved. Finally, using this method, it is possible to implement various complex multi-processor hardware accelerators for the highly-demanding applications (e.g. LDPC decoders of practical importance for the newest upcoming wireless communication standards) very effectively and efficiently, and particularly, very quickly. We hope that the original effort that resulted in this new design methodology for massively parallel multi-processor accelerators will act as a stepping stone on the way towards better well-founded design methods and EDA tools for the multi-processor system design.

### 1.4 Thesis Organization

The thesis is organized as follows. Chapter 2 provides a detailed analysis of the issues and challenges in the design of hardware accelerators for highly-demanding applications. Based on the analysis, the requirements are formulated that have to be satisfied by an adequate accelerator design methodology. The main concepts of the proposed design approach are discussed. Moreover, this chapter includes a comprehensive overview of the existing research work performed in the scope of hardware accelerators. Chapter 3 presents a novel quality-driven model-based multi-processor accelerator design methodology. The design flow and core steps of the proposed methodology are explained. Furthermore, a novel multi-objective and multi-dimensional design space exploration framework and its algorithms are discussed in detail. Chapter 4 discusses the implementation of the proposed design methodology for the LDPC decoder applications used for the case studies. Through the case studies, the design methodology and its design space exploration framework are analyzed and evaluated. Chapter 5 discusses the parallelism exploration and exploitation at the micro-/macro-architecture level and the mutual tradeoffs between the micro- and macro-architecture, when using as a representative example the design of LDPC decoders. Some interesting tradeoffs among performance, power consumption and area are highlighted that are the consequences of the joint consideration of the micro-/macro-architecture level parallelism. Chapter 6 discusses the memory and communication issues involved in the design of massively parallel multi-processor accelerators for the high-end applications. Several novel communication and memory architectures are proposed that address the bandwidth and scalability issues of the massively parallel multi-processor accelerators. Finally, Chapter 7 concludes this thesis and gives some directions for future works.

1.4. THESIS ORGANIZATION

# CHAPTER 2

# Problem Analysis, Research Task Formulation and Related Research

This chapter focuses on the analysis of modern demanding applications from various application fields. The applications are analyzed from various perspectives including: the real-time performance requirements, the character of computation and communication involved, and some other features. The existing design methods and EDA tools, which are used to implement hardware accelerators are discussed. The issues that are involved in the architecture design of hardware accelerators for modern highly-demanding applications are discussed in detail. Afterwards, the LDPC decoding application is briefly introduced. It is used as a representative example to further illustrate the issues of these applications. Based on the analysis of the issues, the requirements are formulated that have to be addressed by an adequate accelerator design methodology for highly-demanding applications. The main concepts of our proposed design method are briefly outlined. The precise research task is formulated. The related research discussion provides an insight into the state-of-the-art methods and EDA tools for the design of hardware accelerators. The main limitations and capabilities of these design method and EDA tools are discussed. Finally, the existing hardware accelerator architectures are overviewed for LDPC decoders with a novel classification to get an insight into these architectures.

The rest of this chapter is organized as follows. Section 2.1 discusses the issues of hardware accelerators for highly-demanding applications. Section 2.2 considers the design issues of LDPC decoders. Section 2.3 discusses the requirements that have to be addressed by an adequate accelerator design methodology for highlydemanding applications. The precise research task formulation and the main assumptions are presented in Section 2.4. Section 2.5 discusses the main concept of the proposed design approach. The related research work is discussed in Section 2.6. Finally, Section 2.7 concludes this chapter.

## 2.1 Issues of Hardware Accelerator Design for Highlydemanding Applications

In Chapter 1, the highly-demanding applications are introduced through several examples. A common feature of these applications is their ultra-high performance demands and also a low energy consumption requirement of many of them, especially, those being mobile. However, various highly-demanding applications may have different computational characteristics and specific design requirements. In the following, the features and the issues involved in the design of hardware accelerators for such applications are discussed.

Although hardware accelerator design is not a new problem, it is only partially solved, and there is much room for further extension and/or improvement of the existing methods and tools. One can construct a trivial hardware accelerator through a straightforward compilation of an algorithm described in a hardware description language, like Verilog or VHDL, or in a high-level language like C. C++, SystemC or MATLAB into hardware. However, in most cases the result of such a straightforward compilation will not be satisfactory for critical parts of demanding applications. In embedded computing, hardware acceleration has been intensively researched during the last decade, mainly for signal, video and image processing applications, for efficiently implementing in hardware transforms, filters and similar complex operations [11–19]. All these operations have in common that they mainly involve functional parallelism, and either do not require (global) memory accesses, because they directly process the incoming stream of data, or they require relatively simple and regular, limited in space and time local memory accesses between which relatively large portions of computations are performed. In consequence, the main problems of hardware accelerator design for this kind of applications are not related to memory or communication bottlenecks, but to an effective and efficient processing unit synthesis through an adequate parallelism exploitation of the basic register-transfer-level (RTL) operations needed for the implementation of the required computations, and adequate implementation of these basic operations in hardware. For this kind of applications, the basic concepts of an effective and efficient accelerator design can be summarized as follows [6, 38]:

• parallelism exploitation for execution of a particular computation instance due to availability of multiple application-specific operational resources working in parallel;

- parallelism exploitation for execution of several different computation instances at the same time due to pipelining;

- application-specific optimal synthesis of processing units, with tailored processing and data granularity.

More specifically, these concepts can be oriented towards the data parallelism, functional parallelism or their mixture. For data parallelism exploitation, multiple data instances of the same type are processed simultaneously provided the application allows for this and the corresponding resources are available. In case of functional parallelism, different operations are performed simultaneously on (possibly) different data instances. Also, the speculative execution can be used to exploit more parallelism. To design a high-quality hardware accelerator of this kind, it is necessary to perform a thorough analysis of the application's computation algorithms and exploit specific computational characteristics inherent to these algorithms. Different characteristics discovered and accounted for result in different approaches to the design of hardware accelerators of this kind, and therefore, in the past a number of different basic accelerator micro-architecture types were considered:

- straightforward datapath/controller architecture;

- parallel hardware architecture;

- pipeline hardware architecture;

- parallel-pipeline hardware architecture.

Summing up, for this kind of applications, the main problems of hardware accelerator design are limited to an effective and efficient computation unit design at the RTL-level (i.e. micro-architecture design) and circuit synthesis for the micro-architecture modules. Circuit synthesis can be performed automatically using one of many available EDA-tools. Currently, in many cases the micro-architecture design for this kind accelerators can also reasonably be supported by the methods of "application analysis and parallelization" (APP), "High-Level-Synthesis" (HLS) [11–19] and emerging commercial HLS tools [20–26]. Nevertheless, the RTL-level computation unit design is often not easy, because some of the modern demanding applications require resolution of complex data or control dependencies (e.g. CABAC decoding in the latest multi-domain video coding standard H.264/AVC [6]), what increases difficulty of an adequate pipeline construction. Further details on APP and HLS methods, and the corresponding state-of-the-art research and commercial tools can be found in Section 2.6 on the related research.

Many modern applications (e.g. various communication, multimedia, networking or encryption applications, etc) are of different kind, and involve serious design issues that are beyond the design capabilities of today's design methods and tools for hardware accelerators. These issues will be discussed in detail as follows.

Many modern highly-demanding applications involve sets of heterogeneous data-parallel tasks with complex inter-task data dependencies and complex interrelationships between the data and computing operations at the task level. Often the tasks iteratively operate on each other's data. One task consumes and produces data in one particular order, while another consumes and produces data in a different order. This all results in complex memory accesses and complex communication between the memories and processing elements in the related hardware multi-processor architectures. For applications of this kind, the main design problems are related to an adequate resolution of memory and communication bottlenecks and to decreasing the memory and communication hardware complexity, which has to be achieved through an adequate memory and communication structure design. Additionally, in the high performance multi-processor accelerators, parallelism has to be exploited on a massive scale. However, due to area, energy consumption and cost minimization requirements, partially-parallel architectures have to be usually used, which are more difficult to design than the fully-parallel ones.

Moreover, for this kind of applications, the memory and communication structure design, and micro-architecture design for computing units cannot be performed independently, because they substantially influence each other. For example, exploitation of more data parallelism in a computing unit micro-architecture usually requires getting the data in parallel for processing, i.e. having simultaneous access to memories in which the data reside (this results in e.g. vector, multi-bank or multi-port memories) and simultaneous transmission of the data (this results e.g. in multiple interconnects), or pre-fetching the data in parallel to other computations. This substantially increases the memory and communication hardware. From the above, it should be clear that for applications of this kind complex interrelationships exist between the computing unit design and corresponding memory and communication structure design, and complex tradeoffs have to be resolved between the accelerator effectiveness (e.g. computation speed or throughput) and efficiency (e.g. hardware complexity, power and energy consumption etc.).

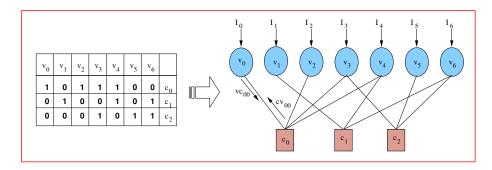

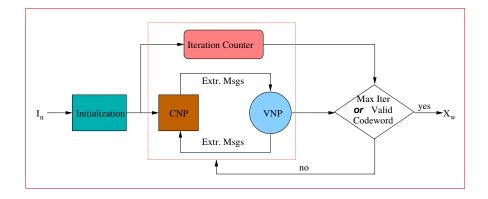

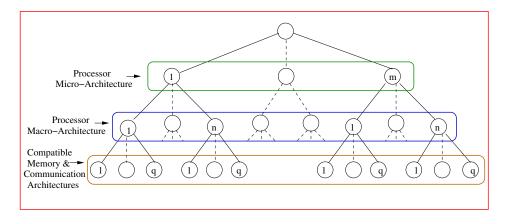

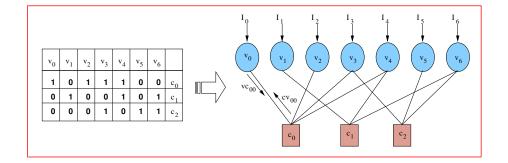

Furthermore, many of the modern demanding applications involve algorithms with massive data parallelism or task-level functional parallelism (e.g. LDPC code decoders of the newest communication system standards like IEEE 802.11n, 802.16e/m, 802.15.3c, 802.3an, etc.). To adequately serve these applications, hardware accelerators with parallel multi-processor macro-architectures have to be considered, involving several identical or different concurrently working hardware processors, each operating on a (partly) different data sub-set. Each of these processors can also be more or less parallel. For this kind of accelerators, the accelerator's parallelism can be realized at two levels:

• macro-architecture level, where elements are elementary processors or accelerators and complex multi-processor or multi-accelerators are build of them, and

• micro-architecture level, where the internal architecture of a single processor or accelerator at the RTL-level can be parallel.

Moreover, there is a tradeoff between the amount of parallelism and resources at each of the two levels (e.g. similar performance can be achieved with less processors each being more parallel and better targeted to particular part of application, as with more processors each being less parallel and less application-specific). The two architecture levels are strongly interrelated and interwoven, also through their relationships with the memory and interconnection structures. In consequence, optimization of the performance/resources tradeoff required by a particular application can only be achieved through a careful construction of an adequate application-specific macro-/micro-architecture combination. The aim here is to find an adequate balance between the number of parallel hardware processors of various kinds, the intra-processor parallelism and complexity, the complexity and effectiveness of memory structures, and the complexity of the inter-processor and/or processor/memory communication, rather than to only optimize the processing units, or separately optimize the micro- or macro-architecture. To achieve this aim several promising micro-/macro-architecture combinations representing complete complex multi-processor accelerator architectures have to be considered, and finally, the best of them has to be selected for an actual realization (see Chapter 3 for details).

Many of the modern highly-demanding applications involve complex algorithms with multi-input multi-output (MIMO) operations and require highly optimized implementation through operation and micro-architecture level parallelism exploitation to satisfy the high-throughput requirements. The micro-architecture level synthesis should exploit among other the operation and data level parallelism, operation chaining, multi-cycle operations, structural and functional pipelining, etc. The traditional hardware design methodologies that incorporate the simple single (two or maximum three) input single output (SISO, MISO) RTL operations are not able to implement the MIMO operations effectively and efficiently. Example of the three input single output operation is the most widely used multiply-accumulate (MAC) operation, required in various applications. Further, these atomic operations when used for the realization of complex MIMO operations result in a large number of computation cycles, what makes it impossible to realize the ultra-high throughput for the high-end applications. Also, the MIMO operations can be implemented using various basic functional units (FUs) having different characteristics (such as fast or slow adders/multipliers, etc.) resulting in various cost/performance tradeoffs. When designing accelerators for highly-demanding applications, the possible micro-architecture tradeoffs have to be carefully considered (see Chapter 5 for details).

Additionally, for the high-end applications that require massively parallel multi-processor accelerators to satisfy the ultra-high throughput, the effective communication and memory architectures, and the compatibility of the processing, memory and communication subsystems play the decisive role. Although some research results related to the memory and communication architectures can be found in the literature [27-33] in the context of programmable on-chip multi-processor systems, the memory and communication architectures were proposed there for the much larger and much slower programmable processors of on-chip multi-processors systems. They are not adequate for the small and ultrafast hardware processors of the massively parallel multi-processor accelerators due to a much too low bandwidth and scalability issues. It will be demonstrated in this thesis that in the massively parallel multi-processor structures for many highlydemanding applications, the communication and memory architectures play a decisive role. The communication architectures can not be designed as a simple flat homogenous networks and the memory as a multi-port memory. Especially, the communication network among the processors or processors and memories has a dominating influence on all the most important design aspects such as delay, area and power consumption. The additional performance gains expected from an increased parallelism will end up in diminished returns, while exploding the interconnect complexity. Therefore, all the architectural, as well as, the data and computation mapping decisions regarding the memories and processors have to be made in the context of the communication architecture design to actually boost the performance. For the massively parallel hardware accelerators, the problem of how to keep up with the increasing processing parallelism, while ensuring the scalability of memory and communication is a very challenging design problem. To our knowledge, it has not been addressed satisfactorily till now (see Chapter 6 for details).

Furthermore, the back-to-back (cyclic) inter-task data dependencies are often so complex that make it extremely difficult or even impossible to overlap the processing of one set of tasks with another set of dependent tasks. The traditional schedulers<sup>1</sup> are not adequate for resolving the kinds of complex scheduling problems involving back-to-back data dependencies among the tasks with one task responsible for producing partial data not only for a single, but for many dependent tasks. This partial fulfillment of data paralyzes the data dependent processors to start their execution earlier until all the data is available, what results in a lower utilization of the processing resources. Even in the case, when an overlap schedule is found (what would result in reduction of a number of processors for a certain performance level), the influence of the scheduling decisions on the cost of memory and communication structures has to be taken into account. It is very probable for this kind of applications that the cost of memory and communication structures may surpass the cost savings due to the decreased processing resources. Therefore, the task scheduling freedom need to be carefully tradeoff against the memory and communication structures complexity, thereby reducing the overall cost to a larger degree and thus providing the opportunity to utilize even more processors (see chapters 3 and 5 for details).

Also, for various modern demanding applications the design objectives and

<sup>&</sup>lt;sup>1</sup>Described in related work section of this chapter

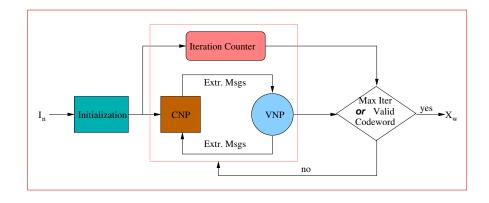

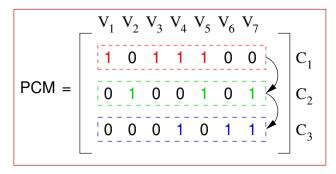

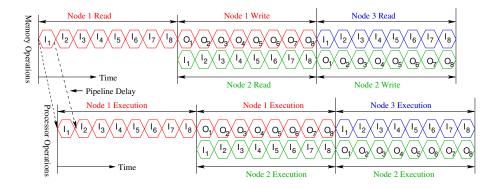

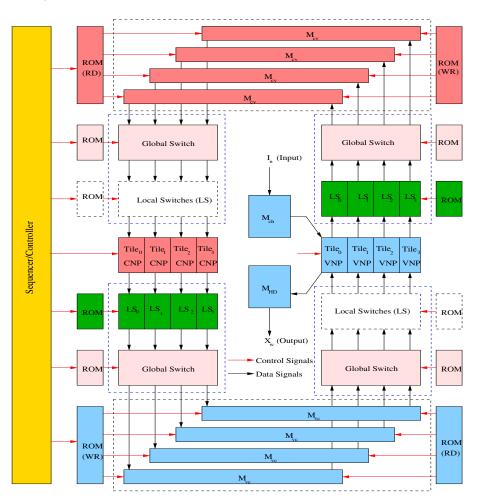

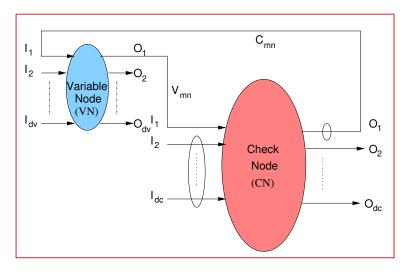

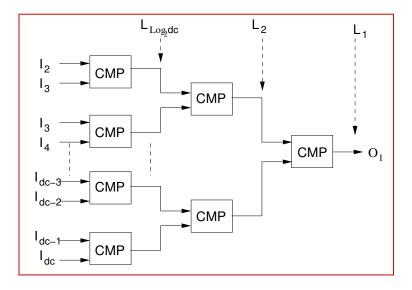

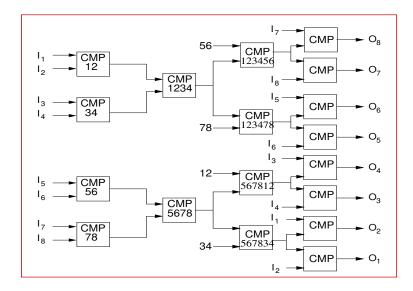

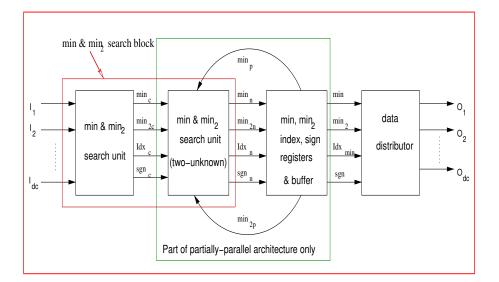

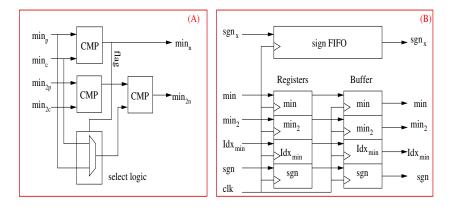

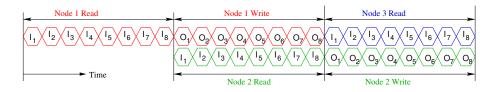

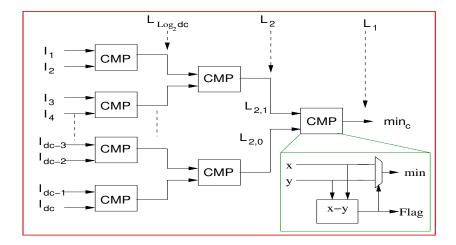

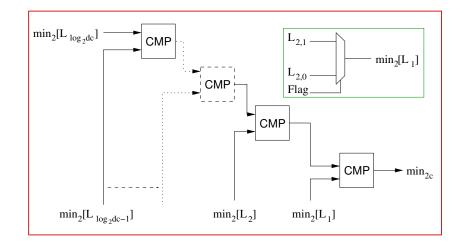

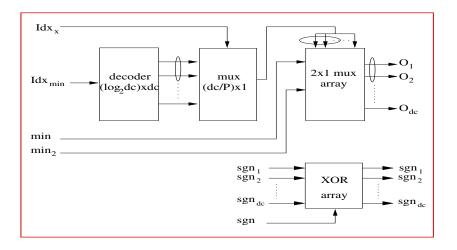

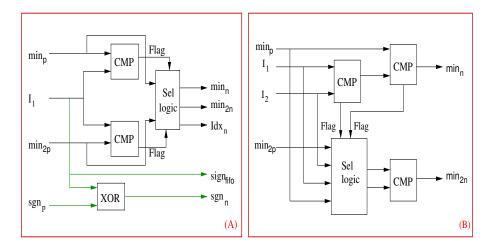

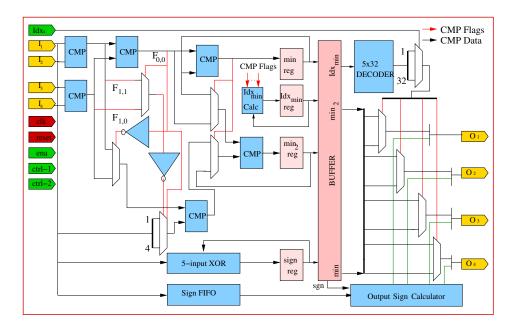

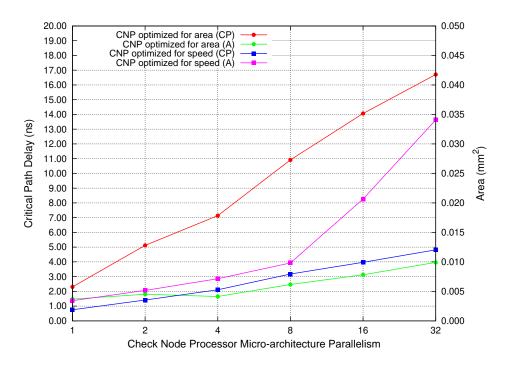

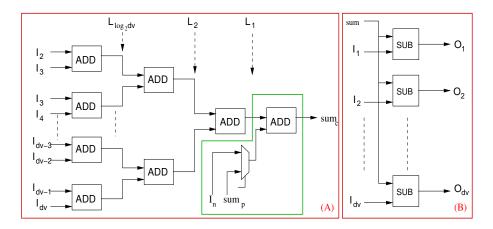

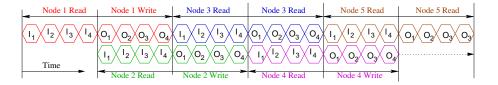

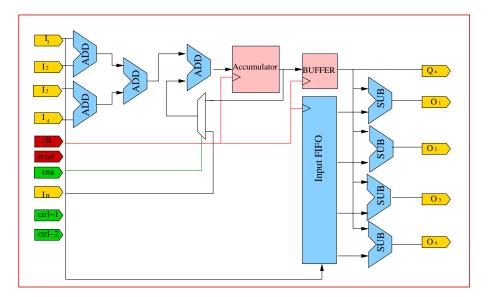

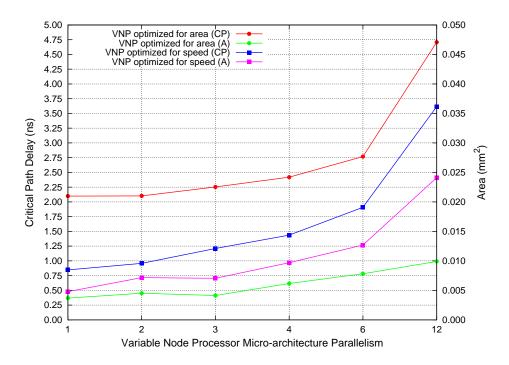

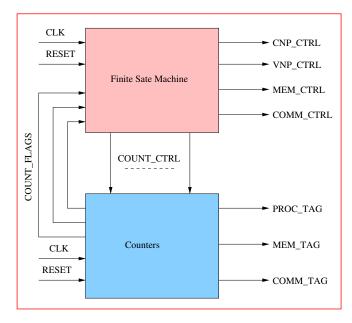

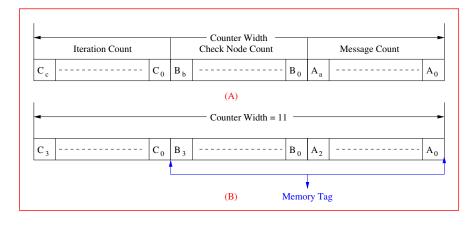

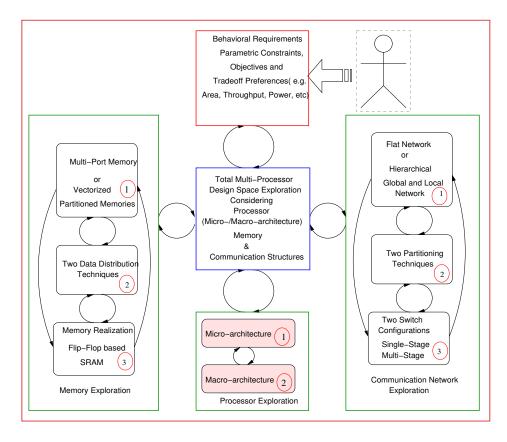

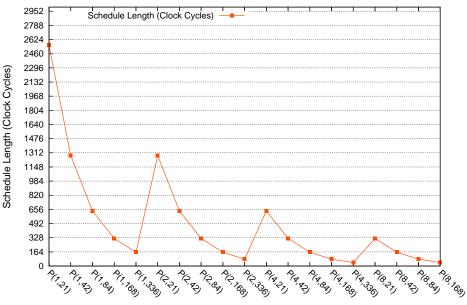

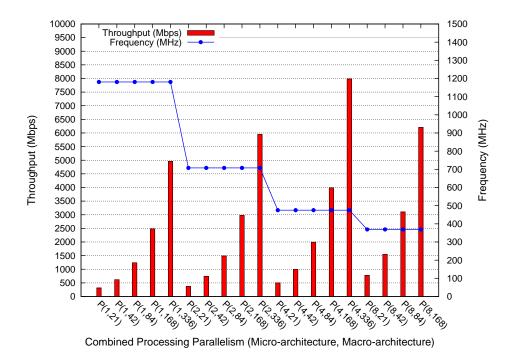

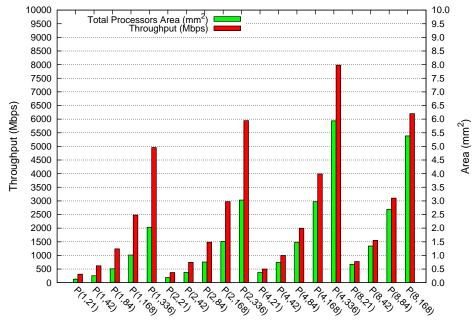

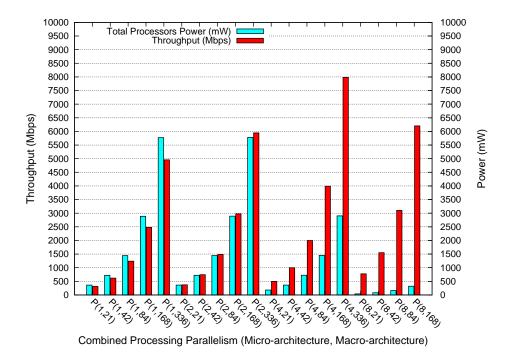

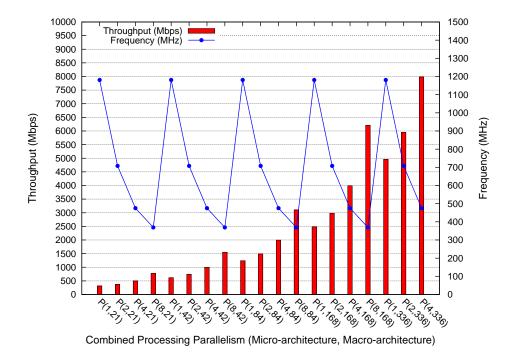

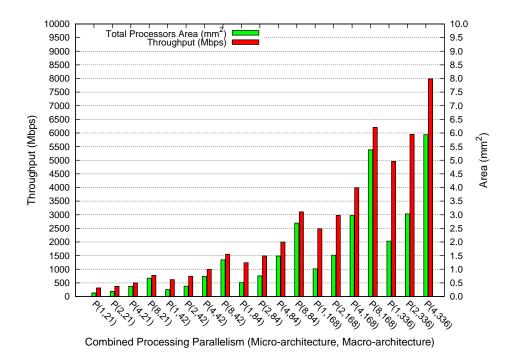

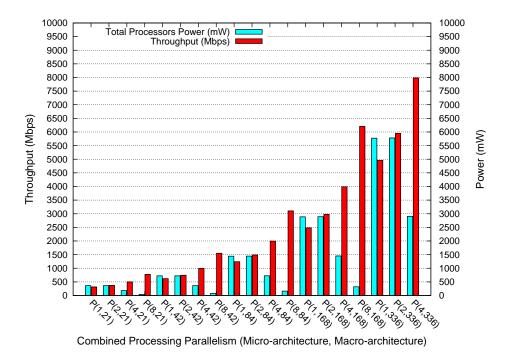

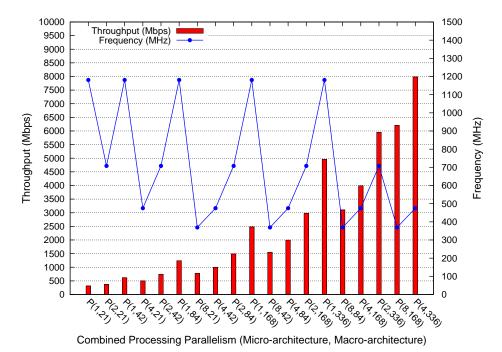

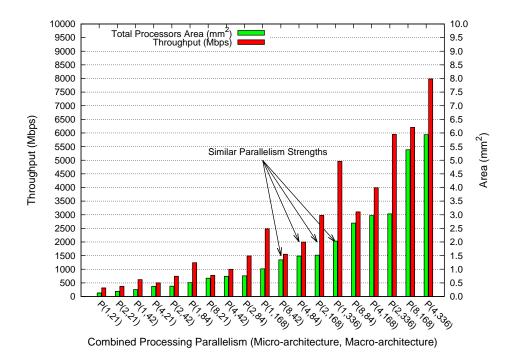

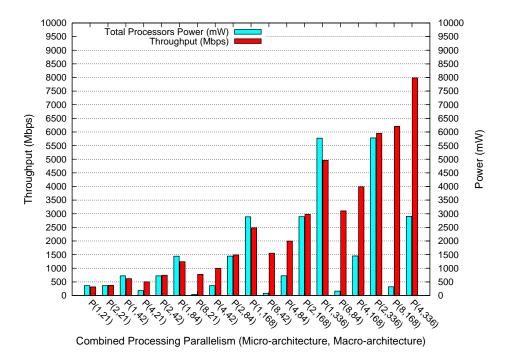

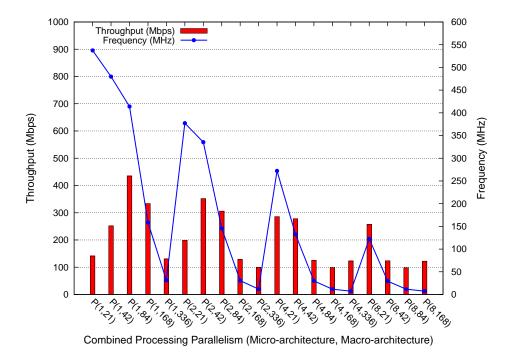

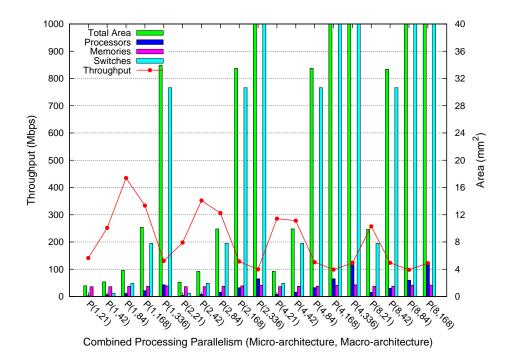

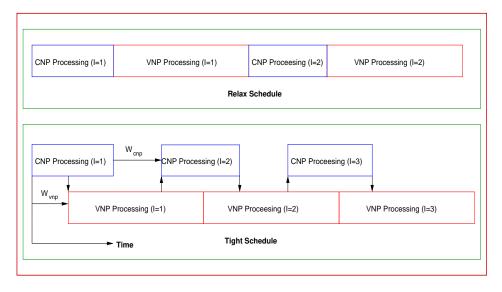

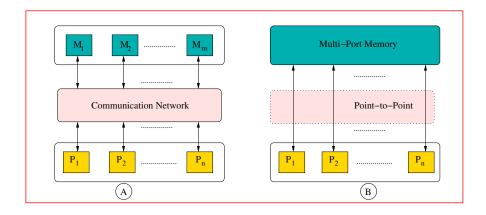

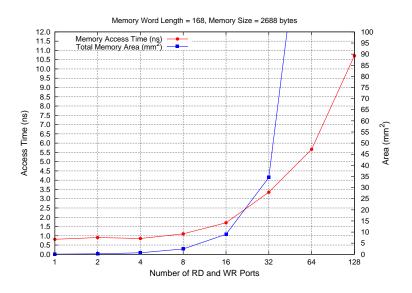

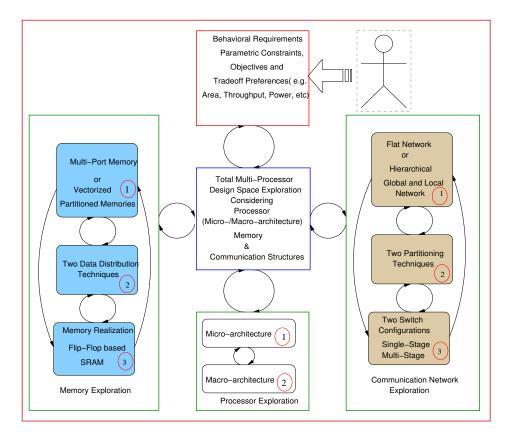

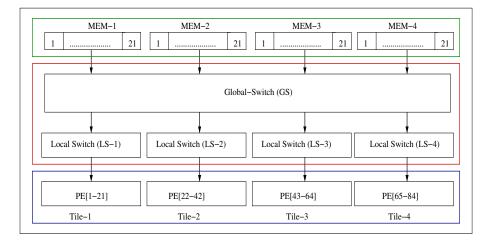

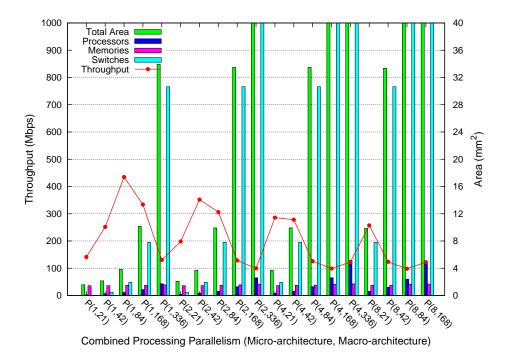

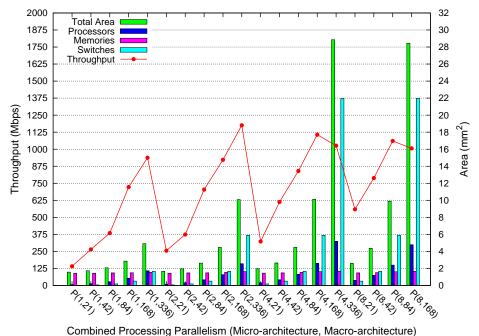

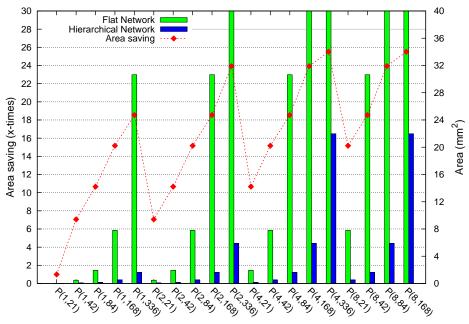

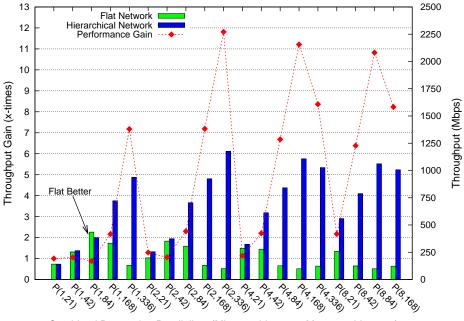

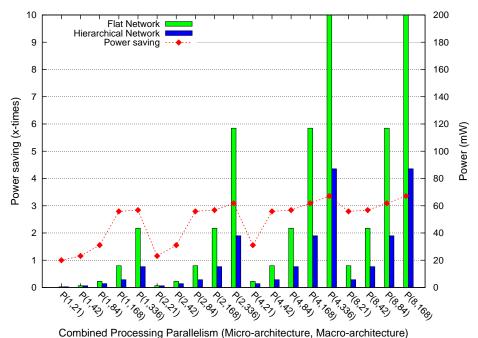

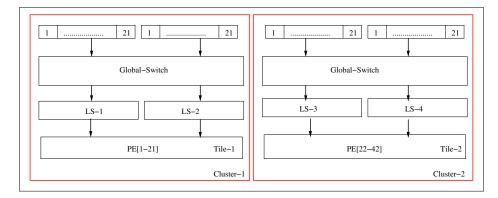

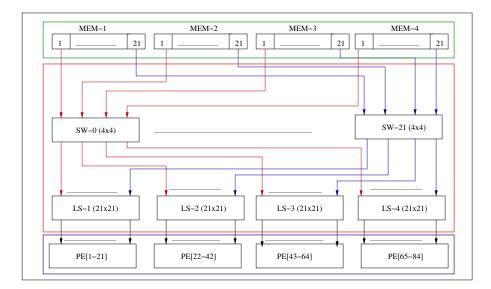

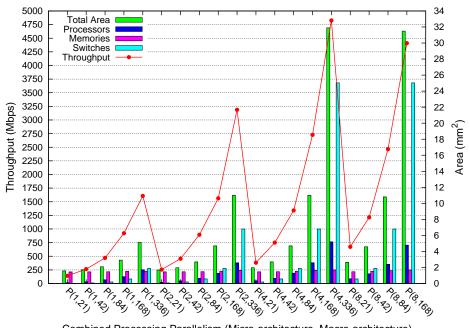

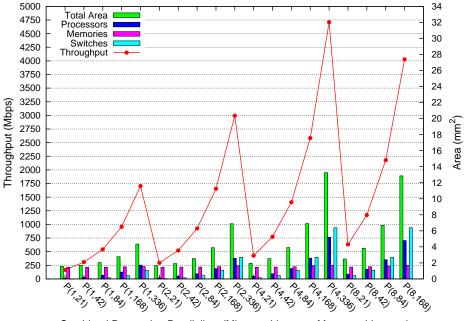

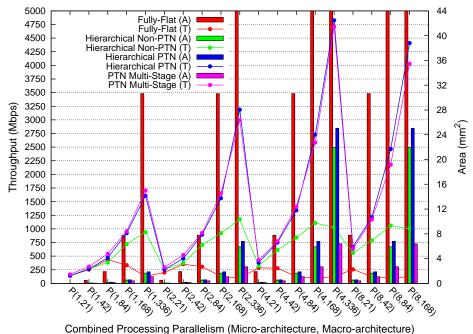

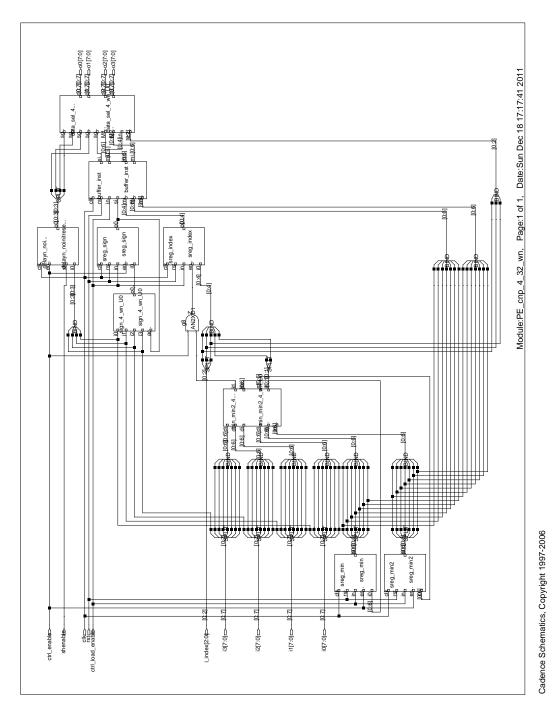

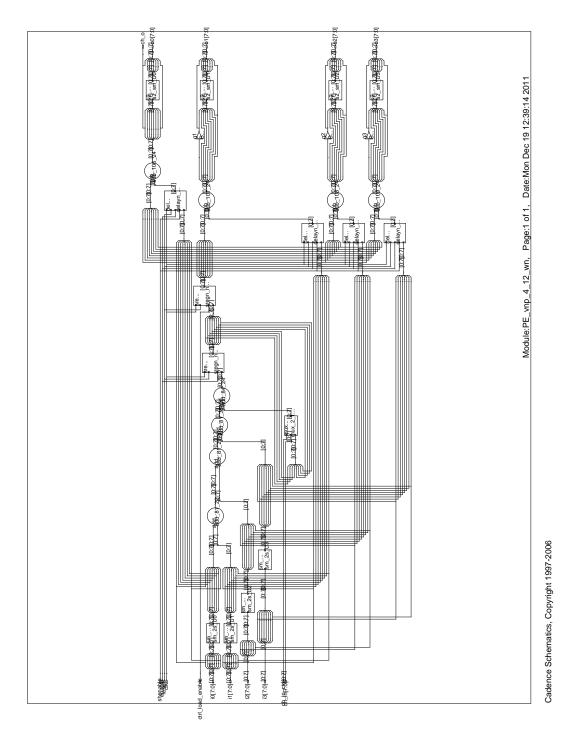

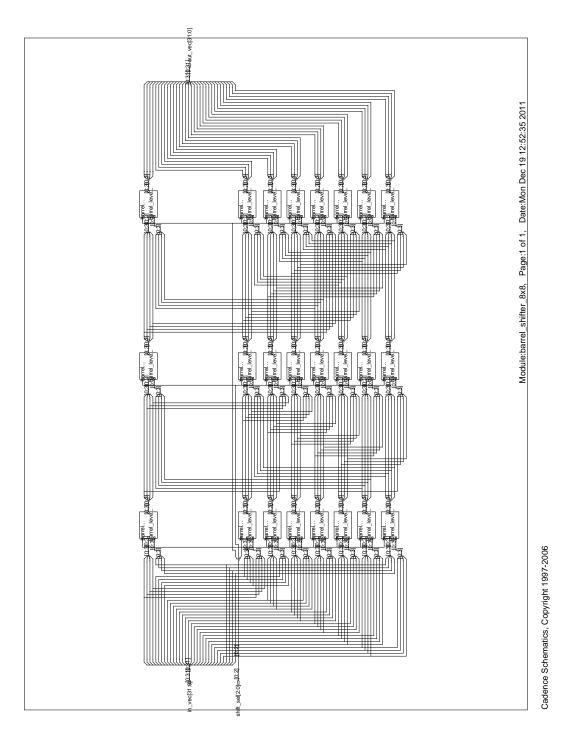

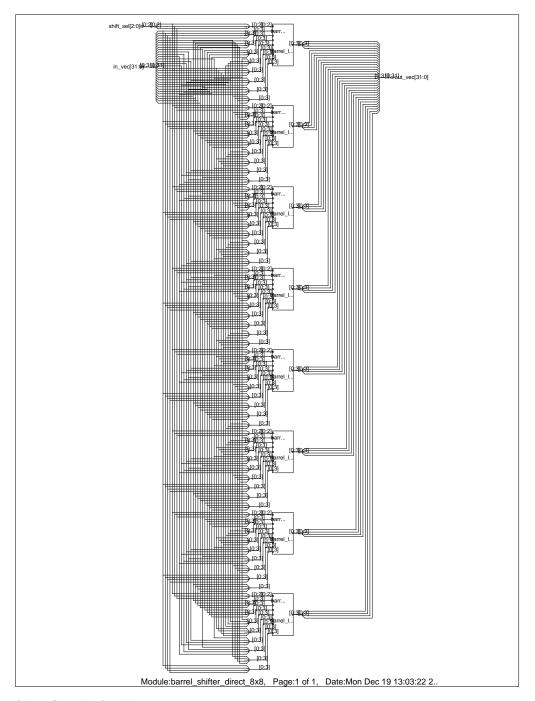

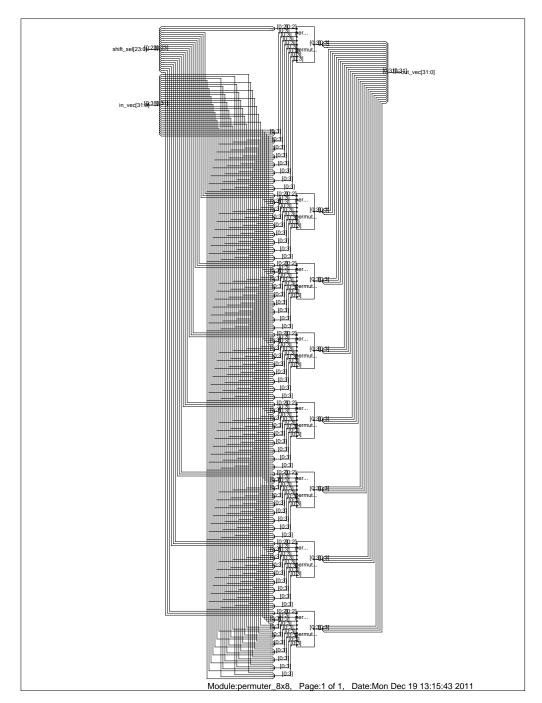

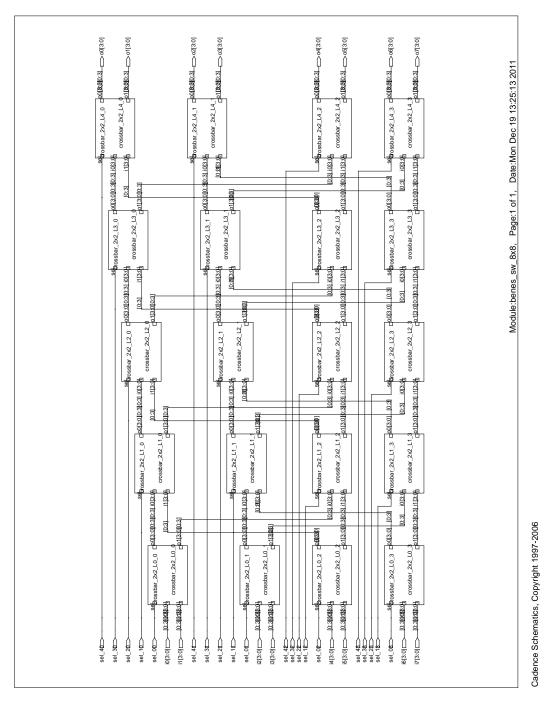

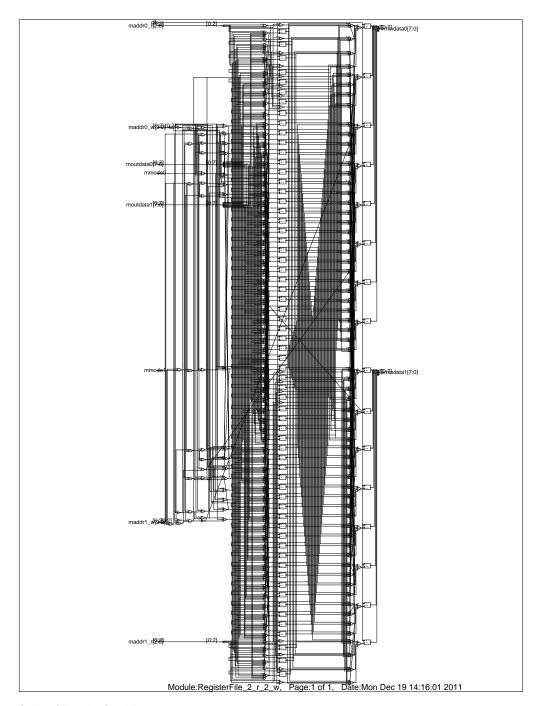

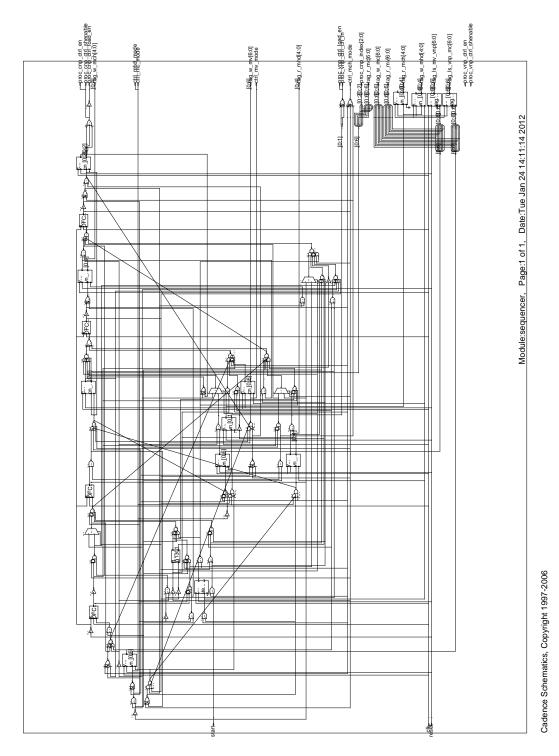

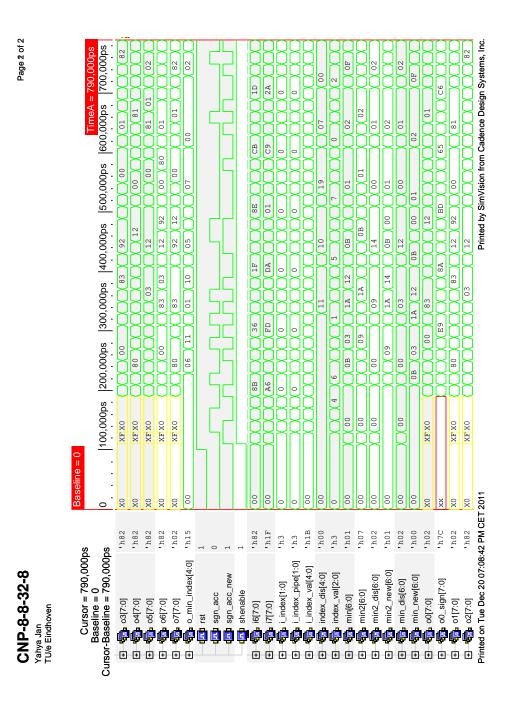

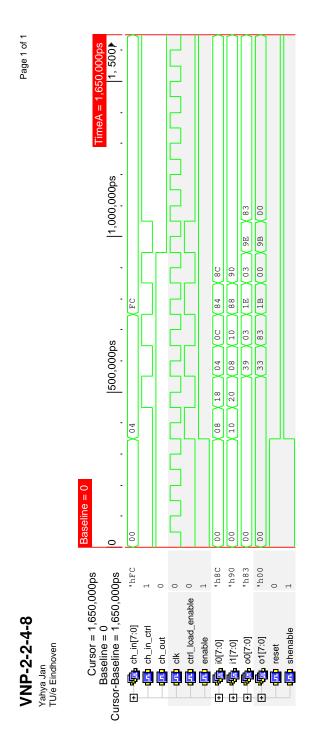

constraints are quite different from those supported by the traditional<sup>2</sup> hardware accelerator design methods presented in literature that usually accept just a few constraints, like only the clock speed constraint. An actual multi-objective optimization and tradeoff exploration are necessary. For instance, let us consider the video decoding. The same kind of video decoding can be used in a low power and area mobile device or a laptop, or a high-definition television (HDTV) from low through moderate to extremely high performance levels. Therefore, to quickly arrive at an adequate design quality for a particular application with all its particular constraints, objectives and tradeoff profiles, an adequate architecture design space exploration is indispensable taking into account the various design objectives, constraints and tradeoffs, which is not supported by the current hardware design methods and tools even for the simple case of micro-architecture synthesis (see Chapter 3 for details).