S. Arash Ostadzadeh

# Quantitative Application Data Flow Characterization for Heterogeneous Multicore Architectures

# Quantitative Application Data Flow Characterization for Heterogeneous Multicore Architectures

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.Ch.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op dinsdag 18 december 2012 om 12:30 uur

door

Sayyed Arash OSTADZADEH

Master of Science in Computer Engineering Ferdowsi University of Mashhad geboren te Mashhad, Iran Dit proefschrift is goedgekeurd door de promotor: Prof. dr. K.L.M. Bertels

Samenstelling promotiecommissie:

Rector Magnificus Prof. dr. K.L.M. Bertels Prof. dr. ir. H.J. Sips Prof. Dr.-Ing. Michael Hübner Prof. Dr.-Ing. Mladen Berekovic Prof. dr. Henk Corporaal Prof. dr. ir. Dirk Stroobandt Dr. G.K. Kuzmanov Prof. dr. ir. F.W. Jansen voorzitter Technische Universiteit Delft, promotor Technische Universiteit Delft Ruhr-Universität Bochum, Duitsland Technische Universität Braunschweig, Duitsland Technische Universiteit Eindhoven Universiteit Gent, België Technische Universiteit Delft Technische Universiteit Delft

#### S. Arash Ostadzadeh

Quantitative Application Data Flow Characterization for Heterogeneous Multicore Architectures

Met samenvatting in het Nederlands.

Subject headings: Dynamic Binary Instrumentation, Application Partitioning, Hardware/Software Co-design.

The cover images are abstract artworks created by the *Agony* drawing program developed by Kelvin (http://www.kelbv.com/agony.php).

Copyright © 2012 S. Arash Ostadzadeh

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the permission of the author.

Printed in The Netherlands

Dedicated to my dear parents

# Abstract

*GECENT* trends show a steady increase in the utilization of heterogeneous

*GECENT* trends show a steady increase in the utilization of heterogeneous

*f* multicore architectures in order to address the ever-growing need for computing performance. These emerging architectures pose specific challenges

*with* regard to their programmability. In addition, they require efficient

application mapping schemes to fully harness their processing power and avoid bottlenecks. In this respect, it is of critical importance to analyse application behaviour, and the data communication between tasks, in particular.

In this dissertation, we present a profiling framework that helps developers to gain an insight into the behaviour of an application. The presented profiling framework is generic and not restricted to a particular platform, application, or purpose. We utilize this framework with the primary goal of mapping applications onto a heterogeneous multicore architecture. The framework includes a memory access profiling toolset, called QUAD, that provides quantitative information regarding the memory accesses in an application. QUAD utilizes Dynamic Binary Instrumentation (DBI) to detect the actual data dependencies that occur between the tasks of an application at runtime. Additionally, it also provides accurate memory access measurements, such as the amount of data transferred between tasks and the memory size required for their communication. Such information can be utilized to identify critical parts of an application, to highlight coarsegrained parallelism opportunities, and to guide code optimizations.

As a proof of concept to substantiate the usefulness of the extracted profiling information, we utilize the main output of *QUAD*, the Quantitative Data Usage (QDU) graph, as the input model to formulate a general application partitioning problem. The formulation of this intractable problem is flexible and accommodates different design objectives and constraints. Subsequently, we propose a heuristic algorithm to find high quality partitions of an application in a reasonable amount of time. In addition to the complexity analysis of the proposed algorithm, we present a thorough theoretical analysis of the application partitioning problem. In order to evaluate the quality of the solutions, we developed a test bench for generating synthetic QDU graphs and compared the results against the optimal partitions obtained using an exhaustive search. The comparison results show that the proposed heuristic algorithm is able to provide optimal or near-optimal solutions.

To further prove the applicability of the profiling framework, we investigate in detail the utilization of the framework in practice, by mapping two real applications onto a heterogeneous reconfigurable architecture. To achieve this goal, we propose a hard-ware/software partitioning methodology that introduces the concept of merging tightly-coupled tasks based on the data communication analysis. Moreover, the profiling information is utilized to fine-tune the applications and optimize their data flow. The obtained results show a performance increase of 192% and 30%.

# Acknowledgements

My interest in computers dates back to 1987, when I managed to get my hands on a Commodore 64. I can still vividly recall the day my brother came up with a magic box in his hands. All it needed was just a "poke" to make my already hypnotized eyes poke out! and yes, I do remember the magical number after all these 25 years! POKE 53280,<color code: 0-15> and bingo... you have the desired border color! Simple, but it was more than enough to cast a spell on me. If I am where I am standing today, it is because of you, Shervin. I decided to study computer science because I was enchanted by your programming skills and enthusiasm. I will never forget all those good times when I used to sit beside you, trying to learn something new about computers. You are not only a dear friend and a true brother to me, but also a perennial source of inspiration and fortitude. Thanks for your selfless support and encouragement through all these years.

This thesis is not only the outcome of my endeavor over the last years, but also the kind guidance, assistance and support of several individuals, to all of whom I am deeply grateful. Words fail to stand for the deep gratitude that I wish to express to all of you. I would like to stress the fact that the order in which I acknowledge the names is not representative of the value that I place on their roles in this respect.

First of all, I would like to sincerely thank my advisor and promotor, Prof. Koen Bertels, who gave me the chance to step into the PhD journey. Koen, I kindly value your continuous support, commitment, and patience, which immensely influenced my research view. You gave me the opportunity to develop myself in different aspects and to have a vision for future research. I am grateful for your dedication to guide me along the entire journey, our fruitful discussions, and the freedom that you granted me to pursue the research work. I am also thankful for your invaluable comments on my thesis. I would like to extend my gratitude to my defense committee for the time that they invested in reading the thesis manuscript. I appreciate their insightful discussions and suggestions to improve the quality of this thesis.

I am indebted to my dear friend, Faisal, for all the proofreading of my thesis. Faisal, I value the time we spent for the research collaboration; but above that, I highly appreciate your genial friendship. Thanks for the helping hand whenever I needed you. My appreciation also goes to Roel for the comments and discussions on our collaborative research work. Roel, thanks for helping me during the recent years in Holland. I would like to express my gratitude to Imran for his valuable contributions to the extension of this research work. Imran, you are a smart, dedicated, hardworking researcher that anyone would cherish working with. At the same time, you are a modest and trustworthy friend. I would also like to thank Kamana for her friendship and support. I am grateful to Carlo for all the proofreading of my manuscripts and his comments over the last few years. I would also like to acknowledge Valery and Marco for their efforts to improve the *QUAD* toolset, Andrew for kindly proofreading the abstract and propositions of the thesis, Roel and Motta for their translation into Dutch.

My appreciation goes to Iranian friends in Holland who helped me settle down here and made me feel at home: Mahmood, Mojtaba, Alireza, Javad, Mehdi, Behnaz, Mahyar, Rahim, Hamed, Asad, Roya, Mehdi, Gholam Reza, Vahid, Azadeh, Ashkan, Ghazaleh, Sepideh, Mohammad Reza, Reza, Masoud, Mohammad, Amin, Behzad, Hossein, Hadi, Arash, Mohamad Reza, Ali, Hossein, and other friends that I have failed to name here. A special thanks goes to Alireza and Javad for tolerating me when I was falling asleep where I was not supposed to! ... thanks for being supportive through all these years. Mahyar, I appreciate all your invaluable support and kindness.

I would also like to acknowledge my present and former colleagues in the Computer Engineering research group at TU Delft: Zubair, Luyi, Thomas, Dimitrios, Sebastian, Jae, Tariq, Fakhar, Seyab, Aqeel, Mafalda, Innocent, Laiq, Bogdan, Omar, Hamid, Roel, Saleh, Elena, Cuong, Vlad, Razvan, Muhammad, Chunyang, and Demid. I am grateful to Lidwina for taking care of all the administrative work during these years. I also wish to thank Bert, Erik and Eef for their technical support.

I would like to take this opportunity to express my sincere appreciation to all my teachers who have taught me since I went to school, and to all my wonderful friends in Iran for their prayers, kind words, and moral support.

Finally, I wish to express my deepest gratitude to my dear parents for their endless love, support, and commitment throughout my life. Mom, Dad, your incomparable love gave me the strength to overcome all the troubles that I faced in my life. You were my one and only motivation to stay and complete this journey. Mom, Dad, I endured just to see the smile on your face, which means more than the world to me. You will always be the dearest to my heart. And I am forever thankful to God because of you and all the blessings that He has given me. He has always been there for me during the saddest and happiest times of my life. Though I have been into problems, and sometimes into pains, I have always felt blessed because of believing in God. I am eternally thankful to God for all the support and guidance, for giving me the courage to face problems, for giving me the strength to fight the difficulties in life, for allowing me to learn from my mistakes, and for hearing my prayers and granting me what I wished for.

Arash Ostadzadeh

Delft, The Netherlands, August 2012

# Table of contents

| Ał | ostrac  | t                          | Ш    |

|----|---------|----------------------------|------|

| Ac | knov    | vledgements                | v    |

| Та | ble o   | f contents                 | vii  |

| Li | st of t | figures                    | xi   |

| Li | st of   | tables                     | хШ   |

| Li | st of   | listings                   | xv   |

| Li | st of . | Acronyms                   | xvii |

| Те | rmin    | ology                      | xxi  |

| 1  | Intr    | oduction                   | 1    |

|    | 1.1     | Problem Overview           | 3    |

|    | 1.2     | Research Challenges        | 4    |

|    | 1.3     | Dissertation Contributions | 6    |

|    | 1.4     | Dissertation Organization  | 7    |

| 2  | Prof    | filing                     | 11   |

|    | 2.1     | Program Profiling          | 13   |

|    | 2.2     | Program Tracing            | 14   |

|    | 2.3     | Profiling Usage            | 14   |

|    | 2.4     | Profiling Classification   | 15   |

|    |         | 2.4.1 Static Analysis      | 15   |

|   |     | 2.4.2   | Dynamic Analysis                             | 16 |

|---|-----|---------|----------------------------------------------|----|

|   |     | 2.4.3   | Static vs. Dynamic Analysis                  | 16 |

|   | 2.5 | Softwa  | re Profiling                                 | 17 |

|   |     | 2.5.1   | Instrumentation Based Profiling              | 18 |

|   |     | 2.5.2   | Sampling Based Profiling                     | 19 |

|   |     | 2.5.3   | Simulation Based Profiling                   | 19 |

|   |     | 2.5.4   | Instrumentation vs. Sampling Based Profiling | 20 |

|   | 2.6 | Hardw   | vare Profiling                               | 21 |

|   | 2.7 | Data S  | tructures for Profiling                      | 21 |

|   | 2.8 | Profili | ng Approaches                                | 24 |

|   |     | 2.8.1   | Basic Block Profiling                        | 24 |

|   |     | 2.8.2   | Control Flow Profiling                       | 25 |

|   |     | 2.8.3   | Value Profiling                              | 26 |

|   |     | 2.8.4   | Variational Path Profiling                   | 26 |

|   | 2.9 | Summ    | ary                                          | 27 |

|   |     |         |                                              |    |

| 3 | Dyn |         | rofiling Framework                           | 29 |

|   | 3.1 |         | t Context                                    | 30 |

|   |     | 3.1.1   | Molen Abstraction Layer                      | 30 |

|   |     | 3.1.2   | Delft Workbench                              | 32 |

|   | 3.2 | Q² Pro  | filing Framework                             | 34 |

|   |     | 3.2.1   | <i>Quipu</i> Modeling Approach               | 35 |

|   |     | 3.2.2   | <i>QUAD</i> Memory Access Profiling Toolset  | 37 |

|   | 3.3 | Runtin  | ne Memory Access Profiling                   | 40 |

|   |     | 3.3.1   | Pin Dynamic Binary Instrumentation           | 42 |

|   |     | 3.3.2   | <i>QUAD</i> -core Development                | 44 |

|   |     | 3.3.3   | Memory Access Tracing                        | 46 |

|   |     | 3.3.4   | Identifying Memory-Intensive Kernels         | 49 |

|   |     | 3.3.5   | Bulk Data Flow Detection                     | 52 |

|   | 3.4 | Memo    | ry Access Intensity Profiler ( <i>MAIP</i> ) | 56 |

|   |     | 3.4.1   | <i>MAIP</i> Implementation                   | 58 |

|   |     | 3.4.2   | Computation Time vs. Communication Time      | 58 |

|   | 3.5 | Runtin  | ne Extraction of Source-Level Data           | 60 |

|   |     | 3.5.1   | DWARF Debugging Information                  | 61 |

|   |     | 3.5.2   | <i>xQUAD</i> Implementation                  | 62 |

|   | 3.6  | Kerne    | Ranking Based on Memory Access Intensity (MAI)                    | 63  |

|---|------|----------|-------------------------------------------------------------------|-----|

|   | 3.7  | Summ     | ary                                                               | 67  |

| 4 | Tem  | iporal I | Memory Bandwidth Analysis                                         | 69  |

|   | 4.1  | Backg    | round                                                             | 71  |

|   | 4.2  | Tempo    | oral Data Extraction                                              | 72  |

|   | 4.3  | tQuae    | Implementation                                                    | 74  |

|   | 4.4  | Case S   | Study: Wave Field Synthesis                                       | 77  |

|   |      | 4.4.1    | Experimental Setup                                                | 79  |

|   |      | 4.4.2    | Kernels Overview                                                  | 80  |

|   |      | 4.4.3    | Quantification of Data Communication                              | 80  |

|   |      | 4.4.4    | Temporal Information Extraction                                   | 84  |

|   |      | 4.4.5    | Phase Detection                                                   | 85  |

|   | 4.5  | Summ     | ary                                                               | 89  |

| 5 | Tasl | k Clust  | ering: A Greedy Approach                                          | 91  |

|   | 5.1  | Applic   | cation Partitioning                                               | 92  |

|   | 5.2  | Partiti  | oning Methods                                                     | 96  |

|   | 5.3  | Proble   | m Formulation                                                     | 99  |

|   | 5.4  | Multi-   | Objective Task Clustering                                         | 105 |

|   |      | 5.4.1    | Input Data Model                                                  | 106 |

|   |      | 5.4.2    | Greedy Algorithm                                                  | 107 |

|   |      | 5.4.3    | Application Partitioning Algorithm                                | 109 |

|   | 5.5  | Comp     | lexity Analysis                                                   | 114 |

|   |      | 5.5.1    | Time Complexity                                                   | 114 |

|   |      | 5.5.2    | Space Complexity                                                  | 118 |

|   | 5.6  | Synthe   | etic Analysis                                                     | 119 |

|   |      | 5.6.1    | Exhaustive Application Partitioning                               | 120 |

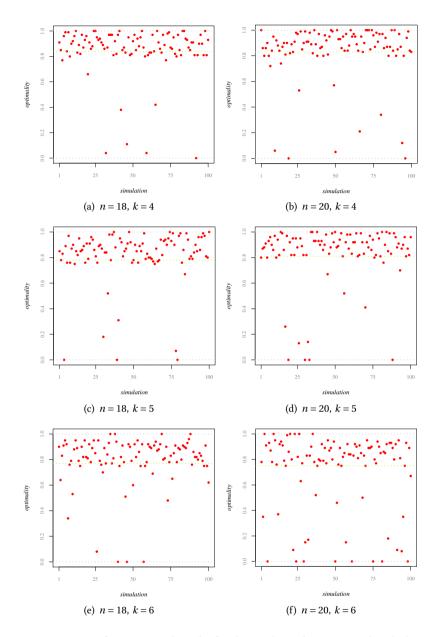

|   |      | 5.6.2    | Experimental Results                                              | 124 |

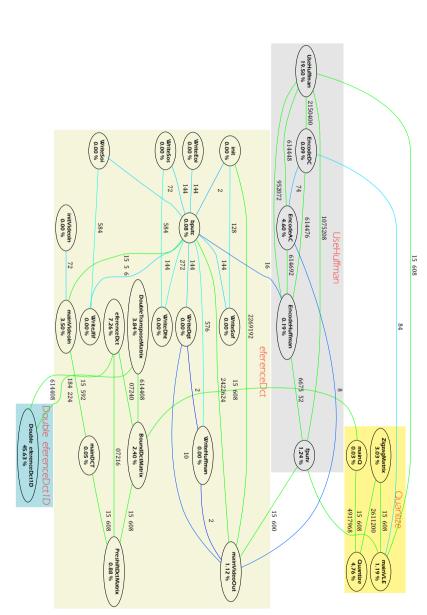

|   | 5.7  | MJPEC    | G Case Study                                                      | 125 |

|   | 5.8  | Summ     | ary                                                               | 127 |

| 6 | Util | izing Q  | <sup>2</sup> in HW/SW Partitioning: Case Studies                  | 131 |

|   | 6.1  | HW/S     | W Partitioning                                                    | 132 |

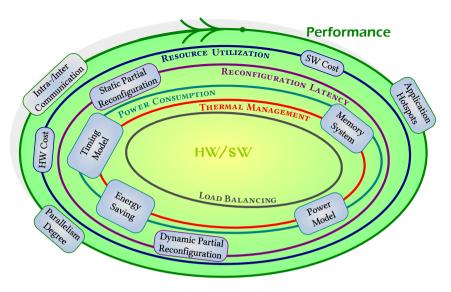

|   |      | 6.1.1    | HW/SW Co-design: Research Directions and Challenges $\ . \ . \ .$ | 134 |

|   |      | 6.1.2    | HW/SW Co-design Objectives                                        | 136 |

|     |         | 6.1.3              | Profile-guided HW/SW Partitioning     | 139 |

|-----|---------|--------------------|---------------------------------------|-----|

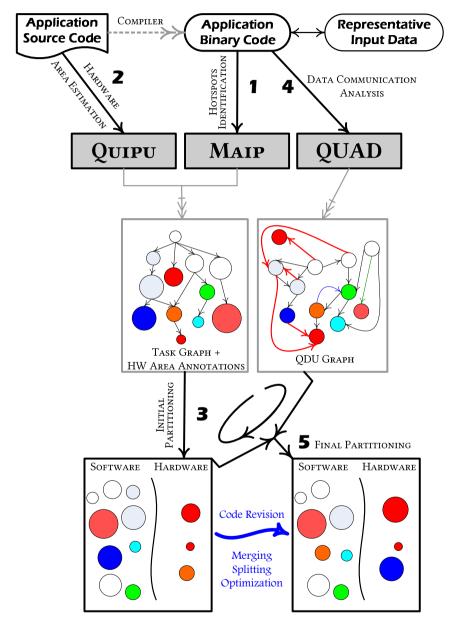

|     | 6.2     | The Q <sup>2</sup> | <sup>2</sup> Partitioning Methodology | 141 |

|     | 6.3     | Canny              | Edge Detection                        | 145 |

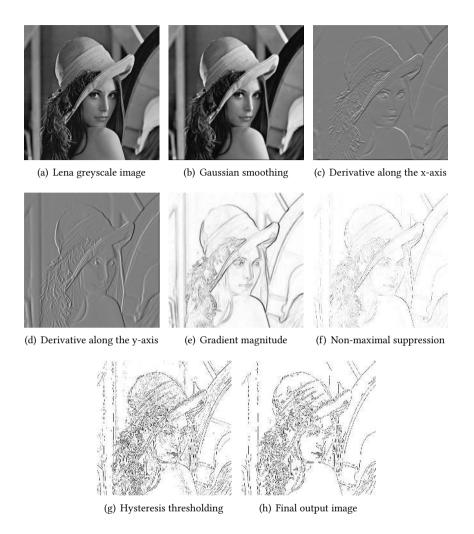

|     |         | 6.3.1              | Edge Detection Overview               | 145 |

|     |         | 6.3.2              | Experimental Setup                    | 147 |

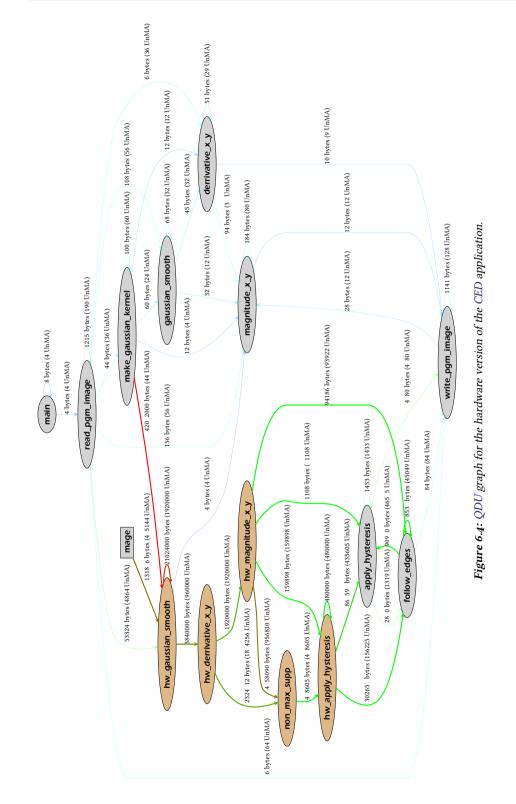

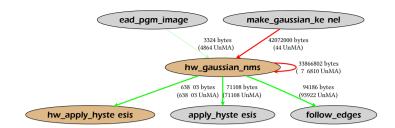

|     |         | 6.3.3              | Experimental Analysis                 | 148 |

|     |         | 6.3.4              | Observations and Results              | 158 |

|     | 6.4     | Mixed              | Excitation Linear Prediction          | 159 |

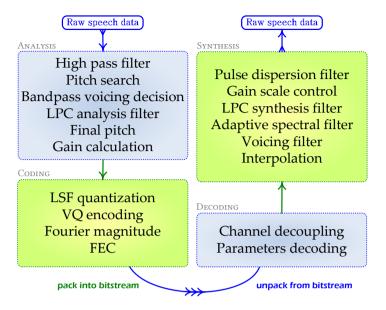

|     |         | 6.4.1              | MELP Overview                         | 159 |

|     |         | 6.4.2              | Experimental Setup                    | 161 |

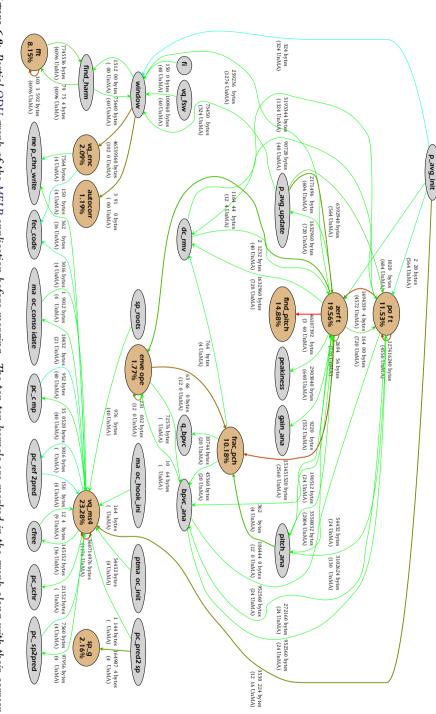

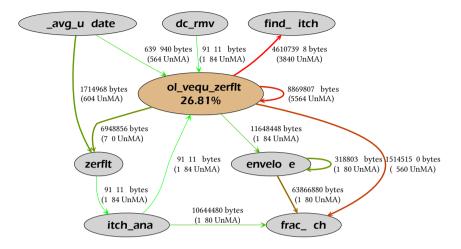

|     |         | 6.4.3              | Experimental Analysis                 | 162 |

|     |         | 6.4.4              | Observations and Results              | 168 |

|     | 6.5     | Summ               | ary                                   | 168 |

| 7   | Con     | clusior            | 15                                    | 171 |

|     | 7.1     | Summ               | ary                                   | 172 |

|     | 7.2     | Main (             | Contributions                         | 173 |

|     | 7.3     | Resear             | ch Opportunities                      | 174 |

| Bi  | bliog   | raphy              |                                       | 179 |

| Lis | st of ] | Publica            | tions                                 | 199 |

| Sa  | menv    | atting             |                                       | 205 |

| Cu  | ırricı  | ılum V             | itae                                  | 209 |

# List of figures

### Chapter 1

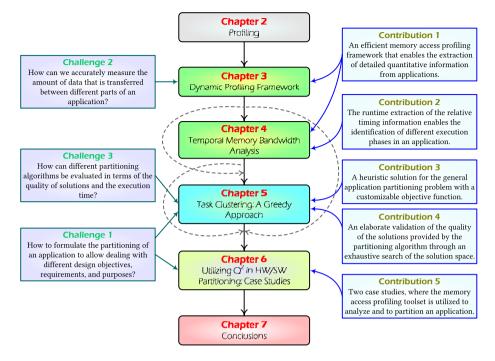

| 1.1 | An outline of the different chapters, challenges, and contributions in this |   |

|-----|-----------------------------------------------------------------------------|---|

|     | dissertation                                                                | 8 |

### Chapter 2

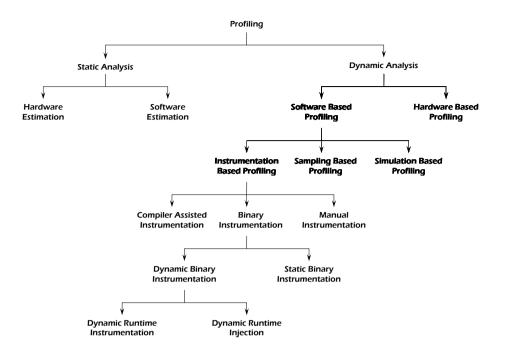

| 2.1 A | An outline of th | ne different class | es of application | profiling. |  | 22 |

|-------|------------------|--------------------|-------------------|------------|--|----|

|-------|------------------|--------------------|-------------------|------------|--|----|

### Chapter 3

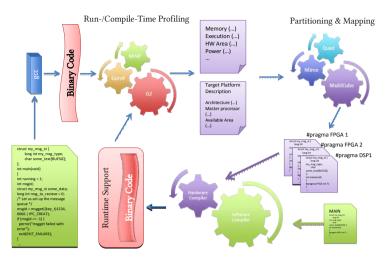

| An overview of the Molen Machine Organization.                                       | 32                                           |

|--------------------------------------------------------------------------------------|----------------------------------------------|

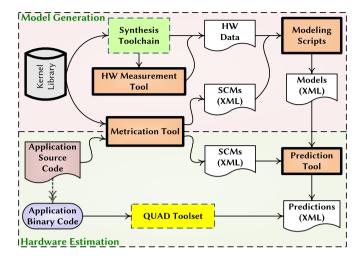

| An overview of the Delft Workbench toolchain. $\ldots \ldots \ldots \ldots$          | 33                                           |

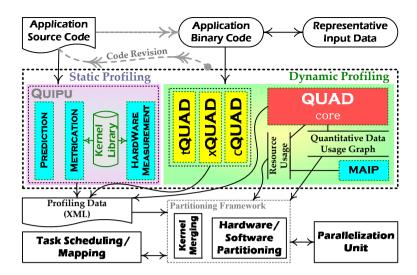

| An overview of the $Q^2$ profiling framework in the <i>Delft Workbench</i>           | 35                                           |

| An overview of the <i>Quipu</i> modeling approach.                                   | 36                                           |

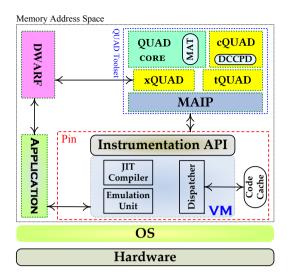

| An architectural overview of the dynamic part of the Q <sup>2</sup> profiling frame- |                                              |

| work                                                                                 | 39                                           |

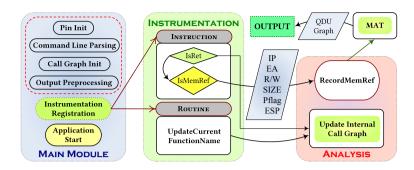

| Implementation overview of the <i>QUAD</i> -core tool                                | 45                                           |

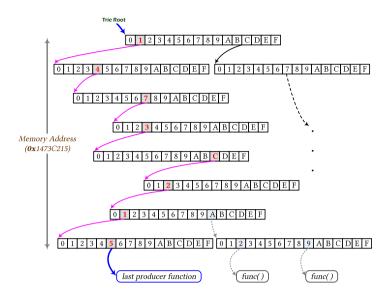

| An outline of the dynamic trie data structure of base 16                             | 47                                           |

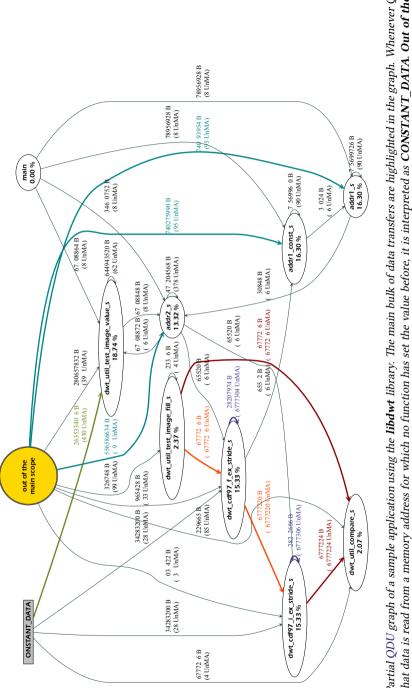

| Partial Quantitative Data Usage (QDU) graph of a sample application                  |                                              |

| using the <b>libdwt</b> library                                                      | 55                                           |

| A sample Debugging Information Entry (DIE).                                          | 61                                           |

|                                                                                      | An overview of the Delft Workbench toolchain |

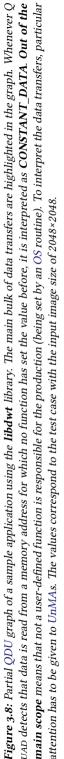

| 4.1 | An overview of the <i>tQUAD</i> implementation. |  |  |  |  |  |  |  | • |  |  | • |  |  |  | • |  |  |  | 75 | 5 |

|-----|-------------------------------------------------|--|--|--|--|--|--|--|---|--|--|---|--|--|--|---|--|--|--|----|---|

|-----|-------------------------------------------------|--|--|--|--|--|--|--|---|--|--|---|--|--|--|---|--|--|--|----|---|

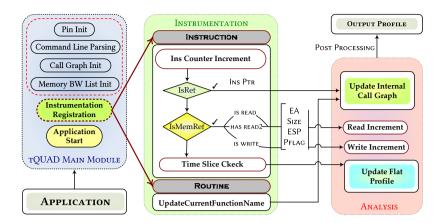

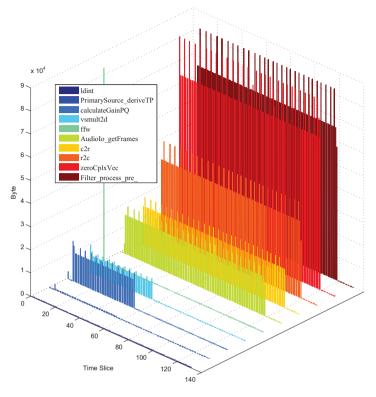

| 4.2 | Memory bandwidth usage of the kernels in the <i>hArtes wfs</i> , considering only the read accesses including the stack area | 85 |

|-----|------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3 | Memory bandwidth usage of kernels in <i>hArtes wfs</i> , considering only the write accesses excluding the stack area.       | 86 |

### Chapter 5

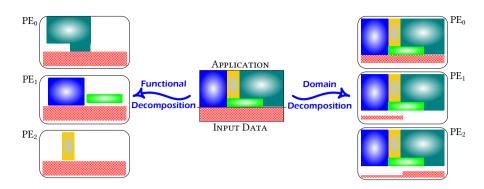

| 5.1 | Domain vs. functional decomposition.                                                        | 93  |

|-----|---------------------------------------------------------------------------------------------|-----|

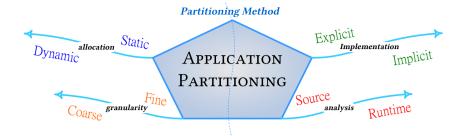

| 5.2 | Different application partitioning factors                                                  | 96  |

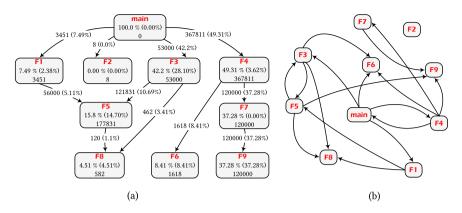

| 5.3 | A typical example of the data dependency among functions in an appli-<br>cation             | 107 |

| 5.4 | The outline of the task clustering algorithm                                                | 112 |

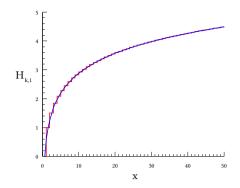

| 5.5 | The generalized harmonic number of order $k$ of 1 ( $\mathcal{H}_{k,1}$ )                   | 116 |

| 5.6 | An example of partitioning a set of five elements                                           | 122 |

| 5.7 | Summary of the experimental results for synthetic data compared with the optimal partitions | 126 |

| 5.8 | A partitioned QDU graph of the Motion Joint Photographic Experts Group (MJPEG) application. | 128 |

| 6.1  | HW/SW co-design objectives.                                              | 137 |

|------|--------------------------------------------------------------------------|-----|

| 6.2  | The $Q^2$ partitioning approach.                                         | 143 |

| 6.3  | The steps of the Canny Edge Detection (CED) implementation               | 148 |

| 6.4  | QDU graph for the hardware version of the CED application                | 155 |

| 6.5  | Partial QDU graph of the CED application after merging                   | 158 |

| 6.6  | Overview of the live ranges of memory blocks in the CED application.  .  | 159 |

| 6.7  | The Mixed Excitation Linear Prediction (MELP) vocoder block diagram      | 162 |

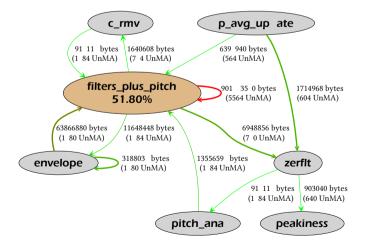

| 6.8  | Partial QDU graph of the MELP application before merging                 | 166 |

| 6.9  | Partial QDU graph of the MELP application after the first merging step   | 169 |

| 6.10 | Partial QDU graph of the MELP application after the second merging step. | 169 |

# List of tables

## Chapter 2

| 2.1 | Static Code Analysis vs. Dynamic Code Analysis. | 17 |

|-----|-------------------------------------------------|----|

| 2.2 | Instrumentation vs. sampling based profiling    | 20 |

### Chapter 3

| 3.1 | <i>gprof</i> flat profile of the <i>x264</i> application on the <i>Intel x86</i> architecture                                                                    | 50 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Summary of the data production/consumption of the <b>satd</b> - and <b>sad</b> -related kernels in the <i>x264</i> application                                   | 51 |

| 3.3 | <i>gprof</i> flat profile of the revised <i>x264</i> application, both for un-instrumented and <i>QUAD</i> -instrumented binaries.                               | 53 |

| 3.4 | Summary of the data production/consumption of <b>pixel_satd_wxh</b> and the <b>sad</b> -related functions in the revised version of the <i>x264</i> application. | 54 |

| 3.5 | Memory access statistics for the <i>hArtes wfs</i> application, divided in stack, heap, and data sections.                                                       | 64 |

| 3.6 | The <i>gprof</i> profiling data for the <i>hArtes wfs</i> application on the <i>Intel x86</i> architecture.                                                      | 65 |

| 3.7 | Communication vs. computation profiling data of the <i>hArtes wfs</i> application on the <i>Intel x86</i> architecture.                                          | 66 |

| 3.8 | A Ranking based on the MAI of the kernels in the $hArtes wfs$ application.                                                                                       | 67 |

|     |                                                                                                                                                                  |    |

| 4.1 | <i>gprof</i> flat profile for the <i>hArtes wfs</i> application    | 81 |

|-----|--------------------------------------------------------------------|----|

| 4.2 | Summary of the data produced/consumed by the kernels in the hArtes |    |

|     | wfs application.                                                   | 82 |

| 4.3 | gprof flat profile for QUAD-instrumented version of the hArtes wfs appli- |    |

|-----|---------------------------------------------------------------------------|----|

|     | cation                                                                    | 83 |

| 4.4 | Identified phases in the execution path of the $hArtes$ wfs application   | 87 |

### Chapter 5

| 5.1 | An overview of various application partitioning approaches previously appeared in literature.                        | 100 |

|-----|----------------------------------------------------------------------------------------------------------------------|-----|

| 5.2 | Total number of possible partitions in an exhaustive search of the solution space regarding different problem sizes. | 125 |

| 5.3 | Clusters in the MJPEG application.                                                                                   | 127 |

| 6.1 | gprof flat profile for the CED application on the $Intelx86$ architecture.                                                      | 149 |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2 | gprof flat profile for the CED application on the embedded PowerPC (PPC).                                                       | 150 |

| 6.3 | <i>MAIP</i> flat profile for the CED application                                                                                | 151 |

| 6.4 | Area predictions and theoretical speedups for the kernels in the CED application                                                | 153 |

| 6.5 | Area predictions and theoretical speedups for the merged and optimized versions of the CED application.                         | 157 |

| 6.6 | <i>MAIP</i> flat profile for the MELP application                                                                               | 163 |

| 6.7 | Area predictions and theoretical speedups for the kernels in the MELP application                                               | 164 |

| 6.8 | Results of the analysis of the merging options, final merged kernels, and the actual synthesis results for the MELP application | 167 |

# List of listings

| 3.1    | Memory access tracing implementation in <i>QUAD</i> -core | 48 |

|--------|-----------------------------------------------------------|----|

| Chapte | r 4                                                       |    |

| 4.1    | <i>tQUAD</i> main interface.                              | 76 |

| 4.2    | $tQ_{UAD}$ instruction instrumentation                    | 78 |

| 4.3    | tQUAD routine instrumentation                             | 79 |

# List of Acronyms

| ACO    | Ant Colony Optimization                                                          |

|--------|----------------------------------------------------------------------------------|

| ANSI-C | American National Standards Institute standard for the C programming language    |

| API    | Application Programming Interface                                                |

| ASCII  | American Standard Code for Information Interchange, a character-encoding scheme. |

| ASIC   | Application Specific Integrated Circuit                                          |

| ASIP   | Application Specific Instruction-set Processor                                   |

| AST    | Abstract Syntax Tree16                                                           |

| BB     | Branch and Bound                                                                 |

| BCS    | Binary-Constraint Search                                                         |

| bpp    | bits per pixel                                                                   |

| bps    | bits per second, also written as bit/s or b/s                                    |

| BRAM   | Block RAM, a local block of RAM on a Virtex FPGA147                              |

| CCU    | Custom Computing Unit                                                            |

| CDFG   | Control and Data Flow Graph23                                                    |

| CED    | Canny Edge Detection                                                             |

| CFG    | Control Flow Graph15                                                             |

| CISC   | Complex Instruction Set Computer                                                 |

| СМР    | Chip Multi-Processor2                                                            |

| СРІ    | Cycles Per Instruction                                                           |

| CPU    | Central Processing Unit12                                                        |

| CU     | Compilation Unit                                                                 |

| DAG    | Directed Acyclic Graph22                                                         |

| DBA    | Dynamic Binary Analysis175                                                       |

| DBI    | Dynamic Binary Instrumentation                                                   |

| DCA    | Dynamic Code Analysis15                                                          |

| DCCPD | Data Communication Channel Pattern Detection                                   |

|-------|--------------------------------------------------------------------------------|

| DCT   | Discrete Cosine Transform                                                      |

| DES   | Data Encryption Standard                                                       |

| DFG   | Data Flow Graph                                                                |

| DFL   | Dataflow Language, a graphical workflow language for dataflows                 |

| DFT   | Discrete Fourier Transform                                                     |

| DIE   | Debugging Information Entry                                                    |

| DMA   | Direct Memory Access                                                           |

| DRAM  | Dynamic Random Access Memory                                                   |

| DSE   | Design Space Exploration35                                                     |

| DSP   | Digital Signal Processor or Digital Signal Processing14                        |

| DTMF  | Dual Tone Multi Frequency    160                                               |

| DWARF | Debugging With Attributed Record Formats                                       |

| DWARV | Delft Workbench Automated Reconfigurable VHDL generator 49                     |

| DWB   | Delft Workbench                                                                |

| DWT   | Discrete Wavelet Transform 52                                                  |

| EA    | Effective Address                                                              |

| EFG   | Execution Flow Graph                                                           |

| ELF   | Executable and Linkable Format, formerly known as Extensible Linking<br>Format |

| ESG   | Extended Syntax Graph                                                          |

| FFT   | Fast Fourier Transform 161                                                     |

| FPGA  | Field Programmable Gate Array                                                  |

| FSM   | Finite State Machine                                                           |

| GA    | Genetic Algorithm                                                              |

| GCLP  | Global Criticality/Local Phase                                                 |

| GPP   | General-Purpose Processor                                                      |

| GPU   | Graphical Processing Unit 133                                                  |

| HCDFG | Hierarchical Control- and Data-Flow Graph                                      |

| HDL   | Hardware Description Language                                                  |

| HDS   | Hardware Debug System                                                          |

| HDVL  | Hardware Description and Verification Language                                 |

| HLL   | High-Level (Programming) Language11                                            |

| HLS   | High-Level Synthesis                                                           |

| НРС   | High Performance Computing1                                                    |

| HTG   | Hierarchical Task Graph24                                                      |

| IBF     | Interleaving Balance Factor                                                                    |

|---------|------------------------------------------------------------------------------------------------|

| IC      | Integrated Circuit                                                                             |

| ILP     | Instruction-Level Parallelism                                                                  |

| ILP     | Integer Linear Programming                                                                     |

| IP      | Intellectual Property                                                                          |

| IP      | Instruction Pointer, also called program counter (PC) or Instruction<br>Address Register (IAR) |

| IPC     | Instructions Per Cycle                                                                         |

| IR      | Intermediate Representation                                                                    |

| ISE     | Integrated Software Environment 162                                                            |

| ЈІТ     | Just-In-Time                                                                                   |

| KLFM    | Kernighan-Lin/Fiduccia-Matheyes                                                                |

| KL      | Kernighan-Lin                                                                                  |

| LPC     | Linear Predictive Coding, a powerful speech analysis technique 160                             |

| LUT     | Look-Up Table                                                                                  |

| MAI     | Memory Access Intensity                                                                        |

| Maip    | Memory Access Intensity Profiler                                                               |

| MAL     | Molen Abstraction Layer 172                                                                    |

| MAR     | Memory Access Ratio                                                                            |

| MAT     | Memory Access Tracing 172                                                                      |

| MELP    | Mixed Excitation Linear Prediction 173                                                         |

| MILP    | Mixed Integer Linear Programming                                                               |

| ΜΙΜΟ    | Multiple-Input and Multiple-Output                                                             |

| MJPEG   | Motion Joint Photographic Experts Group                                                        |

| MOR     | Memory Operand Ratio 57                                                                        |

| MPSoC   | Multi-Processor System on Chip 140                                                             |

| NLOC-MA | <b>R</b> Non-Local Memory Access Ratio                                                         |

| NLOC-MO | <b>R</b> Non-Local Memory Operand Ratio                                                        |

| NPP     | Noise Pre-Processor                                                                            |

| OSCI    | Open SystemC Initiative                                                                        |

| OS      | Operating System                                                                               |

| РСМ     | Pulse-Code Modulation, a method to encode digitally sampled analog signals                     |

| PE      | Processing Element                                                                             |

| PGM     | Portable GrayMap, an image file format defined by the Netpbm project.147                       |

| PLD     | Programmable Logic Device 133                                                                  |

| РРС     | PowerPC                                                                                        |

| PSO     | Particle Swarm Optimization                                                                      |

|---------|--------------------------------------------------------------------------------------------------|

| QDU     | Quantitative Data Usage                                                                          |

| RP      | Reconfigurable Processor                                                                         |

| SA      | Simulated Annealing                                                                              |

| SCA     | Static Code Analysis15                                                                           |

| SCM     | Software Complexity Metric 35                                                                    |

| SDRAM   | Synchronous Dynamic Random Access Memory                                                         |

| SIMD    | Single Instruction Multiple Data 49                                                              |

| SISAL   | Streams and Iteration in a Single Assignment Language                                            |

| SLDL    | System-Level Design Language136                                                                  |

| SLIF    | System-Level Intermediate Format                                                                 |

| SoC     | System on Chip                                                                                   |

| SP      | Stack Pointer                                                                                    |

| SSA     | Static Single Assignment                                                                         |

| SSE     | Streaming SIMD Extensions 49                                                                     |

| STG     | State Transition Graph 24                                                                        |

| тв      | Time Base, a counting register to keep track of system time 161                                  |

| TDFG    | Task Data Flow Graph                                                                             |

| TLM     | Transaction-Level Modeling 136                                                                   |

| UnDV    | Unique Data Value                                                                                |

| UnMA    | Unique Memory Address                                                                            |

| USDoD   | United States Department of Defence                                                              |

| UVM     | Universal Verification Methodology 136                                                           |

| VHDL    | VHSIC Hardware Description Language (VHSIC stands for Very-High-Speed Integrated Circuit)        |

| VLIW    | Very Long Instruction Word                                                                       |

| VLSI    | Very-Large-Scale Integration                                                                     |

| VM      | Virtual Machine                                                                                  |

| VQ      | Vector Quantization                                                                              |

| WCET    | Worst Case Execution Time                                                                        |

| WFS     | Wave Field Synthesis                                                                             |

| XDL     | Xilinx Design Language                                                                           |

| XML     | eXtensible Markup Language 37                                                                    |

| πISA    | Polymorphic Instruction Set Architecture                                                         |

| ρμ-code | configuration microcode, or Reconfigurable Micro-code, used in the Molen<br>Machine Organization |

# Terminology

In this dissertation, we refer to several terms that are ambiguous and may specifically cause confusion when used in the context of Computer Science. In the following, we clarify the most important and frequently used terms.

- QUAD It stands for Quantitative Usage Analysis of Data. By data, we mean data that is communicated (produced, stored, retrieved, and consumed) via main memory in a computing system between a pair of functions. Apart from the main QUADtool, called QUAD-core, there are three dependent tools that are called: tQUAD, cQUAD, and xQUAD. Each of these tools focus on a particular aspect of the analysis. t denotes *Temporal*, c marks *Communication*, and x is for *eXactitude*. The term QUAD is generally used to refer to the whole QUAD toolset. For more details, see Chapter 3 and Chapter 4.

- **Application** A computer software or simply a program that is developed to perform a specific task.

- **Source Code** Any collection of computer instructions (possibly with comments) written using some human-readable computer language, usually as text. The term 'code' may also be used as the short form of 'source code', but usually used where the nature of the code is not relevant, thus 'code' can be in any format.

- **Function** Part of a source code that is an independent unit in relation to the rest of the source code, with clearly defined inputs (formal parameters) and outputs (results). A function can be executed as a whole by calling the function with a set of parameters. Other terms that may be used, in the general sense, for *function* include: (sub)routine, procedure, or method. Caution should be taken as these terms can have their own specific meanings in different contexts, which distinguishes them from the term *function*.

- **Kernel** A code segment in the context of a larger application which performs a set of operations. It contributes to a relatively independent task in the context of the application algorithm. A kernel can be a function or a loop nest. Usually, a kernel consists of *consecutive* instructions of a program, however, this should not be regarded as a restriction. Since we introduce the idea of merging code segments in this thesis, in the general sense, a kernel may refer to a collection of inconsecutive code segments. Furthermore, we mostly use 'kernel' to refer to a candidate for

hardware acceleration in reconfigurable systems. In this dissertation, the terms 'function', 'kernel', and 'code segment' are used interchangeably when no confusion arises.

**Self-contribution** The self-contribution of a function refers to the execution time required by the function alone, without considering the time spent in its descendants (the functions invoked by that function). We use the expression 'entire contribution' to denote the whole execution time needed for the function including its descendants. In the case of direct recursion, the execution time of a recursive function denotes the entire contribution, and self-contribution makes no sense in this respect.

# CHAPTER

# Introduction

"If something is to be done, I have a feeling that I should start doing it." †

— Ehsan Yarshater

*OMPUTING SYSTEMS* today face some big challenges, at the same time, they provide exciting opportunities, due to the end of single-processor performance scaling, new demands imposed by High Performance Computing (HPC), embedded computing, and mobile computing. Furthermore, there is an ever increasing need for energy efficiency across the computing spectrum in general. In this respect, multidisciplinary research is becoming increasingly important, as the boundaries between hardware/software and general-/special-purpose processing blur in today's heterogeneous systems, as the architectures and capabilities of computing systems are becoming ever more varied, and most importantly, as applications continue

The growing disparity of the speed between processor(s) and the memory residing outside the chip(s), referred to as the *Memory Wall*<sup>1</sup>, has created a severe obstacle in the performance gain of computing systems. An important reason for this disparity is the limited communication bandwidth across chip boundaries. From the mid 80s to the beginning of the 21<sup>th</sup> century, the speed of the Central Processing Unit (CPU) improved at a rate of approximately 55% each year, while the rate of improvement for memory speed was only 10%. Given these trends, it was apparent that the memory latency would (potentially) become an overwhelming bottleneck in the performance of the computing systems. Today, improvements in the CPU speed have significantly decelerated, partly due to major physical obstacles, and partly due to the fact that contemporary CPU designs have already hit the memory wall to some extent. Intel, the world's prominent

to expand, both in terms of requirements and sophistication.

<sup>†</sup> Quoted from "*A Lifetime Quest to Finish a Monumental Encyclopedia of Iran*", An article by Patricia Cohen, The New York Times, published on 12<sup>th</sup> August 2011.

<sup>&</sup>lt;sup>1</sup> The term was initially coined by Wulf and McKee in 1994 (*Hitting the Memory Wall: Implications of the Obvious*) [228]

chip manufacturer, has highlighted this issue in its *Platform 2015 White Paper*<sup>2</sup>, which describes the evolution of the Intel's microprocessor architecture over the decade from 2005 to 2015:

In the past, performance scaling in conventional single-core processors has been accomplished largely through increases in clock frequency (accounting for roughly 80 percent of the performance gains). But frequency scaling is running into some fundamental physical barriers. First of all, as chip geometries shrink and clock frequencies rise, the transistor leakage current increases, leading to excess power consumption and heat. Secondly, the advantages of higher clock speeds are in part negated by memory latency, since memory access times have not been able to keep pace with increasing clock frequencies. Third, for certain applications, traditional serial architectures are becoming less efficient as processors get faster (due to the so-called Von Neumann bottleneck), further undercutting any gains that frequency increases might otherwise buy. In addition, resistance capacitance delays in signal transmission are growing as feature sizes shrink, imposing an additional bottleneck that frequency increases do not address.

Sequential computing has dominated the computer architecture landscape for about five decades. Designers were able to design and build faster and faster computers by relying on improvements of fabrication technologies and architectural/organization optimizations. However, due to the aforementioned critical limitations, computing systems now need to achieve performance gains by other means than increasing the clock speed of Processing Elements (PEs). The main idea is that rather than performing operations in a sequence at an extremely high clock frequency, multiple PEs execute large quantities of operations in parallel at moderate clock rates to achieve increased performance. This implies that the running application should somehow be divided into (many) concurrent operational blocks and distributed among the PEs. This radical shift in application development and execution has already forced the industry to move into and promote the *concurrency era*.

The switch to multiprocessor systems has elevated concurrency as a major issue in utilizing the ever increasing number of PEs in computing systems. As a result, the most important direction in microprocessor architecture pertains to *increasing parallelism for increased performance*. The progress initially started with superscaler architectures, then came the multiprocessing functionality, and it continued with some influential capabilities such as out-of-order execution and hyper-threading. These features all laid the tiles for a major milestone in microprocessor architecture, *the movement away from a monolithic processing core to multiple cores on a single chip*. Chip manufactures are making *multicore* processor-based platforms mainstream. These platforms started with two cores and are now evolving to many more. Processors containing dozens and even hundreds of cores are already envisioned in the near future. There is no doubt that Chip Multi-Processors (CMPs) will gain control over the future microprocessor architectures, delivering excellent performance scaling, while, at the same time, solving the power consumption problem.

<sup>&</sup>lt;sup>2</sup> Platform 2015: Intel® Processor and Platform Evolution for the Next Decade [41]

Recently, there has been a substantial growth in applications that require special types of processing in addition to conventional general-purpose and/or high-performance processing. This requirement, in turn, created a trend for the fabrication of chips with specialized functions, such as signal processing, media processing, and network processing. Furthermore, it even brought about versatility and adaptability as major factors in General-Purpose Processors (GPPs) to enable them to dynamically match their capabilities to a diverse range of applications. *Hardware acceleration* is an umbrella term that encompasses the idea of this special form of processing. Generally, hardware acceleration refers to the exploitation of specialized hardware to perform a function more efficiently than is possible in software running on a GPP. Examples of hardware acceleration include motion compensation in Graphical Processing Units (GPUs), matrix operations in Digital Signal Processors (DSPs), and instructions for dealing with complex numbers in conventional CPUs.

In the meantime, reconfigurable architectures have also attracted considerable attention due to the fact that they are identified as powerful alternatives for creating highly efficient computing systems. Reconfigurable architectures offer substantial performance improvements via custom design and reconfiguration capabilities, compared against traditional processing architectures. Reconfiguration is characterized by the ability of hardware devices to rapidly alter the functionalities of their components and the interconnection between them as needed. The primary advantage of these emerging architectures is the ability to increase performance with accelerated hardware implementation, while maintaining the flexibility of a software solution. This is generally accomplished by mapping computationally intensive parts of an application onto reconfigurable hardware. The most widely-used example of reconfigurable devices are Field Programmable Gate Arrays (FPGAs) [173]. FPGA devices are commonly perceived as co-processing units coupled with GPPs to provide hardware acceleration functionalities. In fact, a considerable share of hardware accelerators are built on top of FPGA devices. For example, they are used in automotive navigation systems and rear-seat displays, ultrasound imaging systems, robotically-assisted surgical systems, 3-D televisions, and sophisticated mobile communication systems. Xilinx [230] and Altera [6] are the world's leading providers of FPGA fabrics, which have control over 80% of the whole market<sup>3</sup>.

### **1.1 Problem Overview**

Heterogeneous multicore systems have gained increasing attention over the last couple of years, because the end of era for single-processor computing systems is imminent. In this respect, multiprocessor systems utilizing reconfigurable fabrics are in the focus of attention because they constitute a very interesting coupling between the performance of hardware and the flexibility of software. Reconfigurable fabrics such as FPGAs can be used as stand-alone processors or in combination with GPPs. The functions executed on the reconfigurable fabric can be changed (at runtime or at compile time) with respect to the target application. However, for this technology to really be adopted on a large scale, a number of important gaps have to be bridged, of which some are considered to be difficult. One of these challenges is the need for a machine organization that provides

<sup>&</sup>lt;sup>3</sup> Xilinx, by itself, had nearly 50% of the market share in 2011.

a generic way in which different components such as a GPP and various reconfigurable devices can be combined in a transparent way. Another challenge is that we need the necessary tools to transform (existing or new) applications in such a way that we can ultimately unleash the performance of these systems to the full extent.

We need such tools because application development in this context no longer lends to the conventional sequential model. Furthermore, there is a wide range of legacy applications that need to be mapped onto these emerging architectures. Thus, in the first place, there is a critical need to thoroughly understand and analyse what is happening inside the application. In this respect, the memory access behaviour of the application is of critical importance, as it turns out that data communication is the primary obstacle in achieving the anticipated speedups in parallel systems. Moreover, application developers require detailed information about the memory accesses in applications to fine-tune and customize them for maximum performance on any given architecture.

The complexity of non-trivial applications makes it difficult to manually find the required information, hence there is an obvious need for tools to help developers in pinpointing performance bottlenecks. Extracting the potential coarse-grained parallelism to efficiently map an application onto these systems is only possible if quantitative information about the inter-task data dependencies are available. This, in turn, necessitates the development and usage of tools than can provide these information. Furthermore, an appropriate partitioning approach is needed in order to use these information for mapping the application in such a way that design objectives are met.

### 1.2 Research Challenges

The problem of mapping an application onto a heterogeneous reconfigurable architecture has various aspects. This includes parallelism detection, application partitioning, Design Space Exploration (DSE), among others. In this work, we do not address all the aspects of this research domain. For that reason, we only focus on some specific challenges, which were briefly mentioned earlier in this chapter and are highlighted in the following.

# Challenge 1 – How to formulate the partitioning of an application to allow dealing with different design objectives, requirements, and purposes?

While heterogeneous multicore architectures are excellent candidates for parallel processing, there is an important problem not solved yet. It is not easy nor straightforward to map an existing sequential application onto these systems while fully utilizing their processing potential. As these systems have multiple PEs and diverse shared resources, the problem of balancing the workload among multiple cores becomes critical. The performance of the system is not only determined by the workload of the application tasks, but also by the way these tasks communicate and share the available resources. It is not obvious how to reasonably assign tasks to each PE so that there will be no bottleneck which compromises the performance of the system. Furthermore, not all the mapping objectives are within the same direction, which makes the application partitioning, and subsequent mapping, even more complex. As an example, optimizing energy consumption in these systems may prefer the idleness of some PEs on the availability of extra resources for certain application. This is incongruous with the workload balancing strategy among all available PEs. In this thesis, we formulate a general application partitioning problem, where various objectives are taken into account to find an appropriate solution for the partitioning problem. This will let the application developer efficiently program a heterogeneous multicore system to unleash its potential.

The problem of general application partitioning is formulated in Chapter 5 and a practical methodology to address HW/SW partitioning for a heterogeneous reconfigurable system is discussed in Chapter 6.

#### Challenge 2 — How can we accurately measure the amount of data that is transferred between different parts of an application?

The availability of parallel processing can potentially offer extra processing power compared to sequential processing. However, while an application conventionally exploits the full capacity of a single processor, it is hard to decompose and distribute the application in a way that it actually runs faster on some parallel system. The major problem inherent in the application is data dependencies between tasks or communication costs, which limit the achievable speedup. A critical research problem for heterogeneous multicore systems is how to measure the amount of data that is transferred between a pair of tasks. This is not easy since the exact amount, in most cases, can only be determined dynamically during the execution of the application. What makes the problem complicated is the fact that we have to keep track of all the memory accesses occurring during the execution of an application in order to have an accurate estimation of inter-task data communication. The dynamic profiling framework presented in this thesis addresses this problem by identifying the actual data dependencies arising during the execution of an application.

The dynamic memory access profiling toolset is presented in Chapter 3. An extension of the profiling toolset to extract temporal information is described in Chapter 4.

# Challenge 3 – How can different partitioning algorithms be evaluated in terms of the quality of solutions and the execution time?

One major problem regarding different application partitioning algorithms is the lack of a robust and fair basis of comparison. This research has not been appropriately addressed since it is difficult to compare the results of different partitioning strategies. This is due to the different input models, objective functions, assumptions, test cases, and target architectures that are used in each research work. The diversity of critical factors in these works is such that it is nearly impossible or very difficult and unclear to prefer one over another. Even worse, there is no standard metric to assess the quality of the results. Apart from limited research work that propose deterministic methods to find the optimal solution, for heuristic methods, no solid proof is given to validate the quality of the found solutions. In this thesis, we present a synthetic test bench that can be used as a starting point to allow the comparison of various partitioning algorithms.

The synthetic test bench for the comparison of partitioning algorithms and a strategy to estimate the quality of the found solutions is discussed in Chapter 5.

#### **1.3 Dissertation Contributions**

The focus of this dissertation is on memory access profiling and application partitioning. In these areas of research, we have made the following contributions.

# Contribution 1 – An efficient memory access profiling framework that enables the extraction of detailed quantitative information from applications.

We develop a set of memory access profiling tools, which are based on the Dynamic Binary Instrumentation (DBI) mechanism to inspect the behaviour of an application. We introduce the Quantitative Data Usage (QDU) graph as the primary output of the toolset. It not only reveals the actual data dependencies between the functions of the application, but also provides profiling data which quantifies the data communication between those functions. The information measured by this toolset is quite accurate and verified in several cases where real applications are used. Moreover, the framework is designed in a structured way to make further improvements simple and straightforward. We show how the extracted profiling information can be used in different aspects, including source code optimizations and function merging, among others.

#### Contribution 2 — The runtime extraction of the relative timing information enables the identification of different execution phases in an application.

Although not in the primary focus of the profiling framework, the developed toolset allows the extraction of the relative temporal information during the execution of an application. This information improves the perception of the user in the sense that he can inspect at what time a particular memory access behaviour occurs in the application, or how the data communication between functions proceeds over time. Furthermore, the extracted temporal information can be utilized to give an account of the memory bandwidth requirements of the application during its execution. This is of particular importance in exploring task mapping and scheduling opportunities in multicore systems. However, in this work, we do not investigate these issues, instead we only use the temporal information to identify different phases in the application.

# Contribution 3 – A heuristic solution for the general application partitioning problem with a customizable objective function.

The extracted information regarding the actual data dependencies in an application along with additional quantitative profiles can be beneficial for a number of purposes. Data dependency detection triggers parallelism exploitation, which, in turn, initiates the concept of application partitioning. In our work, we first formulate the application partitioning problem in a general and flexible way, and then propose a heuristic approach to solve the problem. Although the proposed approach may not eventually converge to the optimal solution — as non-heuristic approaches would inherently do - the intractability nature of the problem puts our approach on the plus side for large problem sizes.

Contribution 4 – An elaborate validation of the quality of the solutions provided by the partitioning algorithm through an exhaustive search of the solution space.

In case a heuristic algorithm is proposed to address an optimization problem, it would be assumed a severe flaw if we cannot assess the quality of the found solutions. This is because there is no guarantee that the optimal solution is found. Thus, one should not only care about finding a solution which meets the defined constraints, but also should set the criteria to estimate the value of the found solution among all possible solutions. As such, the first step involves defining the metric against which the quality of the found solution is examined. For this purpose, we present a complete theoretical analysis of an exhaustive solution search for the proposed partitioning model. Subsequently, we perform extensive simulations — using synthetically generated input data — to investigate the actual standing position of the heuristically-found solution against all the possible solutions. This, undoubtedly, represents the best quality assessment for such a partitioning algorithm. The simulation results show that, for the majority of cases, the found solutions stand in acceptable positions in the solution space to be considered as near-optimal ones.

# Contribution 5 – Two case studies, where the memory access profiling toolset is utilized to analyze and partition an application.

In order to evaluate the practical usage of the developed profiling framework, we present two case studies regarding application analysis and partitioning. The first application is a well-known edge detection algorithm from the domain of image processing. The second application is an advanced voice codec featuring good voice quality even at extremely low bit rates. Based on the extracted profiling information, we proposed a hardware/software partitioning methodology to formulate the application mapping procedure. This information is used to guide merging relevant tasks of each application together, while ensuring the feasibility of porting the application to the target platform at hand.

### 1.4 Dissertation Organization

The remainder of this dissertation is organized in several chapters. First, we present an overview of application profiling in Chapter 2. Then, in Chapter 3, we describe the developed profiling framework and further detail the dynamic memory access profiling toolset. After that, we describe the extraction of timing information during the runtime of an application in Chapter 4. Subsequently, we discuss in detail the problem of application partitioning in Chapter 5. Chapter 6 presents two detailed case studies where the profiling framework is validated in practice. Finally, we conclude this dissertation in Chapter 7.

A visual outline of this dissertation is depicted in Figure 1.1. This figure concisely presents the relation between different chapters, the research challenges, and the con-

**Figure 1.1:** An outline of the different chapters, challenges, and contributions in this dissertation. Chapter 2 presents only some background materials. Chapter 3 and Chapter 4 are both related to the development of the dynamic memory access profiling framework. While Chapter 5 deals with theoretical analysis of the application partitioning problem, Chapter 6 focuses only on the practical aspect of partitioning in reconfigurable systems. The dashed lines indicate the possibility of skipping intermediate chapter(s), as it will not interfere with understanding the contents.

tributions of this work. In the following, we present a brief summary of each chapter.

#### Chapter 2 – Profiling

In Chapter 2, we start by describing the concept of profiling an application and discuss how profiling helps to analyse the behaviour of the application. We set out stressing the importance of such analysis in understanding the behaviour of applications, which, in turn, is of great value to application developers and computer architects. Profiling tools are a necessity to evaluate how well applications perform on different platforms as well as to identify the critical parts which pose potential bottlenecks for the performance of a system. Additionally, we explain the idea of application tracing in contrast to profiling and how their objectives differ in the context of application analysis. Furthermore, we describe the different aspects in which profiling can be useful. Subsequently, we list different types of data structures that are used in various profiling and tracing techniques. The choice of proper data structures has crucial effect on the performance of profilers as well as on the execution time of the profiled application itself. We describe the two main categories of profiling, namely the static analysis and the dynamic analysis. From a different perspective, we subsequently discuss the differences

between software and hardware profiling. In particular, we concisely explore different instrumentation techniques. The chapter also provides a brief account of several existing profiling tools used in analysing applications.

#### **Chapter 3** – Dynamic Profiling Framework

The *QUAD* memory access profiling toolset is introduced in Chapter 3. In this chapter, we first present the project context of our work, focusing on the Molen Abstraction Layer (MAL), the *Delft Workbench* tool platform, and the  $Q^2$  profiling framework. The chapter continues with a detailed description of the development issues in the dynamic part of the profiling framework. In particular, we elaborate on the description of the *Pin* DBI framework, and the implementation of the *QUAD*-core tool, the Memory Access Tracing (MAT) module, Memory Access Intensity Profiler (*MAIP*), and the *xQUAD* tool. Furthermore, using the profiling information extracted by *MAIP*, we set out to estimate the time spent on memory operations in distinction of the time spent on computations. Based on this estimation, we propose a ranking strategy that provides a preliminary assessment of the criticality of a function regarding its memory access intensity. In order to demonstrate how the profiling information can be interpreted and used in different aspects, we investigate three real-world applications as case studies. For each application, we highlight some major observations followed by detailed comments.

#### Chapter 4 – Temporal Memory Bandwidth Analysis

Chapter 4 presents the tQUAD tool as an extension to the QUAD toolset. It enables QUAD to extract relative timing information from an application during its execution. This is of critical significance, particularly with respect to task scheduling and mapping in heterogeneous multicore systems. The original QUAD-core tool provides no track of temporal information, mainly because of the high instrumentation overhead. The tQUAD tool collects the relative timing profiles as an indication of the progress of the application. We present a concise overview of how this functionality is implemented in tQUAD. In the presence of the memory access data, the extracted temporal profiles by tQUAD give an account of the memory bandwidth usage of the functions in an application over time. Additionally, we utilize the extracted temporal information to discover the different phases of an application. The chapter ends with a detailed case study of a real application to demonstrate the potential and the applicability of tQUAD in practice. It should be stressed that the extracted timing profiles primarily target temporal task partitioning, in contrast to the spatial task partitioning, which does not fit within the scope of this thesis. Thus, the extracted timing information is not used in subsequent chapters. Nevertheless, one may opt to utilize this extra information as hints for identifying related functions in task clustering.

#### Chapter 5 – Task Clustering: A Greedy Approach

The focus of Chapter 5 is on the problem of the coarse-grained application partitioning in its general sense. We present a detailed investigation into the factors that characterize a partitioning scheme and the methods that are utilized to perform partitioning. In addition to a comprehensive formulation of the general application partitioning problem, we propose a heuristic approach to tackle this intractable problem with the aim of working out a near-optimal (or optimal) solution in a feasible amount of time. The proposed partitioning approach utilizes a greedy strategy with the primary objective of minimizing (and maximizing) the inter-cluster (intra-cluster) data communication, and the uniformity of the processing workload. An application partitioning algorithm is susceptible to failure without a proper input model to fully capture the data transfers in the application. To address this critical issue, we utilize the QDU graph to drive the partitioning procedure. Furthermore, we provide a detailed complexity analysis of the proposed partitioning algorithm, both in terms of time and space. We also present a thorough analysis of the application partitioning problem from a combinatorial mathematics perspective. This is required to conduct an exhaustive search of the solution space in order to have a strictly accurate assessment of how close we can get to the optimal solution. The chapter concludes with experimental results for a real-world application as well as for synthetic data in comparison with the optimal solution.

#### Chapter 6 – Utilizing Q<sup>2</sup> in HW/SW Partitioning: Case Studies

We demonstrate how the dynamic profiling framework can be applied in real scenarios by investigating two realistic cases in Chapter 6. For this purpose, we propose the Q<sup>2</sup> partitioning methodology which divides an application into hardware and software parts. We evaluate the Canny Edge Detection (CED) application, a well-known edge detection algorithm, and the Mixed Excitation Linear Prediction (MELP) application, a high-grade voice coder targeting very low bit rates. Both applications are mapped onto the Molen heterogeneous platform. To this purpose, an elaborate analysis of each application is performed beforehand. During the analysis phase, memory access profiling information provided by *QUAD* is utilized for source code modifications and optimizations. We employ the QDU graph as the main reference to analyse the data transfers between functions, find memory bottlenecks and deficiencies, and spot opportunities to merge functions.

#### Chapter 7 – Conclusions

In Chapter 7, a summary of the work in this dissertation is presented. Several conclusions with respect to the contributions anticipated in the introduction are drawn. Subsequently, the chapter lists several open issues and opportunities for future research.

Although the authors have made an attempt to document in this dissertation the work that has been carried out in the context of this research, it simply cannot be fully representative of what has been done. It is our sincere hope that an enthusiastic reader refer to the accompanying source code, which is — with no doubt — an inseparable part of this work. As Jeff Atwood perfectly puts it in a post at *Coding Horror*: **no matter what the documentation says, the source code is the ultimate truth, the best and most definitive and up-to-date documentation you're likely to find!<sup>4</sup>**

<sup>&</sup>lt;sup>4</sup> Learn to Read the Source, Luke, Jeff Atwood, April 16, 2012.

# CHAPTER **2**

# Profiling

"Indeed, researchers love to find problems to work on." †

- Dennis M. Ritchie