# Qucs-0.0.19S: a new open-source circuit simulator and its application for hardware design

Mike Brinson Centre for Communications Technology,

London Metropolitan University, UK, e-mail: mbrin72043@yahoo.co.uk

<sup>2</sup> and control equipment hardware design tasks. This article intro- 46 which is distributed with mature GUI and modelling tools. <sup>2</sup> duces an extended version of the popular Ques circuit simulator 47 Evaluation of GPL SPICE simulators, plus feedback from 12 implementation details and application cases are considered.

13 14 circuit simulation, EDA

### I. INTRODUCTION

15

16 17 terprise information technology. However, not all sectors have 60 eliminated, making Ques-0.0.19S, a viable choice for research 18 a fully developed software base. One example is electronic de- 61 and industrial circuit design [9], [10]. <sup>19</sup> sign automation (EDA) where General Public Licence (GPL) <sup>20</sup> circuit simulation and printed circuit board layout packages are <sup>62</sup> II. AN OVERVIEW OF QUCS-0.0.19S COMPONENT MODELS 21 undergoing rapid development. The "Quite universal circuit 63 The Spice4ques subsystem is designed for the simulation 22 simulator" (Ques) [1], [2] is one of a new breed of GPL circuit 64 of Ques circuit schematics with Ngspice or Xyce launched 23 simulators. Ques was started by M. Margraf and S. Jahn in 65 as external simulation engines [11]. In general legacy Ques 24 2001. The initial intention was that Ques should be an RF 66 circuit doesn't require tweaking to simulate it with Ques-25 circuit analysis package which offered features not found in 67 0.0.19S. Ques legacy passive components can be simulated 26 SPICE. Recently a new team took over responsible for Qucs 68 with Qucs-0.0.19S. In addition Qucs-0.0.19S introduces a 27 development.

28 29 Linux, Windows © and MacOS © . It includes a simulation 71 Similar to passive components active device models have a 30 kernel called Quesator. Although Quesator has acceptable 72 fixed list of named parameters [1], [12]. Moreover, some of 31 performance it is not fully compatible with SPICE 2g6 or 3f5 73 these are SPICE incompatible. Qucs-0.0.19S allows users to 32 [3], [4]. Ques has a unique netlist syntax and model format 74 construct SPICE device definitions from a name, a model spec-33 with SPICE support implemented via a software compatibility 75 ifier and a SPICE style "modelcard". These can be attached 34 layer. It does not allow direct access to manufacturers SPICE 76 to a schematic symbol and passed directly to a SPICE kernel. 35 models and libraries. The compatibility layer also prohibits 77 Qucs-0.0.19S subcircuit and library components form part 36 access to a number of SPICE built in models, simulation 78 of a file component subclass. These allow the construction of 37 types and the Nutmeg scripting language. A "Spice4qucs" 79 more complex components from pre-defined model primitives 38 subsystem has been added to Ques to form Ques-0.0.19S 80 and manufactures models. Ques-0.0.19S allows users access 39 [5], and hence overcome these limitations. Qucs-0.0.19S was 81 to the following types of file component: <sup>40</sup> presented during MOS-AK workshop at Graz, Austria [6]. 82 Spice4qucs is not another SPICE simulation kernel but 83

42 acts as an interface to a number of established GPL SPICE 84 43 engines. These have excellent performance, but usually lack 85 44 a graphical user interface (GUI) for schematic capture and 86

Vadim Kuznetsov Department of Electronic Engineering, Bauman Moscow State Technical University, Kaluga branch, Russia; e-mail: ra3xdh@gmail.com

Abstract—Circuit simulation is widely used in communication 45 external simulator launch control. The reverse is true for Ques

4 called Ques-0.0.19S. It is a simulation tool which supports 5 multiple SPICE circuit simulators, including Ngspice and Xyce. 48 Ques users, suggested; (a) Ques should support several SPICE 6 The package includes a graphical user interface, component and 49 GPL kernels, (b) Ques should not simple be a schematic 7 compact device modelling tools, a choice of simulation engine, 50 capture and simulation software package but must also offer and advanced simulation data postprocessing facilities. It allows 51 advanced data processing features, and (c) provide a range <sup>9</sup> user to construct new component using XSPICE extension and <sup>10</sup> construct new simulations using Nutmeg scripting. Ques-0.0.198 to the Ngspice [7] and XVCE [8] SPICE simulators. More 11 is targeted at academic and industrial applications. Software 53 the Ngspice [7] and XYCE [8] SPICE simulators. More-54 over, Spice4qucs is able to launch both simulators from the Index Terms-Ques, SPICE, Ngspice, Xyce, Nutmeg scripting, 55 Ques GUI. Quesator has excellent small signal AC and S-56 parameter simulation performance. But Quesator time-domain 57 simulation is not that stable. In particular, Quesator cannot 58 reliably simulate switching circuits. The addition of SPICE Open source software offers access and cost benefits to en- 59 based simulation to Ques allows this limitation to be largely

69 group of passive component models with SPICE format. Ques Qucs-0.0.19S is a freely available package with versions for 70 legacy semiconductor device models are SPICE incompatible.

> 1) Subcircuits, for the construction of new components from predefined components. This form of subcircuit is identical to the original Ques implementation [12], except that each subcircuit is stored as a .SUBCKT netlist;

- 2) SPICE file components, for attaching SPICE .SUBCKTs

- to a circuit schematic. This component allows to pass

unmodified SPICE netlist directly to simulator. Netlist

- <sup>90</sup> is stored in a separate file;

- 91 3) *Library components*, for the storage and recall of 92 previously defined component and device models.

- previously defined component and device models.

Qucs/Qucs-0.0.19S libraries are encoded in text XML

- format Library on store anne difad CDICE and

- <sup>94</sup> format. Library can store unmodified SPICE code.

## 95 III. THE OPERATION PRINCIPLES OF MULTI-SIMULATOR 96 SUPPORT IN QUCS-0.0.19S

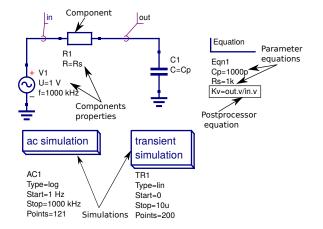

<sup>97</sup> Algorithm 1 outlines the Ques netlist building method. <sup>98</sup> Quesator does not use netlist sections [12]. A Ques schematic <sup>99</sup> is represented as a C++ class, consisting of a set of netlist pro-<sup>100</sup> cessing methods. A single method scans a schematic file in one <sup>101</sup> pass and outputs information describing located components.

Algorithm 1:

end

end of .control section

end

end

The Ques netlist for the RC network is:

| Algorithm 1.                                                  | _115 The Ques netlist for the RC network is:                            |

|---------------------------------------------------------------|-------------------------------------------------------------------------|

| Data: Ques Schematic                                          | 116                                                                     |

| Data: Ques netlist filename                                   | 117 # Ques 0.0.19 RC1.sch                                               |

| Result: Qucs netlist                                          | 118 Vac: V1 in gnd U="1 V" f="1000 kHz"                                 |

| 102 begin                                                     | 119 R:R1 in out R="Rs"                                                  |

| <b>foreach</b> (Component in Schematic) <b>do</b>             | 120 C:Cl gnd out C="Cp"                                                 |

| $ $ Netlist $\leftarrow$ Component.getQucsNetlist()           | 121 Eqn: Eqn1 Cp="1000p" Rs="1k"                                        |

| end                                                           | 122 Kv="out.v/in.v" Export="yes"                                        |

| end                                                           | 123 .AC: AC1 Type="log" Start="1 Hz"                                    |

|                                                               | -124 Stop="1000 kHz" Points="121" Noise="no"                            |

| <sup>103</sup> In contrast, SPICE netlists consist of separat | Cit25 TR·TR1 Type="lin" Start="0"                                       |

| , I                                                           | $d_{123}^{223}$ Stop="10u" Points="200"                                 |

|                                                               |                                                                         |

| 105 component specifications. Hence, building a SPICI         |                                                                         |

|                                                               | 128 The Ngspice netlist for the RU network is                           |

| 106 netlist requires a multiple pass method, see Algorithm 2  |                                                                         |

| Algorithm 2:                                                  | -130 * Ques 0.0.19 RC1.sch                                              |

| 0                                                             | 131 * Parameters section                                                |

| Data: Ques Schematic                                          | 132 .PARAM $Cp = \{1000p\}$                                             |

| Data: SPICE netlist filename                                  | 133 .PARAM $Rs = \{1k\}$                                                |

| Result: SPICE netlist                                         | 134 * Components section                                                |

| begin                                                         | 135 V1 in 0 DC 0 SIN(0 1 1000K 0 0) AC 1                                |

| foreach (Component in Schematic) do                           | 136 R1 in out {RS}                                                      |

| if (Component is Parameter or directive) then                 | 137 C1 0 out {CP}                                                       |

| Netlist ← Component.getSpiceExpression()                      | 138 * Simulations execution section                                     |

| end                                                           | 139 . control                                                           |

| end                                                           | 140 AC DEC 21 1 1000K                                                   |

| foreach (Component in Schematic) do                           | 141 let Kv=V(out)/V(in)                                                 |

| if (Component is Device) then                                 | 142 * Write result to text file                                         |

| $Netlist \leftarrow Component.getSpiceNetlist()$              | 143 write RC1_ac.txt v(in) v(out) Kv                                    |

| end                                                           | 144 TRAN $5e - 08$ $1e - 05$ 0                                          |

| end                                                           | 145 * Write result to text file                                         |

| 107 // begin of .control section                              | 146 write RC1_tran.txt v(in) v(out)                                     |

| foreach (Component in Schematic) do                           | 147 exit                                                                |

| if (Component is Simulation) then                             | 148 . endc                                                              |

| Netlist $\leftarrow$ Component.getBeforeSimScript()           | 149 * Netlist ends here                                                 |

| Netlist $\leftarrow$ Component.getSpiceNetlist()              | 159 .END                                                                |

| Netlist $\leftarrow$ Component.getAfterSimScript()            |                                                                         |

| foreach (Component in Schematic) do                           | <sup>152</sup> Ques output data are translated into an XML dataset when |

| // find equations attached to simulation                      |                                                                         |

| if (Component is Equation) then                               | 153 simulation finishes. The Ngspice netlist format is very close       |

| Netlist $\leftarrow$ Component.getEquation()                  | 154 to an imperative programming language, with .PARAM di-              |

| end                                                           |                                                                         |

| end                                                           | 155 rectives in proper order for error free evaluation. At the          |

|                                                               | 1 1                                                                     |

<sup>154</sup> to an imperative programming language, with .PARAM di-<sup>155</sup> rectives in proper order for error free evaluation. At the <sup>156</sup> end of a Ngspice netlist is a.control ... .endc group. <sup>157</sup> This group contains a Ngnutmeg post-processor script that <sup>158</sup> is executed after a netlist is scanned by Ngspice. During

A Ques schematic consists of a group of components where 159 scanning, simulation and post-processor directives are placed 109 every item has a properties list. For example, let's consider an 160 between the control words .control ... .endc. The 110 RC-network schematic (see Figure 1). Ques simulation icons 161 .control ... .ende group also supports Ngnutmeg file 111 and equations are considered to be a special forms of compo-162 write directives for storing simulation datasets. Ngspice 112 nent. The Ques netlist has declarative format. During scanning 163 datasets are written in the SPICE-3f5 raw-ASCII format which 113 Quesator automatically separates components, equations, and 164 in turn are converted and saved by Ques-0.0.19S as part of a 114 simulator directives. The order has no effect on the final result.165 Ques XML dataset. <sup>166</sup> With Xyce multiple simulations are not supported. The <sup>167</sup> Xyce netlist has the following format:

| 168<br>169 | * Qucs 0.0.19 RC1.sch                                 |

|------------|-------------------------------------------------------|

| 170        | .PARAM $Cp = \{1000p\}$                               |

| 171        | .PARAM $Rs = \{1k\}$                                  |

| 172        | V1 in 0 DC 0 SIN(0 1 1000K 0 0) AC 1                  |

| 173        | R1 in out {RS}                                        |

|            | C1 0 out {CP}                                         |

| 175        | .TRAN $5e - 08$ $1e - 05$ 0                           |

|            | .PRINT tran format=raw file=RC1_tran.txt v(in) v(out) |

| 178        | . END                                                 |

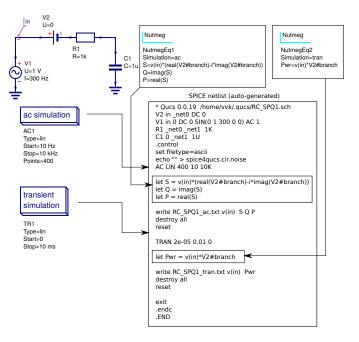

Spice4ques operates at GUI level in distinct steps; netlist

building followed by simulation and finally it uses a rawASCII output data parser to generate a Ques XML dataset.

All schematic symbols have an XML representation which is

written to memory during schematic file loading.

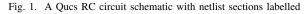

As the Xyce simulator does not include a data postprocessor the netlist building algorithm for Xyce is much

simpler, see Algorithm 3.

<sup>187</sup> The block diagram drawn in Figure 2 illustrates the in-<sup>188</sup> teraction between schematic capture, simulation and data <sup>189</sup> visualization for all used simulation backends.

A number of the SPICE simulation types generate Qucs

incompatible output datasets, implying that they require unique

custom parsers. The parsers implemented in the current ver-

Qucs GUI External simulation kernels Schematic Ngspice dialect Naspice Component 1 Component 2 SPICE Xyce Component 3 netlist dialect Xyce Oucs netlist Oucsator Component N Qucs XML dataset Oucs Data Oucs XML visualization dataset system raw-SPICE3f5 SPICE dataset dataset to Oucs dataset converter

Fig. 2. Spice4qucs subsystem dataflow block diagram

<sup>193</sup> sion of Qucs-0.0.19S are for SPICE-3f5 raw-ASCII (AC,<sup>214</sup> to determine, apparent, active and reactive power, given by <sup>194</sup> DC, TRAN, and Parameter sweep simulation), Fourier sim-<sup>215</sup>  $S = |U \cdot \bar{I}|, P = \Re[U \cdot \bar{I}], Q = \Im[U \cdot \bar{I}]$ , respectively. <sup>195</sup> ulation, noise simulation and HB simulation (XYCE only).<sup>216</sup> Similarly, real power can be calculated from transient data, <sup>196</sup> The Spice4qucs subsystem extracts output data from each<sup>217</sup> using  $P(t) = u(t) \cdot i(t)$ .

<sup>197</sup> simulation request and combines them into single Qucs XML<sup>198</sup> dataset ready for processing by the Qucs data visualization<sup>199</sup> system.

#### IV. QUCS-0.0.19S SIMULATIONS

20

202 A. Common simulations and simulation data postprocessing

The following simulation types are implemented .DC, .AC, 204 .TRAN, .FOUR, .DISTO, .NOISE, and a new "Ngspice Cus-205 tom" form. XYCE backend supports single-tone and multitone 206 Harmonic Balance simulation. Ques allows to get access to 207 these simulations from the GUI.

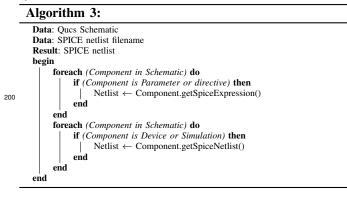

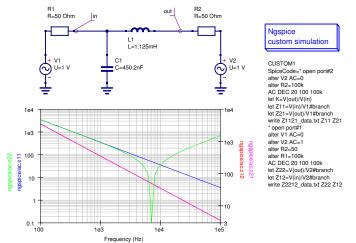

Fig. 3. An example of Nutmeg post-processor equation usage

<sup>208</sup> The Ques data post-processor has many SPICE incom-

209 patible functions. A way to overcome this is to pass post-218 B. Ngnutmeg scripting

<sup>210</sup> processor directives directly to Nutmeg via a new component<sup>219</sup> Qucs-0.0.19S has a powerful new feature, called "Ngspice <sup>211</sup> called "Nutmeg equation". Illustrated in Figure 3 is an RC<sup>220</sup> custom simulation", where a Nutmeg script is added to a Qucs <sup>212</sup> network driven by an AC source. This demonstrates how<sup>221</sup> schematic, allowing SPICE statements and Ngnutmeg scripts <sup>213</sup> .AC and .TRAN are defined and how "Nutmeg" can be used<sup>222</sup> to be passed directly to a SPICE netlist.

It allows to get easy access to all Ngnutmeg functions from 223 224 the GUI. It's able to construct nonstandard simulations using 225 Ngnutmeg scripting (for example scattering matrix and SWR 226 analysis, Monte-Carlo analysis).

For example, Z-parameter analysis is not available for the 227 228 most of SPICE-compatible simulators including proprietary 229 ones. But it could be easily constructed with Oucs-S. Ngspice, 230 and Nutmeg scripting. Figure 4 illustrates this approach for a 231 passive low-pass Butterworth LC-filter.

Fig. 4. Z-parameter extraction with Nutmeg scripting

233 current data form AC-simulation results and convert it into<sup>260</sup> circuit symbol (Figure 7). It's sufficient to specify location of 234 desired Z-parameter value.

#### V. XSPICE SUPPORT IN OUCS-S

235

236 237 circuit design tasks. It is especially important for commu-238 nication equipment. XSPICE introduces a set of additional 239 analog and mixed-signal models targeted on system-level 240 design. Ques-S with Ngspice backend supports a wide range<sup>267</sup> of XSPICE blocks. 241

- 242 <sup>242</sup> Ques-S out-of-box: gain block, integrator, differentiators, <sup>270</sup> a wide range of uncertained and a second s <sup>244</sup> adder, multiplier.

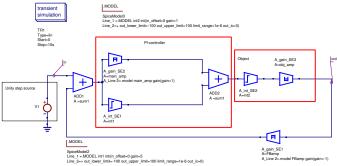

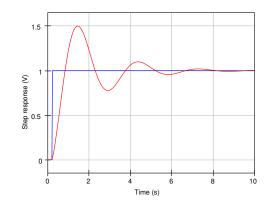

- These blocks allows simulate not only analog circuits, but<sup>272</sup> 246 also to solve control theory tasks. For example, PI-controller<sup>273</sup> Ques-S covers the following application areas: 245 274 <sup>247</sup> step response analysis is shown in the Figure 5.

This simulation uses XSPICE blocks (analog gain, integra-275 248 249 tor, and adder) to define PI-controller elements and transient<sup>276</sup> 277 250 simulation to obtain step response.

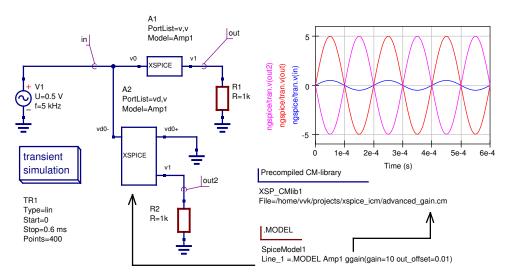

- It's able to construct a new XSPICE block using "XSPICE<sup>278</sup> 25 <sup>252</sup> generic device" component (Figure 7). It's sufficient to provide<sup>279</sup> 253 port list and modelcard reference to create new device. It's 280 254 able to attach user symbol to a new device using standard<sup>281</sup> 282 255 Ques subcircuit technique [12].

- XSPICE allows to develop new devices using CodeModel<sup>283</sup> 256 <sup>257</sup> technique [13]. User can compile a set of CodeModels in<sup>284</sup> 258 a single dynamic-loadable binary library. Now it's available 285 259 inclusion of precompiled CodeModel libraries using special286

Fig. 5. PI-controller analysis with XSPICE analog blocks

Fig. 6. Simulated step response of PI-controller

262 using user-defined XSPICE block and general modelcard.

Ques-S will allow to attach CodeModels to schematic and 263 XSPICE is SPICE-3f5 extension targeted on system-level<sup>264</sup> compile it automatically during netlist building. This feature is 265 under construction now and it will not be considered further.

#### VI. CONCLUSION

Qucs-0.0.19S is the first step in the development of an open-268 source circuit simulator that combines, and extends, the best The following XSPICE analog devices are presented in 269 features available with GPL circuit simulators. It can simulate 270 a wide range of different size circuits, including those designed

Qucs-0.0.19S allows switching of simulation backends.

- 1) Realistic analog circuit simulation in time domain with Ngspice backend. Full support of SPICE-3f5 standard allows to use wide range of component models provided by vendors:

- RF-circuits analysis (S,Z,Y-parameters matrix) using 2) Nutmeg scripting and Harmonic balance analysis with XYCE backend [14]. This application is not available for many other SPICE-compatible simulators;

- 3) Control theory applications using XSPICE analog blocks;

#### The main advantages of Oucs-0.0.19S are:

1) It's free and open-source. It allows users to easily modify sources and propose new features;

Fig. 7. User-defined XSPICE device construction

349

350

- 2) Switchable simulation backends allows user to select the 326 287 most suitable one for every simulation task; 327 288 328

- 3) Advanced postprocessing with Nutmeg Equations; 289

- 329 4) GUI allows to get access to unlimited features of Nut-330 290

- meg scripting. It allows user to construct new simulation<sup>331</sup> 291 332 types (for example RF simulation types) without modi-292 fication of Ques and simulator backends sources; 293 334

- 5) XSPICE allows system-level design. Also CodeModel<sup>335</sup> 294 technique allows to construct new XSPICE devices 337 295 without modification of simulator sources. 338 296

339 Considering all above, we can conclude that  $Qucs-0.0.19S_{340}$ 297 298 is not simple GUI for SPICE backends. It allows also ad-341 vanced features in simulation result postprocessing, circuit<sup>342</sup><sub>343</sub><sup>[10]</sup> 299 300 parametrization, and user devices and simulation definition. 344 301 And Oucs-0.0.19S could be recommended for communication<sup>345</sup> [11] 346 302 and control equipment equipment hardware design tasks. 347

#### REFERENCES

303

- [1] M. E. Brinson and S. Jahn, "Ques: A GPL software package for circuit<sup>352</sup> 304

- simulation, compact device modelling and circuit macromodelling<sup>353</sup> 305 from DC to RF and beyond," International Journal of Numerical<sup>354</sup> [14] 306 Modelling (IJNM): Electronic Networks, Devices and Fields, vol. 22,355 307 no. 4, pp. 297 - 319, September 2008. [Online]. Available: 308

- 309 http://www3.interscience.wiley.com/journal/121397825/abstract

- W. Grabinski, M. Brinson, P. Nenzi, F. Lannutti, N. Makris, [2] 310 A. Antonopoulos, and M. Bucher, "Open-source circuit simulation 311 tools for RF compact semiconductor device modelling," International 312 Journal of Numerical Modelling: Electronic Networks, Devices and 313 Fields, vol. 27, no. 5-6, pp. 761-779, 2014. [Online]. Available: 314 http://dx.doi.org/10.1002/jnm.1973 315

- A. Newton, D. O. Pederson, and A. Sangiovanni-Vincentelli, SPICE 316 [3] Version 2g User's Guide. Department of Electrical Engineering and 317 Computer Sciences, University of California, 1981. 318

- B. Johnson, T. Quarles, A. R. Newton, D. O. Pederson, and 319 [4] Sangiovanni-Vincentelli, SPICE3 Version 3f User's Manual. 320 partment of Electrical Engineering and Computer Sciences, University 321 of California, 1992. 322

- V. Kuznetsov. Unofficial build with spice4qucs features enabled. [5] 323 Release candidate 3. Ques project team. [Online]. Available: https: 324 //github.com/ra3xdh/qucs/releases/tag/0.0.19S-rc3 325

- [6] M. Brinson, R. Crozier, V. Kuznetsov, C. Novak, B. Roucaries, F. Schreuder, and G. B. Torri. Oucs: An introduction to the new simulation and compact device modelling features implemented in release 0.0.19/0.0.19Src2 of the popular GPL circuit simulator. MOS-AK Workshop, Graz. [Online]. Available: http://www.mos-ak.org/graz\_ 2015/presentations/T\_5\_Brinson\_MOS-AK\_Graz\_2015.pdf

- Ngspice: mixed-level/mixed-signal circuit simulator based on Berkeley's [7] Spice3f5. Ngspice project team. [accessed August 2015]. [Online]. Available: https://www.ngspice.org/

- [8] Xyce Parallel electronic simulator: version 6.2. Sandia National Laboratories. [accessed August 2015]. [Online]. Available: https: //xvce.sandia.gov/

- A. Zonca, B. Roucaries, B. Williams, I. Rubin, O. D'Arcangelo, P. Mein-[9] hold, P. Lubin, C. Franceschet, S. Jahn, A. Mennella, and M. Bersanelli, "Modeling the frequency response of microwave radiometers with QUCS," Journal Of Instrumentation, no. 5(12):T12001, November 2010.

- V. Kuznetsov and L. Kechiev, "Charged Board Model ESD Simulation for PCB Mounted MOS Transistors," Electromagnetic Compatibility, IEEE Transactions on, vol. 57, no. 5, pp. 947-954, 2015.

- M. Brinson and V. Kuznetsov. Spice4qucs-help documentation. User Manual and Reference Material. [Online]. Available: https: //qucs-help.readthedocs.org/en/spice4qucs

- 348 [12] S. Jahn, M. Margraf, V. Habchi, and R. Jacob, Ques. Technical papers. [Online]. Available: http://qucs.sourceforge.net/docs/technical/technical. pdf

- 351 [13] F. Cox III, W. Kuhn, J. Murray, and S. Tynor, "Code-level modeling in xspice," in Circuits and Systems, 1992. ISCAS '92. Proceedings., 1992 IEEE International Symposium on, vol. 2, May 1992, pp. 871-874 vol.2.

- M. Brinson and V. Kuznetsov, "Qucs equation-defined and Verilog-A RF device models for harmonic balance circuit simulation." in *Mixed Design* of Integrated Circuits Systems (MIXDES), 2015 22nd International Conference, June 2015, pp. 192-197.