## **Radio Frequency Digital to Analog Converter**

by

Susan Luschas

S.B., Massachusetts Institute of Technology (1997) M.Eng, Massachusetts Institute of Technology (1998)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

### at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY May 2003

© Massachusetts Institute of Technology, 2003. All Rights Reserved.

Author ..... Department of Electrical Engineering and Computer Science May 21, 2003

Certified by ... Hae-Seung Lee Professor of Electrical Engineering and Computer Science Thesis Supervisor

| Accepted by | 2                                              |

|-------------|------------------------------------------------|

|             | Arthur C. Smith                                |

| Cha         | man, Department Committee on Graduate Students |

| MASSACHUSETTS INSTITUTE<br>OF TECHNOLOGY |  |  |  |  |

|------------------------------------------|--|--|--|--|

| JUL 0 7 2003                             |  |  |  |  |

| LIBRARIES                                |  |  |  |  |

BARKER

#### A Radio Frequency Digital to Analog Converter

by

Susan Luschas

Submitted to the Department of Electrical Engineering and Computer Science on May 19, 2003, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

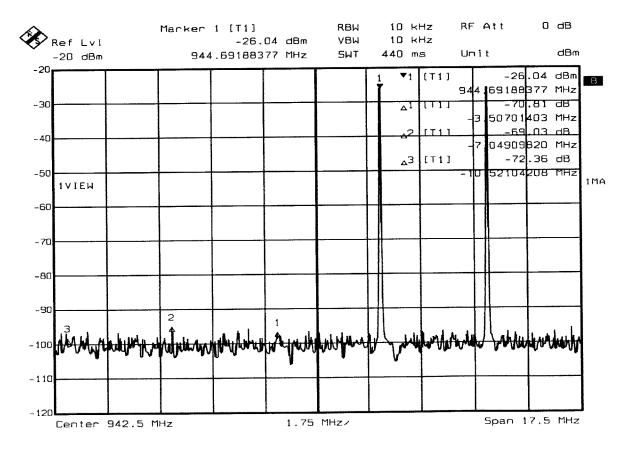

Dynamic performance of high speed, high resolution digital-to-analog converters (DACs) is limited by distortion at the data switching instants. Inter-symbol interference (ISI), imperfect timing synchronization and clock jitter are all culprits. A DAC output current controlled by an oscillating waveform is proposed to mitigate the effects of the switching distortion. The oscillating waveform should be a multiple  $(k^*f_s)$  of the sampling frequency  $(f_{o})$ , where k>1. The waveforms can be aligned so that the data switching occurs in the zero regions of the oscillating output. This makes the DAC insensitive to switch dynamics and jitter. The architecture has the additional benefit of mixing the DAC impulse response energy to a higher frequency. An image of a low IF input signal can therefore be output directly at a high IF or RF frequency for transmit communications applications. A narrowband sigma-delta DAC with eight unit elements is chosen to demonstrate the radio frequency digital-to-analog converter (RF DAC) concept. A sigma-delta architecture allows the current source transistors to be smaller since mismatch shaping is employed. Smaller current source transistors have a lower drain capacitance, allowing large high frequency output impedance to be achieved without an extra cascode transistor. Elimination of the cascode reduces transistor headroom requirements and allows the DAC to be built with a 1.8V supply. The RF DAC prototype is targeted to GSM transmit specifications and implemented in 0.18µm CMOS technology. Measured single-tone SFDR is -75dBc, SNR is 52dB, and IMD3 is -70.8dBc over a 17.5MHz bandwidth centered at 942.5MHz. Measured SNR has the predicted dependence on the phase alignment of the data clock and oscillating pulse.

Thesis Supervisor: Hae-Seung Lee Title: Professor of Electrical Engineering and Computer Science

## Acknowledgements

I would like to thank Professor Hae-Seung Lee for supervising this thesis. His advising style has allowed me the opportunity to direct the course of my research. This freedom has proved invaluable to my personal and professional growth. The no-strings funding support of NDSEG DOD Fellowship, Lucent Technologies GRPW, ABB Corp, National Semiconductor Corporation, Analog Devices, and the MIT Center for Integrated Circuits and Systems is gratefully acknowledged.

Many thanks are also due to Dr. Richard Schreier and the wonderful folks at Analog Devices for their technical support and guidance. My team of advisors consisted of Richard Schreier, Doug Mercer, Dr. Jennifer Lloyd, Dr. Bill Schofield, Larry Singer, and Dr. Steve Decker. Mark Robinson and Jack Moran helped with the layout tools, and Justin Munson, Salina Downing, and Rodney Kranz helped me get oriented in the lab. Thanks are also due to Greg Poehrl from Coilcraft for the awesome high-frequency transformers.

Thanks are also due to Kent Lundberg, who TAed me patiently through the 6.301, 6.302, 6.331 series. Kent's commitment and ability to teach will have a lasting effect on myself and many others. To Akin Aina, my buddy who laughed and cried with me through the Ph.D. and analog process - you're the best! Thanks to Professor Charlie Sodini for supervising my masters thesis, and providing encouragement throughout my PhD. To Professor Jesus del Alamo, thank you for allowing me the opportunity to be on the 6.012 staff and improve my teaching skills. The 6.012 students in my section should also be recognized for being patient with my sometimes under-prepared and buggy tutorials. The students on Burton 2 and Simmons West Tower ensured that I stayed flexible throughout my graduate career.

The women of GW6, GWG, D@MIT, and the club hockey team are wonderful colleagues. Thanks to all of you ladies for the years of support! Although not an inclusive list: Tamara Williams, Robbin Chapman, Blanche Staton, Lynne Roberson, Marilyn Pierce, Peggy Carney, Mary Krasovec, Aimee Smith, Julie Kiang, Olivera Kesler, Brenda MacLeod, Iliana Fujimori-Chen, Aurelie Thiele, Dawn Ostenberg, Emily Nelson, Christine Alvarado and Heather Gunther (my triathalon partners), and Michelle Bonugli, my adventure race partner. Thanks are also due to my fellow office mates at MIT for making sure I played enough hockey: Dan McMahill, Don Hitko, Mark Spaeth, Ayman Shabra, Pablo Acosta, Ginger Wang. Thanks to Don, Dan and Mark for technical suggestions about the development of this project. Laura Lemieux and Carolyn Collins also provided essential support over the years.

Last but not least, I would like to give credit to my family for their support and understanding. Thanks mom, for sharing all of the ups and downs with me. Dad, Jeannie and Liver Lizzy for making sure I took a few days off for Thanksgiving every year. My husband, Manuel for his encouragement and full support over the years. I never would have finished this semester had it not been for him taking over all of the work at home, helping with the figures and formatting of this thesis, and understanding when I come home late at night and leave first thing in the morning.

# **Table of Contents**

| 1 | Intro | luction                                               | 8   |

|---|-------|-------------------------------------------------------|-----|

|   | 1.1   | State-of-the-art High-Speed ADCs                      | 10  |

|   | 1.2   | State-of-the-art High-Speed DACs                      | .12 |

|   | 1.3   | Jitter Limits in Converters                           | 13  |

|   |       |                                                       |     |

| 2 |       | AC Concept                                            |     |

|   | 2.1   | Background                                            |     |

|   | 2.2   | RF DAC Description                                    |     |

|   |       | 2.2.1 RF DAC Advantages                               |     |

|   |       | 2.2.2 RF DAC Disadvantages                            | .21 |

|   |       |                                                       |     |

| 3 | Sourc | ces of Error in RF DAC                                |     |

|   | 3.1   | Ideal Locking                                         |     |

|   | 3.2   | Locking Error                                         |     |

|   |       | 3.2.1 Static Offset                                   | .26 |

|   |       | 3.2.1 Dynamic Offset                                  |     |

|   | 3.3   | Phase and Amplitude Noise in the Oscillating Waveform |     |

|   |       | 3.3.1 Phase Noise                                     |     |

|   |       | 3.3.1.1 Intuitive Analysis                            |     |

|   |       | 3.3.1.2 Analytical Analysis                           | .32 |

|   |       | 3.3.2 Amplitude Noise                                 | .35 |

|   | 3.4   | Multiple pulses per sampling period                   | .37 |

| 4 | Proto | type Design                                           | 39  |

| • | 4.1   | System specifications                                 |     |

|   | 4.2   | RF DAC Architecture                                   |     |

|   | 1.2   | 4.2.1 $\Sigma\Delta$ DACs and Mismatch Shaping        |     |

|   |       | 4.2.2 Nyquist vs. $\Sigma\Delta$ DAC                  |     |

|   |       | 4.2.3 Frequency Planning                              |     |

|   |       | $4.2.4 \Sigma\Delta$ Design Space                     |     |

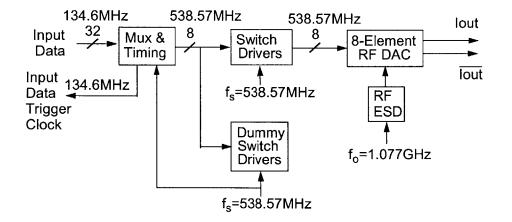

|   |       | 4.2.5 System Block Diagram                            |     |

|   | 4.3   | Output Impedance for DACs                             |     |

|   |       | 4.3.1 Static Performance Specifications               |     |

|   |       | 4.3.2 Dynamic Performance Specifications              |     |

|   |       | 4.3.3 Elimination of the Cascode Transistor           |     |

|   | 4.4   | Circuit Design                                        | .58 |

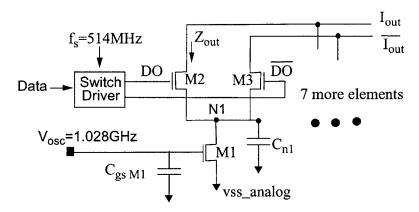

|   |       | 4.4.1 Unit Elements                                   |     |

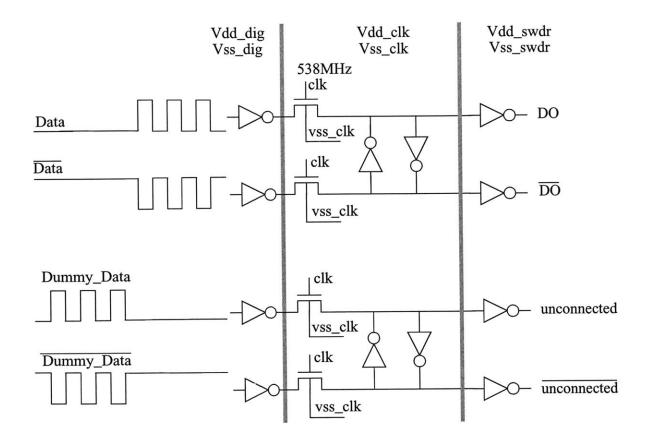

|   |       | 4.4.2 Switch Drivers                                  |     |

|   |       | 4.4.3 Analog DAC Core Summary and Simulations         |     |

|   |       | 4.4.4 Timing Circuits and Multiplexer                 |     |

|   |       | 4.4.5 Dummy Data Generation                           |     |

|   |       | 4.4.6 High Frequency Electrostatic Discharge (ESD)    |     |

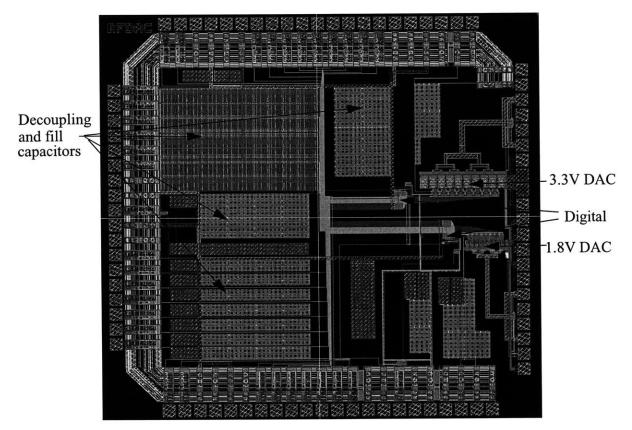

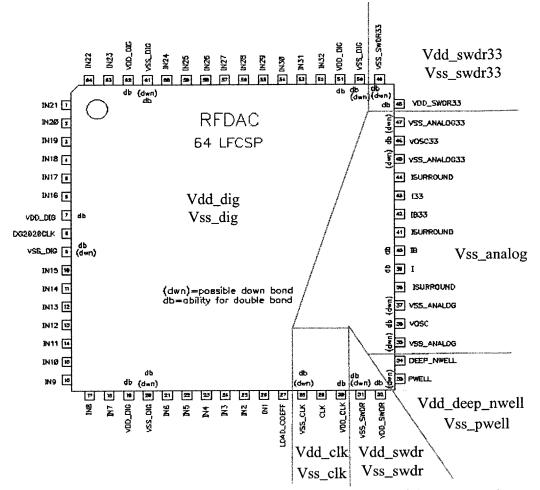

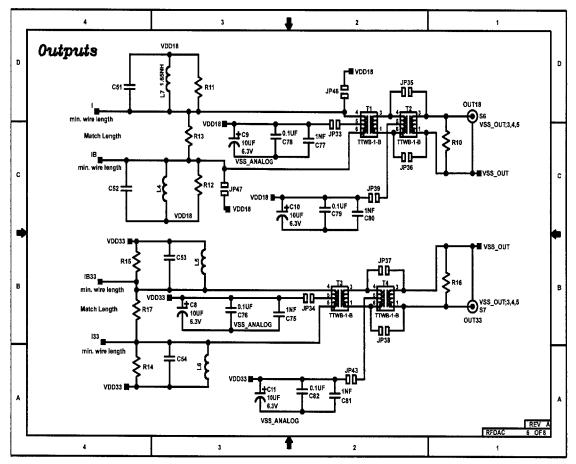

| 4.5     | Layout                                                | 75  |

|---------|-------------------------------------------------------|-----|

| 4.5     | Board Design                                          | 79  |

| 5.24    | next Deve 14                                          | 82  |

|         | surement Results                                      |     |

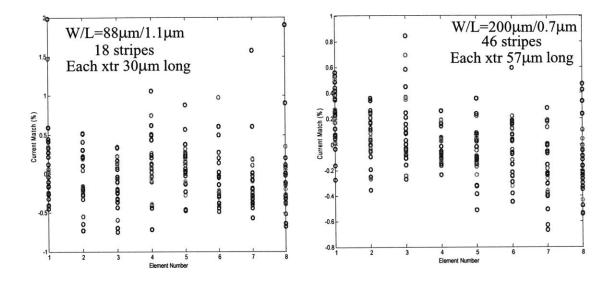

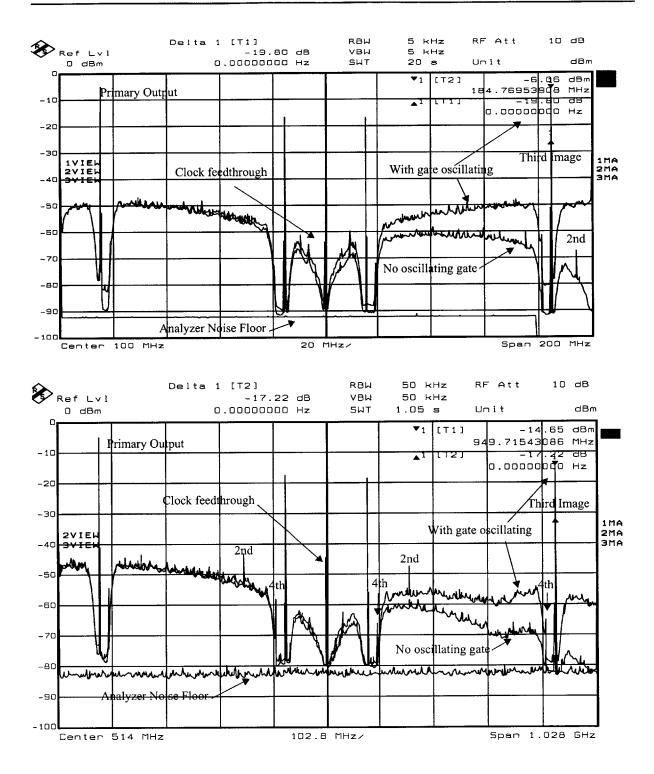

| 5.1     | DC Results                                            |     |

|         | 5.1.1 Repeatability                                   |     |

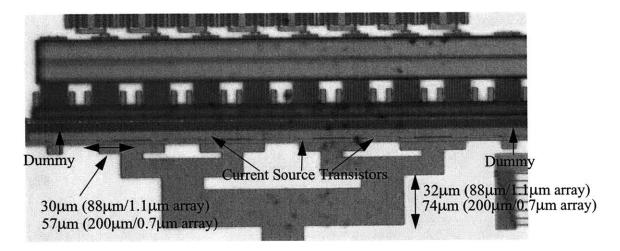

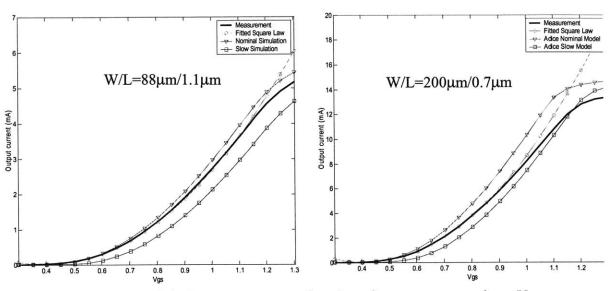

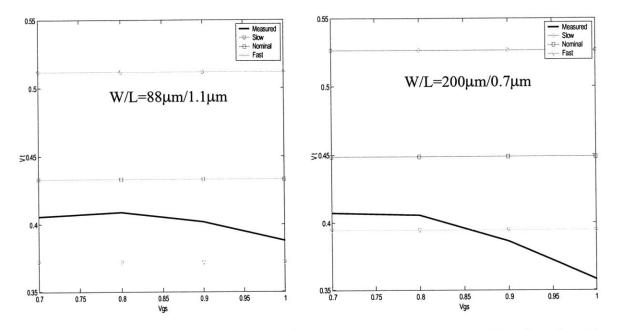

|         | 5.1.2 Transistor Transfer Characteristics (I vs. Vgs) |     |

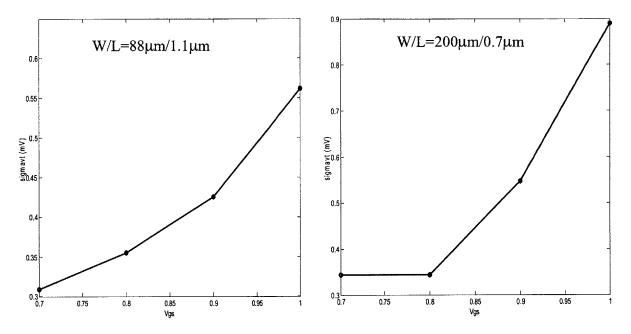

|         | 5.1.3 Threshold Voltage                               |     |

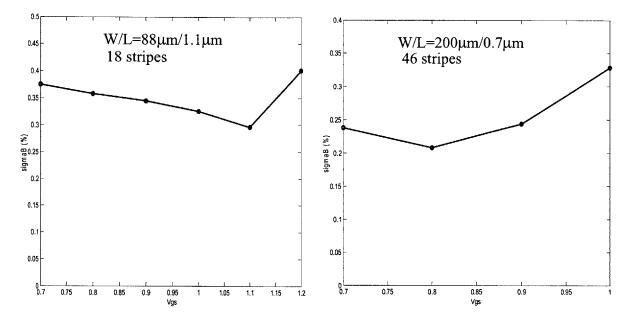

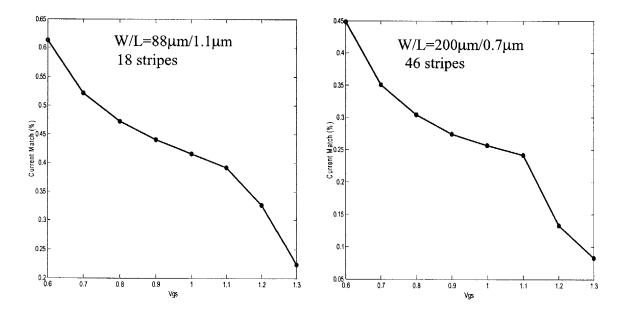

|         | 5.1.4 Matching                                        |     |

|         | 5.1.5 Edge Effects                                    |     |

|         | 5.1.6 Summary of Matching Results                     |     |

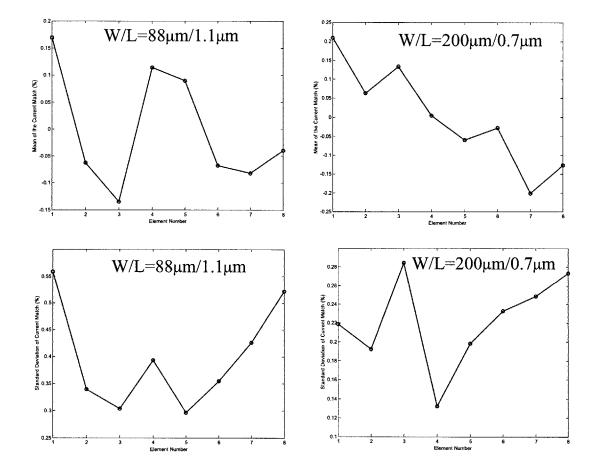

| 5.2     | AC Results                                            |     |

|         | 5.2.1 Test Setup                                      |     |

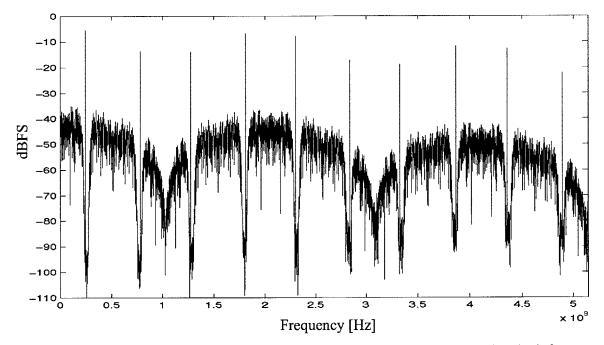

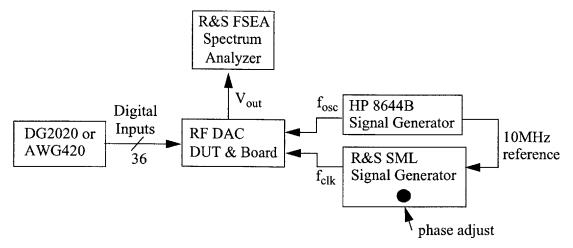

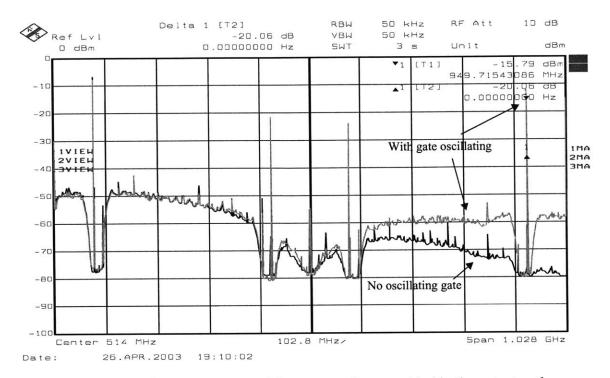

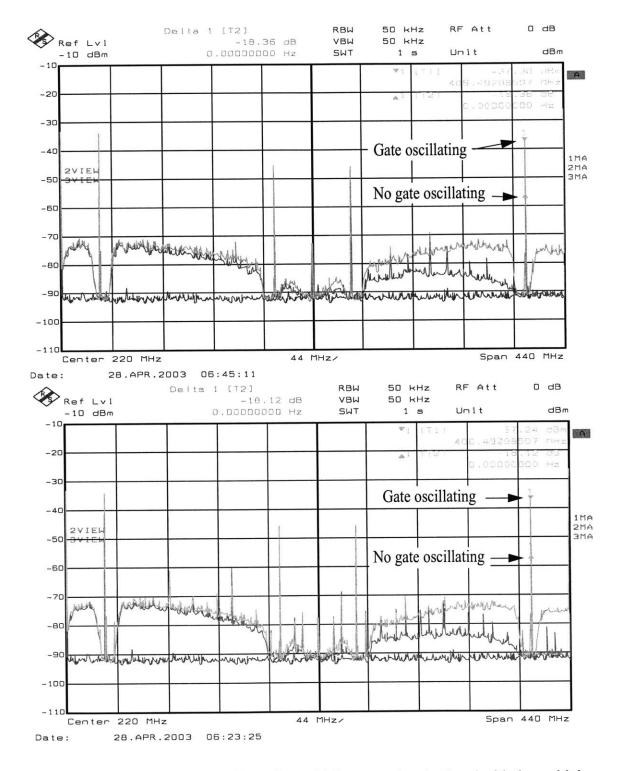

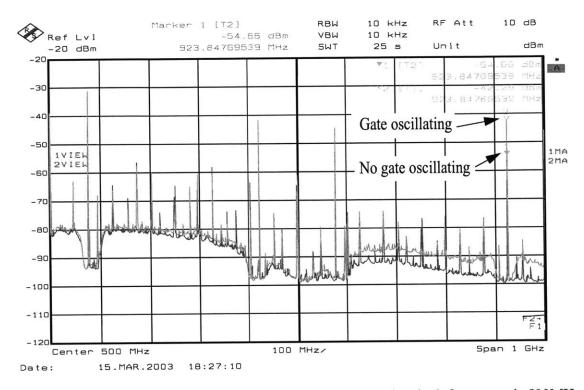

|         | 5.2.2 Spectrum and Overall Functionality              |     |

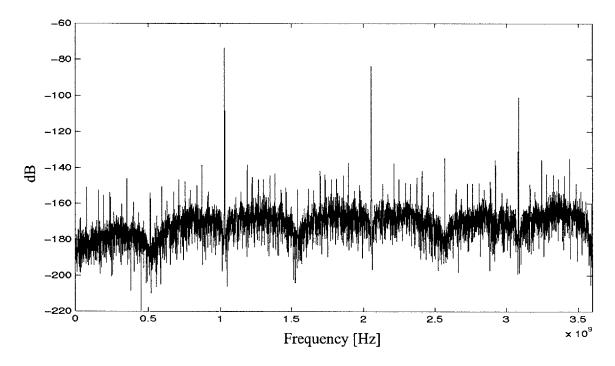

|         | 5.2.3 Single-Tone Performance                         |     |

|         | 5.2.3.1 Sources of SNR Degradation                    |     |

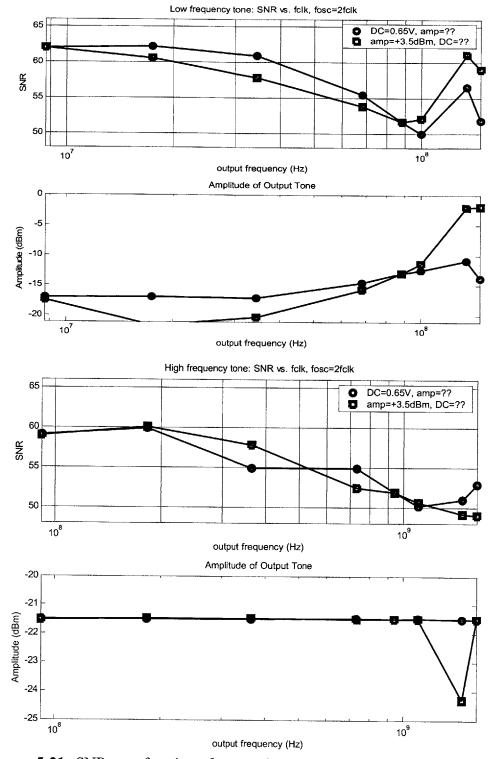

|         | 5.2.3.2 SNR versus Frequency                          |     |

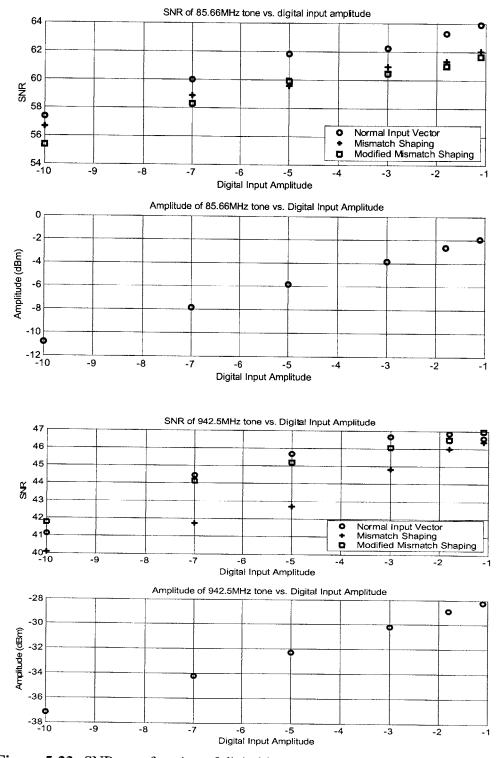

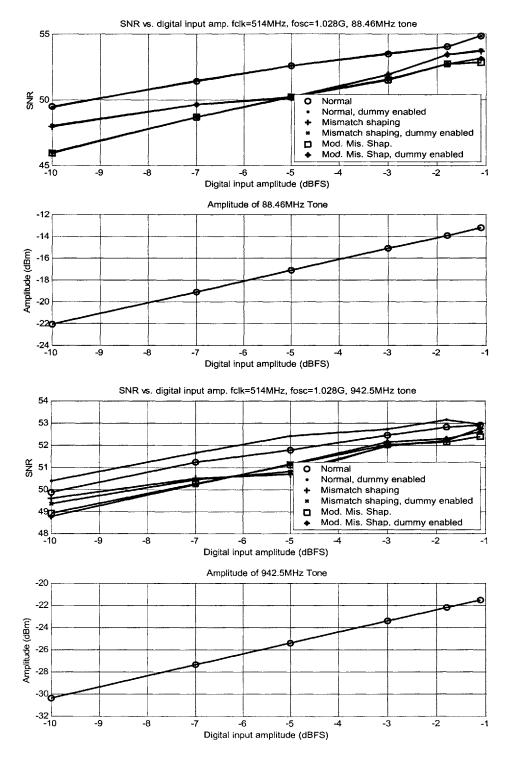

|         | 5.2.3.3 SNR versus Digital Input Amplitude            |     |

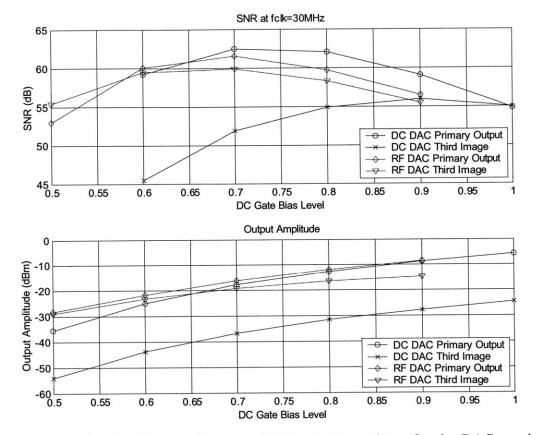

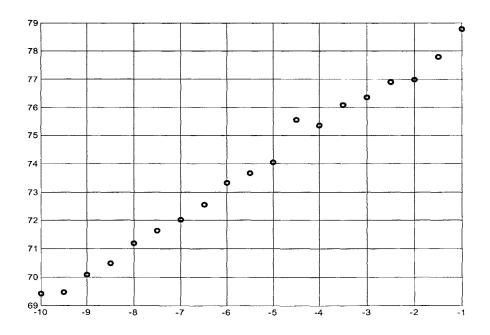

|         | 5.2.3.4 SNR versus Phase                              |     |

|         | 5.2.3.5 Sensitivity to Switch Driver Supply Voltage   |     |

|         | 5.2.4 Two-tone IMD3 Performance                       | 116 |

| 5.3     | Performance Comparison                                | 117 |

| 6 Conc  | lusions                                               | 118 |

| 6.1     | Summary                                               |     |

| 6.1     | Contributions of Thesis                               |     |

| 6.2     | Future Work                                           |     |

| 0.2     |                                                       |     |

| Append  | lix A: Jitter Limits in DACs                          | 121 |

| A.1     | RZ DAC Jitter Limit                                   | 122 |

| A.2     | NRZ DAC Jitter Limit                                  |     |

| Referer | ıces                                                  | 124 |

|         |                                                       |     |

### **1** Introduction

One of the largest growth areas in electronics over the past five years has been in applications of wireless communications. High resolution analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) are required in these systems to meet challenging signal-to-noise ratio (SNR), spurious-free dynamic range (SFDR), and distortion specifications in the presence of large nearby interferers. Additionally, recent trends have pushed towards higher speed data converters in pursuit of a "software radio" system, where receiver digitization is performed at an intermediate frequency (IF) or higher [1]. This permits channel selection filters and demodulation to be performed in the digital domain. Ideally, if the whole band can be digitized at a high speed, the band select filter can also be pushed to the digital domain. Reference [2] claims that converting to digital as early as possible in the receiver chain can result in overall size, weight and power reductions of over an order of magnitude. Similarly on the transmitter side, high speed, accurate DACs require fewer mixing and filtering stages before the antenna. The desirability of these programmable architectures has created a demand for high performance, high speed data converters.

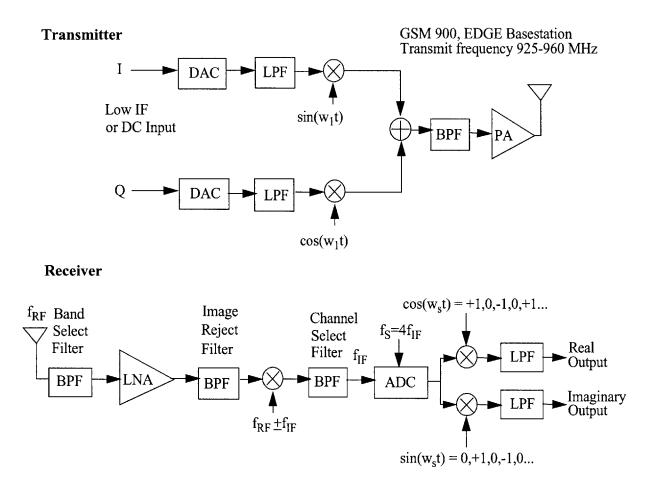

Figure 1-1 shows conventional transmitter and receiver architectures. Both architectures typically include a low or zero-IF data converter and one or more mixing stages. The mixing stages may not be completely eliminated due to speed and resolution limitations of modern day data converters. Of particular interest for radio applications are ADCs whose sampling frequency is four times the carrier frequency, called  $f_s/4$  bandpass converters. This ratio of IF to sampling frequency makes mixing down to baseband particularly simple in the digital domain, as depicted in Figure 1-1.

Jitter in the sampling/conversion clock is one of the main resolution limits of high speed data converters. Although there are many other noise sources, sampling jitter starts to dominate as input frequencies increase. Traditional approaches to mitigating the DAC clock jitter problem have focused on either building a high-power sampling clock with low jitter or using systems with oversampling to reduce the inband noise. This research initially concentrated on the limits of sampling jitter in converters and ultimately led to the development of a radio frequency (RF) DAC. This DAC trades sampling clock jitter for phase noise. It also has the additional benefit of mixing the DAC impulse response energy to a higher frequency. An image of a low IF input signal can

Figure 1-1: Conventional transmitter and receiver architectures.

therefore be output directly at a high IF or RF frequency for transmit communications applications to offer a lower noise, power, and area transmit solution. This saves power and hardware relative to a conventional transmitter architecture by eliminating the need for mixers and intermediate frequencies.

This section reviews state-of-the-art in data converters and the sampling jitter problem. Chapter 2 describes the new RF DAC concept. Chapter 3 is an analysis and comparison of the SNR of a square wave pulse used in conventional DACs and the cosine feedback pulse used in the RF DAC. Chapter 4 discusses trade-offs in the implementation of a prototype to demonstrate the new concept. Measurement results for the RF DAC prototype are presented in Chapter 5. Conclusions and areas for future work are detailed in Chapter 6.

#### 1.1 State-of-the-art High Speed ADCs

State-of-the-art ADC architectures are dependent on the speed and resolution requirements of the converter. High speed (>1GHz) low resolution (6b) converters are driven by disk drive and high-speed Ethernet applications. These converters typically use a flash architecture, often with interpolation to save area and power or interleaving to increase speed [3]. They are currently limited by the speed and resolution of the sampling operation as well as by offsets and mismatches in interleaved paths [3] [5]. High resolution (>10b) converters typically utilize pipeline architectures and currently achieve as high as 100MSample/s rates. The resolution and speed of these converters are limited by device matching and the speed of closed-loop operational amplifiers respectively [6]. Digital calibration techniques can be used to ease the matching requirements in pipeline converters [7].

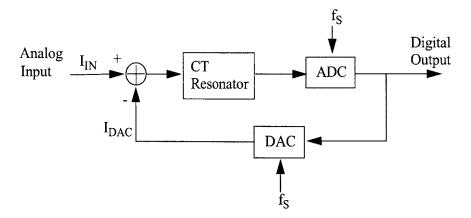

As the sampling frequency increases, continuous-time (CT) sigma delta modulators ( $\Sigma\Delta Ms$ ) have been preferred for narrowband applications because they do not have the op-amp settling-time constraints or the fast, high-precision sample and hold (S/H) requirements that limit the maximum clock rate in discrete-time (DT)  $\Sigma\Delta Ms$  and upfront sampled ADCs. A block diagram of a typical current feedback CT  $\Sigma\Delta M$  is shown in Figure 1-2. The input is no longer sampled upfront. Instead the error signal at the output of the CT resonator is sampled. The CT resonator can be active  $g_m$ -C or passive LC, so no fast-settling op-amps are needed in the loop. This makes CT  $\Sigma\Delta Ms$  particularly attractive for high speed, high bandwidth conversion. Indeed recent work has shown that sample rates of CT  $\Sigma\Delta Ms$  have been steadily increasing and have surpassed those of their DT counterparts [2] [8] [9] [10] [12].

Unfortunately for their potential as high speed converters, the effect of clock jitter on the performance of CT  $\Sigma\Delta Ms$  is worse than an upfront sampled system. The effect of clock jitter at the ADC is shaped by the feedback loop. The jitter in the DAC clock, however, is added directly to the input and does not benefit from loop shaping. Furthermore, this jitter on the DAC clock acts on the quantized DAC signal, which is a stepped version of the CT input. Thus, the CT  $\Sigma\Delta M$ ADC ends up with more SNR degradation due to jitter than the upfront sampled system, which samples the un-quantized input directly [21].

Figure 1-2: Typical CT  $\Sigma \Delta M$  block diagram.

Reference [10] concludes that most gigahertz CT  $\Sigma \Delta M$  ADCs are limited to an effective oversampling ratio (OSR) of about 16. Above this OSR, they are dominated by in-band white noise due to jitter rather than shaped quantization noise. Although DT  $\Sigma \Delta Ms$  have been pushed to high speeds, their speed is limited due to the use of closed loop operational amplifiers [11]. Table 1-1 summarizes the performance of some of the best state-of-the-art high-speed ADCs.

| ADC Architecture                | SNDR<br>(ENOB)                 | Power | Sampling<br>Rate | Signal<br>Bandwidth                 |

|---------------------------------|--------------------------------|-------|------------------|-------------------------------------|

| CMOS Flash [4]                  | 33dB (5.5)                     | 545mW | 1.3GHz           | 650MHz                              |

| CMOS Interpolating<br>Flash [3] | 36dB (5.6)                     | 300mW | 900MHz           | 450MHz                              |

| CMOS Pipeline [6]               | 57dB (9.4)                     | 180mW | 100MHz           | 50MHz                               |

| SiGe HBT CT ΣΔΜ<br>[10]         | 40dB (6.3)                     | 450mW | 4GHz             | 20MHz cen-<br>tered at 1GHz         |

| AlInAs/GaInAs CT<br>ΣΔΜ [2]     | 75.8dB (12)<br>in 1MHz<br>band | 3.2W  | 4GHz             | 1MHz/60MHz<br>centered at<br>180MHz |

|                                 | 39dB (6) in<br>60MHz band      |       |                  |                                     |

| GaAs CT ΣΔΜ [12]                | 41dB (7) in<br>25MHz band      | 1.8W  | 3.2GHz           | 25MHz/<br>100kHz band               |

|                                 | 66d B (11) in<br>100kHz band   |       |                  | centered at<br>800MHz               |

| CMOS DT ΣΔΜ [11]                | 87dB (14)                      | 150mW | 64MHz            | 2MHz                                |

| Table 1-1 | State-of-the-art | high-speed ADCs |

|-----------|------------------|-----------------|

|-----------|------------------|-----------------|

#### **1.2 State-of-the-art High-Speed DACs**

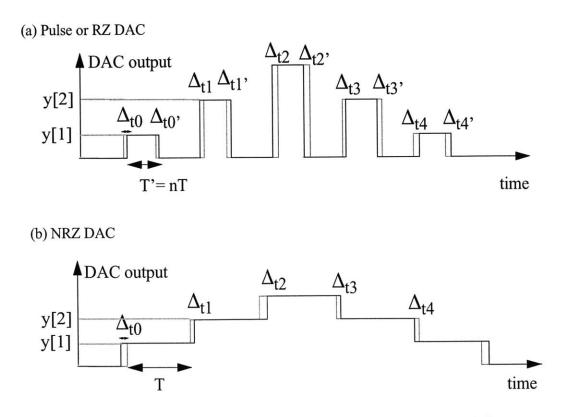

Communications applications are pushing the sampling speed and frequency domain performance requirements of high-speed DACs [14]. Direct digital synthesis (DDS) is another application demanding high speed DACs with good spurious performance [13]. Specifications of SNR, SFDR, and adjacent channel power ratio in a narrow bandwidth are becoming more important than static specifications such as integral nonlinearity (INL) and differential nonlinearity (DNL). Furthermore, third-order distortion (IMD3) is often the only significant harmonic that falls inband in narrowband communications applications. The SNR and SFDR performance of high-speed, high-resolution DACs is limited by dynamic errors at the switching instants [15] [17] [30]. This causes the SFDR performance to worsen as the input frequency increases. One source of dynamic degradation is inter-symbol interference (ISI). When ISI is present, the DAC output is dependent on the current data as well as the previous data, often in a nonlinear way. This problem is solved by using a return-to-zero (RZ) DAC output pulse, which essentially nulls the memory the DAC had of the previous data. However, this approach introduces large steps in the DAC output, thereby increasing jitter sensitivity and causing problems in the linearity of the output stage [21] [36]. The jitter problem will be studied further in Section 1.3.

Another source of DAC degradation is imperfect synchronization of the switch control signals between the elements of the DAC. This is especially troublesome in a multibit DAC, where glitches are created if the bits switch at different times. This has been solved by a combination of building a synchronization block in front of the switches and careful layout to match path delays [15] [30]. The accuracy of this method is still limited by the matching achievable in the synchronization blocks and layout routing.

The author has not been able to find any work on directly solving the clock jitter problem in DACs. DACs rely on a high-power sampling clock with low jitter and large oversampling ratios to reduce the inband noise. Return-to-zero (RZ) DACs have been shown to have worse jitter performance than non-return-to-zero (NRZ) DACs. A dual return-to-zero DAC has been proposed in [16] to alleviate the jitter problem in RZ DACs.

| DAC Type                         | Resolution | Power     | Sample Rate | Performance                                             |

|----------------------------------|------------|-----------|-------------|---------------------------------------------------------|

| Current Steering<br>Nyquist [15] | 10b        | 110mW     | 1GSample/s  | SFDR = 61dB@<br>500MHz output                           |

| Current Steering<br>Nyquist [37] | 16b        | not given | 400MS/s     | SFDR~80dBc@300<br>MHz output, IMD3=-<br>80dBc to 300MHz |

| Current Steering<br>Nyquist [20] | 14b        | 180mW     | 100MHz      | SFDR=72dBc<br>@42.5MHz output<br>with $f_s$ =100MHz     |

|                                  |            | 210mW     | 200MHz      | SFDR=50dBc<br>@90MHz output<br>with fs=200MHz           |

| ΣΔ DAC [19]                      | 13b        | 95mW      | 120MHz      | DR=85dB                                                 |

|                                  |            |           |             | SNDR=80dB                                               |

|                                  |            |           |             | both in 5MHz BW                                         |

| ΣΔ DAC [18]                      | 16b        | 290mW     | 96kHz       | SNR=113dB in a<br>40kHz BW                              |

Table 1-2

State-of-the-art

DACs

Narrowband  $\Sigma\Delta$  DACs with oversampling and mismatch shaping would seem useful in solving static and dynamic mismatch problems. Research in narrowband  $\Sigma\Delta$  DACs has been driven by audio applications, which require high resolutions at relatively low speeds [18]. Multibit  $\Sigma\Delta$  DACs are beginning to be investigated for MHz range-frequency applications [19]. Table 1-2 summarizes the performance of state-of-the-art high speed Nyquist rate and  $\Sigma\Delta$  DACs.

### **1.3 Jitter Limits in Converters**

Both the pipeline and flash converter ADC architectures utilize up-front samplers or track-andholds. Resolution in these converters is not currently limited by jitter in the sampling process. However, resolution will become jitter-limited as technology improves the speed of converters as well as the other sources of converter noise.

In any up-front sampled ADC, sampling clock timing jitter creates an error in the sampled value. Regardless how much resolution the ADC has, it will never achieve better signal-to-noise ratio (SNR) than this sampling operation. The theoretical limit due to sampling a signal at frequency  $f_{in}$  with a jittered clock is [21], [22]

$$SNR = 20\log \frac{\sqrt{OSR}}{2\pi\sigma_t f_{in}} \tag{1.1}$$

where  $\sigma_i$  is the standard deviation of a Gaussian, white-noise random sampling jitter in seconds and OSR is the oversampling ratio, i.e. the ratio of the sampling frequency  $f_s$  to the Nyquist bandwidth of the signal  $2f_b$ . As the input frequency  $f_{in}$  increases, the achievable SNR due to a fixed amount of sampling jitter  $\sigma_i$  decreases. Plugging in  $OSR = \frac{f_s}{2f_b}$  to Equation 1.1 gives

$$SNR = 20\log \frac{\sqrt{f_s}}{f_{in}} \frac{1}{2\pi\sigma_i \sqrt{2f_b}}$$

(1.2)

Equation 1.2 shows that even if the sampling frequency  $f_s$  is scaled with the input frequency  $f_{in}$ , the maximum achievable SNR still degrades as the square root of  $f_{in}$ .

The SNR for high speed DACs is similarly jitter limited. SNR for a RZ and an NRZ DAC are derived in Appendix A. For a RZ DAC, the SNR limit is shown to be

$$SNR = 20\log \frac{n}{2\sqrt{f_s f_b} \sigma_t}$$

(1.3)

where n is the fractional duration of the RZ pulse relative to the sampling period.

In the NRZ DAC case the SNR limit is shown to be

$$SNR = 20\log\left(\frac{y_{rms}}{\sqrt{2f_s f_b} \sigma_{t} y_{diffrms}}\right)$$

(1.4)

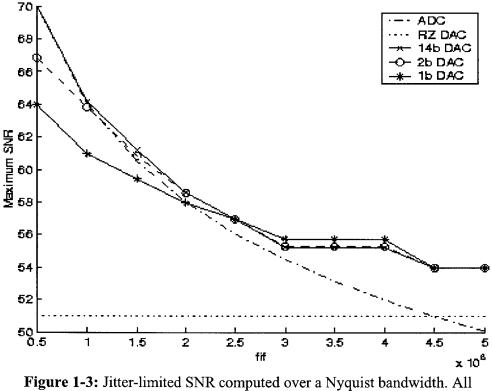

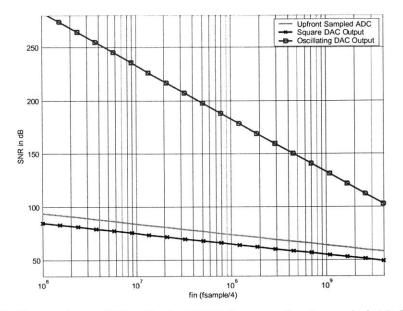

where  $y_{rms}$  is the rms value of the digital input and  $y_{diffrms}$  is the rms value of the difference in input values. The jitter limited SNRs derived in Equation 1.2, Equation 1.3, and Equation 1.4 are plotted in Figure 1-3 versus the frequency of the input tone  $f_{in}$ . They are compared over a Nyquist bandwidth ( $f_s=2f_b$ ) with  $f_s=1$ GHz and  $\sigma_t=1$ psec. The RZ DAC pulse is half (n=0.5) the sampling period. Equation 1.4 is plotted for a 14-bit, 2-bit and 1-bit NRZ DAC.

converters are sampling at  $f_s=1$ GHz with a clock jitter  $\sigma_t=1$ psec. In the RZ DAC the pulse is half the sampling period (n=0.5).

As expected, the RZ DAC has a jitter-limited SNR that is independent of the input frequency and the number of bits in the DAC. The RZ DAC pulse always has two edges with jitter, whereas the NRZ DAC has a random number of edges between 0,1, and 2. The number of transitions in the NRZ DAC increases as the input frequency increases, so the SNR decreases. The NRZ DAC curves depend on the number of bits at low input frequencies. For small  $f_{in}$ , the oversampling ratio is large and there are many samples per period. Many samples per period with a large number of bits translates to small step sizes. These small step sizes translate to less error and better SNR. As the number of bits increases, the low-frequency SNR limit approaches that of a sampler. At large input frequencies, however, the SNR limit becomes independent of the number of bits in the DAC. This case corresponds to fewer samples per period, or large transitions at every sampling instant. These transitions are so large that they become practically independent of how well they are quantized.

Near Nyquist sampling the NRZ DAC jitter-limited SNR is expected to be 3dB higher than the RZ DAC SNR. This is because the RZ pulse has an extra switching edge, causing  $a\sqrt{2}$  larger error. The sampler SNR curve is lower near Nyquist sampling due to the lower signal power in the rms value of a sinusoid versus a square wave.

### 2 RF DAC Concept

#### 2.1 Background

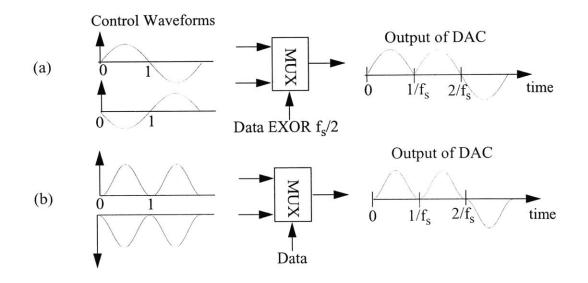

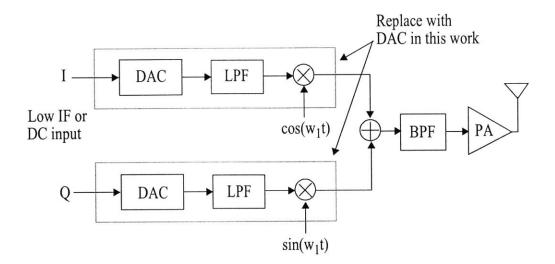

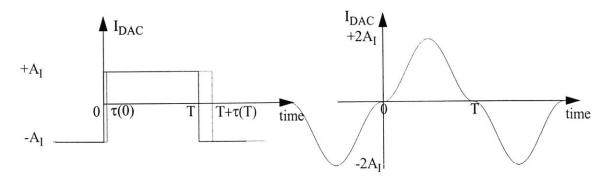

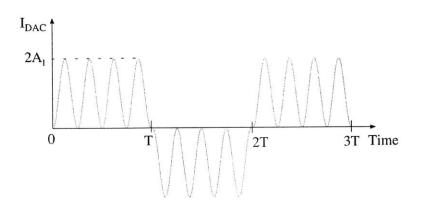

Zhang [23] recognized the problem of clock jitter in the feedback DAC waveform of a CT  $\Sigma\Delta$  ADC. His thesis described the use of a sine wave to generate a RZ DAC output pulse, as illustrated in Figure 2-1. Figure 2-1 (a) shows an f<sub>s</sub>/2 sine wave at the input to the mux, where f<sub>s</sub> is the data update rate of the DAC. The mux switches at the zero crossings of the sinusoid, depending on the value of the input data. Figure 2-1 (b) shows the same concept implemented using a sine wave at frequency f<sub>s</sub> with a DC offset. If the sine wave is noise free and perfectly locked to the data clock, first order jitter insensitivity is achieved in Figure 2-1 (a) due to the zero value of the control waveform at the switching instant. First and second order jitter insensitivity are expected from the waveform of Figure 2-1 (b) due to the zero value *and* zero slope of the control waveform at the sampling instants.

#### 2.2 **RF DAC Description**

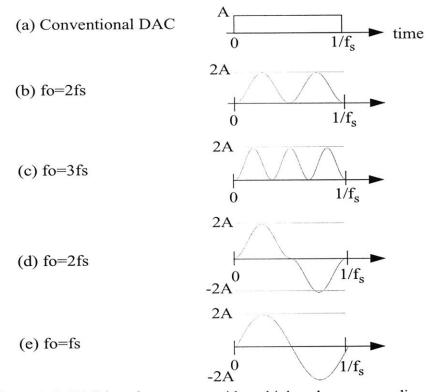

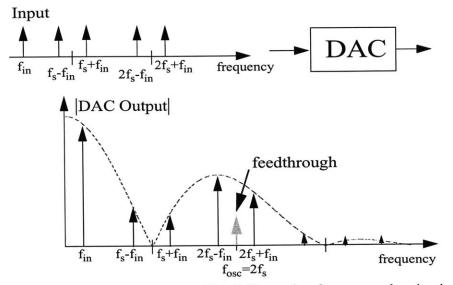

The RF DAC concept builds on Zhang's theoretical work by using multiple pulses per DAC output value. A harmonic of the DAC data clock (frequency  $f_s$ ) is used as the DAC control waveform (frequency  $f_o$ ). Figure 2-2 (a) shows the impulse response of a conventional DAC, while Figure 2-

Figure 2-1: Binary DACs with jitter insensitive output [23].

2 (b), (c), (d), and (e) show possible DAC impulse responses using this RF DAC concept. The control waveform frequency  $f_0$  could be any multiple of the DAC data clock,  $f_0=kf_s$ . The RZ pulses do not have to be identical, as illustrated by the examples in Figure 2-2 (d) and (e).

The frequency domain impulse responses for the time domain waveforms of Figure 2-2 are shown in Figure 2-3. Cases (b)-(e) and the family of curves  $f_0=kf_s$  implemented as in Figure 2-2 (b)-(e) have a high energy lobe at frequency  $kf_s$ . This allows an image of a low frequency DAC's input to be output with more energy at higher frequencies. This can also be thought of as a 'mixing DAC,' since the oscillating control waveform essentially mixes the DAC impulse response up to  $kf_s$ . Note that the control waveform does not have to be a perfect sinusoid to produce the high frequency lobe. Any distortion in the control waveform will cause a slightly different DAC impulse response and thereby a different inband gain, but the SNR at the output is not disturbed.

The concept of a DAC with an oscillating control waveform could be applied to Nyquist rate DACs,  $\Sigma\Delta$  DACs, feedback DACs in  $\Sigma\Delta$  ADCs, binary DACs, multibit DACs, current steering DACs, or resistor ladder DACs. The embodiments shown in Figure 2-2 are not the only possibilities. Any oscillating DAC control waveform with  $f_0=kf_s$  can achieve a large high frequency lobe in the impulse response. The additional constraints  $f_0=kf_s$  and switching at the zero crossings of the control waveform reduce ISI and improve noise performance.

#### 2.2.1 RF DAC Advantages

The RF DAC has several advantages over conventional DACs. Some advantages are listed below:

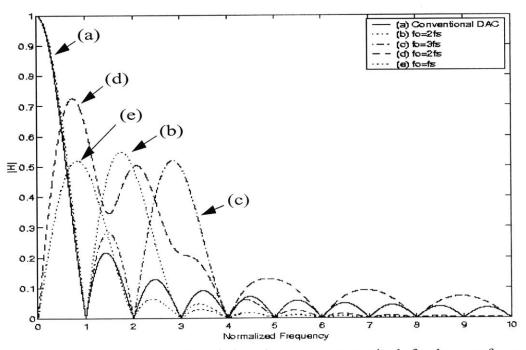

• Ability to directly output a high frequency signal with large energy. This could be a high IF frequency or even a direct RF frequency in transmitters in communications systems. This can save power and hardware by eliminating the need for mixers, choppers, and filters in the additional intermediate frequencies currently present in state-of-the-art communication transmit systems. This concept is depicted in Figure 2-4. Noise and linearity requirements of the DAC are also relaxed, since there are fewer circuits before the antenna.

Figure 2-2: DAC impulse response with multiple pulses per sampling period.

Figure 2-3: Frequency domain impulse response magnitude for the waveforms of Figure 2-2 normalized to  $f_s$ .

- Reduction of switch timing synchronization problems between the elements of the DAC. The burden of timing accuracy is placed on the control waveform. If the data clock is locked to the control waveform, it will switch at the zero value, zero slope points of the control waveforms of Figure 2-2 (a)-(d). Thus small mismatches in the data clock or control waveform distribution (relative to the period of the control waveform) will have little effect on the output.

- Reduced sensitivity to random jitter in the DAC data clock since the data clock switches when the control waveform is zero valued with zero slope. Performance is sensitive to the phase and amplitude noise of the oscillating control waveform. However, in practice it is easier to build a low phase noise sine wave than a low jitter clock or square wave. Thus improved jitter-limited SNR is expected over conventional square wave RZ and NRZ DACs. This point will be elaborated in Chapter 3.

- Reduced sensitivity to digital signal feed-through via the C<sub>gd</sub> of the switch transistors. Conventional current steering DACs have solved this problem by using a reduced signal swing at the input to the switch transistors [24]. Reducing the switch transistor input swing, however, reduces the speed of the switching. In the RF DAC implementation, the output voltage is the same value at each switching instant. Thus the charge feed through is a disturbance proportional to the input that causes no distortion. Note that this constant output voltage at the switching instants is also an advantage present in any RZ DAC.

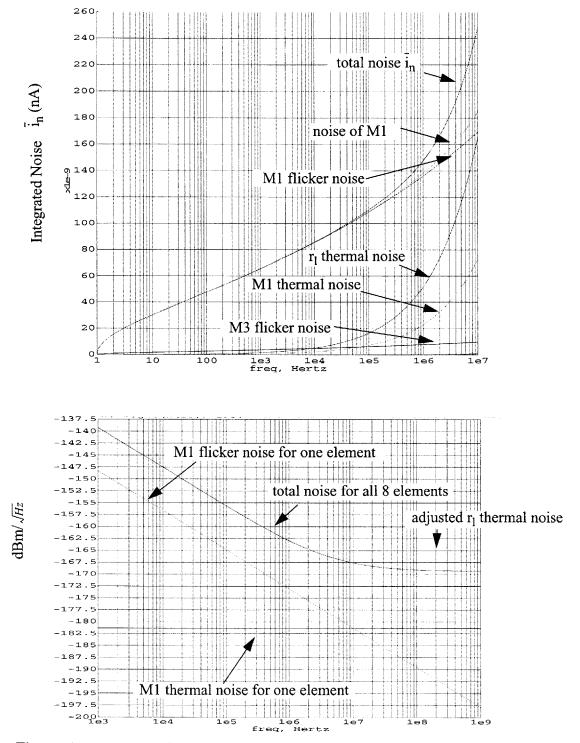

- Potential for reduced upconversion of 1/f noise. References [25] and [26] have shown that switching a MOS transistor between strong inversion and accumulation can reduce 1/f noise power. The best explanation for this effect is that the accumulation phase interferes with the long time constant associated with the 1/f noise trapping and detrapping process, and therefore with the long term memory that characterizes 1/f noise. Reference [26] has shown experimentally an 8dB improvement in upconverted 1/f noise. In a current steering RF DAC implementation, the current source transistor is turned on and off by the control waveform. If the transistor is driven into accumulation during the off state, the upconverted 1/f noise should be reduced, offering higher inband SNR than a conventional DAC.

Figure 2-4: Conventional transmitter architecture shown with components that can be replaced by the RF DAC.

#### 2.2.2 RF DAC Disadvantages

One disadvantage of using an image of the DAC output is illustrated in Figure 2-5. If the DAC output waveform has a DC component, the thermal or wideband noise from the primary image gets aliased inband for all of the subsequent images. If this thermal or wideband noise dominates, it could degrade the SNR of the images relative to that of the primary output. Similarly, thermal noise or any other source of noise in the DAC current will mix with the input and potentially alias out-of-band quantization noise back in-band.

Depending on the number of bits and frequencies used in RF DAC, the oscillator may have to drive a large capacitive load with a high-frequency signal. This can require large power consumption, specifically as the number of bits and frequencies increase.

**Figure 2-5:** Illustration of noise aliasing of the thermal noise from the DC component to high frequencies.

### **3 Sources of Error in RF DAC**

The RF DAC concept presented in the previous section changes the constraint from building a good data clock or DAC switching clock to building a low noise oscillating output waveform (or oscillator) that is accurately locked to a clock. These two waveforms are depicted in Figure 3-1. This chapter will explore the sources of error in the RF DAC system, including locking error, phase and amplitude noise [27]. The phase and amplitude noise will be compared both intuitively and analytically between the square waveform and the oscillating waveform. Since this chapter is relatively mathematical, quick intuitive arguments are first presented to explain the expected results.

Both waveforms in Figure 3-1 will be subject to uncertainties in the amplitude, also called amplitude noise. The amplitude noise of the voltage reference is expected to be the similar in both cases and set by the noise of a bandgap. The amplitude of the oscillating DAC is twice that of the square wave for the same amount of delivered charge. Thus the amplitude noise is expected to be worse in the oscillating waveform than in the square waveform.

A few quick hand-waving arguments can also be made about why the phase noise performance of an oscillating waveform is expected to be better than a square waveform with jitter. First, it is easier to practically build an oscillator with low phase noise than it is to build a clock with low jitter. An oscillating waveform can be filtered with passive components, whereas a square wave has harmonic frequency components that cannot be filtered as easily.

The second argument has to do with how the waveforms are used. In a DAC, the variation in the amount of charge delivered each cycle determines the SNR. Any timing jitter  $\tau(t)$  on the switching edges of the square wave pulse of Figure 3-1 affects the amount of charge delivered. The

**Figure 3-1:** Square wave pulse with jitter on the switching edges (left). Oscillating pulse with phase noise not shown (right). Both waveforms will also be subject to amplitude noise.

instantaneous value of the timing jitter at the switching instants is important. However, in an oscillating DAC output waveform with phase noise the instantaneous value of the phase noise is irrelevant, only the integrated noise over a switching period contributes to SNR. This is equivalent to noise averaging or band-limiting the noise. Thus the phase noise performance in the oscillating case is expected to be better than the timing jitter performance of the square wave case. The remainder of this chapter will analyze and compare the sources of error in the DAC output waveforms of Figure 3-1. Ideal locking between the oscillating DAC output waveform and the data clock will be considered first. Then the case of non-ideal locking with jitter on the data clock will be analyzed. Finally phase and amplitude noise in the oscillating waveform will be discussed intuitively and analytically. The chapter will conclude with an example of a numerical comparison.

### 3.1 Ideal Locking

Suppose the cosine feedback pulse is ideal and perfectly locked to the DAC clock. The only source of error is then jitter in the feedback DAC clock. Integrating  $I_{DAC}$  over a period gives the amount of charge fed back in one cycle,

$$q_f = A_I \int_{\tau(t_0)}^{T + \tau(t_T)} (1 - \cos(w_s t)) dt$$

(3.1)

Where  $\tau(t_0)$  and  $\tau(t_T)$  are the values of the clock jitter at times 0 and T respectively, and A<sub>I</sub> is the amplitude of the cosine feedback pulse. The nominal value of the integral in Equation 3.1 is A<sub>I</sub>T when  $\tau(t_0)$  and  $\tau(t_T)$  are zero. Thus, the error in the fed-back charge of Equation 3.1 is given by

$$E_q = q_f - A_I T \tag{3.2}$$

Using Equation 3.1 and Equation 3.2 with simplification gives

$$E_q \approx \frac{A_I w_s^2}{3!} (\tau(t_T)^3 - \tau(t_0)^3)$$

(3.3)

The variance of the error  $E_q$  is given by

$$\sigma_e^2 = E[E_q^2] - E^2[E_q]$$

(3.4)

For simplification, assume  $\tau(t_0)$  and  $\tau(t_T)$  are zero-mean Gaussian uncorrelated random variables with variance  $\sigma_t^2$ . This is the same assumption used in Section 1.3 for deriving Equation 1.1. The variance of the error is found from Equation 3.4 and Equation 3.3 with simplification,

$$\sigma_e^2 \approx \frac{5A_I^2 w_s^4 \sigma_t^6}{6} \tag{3.5}$$

The SNR can be computed by approximating the input charge as half the value of the nominal feedback pulse  $A_IT/2$ . This is the same assumption used in [21], to which this analysis will be compared. This value is chosen to avoid modulator overload since [21] uses the DAC for feedback DAC in a CT  $\Sigma\Delta M$ .

$$SNR = 20\log \frac{A_I T \sqrt{OSR}}{2\sigma_e}$$

(3.6)

Substituting Equation 3.5 into Equation 3.6 and simplifying gives

$$SNR = 20\log \frac{\sqrt{OSR}}{7.3\pi^2 f_s^3 \sigma_t^3}$$

(3.7)

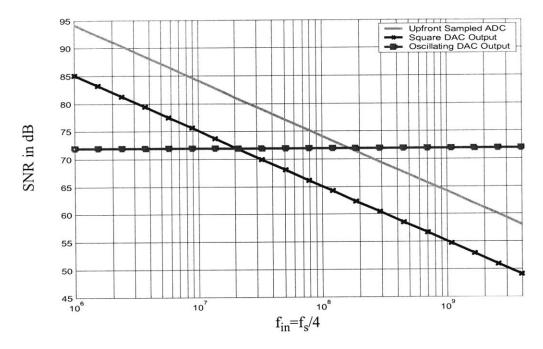

This third order jitter sensitivity ( $\sigma_t^3$ ) is expected due to the zero value and zero slope of I<sub>DAC</sub> at the sampling instants ±kT. The SNR limit in Equation 3.7 is compared in Figure 3-2 to the SNR limits in an upfront sampled converter (Equation 3.1.1) and a conventional CT  $\Sigma\Delta M$  with a single bit, square wave, NRZ DAC pulse as derived in [21]. The standard deviation of the sampling jitter  $\sigma_t$  is assumed to be 0.7ps<sub>rms</sub>. The curves are plotted versus the input frequency for an f<sub>in</sub>=f<sub>s</sub>/4 bandpass (BP) CT  $\Sigma\Delta M$ . The input signal bandwidth f<sub>b</sub> is 40MHz, but the relative comparison between the curves is the same no matter what f<sub>b</sub> is used. It is clear that under ideal locking, jitter in the feedback DAC's clock will not be the limiting source of error in the SNR performance of the RF DAC.

**Figure 3-2:** Comparison of jitter-limited SNR for an upfront sampled ADC, a DAC with square output pulse, and an oscillating output pulse. A signal bandwidth of 40MHz and sampling jitter standard deviation of 0.7ps<sub>rms</sub> were used.

#### 3.2 Locking Error

A locking error of  $t_0$  between the sampling clock edge and  $I_{DAC}$  is depicted in Figure 3-3. The feedback waveform is sampled at an offset of  $t_0$  from the zero crossings of the  $I_{DAC}$  waveform. This creates two sources of error that could degrade SNR. The first is the static offset, or "excess loop delay" in a CT  $\Sigma \Delta M$  [10]. The second is the data clock jitter acting on the nonzero  $I_{DAC}$  waveform.

#### 3.2.1 Static Offset

Static offset between the sampling pulse and the DAC feedback pulse in a CT  $\Sigma\Delta M$  is the same as the "excess loop delay" discussed in [10]. If t<sub>o</sub> is known, the loop can be designed with this delay, and the transfer function adjusted accordingly. If t<sub>o</sub> is not known precisely, feedback coefficient tuning can be used to adjust the loop transfer function [10].

#### 3.2.2 Dynamic Offset

Figure 3-2 indicates that clock jitter in the ideally locked case will not limit the SNR. However, if the feedback pulse and the clocking signal are not perfectly aligned as shown in Figure 3-3, the clock jitter will act on a nonzero DAC output with a nonzero slope. Suppose the clock is offset

Figure 3-3: Static locking error.

from the feedback pulse by a constant value of  $t_0$  as shown in Figure 3-3. The fed-back charge is given by

$$q_f = A_I \int_{t_o + \tau(0)}^{T + t_o + \tau(T)} (1 - \cos(w_s t)) dt$$

(3.8)

Integrating, the error in the fed-back charge is

$$E_a \approx A_I(\tau(T) - \tau(0))(1 - \cos(w_s t_o))$$

(3.9)

Assuming that  $\tau(0)$  and  $\tau(T)$  are zero-mean Gaussian uncorrelated random variables with variance  $\sigma_t^2$  the variance in the fed-back charge is

$$\sigma_e^2 \approx 2A_I^2 \sigma_t^2 (1 - \cos(w_s t_o))^2$$

(3.10)

Using Equation 3.6 and Equation 3.10,

$$SNR \approx 20\log \frac{\sqrt{OSR}}{2\sqrt{2}\sigma_t (1 - \cos(w_s t_o))f_s}$$

(3.11)

Simplifying for  $w_s t_o \ll 1$  or  $t_o \ll T/6$  gives

$$SNR \approx 20 \log \frac{\sqrt{OSR}}{56\sigma_t f_s \left(\frac{t_o}{T}\right)^2}$$

(3.12)

Given the fixed locking delay  $t_0$  and the standard deviation of the clock jitter  $\sigma_t$ , Equation 3.11 can be used to find the jitter imposed SNR limit.

In a conventional CT $\Sigma\Delta M$  with a square-wave feedback pulse, the jitter acts on a signal of height A<sub>I</sub> when the output is switching. In the RF DAC case, the clock jitter acts on I<sub>DAC</sub> with height A<sub>I</sub>(1-cos(w<sub>s</sub>t<sub>o</sub>)), giving the error in Equation 3.9. Although the output in the square wave pulse system is not always switching, the input to sampling frequency ratio may be low and the output will almost always be switching, especially in a single bit DAC case. Thus the SNR is expected to be better as long as A<sub>I</sub>(1-cos(w<sub>s</sub>t<sub>o</sub>)) << A<sub>I</sub> (i.e. t<sub>o</sub> <T/4), or as long as the DAC switching does not occur near the peak of the cosine wave.

#### 3.3 Phase and Amplitude Noise in the Oscillating Waveform

Timing jitter in the sampling clock is not the only source of error in the RF DAC. There are also nonidealities in the oscillating waveform itself. These nonidealities are expressed as amplitude and phase noise.

If the cosine pulse has phase noise  $\phi(t)$ , amplitude noise  $A_m(t)$  in the DC level and  $A_c(t)$  in the oscillator, the feedback current can be written,

$$I_{DAC} = A_I + A_m(t) - (A_I + A_c(t))\cos(w_s t + \phi(t))$$

(3.13)

The charge transferred over one period can be written as

$$q_{f} = \int_{0}^{T} (A_{I} + A_{m}(t) - (A_{I} + A_{c}(t))\cos(w_{s}t + \phi(t)))dt$$

(3.14)

The nominal value of this feedback pulse is  $\pm A_I T$  when there is no phase or amplitude noise. In the following analysis, the phase and amplitude noise will be analyzed separately. They are assumed to be uncorrelated and the total SNR degradation can be found by computing the sum of the squares of their error variances.

#### 3.3.1 Phase Noise

The fed-back charge q<sub>f</sub> with only phase noise in the cosine feedback pulse is given by

$$q_f = \int_{0}^{T} (1 - \cos(w_s t + \phi(t))) dt$$

(3.15)

The error in  $q_f$  due to phase noise is then

$$E_{q} = A_{I} \int_{0}^{T} -\cos(w_{s}t + \phi(t))dt$$

(3.16)

Expanding the sum and assuming  $\phi(t) << \pi/2$  gives

$$E_q \approx -A_I \int_0^T \phi(t) \sin(w_s t) dt$$

(3.17)

#### 3.3.1.1 Intuitive Analysis

Suppose there is a phase noise tone at frequency  $w_\tau$  of amplitude  $\Delta$  and phase  $\theta$  given by

$$\phi(t) = \Delta \cos(w_{\tau} t + \theta) \tag{3.18}$$

Substituting Equation 3.18 into Equation 3.17 gives

$$E_q \approx -A_I \int_{0}^{T} \Delta \cos(w_{\tau} t + \theta) \sin(w_s t) dt$$

(3.19)

Integrating and simplifying gives (for  $w_{\tau} \neq w_s$ )

$$\frac{E_q}{\Delta}(w_{\tau}) \approx -\frac{A_I w_s}{w_{\tau}^2 - w_s^2} (\cos(w_{\tau} t + \theta) - \cos(\theta))$$

(3.20)

and for  $w_{\tau}\!\!=\!\!w_s$

$$\frac{E_q}{\Delta} \approx -\frac{A_I T}{2} \sin(\theta)$$

(3.21)

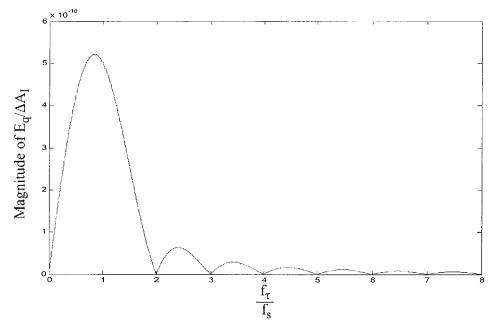

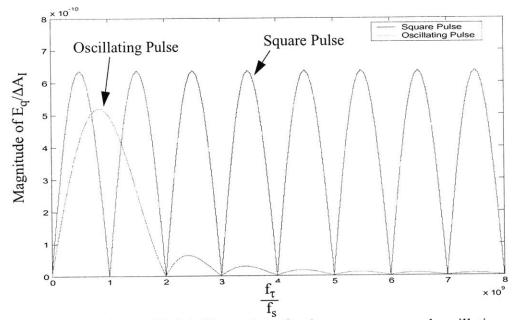

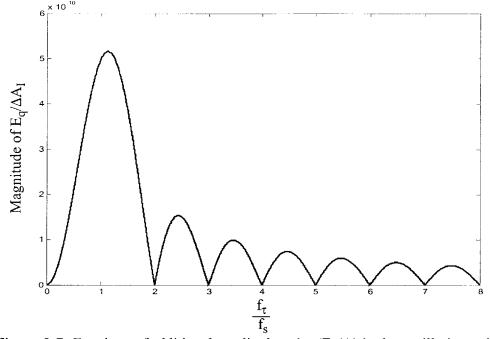

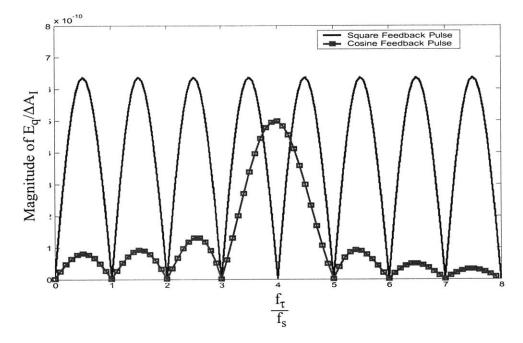

Plotting the magnitude of the maximum value over  $\theta$  (i.e. the envelope) of this transfer function as a function of the frequency of the tone ( $f_{\tau} = w_{\tau}/2\pi$ ) with  $f_s = w_s/2\pi$  gives the phase noise sensitivity curve shown in Figure 3-4. The envelope of the transfer function is scaled by A<sub>I</sub>. This curve gives an intuitive feel for the frequencies of noise that cause large error in the delivered charge.

Figure 3-4: Envelope of  $E_q/\Delta A_I$  versus  $f_\tau$  for oscillating DAC waveform.

The curve can easily be multiplied by the measured magnitude  $\Delta$  of the noise tones at different frequencies when used in a specific system to get the actual sensitivity plot.

It is interesting to note that the envelope is largest at  $f_{\tau}=f_s$ , and that  $E_q/\Delta A_I$  with  $f_s=w_s/2\pi$  approaches 0 as  $f_{\tau}$  approaches 0 and as  $f_{\tau}$  approaches  $\infty \cdot E_q/\Delta A_I$  is most sensitive to phase noise at frequencies near  $f_{\tau}=f_s$ . This corresponds to modulated phase noise at offset frequencies  $f_{\tau}=f_s$  away from the carrier, i.e. near DC and  $2f_s$ . Thus, when designing a DAC with the cosine feedback pulse, it is advantageous to try to null out phase noise at DC and  $2f_s$ .

For comparison, the same analysis is performed with a conventional NRZ DAC square-wave feedback pulse. The square-wave pulse shown in Figure 3-1 has jitter on the clocked edges defined as  $\tau(0)$  and  $\tau(T)$ . The charge in the fed-back pulse is given by

$$q_f = A_I \int_{0}^{T} (2u(t - \tau(0)) - u(t - T - \tau(T)) - 1) dt$$

(3.22)

The noise free value of this pulse is  $A_I T$  when  $\tau(0)$  and  $\tau(T)$  are both zero. This is the same nominal feedback charge in Equation 3.15. The error in the fed-back charge is

$$E_{q} = 2A_{I}(\tau(T) - \tau(0))$$

(3.23)

Figure 3-5: Comparison of  $E_q/\Delta A_I(f_\tau)$  envelope for the square wave and oscillating wave DAC outputs.

To compare directly with the oscillating pulse, the timing jitter is defined analogously to Equation 3.18,

$$\tau(t) = \frac{\Delta}{w_s} \cos(w_\tau t + \theta)$$

(3.24)

This gives

$$\frac{E_q}{\Delta}(w_{\tau}) = \frac{2A_I}{w_s}(\cos(w_{\tau}T + \theta) - \cos(\theta))$$

(3.25)

The envelope is compared in Figure 3-5 with the oscillating pulse envelope from Figure 3-4. This plot is also normalized to  $A_I$  and plotted versus  $f_{\tau}$ .

The envelope of  $E_q/\Delta A_I(w_\tau)$  for the square-wave pulse is sensitive to noise at all frequencies except at multiples of  $f_s$ . Thus, for broadband noise, the oscillating pulse should have better SNR performance. Additionally, if the noise at offsets of  $f_s$  can be nulled, the oscillating pulse has the potential for even better noise tolerance.

#### 3.3.1.2 Analytical Analysis

The preceding analysis gives an intuitive view of which phase noise frequencies will cause large errors in the fed-back charge. It does not, however, give an analytical means of calculating the maximum achievable SNR. An analytical SNR expression is desired so that it can be compared to the SNR of upfront sampled ADCs and CT  $\Sigma\Delta$ Ms with square-wave pulses.

To find the SNR degradation, the variance of the feedback charge error  $\sigma_e^2$  is needed. From Equation 3.17,

$$\sigma_e^2 \approx E \left[ \int_0^T A_I \phi(t) \sin(w_s t) dt \int_0^T A_I \phi(t') \sin(w_s t') dt' \right]$$

(3.26)

Simplifying gives

$$\sigma_e^2 \approx A_I^2 \iint_{0}^{TT} R_{\phi\phi}(t-t') \sin(w_s t) \sin(w_s t') dt dt'$$

(3.27)

where  $R_{\phi\phi}(t-t')$  is the auto-covariance function of the phase noise.  $R_{\phi\phi}(t-t')$  can be written in the frequency domain as a function of the power spectral density of the noise

$$R_{\phi\phi}(\tau) = \frac{1}{2\pi} \int_{-\infty}^{\infty} S_{\phi\phi}(w) e^{jw\tau} dw$$

(3.28)

Simplifying gives

$$R_{\phi\phi}(\tau) = \frac{1}{\pi} \int_0^\infty S_{\phi\phi}(w) \cos(w\tau) dw$$

(3.29)

Once  $S_{\phi\phi}(w)$  is known or measured,  $R_{\phi\phi}(\tau)$  can be found from Equation 3.29. Then  $\sigma_e^2$  can be found from Equation 3.27 and used in Equation 3.6 to find the exact value of the SNR.

For the sake of comparison, assume  $S_{\phi\phi}(w)$  is a constant value of A over the frequency range  $w_H$  to  $w_L$  and zero elsewhere. The previous analysis indicates that the phase noise at offset frequencies  $w_s$  will end up contributing most to the error in the fed-back charge. Indeed for such large offset frequencies from the carrier, a flat thermal noise limit is expected. Using this assumption gives

$$R_{\phi\phi}(\tau) = \frac{A}{\pi\tau} (\sin(w_H \tau) - \sin(w_L \tau))$$

(3.30)

Substituting Equation 3.30 into Equation 3.27,

$$\sigma_e^2 \approx \frac{AA_I^2}{\pi} \int_{00}^{TT} \frac{1}{t-t'} (\sin(w_H(t-t')) - \sin(w_L(t-t'))) \sin(w_s t) \sin(w_s t') dt dt'$$

(3.31)

Carrying out this integration over a small band of frequencies  $w_H \approx w_L \approx w_\tau$  gives the same phase noise sensitivity plot as in Figure 3-4. This corroborates that  $\sigma_e$  is dominated by the phase noise at  $w_s$  away from the carrier.

Integrating Equation 3.31 in the limit  $w_H \rightarrow \infty$  to  $w_L \rightarrow 0$

$$\lim_{w_H \to \infty, w_L \to 0} \iint_{00}^{TT} \frac{1}{t-t'} (\sin(w_H(t-t')) - \sin(w_L(t-t'))) \sin(w_s t) \sin(w_s t') dt dt' = \frac{\pi T}{2}$$

(3.32)

This gives

$$\sigma_e^2 \approx \frac{AA_I^2 T}{2} \tag{3.33}$$

Using Equation 3.6 and  $\mathrm{OSR}{=}f_{s}/2f_{b}$  with simplification,

$$SNR \approx 20\log \frac{1}{2\sqrt{Af_b}}$$

(3.34)

This result indicates that the SNR limit due to phase noise in the pulse is not dependent on  $f_{in}$  or  $f_s$ . It is only dependent on the amplitude of the phase noise A and the bandwidth of the signal  $f_b$ . The only assumption made was that the phase noise spectrum was flat with an amplitude A at frequencies near an offset of  $w_s$  away from the carrier.

Figure 3-6 compares the jitter limited SNR in an upfront sampled signal (Equation 1.1), a conventional CT  $\Sigma\Delta M$  with a square feedback pulse [21], and a CT  $\Sigma\Delta M$  with the cosine-shaped feedback pulse (Equation 3.34). The SNR is plotted for a  $f_{in}=f_s/4$  BP converter with a bandwidth  $f_b=40$ MHz. The phase noise amplitude, A, is -150dBm with a 7dBm carrier, and the standard

**Figure 3-6:** Comparison of maximum achievable SNR in an upfront sampled ADC with jitter  $\sigma_t = 0.7 \text{ps}_{\text{rms}}$ , a square waveform feedback CT  $\Sigma \Delta M$  with jitter  $\sigma_t = 0.7 \text{ps}_{\text{rms}}$ , and a DAC with an oscillatory output waveform where the oscillator has phase noise - 150dBm. The bandwidth of the input signal is 40MHz for all three curves.

deviation of the jitter is  $\sigma_t=0.7 ps_{rms}$ . These values were chosen as typical numbers from current state-of-the-art.

Note that, as  $f_{in}$  increases, the maximum achievable SNR degrades for the upfront sampled converter and the square-pulse feedback CT  $\Sigma\Delta M$ , but not for the CT  $\Sigma\Delta M$  with oscillating pulse. For these typical clock jitter and oscillator phase noise numbers, the oscillating pulse has better performance than the conventional CT  $\Sigma\Delta M$  above  $f_{in} \sim 20MHz$  and better performance than an upfront sampled converter above  $f_{in} \sim 200MHz$ .

There are a few more potential advantages of the oscillatory feedback CT  $\Sigma\Delta M$  that are not depicted in Figure 3-6:

• If the DAC is built on a large single chip system, it is likely that the only clock or oscillator available will be noisy with  $\sigma_t >> 0.7 ps_{rms}$  and large close-in phase noise. As long as the phase noise around DC and  $2w_s$  stays at the thermal limit, the curve in Figure 3-6 for the oscillatory

waveform will be almost the same, outperforming the upfront sampled ADC and square waveform.

- If the phase noise around  $2w_s$  is notched or nulled, the cosine feedback  $\Sigma\Delta M$  could also perform better than indicated in Figure 3-6.

- Building an accurate upfront sampled converter which operates at high f<sub>s</sub> is very difficult without a large amounts of power [28] and/or an operational amplifier in the converter. Once the opamp is introduced, however, settling time limits the maximum conversion speed [6]. Thus building an upfront sampled converter to meet the SNR curve of Figure 3-6 in the high MHz and GHz regions is very difficult in practice.

#### 3.3.1.3 Amplitude Noise

Amplitude noise in the oscillating waveform also causes variations in the fed-back charge. Expressing the amplitude noise in the mean as  $A_m(t)$  and the amplitude noise in the oscillatory pulse as  $A_c(t)$ , the fed-back charge is

$$q_f = \int_{0}^{T} (A_I + A_m(t) - (A_I + A_c(t))\cos w_s t)dt$$

(3.35)

For comparison, the error in the fed-back charge due to amplitude noise in the square-wave pulse is given by

$$E_q = \int_0^T A_m(t)dt \tag{3.36}$$

The noise  $A_m(t)$  depends on the noise of a voltage source in both DACs. On the other hand,  $A_c(t)$  is dependent upon the oscillator. The oscillatory and square-wave pulses are compared in a system with the same voltage source reference quality. In this case, the oscillatory pulse has an additional amplitude noise sensitivity over the square-wave pulse

$$E_{q} = \int_{0}^{T} (A_{c}(t)\cos w_{s}t)dt$$

(3.37)

To obtain an intuitive analysis, consider the response to a tone at frequency  $f_{\tau}$ ,  $A_c(t)=A\cos(w_{\tau}t+\theta)$ . Substituting into Equation 3.36 and simplifying,

Figure 3-7: Envelope of additional amplitude noise  $(E_q/A)$  in the oscillating pulse versus

$$\frac{E_q}{A}(w_{\tau}) = \frac{w_{\tau}}{w_{\tau}^2 - w_s^2} (\sin(w_{\tau}T + \theta) - \sin(\theta))$$

(3.38)

for  $w_{\tau} \neq w_s$  and

$$\frac{E_q}{A} = \frac{T}{2}\cos(\theta) \tag{3.39}$$

for  $w_{\tau} = w_{s}$ .

This extra amplitude noise error in the cosine pulse is plotted in Figure 3-7. The error in the fedback charge is again most sensitive to amplitude noise at a frequency of  $f_s$  away from the carrier. If the amplitude noise is small or nulled at these large offset frequencies, then the amplitude noise sensitivity will approach the same performance as the square-wave pulse.

Using Equation 3.37 to calculate the exact additional variance of the fed-back charge due to amplitude noise,

$$\sigma_e^2 = E \left[ \iint_{00}^{TT} A_c(t) A_c(t') \cos(w_s t) \cos(w_s t') dt dt' \right]$$

(3.40)

$$\sigma_e^2 = E \left[ \iint_{00}^{TT} R_{AA}(t-t') \cos(w_s t) \cos(w_s t') dt dt' \right]$$

(3.41)

$R_{AA}(t-t')$  can be found from Equation 3.28, given the power spectrum of the amplitude noise. This can be substituted into Equation 3.41 to find the exact value of  $\sigma_e^2$ . If the amplitude noise is assumed to be flat over the sensitive frequencies around DC and  $2w_s$ , the calculations fall out exactly as in the phase noise case and Equation 3.34 gives the additional SNR limit due to amplitude noise in the oscillator. The curve in Figure 3-6 is then also the maximum achievable SNR for an oscillatory pulse with -150dBm of amplitude noise near frequencies  $w_s$  away from the carrier, assuming no noise in the mean of the fed-back pulse. There will be additional degradation due to variations in the mean, but they are the same as in the square-wave pulse and are expected to be small in a system with a good bandgap reference. If the oscillatory pulse has phase and amplitude noise, the total noise variance can be found as the sum of the two variances in Equation 3.41 and Equation 3.33.

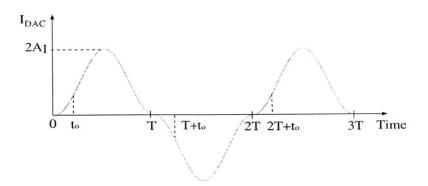

# 3.4 Multiple pulses per sampling period

Figure 3-3 assumes that the oscillator frequency is the same as the sampling clock frequency. Suppose instead that the cosine pulse frequency is n times the sampling frequency. An example feedback waveform is shown in Figure 3-8 for the case n=4 with four oscillator periods per sampling period.

Figure 3-8: Four pulses per sampling period.

Figure 3-9: Envelope of  $E_q/\Delta A_I(f_{\tau})$  with four oscillatory pulses per sampling period.

This DAC is much more sensitive to locking errors than a DAC with only one pulse per sampling period, since smaller values of locking error  $t_0$  can cause the clock edges to land in the middle of the cosine pulse, giving the same or worse sensitivity to clock jitter than the square wave pulse. However, amplitude and phase noise sensitivity are expected to improve due to averaging. A new error envelope for the phase noise is plotted in Figure 3-9. The error in the delivered charge is now most sensitive to noise at offset frequencies  $n^*w_s$  away from the sampling frequency. Thus a DAC with oscillatory output n>1 offers a trade-off between locking error and phase and amplitude noise sensitivity. The chosen value of n will likely depend on the accuracy of the locking scheme that can be built.

# **4** Prototype Design

The RF DAC concept could be used in many applications, including a direct transmit or low-IF DAC for communications systems, a direct digital synthesis (DDS) DAC, or a feedback DAC in a CT  $\Sigma\Delta M$ . The prototype implemented to demonstrate the RF DAC concept needed to be flexible in order to demonstrate, compare and fully test the concept. Specifically, the prototype needed the ability to test different ratios of oscillating and sampling frequency, compare square waves to oscillatory waves, adjust the phase between the sampling clock and oscillatory wave, handle a wide range of communications input vectors, and demonstrate high speed operation for communications applications. This section begins by discussing the specifications and architectural tradeoffs in implementing a prototype to meet all of these needs. The circuit design and layout is then discussed, focusing on the design trade-offs in implementing RF DAC that are different from those encountered when implementing a conventional DAC.

# 4.1 System specifications

Since wireless communications is pushing the development of high speed, high resolution converters, it seemed appropriate to pick a challenging wireless transmit specification to demonstrate the RF DAC concept. Table 4-1 lists a few of the current wireless transmission standards.

| System<br>Generation | Wireless<br>System | Base-station<br>TX<br>Frequency<br>(MHz) | Base-station<br>RX<br>Frequency<br>(MHz) | Channel<br>Bandwidth |

|----------------------|--------------------|------------------------------------------|------------------------------------------|----------------------|

| 2G                   | GSM 850<br>(MXM)   | 869-894                                  | 824-849                                  | 200kHz               |

| 2G                   | GSM 900            | 925-960                                  | 880-915                                  | 200kHz               |

| 2.5G                 | EDGE<br>(Europe)   | 925-960                                  | 880-915                                  | 200kHz               |

| 2G                   | GSM 1800<br>(DCS)  | 1805-1880                                | 1710-1785                                | 200kHz               |

Table 4-1: State-of-the-art wireless standards

The GSM 900/EDGE system was chosen as the target design specification due to its modern day wide deployment in the industry. However, RF DAC could just as easily be applied to any of the systems in Table 4-1.

The target specifications for a TX DAC in the GSM 900 system are shown in Table 4-2. A 17.5MHz bandwidth target is chosen as half the 35MHz total GSM band. Often this band is split among one or more suppliers, making a converter that operates on only half the band potentially desirable to industry. The SNR specification for a 17.5MHz band is calculated from GSM transmit masks found in reference [29]. These masks indicate that a -80dBc noise level is needed at 6MHz away from the signal over a 100kHz band. This requires -130dBc/Hz, which over a 17.5MHz band gives 57.5 dB. Note that these are the levels needed at the transmit antenna. Extra noise will be added from the filter and power amplifier still needed in the transmit signal path before the antenna. SFDR should also be greater than 80dBc. Since the bandwidth is so narrow, the only spur expected to fall inband is the third order intermodulation product (IMD3). For lower frequency communications DACs which require mixing and filtering stages after the DAC, other spurs could mix inband through the nonlinearities of these later stages. However, since the RF DAC concept eliminates the need for the extra mixers, the SFDR requirements can be relaxed to be closer to those actually needed at the antenna. The full scale output current of the DAC should be maximized, since power amplifiers are only ~20-40% efficient [39]. A large output amplitude can also increase the SNR by ensuring that the output is above the other sources of noise in the system. Pouring extra output power into the DAC doesn't make much sense unless the DAC is more efficient than the power amplifier. For reference, state-of-the-art low-IF DACs typically used in transmit applications have 10-20mA full scale output currents.

| Parameter                           | Value                                                                                                                                                                                     |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1/2 GSM 900 and EDGE<br>System Band | 933.75-951.25 MHz<br>(17.5MHz Bandwidth)                                                                                                                                                  |  |

| SNR                                 | > 60dB                                                                                                                                                                                    |  |

| Inband SFDR (IMD3)                  | > 80dBc                                                                                                                                                                                   |  |

| Full Scale Output                   | maximum, $> 20 \text{ mA} (13 \text{dBm} \text{with } 50\Omega, 10 \text{dBm} \text{ with } 25\Omega, 10-30 \text{dBm} \text{ output power}$ typically required in transmit applications) |  |

Table 4-2: RF DAC Target Design Specifications

# 4.2 **RF DAC Architecture**

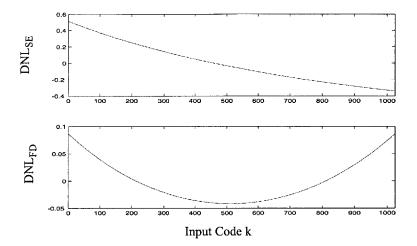

## **4.2.1** $\Sigma\Delta$ DACs and Mismatch Shaping

Nyquist rate DACs have an input and output bandwidth of half the clock rate. The number of bits in the DAC sets the output quantization noise floor. High resolution typically requires trimming in a Nyquist rate DAC [30]. In contrast,  $\Sigma\Delta$  DACs rely on oversampling to reduce the quantization noise in a narrow band of interest, thereby reducing the number of elements needed in a  $\Sigma\Delta$  DAC. Mismatch shaping offers the additional benefit of reducing the accuracy required in the DAC unit elements. A  $\Sigma\Delta$  DAC trades digital complexity and oversampling for reduced sensitivity to analog accuracy.

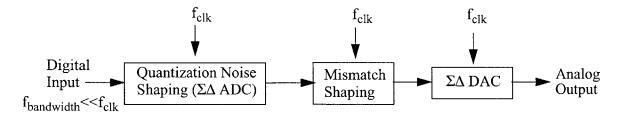

Figure 4-1 shows the input data path for a  $\Sigma\Delta$  DAC. The narrowband digital input data is shaped by a quantization noise shaper, typically a digital  $\Sigma\Delta$  ADC. A wealth of details about  $\Sigma\Delta$  ADCs, modulation, and quantization noise shaping can be found in [31]. Once the data is quantization noise shaped, mismatch shaping is employed to decide which elements of the DAC should be used to implement each input code. Mismatch shaping algorithms seek to mimic transfer functions that place zeros in the band of interest, thereby nulling the inband mismatch noise [32] [33]. Although theoretically any order mismatch transfer function centered around any band of interest is possible [32], there are trade-offs in complexity and cost of implementing different mismatch shaping transfer functions [33].

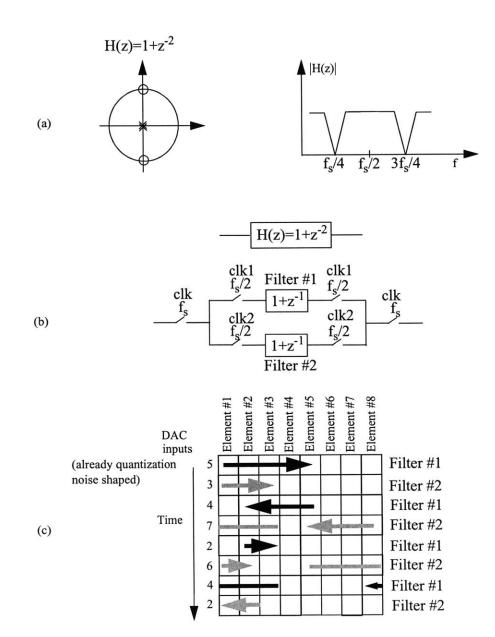

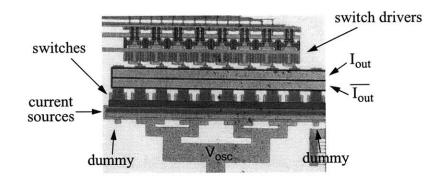

The N-Path filter approach to bandpass mismatch shaping is an efficient method that can be implemented in modern digital technology. An example is shown in Figure 4-2. The desired transfer function shown in Figure 4-2 (a) is  $H(z)=1+z^{-2}$ . This transfer function has a zero which will reduce the noise in a band near  $f_s/4$ . Figure 4-2 (b) shows an alternative implementation of H(z). This shows that two first order interleaved filters  $H'(z)=1+z^{-1}$  can be used to implement H(z). Figure 4-2 (c) shows the algorithm used to mimic H(z) in selecting the unit elements of an 8-element DAC that are used to implement each input code. The dark arrows and light arrows rep-

**Figure 4-1:** Data path for a  $\Sigma\Delta$  DAC.

resent the two filters. The input data is alternated between the two filters. Each filter rotates back and forth through the most recently used elements. The reason for reusing the most recently used elements is that the impulse response of H(z) is  $\{1,0,1\}$ , indicating that the errors made selecting the elements in the previous step need to be repeated.

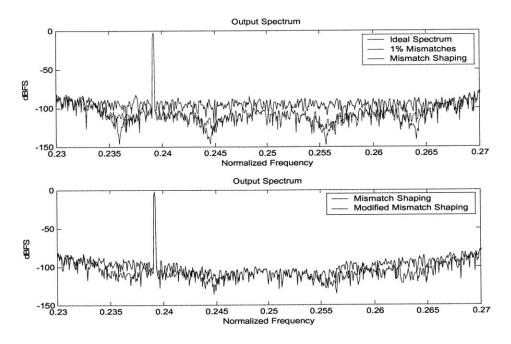

Reference [33] recognizes that mismatch shaping increases the data switching activity. Each element in the process of switching introduces noise and distortion. Modified mismatch shaping is introduced in an attempt to keep the number of elements switching constant. This reduces the switching distortion to a DC offset. The 'modified mismatch shaping' algorithm described in [33] offers a trade-off between mismatch shaping performance and switching noise performance.

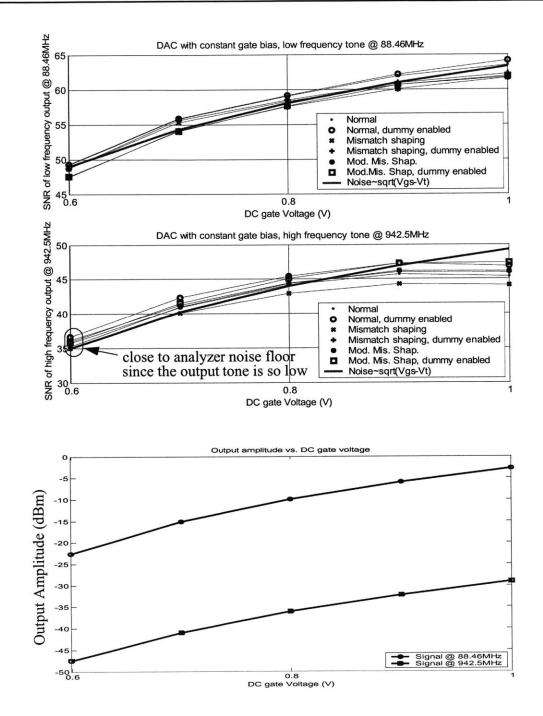

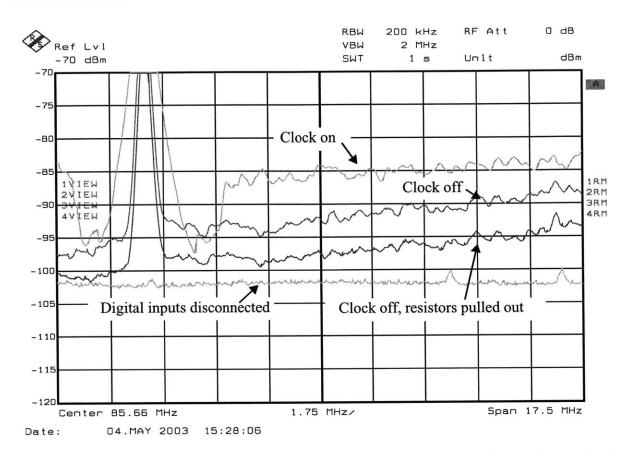

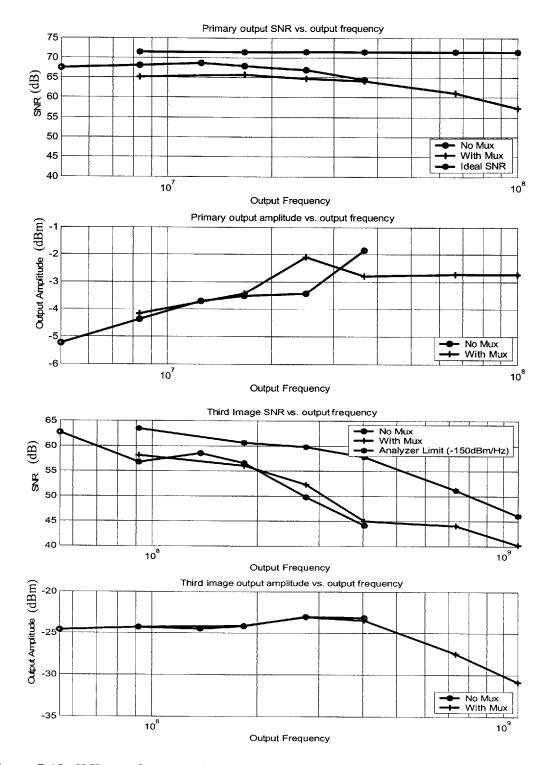

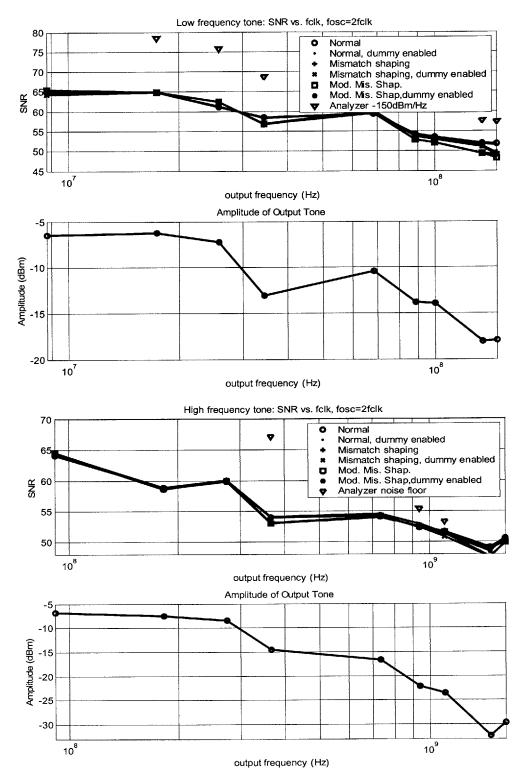

An example MATLAB simulation of an 8-element  $\Sigma\Delta$  DAC with a band centered around  $f_s/4$  is shown in Figure 4-3. The MATLAB simulation was performed using the Sigma-Delta Toolbox [34] [35]. The ideal spectrum has an SNR of 79dB. If implemented with elements matched to 1%, the SNR degrades to 65dB. Mismatch shaping as described in Figure 4-2 in the  $f_s/4$  band improves the SNR by 12dB to 77dB. Modified mismatch shaping improves the inband SNR by only 4.6dB to 69.6dB, but offers a near constant 3 elements switching per clock cycle. The simulation of Figure 4-2 only models 1% element mismatches, so no SNR improvements due to reduction in switching-induced noise can be seen.

Table 4-3 shows the mean and standard deviation of the number of elements switching for various input vectors. These values are simulated using Matlab and are the actual numbers for the test vectors. As expected, the modified mismatch shaping algorithm has the lowest standard deviation of the number of elements switching.

| Input vector                    | Meaning                                                                                                                                               | Mean<br>number of<br>elements<br>switching<br>(out of 8) | Standard<br>deviation of<br>number of<br>elements<br>switching |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------|

| 'Normal'<br>input vector        | sigma-delta quantization noise shaping, but<br>NO mismatch shaping                                                                                    | 1.9827                                                   | 1.1429                                                         |

| Mismatch<br>shaping             | quantization noise shaping, standard mis-<br>match shaping                                                                                            | 3.2658                                                   | 1.3645                                                         |

| Modified<br>mismatch<br>shaping | quantization noise shaping, mismatch shap-<br>ing with a 'modified' algorithm that attempts<br>to keep the number of elements switching a<br>constant | 2.655                                                    | 0.68                                                           |

Table 4-3: Switching statistics for various input vectors.

**Figure 4-2:** Mismatch shaping in  $\Sigma\Delta$  DACs (a) Desired mismatch shaping transfer function with zeros at fs/4. (b) Two-path filter implementation of H(z). (c) Example of element rotation to implement H(z) as in (b).

**Figure 4-3:** Example of mismatch shaping for a band centered at fs/4. The ideal spectrum has an inband SNR of 79dB. The spectrum with a 1% mismatch in the elements has an SNR 65.4dB. The spectrum with mismatch shaping has an SNR 77.5dB.

#### **4.2.2** Nyquist vs. $\Sigma \Delta$ DAC

The RF DAC concept could be applied to both Nyquist rate and  $\Sigma\Delta$  DACs. However, communication transmit applications require SNR and SFDR performance only in a narrow signal band. Outof-band distortion is filtered by the BPF shown in Figure 1-1. Although  $\Sigma\Delta$  DACs are currently not deployed or heavily researched for high speed applications, there are several good reasons why they are good candidates. This chapter is devoted to clarifying the advantages of  $\Sigma\Delta$  DACs at high frequencies.

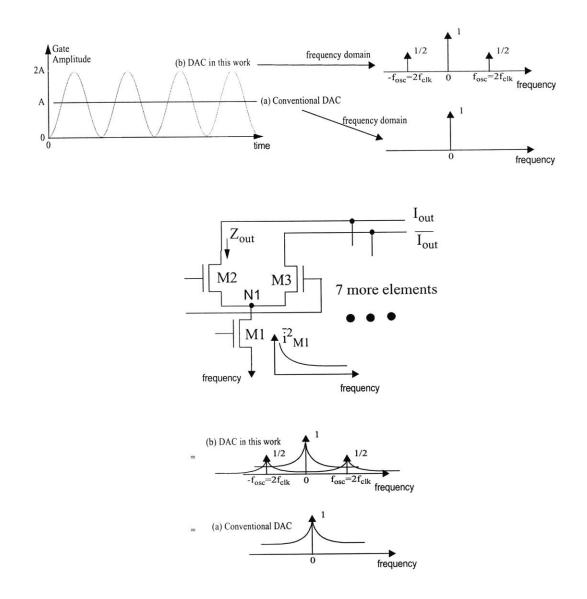

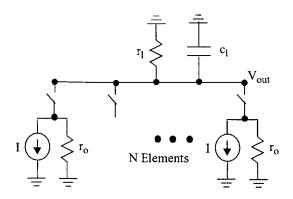

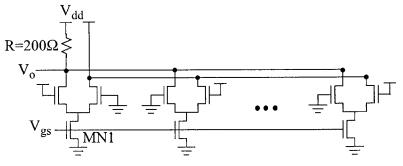

High frequency, high accuracy DACs are typically CMOS current steering architectures because they are fast and cost effective [36] [24] [37]. Unit current sources are used for the MSBs to achieve good static and dynamic performance. The static performance of these DACs is limited by the matching of the current source transistors in these unit elements. For instance, to achieve half of a least significant bit (LSB) accuracy at 10 bits requires a device with an area of about  $300\mu m^2$ . These large current source devices consume a lot of die area and require careful layout techniques to ensure good matching. Using a  $\Sigma\Delta$  DAC with mismatch shaping alleviates the matching constraint. If mismatch shaping is employed, inband resolution can exceed device matching. Thus smaller current source devices can be used to achieve the same inband resolution. Furthermore, there can be fewer elements in the DAC since quantization noise is also shaped out-of-band. This allows  $\Sigma\Delta$  DACs to be built with reduced area.

Large current source devices needed in a Nyquist rate DAC also have a large gate to source capacitance  $C_{gs}$ . If the high frequency oscillating control waveform needed for the RF DAC controls these gates directly, their combined  $C_{gs}$ 's will require a lot of power to drive. Smaller, fewer current sources achievable in  $\Sigma\Delta$  DACs have reduced input capacitance and require lower power to drive.

In addition to current source transistor matching,  $\Sigma\Delta$  DACs also shape static timing offset mismatches between the elements of the DAC. Although previous work [36] [24] [37] solves this problem in Nyquist rate DACs by careful layout, this may become intractable as speeds increase. Mismatch shaping can ensure that this source of distortion does not dominate.

Since mismatch shaping allows smaller current sources, these current sources have a lower capacitance at their drains. This drain capacitance can dominate the output impedance of the current source at high frequencies. Reduced drain capacitance improves the output impedance of the current source. This improved output impedance allows the elimination of the impedance-boosting cascode transistor found in conventional Nyquist-rate DACs. This will be discussed further in Section 4.3. The elimination of this transistor allows increased headroom so the DAC can be implemented with a reduced supply voltage.

Since the use of  $\Sigma\Delta$  DACs for high frequency transmit applications is a relatively new concept, the advantages over a Nyquist architecture are summarized below.

- The same inband noise can be achieved with lower area due to mismatch shaping.

- $\Sigma\Delta$  mismatch shaping also shapes static timing differences and offsets in the unit elements. This allows higher SNR and SFDR performance.

- Smaller devices mean smaller drain capacitance, giving larger output impedance at high frequencies. Elimination of the output impedance boosting cascode transistor allows DACs to be built with low supply voltages in aggressive technologies. It also gives associated power and area reduction since the cascode and its bias circuitry are eliminated.

• Smaller drive capacitance for the oscillating control waveform (advantage applies to RF DAC implementation only).

The primary disadvantage of using a  $\Sigma\Delta$  architecture is that the out-of-band quantization noise needs to be filtered. Transmit communications applications require a filter before the power amplifier anyway. The filter may have to be narrower than previously required, or extra bits added to the DAC to widen the bandwidth and relax constraints on the filter. Thus there is a tradeoff between the filter roll-off and bandwidth of the  $\Sigma\Delta$  DAC.

#### 4.2.3 Frequency Planning

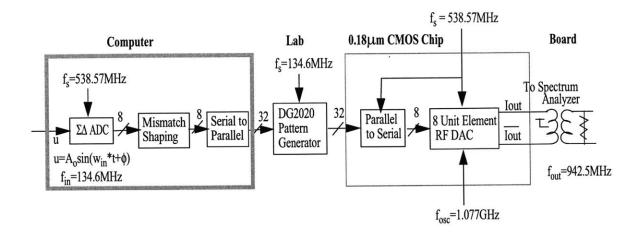

There are some interesting trade-offs in choosing the input, sampling, and oscillating control waveform frequencies. The system is intended for the GSM 900/EDGE specification as given in Table 4-2. Setting the band center at 942.5MHz gives a constraint on the relation between the control waveform frequency  $f_{osc}$  and the input frequency  $f_{in}$ :

$$f_{osc} - f_{in} = 942.5 MHz \tag{4.5}$$

The sampling frequency  $f_s$  is another design parameter. A large oversampling ratio (OSR= $f_s/2f_b=f_s/35MHz$ ) increases the SNR that can be achieved in a  $\Sigma\Delta$  implementation. Thus  $f_s=f_{osc}/2$  was chosen to maximize the OSR. Mismatch shaping in a  $\Sigma\Delta$  DAC is easier to practically implement and more effective if the additional following constraint is met [32] [33]:

$$f_{in} = \frac{af_s}{b} \tag{4.6}$$

where a and b are integers.

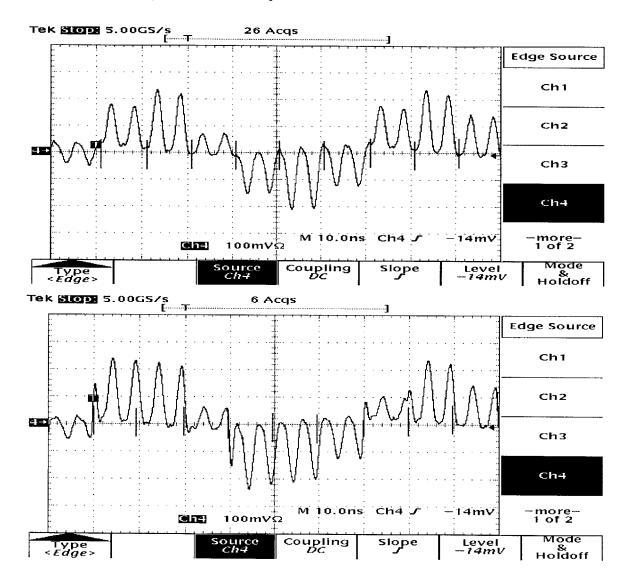

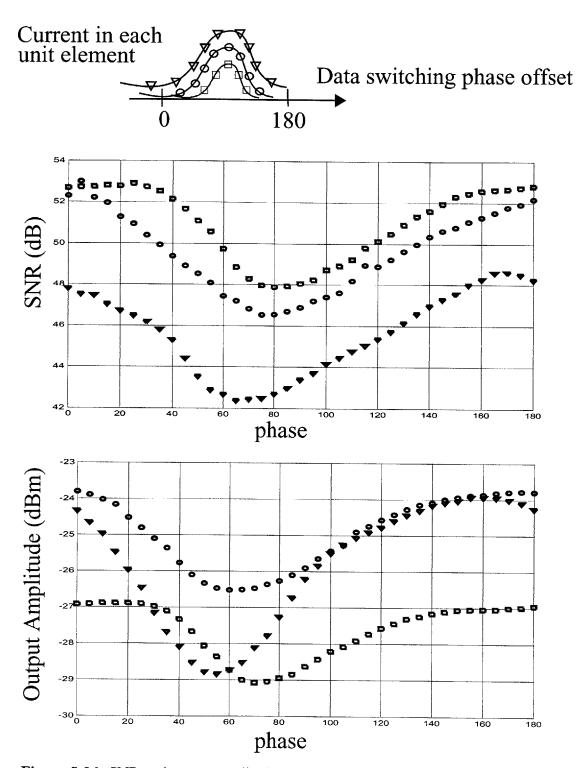

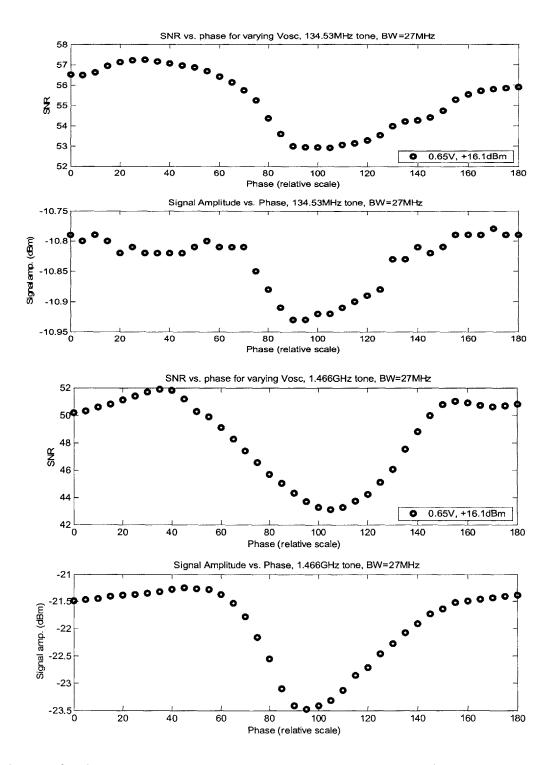

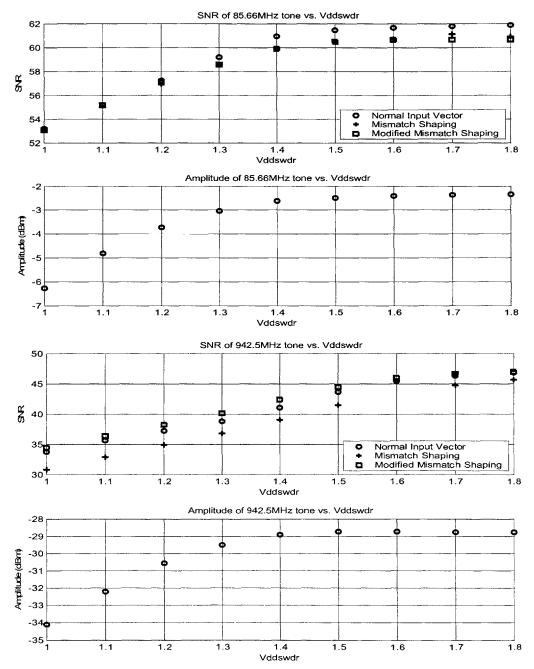

Figure 4-4 shows the RF DAC input and output frequency spectrums as a function of  $f_s$ ,  $f_{in}$  and  $f_{osc}$  for m = 4, 8. Large  $f_{in}$  is desirable so that the signal band is far away from any control wave-form feed through at frequency  $f_{osc}$ . However, the larger  $f_{in}$ , the faster the operating speed of the front end digital hardware operating speed.