## Research Article

# Rainbow: An Operating System for Software-Hardware Multitasking on Dynamically Partially Reconfigurable FPGAs

## Krzysztof Jozwik,<sup>1</sup> Shinya Honda,<sup>1</sup> Masato Edahiro,<sup>1</sup> Hiroyuki Tomiyama,<sup>2</sup> and Hiroaki Takada<sup>1</sup>

<sup>1</sup> Graduate School of Information Science, Nagoya University, C3-1 (631) Furo-cho, Chikusa-ku, Nagoya 464-8603, Japan <sup>2</sup> Department of VLSI System Design, College of Science and Engineering, Ritsumeikan University, 1-1-1 Noji-Higashi Kusatsu,

Shiga 525-8577, Japan

Correspondence should be addressed to Krzysztof Jozwik; kjozwik@acm.org

Received 28 February 2013; Revised 4 July 2013; Accepted 8 July 2013

Academic Editor: Michael Hübner

Copyright © 2013 Krzysztof Jozwik et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Dynamic Partial Reconfiguration technology coupled with an Operating System for Reconfigurable Systems (OS4RS) allows for implementation of a hardware task concept, that is, an active computing object which can contend for reconfigurable computing resources and request OS services in a way software task does in a conventional OS. In this work, we show a complete model and implementation of a lightweight OS4RS supporting preemptable and clock-scalable hardware tasks. We also propose a novel, lightweight scheduling mechanism allowing for timely and priority-based reservation of reconfigurable resources, which aims at usage of preemption only at the time it brings benefits to the performance of a system. The architecture of the scheduler and the way it schedules allocations of the hardware tasks result in shorter latency of system calls, thereby reducing the overall OS overhead. Finally, we present a novel model and implementation of a channel-based intertask communication and synchronization suitable for software-hardware multitasking with preemptable and clock-scalable hardware tasks. It allows for optimizations of the communication on per task basis and utilizes point-to-point message passing rather than shared-memory communication, whenever it is possible. Extensive overhead tests of the OS4RS services as well as application speedup tests show efficiency of our approach.

## 1. Introduction

The research on Dynamically Partially Reconfigurable (DPR) Field-Programmable Gate Arrays (FPGAs) is motivated by their superior flexibility, when compared to traditional FPGAs and Application-Specific Integrated Circuits (ASICs), as well as their potential to increase overall system performance and reduce dynamic power consumption by adapting to varying processing requirements of a system. DPR technology allows to partially change contents of the initial FPGA's configuration at run-time, without disturbing operation of the rest of the system [1]. It leads to a concept of virtualization of hardware resources where a small, however, dynamically reconfigurable array, multiplexing its hardware resources in time, may give an illusion of hosting circuitry by far exceeding its real capacity [2]. While the idea of virtual hardware managed by an OS was first proposed by Brebner in [3, 4], Wigley and Karney [5] defined a set of properties an Operating System for Reconfigurable Systems (OS4RS) should have. These properties have been refined later on as the research in this field progressed [6].

The main objective of the OS4RS is to provide an abstraction layer boosting development of applications composed of both software (SW) and hardware (HW) tasks. The HW task [7]/thread [8] can be thought of as a flow of execution running on an FPGA, sharing the reconfigurable resources with other HW tasks in a time-multiplexed manner. However, the concept of the HW task is different than that of an FPGA-based HW accelerator. The HW tasks are dynamic objects, just like the SW tasks in the traditional OSes [9, 10]. They may compete for reconfigurable computing resources with other HW tasks, request OS services such as communication, synchronization, or even activate other HW tasks. To accomplish that, the OS4RS must provide the HW tasks with an adequate interface to access those services. The OS4RS is responsible for control over all the aspects related to execution of SW tasks, that is, state management, dispatching, scheduling, and their intertask communication, just like a conventional OS does. In addition to that, it is responsible for all the aspects related to execution of HW tasks [6], that is, their allocation and deallocation on the FPGA, scheduling, state management, and intertask communication within and across SW and HW domains. While performing all these activities, the OS4RS must keep in mind applications' execution time, response times, and utilization of the FPGA resources, meeting requirements imposed on executed applications.

Apart of meeting the aforementioned basic requirements, the OS4RS may additionally provide some of the following more advanced functions, that is, *HW task preemption* by allowing suspension and restoration of HW task's execution, *Dynamic Frequency Scaling (DFS)* of HW task's clock (HW task clock scaling), *HW task migration* by allowing relocation of HW tasks on the FPGA, and *SW-HW task morphing* by allowing the tasks to migrate between SW and HW domains during their execution. All these functions aim at improving performance and reducing power consumption of an application running on top of the OS4RS.

Concept of the HW task and the SW-HW Multitasking OS4RS recently gained wider popularity in the industrial world and research community due to promising results of High-Level Synthesis (HLS) technology [11]. When combined with it, the concepts of the HW task and OS4RS make it easier for software developers with weak or no background in hardware design to take advantage of the computing potential of reconfigurable hardware. SW-HW partitioned applications can be entirely written in the same way, using high-level description language like C and then mapped to either Central Processing Unit (CPU) or FPGA depending on the performance and power consumption requirements imposed on the application. Yet, further optimizations on the software or hardware side could be allowed by supporting assembly or Hardware Description Language (HDL) as a language to describe SW and HW tasks, respectively.

The contributions to the state-of-the-art OS4RS made by this work can be grouped into three following research topics.

- (i) OS4RS Architecture. It proposes a complete and novel model and implementation of the OS4RS architecture supporting preemptable and clock-scalable HW tasks. The proposed OS4RS is composed of a conventional off-the-shelf Real-Time Operating System (RTOS) kernel which provides the SW multitasking functionality and created reusable extension, called Rainbow, which adds the HW multitasking capability.

- (ii) Scheduling Mechanism. It proposes a novel, lightweight software-based scheduling mechanism allowing for timely and priority-based reservation of reconfigurable resources, which aims at use of HW task preemption only at the time it brings benefits to the total performance of a system. The architecture

of the scheduler and the way it schedules allocations and deallocations of the HW tasks on the FPGA result in shorter latency of Application Programming Interface (API) calls, thereby reducing the overall OS overhead.

(iii) Intertask Communication. It shows a novel model and implementation of an easily scalable channelbased inter-task communication and synchronization suitable for SW-HW multitasking with preemptable and clock-scalable HW tasks. The model allows for optimizations of the communication on per task basis and takes advantage of more efficient point-topoint message passing rather than shared-memory communication, whenever it is possible.

The remaining contents of this paper are organized as follows. In Section 2, related research works are described, and work presented in this paper is compared with them. Section 3 gives a general overview of the developed OS4RS and its architecture. Section 4 introduces the base OS kernel used in our implementation of the OS4RS, whereas Sections 5, 6, 7, and 8 show implementation details of HW tasks' reconfiguration, scheduling, management and intertask communication services provided by the developed extension. Section 9 presents results of extensive evaluation of the OS4RS's services and application speed-up tests. Finally, Section 10 concludes the work and reveals area of prospective research.

## 2. Related Research

Several previous research works were devoted to design of the OS4RS or its certain services. While some of the works provide only a means of run-time management of HW accelerators [12-17], the others provide a proper support for HW tasks [18-21]. This is accomplished by supplying the HW tasks with a dedicated OS interface. BORPH [18] is a Linux extension which targets multi-FPGA platforms where each HW task is implemented on a separate FPGA. The HW tasks are modeled with a Simulink [22] and provided with an equivalent API to the one that SW tasks have. ReconOS [19, 20] targets DPR FPGAs where HW tasks are implemented as reconfigurable modules on a common FPGA. It is implemented as an extension for Linux and eCos [10] and utilizes a unified POSIX-compliant API for SW and HW tasks. HThreads [21] presents another OS which is a Linux extension; thus it is also based on a POSIX-compliant API. An interesting aspect of that work is architecture of the OS interface for HW tasks which gives them support for dynamic memory allocation and recursive execution of functions. That work, however, lacks the support for DPR. An interesting work is shown in [23] where tasks can migrate between software and hardware domains during their execution, that is, the work supports software-hardware morphing.

In this paper, we present a model of a portable and lightweight OS4RS built as an extension to existing OS kernel. The presented OS4RS treats HW tasks as active computing objects. Moreover, we show a complete implementation of this model which fully utilizes DPR. The implementation is based on Toyohashi OPen Platform for Embedded Real-time Systems (TOPPERS) [24] Advanced System Profile (ASP) RTOS kernel compliant with an uItron [9] API specification. The uItron specification is widely used in the Japanese industry, research communities, and the European automotive industry.

Several works were devoted to scheduling and placement of HW tasks (or reconfigurable hardware accelerators) on the FPGA [25-31]. In [25], an online scheduling and placement algorithm targeting 1D and 2D model of reconfigurable area is presented. The work considers nonpreemptable HW tasks which execute independently of each other. On the contrary, works in [26-30, 32] present scheduling strategies for reconfigurable area divided into fixed slots. As modern FPGA architectures are becoming increasingly heterogeneous in terms of their resources, this model of a reconfigurable area seems to be more applicable. [26] presents a mixed offline/online scheduling strategy, where the Control Data Flow Graphs (CDFGs) representing applications are analyzed offline by means of customized list scheduling techniques, and then extracted parameters are used to optimize the scheduling result at run-time. The online scheduling step is implemented in hardware as dedicated logic. [27] presents another hardware implementation of a run-time scheduler utilizing information extracted from the CDFGs. Similarly to work presented in [26]. Configuration Access Port OS (CAP-OS) [31] shows a mixed offline/online scheduling strategy utilizing information extracted from the CDFGs and is implemented on Xilkernel OS [33] running on a microprocessor. In the approaches presented in [26, 27, 31], HW tasks comprising the CDFGs execute in a nonpreemptive manner till their completion. Work in [32] presents a non-preemptive scheduling strategy where HW tasks may voluntarily relinquish the allocated resources at certain points of their execution. Works in [28, 29] present a Deadline-Monotonic- (DM-) based scheduling approach for real-time systems, where HW tasks' reconfigurations rather than executions are scheduled. The work does not consider data dependencies between HW tasks. The works in [28, 29] and CAP-OS [31] do not support preemption of the HW tasks' execution but allow for termination of their reconfigurations.

This paper presents a simple preemptive priority-based scheduling mechanism with certain customizations allowing for HW task prefetching and timely reservation of reconfigurable resources. Similarly to works presented in [26–30, 32], it targets systems where the reconfigurable area is divided into fixed regions. Unlike the works in [28, 29, 31], this work allows for true preemption of the HW task's execution phase. The concept of reservation of reconfigurable resources has been already introduced in [29, 30]. In [29], one or more slots are reserved at the design time, exclusively for a given set of high-priority tasks, and then used by these tasks only. In [30], reconfigurable slots, called tiles, are reserved (locked) by the most frequently executed HW tasks. Unlike those works, the work presented in this paper allows for timely reservation of the resources, based on blocking time of HW tasks, which can be adapted to match the latency characteristics of a given system. The timely reservation of the resources will allow for preemption of the HW task only after a specified time

from the point the HW task blocks. While the presented scheduling mechanism is implemented mostly in software, it allows for overlapped execution of the scheduler and HW tasks' reconfigurations. The presented work is suitable for both, set of independent HW tasks as well as set of HW tasks with data dependencies described, for example, in form of CDFGs.

In the first case, the overall ability of preemption may be used to prevent HW tasks from starving for reconfigurable resources in case another task has been executing for a very long time. Ability of preemption after a specified time may be used to allow execution of another HW task, while the currently running task blocked, waiting for data for a specified time. Yet, at other times, the preemption and related reconfiguration overhead can be avoided. It can be beneficial especially in systems with memory virtualization and systems with networking where data delivery latencies may be variable and higher than reconfiguration times present in today's DPR FPGAs. Furthermore, it may be also used as a deadlock recovery measure.

In the second case, where there are data dependencies between some HW tasks, the set of tasks could be analyzed offline and divided into set of independent CDFGs. These could be further analyzed and appropriate setting of HW tasks priorities and sequence of their activations generated in form of API calls.

This part is assumed to be done by an offline tool and is considered orthogonal to the work presented in this paper. While the prefetching capability presented in this work may allow for efficient execution of such CDFGs, the timely reservation of reconfigurable resources may be used to allow execution of another CDFG, while the currently executing one is waiting for data.

Several works presented inter-task communication mechanisms targeting SW-HW multitasking. Works in [8, 34] utilize POSIX-like communication and synchronization mechanisms known from traditional SW multitasking OSes, such as message queues, semaphores, and apply them to the SW-HW multitasking domain. In both works, HW tasks request the communication and synchronization services via a dedicated OS interface module. In [34], the inter-task synchronization objects are located in software and are accessed by delegate SW tasks executed on behalf of the HW tasks. In [8], the corresponding objects are implemented in hardware. ReconOS [34] additionally implements HW-HW message passing communication with FIFO buffers which are directly connected to the OS interface for HW tasks. While the additional fixed FIFO buffers avoid software processing overhead, the approach lacks scalability. Although the hardware implementation given in [8] significantly reduces the processing overhead, it only allows for shared memory communication which does not seem to be suitable for all HW-HW inter-task communication.

The work in [35] shows an inter-task communication mechanism for SW and HW tasks based on additional software-hardware codesigned virtualization extension for Linux. The extension uses the concept of memory paging. The hardware side of the extension consists of specialized a local storage for pages and perform address translation for the HW task's memory accesses. The software side of the extension handles copying of pages during misses as well as their speculative prefetching to the local memory. Thanks to the created extension, SW and HW tasks may communicate with each other transparently, without knowing whether their communication partner is located in hardware or software. This results in easier programming and better application's portability. While it is an interesting approach, it only supports shared memory communication and does not consider run-time reconfiguration of HW tasks.

An interesting work is shown in [36] where FPGA's Configuration Memory (CM) is used for communication between HW tasks. The data to be transferred is read from a sending HW task's buffer through the configuration port of the FPGA and stored in some different location in the CM which corresponds to a buffer of the receiving HW task. While this approach avoids signal routing issues related to HW Task's relocation, it creates a significant overhead for communication.

In works [18, 37, 38], SW and HW tasks communicate through FIFO buffers. FUSE [12] shows implementation of an SW-HW communication interface for dynamically reconfigurable HW accelerators. In that work, the communication drivers located on the software side can be loaded dynamically, thereby providing a means of their run-time customization. However, the hardware side of the interface is fixed, and the work does not show implementation in which the accelerators are dynamically reconfigured. One of the interesting works on channel-based communication for SW-HW Multitasking systems is presented in [39]. In this work, the tasks communicate through dynamically allocated channels managed by a hardware-based communication manager. Although performance advantages of the hardware implementation are mentioned, the work does not allow for optimizations based on a type of communication. Moreover it does not actually support blocking communication semantics as our work does.

We show a complete model and implementation of a channel-based intertask communication and synchronization allowing for Point-2-Point (P2P) communication between the tasks, similarly to [39]. Unlike [18, 37–39], it allows for optimization of the communication based on a given pair of tasks. This is achieved by, firstly, matching the type of the channel to communication requirements and, secondly, by allowing the channel interfaces to be allocated and deallocated together with HW tasks. Unlike [39], this work allows for truly blocking communication semantics. Unlike the previous works, the presented inter-task communication and synchronization mechanism is suitable for clock-scalable and preemptable HW tasks.

Dynamic Frequency Scaling (DFS) [40, 41] makes it easier to balance the trade-off between the performance and power consumption of the resources held by an HW task. It has been widely used in single and multicore CPUs as a method to balance the trade-off between low power consumption and high performance depending on current processing demands of applications. In the field of FPGAs, previous works either only discussed this mechanism in general [42, 43] without the context of HW multitasking or only assumed its presence in their scheduling mechanisms without showing any implementation [31]. The works in [44, 45] show implementation of a HW task utilizing the regional clocking resources available in Xilinx FPGAs in order to enhance HW task relocation and provide means of discrete clock division. It is, however, not a substitute for continuous clock-scaling functionality, but rather its enhancement.

This work proposes a complete model and implementation of the OS4RS supporting preemptable and clock-scalable HW tasks. The DFS presented in this work is supported by all services provided by the OS4RS, that is, management, scheduling, reconfiguration, and inter-task communication and synchronization.

### 3. OS Architecture

*3.1. Architecture Model: Overview.* Instead of building the OS4RS completely from scratch, we decided to use an already available OS kernel with a well-established API as a base and create a HW multitasking extension for it. This was done to utilize already available SW multitasking support and to facilitate future reuse of already available applications. The HW multitasking extension is general enough, so that a variety of existing SW multitasking RTOS kernels [10, 24, 33] could be used as its base.

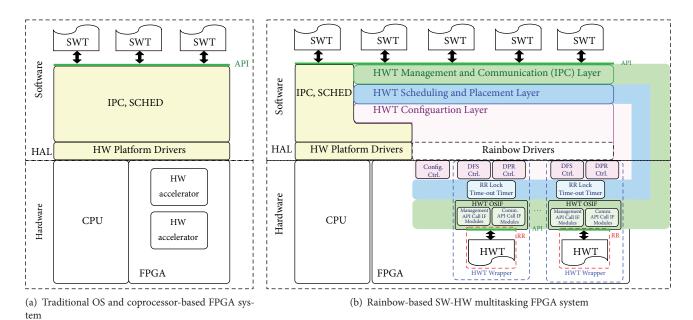

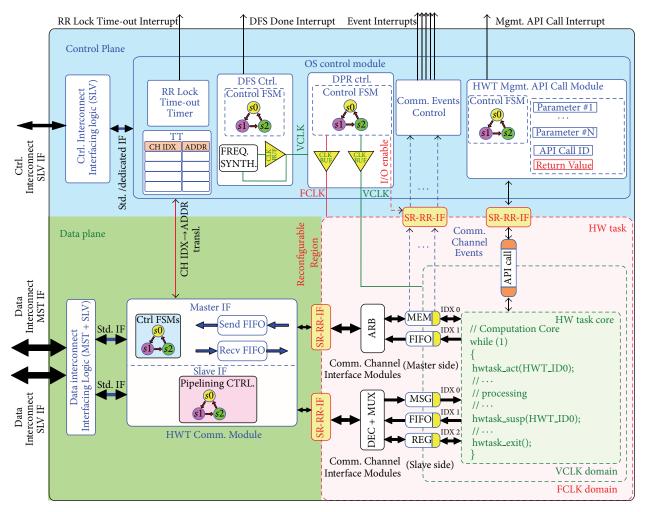

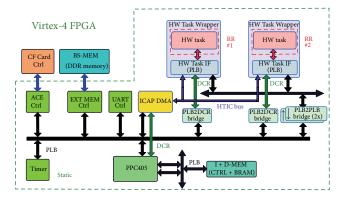

The software-hardware codesigned extension, called Rainbow, follows a layered architecture in both software and hardware, which improves code reuse and portability and helps in grouping different OS services. An abstracted view of the developed OS4RS architecture is shown in Figure 1(b). The HW Task Management and Communication Layer manages HW tasks' high-level execution state, reflecting the API calls made by interacting SW and HW tasks, as well as inter-task communication and synchronization. The state of SW tasks is managed independently, by the base OS kernel. The HW Task Scheduling and Placement Layer is responsible for scheduling allocations, deallocations, and preemptions of HW tasks as well as process of their clock dynamic frequency scaling. Finally, the HW Task Configuration Layer, which is specific to a given FPGA architecture, manages the related low level aspects of these activities.

The software part of the extension is executed on a CPU together with the base OS kernel, whereas hardware part is implemented on an FPGA. Hardware part is comprised of a Configuration Controller which belongs to the HW Task Configuration Layer and HW Task Wrappers whose modules logically belong to all three layers. The Configuration Controller gives a physical means of allocation and preemption of HW tasks by providing an interface to access the FPGA's CM. The HW Task Wrapper contains a Dynamic Partial Reconfiguration (DPR) Controller which also belongs to the same layer as the Configuration Controller. It handles the low-level physical aspects of the DPR technology related to HW task's allocation and preemption [46–48]. The Dynamic Frequency Scaling (DFS) Controller is another module which belongs to the HW Task Configuration Layer. It provides access to clock frequency scaling feature of HW tasks. The Reconfigurable

FIGURE 1: OS architecture model: Traditional versus Rainbow-extended.

Region (RR) Lock Timer, being part of the HW Task Scheduling and Placement Layer, is used to implement a mechanism of timely reservation of reconfigurable resources, described in Section 6.2. Finally, the Management API Call Interface Modules and the Communication API Call Interface Modules belong to the HW Task Management and Communication Layer. They comprise a Hardware Task Operating System Interface (HWT OSIF) which is an interface for HW tasks to access the OS services.

Figure 1 shows the relationship between SW tasks and HW tasks in a traditional and Rainbow-extended OS. In the traditional OS, SW tasks use HW platform drivers provided by the *Hardware Abstraction Layer (HAL)* to access the FPGA resources. These drivers have to be customized on per HW accelerator basis, thus making porting difficult. In the OS4RS based on the Rainbow extension, the HW tasks are treated as active objects which have access to the same OS services as SW tasks do. The services are accessed by means of a high-level API, which improves application portability. The Rainbow extension uses HAL drivers internally, only to bind together its software and hardware components.

There are two types of service calls the SW and HW tasks can make: *Management API Calls* and *Communication API Calls*. The *Management API Calls* give the tasks an ability to directly control their state and the state of other tasks. It includes calls for task activation, termination, task-dependent synchronization, for example, suspension and resumption, as well as clock management functionality for the HW tasks, that is, DFS calls. The *Communication API Calls* give the means of communication between tasks and task-independent synchronization, that is, the one implemented by communication primitives.

When compared to the traditional OSes, the inter-task communication implemented by Rainbow is based on a concept of channel adopted from Electronic System-Level (ESL) Design Methodology [49]. The channels are abstract objects encapsulating communication between two computing processes. In our case, the channels are referenced by their Identifiers (IDs) and provide the tasks with an easy interface to access communication and synchronization resources of the OS.

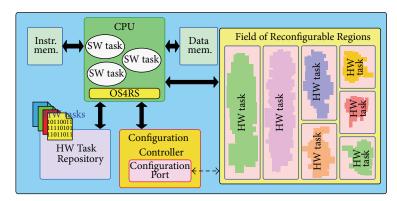

3.2. A Reconfigurable Hardware Architecture Model. The developed OS4RS assumes the hardware model of a reconfigurable architecture shown in Figure 2. SW tasks execute on a CPU. HW tasks are represented by configuration bitstreams stored in the *HW Task Repository* and take a form of digital circuits once configured in the *Reconfigurable Region (RR)* by means of the *Configuration Controller*.

Depending on placement restrictions imposed on HW tasks, we can distinguish different models of reconfigurable area [6]. 2D model is the most flexible and does not impose any restrictions on the placement of the tasks, provided that they do not overlap. In 1D model vertical dimension is fixed, but allows unconstrained placement in horizontal dimension. Finally, in fixed-slots model tasks can be only placed at predefined positions. An additional, fixed-regions model can be thought of as a generalized fixed-slots model in which not all of the regions are of the same dimensions. This may be a disadvantage by limiting task relocation to compatible regions only, but on the other hand allows them to better match their associated regions, thereby alleviating the problem of region's internal fragmentation.

Due to increasing heterogeneity of FPGAs, accompanied by limitations of frame-based Configuration Memory's architecture and Partial Reconfiguration (PR) technology, the last two models are by far the most suitable for recent FPGA devices and their supporting design tools. The fixedregions model is currently widely used by Xilinx and Altera and has been also adopted in our model of reconfigurable

FIGURE 2: Reconfigurable architecture model.

architecture. In this model, HW tasks are prepared offline and loaded at run-time to predefined regions. The HW tasks have also their state which can be saved and restored if the preemption mechanism is available. Furthermore, they can migrate between compatible regions if the bitstream relocation [36, 50–53] is supported.

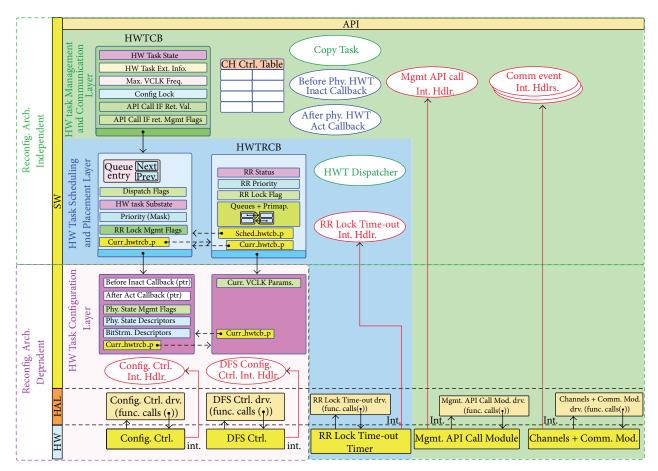

*3.3. Rainbow Extension: Software Structures Overview.* The details of the architecture of the software side of the Rainbow extension are given in Figure 3.

The key structures of the software side of the extension are the arrays of *HW Task Control Blocks (HWTCBs)* and *HW Task Region Control Blocks (HWTRCBs)* which span all three layers.

Entries in the arrays of *HWTCBs* and *HWTRCBs* correspond to the HW tasks and RRs with given IDs. The HW tasks' IDs are currently considered separately from those of SW tasks, managed by the base OS. As the task IDs are passed to *Management API Calls*, this requires that different API calls are used for SW and HW tasks. This is not the case with *Communication API Calls* which use a common ID space for all channels. The common ID space for both SW and HW tasks would allow for entirely unified API for SW and HW tasks. It is left as a part of future work.

3.3.1. HW Task Configuration Layer. Part of the HWTCB located in this layer holds information such as memory address and size of the bitstream(s) needed to configure a given task as well as initialize, save, and restore its state. It is represented by the *Bitstream Descriptors* and the *Physical State Descriptors* initialized during OS4RS boot-up, while the bitstreams representing the HW tasks are read from an external nonvolatile storage and stored in a faster volatile memory serving as a bitstream repository.

*3.3.2. HW Task Scheduling and Placement Layer.* The key structure related to scheduling is an array of *HWTCBs* queues ordered by priority, that is, ready queues. Each RR, where HW tasks are allocated, has an independent array of ready queues associated with it. It is located in the *HWTRCB*.

This layer implements a preemptive scheduling with timely and priority-based resource reservation, called *RR*

*Locking*, described in details in Section 6. The hardware side of this layer implements the *Time-out Timer* used in the *RR Locking*. The *HWT Dispatcher* shown in Figure 3 is an additional SW task which is started whenever a scheduling decision results in requests for allocation, deallocation, or clock management. The *Dispatch Flags* entry in the *HWTCB* is used to pass information about actions to be performed between the scheduler and the *HWT Dispatcher*.

3.3.3. HW Task Management and Communication Layer. Each HWTCB in this layer stores the HW task state and extended information, such as, for example, ID of the system it was made for, retrieved from the configuration bitstream upon OS initialization. It also holds control information of the Management API Call Module such as whether the HW task was blocked as a result of executing the API call (API Call IF Mgmt Flags), and the return value that should be passed to it when it is released from blocking and allocated again. The API Call IF Mgmt Flags are used to control operation of the Finite State Machine (FSM) located in the Management API Call Module. The control information entries are updated by the Management API Call Interrupt Handler and After Physical HWT Activation Callback.

The Management API Call Interrupt Handler is executed whenever a HW task makes a Management API Call. The Before Physical HWT Inactivation and the After Physical HWT Activation callbacks are functions of the HW Task Management and Communication Layer registered and executed within the HW Task Configuration Layer. The first callback contains code which is to be executed just before the HW task is deallocated or its clock is suspended, whereas the second one contains the code to be executed just after the HW task is allocated or its clock is switched on.

The *Config Lock* field of the *HWTCB* is used to implement a configuration locking mechanism used by the inter-task communication. The idea behind it is to prevent possible HW task deallocations when the transfer over the channel connecting the task is in progress.

A key structure in the *HW Task Management and Communication Layer* is the *Channel Control Table* which controls the communication and synchronization over channels. The table is updated by the *Comm Event Interrupt Handlers*, SW Task API calls, *Copy Task*, and *Callbacks* which act together

FIGURE 3: Rainbow extension—software structures and software-hardware interface.

in order to provide communication services to SW and HW tasks.

The *Comm Event Interrupt Handlers* are interrupt handlers executed in response to channel events which are generated by the hardware side of the OS4RS whenever HW tasks access the communication channels. SW Task API calls are communication calls provided by the OS4RS which are executed by the SW tasks. The *Copy Task* is an additional SW task executed whenever a direct point-to-point (P2P) communication between the HW tasks is not possible. All of them are described in details in Section 8.

#### 3.4. Rainbow Extension: Hardware Components Overview

*3.4.1. Configuration Controller.* The Configuration Controller provides physical means of allocation and preemption of HW tasks. It accomplishes this job by talking to the configuration port of the FPGA and transferring configuration bitstreams representing HW tasks between their storage memory and FPGA's CM.

3.4.2. HW Task Wrapper. The HW Task Wrapper can be divided into static part, that is, *Static Region (SR)*, and reconfigurable part, that is, *Reconfigurable Region (RR)*. Logically, the RR serves as a container where HW modules,

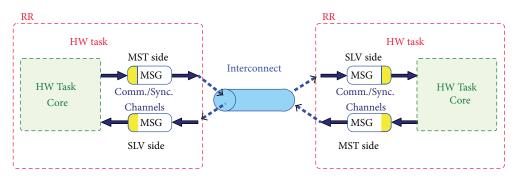

representing HW tasks, can be plugged in. Physically, once the whole system is programmed on an FPGA, the RR becomes an area on the FPGA where HW tasks are allocated and deallocated. Figure 4 shows the *HW Task Wrapper* and the *HW Task* allocated in the RR.

To alleviate timing issues during placement and routing of a DPR system, the boundary between the SR and the RR must be designed in an appropriate way. More specifically, all signals crossing the SR-RR boundary should be registered by inserting FFs before they are passed to the other side of the boundary. In the developed *HW Task Wrapper*, the SR side of the boundary is always registered, whereas the RR side is registered on per task basis.

The HW Task Wrapper is composed of two planes: a Data Plane and a Control Plane. The Data Plane contains an HW Task Communication Module and a Data Interconnect Interfacing Logic module, whereas the Control Plane is composed of an OS Control Module and a Ctrl Interconnect Interfacing Logic module. The OS Control Module is further divided into an RR Lock Time-out Timer, a Translation Table (TT), a DFS Controller, a DPR Controller, an HW Task Communication Event Control, and an HW Task Management API Call Module.

The HW Task Communication Module, the HW Task Communication Event Control, the TT, and Communication

FIGURE 4: HW Task and HW Task Wrapper.

*Channel Interface Modules* located in the HW Task logically belong to a group of *Communication API Call Interface Modules*. The HW Task Management *API Call* Module and the API Call channel located in the HW Task logically belong to another group called *Management API Call Interface Modules*. Both groups form the *HWT OSIF* and described before. All *HW Task Wrapper's* modules are briefly described below.

*HW Task Communication Module.* The *HW Task Communication Module* and the *Data Interconnect Interfacing Logic* module give access for master- and slave-side *Communication Channel Interface Modules* to the physical interconnect. The *HW Task Communication Module* contains additional FIFO buffers and pipelining logic. The FIFO buffers are required by the master interface of the *Data Interconnect Interfacing Logic* module in order to allow burst transfers. The pipelining logic is required by the slave interface of the *Data Interconnect Interfacing Logic* module to allow for burst transfers to and from the storage located within the RR as transfers over the SR-RR boundary undergo additional latency. *Translation Table (TT).* The communication channels are accessed through the channel interface modules by providing their IDs. These IDs are assigned globally and used by all channels in the system. Locally, within each HW task, channel interface modules are assigned index numbers. The index numbers are used to facilitate mapping of channel interfaces on both sides of the channel to their location in the address space.

The *Translation Table* is used to translate the channel index, provided by the master-side interface, into address of the slave-side interface located in another HW task. Thanks to local index addressing of channels, rather than global ID addressing, the size of the table can be reduced to the maximum number of indices allowed per HW task.

*Communication Events Control.* This module is used to collect the events from all channel interface modules located within a currently allocated HW task and notify the software side of the OS about their occurrence. When it happens, a dedicated interrupt handler, that is, the *Comm Event Interrupt Handler* mentioned previously, is executed. It contacts the *Communication Events Control* to retrieve the index of the channel generating the event.

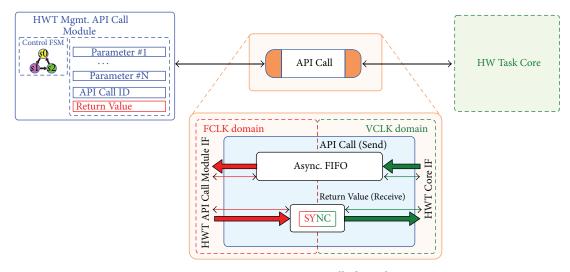

*HW Task Management API Call Module.* The *HW Task Management API Call Module* serves as a middle man between the HW task and the software side of the OS4RS, whenever the HW task makes a *Management API Call*. It is described in Section 7.2.

*DFS Controller*. The *DFS Controller* is used to implement the very feature of dynamic clock frequency scaling. It consists of the main part, being the *Frequency Synthesizer* module itself and the wrapping logic built around it. As the *Frequency Synthesizer* module, a Digital Clock Manager (DCM) [54] or Phase-Locked Loop circuits common in modern FPGAs may be used. The wrapping logic provides the OS4RS with an interface to control the process of frequency scaling.

DPR Controller. The Dynamic Partial Reconfiguration (DPR) Controller is used to control the low-level aspects of reconfiguration and preemption of HW tasks. This includes isolation of the SR-RR boundary during reconfiguration and preemption as well as clock suspension.

*RR Lock Time-out Timer.* The *RR Lock Time-out Timer* is used in implementation of the developed scheduling mechanism. It is a simple count-down counter, started and stopped by the OS4RS, which generates an interrupt once its reaches value zero.

3.4.3. HW Task: Architecture. From the architectural point of view, the HW Task, shown in the bottom right corner of Figure 4, is composed of a HW Task Core, Communication Channel Interface Modules (referred to as channel interface modules), and the remaining HW task glue logic. The HW Task Core represents a computational part of the HW Task, which can be either synthesized from a high-level description using an HLS tool or already provided in form of an HDL description.

The *HW Task Core* communicates with an outside world through ports using standardized signal protocols. The protocol can be either nonblocking or blocking. The channel interface modules, shown as white-yellow ovals connected to the *HW Task Core*, are implemented keeping these simple and standardized protocols in mind. Depending on the side of channel where they are located, the channel interface modules can be of two types: master side and slave side. The type defines which module is responsible for starting the transaction over the physical interconnect.

The channel interface modules are part of the *HW Task* and reconfigured along with it. The channel interface modules implement local storage space for the data to be sent or received by the *HW Task Core* over the physical interconnect. They are also the key components interacting with the software side of the OS4RS during initialization and completion of the data transfer over the channel.

The slave-side interfaces of the communication channels are accessed from outside the *HW Task Wrapper* as a part

of one contiguous address space defined by the *HW Task Wrapper*. This allows for a fixed interface between the static part of the *HW Task Wrapper* and the RR containing the *HW Tasks*, irrespective of the number and type of channels *HW Tasks* use. The fixed interface is required by the current DPR design flows provided by the major FPGA manufacturers, that is, Xilinx [46] and Altera [47]. As a result, the multiplexers and address decoding logic must be a part of the *HW Task's* glue logic.

If the number of master-side interface modules is bigger than one, the *HW task* glue logic will also contain a lightweight arbiter controlling access of those interface modules to the *HW Task Communication Module*, in turn, giving them access to the physical interconnect.

The *API Call* channel, shown in Figure 4, is a special kind of channel. It is used by the *HW Task Core* at the time of making the *Management API Call*.

The *HW Task* works in two, potentially unrelated clock domains, that is, *Fixed Clock (FCLK)* domain and *Variable Clock (VCLK)* domain. The *FCLK* domain is controlled by a system-wide clock, whose frequency is fixed during operation of the system. On the other hand, the clock in the *VCLK* domain can be dynamically adapted depending on the performance and power consumption needs of an application, provided that the maximum frequency of operation of the related logic allows for it. The *HW Task Core* works in the *VCLK* domain, whereas the glue logic works in the *FCLK* domain, just as the *HW Task Wrapper* does. The channel interface modules work partly in the *FCLK* and partly in the *VCLK* domain. They encapsulate the details of clock domain crossing to the *HW Task* glue logic and the *HW Task Core*.

3.4.4. HW Task: Architecture's Pros and Cons. The ability of the HW Task Core to operate at different frequencies solves many issues and lets designs avoid the limitations of the DPR technology. The HW Task Cores which can work at much higher frequencies than the rest of the system are not restricted by it anymore. On the other hand, the HW Task Cores which may have problems in achieving frequencies defined by the rest of the system will also not impose any limitations on the system itself. Although in the cases above, bridge logic could be used on the interconnect, the fixed clock in the RR would still make the slowest HW Task limit the performance of the other tasks that may be allocated to this RR. The downside of this approach is, however, increased latency of data communication.

A fundamental question about the architecture of the proposed *HW Task*, that may arise, concerns placement of the channel interface modules within the RR. Since it is better to transfer data directly between HW tasks rather than using shared memory as an additional middle man, the channel interfaces and the related storage are not placed outside the *HW Task Wrapper*. It will be especially beneficial in case of Network-On-Chip (NoC) where latencies associated with transferring data between nodes may be high.

The *HW Task Wrapper* contains logic common for all the HW Tasks. Common local storage for all the channel interface modules can be a bottleneck. Also, number and type of used channels are specific to each HW task and thus may vary among different tasks. Since we want the communication to be customized on per HW task basis, the channel interface modules are not placed in the *HW Task Wrappers*.

Although, in Figure 4, slave-side interface modules share the access to the interconnect, multiple other HW tasks may prefetch the data to storage contained in these modules, one after another, while the HW Task Core is executing. This way the communication and execution of the whole application composed of SW and HW tasks may be overlapped. Besides, more interfaces could be provided depending on the performance requirements of a given system. Since the current state of channels constitutes the context of the executing HW Task, the placement of the interface modules within the RR also facilitates HW task's preemption. The developed architecture does not support HW task preemption when the actual transfer over the channel is in progress, that is, the preemption is possible only once the whole data transferred over the channel has been stored in the storage element of the interface module.

Another question may concern the decision about the location of the boundary of *FCLK* and *VCLK* domains. Its location within the *HW Task* rather than at the SR-RR boundary was dictated by performance reasons. For improved throughput of streaming data communication across two unrelated clock domains, asynchronous FIFOs provide significant advantage over the double-flopping synchronization method. While the latter one could be easily adopted to match the requirements of the SR-RR interface, it is not the case with the asynchronous FIFOs. For this reason, we decided to place the clock domain boundary within the *HW Task*.

A downside of the proposed approach may be increased size of HW tasks and, as a result, their longer reconfiguration time. However, our evaluation results in Section 9.4 show that, in many cases, the increase in logic area due to the additional logic is not high when compared to the size of the computing *HW Task Cores*.

## 4. Base OS Kernel

As a base OS kernel for the implementation of the OS4RS, we used the Toppers ASP RTOS kernel [24]. It mainly targets highly reliable small-scale real-time embedded systems, although memory protection extension is also available, making it applicable to larger scale systems. Toppers ASP kernel is of a small size which results in low memory usage. It follows a one object linking model, where both the kernel and the application are merged together and run in a privileged CPU mode.

ASP kernel provides basic services for the application composed of SW tasks, such as task state management, scheduling, and inter-task communication and synchronization. It implements a preemptive-priority scheduling and a Task Control Block (TCB) model, where special structures, that is, TCBs, are used by the kernel to store information related to task's execution state, its priority, and so forth. The kernel provides basic communication/synchronization primitives for SW tasks, that is, data queues, mailboxes, semaphores, and event flags, to name a few [9]. It also provides means of task-dependent synchronization, to allow an SW task to block or unblock another task by executing a system call.

The kernel is highly portable as the large part of it is CPU architecture independent. Only small part related to low-level system initialization, interrupt processing, and task dispatching depends on a given processor's architecture. Although a wide gamma of CPU architectures is currently supported by the ASP kernel, the Power PC (PPC) 405 processor being part of the FPGA used in our tests was not. For this reason, we had to port the architecture-dependent part of the kernel to the PPC 405 processor's architecture.

## 5. HW Task Configuration and Clock Scaling

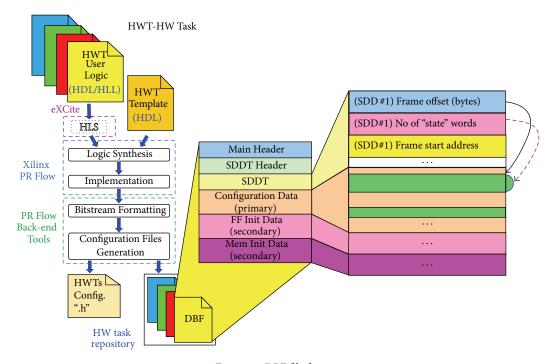

The HW Task Configuration Layer implements a model of a HW task state accessible by means of the Configuration Port Access (CPA) approach presented in [48, 55]. In this approach, the state is described by complete configuration frames rather than separate bits within the frame. While it may lead to redundancy, it is a much more portable approach, which leads to more efficient implementation of a preemption mechanism. In this approach a mapping between the state-containing frames, stored in the bitstreams, and those in FPGA's Configuration Memory (CM) is established and used afterwards by the save and restore functions. We developed a tool, called Bitformatter, whose role is to analyze the configuration bitstream representing a given HW task and to extract all the state-related information, creating a sort of extension containing the information about the aforementioned mapping of the state frames. The extended bitstream follows a developed DBF (Dynamically partially reconfigurable system's Bitstream Format).

The DBF file is divided into six sections, as shown in Figure 5. Main Header corresponds to the header of the original configuration file, State Data Descriptor Table (SDDT) Header contains information about the SDDT itself, whereas each State Data Descriptor (SDD) is composed of three-word elements. The first one is the offset of the first frame which contains the state information, calculated versus beginning of the configuration bitstream. Knowing the base address of the configuration bitstream, we can calculate the address of the state-related frame within the HW task bitstream repository. The second word in the SDD indicates the number of words in the state frames. Finally, the third word in the SDD is the start address of the first frame in the CM. Primary Configuration Bitstream section represents the original configuration bitstream that may be slightly modified for the purpose of preemption [48, 55]. FF Init Data bitstream is used to reinitialize and restore the state of all tasks, whereas Mem Init Data bitstream only is used to reinitialize the state of a memory-based HW tasks.

5.1. Configuration Controller and HTIC Bus. ICAP-DMA, presented in [48, 55], is a reconfiguration/readback controller which also controls the physical aspects of HW Tasks' reconfiguration and preemption. The controller's architecture allows for burst transfers of both configuration and readback data, which results in significantly improved reconfiguration

FIGURE 5: DBF file format.

and preemption times. Moreover, it allows for buffering of all requests related to reconfiguration and preemption, thereby reducing CPU utilization. Management of the physical aspects of the reconfiguration and preemption is done via the *HTIC* bus which connects the *ICAP-DMA* with the *DPR Controller* inside the *HW Task Wrapper*.

The *HTIC* bus has a simple, one master (*ICAP-DMA*), multiple slaves (*HW Task Wrappers*) topology and is a write only bus. Every *HTIC* bus slave interface has a unique RR ID assigned at a system design time and used later on when being addressed by the *ICAP-DMA*.

5.2. DPR Controller. In the developed method [48, 55], saving of the HW task's state is based on readback of the configuration bitstream from the FPGA's CM and its filtering, in order to retrieve the task's state. Restoring of the state is accomplished by configuring the CM with the bitstream containing previously saved state and assertion of the reset signal. The last one brings back all the storage elements constituting the HW task to their previously saved state. As the mechanism presented in [48, 55] was only suitable for synchronous logic, some additions were needed to make it work with the clock-scalable HW tasks.

The DPR Controller is composed of three modules: a Parent Control Module and two Child Modules. The Parent Module and one of the Child Modules work in the FCLK domain, whereas the other Child Module, in the VCLK domain. Communication between the parent and its children is based on sending request signals and receiving feedbacks. These handshaking signals have to be additionally synchronized for the case of Parent and the VCLK Child Module. After the control Finite State Machine (FSM) in the Parent Module sends the request, it waits for feedback, before moving

to the next state. In order to support dynamic frequency scaling, the clock in the *VCLK Child Module* has to be suspended whenever the DCM generating the clock is being reconfigured. For this reason, the *DPR Controller* is not used at that time.

In order to make sure that upon restoring of the task's state both *FCLK* and *VCLK* domains come out of reset simultaneously, the *Parent Module* has to adhere to the following order of steps. First, it requests both *Child Modules* to assert reset, then to switch on clocks, so that the both domains are reset, then switch off the clocks back, and finally deassert the reset. Since the *Parent Module* waits for the feedback when following the aforementioned procedure, we ensure that the reset is asserted for long enough to reset the domain with much slower clock than the static part. Apart of switching of resets and clocks, the *DPR Controller* is also responsible for enabling and disabling the SR-RR interface as well as enabling and disabling memory accesses within the HW task. The corresponding steps are not given for the sake of simplicity.

5.3. DFS Controller. Our implementation of the DFS Controller is based on the DCM module available on Virtex-4 FPGAs, which we used as the Frequency Synthesizer. The wrapping logic built around the DCM contains a control FSM which directly interfaces the Dynamic Reconfiguration Port (DRP) of the DCM [54]. Further details on DCMs and different ways of interfacing them can be found in [42, 43, 54].

The wrapping logic also implements a set of registers: *Clock Multiplier, Clock Divider, Control, Status,* and registers for enabling and acknowledging interrupts. First two registers control the frequency of the clock generated by the DCM module with respect to its input clock. *Control* and *Status* are

FIGURE 6: HWT State (HWT Scheduling and Placement Layer perspective).

FIGURE 7: RR State (HWT Scheduling and Placement Layer perspective).

used to request dynamic clock frequency scaling and to check its current progress status. Finally, interrupt-related registers control generation and acknowledgment of the interrupt indicating completion of the scaling operation.

Although logically, the DCM-based DFS Controller (DCM Controller) is a part of the HW Task Wrapper, physically it is connected to it externally but still being controlled by the HW Task Wrapper. This is done to simplify application of timing constraints on the VCLK generated by the DCM.

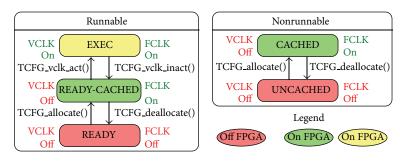

### 6. HW Task Scheduling and Placement

6.1. HW Task and Reconfigurable Region' State. While above the HW Task Scheduling and Placement Layer tasks are only seen as Runnable and Non-runnable, this layer makes an actual decision upon which HW task to allocate and start execution and is responsible for managing caching of HW tasks. HW task's states visible from the perspective of this layer are shown in Figure 6. READY and UNCACHED are used to describe deallocated HW tasks. HW tasks in READY-CACHED and CACHED states are allocated, but only their part located in the FCLK domain is operating, whereas the computational part, that is, the HW Task Core, is off. Finally, in EXEC state, both clock domains of the HW task are operating.

While maintaining the state of HW tasks, the *HW Task Scheduling and Placement Layer* is also responsible for managing the state of the RRs where the HW tasks are allocated. The RRs can be in one of three states: *DEALLOCATED*, *ALLOCATED*, and *ACTIVATED*. They are shown in Figure 7. The RR in the first state is ready for new allocations, in the second state is already allocated with some HW task which is currently not executing, and in the third state is allocated with some HW task which is currently executing.

The labels near transition edges in Figures 6 and 7 denote the calls made to the *HW Task Configuration Layer* in order to realize a given state. *TCFG\_allocate()* and *TCFG\_deallocate()* denote HW tasks' allocation and deallocation requests for a given RR, and they additionally cause the *FCLK* to be switched on and off, respectively. *TCFG\_vclk\_act()* and *TCFG\_vclk\_inact()* denote requests for switching the *VCLK* clock in the *HW Task Core* on and off, respectively.

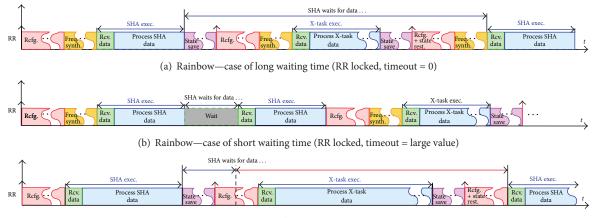

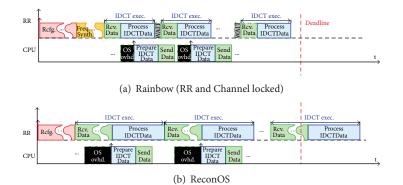

6.2. Preemptive Scheduling with Reservation of Reconfigurable Resources. The HW Task Scheduling and Placement Layer maintains Ready Queues and a Priority Map for each RR. The *Priority Map* is used in speeding up searching of the highest priority task located in these queues. The Ready Queues (Figure 8) link together all runnable tasks and one task which was granted lock on the RR resource. The latter one is kept in the first entry, in one of the queues even if it becomes *Non-runnable*. This way, tasks which block only for a short time can be kept allocated on the FPGA and restarted without reconfiguration overhead. Whenever a task acquires the lock, its priority is elevated to the priority of the resource, in case it was lower than it, or remains unchanged otherwise. If the RR's priority is set to the highest possible value, no task will be able to preempt that which holds the lock, resulting in a nonpreemptive scheduling. Setting priority of the RR to any lower value will allow some critical task to preempt the locked task. The lock will be restored when the critical task finishes execution.

A HW task may request the lock by means of *Rbow\_hwt\_req\_RR\_lock()* API call; however, granting of the lock will occur only when it is selected by the scheduler as shown in Figure 8. The lock may be requested with an additional time-out value or *EXIT REL FLAG* which makes the HW task releases the lock upon completion of its execution. The timely lock, which expires after a specified amount of time, may be used as a deadlock [56] recovery measure. It may be also used to prevent unnecessary preemptions in certain phases of execution of an application, still taking advantage of the preemption while waiting for some data from external source. Whenever a task which was granted the lock with time-out becomes *NON-RUNNABLE*, that is, idle, a *RR Lock Time-out Timer*, located in the *HW Task Wrapper*, will be started. When the counter's value

FIGURE 8: HWT Ready Queues and RR locking.

reaches zero, the executed interrupt handler will release the lock, possibly making the other *RUNNABLE* task allocated.

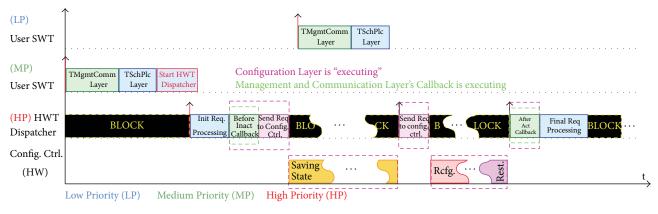

6.3. Delayed Execution of Configuration and Preemption Requests. The processing done by the HW Task Scheduling and Placement Layer can be divided into two steps. The first one is done at the caller's side; that is, it is implemented by a function of the HW Task Scheduling and Placement Layer called by the upper layer as a result of executing an API call. This processing consists of state management and scheduling. The second step is done by the HW Task Dispatcher task, which is started in the first step whenever the allocation, deallocation, or clock management is requested.

The main job of the *HW Task Dispatcher* is to process all these requests and call appropriate functions of the *HW Task Configuration Layer* to realize them. The *HW Task Dispatcher* is implemented as a highest priority task in the base OS in order to make the necessary allocations, deallocations, or clock management operations start with a minimum delay.

The interaction between the scheduler and the *HW Task Dispatcher* is based on the idea of pointers to the *HWTCB* of the scheduled task and currently allocated task as well as additional *Dispatch Flags*. The pointer corresponding to the scheduled task is maintained and assigned by the scheduler, whereas the pointer corresponding to the currently allocated task is assigned by the *HW Task Dispatcher*. When the *HW Task Dispatcher* starts, it compares the pointers and starts allocations and deallocations accordingly. When it completes, it assigns the scheduled task's pointer to the currently allocated task's pointer. The *Dispatcher Flags* are used to signal additional requests related to clock management, while the aforementioned pointers are equal.

Since the allocations, deallocations, and clock management operations may take some time to be completed, the state maintained by the *HW Task Scheduling and Placement Layer* can be pending for that period of time. The state and a *Pending Flag* are set in the first step, mentioned above, whereas the actual realization of that state and clearing of that flag are done within the *HW Task Dispatcher*.

The main advantage of the aforementioned division in processing is that API calls which do not result in requests for allocation, deallocation, or clock management are very short. Moreover, when the requests are actually being processed, the SW and HW tasks may continue their execution; that is, their processing is overlapped with the processing performed by the HW Task Configuration Layer; it is shown in Figure 9. In the figure, the Send Request to Configuration Controller corresponds to processing done by the HW Task Configuration Layer. It sends the reconfiguration and readback requests to the *Configuration Controller* and then blocks, waiting for the processing to be completed. This interaction is based on semaphore, acquired by the HW Task Configuration Layer and released by the dedicated Configuration Controller interrupt handler. In case of clock scaling requests, the HW Task Configuration Layer talks to DFS Controller module (DCM Controller), following similar procedure as in case of Configuration Controller (ICAP-DMA). The Before Inact Callback and the After Act Callback refer to function callbacks of the upper layer described previously in Section 3.3.3

The *Init Req Processing* corresponds to accessing of the structures related to the request, shared between the *HW Task Dispatcher* and the scheduler. At this time, also the decision about which functions of the *HW Task Configuration Layer* to call is made. This decision is based on checking the status of the *Dispatch Flags* and comparison of the pointers of the scheduled and currently allocated task, described before. In the *Final Req Processing*, the assignment of the pointer corresponding to the currently allocated task and clearing of the *Pending Flag* is conducted. The latter one is performed, provided that no further requests have been made, while the processing which has now completed was in progress.

The actions in the *Init Req Processing*, the *Final Req Processing*, and those in the *Callbacks* are performed in the state of disabled interrupts, enforcing exclusive access to the shared OS4RS structures.

FIGURE 9: Delayed execution of configuration requests.

## 7. HW Task Management

7.1. HW Task Management API. The Table 1 shows the Management API Calls for SW and HW tasks. We provided API Calls for SW tasks as C preprocessor macros which reference the functions of the HW Task Management and Communication Layer. We also provided implementation of these calls for HW tasks coded in C and synthesized using eXCite [57] HLS tool. These are converted into states of the control FSM accessing ports of the synthesized HW Task Core module, mentioned in Section 3.4. Outside the HW Task Core, the ports are connected to the interface of the Management API Call Channel, described later on in Section 7.2.

The calls with\* can be only executed by the SW task caller. The restriction for *Rbow\_swt\_exit()* is natural as it is a voluntary exit call to be made only by the SW tasks. The restriction for the other calls comes from the fact that the calls made by the HW task caller are actually executed on its behalf by a dedicated interrupt handler. Currently, the base OS implementing SW multitasking does not provide support for these calls made within the interrupt context. Extension of the base OS is a part of a future work.

While the majority of calls in the Table 1 are typical for conventional OSes [9, 24], the other ones have been specifically designed for the HW tasks. *Rbow\_hwt\_acq\_RR\_lock* and *Rbow\_hwt\_rel\_RR\_lock()* are used to reserve and release the reconfigurable resources for a given HW task (RR Locking), described in Section 6.2. The *Rbow\_hwt\_prefetch()* call is used in HW task prefetching, that is, putting it into a PREFETCH state, described in Section 7.3. The actual activation of the task put into the PREFETCH state is done when the *Rbow\_hwt\_prefetch\_act()* call is executed. Another special call, *Rbow\_hwt\_updt\_freq()*, is used to dynamically update the clock frequency of a HW task. If the new requested frequency is within the range of frequencies supported by the HW task and the Frequency Synthesizer module itself, the clock frequency scaling will be requested from the HW Task Configuration Layer. The new frequency is calculated using the clock frequency multiplier (MULT) and divider (DIV) parameters passed to the call as well as the input clock

TABLE 1: Management API.

| SW tasks                              | HW tasks                                                  |

|---------------------------------------|-----------------------------------------------------------|

| _                                     | Rbow_hwt_prefetch (HWT ID)                                |

| _                                     | Rbow_hwt_prefetch_act (HWT ID)                            |

| Rbow_swt_act (SWT ID)                 | Rbow_hwt_act (HWT ID)                                     |

| Rbow_swt_term (SWT ID)*               | Rbow_hwt_term (HWT ID)                                    |

| Rbow_swt_exit ()*                     | Rbow_hwt_exit (HWT ID)                                    |

| Rbow_swt_chg_pri (SWT ID, NEW PRI)*   | Rbow_hwt_chg_pri (HWT ID, NEW PRI)                        |

| Rbow_swt_susp (SWT ID)*               | Rbow_hwt_susp (HWT ID)                                    |

| Rbow_swt_resm (SWT ID)*               | Rbow_hwt_resm (HWT ID)                                    |

| Rbow_swt_rotate_queue (PRI)           | Rbow_hwt_rotate_queue (RR ID, PRI                         |

| _                                     | Rbow_hwt_acq_RR_lock (HWT ID,<br>EXIT REL FLG, TMOUT VAL) |

| _                                     | Rbow_hwt_rel_RR_lock (HWT ID)                             |

| _                                     | Rbow_hwt_updt_freq (HWT ID,<br>MULT, DIV)                 |

| _                                     | Rbow_hwt_wait_state (HWT ID)                              |

| Rbow_ch_lock_acq (CH ID)              | Rbow_ch_lock_acq (CH ID)                                  |

| Rbow_ch_lock_rel (CH ID)              | Rbow_ch_lock_rel (CH ID)                                  |

| * Only converse to the the CM/T colle |                                                           |

\*Only supported by the SWT caller.

frequency of the *Frequency Synthesizer* module, given as a system-wide constant.

Some of calls may result in long HW task's allocation or clock scaling process. As mentioned in Section 6, these are done in background, while other tasks continue their execution. As a result, by the time the API call returns to the caller, and the allocation or clock scaling will be still in progress. This is done to allow the caller for further execution without waiting for the time-consuming process to complete. In some situations, it may be required to synchronize the further task's execution with the completion of the time-consuming reconfiguration. This is where the *Rbow\_hwt\_wait\_state()* call comes into play. This call will only make the caller wait if the previous call resulted in any of the aforementioned time-consuming processes and otherwise

FIGURE 10: Management API Call Channel.

will return immediately. It is currently supported only by the SW task caller. It should be noted that communication calls, presented later in this paper, do not require this additional synchronization call as they always block if the conditions for the communication are not met.

Finally, the *Rbow\_ch\_lock\_acq()* and *Rbow\_ch\_lock\_rel()* calls are used in tandem with the RR Locking and only when the HW task is involved in communication. Although they are related to communication, they logically belong to the group of *Management API Calls*. The first call acquires a lock on a channel, whereas the second one releases it. The channel lock is an idea, described in details in Section 8.4.1, which optimizes the communication by reducing OS4RS processing overhead.

#### 7.2. Processing of HW Task Management API Call

7.2.1. Management API Call Channel. A Management API Call Channel, shown in Figure 10, is a special kind of channel used by the HW Task Core to pass the information about the Management API Call it makes, that is, API call ID and its parameters, to the Management API Call Module, located in the HW Task Wrapper, and then get the return value of the call when it completes. The API call ID and the parameters are first buffered in the FIFO structure of the channel and then read by the Management API Call Module. The buffer is used to decrease the latency of sending the API call-related information across the asynchronous clock domains. The return value is passed to the HW Task Core using a standard double flopping synchronization scheme.

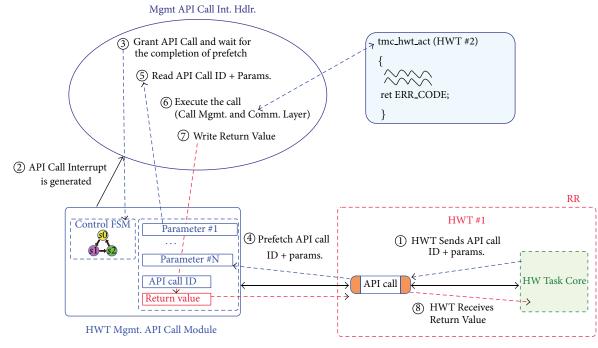

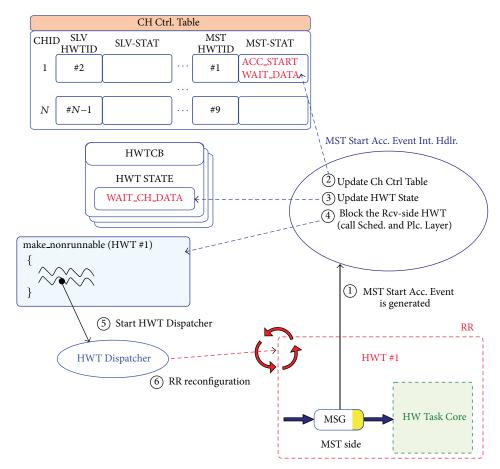

7.2.2. Processing of Management API Call. While SW task callers make the OS4RS service calls by directly calling the API functions of the Rainbow extension, this process is different for HW tasks. It is shown in Figure 11.

Firstly, the *HW Task Core*, being part of the HW task, sends the ID of the call and its parameters to the *API Call* channel. The control FSM of the *Management API Call*

Module constantly checks for presence of data in the channel. When the HW Task Core sends the data, the control FSM detects it and notifies the software side of the OS4RS about it by generating an interrupt. As a result, a dedicated interrupt handler, called Management API Call Interrupt Handler, is executed which grants the request in the Management API Call Module. This starts prefetching of the data from the channel to the internal storage of the Management API Call Module. The software side of the OS4RS waits till the prefetching is over and then reads the ID and parameters of the call from the Management API Call Module. The API call made by the HW task is then executed on its behalf and return value sent back to the API Call channel. This completes the calling process for the HW task caller. However, if the call made by the HW task results in its preemption or blocking, then the return value is saved, at this time, in the HWTCB and passed to the HW Task Core later on, upon its allocation.

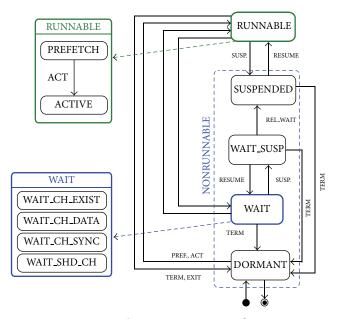

7.3. A HW Task State. Figure 12 shows the HW task state diagram from the perspective of the HW Task Management and Communication Layer. ACT, TERM, EXIT, SUSP, RESUME, WAIT, and REL\_WAIT labels near the transition edges indicate a corresponding action requested from the HW Task Management and Communication Layer, which results in the state transition. ACT corresponds to task activation, TERM corresponds to its forced termination, and EXIT corresponds to voluntary exit, whereas the SUSP, RESUME correspond to blocking and resumption as a result of execution of the task-dependent synchronization calls. Finally, WAIT and REL\_WAIT denote actions requested as a result of communication of the HW task over channels.

The *PREFETCH* state being part of the *RUNNABLE* macrostate is a special state. In this state, the SR-RR interface, mentioned in Section 3.4, is enabled, but only the part of the HW task operating in the *FCLK* clock domain is switched on. On the other hand, the computational part, that is, the *HW Task Core*, is off. For this reason, the channel interface modules and their storage elements are accessible from

FIGURE 11: Processing of Task Management API Call by an HWT caller.

FIGURE 12: HWT State (HWT Management and Communication Layer perspective).

outside of the HW task. These conditions allow other tasks to prefetch data to the channel interface modules before the *HW Task core* starts executing and so cannot possibly block on any API calls and be deallocated.

The WAIT macrostate is composed of WAIT\_CH\_EXIST, WAIT\_CH\_DATA, WAIT\_CH\_SYNC, and WAIT\_SHD\_CH states. These states indicate waiting condition on the communication channel. The first one indicates that the HW

task is waiting for the other side of the channel, that is, its interface module, to become allocated. The second one means that the HW task either waits for the storage element being part of the channel interface on the other side of the channel to be empty, so that the data can be written to it, or waits for the storage element on its side of the channel to filled, so that the data can be read from it. The third one is used when the HW task communicates over the Message (MSG) channel, where a sending HW task is blocked and put to WAIT\_CH\_SYNC till the other side executes the complementary API call and receives the data. Finally, the WAIT\_SHD\_CH state is used whenever the P2P communication over the channel is not possible and an intermediate shared memory, called Shadow Channel, has to be used. As the communication over the Shadow Channel takes more time than the P2P communication, it may happen that the HW task will try accessing the channel again, before the previous communication completes. If that happens, the HW task will be put into WAIT\_SHD\_CH state. Details on the intertask communication and synchronization are given in Section 8.

## 8. Intertask Communication and Synchronization

8.1. Overview. The inter-task communication and synchronization implemented by the presented OS4RS is based on the concept of channel. In our opinion, it is more suitable for SW-HW multitasking systems than previous approaches which directly follow the model of communication and synchronization based on data queues and semaphores, known from traditional SW multitasking OSes.

FIGURE 13: Channel with reconfigurable interfaces.

The channel provides interface for tasks to communicate with other tasks, located either in software or hardware. The data sent to the channel is transfered over the physical interconnect provided by the hardware platform before it can be received by another task. Multiple channels can share the same interconnect.

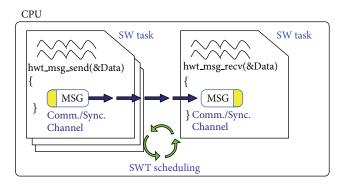

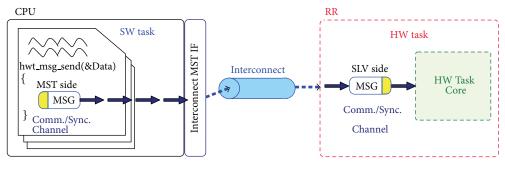

We have implemented four types of channels which can be used by SW and HW tasks. These are FIFO, MSG, Shared Memory (SHARED MEM), and Register (REG) channels. The FIFO channel implements FIFO like, unidirectional, P2P communication. In this style of communication, the receiver blocks only if the sender has not sent the data yet (FIFO empty condition), while the sender is able to send as much data as is the depth of the channel, before it blocks (FIFO full condition). The MSG channel implements a unidirectional, P2P, rendezvous style of communication where the receiver and the sender block till their communicating partner makes a corresponding Communication API Call and sends or receives the data. The SHARED MEM channel implements a nonblocking, bidirectional communication based on the storage located externally to tasks. Finally, the REG channel implements a nonblocking communication and is used for polling-based synchronization of SW and HW tasks communicating over the SHARED MEM channel.

8.2. HW Task Wrapper: Implementation Details. As mentioned previously in Section 3.4, HW Tasks access communication services of the OS4RS via a dedicated interface, that is, the HWT OSIF, which consists of the HW Task Communication Module, the HW Task Communication Event Control, and the Translation Table modules located in the HW Task Wrapper.

The proposed communication model has been implemented on top of IBM CoreConnect buses. The Processor Local Bus (PLB) is used for data transfers, whereas the Device Control Register (DCR) bus is used to control the HW task's OS interface. Nevertheless, it is also suitable for other types of interconnects. The benefits of the model will be especially visible in case of NoC, which promotes P2P communication and where communication latencies between nodes may be high.

Channel interfaces use ID addressing globally and index addressing locally, within the HW task. The maximum number of channel indices allowed in the HW task was set to 16 which made it possible to reduce the size of the *Translation Table* to 16 entries. The table was implemented with LUT-RAMs allowing for index to address translation within one clock cycle after the translation request is sent by the *HW Task Communication Module*.

#### 8.3. Hardware Side View

8.3.1. Channel with Reconfigurable Interfaces. The channel interface used by a HW task is a hardware module which lets the task access the channel with an easy protocol while taking care of the intricacies of conducting the actual communication over the channel. The channel interface has its local storage used to buffer the data received over the channel, before it can be accessed by the task or data that is written by the task, before sending it over the channel.

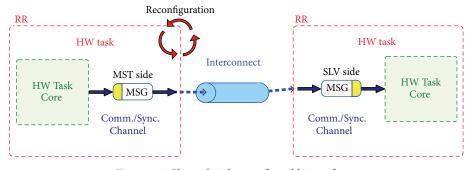

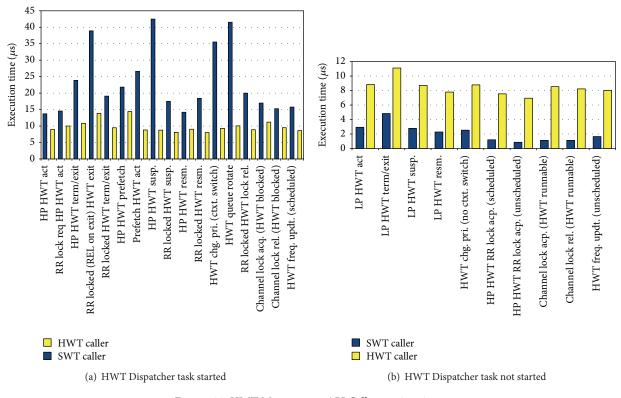

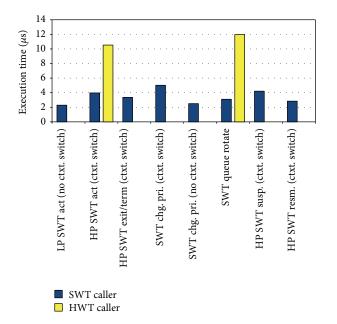

One of the ideas used in the developed inter-task communication and synchronization mechanism is the one of a *reconfigurable channel interface*, shown in Figure 13. The *reconfigurable channel interface* is an interface allocated and deallocated together with the HW task which uses it.

As interfacing modules, containing local storage, are part of the HW tasks, the P2P communication between two already configured HW tasks is possible. Moreover, thanks to this specific location of the channel interfaces, their number, type, and size of their local storage can be defined based on communication needs of the task. As in the developed OS4RS, the *HW Task Core* and the remaining part of the HW Task use separate clocks, prefetching of data to the channel interfaces is still possible, while the computational part is halted.

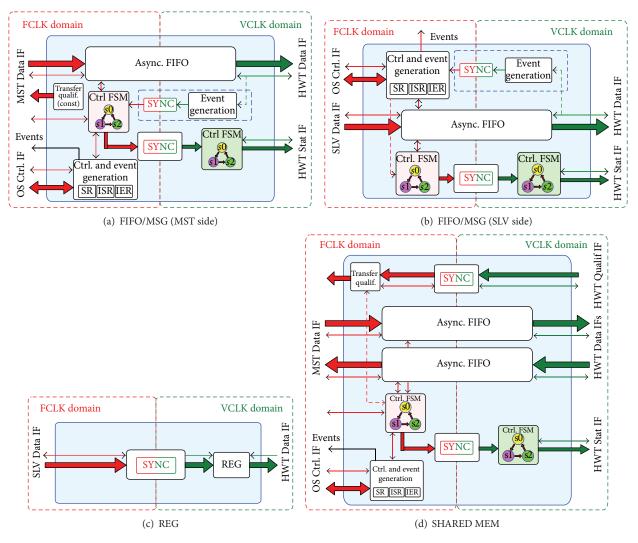

8.3.2. Hardware-Side Channel Interface Modules. The channel interfaces for HW tasks are implemented by the hardware modules presented in Figure 14, referred to as *channel interface modules* or simply *channel interfaces*. The *channel interface modules* have two sides: the interconnect side and the HW task Core side. For the presented modules, the interconnect side is shown on the left side of the module, whereas the HW task Core side is shown on the right side of it.

Depending on the type of the interconnect interface, there are two major types of interfacing modules for *FIFO* and *MSG* channels. These are master-side and slave-side modules.

FIGURE 14: Hardware-side Channel Interface Modules.

SHARED MEM channel interface modules and REG channel interface modules are only available as master- and slaveside modules, respectively. The modules for FIFO, MSG and REG channels can be additionally divided based on a direction of the channel, that is, whether they are connected to the sender or receiver. We will refer to them as read-side (receive-side) modules and write-side (send-side) modules. This terminology will be used in the rest of the text. The exception is the interface modules for the SHARED MEM channel which is bidirectional.

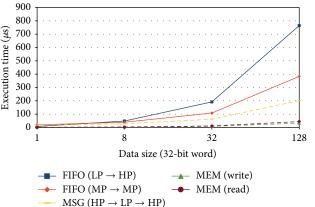

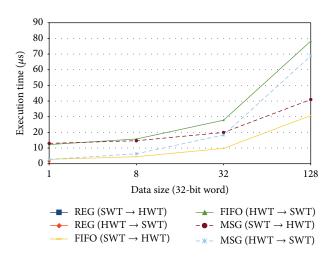

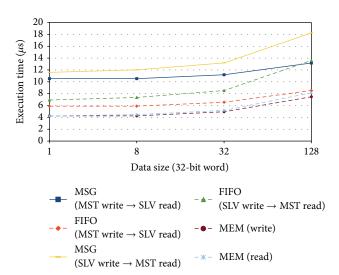

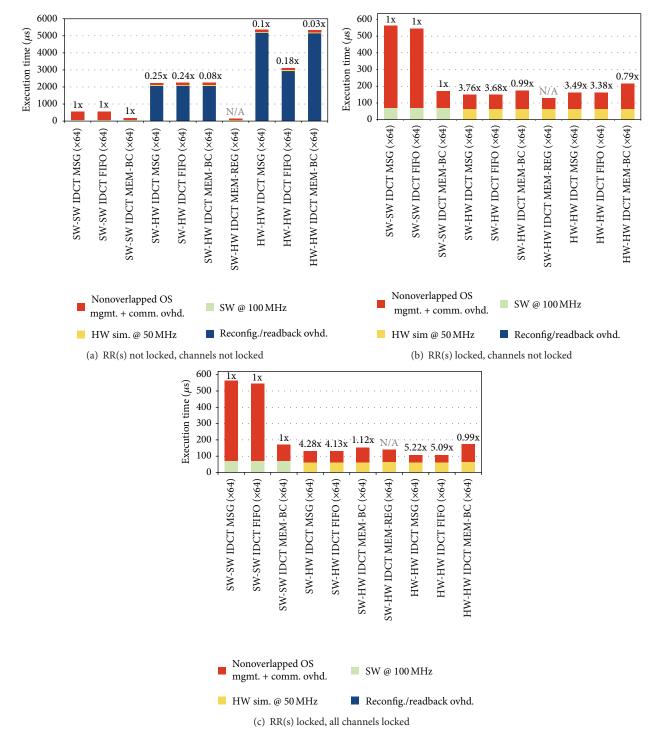

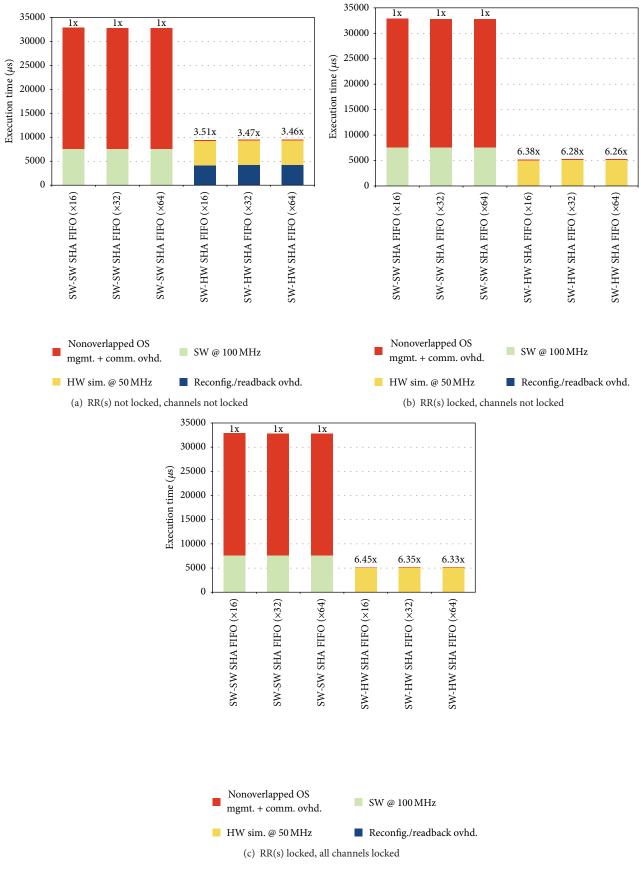

Channel interface modules operate partly in the *FCLK* domain and partly in the *VCLK* domain. The interface between the asynchronous domains is implemented by means of the asynchronous FIFO and double-flopping synchronization primitives. As such, channel interface modules encapsulate communication across the clock domains.