Mälardalen University Press Licentiate Thesis No.224

# Raising Abstraction of Timing Analysis through Model-Driven Engineering

Alessio Bucaioni

December 2015

School of Innovation, Design and Engineering Mälardalen University Västerås, Sweden

Copyright © Alessio Bucaioni, 2015 ISSN ISBN — Printed by Mälardalen University, Västerås, Sweden

## Abstract

The complexity of software running on vehicular embedded systems is constantly increasing and this negatively affects its development costs and time to market. One way to deal with these issues is to boost abstraction in the form of models to (i) ease the reasoning about the system architecture, (ii) automate certain stages of the development, (iii) early detect flaws in the system architecture through fundamental analysis and (iv) take appropriate countermeasures before the system is implemented.

Considering the importance of timing requirements in the design of software for vehicular embedded systems, in this licentiate thesis we leverage Model-Driven Engineering for realizing a semi-automatic approach which allows the developer to perform end-to-end delay timing analysis on design models, without having to manually model timing elements and set their values.

The proposed approach, starting from a design model of an automotive software functionality, automatically generates a set of models enriched with timing elements whose values are set at generation time. End-to-end delay timing analysis is run on the generated models and, based on the analysis results, the approach automatically selects the generated models which better meet a specific set of timing requirements.

## Sammanfattning

Nuförtiden finns inbyggda datorsystem i de flesta elektroniska och elektriska produkter. Allt ifrån strömbrytare och mikrovågsugnar till bilar och tåg är beroende av moderna inbyggda datorsystem. I fordonsindustrin, ökar ständigt antalet inbyggda system som ersätter hydrauliska och mekaniska delar som inte kan leverera moderna tjänster som kollisionsskydd och antisladdsystem. Samtidigt ökar komplexiteten av dessa datorsystem och deras mjukvara, och detta påverkar negativt utvecklingskostnader och tid. Ett sätt att minska dessa problem är att använda abstraktioner i form av modeller för att i) enklare resonera över systemets arkitektur, ii) automatisera vissa utvecklingsfaser, iii) tidigt spåra brister i systemets arkitektur genom grundläggande analyser och iv) åtgärda brister innan systemet färdigställs.

I denna avhandling använder vi modelldriven utveckling för att skapa en ny metod som förenklar utvecklingen av inbyggda system för fordon. Detta sker genom att utvecklaren beskriver systemet som en abstrakt arkitekturmodell som används av metoden för att automatiskt generera ett antal möjliga konkreta modeller. End-to-end tidsanalys körs på de genererade modellerna och analysresultat används av metoden för att automatiskt välja bland de genererade modellerna dem som uppfyller de uppsatta tidskraven bäst.

## Acknowledgements

First and foremost, my utmost gratitude to my supervisors Mikael Sjödin, Antonio Cicchetti and Federico Ciccozzi whose guidance is making this a possible and pleasant journey. They are mentors, colleagues and friends and they are helping me in becoming a better person before than a better researcher.

I would like to express my deepest gratitude to my "buddy" Saad Mubeen, who helped me in moving the first steps into the research world. We shared unforgettable moments and i could not ask for a better "buddy".

I would like to thank Kurt-Lennart Lundbäck and all the people from Arcticus Systems AB for giving me the possibility to work in such a successful company without never interfere with my researches.

I would like to thank all the administrative staff, especially Carola Ryttersson and Susanne Fronnå for making "paper-work" easier.

I would like to thank my friends and colleagues at the department for all the good and funny moments and for the inspiration they give me each day.

I will never thank enough my family for supporting me, even financially, and for never discussing my decisions, even when these brought me far away from their life. Without you, i would be lost.

I would like to thank all my friends, both in Italy and Sweden, for standing by my side and for never making me feel alone. Especially, i would like to thank Manuel, Mirco and Giada for having brought some joy in a difficult period of my life.

I would like to thank my grandpas Vincenzo and Terzilio, my aunts Ines and Nunziata and my uncle Pasquale for watching over me.

Last, but not least i would like to thank the One above us all, God, for answering my prayers and for giving me the strength to never throw in the towel.

> Alessio Bucaioni Västerås, December, 2015

## **List of Publications**

## Publications Included in this Licentiate Thesis<sup>1</sup>

**Paper A – A Metamodel for the Rubus Component Model: Extensions for Timing and Model Transformation from EAST-ADL**, *Alessio Bucaioni, Saad Mubeen, Federico Ciccozzi, Antonio Cicchetti, Mikael Sjödin*, Conditionally accepted at the Journal of Systems and Software (JSS).

Paper B – Exploring Timing Model Extractions at EAST-ADL Design -level Using Model Transformations, *Alessio Bucaioni, Saad Mubeen, Antonio Cicchetti, Mikael Sjödin*, IEEE 12th International Conference on Information Technology: New Generations (ITNG), Las Vegas, Nevada (USA), April, 2015.

**Paper C – Raising Abstraction in Timing Analysis for Vehicular Embedded Systems through Model-Driven Engineering**, *Alessio Bucaioni*, Doctoral Symposium at Software Technologies: Applications and Foundations (STAF), L'Aquila, Italy, July, 2015. *Best paper award*.

Paper D – Anticipating Implementation-Level Timing Analysis for Driving Design-Level Decisions in EAST-ADL, Alessio Bucaioni, Antonio Cicchetti, Federico Ciccozzi, Romina Eramo, Saad Mubeen, Mikael Sjödin, 1st International Workshop on Modelling in Automotive Software Engineering (MASE) at ACM/IEEE 18th International Conference on Model Driven Engineering Languages and Systems (Models), Ottawa, Canada, September, 2015.

<sup>&</sup>lt;sup>1</sup>The included publications are reformatted to comply with the licentiate thesis printing format

### **Related Publications not Included in this Thesis**

**Comparative Evaluation of Timing Model Extraction Methodologies at EAST-ADL Design Level**, *Alessio Bucaioni, Saad Mubeen, Federico Ciccozzi, Antonio Cicchetti, Federico Ciccozzi, Mikael Sjödin,* IEEE 12th International Conference on Embedded Software and Systems (ICESS), New York, New York, August, 2015.

**Towards a metamodel for the Rubus Component Model**, *Alessio Bucaioni, Antonio Cicchetti, Mikael Sjödin*, 1st International Workshop on Model-Driven Engineering for Component-Based Software Systems at ACM/IEEE 17th International Conference on Model Driven Engineering Languages and Systems (Models), Valencia, Spain, September, 2014.

**OSLC Tool Integration and Systems Engineering - The Relationship Between The Two Worlds**, *Mehrdad Saadatmand*, *Alessio Bucaioni*, 40th Euromicro Conference on Software Engineering and Advanced Applications, Verona, August, 2014.

**Demonstrator for modeling and development of component-based distributed real-time systems with Rubus-ICE**, *Alessio Bucaioni, Saad Mubeen, John Lundbäck, Kurt-Lennart Lundbäck, Jukka Mäki-Turja, Mikael Sjödin*, Open Demo Session of Real-Time Systems (RTSS @ Work) at Real Time Systems Symposium (RTSS), Vancouver, Canada, December, 2013.

### **Other Publications**

**Understanding bidirectional transformations with TGGs and JTL**, *Alessio Bucaioni, Romina Eramo*, 2nd International Workshop on Bidirectional Transformations (BX) at European Joint Conferences on Theory and Practice of Software (ETAPS), Roma, Italy, March, 2013.

A Model-Based Testing Framework for Automotive Embedded Systems, Raluca Marinescu, Mehrdad Saadatmand, Alessio Bucaioni, Cristina Seceleanu, Paul Pettersson, 40th Euromicro Conference on Software Engineering and Advanced Applications, Verona, August, 2014.

#### viii

EAST-ADL Tailored Testing: From System Models to Executable Test Cases, Raluca Marinescu, Mehrdad Saadatmand, Cristina Seceleanu, Paul Pettersson, Alessio Bucaioni, MRTC Report MDH-MRTC-278/2013-1-SE, September, 2013.

ix

To my princesses Chiara and Elisa

xi

# Contents

| Ι  | r     | Thesis                                                           | 1  |

|----|-------|------------------------------------------------------------------|----|

| 1  | Intr  | oduction                                                         | 3  |

|    | 1.1   | Thesis Contribution                                              | 5  |

|    | 1.2   | Terminology                                                      | 6  |

|    | 1.3   | Thesis Outline                                                   | 7  |

| 2  | Res   | earch Plan                                                       | 9  |

|    | 2.1   | Research Goal                                                    | 9  |

|    | 2.2   | Research Challenges                                              | 10 |

|    | 2.3   | Research Contributions                                           | 11 |

|    | 2.4   | Papers Contribution                                              | 16 |

|    |       | 2.4.1 Paper A                                                    | 16 |

|    |       | 2.4.2 Paper B                                                    | 17 |

|    |       | 2.4.3 Paper C                                                    | 17 |

|    |       | 2.4.4 Paper D                                                    | 18 |

|    | 2.5   | Research Methodology                                             | 19 |

| 3  | Con   | clusions and Future Works                                        | 21 |

| Bi | bliog | raphy                                                            | 23 |

| II | ]     | Included Papers                                                  | 25 |

| 4  | ΑÑ    | er A:<br>Ietamodel for the Rubus Component Model: Extensions for | 25 |

|    |       | ing and Model Transformation from EAST-ADL                       | 27 |

|    | 4.1   | Introduction                                                     | 29 |

### xiv Contents

|   | 4.2  | Backg   | round and related work                              | 31 |

|---|------|---------|-----------------------------------------------------|----|

|   |      | 4.2.1   | MDE and CBSE in the Automotive Domain               | 31 |

|   |      | 4.2.2   | End-to-end timing models and analyses               | 34 |

|   |      | 4.2.3   | Paper contributions                                 | 36 |

|   | 4.3  | Provid  | ling a metamodel for RCM                            | 37 |

|   | 4.4  | DL2R    | CM model transformation                             | 41 |

|   | 4.5  | Applic  | cation to the steer-by-wire system                  | 48 |

|   | 4.6  | Evalua  | ation and discussion                                | 52 |

|   | 4.7  | Conclu  | usions and future work                              | 56 |

|   | Bibl | iograph | у                                                   | 57 |

|   |      |         |                                                     |    |

| 5 |      | er B:   |                                                     |    |

|   | _    | -       | Timing Model Extractions at EAST-ADL Design-level   |    |

|   |      | 0       | el Transformations                                  | 61 |

|   | 5.1  |         |                                                     | 63 |

|   |      | 5.1.1   | Paper Contribution                                  | 63 |

|   |      | 5.1.2   | Relation with Authors' Previous Works               | 64 |

|   | 5.2  | U       | round and Related Works                             | 65 |

|   |      | 5.2.1   | EAST-ADL Development Methodology                    | 65 |

|   |      | 5.2.2   | The Rubus Component Model (RCM)                     | 66 |

|   |      | 5.2.3   | End-to-end Timing Models and Analyses               | 67 |

|   |      | 5.2.4   | Model Driven Engineering (MDE) and Janus Transfor-  |    |

|   |      |         | mation Language (JTL)                               | 68 |

|   |      | 5.2.5   | MDE for DSE                                         | 69 |

|   | 5.3  |         | em Statement                                        | 69 |

|   | 5.4  | -       | sed Solution and Methodology                        | 71 |

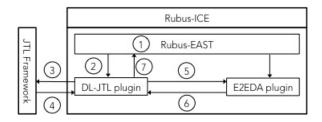

|   |      | 5.4.1   | Transformation phase                                | 73 |

|   |      | 5.4.2   | Timing analysis phase                               | 73 |

|   |      | 5.4.3   | Proof of concept                                    | 75 |

|   | 5.5  | Conclu  | usion                                               | 75 |

|   | Bibl | iograph | у                                                   | 77 |

| 6 | Dan  | er C:   |                                                     |    |

| U | -    |         | straction in Timing Analysis for Vehicular Embedded | 4  |

|   |      |         | rough Model-Driven Engineering                      | 79 |

|   | 6.1  |         |                                                     | 81 |

|   | 0.1  | 6.1.1   | Context                                             | 81 |

|   |      | 6.1.2   | Paper Outline                                       | 84 |

|   | 6.2  |         | m Formulation                                       | 84 |

|   | 0.2  | rioule  |                                                     | 04 |

| Contents | XV |

|----------|----|

|          |    |

|   | 6.2.1 Research Goal                                                                                                                                                                                                                                                                                                                                                                    | 84                                                                                                         |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   | 6.2.2 Research Challenges                                                                                                                                                                                                                                                                                                                                                              | 85                                                                                                         |

|   | 6.3 Proposed Solution and Intended Contributions                                                                                                                                                                                                                                                                                                                                       | 86                                                                                                         |

|   | 6.4 Preliminary Work and Current Status                                                                                                                                                                                                                                                                                                                                                | 88                                                                                                         |

|   |                                                                                                                                                                                                                                                                                                                                                                                        | 89                                                                                                         |

|   |                                                                                                                                                                                                                                                                                                                                                                                        | <u>89</u>                                                                                                  |

|   |                                                                                                                                                                                                                                                                                                                                                                                        | <u>89</u>                                                                                                  |

|   | 6.6.2 Model-Driven Engineering for Vehicular Embedded                                                                                                                                                                                                                                                                                                                                  |                                                                                                            |

|   |                                                                                                                                                                                                                                                                                                                                                                                        | 91                                                                                                         |

|   | Bibliography                                                                                                                                                                                                                                                                                                                                                                           | 93                                                                                                         |

| 7 | Paper D:                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                            |

|   | Anticipating Implementation-Level Timing Analysis for Driving De-<br>sign -Level Decisions in FAST-ADL                                                                                                                                                                                                                                                                                 | )7                                                                                                         |

|   | sign -Level Decisions in EAST-ADL                                                                                                                                                                                                                                                                                                                                                      | <b>97</b>                                                                                                  |

|   | sign -Level Decisions in EAST-ADL       9         7.1 Introduction       9                                                                                                                                                                                                                                                                                                             | 99                                                                                                         |

|   | sign -Level Decisions in EAST-ADL       9         7.1 Introduction       9         7.2 Related Work       10                                                                                                                                                                                                                                                                           | 99<br>00                                                                                                   |

|   | sign -Level Decisions in EAST-ADL       9         7.1 Introduction       9         7.2 Related Work       10                                                                                                                                                                                                                                                                           | 99<br>00<br>01                                                                                             |

|   | sign -Level Decisions in EAST-ADL       9         7.1 Introduction       9         7.2 Related Work       10         7.3 A Running Example: the Steer-by-wire System       10                                                                                                                                                                                                          | 99<br>00<br>01<br>02                                                                                       |

|   | sign -Level Decisions in EAST-ADL97.1Introduction97.2Related Work107.3A Running Example: the Steer-by-wire System107.4Applying the methodology10                                                                                                                                                                                                                                       | <ul> <li>99</li> <li>00</li> <li>01</li> <li>02</li> <li>03</li> </ul>                                     |

|   | sign -Level Decisions in EAST-ADL       9         7.1 Introduction       9         7.2 Related Work       10         7.3 A Running Example: the Steer-by-wire System       10         7.4 Applying the methodology       10         7.4.1 Transformation Phase       10         7.4.2 End-to-end Delay Analysis Phase       10         7.4.3 Filtering and Propagation Phases       10 | <ul> <li>99</li> <li>00</li> <li>01</li> <li>02</li> <li>03</li> </ul>                                     |

|   | sign -Level Decisions in EAST-ADL       9         7.1 Introduction       9         7.2 Related Work       10         7.3 A Running Example: the Steer-by-wire System       10         7.4 Applying the methodology       10         7.4.1 Transformation Phase       10         7.4.2 End-to-end Delay Analysis Phase       10                                                         | <ul> <li>99</li> <li>00</li> <li>01</li> <li>02</li> <li>03</li> <li>07</li> <li>08</li> </ul>             |

|   | sign -Level Decisions in EAST-ADL       9         7.1 Introduction       9         7.2 Related Work       10         7.3 A Running Example: the Steer-by-wire System       10         7.4 Applying the methodology       10         7.4.1 Transformation Phase       10         7.4.2 End-to-end Delay Analysis Phase       10         7.4.3 Filtering and Propagation Phases       10 | <ul> <li>99</li> <li>00</li> <li>01</li> <li>02</li> <li>03</li> <li>07</li> <li>08</li> <li>09</li> </ul> |

Ι

# Thesis

1

## Chapter 1

## Introduction

Nowadays, embedded systems play a prevailing role in everyday life as they are widely employed in most electronic and electrical products, from microwave ovens to trains and cars. In the specific case of the automotive domain, embedded systems replace many of the hydraulic and mechanical parts of a vehicle, improving the driving experience, the comfort of the passengers and the safety of the vehicle. The growing complexity of software running on embedded systems results in an increasing complexity of its development, which in turn negatively affects the development costs and time to market [1].

The software engineering community has agreed on three instruments when dealing with the increasing complexity of software and its development: i) *abstraction*, ii) *separation of concerns* and iii) *automation*. In the midst of the many methodologies advocating these three instruments when developing software systems, Model-Driven Engineering (MDE) has progressively gained recognition and industrial attention in the last 15 years [2].

MDE is a paradigm which aims at raising the level of abstraction of software development by shifting the focus from coding to modeling activities. In this context, *models* and *model manipulations* are promoted as first-class citizens. A model represents an abstraction of the software system, from a particular point of view [3]. Models promote separation of concerns by describing the software system by means of different models each of which highlighting different concerns corresponding to different views. The set of rules and constraints for the construction of valid models are specified in the so-called *metamodel* [3]. The relation between a model and its metamodel is called conformance [3]. According to the MDE paradigm, a software system is developed

#### 4 Chapter 1. Introduction

by means of model manipulations, where abstract models are refined into more detailed ones, until code is automatically generated. Model manipulations are performed by means of *model transformations* [4] which automatically translate a source model into a target model while ensuring their conformance to their respective metamodels.

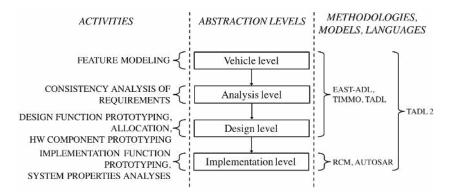

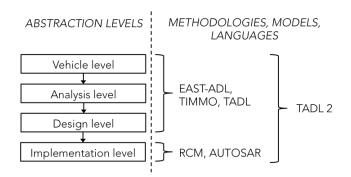

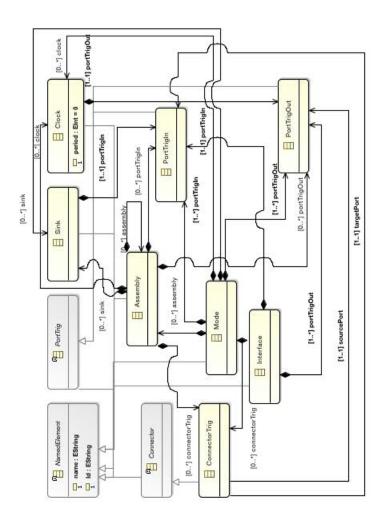

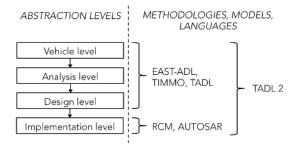

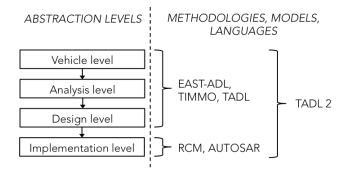

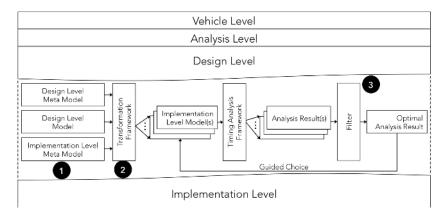

In the automotive domain, the adoption of MDE resulted in the standardization of an architectural description language, EAST-ADL [5], which is used for modeling product-lines of vehicular embedded systems. EAST-ADL proposes a view over the software development process composed by four different *abstraction levels*, which implicitly ensure separation of concerns through the different engineering phases. Each abstraction level is described by means of metamodeling constructs and aims at hiding unnecessary information from higher abstraction levels. EAST-ADL defines a set of activities to perform for each abstraction level, based on the expressible concepts. Figure 1.1 shows the EAST-ADL abstraction levels together with the related languages and activities.

Figure 1.1: EAST-ADL Abstraction Levels Together With The Related Languages and Activities

The highest abstraction level is represented by the *vehicle level*, which captures information regarding the system's functionality. At the *analysis level*, by using formal notations, vehicle functions are expressed in terms of behaviors and interfaces. Yet, design and implementation details are omitted. At this stage, high level analysis for consistency checking of the requirements can be performed. At the *design level*, analysis-level artifacts are refined with designoriented details, such as software, middleware and hardware separation as well

#### 1.1 Thesis Contribution 5

as allocation of software. At the *implementation level*, artifacts introduced at the design level are refined with implementation details for enabling system properties analyses, e.g., end-to-end delay timing analysis. At this stage, component models<sup>1</sup> (e.g., Rubus Component Model (RCM) or AUTOSAR) are used to model the system in terms of components and their interactions. The output of this level is a complete software architecture which can be used for code generation.

In this thesis, we consider RCM as the language for the implementation level [7]. RCM is a component model for the development of resource-constrained embedded real-time software systems. It is developed by Arcticus Systems AB in collaboration with Mälardalen University and it is currently adopted by several international companies, e.g., as alternative to AUTOSAR. Considering the importance of timing analysis for vehicular embedded systems [8] [9], RCM implements state-of-the-art end-to-end delay timing analysis [10] [11]. End-to-end delay timing analysis is used for providing evidence that behaviors of the software system meet a specific set of timing requirements. Within EAST-ADL, end-to-end delay timing analysis gives meaningful results only if run on implementation models which are currently manually defined starting from design models. Unfortunately, when dealing with systems of industrial size, this manual process becomes soon overwhelming, leading to the creation of a very limited subset of implementation models only. By having automation support among the different EAST-ADL abstraction levels, and in our specific case between EAST-ADL design and implementation levels, it would be possible to enable swift transitions avoiding error-prone and tedious manual activities (model manipulations). Also, it would be possible to leverage end-to-end delay timing analysis results for driving design decisions avoiding late discoveries of unacceptable quality of service with respect to timing requirements [8].

### **1.1 Thesis Contribution**

In this licentiate thesis, we leverage MDE for realizing a semi-automatic approach which allows the developer to perform timing analysis on EAST-ADL design models without having to manually specify their timing elements. More precisely, starting from an EAST-ADL design model of an automotive software

<sup>&</sup>lt;sup>1</sup>A *software component* is a software element which i) conforms to a component model, ii) can be deployed independently and iii) can be composed according to a composition standard [6]. A *component model* specifies i) the properties of software components and ii) how software components can be composed [6].

### 6 Chapter 1. Introduction

functionality, the proposed approach automatically generates a set of RCM models enriched with timing elements. End-to-end delay timing analysis is run on the generated RCM implementation models and, based on the results, the approach supports the selection of the generated RCM implementation model (or set of models) which better meets a specific set of timing requirements. To this end, the following contributions are identified:

- RCM metamodel. Model transformations are required for achieving a full-fledged MDE approach for leveraging end-to-end delay timing analysis at design level. Moreover, model transformations are specified on the involved metamodels. While EAST-ADL provides a metamodel definition for the design level, RCM has not been described by metamodeling means. This contribution provides a metamodel definition for RCM.

- 2. *Model transformation between EAST-ADL design level metamodel and RCM metamodel.* This contribution allows the automatic translation from an EAST-ADL design model into a set of meaningful RCM implementation models that can be used as input for running end-to-end delay timing analysis.

- 3. *Selection mechanism.* Based on end-to-end delay timing analysis results, this contribution supports the selection of the RCM implementation model (or set of models) which better meets a specific, non-empty set of timing requirements.

## 1.2 Terminology

In this section we introduce the terms that we use in the remainder of this licentiate thesis.

- *End-to-end delay timing analysis*. Schedulability analyses are *a priori* analysis techniques used for ensuring that the software system meets its timing requirements. End-to-end delay timing analysis are well-established schedulability analyses which calculate upper bounds on the response time and delays of event chains distributed over several nodes or in the system. We will refer to *end-to-end delay timing analysis* simply as *timing analysis*.

- *EAST-ADL design level*. We will refer to *EAST-ADL design level* simply as *design level*.

### 1.3 Thesis Outline 7

- *EAST-ADL implementation level*. We will refer to *EAST-ADL implementation level* simply as *implementation level*.

- *EAST-ADL design level model*. We will refer to *EAST-ADL design level model* simply as *design model*.

- *EAST-ADL implementation level model.* We will refer to *EAST-ADL implementation level model* simply as *implementation model*.

- *RCM implementation model*. Different component models can be used at the implementation level. As aforesaid, we decided to use RCM as the target language for the implementation level. With the term *RCM implementation model* we refer to a RCM model used at the implementation level.

- *Timing requirement*. We will refer to *timing requirement* as the required timing performance specified on the vehicle functionality. A typical example would be: "the time between the request from the driver and the response of the physical system shall be lower than 10 milliseconds".

- *Timing property and timing value. Timing property* is a property which concerns the timing behavior of the software. A typical example of a timing property is the worst-case execution time of a function. *Timing value* is the actual value of a timing property.

- *Timing element*. We refer to *timing element* as a modeling element which represents a timing property or requirement.

- *Non-bijective model transformation*. A *non-bijective model transformation* is a model transformation that translates a single source model into multiple target models.

## **1.3 Thesis Outline**

The remainder of this thesis is organized as follows. Chapter 2 describes the research plan in terms of research goals, challenges and contributions. Chapter 3 discusses conclusions and future directions. The second part of the thesis consists of Chapter 4 through Chapter 7 and describes the research contributions in terms of research publications.

## Chapter 2

## **Research Plan**

This chapter discusses the adopted research plan in terms of research goal, research challenges (RCs), research methodology and research contributions (RCOs).

### 2.1 Research Goal

Timing requirements are crucial in the design of the software running on vehicular embedded systems [9] [8]. Timing analysis is a primary means by which timing requirements are verified. However, design decisions are usually not driven by timing analysis results as timing analysis is usually performed after the design activities [12]. To this end, we believe that anticipating timing analysis at design level can mitigate software development issues (e.g., cost, time-to-market) as it would avoid late discoveries (i.e., during the testing activities) that the system delivers services of unacceptable quality with respect to timing [10] [8]. Within an EAST-ADL based methodology, the way towards early timing analysis is hampered by the weak linkage between the modeling language used at the implementation level (where timing analysis is usually performed) and the language used at the design level.

The goal of this research work is to enable timing analysis at design level for supporting design decisions. More specifically, we aim at providing an approach which gives automation means for seamlessly linking design and implementation level.

### 10 Chapter 2. Research Plan

## 2.2 Research Challenges

Considering the research goal, the following RCs have been formulated and used as main drivers for this research work.

#### RC 1. Definition of a metamodel for RCM.

While EAST-ADL does not fully embrace the MDE paradigm, it still provides metamodel definitions for the languages adopted at each abstraction level. Consequently, MDE seems to be the natural choice for automating an EAST-ADL based methodology.

According to the MDE paradigm, metamodels and model transformations are crucial for providing automation within the software development: the former serves for regulating the specification of models while the latter for automating their manipulations. In particular, it is very beneficial that all the modeling languages involved in the development process are provided with a metamodel definition. Considering that we want to provide automation between the design and implementation levels, both the languages used at these levels should be provided with metamodel definitions. While for the design level a metamodel definition exists, our challenge is the definition of a metamodel for RCM, the language we use at the implementation level. In particular, the metamodel should be defined bearing in mind the following:

- 1. *Backward compatibility:* the metamodel should not hinder a migration of legacy RCM artifacts.

- 2. Maintainability: the metamodel should be easy to update and refine.

### RC 2. Definition of a mapping between EAST-ADL design level metamodel and RCM metamodel.

Separation of concerns and abstraction are the pillars on which EAST-ADL relies and the EAST-ADL abstraction levels are designed to ensure these principles. Within EAST-ADL, timing analysis can only be performed at the implementation level, since timing properties are not entailed in higher abstraction levels.

One way to leverage timing analysis results at design level is the definition of a transparent and automatic process able to translate design models to implementation models, i.e., RCM implementation models, on which timing analysis can be performed. In fact, RCM implementation models contain timing elements, e.g., clocks, control-flow ports, to mention a few, that can not be modeled at the design level. However, these elements represent variability points in the transition from design to implementation level, meaning that

#### 2.3 Research Contributions 11

more than one RCM implementation model can be a valid translation of a given design model [13].

The challenge is to define and implement a semi-automatic translation able to produce a set of RCM implementation models for a given design model avoiding any manual, error-prone and time-consuming model manipulations.

## **RC 3.** Definition of a mechanism for the selection of the best **RCM** model for a specific, non empty set of timing requirements.

This represents the last step in the process of leveraging timing analysis at design level for enabling guided design decisions. After the RCM implementation models are generated, timing analysis is run. Based on the timing analysis results, the challenge is to define a mechanism able to select the RCM implementation model which better meets a specific, non empty set of timing requirements. The mechanism should be able to select multiple equally good RCM implementation models. Once the RCM implementation model (or set of models) is identified, its analysis results should be propagated back to design level and made accessible to the developer. In case no RCM implementation model are required.

## 2.3 Research Contributions

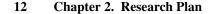

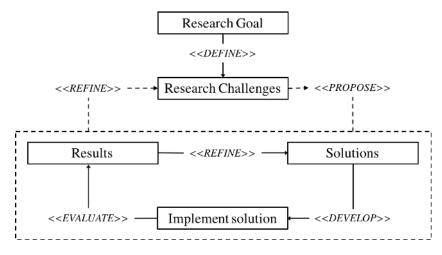

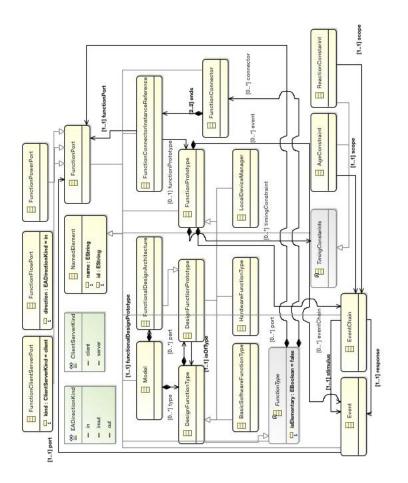

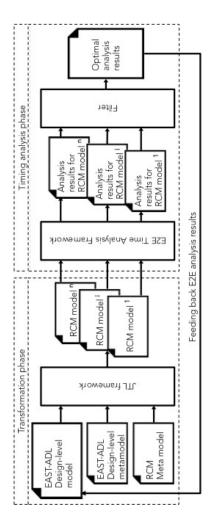

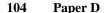

The main contribution of this licentiate thesis is the definition of an approach for seamlessly linking design and implementation level in order to enable timing analysis at design level. This is needed to allow timing analysis results to drive design decisions. Figure 2.1 provides a graphical representation of the proposed approach.

Starting from a *Design Model* representing an automotive software functionality, the approach is able to generate a set of corresponding *RCM Model(s)*. The generated set contains all the *RCM Model(s)* which are meaningful for the considered *Timing Analysis*. *RCM Model(s)* are equipped with timing elements. While the generation of these elements is fully automated, their completion with timing properties is entrusted to the developer. That is to say, the developer drives the automatic generation of all the meaningful combinations of timing elements by inserting timing properties, via configuration files, only once per element instead of having to manually edit all the generated *RCM Model(s)*. At this point, *Timing Analysis* is run on the generated *RCM Model(s)* resulting in a set of *Analysis Result(s)*. These results are checked against a non-

Figure 2.1: Research Contributions

empty set of *Timing Requirements* and the *RCM Model* which better satisfies the *Timing Requirements* is selected; note that multiple *RCM Models* might be equally good and thereby selected. Eventually, the corresponding analysis results, i.e., *Selected Analysis Result(s)*, are propagated back to the developer by means of annotations to the design model. Figure 2.1 provides a breakdown of the main contribution in specific RCOs.

**RCO 1 - RCM metamodel**. This contribution, marked as 1 in Figure 2.1, provides a metamodel definition for RCM as the first step in the process of providing automation means. The RCM metamodel has been realized within the Eclipse Modeling Framework<sup>1</sup> (EMF) as an EMF model, and it has been defined with particular attention to backward compatibility and maintainability.

In order to address the first goal, i.e., backward compatibility, we reverseengineered the internal representation of RCM into the Rubus-ICE for polishing redundancies and optimizing model traversals. This resulted in the addi-

<sup>&</sup>lt;sup>1</sup>http://www.eclipse.org

#### 2.3 Research Contributions 13

tion of 6 modeling elements (e.g., connectors) and the refinement of element hierarchies (e.g., ports and data element hierarchies). With respect to maintainability, building-up the development environment on the RCM metamodel allows to separate the modeling elements from their rendering and features of the development environment.

**RCO 2 - DL2RCM transformation**. This contribution, marked with 2 in Figure 2.1, provides a model-to-model transformation between design models and RCM implementation models (DL2RCM).

The DL2RCM transformation has been implemented by means of a bidirectional model transformation language, namely Janus Transformation Language (JTL) [14]. JTL is a constraint-based bidirectional model transformation language specifically tailored to support non-bijectivity by generating all the possible models, at once. JTL adopts a QVTr-like syntax [15], supports object pattern matching, and implicitly creates traces to record what occurs during the execution of a model transformation. The JTL implementation relies on the Answer Set Programming (ASP) [16], which is a declarative programming language based on the *answer set* (model) semantics of logic programming. The ASP solver, by means of a deductive process, finds and generates in a single execution all the possible models which are consistent with the transformation rules.

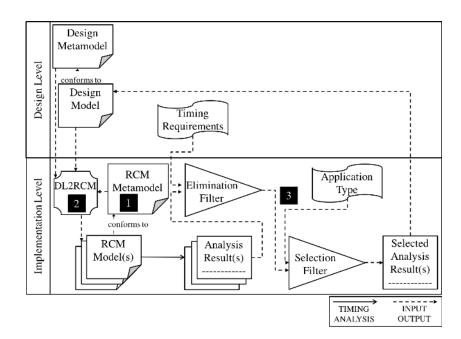

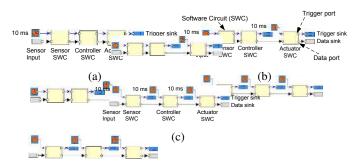

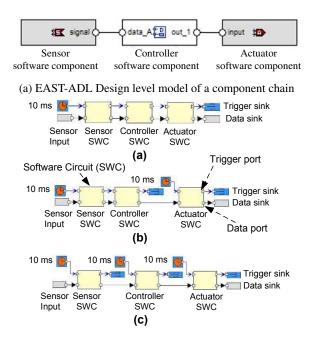

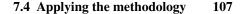

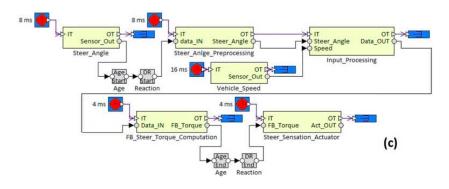

The DL2RCM transformation consists of 28 rules mapping design elements to corresponding RCM implementation elements. The contribution brought by the DL2RCM transformation is two-fold. On the one hand, it allows the automatic translation of EAST-ADL design models to RCM implementation models. On the other hand, it is able to generate the set of all meaningful RCM implementation models for a given design model. That is to say, given the EAST-ADL design model depicted in Figure 2.2a and considering the generation of clocks in the RCM implementation models, the DL2RCM transformation produces 8 RCM implementation models each of which has a unique combination of clocks. 3 of the 8 possible models are depicted in Figure 2.2b.

It is worth to note that JTL supports the specification of logic constraints which can be used for reducing the number of generated models and tailoring their generation for specific purposes. In the specific case of the DL2RCM transformation, we employed logic constraints for forcing the injectivity on the design elements not affected from the specified timing constraints. Paper A (Section 4) discusses an initial version of the transformation which produces one single RCM model from a design model. In Paper D (Section 7) we provide an enhanced version which is able to generate all the meaningful RCM

### 14 Chapter 2. Research Plan

(b) 3 of the 8 RCM implementation models for the model in Figure 2.2a

Figure 2.2

models for the leveraged timing analysis.

RCO 3 - Filtering mechanism. This contribution, marked as 3 in Figure 2.1, provides a conceptual mechanism supporting the selection of the best RCM implementation models for a specific, non-empty, set of timing requirements. This represents the last step in the process of leveraging timing analysis at design level for driving design decisions. The proposed filtering mechanism consists of two cascaded filters, i.e., the elimination filter and the selection filter, as shown in Figure 2.1. After timing analysis is run on the generated RCM implementation models, the RCM implementation models and their analysis results are provided as input to the elimination filter together with the non-empty set of timing requirements specified on the vehicle functionality. The elimination filter discards all the RCM implementation models whose analysis results violate the set of timing requirements. The remaining RCM implementation models, along with their analysis results, are provided as input to the selection filter. This filter further refines the selection by considering the type of component chains required from the vehicle software functionality, i.e., single-rate chain or *multi-rate chain*<sup>2</sup>, also received as an input. If the selection mechanism fails in identifying a suitable RCM implementation model, architectural refinements at the design model may be needed and the developer will be notified with a message in the console. Similarly, the developer will be notified if one (or a set of) RCM implementation model is selected. Paper B (Section 5) and Paper C (Section 6) present and discuss an initial version of the selection mechanism consisting of the elimination filter. Paper D (Section 7) describes the enhanced version of the selection mechanism consisting of the two cascade filters. Table 2.1 summarizes the relations between RCOs and RCs: RC 1 and RC 2 are addressed by the RCO 1 and RCO2, while RCO 3 addresses RC 3.

|                        |       | Research Challenges |      |      |  |

|------------------------|-------|---------------------|------|------|--|

|                        |       | RC 1                | RC 2 | RC 3 |  |

|                        | RCO 1 | X                   | Х    |      |  |

| Research Contributions | RCO 2 |                     | Х    |      |  |

| Research Contributions | RCO 3 |                     |      | Х    |  |

Table 2.1: Research Contributions in relation to the Research Challenges

<sup>&</sup>lt;sup>2</sup>In the body electronics domain, the applications are modeled with single-rate chains whereas in the control systems domain the applications are modeled with multi-rate chains.

### 16 Chapter 2. Research Plan

### 2.4 Papers Contribution

Table 2.2 shows the relation between the included papers and the RCOs.

|                 | Research Contributions |       |       |       |

|-----------------|------------------------|-------|-------|-------|

|                 |                        | RCO 1 | RCO 2 | RCO 3 |

|                 | Α                      | Х     | Х     |       |

| Included papers | В                      |       | Х     | Х     |

| included papers | С                      |       | Х     | Х     |

|                 | D                      |       | Х     | Х     |

Table 2.2: Included papers in relation to the Research Contributions

### 2.4.1 Paper A

A Metamodel for the Rubus Component Model: Extensions for Timing and Model Transformation from EAST-ADL, Alessio Bucaioni, Saad Mubeen, Federico Ciccozzi, Antonio Cicchetti, Mikael Sjödin.

*Abstract* –According to the model-driven engineering paradigm, one of the entry requirements when realizing a seamless tool chain for the development of software is the definition of metamodels, to regulate the specification of models, and model transformations, for automating manipulations of models. In this context, we present the metamodel for an industrial component model, the Rubus component model, which is used by several international companies for the development of vehicular embedded systems. The metamodel includes the definition of structural elements as well as concepts for describing timing information. In order to show how, using model-driven engineering, the integration between models conforming to the automotive domain-specific architecture description language EAST-ADL and models described with the Rubus component model. We also conduct an automotive-application case study to show the applicability of the Rubus component model and the model transformation.

Status. Conditionally accepted at the Journal of Systems and Software (JSS).

**Personal Contribution.** The research work presented in this paper was done in collaboration with all the authors. I am the main contributor and driver.

#### 2.4 Papers Contribution 17

### 2.4.2 Paper B

**Exploring Timing Model Extractions at EAST-ADL Design-level Using Model Transformations**, *Alessio Bucaioni, Saad Mubeen, Antonio Cicchetti, Mikael Sjödin*, Proceedings of the 12th International Conference Information Technology: New Generations (ITNG), IEEE, Las Vegas, Nevada (USA), April, 2015.

*Abstract* – We discuss the problem of extracting control and data flows from vehicular distributed embedded systems at higher abstraction levels during their development. Unambiguous extraction of control and data flows is vital part of the end-to-end timing model which is used as input by the end-to-end timing analysis engines. The goal is to support end-to-end timing analysis at higher abstraction levels. In order to address the problem, we propose a two-phase methodology that exploits the principles of model driven engineering and component based software engineering. Using this methodology, the software architecture at a higher level is automatically transformed to all legal implementation-level models. The end-to-end timing analysis results are fed back to the design-level model. This activity supports design space exploration, model refinement and/or remodeling at higher abstraction levels for tuning the timing behavior of the system.

Status. Published.

**Personal Contribution.** The research work presented in this paper was done in collaboration with all the authors. I am the main contributor and driver.

### 2.4.3 Paper C

**Raising Abstraction in Timing Analysis for Vehicular Embedded Systems through Model-Driven Engineering**, *Alessio Bucaioni*, Proceedings of the Doctoral Symposium at Software Technologies: Applications and Foundations (STAF), L'Aquila, Italy, July, 2015. *Best paper award*.

*Abstract* – The complexity of vehicular embedded systems is continuously increasing and this can negatively affect their development cost and time to market. One way to alleviate these issues is to anticipate analysis of system properties at design time for early architectural refinements. In this paper, we

#### 18 Chapter 2. Research Plan

present a licentiate work which aims at contributing to this effort. In particular, considering the importance of timing constraints typical of vehicular embedded systems, we leverage model-driven engineering for realizing an automatic approach which allows the developer to perform timing analysis on design models, without having to manually specify timing elements. The proposed approach, starting from a high-level model of the vehicular embedded application, generates a set of candidate models enriched with timing elements in a semi-automatic manner. Timing analysis is run on the generated models and, based on its results, the approach supports the selection of the best candidate model for a specific, non-empty, set of timing constraints.

Status. Published.

Personal Contribution. I am the main contributor and driver.

### 2.4.4 Paper D

Anticipating Implementation-Level Timing Analysis for Driving Design-Level Decisions in EAST-ADL, *Alessio Bucaioni, Antonio Cicchetti, Federico Ciccozzi, Romina Eramo, Saad Mubeen, Mikael Sjödin, Proceedings of the 1st International Workshop on Modelling in Automotive Software Engineering (MASE) at ACM/IEEE 18th International Conference on Model Driven Engineering Languages and Systems (Models), Ottawa, Canada, September, 2015.*

*Abstract* – The adoption of model-driven engineering in the automotive domain resulted in the standardization of a layered architectural description language, namely EAST-ADL, which provides means for enforcing abstraction and separation of concerns, but no support for automation among its abstraction levels. This support is particularly helpful when manual transitions among levels are tedious and error-prone. This is the case of design and implementation levels. Certain fundamental analyses (e.g., timing), which have a significant impact on design decisions, give precise results only if performed on implementation-level models, which are currently created manually by the developer. Dealing with complex systems, this task becomes soon overwhelming leading to the creation of a subset of models based on the developer?s experience; relevant implementation-level models may therefore be missed. In this work, we describe means for automation between EAST-ADL design and implementation levels to anticipate end-to-end delay analysis at design level for driving design decisions.

Status. Published.

**Personal Contribution.** The research work presented in this paper was done in collaboration with all the authors. I am the main contributor and driver.

## 2.5 Research Methodology

Software engineering research is often stimulated by problems arising from the development and usage of software in the real-life [17]. Collaborative research between industry and academia is a great example of this phenomenon. The

Figure 2.3: Research Methodology

research methodology applied to this licentiate thesis follows the definition of the *engineering method* given in [18]. That is, "observe existing solutions, propose better solutions, build/develop, measure and analyze, and repeat the process until no more improvements appear possible".

Figure 2.3 shows a refinement of this engineering method, adopted for this licentiate thesis work. The industrial demands coming from our industrial partners were used for driving an initial investigation of the related state-of-the-art and the state-of-the-practice. The underlying goal of such an investigation was the definition of a clear research goal. Eventually, starting from the elicited re-

#### 20 Chapter 2. Research Plan

search goal, we defined a set of set of research challenges. For each of them, we conducted an investigation of the related state-of-the-art and the state-of-thepractice with the aim of proposing a possible solution if none existed. After a solution was developed, we evaluated its applicability upon industrial case studies (or case studies mimicking industrial scenarios). Based on the evaluation results, the proposed solution could be refined. This was the case of the model transformation described in RCO 2. In fact, the initial model transformation presented in Paper B (Section 5) has been enhanced in Paper C (Section 7) and Paper E (Section 7), considering the collected results. Eventually, the findings acquired during the elicitation, implementation and evaluation of the solutions, were used for refining the set of research challenges. An example of this iterative process is the selection mechanism described in RC 3. Such a challenge arose only when the enhanced version of the model transformation was developed. In fact, the need of a selection mechanism would be negligible if the model transformation would produce only one single RCM model per design model.

## Chapter 3

## **Conclusions and Future Works**

The complexity of software running on embedded systems is constantly increasing, negatively affecting its development costs and time to market. Among the many software development methodologies advocating i) abstraction, ii) separation of concerns, and iii) automation, when dealing with the software development, MDE has progressively gained academic and industrial recognition. Within the automotive domain, the adoption of MDE resulted in the standardization of the layered architecture description language EAST-ADL. While EAST-ADL provides means for abstraction and separation of concerns it does not support automation for transformation between its abstraction levels.

With this licentiate thesis, we introduced an approach which provides automation means for seamlessly linking EAST-ADL design and implementation levels. The underlying goal is to leverage timing analysis at design level such that analysis results can drive design decisions. The overall contribution of the thesis can be broken down into three main research contributions: i) a meta-model definition for the Rubus Component Model (RCM) which is one posisble implementation model for EAST-ADL, ii) automated model transformation from design model to RCM implementation models (called DL2RCM) and iii) a mechanism for the selection of the RCM implementation model which better meets a specific set of timing requirements. The formalization of the RCM metamodel serves as base for leveraging the proposed approach. The DL2RCM transformation provides automation means for seamlessly linking

#### 22 Chapter 3. Conclusions and Future Works

design and implementation levels, avoiding error-prone and time-consuming activities. By doing so, it allows to leverage timing analysis at design level avoiding the problem of manually identifying a suitable RCM implementation models, in terms of timing characteristics. Eventually, the selection mechanism serves as last step for automatically identifying the best RCM implementation model (or set of models) and propagating back the corresponding analysis results.

Leveraging timing analysis at design level can bring multiple advantages. First of all, it helps the designer in taking design decisions based on much more precise feedback than common design level analysis, which often provides just estimations based on guessed values. We believe that, through our approach it is possible to disclose the opportunity of employing expensive software development resources (e.g., developers, timing experts) more efficiently, therefore to reduce software development costs and time to market. In fact, the proposed approach allows the developer to focus only on design activities exploiting timing analysis without having to investigate nor manually edit implementation models.

The DL2RCM may suffer from scalability issues when dealing with complex design models. Therefore, as a possible continuation of this research work towards a doctoral thesis, we plan to improve the scalability of the generation process. In particular, we will investigate the definition of smarter transformation rules which could avoid the generation of less relevant RCM implementation models by considering preliminary/run time knowledge. Also, we are planning to improve the Janus Transformation Language such that it could consider heuristics for the generation of classes of models. Our experience has shown that, besides timing, other relevant system properties need to be dealt with at design level. Therefore, another interesting research direction could be to investigate the possibility to leverage our approach to combine the optimization of multiple system properties, e.g., memory demands. Eventually, together with our industrial partners we will investigate challenges as well as possible benefits and drawbacks of extending the proposed approach to higher abstraction levels in EAST-ADL. We would also like to conduct empirical evaluations of the proposed technique in a real industrial context.

## **Bibliography**

- [1] Bas Graaf, Marco Lormans, and Hans Toetenel. Embedded software engineering: the state of the practice. *Software*, *IEEE*, 20(6):61–69, 2003.

- [2] Stuart Kent. Model driven engineering. In *Integrated formal methods*, pages 286–298. Springer, 2002.

- [3] Jean Bézivin and Olivier Gerbé. Towards a precise definition of the omg/mda framework. In Proceedings of the 16th IEEE International Conference on Automated Software Engineering, 2001.

- [4] Shane Sendall and Wojtek Kozaczynski. Model transformation: The heart and soul of model-driven software development. *Software, IEEE*, 20(5):42–45, 2003.

- [5] EAST-ADL Domain Model Specification, Deliverable D4.1.1, 2010. http://www.atesst.org/home/liblocal/docs/ATESST2\_D4.1.1\_EAST-ADL2-Specification\_2010-06-02.pdf.

- [6] George T. Heineman and William T Councill. Component-based software engineering: putting the pieces together. *Component-based software engineering: putting the pieces together*, pages 33–48, 2001.

- [7] Kaj Hänninen, Jukka Mäki-Turja, Mikael Sjödin, Mats Lindberg, John Lundbäck, and Kurt-Lennart Lundbäck. The rubus component model for resource constrained real-time systems. In 3rd IEEE International Symposium on Industrial Embedded Systems, June 2008.

- [8] Bran Selic and Leo Motus. Using models in real-time software design. *Control Systems, IEEE*, 23(3):31–42, June 2003.

- [9] Philippe Cuenot, Patrick Frey, Rolf Johansson, Henrik Lönn, Mark-Oliver Reiser, David Servat, R Tavakoli Koligari, and DeJiu Chen. Developing automotive products using the east-adl2, an autosar compliant architecture description language. In *Embedded Real-Time Software Conference*. Citeseer, 2008.

- [10] Nico Feiertag, Kai Richter, Johan Nordlander, and Jan Jonsson. A Compositional Framework for End-to-End Path Delay Calculation of Automotive Systems under Different Path Semantics. In Proceedings of the IEEE Real-Time System Symposium ? Workshop on Compositional Theory and Technology for Real-Time Embedded Systems, 2008.

- [11] Ken Tindell and John Clark. Holistic schedulability analysis for distributed hard real-time systems. *Microprocessing and microprogramming*, 40(2):117–134, 1994.

- [12] Ian Sommerville, Wendy Boggs, Michael Boggs, Bernd Bruegge, Allen H Dutoit, Wendy Boggs, and Michael Boggs. Software engineering 7 th ed. 2002.

- [13] Alessio Bucaioni and Romina Eramo. Understanding bidirectional transformations with tggs and jtl. In *Second International Workshop on Bidirectional Transformations*, March 2013.

- [14] Antonio Cicchetti, Davide Di Ruscio, Romina Eramo, and Alfonso Pierantonio. Jtl: A bidirectional and change propagating transformation language. In *Software Language Engineering*, volume 6563, pages 183– 202. 2011.

- [15] Meta Object Facility (MOF) 2.0 Query/View/Transformation (QVT). OMG Group.

- [16] Michael Gelfond and Vladimir Lifschitz. The stable model semantics for logic programming. volume 88, pages 1070–1080. MIT Press, 1988.

- [17] Mary Shaw. The coming-of-age of software architecture research. In Proceedings of the 23rd International Conference on Software Engineering, page 656. IEEE Computer Society, 2001.

- [18] Victor R. Basili. The experimental paradigm in software engineering. In Experimental Software Engineering Issues: Critical Assessment and Future Directions, pages 1–12. Springer, 1993.

II

**Included Papers**

**Chapter 4**

# Paper A: A Metamodel for the Rubus Component Model: Extensions for Timing and Model Transformation from EAST-ADL

Alessio Bucaioni, Saad Mubeen, Federico Ciccozzi, Antonio Cicchetti and Mikael Sjödin

Conditionally accepted at the Journal of Systems and Software (JSS)

## Abstract

According to the Model-Driven Engineering paradigm, one of the entry requirements when realizing a seamless tool chain for the development of software is the definition of metamodels, to regulate the specification of models, and model transformations, for automating manipulations of models. In this context, we present the metamodel for an industrial component model, the Rubus Component Model, which is used by several international companies for the development of vehicular embedded systems. The metamodel includes the definition of structural elements as well as elements for describing timing information. In order to show how, using Model-Driven Engineering, the integration between models can be automate, we present a model-to-model transformation between models conforming to the automotive domain-specific architecture description language EAST-ADL and models described with the Rubus Component Model. We also conduct an automotive-application case study to show the applicability of the Rubus Component Model metamodel and the model transformation.

| ĺ | 1.1 | Introduction | - 29 |

|---|-----|--------------|------|

|   |     |              |      |

## 4.1 Introduction

During the last decades, industrial demands on vehicular embedded systems have been constantly evolving causing an increment of the related software complexity. It has been estimated that current vehicles can have more than 70 embedded systems running up to 100 million lines of code [1]. On the one hand, industry needs efficient processes to cope with the size of these systems for optimizing software development cost and time-to-market. On the other hand, most of vehicular embedded systems have extra-functional properties, e.g., timing requirements and constraints, which have to be taken into account from the early stages of the development. In fact vehicular embedded systems are real-time systems [2], meaning that they must deliver their functionality within their timing deadlines. Consequently, timing requirements are crucial for these systems. In this context, traditional software development processes have shown strong limitations.

Component Based Software Engineering (CBSE) has been acknowledged as an effective practice to deal with the increasing complexity of modern embedded software [3] by promoting software development at a higher level of abstraction relying on the definition and reuse of atomic units of composition, i.e., software components. Additionally, CBSE allows to express timing properties, e.g., by annotating the software components with properties and constraints (e.g., worst-case execution time) thus enabling timing analysis, e.g., end-to-end response time and delay analysis [4].

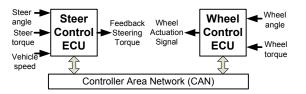

AUTOSAR [5] and the Rubus Component Model (RCM) [6], to name a few, are examples of component models (CMs) used within the vehicular domain. Lately, AUTOSAR has become part of the EAST-ADL initiative [7]. EAST-ADL is an architecture description language (ADL) which provides concepts and methods for managing and organizing the various artifacts produced along the software development of vehicular embedded systems [8]. It promotes the separation of concerns through a top-down software development process relying on four different abstraction levels, i.e., vehicle, analysis, design and implementation level. In the latter level, EAST-ADL makes use of AUTOSAR. Both EAST-ADL and AUTOSAR, embracing the Model-Driven Engineering (MDE), have been provided with metamodel definitions. MDE is a paradigm that intends software development as the process of designing and refining models, starting from higher and moving towards lower levels of abstraction, via the so-called model transformations.

While EAST-ADL has been proven successful in coping with the software complexity and size of industrial embedded software, it still provides

limited support for dealing with timing requirements. In fact, by employing AUTOSAR at implementation level, most of the timing, implementation and communication details are neglected. This information is necessary for building software timing models used for verifying timing requirements.

In this context, an increasing number of vehicular manufacturers are using RCM as a complementary technology in EAST-ADL based processes. In this case, in order to allow a smooth interplay between different languages in these processes, proper automation is needed for the translation among the various artifacts specified using, e.g., RCM and EAST-ADL. This aspect is even more crucial when considering that, in practice, manual translations are not only tedious, time consuming and error-prone, but even unfeasible in most of the cases due to the size and complexity of the models involved. To this end, MDE has been proven effective in reducing the software development cost and time to market [9] while automating the whole development process. In order to embrace the MDE paradigm and benefit from its advantages, it is necessary to define proper metamodels for any modeling language (e.g., component models) involved in the development process together with proper model transformations devoted manipulations of models, taking into account the need of modeling both functional and extra-functional concepts.

In this paper, we define a metamodel for RCM, that is used for the software development of vehicular real-time embedded systems. The metamodel is defining according to the following main goals:

- **backward compatibility:** the metamodel should allow an easy migration of legacy RCM artifacts into the new modeling environment;

- **maintainability:** the metamodel should enable a better management of RCM updates and refinements;

- **extensibility:** the metamodel should disclose the opportunity to integrate in a smooth way RCM modeling environment in a typical automotive application development chain.

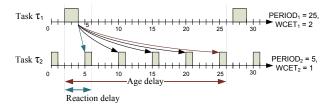

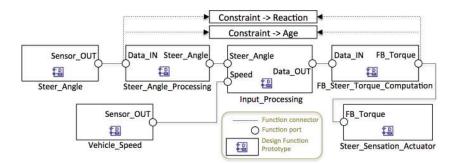

To this end, we first present the definition of metamodeling elements representing the software architecture. Then, we extend the metamodel with concepts representing timing constraints and properties for different type of delays in event chains. Instead of discussing the complete timing package in RCM, we focus on the elements representing the latest timing constraints (and corresponding timing information and analyses) introduced and practically used within the automotive industrial domain, i.e., the age and reaction delays [10, 7, 11, 4]. Moreover, we show how the integration between EAST-ADL and

#### 4.2 Background and related work 31

RCM can be automated using the MDE paradigm, by presenting a model-tomodel transformation from the EAST-ADL Design level to RCM (DL2RCM) together with a case study which mimics a typical industrial scenario.

The rest of the article is organized as follows. Section 4.2 presents the context of this work together with its related works. Section 4.3 introduces the RCM metamodel and extensions for timing elements. Section 4.4 shows the DL2RCM transformation while Section 4.5 discusses its applicability on a case study. Finally, Section 4.6 highlights the benefits of having a proper metamodel for RCM while Section 4.7 draws conclusions and discusses future works.

## 4.2 Background and related work

## **4.2.1** MDE and CBSE in the Automotive Domain

MDE is a paradigm which aims at raising the level of abstraction of software development by focusing on modeling activities rather than coding. In this context, MDE promotes *models* and *model transformations* as first-class citizens.

Models represents an abstraction of the system under development, from a particular point of view [12]. The set of rules and constraints needed for building a valid model is specified in the so-called *metamodel*. Formally, a metamodel defines the abstract syntax of a given model, or set of models; the relation between metamodel and models is called conformance. Model transformations represent the means of refinement by which models are manipulated [13]. In fact, model transformations translate a source model into a target model keeping their conformance to the respective metamodel intact.

According to the MDE paradigm, starting from a model and by means of model transformations it is possible to automatically obtain a variety of artifacts, such as new models, code, etc. In this context, the entire software development can be seen as a transformation process where low level abstraction models are automatically obtained by means of model transformations from higher-level abstraction models.

Within the automotive domain, the adoption of MDE and CBSE paradigms led to the standardization of an architectural description language, namely EAST-ADL [7]. EAST-ADL proposes a view over the development process composed by four different abstraction levels. Figure 4.1 shows the abstraction levels together with methodologies and languages used at each one of them.

Figure 4.1: EAST-ADL abstraction levels

The *vehicle level* is the highest abstraction level and captures information regarding the system's functionality. In this level, feature models can be used for showing what the system provides in terms of functionality. Also, these models are decorated with requirements. The vehicle level is also known as end-to-end level as it serves to capture requirements and features on the end-to-end vehicle functionality.

At the *analysis level*, vehicle functions are expressed, using formal notations, in terms of behaviors and interfaces. Yet, design and implementation details are omitted. The artifact developed at this level is called Functional Analysis Architecture. At this stage, high level analysis for functional verification can be performed.

At the *design level*, the analysis-level artifacts are refined with designoriented details: while the analysis level does not differentiate among software, middleware and hardware, the design level explicitly separates them. Allocation of software functions to hardware nodes is expressed at this level too. The artifacts developed at this level include Functional Design Architecture and Hardware Design Architecture.

At the *implementation level*, artifacts introduced at the design level are refined with implementation details. The output of this level is a complete software architecture which can be used for code generation. At this stage component models, e.g., RCM, AUTOSAR, are used to model the system in terms of components and interactions among them.

AUTOSAR is an industrial initiative to provide standardized software architecture for the software development of vehicular embedded systems. Within AUTOSAR, the software architecture is defined in terms of *software compo*-

### 4.2 Background and related work 33

*nents* (SWCs) and *Virtual Function Bus* (VFB). VFB handles the virtual integration and communication among SWCs, hiding low-level implementation details. AUTOSAR describes the software at a high level of abstraction focusing on the functional and structural aspects of the architecture. Also, it does not distinguish between data and control flow, as well as between inter- and intra-node communication.

Lately, AUTOSAR has been provided with a timing model within the two EU research projects TIMMO [14] and TIMMO-2-USE [15], respectively. To this end, TIMMO provides a predictable methodology and language, called TADL [16] for expressing timing requirements and constraints. TADL is inspired by MARTE [17], which is a UML profile for modeling and analysis of real-time and embedded systems. The TIMMO methodology makes use of EAST-ADL and AUTOSAR interplay, where the former is used for the software structural modeling, while the latter is used for the implementation. TIMMO-2-USE [15], a follow up project, presents a major redefinition of TADL in TADL2 [10]. The purpose of this project is to include new functionality for supporting the AUTOSAR extensions regarding timing model. Although both TIMMO and TIMMO-2-USE attempt to annotate AUTOSAR with a timing model, AUTOSAR is still not expressive enough for representing timing, implementation and communication information of the software architecture.

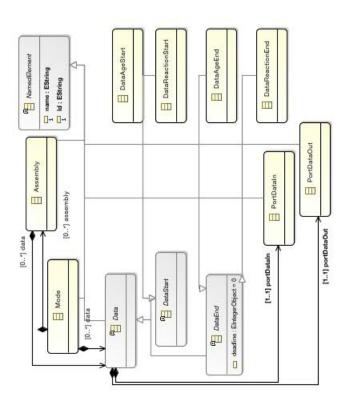

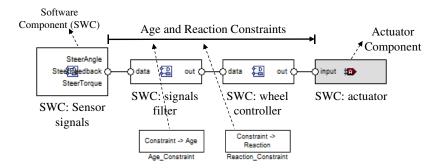

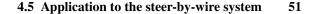

In this context, an increasing number of vehicular manufacturers are considering RCM as an alternative to AUTOSAR within the EAST-ADL based methodology. RCM supports both model- and component-based development. The main goal of RCM is to express the software architecture in terms of software functions and interactions among them. In RCM, the basic entity is the so-called *software circuit* (SWC) which represents the lowest-level hierarchical element in RCM and encapsulates basic software functions. Each SWC is defined by its *behavior* and *interface*. Interfaces manage the interactions among SWCs via ports. RCM distinguishes between data and control flow. Therefore, the interfaces have two types of ports: *data ports* for the data flow and *trigger ports* for the control flow. The SWC is characterized by run-to-completion semantics meaning that, upon triggering, it reads data from the data input ports, executes its behavior and writes data on the data output ports.

SWCs can be grouped and organized in *assemblies*, decomposing the system in a hierarchical manner. *Modes* are used to represent different configurations of the software architecture. *Target* entities are used for grouping modes that are deployed on the same Electronic Control Unit (ECU). Moreover, they provide details regarding hardware and operating system. *Node* is a hardware

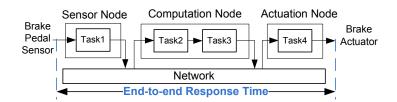

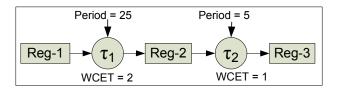

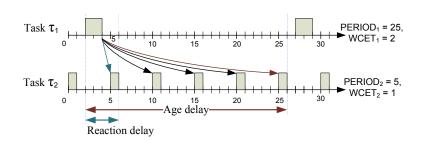

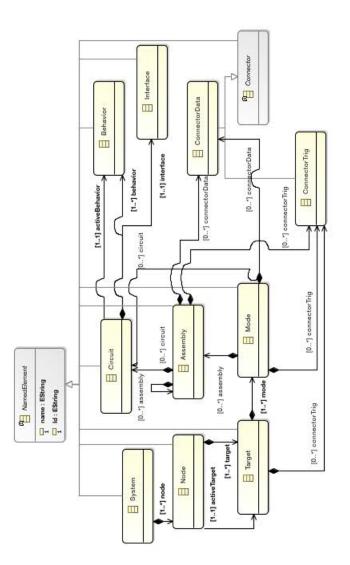

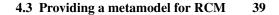

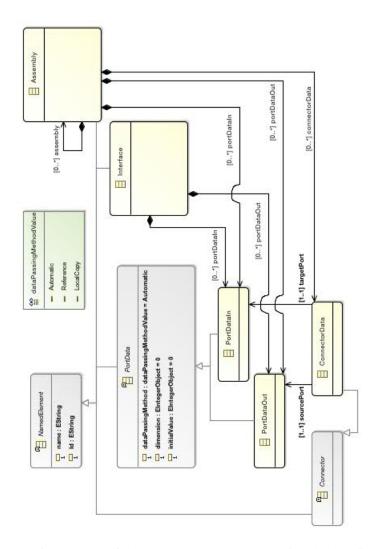

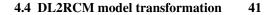

and operating-system independent abstraction of a target entity. Finally, *System* is the top-level hierarchical entity, which describes software architecture for the complete vehicular system.