# Random Dopant Induced Threshold Voltage Lowering and Fluctuations in Sub-0.1 $\mu$ m MOSFET's: A 3-D "Atomistic" Simulation Study

Asen Asenov

Abstract— A three-dimensional (3-D) "atomistic" simulation study of random dopant induced threshold voltage lowering and fluctuations in sub-0.1  $\mu$ m MOSFET's is presented. For the first time a systematic analysis of random dopant effects down to an individual dopant level was carried out in 3-D on a scale sufficient to provide quantitative statistical predictions. Efficient algorithms based on a single multigrid solution of the Poisson equation followed by the solution of a simplified current continuity equation are used in the simulations. The effects of various MOSFET design parameters, including the channel length and width, oxide thickness and channel doping, on the threshold voltage lowering and fluctuations are studied using typical samples of 200 atomistically different MOSFET's. The atomistic results for the threshold voltage fluctuations were compared with two analytical models based on dopant number fluctuations. Although the analytical models predict the general trends in the threshold voltage fluctuations, they fail to describe quantitatively the magnitude of the fluctuations. The distribution of the atomistically calculated threshold voltage and its correlation with the number of dopants in the channel of the MOSFET's was analyzed based on a sample of 2500 microscopically different devices. The detailed analysis shows that the threshold voltage fluctuations are determined not only by the fluctuation in the dopant number, but also in the dopant position.

*Index Terms*—Fluctuations, MOSFET, numerical simulation, 3-D, threshold.

#### I. INTRODUCTION

T the end of the silicon roadmap [1] in the year 2012, the feature size of integrated MOSFET's will be below 50 nm. However, individual devices with channel length below 50 nm have already been fabricated and characterized by several research groups [2], [3]. Full scale complementary metal-oxide-semiconductor (CMOS) technology based on 50 nm transistors has also been reported [4]. The steady lowering of the supply voltages, to reduce the power consumption and to hold the reliability, will make the systems based on such devices more sensitive to fluctuations in the device characteristics. Even if the fluctuations associated with lithographic dimensions and layer thicknesses are well controlled, random fluctuation of the relatively small number of dopants

The author is with the Device Modeling Group, Department of Electronics and Electrical Engineering, University of Glasgow, Glasgow G12 8LT, U.K.

Publisher Item Identifier S 0018-9383(98)09025-X.

and their discrete microscopic arrangement in the channel of sub-0.1  $\mu$ m MOSFET's will lead to significant variations in the threshold voltage and drive current. The problem was pointed out in the early seventies [5], [6] and first treated analytically and numerically in [7]. The predicted threshold voltage fluctuations were experimentally confirmed for a wide range of fabricated and measured MOSFET's [8]–[10] down to sub-0.1  $\mu$ m dimensions [11]–[14]. Such fluctuations may seriously affect the functionality [15], performance, and yield of the corresponding systems.

Several analytical models with different degrees of complexity, describing the random dopant induced threshold voltage fluctuations in MOSFET's, have been developed over the years [7], [8], [10], [16], [17]. Two-dimensional (2-D) numerical simulations have also been used to study, to some extent artificially, the effects of random dopant fluctuations in devices with a channel length down to 0.1  $\mu$ m [7], [18], [19]. Doping density fluctuations at each discretization node are introduced in such 2-D simulations through the statistical fluctuation of the random number of dopants in the volume associated with the node, depending on the width of the device. A similar approach has been adopted in the few published threedimensional (3-D) simulation studies [18], [20]. It is, however, clear that the detailed study of effects associated with the number fluctuations and the individual microscopic random distribution of the dopant atoms in sub-0.1  $\mu$ m MOSFET's requires 3-D simulations with fine grain discretization on a statistical scale. This is a computationally demanding task and very few 3-D "atomistic" simulation studies of random dopant fluctuation effects in MOSFET's have been published until now. In [21] for the first time, full scale 3-D "atomistic" drift-diffusion simulations were presented for a limited set of three transistors with channel length 100, 70, and 50 nm using statistics based on 24 microscopically different samples at each one channel length. In [22], the principles of 3-D "atomistic" hydrodynamic simulations were illustrated but no analysis of fluctuation phenomena on a statistical scale was carried out.

In this paper, we present a systematic 3-D "atomistic" simulation study of random dopant induced threshold voltage lowering and fluctuation in sub-0.1  $\mu$ m MOSFET's on a large statistical scale, involving samples of hundreds and thousands of microscopically different devices. The next section gives the

Manuscript received May 7, 1998; revised July 20, 1998. The review of this paper was arranged by Editor W. Weber.

details of our simulation approach. Section III summarizes the results for a wide range of sub-0.1  $\mu$ m devices with different channel lengths, channel widths, doping concentrations, and oxide thicknesses. It highlights also some of the problems associated with the control of the threshold voltage and its fluctuations in such devices. In Section IV, we discuss in more detail the origin of the threshold voltage fluctuations, making an attempt to disentangle the contributions from the dopant number fluctuations and from their random microscopic arrangement in the gate controlled depletion layer.

## II. SIMULATION TECHNIQUE

The computing power, typically available today, is still insufficient for carrying out 3-D "atomistic" simulations on a large statistical scale, even in a conventional drift-diffusion context. We focus our analysis only on the random dopant induced threshold voltage lowering and fluctuations in MOS-FET's with sub-0.1  $\mu$ m channel lengths. To substantially reduce the computation time all simulations and the threshold voltage extraction are carried out at a low drain voltage. This allowed us to use a single 3-D solution of the nonlinear Poisson equation at each bias point. At room temperature Boltzmann statistic is used for the electron and hole concentrations in the charge density term of the Poisson equation. At low drain voltage, the current for each bias point is calculated by solving a simplified current continuity equation, based on the majority carrier concentration obtained from the solution of the Poisson's equation. The threshold voltage is determined by using a current criteria of  $10^{-8}W_{\rm eff}/L_{\rm eff}$  A and an efficient search algorithm.

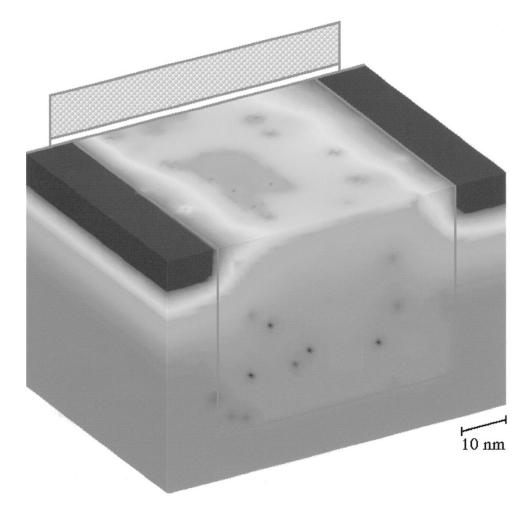

A typical solution domain for a MOSFET with an effective channel length  $L_{\text{eff}} = 50$  nm and an effective channel width  $W_{\rm eff} = 50$  nm is illustrated in Fig. 1. The "atomistic" region with random dopants under the gate is outlined in the picture. A 3-D solution of the Poisson equation, based on a uniform finite difference grid in such "atomistic" simulations, represents correctly the potential and the field associated with a single dopant only for distances larger than three mesh spacings from the node to which the dopant is assigned [23]. In order to resolve the effects associated with random discrete dopants down to an individual dopant level in sub-0.1  $\mu$ m devices, we use a uniform grid with a mesh spacing h typically 1 nm in the random dopant region. The average number of dopants in this region is calculated by integrating the continuous doping distribution within it. The actual number of dopants in the region is chosen from a Poisson distribution with a mean equal to the calculated average dopant number. Impurities with a probability distribution corresponding to the continuous doping distribution are placed randomly in the random dopant region using a rejection technique. They are assigned to the nearest point of the grid, introducing a charge density  $q/h^3$ .

The Poisson equation at a particular gate voltage is solved for a zero voltage applied between the source and the drain. Then, in the case of an n-channel MOSFET for example, the current density  $J_n$  associated with low applied drain voltage  $V_D$  is calculated by solving the continuity equation  $\nabla \cdot J_n =$ 0 with  $J_n = \sigma_n E_v$  where  $\sigma_n$  is the local conductivity and  $E_V$  is the electric field associated with the applied drain voltage. This leads to the following elliptic equation for the potential V driving the current

$$\nabla \cdot \mu_n n \nabla V = 0 \tag{1}$$

where  $\mu_n$  is the electron mobility and *n* is the electron concentration calculated from the solution of the Poisson equation. For properly scaled MOSFET's it is usually enough to solve (1) in a solution domain extending from the Si/SiO<sub>2</sub> interface down to less than 10 nm in the semiconductor. The boundary conditions are V = 0 at the source contact,  $V = V_D$ at the drain contact, and zero normal derivative of V at all other boundaries of the solution domain. In contrast to the standard drift-diffusion equation [24], the discretization of (1) leads to a symmetrical positive definite matrix which can be solved using standard iterative techniques.

The sharp variations in the potential resulting from the discrete nature of the charges on short length scales have an adverse effect on the convergence of most iterative solvers [23]. We have developed a multigrid solver for the solution of the Poisson and current continuity equations. It is very efficient, reducing both the long range residual components associated with the boundary conditions and the short range residual components associated with the discrete dopants in one W iteration cycle.

The whole simulator is written in a memory saving manner. In the case of a uniform grid, due to the extremely simple structure of the coefficients for a seven-point finite difference discretization star, and the simplicity of the multigrid solver, we do no use memory to store any matrices. This allows us to run a  $50 \times 70 \times 200$  node problem, without paging, on processing nodes with 32M RAM. Approximately three hours are required on a PowerMouse 4 processor Parsytec system, to accumulate statistics for the threshold voltage in a sample of 200 microscopically different MOSFET's with a  $50 \times 50 \times 70$  nm grid.

#### **III. SIMULATION RESULTS**

#### A. Setting the Scene

Our simulations are centered around MOSFET's with an effective channel length  $L_{\rm eff}$  = 50 nm representing the level of the technology expected near the end of the roadmap. The effective channel length is defined as the distance between the metallurgical pn junctions of the source and the drain at the Si/SiO2 interface. The channel width in most of the simulations is  $W_{\text{eff}} = 50$  nm. For comparison with analytical models, and an easier interpretation of the results, a uniform acceptor concentration is adopted in the random dopant region. Standard 2-D simulations shows that a doping level of  $N_A =$  $5 \times 10^{18} {\rm ~cm^{-3}}$  is required to efficiently suppress the short channel effects around the 50 nm channel length barrier. The typical oxide thickness in the simulations is  $t_{ox} = 3$  nm and the source/drain junction depth of all simulated devices is  $x_i = 7$  nm. However, both  $L_{\text{eff}}, W_{\text{eff}}, N_A$ , and  $t_{ox}$  are varied in the different simulation experiments in order to investigate their effect on the threshold voltage lowering and

Fig. 1. Solution domain and potential distribution in the "atomistic" simulation of a  $50 \times 50$  nm MOSFET.

fluctuations. A gate workfunction of 4 eV is used to emulate an n-type polysilicon gate but no polysilicon depletion effects are included in the simulations.

Based on previously published results [10], [14] we adopted the hypothesis that the threshold voltage fluctuations associated with random dopants follow a normal distribution. If the standard deviation of the threshold voltage for the whole population of microscopically different transistors is  $\sigma V_T^p$ , the mean threshold voltage  $\langle V_T \rangle$  and the standard deviation  $\sigma V_T$ estimated from a simulation sample with size N will have standard deviations  $\sigma_{\langle \rangle} = \sigma V_T^p / \sqrt{N}$  and  $\sigma_{\sigma} = \sigma V_T^p / \sqrt{2N}$ which determine the size of the error bars in our figures. Typically samples of 200 microscopically different MOSFET's are simulated for each combination of macroscopic device parameters such as  $L_{\text{eff}}$ ,  $W_{\text{eff}}$ ,  $N_A$ , and  $t_{ox}$ . For such samples the value of  $\sigma_{\sigma}$  is, for example, 5% of  $\sigma V_T^p$ .

#### B. Channel Length

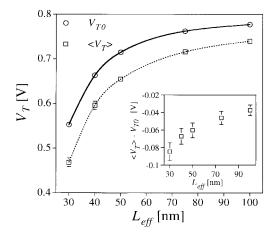

The "atomistically" simulated average threshold voltage  $\langle V_T \rangle$  for a set of MOSFET's with different channel lengths is compared in Fig. 2 to the threshold voltage  $V_{T0}$  of devices with continuous doping. In the same picture, as an insert, the difference between  $V_{T0}$  and  $\langle V_T \rangle$  is also shown. As pointed out in [21] the "atomistic" simulations predict lowering in the

threshold voltage compared to continuous doping simulations. The lowering increases rapidly below a 50-nm effective channel length and reaches almost 0.1 V in a 30-nm MOSFET. This threshold voltage lowering will partially compensate the increase in the threshold voltage associated with quantum mechanical effects [25] in short, heavily doped MOSFET's, not taken into account in our simulations. No analytical models predicting the random dopant related threshold voltage lowering are available at present. From Fig. 2, it is clear that the threshold voltage roll-off for doping concentration  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup> starts at 50 nm, even at a low drain voltage. The random dopant related threshold voltage to this short channel effect.

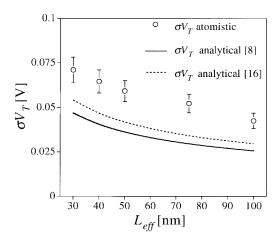

The standard deviation in the threshold voltage  $\sigma V_T$  obtained from our "atomistic" simulations is compared in Fig. 3 to the simple analytical models proposed in [8] and [16]. The expression for  $\sigma V_T$  in [8] can be presented in the following form:

$$\sigma V_T = \frac{q t_{ox}}{\varepsilon_{ox}} \sqrt{\frac{N_A W_d}{4 L_{\text{eff}} W_{\text{eff}}}}$$

(2)

where  $\varepsilon_{ox}$  is the permittivity of the gate oxide and  $W_d$  is the width of the depletion layer under the gate. For uniform doping under the gate the analytical model in [16] introduces

Fig. 2. Comparison of "atomistically" simulated average threshold voltage  $\langle V_T \rangle$  and the threshold voltage  $V_{T0}$  of devices with continuous doping for a set of MOSFET's with different channel length.  $W_{\rm eff}$  = 50 nm,  $N_A$  = 5 × 10<sup>18</sup> cm<sup>-3</sup>, and  $t_{ox}$  = 3 nm. Samples of 200 transistors.

Fig. 3. Comparison of the standard deviation in the threshold voltage  $\sigma V_T$  obtained from "atomistic" simulations and the analytical models proposed in [8] and [16] for a set of MOSFET's with different channel length.  $W_{\rm eff} = 50 \text{ nm}, N_A = 5 \times 10^{18} \text{ cm}^{-3}$ , and  $t_{ox} = 3 \text{ nm}$ . Samples of 200 transistors.

a correction factor of  $2/\sqrt{3}$  to (2). The atomistically calculated standard deviation follows the  $1/\sqrt{L_{\text{eff}}}$  dependence predicted by the analytical models, but its magnitude is larger. The disagreement is possibly due to the fact that the analytical models take into account only the fluctuations in the total charge controlled by the gate, resulting from the dopant number fluctuations in the depletion layer, but do not incorporate effects associated with the random microscopic arrangements of the individual dopants. The disagreement increases at shorter channel length but we do not observe a strong need for the short channel corrections proposed in [9].

## B. Channel Width

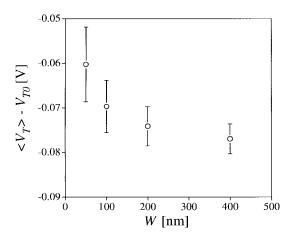

The conventional channel width effects are excluded from our simulations by using symmetry boundary conditions in the channel width direction. Thus, the threshold voltage  $V_{T0}$ calculated for device with  $L_{\text{eff}} = 50$  nm and continuous doping distribution  $N_A = 5 \times 10^{18} \text{ cm}^{-3}$  is independent of the width of the simulation domain  $W_{\text{eff}}$  and equal to 0.714 V. Fig. 4

Fig. 4. Difference between the atomistically calculated average threshold voltage  $\langle V_T \rangle$  and the continuous doping threshold voltage  $V_{T0}$  as a function of the channel width.  $L_{\rm eff} = 50$  nm,  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup>, and  $t_{ox} = 3$  nm. Samples of 200 transistors.

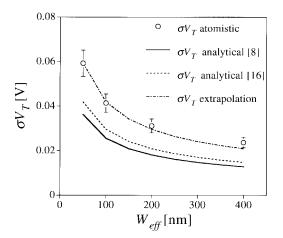

Fig. 5. Comparison between atomistically calculated standard deviation  $\sigma V_T$  as a function of the channel width and the analytical models in [8] and [16].  $L_{\rm eff} = 50$  nm,  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup>, and  $t_{ox} = 3$  nm. Samples of 200 transistors.

illustrates the difference between the atomistically calculated average threshold voltage  $\langle V_T \rangle$  and  $V_{T0}$  for transistors with different channel widths. Note that for the simulation of the MOSFET with  $W_{\text{eff}} = 0.4 \ \mu\text{m}$  in this figure a 70 × 50 × 400 node grid was used, involving the solution of a system of 1 400 000 equations. We observe a steady increase in the random dopant induced threshold voltage lowering with the increase of  $W_{\text{eff}}$ .

The dependence of the atomistically calculated standard deviation  $\sigma V_T$  as a function of the channel width is compared in Fig. 5 with the analytical models from [8] and [16]. Similarly to the channel length dependence, the analytical models describe qualitatively well the trends in the channel width dependence, but fail to predict quantitatively the magnitudes of the threshold voltage fluctuations. An extrapolation of  $\sigma V_T$ , based only on the atomistic results for a MOSFET with  $W_{\text{eff}} = 50$  nm and assuming  $1/\sqrt{W_{\text{eff}}}$  dependence is also plotted in the same figure. The extrapolation slightly departs from the atomistic results for the widest simulated device, but in

Fig. 6. Comparison of the doping concentration dependencies of  $\langle V_T \rangle$  and  $V_{T0}$  for transistors with  $L_{\rm eff} = W_{\rm eff} = 50$  nm and  $t_{ox} = 3$  nm. Samples of 200 transistors.

Fig. 7. Comparison between the atomistically calculated doping concentration dependence of  $\sigma V_T$  and the analytical models in [8] and [16].  $L_{\rm eff} = W_{\rm eff} = 50$  nm and  $t_{ox} = 3$  nm. Samples of 200 transistors.

general the agreement is good. This suggests that atomistic simulations of relatively narrow devices can be used to predict the matching properties of transistors with a larger  $W_{\rm eff}/L_{\rm eff}$  ratio.

#### C. Doping Concentration

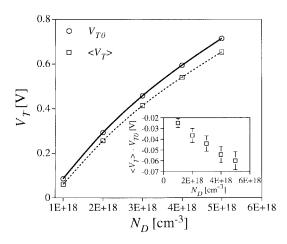

In Fig. 6 the doping concentration dependences of  $\langle V_T \rangle$  and  $V_{T0}$  are compared for transistors with  $L_{\text{eff}} = W_{\text{eff}} = 50$  nm and  $t_{ox} = 3$  nm. The insert in the same figure shows that the random dopant induced threshold voltage lowering increases almost linearly with the increase in the doping concentration.

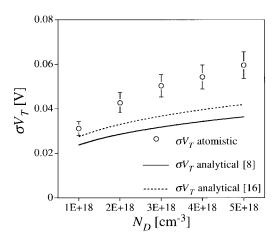

In Fig. 7 the atomistically calculated doping concentration dependence of  $\sigma V_T$  is compared with the analytical models in [8] and [16]. At a low doping concentration,  $N_A = 1 \times 10^{18}$  cm<sup>-3</sup>, the discrepancy between the atomistic results and the analytical model in [16] is less than 10% but increases rapidly with the increase of the doping concentration. Obviously the doping concentration dependence of  $\sigma V_T$  is stronger than the  $N_A^{1/4}$  dependence adopted in the examined analytical models.

TABLE I

COMPARISON BETWEEN "ATOMISTIC" RESULT IN THIS WORK AND IN [20]

|                  | Leff | Weff | t <sub>ox</sub> | N <sub>A</sub>       | $\langle V_{T} \rangle$ - $V_{T0}$ | σ⇔   | $\sigma V_{\tau}$ | $\sigma_{\sigma}$ |

|------------------|------|------|-----------------|----------------------|------------------------------------|------|-------------------|-------------------|

|                  | [nm] | [nm] | [nm]            | [cm-3]               | [mV]                               | [mV] | [mV]              | [mV]              |

| Wong et al. [20] | 50   | 50   | 3               | 8.6x10 <sup>17</sup> | 32                                 | 5.9  | 29                | 4.2               |

| This work        | 50   | 50   | 3               | 1x10 <sup>18</sup>   | 26                                 | 2.3  | 32                | 1.6               |

Fig. 8. Dependence of  $\langle V_T \rangle$  and  $V_{T0}$  on the oxide thickness for a MOSFET with  $L_{\rm eff} = W_{\rm eff} = 50$  nm, and  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup>. Samples of 200 transistors.

Our results for a MOSFET with  $L_{\text{eff}} = W_{\text{eff}} = 50$  nm,  $t_{ox} = 3$  nm and doping concentration  $N_A = 1 \times 10^{18}$  cm<sup>-3</sup> are in a good agreement with the results published in [21] for a similar device, bearing in mind the statistical uncertainty associated with the size of the samples used in both investigations. A detailed comparison is given in Table I.

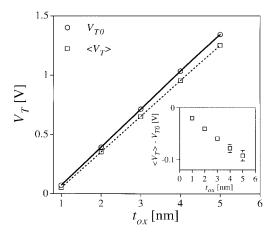

## D. Oxide Thickness

Taking into account the encouraging results reported in [26], the investigation of the effect of the oxide thickness on the threshold voltage fluctuations is extended down to tunneling oxide thicknesses. The dependencies of  $\langle V_T \rangle$  and  $V_{T0}$  as a function of the oxide thickness for MOSFET's with  $L_{\rm eff} = W_{\rm eff} = 50$  nm, and doping concentration  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup> are shown in Fig. 8. As expected the dependence is linear but the slope of  $\langle V_T \rangle$  is smaller than the slope of  $V_{T0}$  giving rise to an almost linear increase in the random dopant induced threshold voltage lowering with the increase in the oxide thickness (see the insert in Fig. 8).

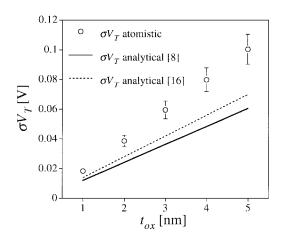

The atomistically calculated oxide thickness dependence of  $\sigma V_T$  is compared with the prediction of the analytical models from [8] and [16] in Fig. 9. Both the atomistic and the analytical results show a linear increase of  $\sigma V_T$  with the oxide thickness. However, the slope of the atomistic results is almost 1.5× higher than the prediction of the analytical model in [16].

#### IV. ANALYSIS

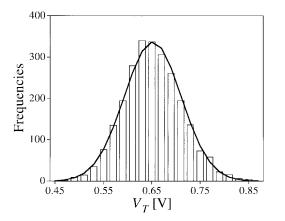

To test the hypothesis that the random dopant induced threshold voltage fluctuations follow a normal distribution we

Fig. 9. Comparison of the atomistically calculated oxide thickness dependence of  $\sigma V_T$  with the analytical models in [8] and [16].  $L_{\rm eff} = W_{\rm eff} = 50$  nm and  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup>. Samples of 200 transistors.

Fig. 10. Threshold voltage frequency distribution and the corresponding normal distribution for a random sample of 2500 microscopically different transistors with  $L_{\rm eff} = W_{\rm eff} = 50$  nm,  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup> and  $t_{ox} = 3$  nm.

TABLE II FIRST FOUR MOMENTS OF THE  $V_T\,$  Distribution from Fig. 10

| $\langle V_{\tau} \rangle$ [V] | 0.652 |

|--------------------------------|-------|

| $\sigma V_T [mV]$              | 59.2  |

| Skew                           | 0.161 |

| Kurtosis                       | 0.049 |

use a sample of 2500 microscopically different transistors with  $L_{\rm eff} = W_{\rm eff} = 50$  nm,  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup>, and  $t_{ox} = 3$  nm. The threshold voltage frequency distribution and the corresponding normal distribution are compared in Fig. 10. The goodness of fit for the data is excellent with  $\chi^2$  probability  $p(X > \chi^2) = 0.21$ . There is, however, a visual indication that the threshold voltage distribution is slightly positively skewed. This is confirmed by the calculated Pearson second coefficient of skewness which has a value of 0.13 for the above data. The first four moments of the threshold voltage distribution from Fig. 10 are summarized in Table II.

The analytical models, used for comparison with our atomistic results in the previous section, are based on the common

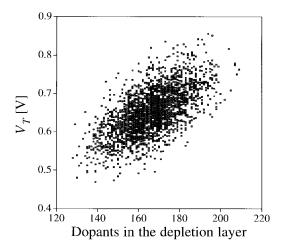

Fig. 11. Threshold voltages in a sample of 2500 microscopically different transistors as a function of the number of dopants in the depletion layer.  $L_{\rm eff} = W_{\rm eff} = 50$  nm,  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup> and  $t_{ox} = 3$  nm.

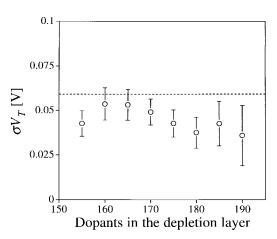

Fig. 12. Standard deviations of the threshold voltage  $\sigma V_T$  extracted from different subsamples, with constant number of dopants in the depletion region in each subsample.

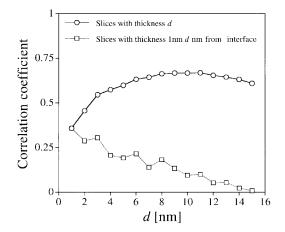

Fig. 13. Correlation coefficient between  $\sigma V_T$  and the number of dopants at different positions below the Si/SiO<sub>2</sub> interface.

understanding of the threshold voltage fluctuations in terms of fluctuations of the number of dopants in the depletion region. However, in all comparisons the atomistic simulations predict higher level of fluctuations than the analytical models. In order to understand this discrepancy we investigated the correlation between the threshold voltage and the number of dopants in the depletion layer for the above sample of 2500 MOSFET's. The numbers of dopants used for this correlation are counted in a layer with thickness corresponding to the maximum depletion layer width of a continuously doped sample at threshold. For a doping concentration  $N_A = 5 \times 10^{18}$  cm<sup>-3</sup> the maximum depletion layer width is 13.6 nm and the average number of dopants in the channel depletion layer of a 50  $\times$  50 nm transistor is 170. Fig. 11 displays the dependence between the threshold voltage and the number of dopants in the depletion layer for all 2500 transistor in the sample. It is clear that even for transistors with equal numbers of dopants in the depletion layer there is still a strong variation in the threshold voltage which has to be attributed to the microscopic arrangements of the dopants within the depletion layer.

The 2500 transistors of the whole sample are further grouped in subsamples with a constant number of dopants in the depletion region for each subsample. Standard deviations of the threshold voltage  $\sigma V_T$  extracted from several such subsamples are shown in Fig. 12. The standard deviations in these subsamples are lower but rather close to the standard deviation of the whole sample. This means that the random arrangement of a constant number of dopants in the depletion layer can be responsible for a significant portion of the threshold voltage fluctuations.

However, the described correlation between the threshold voltage and the number of dopants in the depletion layer is to some extent ambiguous because both the dopant number and position fluctuations themselves introduce fluctuations and nonuniformity in the channel depletion width. The solid line in Fig. 13 represent the correlation coefficient between the threshold voltage and the number of dopants in a layer with thickness d, measured from the Si/SiO<sub>2</sub> interface, as a function of this thickness. The correlation coefficient increases until the layer thickness reaches 10 nm and then falls. The maximum value of the correlation coefficient does not exceed 0.67 which confirms the conclusions that not only the numbers but also the arrangement of the dopants in the depletion layer has a significant contribution to the threshold fluctuations. Clearly all of the dopants in the depletion layer contribute to the increase of the correlation coefficient with d. It may be argued that the average depletion layer width is related to the maximum of the correlation coefficient. This in turn leads to the conclusion that the average depletion layer in the atomistic devices is somewhat narrower than the 13.6 nm estimated from a continuous doping distribution. The dashed line in Fig. 13 represent the dependence of the correlation coefficient between the threshold voltage and the number of dopants in a layer with thickness 1 nm, as a function of the distance of this layer from the Si/SiO<sub>2</sub> interface. Clearly the dopant which are closer to the interface have a larger influence on the threshold voltage fluctuations.

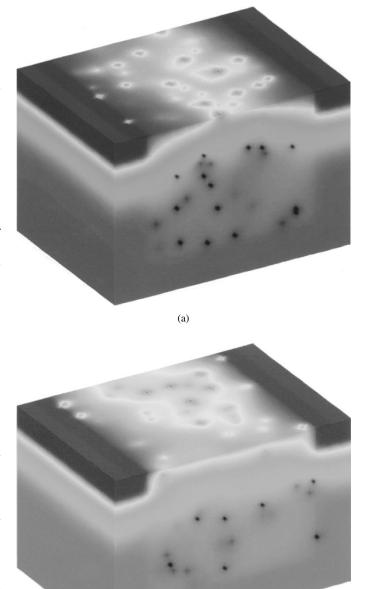

How the individual distribution of dopants affects the threshold voltage becomes clearer from Fig. 14(a) and (b) where the potential distributions at the Si/SiO<sub>2</sub> interface of two microscopically different MOSFET's are compared. The two devices have the same number of 170 dopants in the

Fig. 14. Potential distributions at the  $Si/SiO_2$  interface of two microscopically different MOSFET's both with 170 dopant atoms in the channel depletion region. (a) MOSFET with threshold voltage 0.78 V and (b) MOSFET with threshold voltage 0.56 V.

(b)

channel depletion region but the transistor from Fig. 14(a) has a threshold voltage of 0.78 V, while the transistor from Fig. 14(b) has a threshold voltage of 0.56 V. In the device from Fig. 14(a), six to seven dopants in the middle of the channel, almost equally spaced along the channel width, block the current path and are responsible for the high threshold voltage. In the device in Fig. 14(b) there is a "lucky" channel on the right side with virtually no dopants at the surface and a low local threshold voltage. The probability for distributions which result in direct channels like the one in Fig. 14(b) increases with the increase in the channel width resulting in the increase

of the threshold voltage lowering with  $W_{\text{eff}}$  observed in Fig. 4.

The overall reduction in the threshold voltage is associated with the inhomogeneous potential distribution, allowing for an early turn on in parts of the channel. This inhomogeneity, according to the percolation theory, leads to a higher current than the current corresponding to the mean value of the potential. In longer devices the fluctuations in the potential associated with fluctuations in the mean doping density dominate this effect. In shorter devices the potential fluctuations associated with the individual dopant atoms, as seen in Fig. 14, become comparable to the channel length and start to insert their strong influence on the threshold voltage lowering as shown in Fig. 2.

### V. CONCLUSION

This paper reported a 3-D "atomistic" simulation study of random dopant induced threshold voltage lowering and fluctuations in sub-0.1  $\mu$ m MOSFET's. The study was centered around devices with a 50-nm channel length, representing the level of the technology at the end of the silicon roadmap. For the first time a systematic analysis of random dopant effects down to an individual dopant level was carried out in 3-D on a scale sufficient to provide quantitative statistical predictions. This became possible due to the efficient algorithm used to calculate the threshold voltage at low drain voltage.

The effects of the channel length and width, oxide thickness, and doping concentration on the random dopant induced threshold voltage lowering and fluctuations are studied using typical samples of 200 microscopically different MOSFET's. Both the threshold voltage lowering and the fluctuations increase with the increase in the doping level and the oxide thickness, and with the decrease in the channel length. The threshold voltage fluctuations also decrease with the increase of the channel width. In the same time we observe an increase in the threshold voltage lowering with the increase in the channel width.

The atomistic results for the threshold voltage fluctuations were compared with two analytical models based on dopant number fluctuations. Although the analytical models predict the general trends in the threshold voltage fluctuations associated with the variations of the basic device design parameters, they fail to predict quantitatively the magnitude of the fluctuations. The discrepancy increases with the increase of the doping level. The model presented in [16] was found to produce results closer to the atomistic results than the model from [8].

The atomistically calculated threshold voltage for a sample of 2500 MOSFET's has close to a normal distribution with a slightly pronounced positive skewnes. The correlation between the number of dopants in the gate depletion region and the threshold voltage for the same sample does not exceed 0.67 clearly showing that not only the number of dopants but also their individual arrangement has a significant contribution to the threshold voltage fluctuations. In sub-0.1  $\mu$ m transistors the characteristic range of the potential fluctuations associated with individual dopants near the Si/SiO<sub>2</sub> interface become comparable to the channel length and enhances the threshold voltage lowering.

### ACKNOWLEDGMENT

The author would like to thank Dr. S. Saini, NASA Ames Research Center, for his encouragement and helpful discussions.

#### REFERENCES

- The National Technology Road-Map for Semiconductors, Semiconductor Industry Association, San Jose, CA, 1997 revision.

- [2] H. Kawaura, T. Sakamoto, T. Baba, Y. Ochiai, J. Fujita, S. Matsui, and J. Sone, "Transistor operation of 30-nm gate-length EJ-MOSFET's," *IEEE Electron Device Lett.*, vol. 19, pp. 74–76, 1998.

- [3] M. Ono, M. Saito, T. Yoshimi, C. Fiegna, T. Ohguro, and H. Ivai, "A 40 nm gate length n-MOSFET," *IEEE Trans. Electron Devices*, vol. 42, pp. 1822–1830, 1995.

- [4] A. Hori, H. Nakaoka, H. Umimoto, K. Yamashita, M. Tkese, N. Shimuitsu, B. Mizuno, and S. Odanka, "A 0.05 μm CMOS with ultra shallow source/drain junctions fabricated by 5 keV ion implantation and rapid thermal annealing," in *IEDM Tech. Dig.*, 1994, pp. 485–488.

- [5] B. Hoeneisen and C. A. Mad, "Fundamental limitations in microelectronics—I, MOS technology," *Solid-State Electron.*, vol. 15, pp. 819–829, 1972.

- [6] R. W. Keys, "Physical limits in digital electronics," Proc. IEEE, vol. 63, pp. 740–766, 1975.

- [7] T. Hagivaga, K. Yamaguchi, and S. Asai, "Threshold voltage variation in very small MOS transistors due to local dopant fluctuations," in *Proc. Symp. VLSI Technol., Dig. Tech. Papers*, 1982, pp. 46–47.

- [8] K. R. Lakshmikumar, R. A. Hadaway, and M. A. Copeland, "Characterization and modeling of mismatch in MOS transistors for precision analogue design," *IEEE J. Solid State Circuits*, vol. SC-21, pp. 1057–1066, 1986.

- [9] M. Steyaert, J. Bastos, R. Roovers, P. Kinget, W. Sansen, B. Graindourse, A. Pergot, and Er. Janssens, "Threshold voltage mismatch in short-channel MOS transistors," *Electron. Lett.*, vol. 30, pp. 1546–1548, 1994.

- [10] T. Mizuno, J. Okamura, and A. Toriumi, "Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFET's," *IEEE Trans. Electron Devices*, vol. 41, pp. 2216–2221, 1994.

- [11] T. Mizuno, M. Iwase, H. Niiyama, T. Shibata, K. Fujisaki, T. Nakasugi, A. Toriumi, and U. Ushiku, "Performance fluctuations 0.1 μm MOS-FET's—Limitation of 0.1 μm ULSI's," in *Proc. VLSI Symp.*, 1994, pp. 13–14.

- [12] O. R. dit Buisson and G. Morin, "MOSFET matching in deep submicron technology," in *Proc. ESSDERC*, 1996, pp. 731–734.

- [13] M. Eisele, I. Berthold, R. Thewes, F. Wohlrab, D. Schmitt-Landsidel, and W. Weber, in *IEDM Tech. Dig.*, 1995, pp. 67–70.

- [14] J. T. Horstmann, U. Hilleringmann, and K. F. Goser, "Matching analysis of deposition defined 50-nm MOSFET's," *IEEE Trans. Electron Devices*, vol. 45, pp. 299–306, 1997.

- [15] T. Mikolajick and H. Ryssel, "Influence of statistical dopant fluctuations on MOS transistors with deep submicron channels," *Microelectron. Eng.*, vol. 21, pp. 419–433, 1993.

- [16] K. Takeuchi, T. Tatsumi, and A. Furukawa, "Channel engineering for the reduction of random-dopant-placement-induced threshold voltage fluctuations," in *IEDM Tech. Dig.*, 1996

- [17] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S. H. Lo, A. A. Sai-Hakasz, R. G. Viswanathan, H. J. C. Wann, S. J. Wind, and H. S. Wong, "CMOS scaling into the nanometer regime," *Proc. IEEE*, vol. 85, pp. 486–504, 1997.

- [18] K. Nishiohara, N. Shiguo, and T. Wada, "Effects of mesoscopic fluctuations in dopant distributions on MOSFET threshold voltage," *IEEE Trans. Electron Devices*, vol. 39, pp. 634–639, 1992.

- [19] P. A. Stolk and D. B. M. Klaasen, "The effect of statistical dopant fluctuations on MOS device performance," in *IEDM Tech. Dig.*, 1996.

- [20] P. A. Stolk, F. P. Widdershoven, and D. B. M. Klaassen, "Device modeling of statistical dopant fluctuations in MOS transistors," in *Proc. SISPAD*'97, 1997, pp. 153–156.

- [21] H. S. Wong and Y. Taur, "Three dimensional 'atomistic' simulation of discrete random dopant distribution effects in sub-0.1 mm MOSFET's," in *IEDM Tech. Dig.*, 1993, pp. 705–708.

- [22] J. R. Zhou and D. K. Ferry, "Three-dimensional simulation of the effect of random dopant distribution on conductance for deep submicron devices," in 1994 Proceedings of the Third International Workshop

on Computational Electronics. New York: Plenum Press, 1994, pp. 74–77.

- [23] C. R. Arokianathan, J. H. Davies, and A. Asenov, "Ab-initio Coulomb scattering in atomistic device simulation," *VLSI Design*, to be published.

- [24] D. L. Scharfetter and H. K. Gummel, "Large-signal analysis of silicon read diode oscillator," *IEEE Trans. Electron Devices*, vol. ED-16, pp. 64–77, 1969.

- [25] G. Chindalore, S. A. Hareland, S. Jallepalli, A. F. Tasch, C. M. Maziar, V. K. F. China, and S. Smit, "Experimental determination of threshold voltage shifts due to quantum mechanical effects in MOS electron and hole inversion layers," *IEEE Trans. Electron Devices*, vol. 206, pp. 206–208, 1987.

- [26] H. S. Momose, S. Nakamura, T. Ohguro, T. Yoshitomi, E. Morifuji, T. Morimoto, Y. Katsumata, and H. Ivai, "Study of the manufacturing feasibility of 1.5-nm direct-tunnelling gate oxide MOSFET's: Uniformity, reliability, and dopant penetration of the gate oxide," *IEEE Trans. Electron Devices*, vol. 45, pp. 691–700, 1998.

Asen Asenov had ten years industrial experience as a Head of the Process and Device Modeling Group in IME-Sofia, Bulgaria, developing one of the first integrated process and device CMOS simulators IMPEDANCE. From 1989 to 1991, he was a Visiting Professor at the Physics Department, Technical University of Munich, Munich, Germany. He is currently a Reader in the Department of Electronics and Electrical Engineering, Glasgow University, Glasgow, U.K. As a Leader of the Device Modeling Group and Academic Director

of the Process and Device Simulation Centre, University of Glasgow, he coordinates the development of 2-D and 3-D device simulators and their application in the design of FET's, SiGe MOSFET's, and IGBT's. He has more than 110 publications in process and device modeling and simulation, semiconductor device physics, "atomistic" effects in ultra small devices, and parallel computing.