# SCIENTIFIC REPORTS

Received: 12 July 2017 Accepted: 13 December 2017 Published online: 10 January 2018

## **OPEN** Random telegraph noise from resonant tunnelling at low temperatures

Zuo Li<sup>1</sup>, Moïse Sotto<sup>1</sup>, Fayong Liu<sup>1</sup>, Muhammad Khaled Husain<sup>1</sup>, Hiroyuki Yoshimoto<sup>2</sup>, Yoshitaka Sasago<sup>2</sup>, Digh Hisamoto<sup>2</sup>, Isao Tomita<sup>1</sup>, Yoshishige Tsuchiya<sup>1</sup> & Shinichi Saito<sup>1</sup>

The Random Telegraph Noise (RTN) in an advanced Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) is considered to be triggered by just one electron or one hole, and its importance is recognised upon the aggressive scaling. However, the detailed nature of the charge trap remains to be investigated due to the difficulty to find out the exact device, which shows the RTN feature over statistical variations. Here, we show the RTN can be observed from virtually all devices at low temperatures, and provide a methodology to enable a systematic way to identify the bias conditions to observe the RTN. We found that the RTN was observed at the verge of the Coulomb blockade in the stability diagram of a parasitic Single-Hole-Transistor (SHT), and we have successfully identified the locations of the charge traps by measuring the bias dependence of the RTN.

Charge traps in advanced Silicon (Si) Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) have been used for many important applications<sup>1</sup> in semiconductor industries. For example, a Metal-Oxide-Nitride-Oxide-Semiconductor (MONOS) memory device<sup>2,3</sup> has an advantage on a long retention time at high temperatures, which is suitable for an integrated microprocessor in a vehicle. An interface trap is also useful to extend the current plateau in a single electron pump<sup>4</sup> at low temperatures, which is a promising candidate for a redefinition of ampere to establish a new current standard based on an elementary charge in quantum metrology. On the other hand, charge traps also affect reliability problems<sup>5,6</sup>, such as Random Telegraph Noise (RTN)<sup>7-11</sup> and Negative Bias Temperature Instabilities (NBTI)<sup>12</sup>, causing failures of Static Random Access Memory (SRAM) cells and degradations of long term performance<sup>13,14</sup>. In particular, the impact of RTN is getting more important with the scaling<sup>15-17</sup>, since the variations<sup>18-20</sup> in an atomic level can affect the drain current in sub-20 nm MOSFETs.

RTN is coming from the carrier trapping and de-trapping processes through charge traps at the gate insulator/Si interface, which are intrinsic quantum processes<sup>21,22</sup>. Quantum effects are not negligible in advanced MOSFETs, since the gate insulator is as thin as 1 nm<sup>23</sup>, and the direct tunnelling currents from the channel into the traps are expected due to enhanced coupling<sup>24</sup>. Previously, the most of the works on RTN were based on measurements at room temperatures<sup>7-11,25,26</sup>. At room temperatures, the thermal fluctuation significantly affect the carrier dynamics<sup>27</sup>, and it was difficult to identify the quantum energy levels of charge traps. By measuring the MOSFETs at low temperatures, it is easier to observe various quantum effects<sup>28</sup>.

In our previous study, we have found current peaks at low temperatures in advanced Si MOSFETs<sup>29</sup>, but the mechanism of the peaks was not elucidated. In this paper, we characterised the peaks in time domain, and found that the current peaks are related to RTN. The bias conditions to observe the current peaks have been clarified from the stability diagram of the associated with a parasitic Single-Hole-Transistor (SHT) at low temperatures. We also studied the bias dependence of RTN to identify the possible origin of charge traps.

### **Current Peaks in the Stability Diagram**

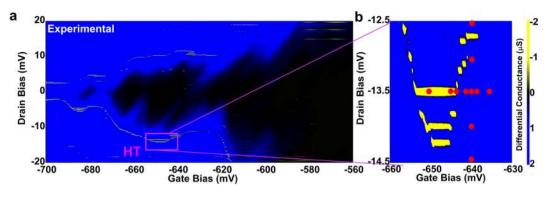

The device was measured at 2 K, and the fundamental characteristics are shown in the supplementary information. From the stability diagram, open diamonds were observed in the stability diagram of the device, as shown in Fig. 1(a), which implies that several quantum dots in series were responsible for  $I_d$  in the subthreshold regime. The quantum dots might be coming from the remote surface roughness coming from Poly-Si grains<sup>30,31</sup>. At the edge of Coulomb diamonds, we have observed current peaks in the stability diagram, which were previously

<sup>1</sup>Sustainable Electronics Technologies, Department of Electronics and Computer Science, Faculty of Physical Science and Engineering, University of Southampton, Southampton, UK.<sup>2</sup>Research and Development Group, Hitachi, Ltd., 1-280 Higashikoigakubo, Kokubunji, Tokyo, 185-8601, Japan. Correspondence and requests for materials should be addressed to S.S. (email: S.Saito@soton.ac.uk)

reported in our studies on MOSFETs at low temperatures<sup>29</sup>. The regime where current peaks can be observed formed a border at the edge of Coulomb diamonds. Particularly, the density of current peaks was much higher at some narrow bias conditions. We mark one of them as HT. The extended view of stability diagram in HT regime is shown in Fig. 1(b).

#### Quantum Probabilities of the Trap States

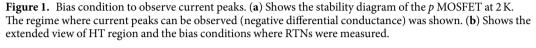

We measured the time domain characteristics of  $I_d$  at the bias conditions near the current peaks, and observed RTN. One example of the measurement results, which was measured at  $V_g$  of -640 mV and  $V_d$  of -13.5 mV, is shown in Fig. 2(a). Two types of RTN could be identified, which were named as RTN1 and RTN2, as shown in Fig. 2(a). RTN1 has larger amplitude and longer average switching time, while RTN2 has smaller amplitude and shorter average switching time. The long switching time and high amplitude imply that the trap corresponding to RTN1 is a deep oxide trap, while RTN2 might come from the shallow interface trap in the SiON/substrate interface. We could roughly estimate the amplitude of RTN1 by estimating the number of carriers inside the channel<sup>32–34</sup>,  $N_0 = k_B T C_{\text{gate}}/e^2 = k_B T \varepsilon_{ox} \varepsilon_0 WL/t_{eq} e^2 = 11.6$ , where  $k_B$  is Boltzmann constant, e is the value of elementary charge,  $\varepsilon_{ox}$  is the dielectric constant of SiO<sub>2</sub>,  $\varepsilon_0$  is the permittivity in vacuum, W is the width of the channel, L is the length of the channel and  $t_{eq}$  is the capacitive equivalent thickness of SiON layer<sup>35–37</sup>. Then the relative amplitude of RTN1 can be estimated as  $\Delta I/I = 1/N_0 = 8.6\%$ , which was roughly in agreement with the experimental data.

In order to study the statistics of  $I_d$ , we analysed the frequency with which we observed  $I_d$  at certain ranges, with the minimum step of 4pA, which was determined by the systematic noise of the system in a bandwidth of 5 Hz, as shown in Fig. 2(b). This is the quantum mechanical probability finding the system under a certain current state,  $P(I_d)$ , which reveals the information about the wave function of the traps,  $\psi(I_d)$ , as

$$P(I_{\rm d}) = |\psi(I_{\rm d})|^2. \tag{1}$$

At higher temperatures, RTN1 could not be observed, which is shown in the supplementary data. This is because the number of carriers significantly increased at higher temperatures<sup>38,39</sup>. As a result, the relative amplitude of RTN dropped, and will be hidden in the 1/f noise.

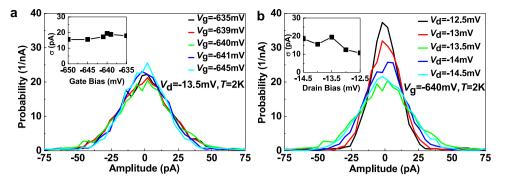

In order to study the bias dependence of RTN1 and RTN2, the time domain characteristics of  $I_d$  were measured at the bias conditions marked as red points in Fig. 1(c). The dependence of the time domain characteristics on  $V_g$  is shown in Fig. 2(c). The corresponding  $P(I_d)$  at different bias conditions is shown in Fig. 2(d). RTN1 was only observed in a narrow window of  $V_g$ , between -635 mV and -650 mV. We observed that the current was more likely to be in the high current state if we increased  $|V_g|$ . This showed the charge trap shifted from the unoccupied state to the occupied state as we changed  $V_g$ . It is also in agreement with the  $I_d - V_g$  characteristics near the HT regime as shown in supplementary data.

The  $V_d$  dependence on time domain characteristics is shown in Fig. 2(e), and the corresponding  $P(I_d)$  at different bias conditions is shown in Fig. 2(f). The high current state regarding RTN1 was only observed at a narrow window of  $V_d$ , between -13 mV and -13.5 mV. This narrow bias window, along with the fact that the current peaks were observed at the edges of the Coulomb diamonds, implies that the RTN1 has originated from resonant tunnelling<sup>40</sup>.

#### Nature of the trap

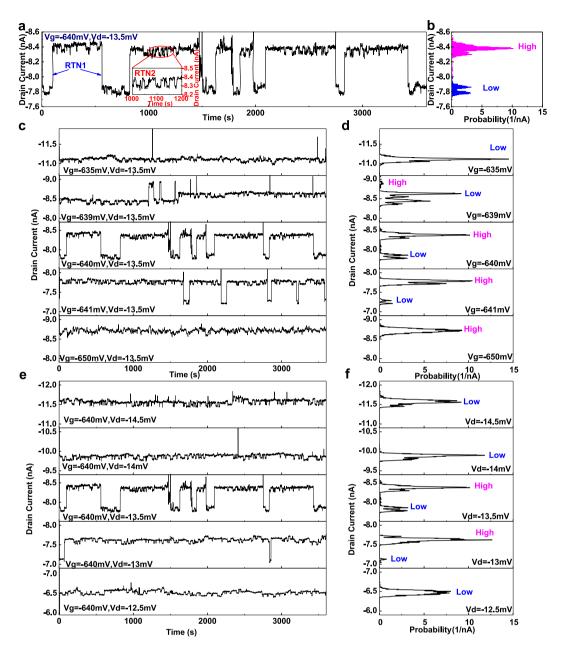

We will investigate on the probability of finding  $I_d$  at the high current State ( $P_h$ ) or the low current state ( $P_1$ ) shown in Fig. 2(b) to identify the nature of the charge trap. The way to extract  $P_h$  and  $P_1$  is shown in the method. The dependence of  $P_h$  and  $P_1$  on  $V_g$  and  $V_d$  are shown in Fig. 3(a) and (b), respectively.

From Fig. 3(a),  $I_d$  was more likely to be in the high current state if  $|V_g|$  was large, and a sharp transition of the preferred  $I_d$  state can be observed near  $V_g$  of -640 mV. This sharp transition showed that the occupancy of the trap, which is revealed from  $P_h$  and  $P_1$ , was modulated by  $V_g$ . This implies the charge trap corresponding to RTN1 is located in the SiON layer. The high current state was only observable at  $V_d$  of -13 mV and -13.5 mV

**Figure 2.** Time domain characteristics of  $I_d$ . (a) Shows the time domain characteristics of  $I_d$  measured at  $V_g$  of -640 mV and  $V_d$  of -13.5 mV. RTN1 and RTN2 are marked. (b) Shows the probability distribution of current versus its value. The state 'High' and 'Low' regarding RTN1 is marked. (c) Shows the dependence of RTN on  $V_g$  if  $V_d$  is biased at -13.5 mV, and (d) Shows the probability distribution of current accordingly. (e) Shows the dependence of RTN on  $V_d$  if  $V_g$  is biased at -640 mV, and (f) shows the probability distribution of current accordingly.

accroding to Fig. 3(b), which implies the presence of resonant tunnelling in the channel due to the narrow bias window of  $V_d$ . The  $V_g$  and  $V_d$  dependence of RTN1 amplitude were shown in Fig. 3(c) and (d), respectively. We can see that the amplitude of RTN1 almost has no dependence on both  $V_g$  and  $V_d$ . Since the dependence of  $I_d$  on  $V_g$  is non-linear, as shown in supplementary information, RTN1 is unlikely to have come from the impact of the shift of threshold voltage caused by carrier trapping/de-trapping. Otherwise, if the shift of threshold voltage was constant, the amplitude of RTN1 will have dependence on  $V_g$  and  $V_d$ , which was not what we observed in Fig. 3(c). We could use a similar method to investigate the characteristics of RTN2. The dependence of RTN2 on biases was complex, which implies RTN2 came from a shallow trap near SiON/substrate interface. The dependence of RTN2 on biases is shown in Supplementary information.

The position of the single hole is determined by the wavefunction of single hole in the charge trap. Different positions of the single hole in the charge trap show different impact on the  $I_d$ . Therefore, the wavefunction of the single hole in this charge trap resulted in an extra noise in  $I_d$ . In order to understand the wavefunction of the

**Figure 3.** The bias dependence of RTN1. (a) and (b) Shows the dependence of  $P_h$  and  $P_1$  on  $V_g$  and  $V_d$ , respectively. (c) and (d) Shows the dependence of RTN1 amplitude on  $V_g$  and  $V_d$ , respectively.

single hole as shown in Fig. 2(d) and (f), we must study its bias dependence. We will study the noise coming from wavefunction in order to understand its dependence on biases. The differential current,  $\Delta I_d$ , is defined as

$$\Delta I_{\rm d} = I_{\rm d}(t+1) - I_{\rm d}(t),\tag{2}$$

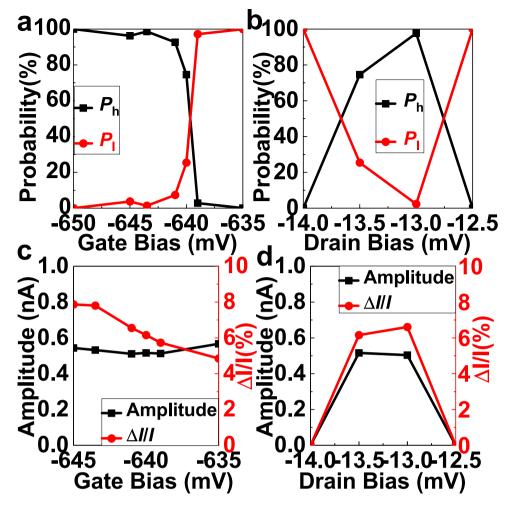

where t is time with the unit of second. The dependence of its probability distribution on  $V_{\rm g}$  and  $V_{\rm d}$  are shown in Fig. 4(a) and (b), respectively. The standard deviation of  $\Delta I_{\rm d}$  was extracted by fitting the distribution of  $\Delta I_{\rm d}$  with the Gaussian distribution function.

The probability distribution of  $\Delta I_d$  had very weak dependence on  $V_g$ , as shown in Fig. 4(a), while it showed more significant dependence on  $V_d$ , as shown in Fig. 4(b). Since the change of  $I_d$  is similar between Fig. 4(a) and (b), the fact that  $\Delta I_d$  shows more significant dependence on  $V_d$  implies that the coupling between the quantum dot and energy level created by charge trap was mainly modulated by  $V_d$ . We observe that the standard deviation of probability distribution showed a peak value if  $V_d$  was at -13.5 mV, as shown in Fig. 4(b). This reveals that the wavefunction of the single hole in the channel became the broadest at this bias condition, which implies that the strongest correlation between two energy levels in the channel at this bias condition. This is also in agreement with the assumption of resonant tunnelling. The resonant level is likely to have originated from the charge traps. The Johnson noise<sup>41,42</sup> of this system was calculated to be ~20 fA/ $\sqrt{Hz}$  and the background noise of the system was ~4pA in a bandwidth of 5 Hz, which were both much smaller than the noise coming from wavefunction.

#### **Two Traps RTN**

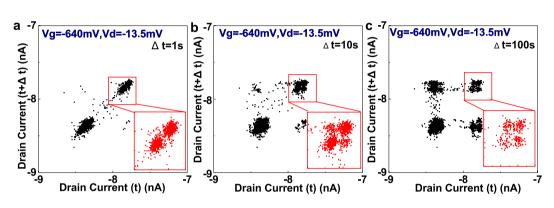

We could use lag plots<sup>43</sup> to study the correlation behaviour of  $I_d$  and the fractal nature of the two charge traps<sup>44</sup>. The lag plot of  $I_d$ , with the time lag,  $\Delta t$ , of 1 s, 10 s and 100 s, were shown in Fig. 5(a),(b) and (c) respectively.

When  $\Delta t$  was 1 s, we could observe strong correlation behaviour, as shown in Fig. 5(a). The fractal shape of the lag plot is diagonal, which reveals the strong positive autocorrelation behaviour of  $I_d$  in this time scale. When  $\Delta t$  was increased to 10 s, the shape of lag plot remained diagonal, but become rectangular within each small area, as shown in Fig. 5(b). This reveals the lost of  $I_d$  correlation behaviour regarding RTN2. When  $\Delta t$  was further

**Figure 4.** The dependence of experimental parameters on wavefunction broadening. (**a**) and (**b**) Shows the dependence of wave function broadening on  $V_{\rm g}$  and  $V_{\rm d}$ , respectively. The  $V_{\rm g}$  and  $V_{\rm d}$  dependence on standard deviation of the corresponding Gaussian wave function,  $\sigma$ , is shown in subfigures inside (**a**) and (**b**), respectively.

**Figure 5.** Fractal nature of the charge traps. The lag plot of  $I_d$  with different time lag shows fracture nature of charge traps. (**a**-**c**) Shows the correlation behaviour of  $I_d$  if time lag was 1 s, 10 s and 100 s, respectively.

increased to 100 s, the fractal shape of lag plot became rectangular in both large and small area, as shown in Fig. 5(c). This reveals that the correlation behaviour of  $I_d$  almost disappeared in this time scale.

#### Discussion

In the previous sections, we discussed about the characteristics of charge traps. Based on the experimental data, we found that the RTN1 is coming from the opening/closing of a resonant level in the device channel, and the carrier trapping/de-trapping process have originated from the tunnelling process between the Poly-Si gate and charge trap in the SiON layer. The lag plot clearly shows the correlation behaviour and fractal nature of the two charge traps. We also observed the crossover between RTN and 1/f noise, which was previously reported to be observed in magnetic nanodot system<sup>45</sup>, as shown in the Supplementary information.

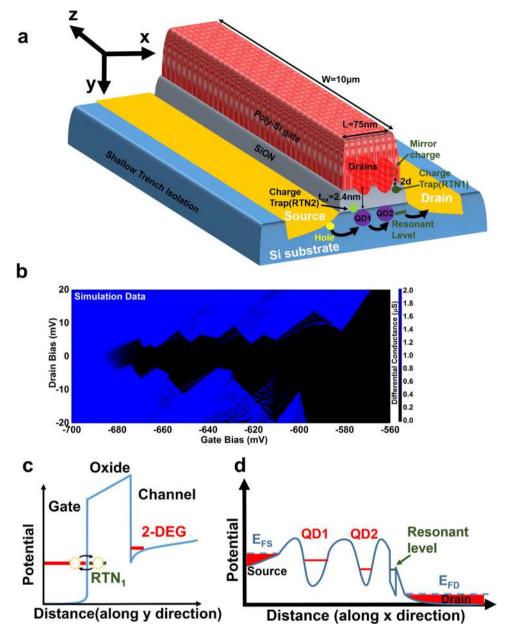

Based on the information shown above, we could establish a physical model to describe the RTN1, as shown in Fig. 6. A schematic 3-D diagram of the device and its physical model is shown in Fig. 6(a). Two quantum dots in series, marked as QD1 and QD2, were responsible for the drain current. The series quantum dots have presumably originated from the remote surface roughness caused by Poly-Si grains. We simulated the stability diagram of the series quantum dots system based on the master equations<sup>46,47</sup>, which is explained in detail in method part. The parameters are summarised in the supplementary information. The simulated stability diagram is shown in Fig. 6(b), which is roughly in agreement with the experimental data obtained in Fig. 1(a). The simulation result of stability diagram for individual QD1 and QD2 have been summarised in Supplementary information.

The trap corresponding to RTN1 is located in the SiON layer. Considering the  $V_g$  dependence, the charge trapping/de-trapping process has likely originated from the tunnelling of carriers between the poly-Si gate and the trap inside the SiON, as shown in Fig. 6(c). If  $|V_g|$  is decreased, the tunnelling barrier between the hole in the poly-Si gate and the energy level in the gate oxide becomes lower, and the trap was easier to be occupied. This corresponds to the trend observed in Fig. 3(a).

The different current states can be explained by the opening/closing of the resonant level<sup>48–50</sup> in the channel created by the charge trap. Due to the strong  $V_d$  dependence, the resonant level should be close to the drain reservoir. We address the resonant level to be located in the tunnelling barrier between QD2 and the drain reservoir. As a result, the resonant level is strongly coupled with QD2. Due to the relatively much larger distance between the resonant level and QD1, the coupling between the resonant level and QD1 is much weaker than the coupling between the resonant level and QD2, and therefore can be neglected.

**Figure 6.** The physical model for the RTN. (**a**) Shows the schematic physical model of the device. Series quantum dots are assumed to be responsible for the drain current, and the resonant level was formed by the trap 1, presumably a Boron ion. (**b**) Shows the simulated stability diagram based on the series quantum dots model. (**c**) Shows the schematic potential diagram across the oxide layer associated with the charge trapping and detrapping process. (**d**) Shows the schematic diagram of the potential across the channel.

A schematic diagram of the potential profile across the channel is shown in Fig. 6(d). If no single hole occupies the charge trap, it was not neutral. Since the Poly-Si gate behaves like a metal, the trap generates mirror charge in the Poly-Si gate. As a result, the trap and the corresponding mirror charge forms an electric dipole. The electric dipole therefore forms a potenetial well for the single hole in the channel. Under certain bias conditions, the energy level inside this potential well is aligned with the energy level in the QD2. Under that circumstance, resonant tunnelling is observed and the tunnelling barrier between QD2 and drain reservoir is made more transparent. As a result,  $I_d$  will increase, therefore we can observe the high current state. If the charge trap is occupied by a single hole, the charge trap will become neutral, and no resonant level will be found in the channel. Under this condition, the tunnelling barrier therefore becomes less transparent, and we can only observe the low current state. This model, which is based on resonant tunnelling, could explain the reason for the narrow  $V_g$  and  $V_d$  bias condition to observe RTN. Since the resonant level is in the channel, it is therefore more significantly modulated by  $V_d$ . Besides, the transmission coefficient and wavefunction were mainly influenced by the  $V_d$ , which explains the fact that the wavefunction was mainly affected by  $V_d$ , as shown in Fig. 4. We can estimate the position of charge trap based on the depth of the resonant energy level. From the simplicity point of view, since RTN1 is only observed in the HT regime at the edge of Coulomb diamond, the depth of the potential well,  $\Delta V$ , is assumed to be 13.5 mV. We could estimate the distance between trap and Poly-Si/SiON interface, d, from

$$e\Delta V = \frac{2e^2d}{4\pi\varepsilon_{\rm ox}\varepsilon_0 t_{\rm eff}^2}.$$

(3)

From Equation (3), we can roughly estimate d to be  $\sim$ 0.2 nm. This is on the same magnitude with the lattice constant of SiON. This estimation should be correct in magnitude, and is in agreement assuming that the charge trap is located on the top side of SiON. As a result, we think a charge trap located near the Poly-Si/SiON interface, which was presumbally a boron ion coming from the ion implantation process, is responsible for the resonant level in the channel.

In conclusion, we successfully demonstrate that we could identify the nature of the trap by measuring the RTN and investigating its bias dependence at low temperatures. We could estimate the position of the trap from the experimental data. Our research demonstrate a way to study the characteristics of charge trap systematically, and will pave the way for scientists to understand the detailed nature of the RTN.

#### Methods

**Sample and experiments.** The device we measured was a standard bulk-Si *p*-type MOSFET (*p* MOSFET), fabricated by a standard 65nm-node technology. The channel of the *p* MOSFET was 10  $\mu$ m wide and 75 nm long. Wide-channel devices were chosen to increase the chance to find charge traps. The gate was made of high-ly-doped poly-crystalline silicon (Poly-Si). The gate oxide was made of SiON, with the equivalent oxide thickness of 2.4 nm. The *p* MOSFET was wire-bonded with Aluminium wire onto a chip carrier. Then the *p* MOSFET was put into a cryostat, with the maximum capability to control temperatures down to 2 K. The *I*<sub>d</sub> was measured by a B1500A with high resolution current module. The value of current at each bias was obtained after averaging over 10<sup>5</sup> sampling taken with the duration of 2  $\mu$ s for each point. The background noise was less than 4pA, in a bandwidth of 5 Hz.

**Data analysation.** The probability to observe high current state and low current state in Figs 2 and 3 are determined by fitting the experimental data with Gaussian distribution functions. The amplitude of RTN is determined by the difference of the peaks. The probability of each state is determined by integrating the corresponding probability distribution function over the current. For example, if the probability distribution function corresponding to the high current state in Fig. 2 is  $p_h(I_d)$ , and the probability distribution function corresponding to the low current state in Fig. 2 is  $p_1(I_d)$ ,  $P_h$  and  $P_1$  are determined from

$$P_{\rm h} = \frac{\int_{-\infty}^{\infty} p_{\rm h}(I_{\rm d}) dI_{\rm d}}{\int_{-\infty}^{\infty} p_{\rm h}(I_{\rm d}) dI_{\rm d} + \int_{-\infty}^{\infty} p_{\rm l}(I_{\rm d}) dI_{\rm d}},\tag{4}$$

and

$$P_{l} = \frac{\int_{-\infty}^{\infty} p_{l}(I_{d}) dI_{d}}{\int_{-\infty}^{\infty} p_{h}(I_{d}) dI_{d} + \int_{-\infty}^{\infty} p_{l}(I_{d}) dI_{d}},$$

(5)

which correspond to the shaded areas (magenta and blue, respectively) in Fig. 2(b).

**Simulation of Quantum Dots.** In semiconductor quantum dots, the single particle energy spacing is comparable to the charging energy. Therefore, the Hamiltonian of the system does not simply depend on the charging energy, and the effect of single particle spacing must be considered. In order to simulate the quantum dots in a simple way, we used mesoscopic capacitor model, with different effective coupling capacitances in different hole states, as an approximation.

Assuming the gate capacitance, drain capacitance, and source capacitance when n holes occupy the quantum dots are  $C_{\rm g}(n)$ ,  $C_{\rm d}(n)$  and  $C_{\rm s}(n)$  respectively. Considering the circumstance when one less hole occupies the quantum dot, the change in free energy when a hole tunnels out through the electrode drain,  $\Delta F_{\rm d}^-(n)$ , or tunnels out through the electrode source,  $\Delta F_{\rm s}^+(n)$ , can be expressed as

$$\Delta F_{\rm d}^{-}(n) = F_{\rm d}(n-1) - F_{\rm d}(n) = -\frac{(n-1/2)e^2 - e[(C_{\rm s}(n) + C_{\rm g}(n))V_{\rm d} - C_{\rm g}(n)V_{\rm g}]}{C_{\Sigma}(n)},\tag{6}$$

and

$$\Delta F_{\rm s}^{+}(n) = F_{\rm s}(n-1) - F_{\rm s}(n) = \frac{(n-1/2)e^2 + e[C_{\rm d}(n)V_{\rm d} + C_{\rm g}(n)V_{\rm g}]}{C_{\Sigma}(n)}.$$

(7)

We could easily obtain the expression of  $\Delta F_d^+(n) = F_d(n+1) - F_d(n)$ , and  $\Delta F_s^-(n) = F_s(n+1) - F_s(n)$  from Eqs (6) and (7). Therefore, using Fermi's golden rule, the tunnelling rate through the drain and source can be expressed as

$$\Gamma_{\rm d}^{\pm}(n) = \frac{1}{R_d e^2} \left[ -\frac{\Delta F_{\rm d}^{\pm}(n)}{1 - \exp\left(\frac{\Delta F_{\rm d}^{\pm}(n)}{k_{\rm B}T}\right)} \right],\tag{8}$$

and

$$\Gamma_{s}^{\pm}(n) = \frac{1}{R_{s}e^{2}} \left[ -\frac{\Delta F_{s}^{\pm}(n)}{1 - \exp\left(\frac{\Delta F_{s}^{\pm}(n)}{k_{B}T}\right)} \right].$$

(9)

The master equation can be expressed as

$$\frac{\partial p(n,t)}{\partial t} = p(n+1)[\Gamma_s^+(n+1) + \Gamma_d^-(n+1)] - p(n)[\Gamma_s^-(n) + \Gamma_d^+(n)].$$

(10)

In the steady state, the probability is not assosiated with time, so

$$\frac{\partial p(n,t)}{\partial t} = 0. \tag{11}$$

The drain current is therefore expressed as

$$I = e \sum_{n = -\infty}^{n = \infty} p(n) [\Gamma_{s}^{+}(n) - \Gamma_{s}^{-}(n)].$$

(12)

We solve the equations listed above using extracted parameters to simulate the characteristics of drain current and differential conductance in series quantum dots system. The effect of inversion layer when  $V_{\rm g}$  is near the threshold voltage is considered in the simulation.

#### References

- King, Y.-C., King, T.-J. & Hu, C. Charge-trap memory device fabricated by oxidation of si/sub 1-x/ge/sub x. IEEE Trans. Electron Devices 48, 696–700 (2001).

- 2. Keshavan, B. & Lin, H. Monos memory element. In Electron Devices Meeting, 1968 International, 140-142 (IEEE, 1968).

- Minami, S.-I. & Kamigaki, Y. A novel monos nonvolatile memory device ensuring 10-year data retention after 10/sup 7/erase/write cycles. IEEE Trans. Electron Devices 40, 2011–2017 (1993).

- Yamahata, G., Nishiguchi, K. & Fujiwara, A. Gigahertz single-trap electron pumps in silicon. *Nature communications* 5, 5038 (2014).

Shi, Y., Saito, K., Ishikuro, H. & Hiramoto, T. Effects of traps on charge storage characteristics in metal-oxide-semiconductor

- memory structures based on silicon nanocrystals. J. Appl. Phys. 84, 2358–2360 (1998).

Grasser, T. Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities. Microelectronics Reliability 52, 39–70 (2012).

- 7. Machlup, S. Noise in semiconductors: spectrum of a two-parameter random signal. J. Appl. Phys. 25, 341-343 (1954).

- Uren, M. J., Day, D. J. & Kirton, M. J. 1/f and random telegraph noise in silicon metal-oxide-semiconductor field-effect transistors. Appl. Phys. Lett. 47, 1195–1197 (1985).

- Hung, K. K., Ko, P., Hu, C. & Cheng, Y. C. Random telegraph noise of deep-submicrometer mosfets. *IEEE Electron Device Lett.* 11, 90–92 (1990).

- Grasser, T. et al. Switching oxide traps as the missing link between negative bias temperature instability and random telegraph noise. In Electron Devices Meeting (IEDM), IEEE International, 1–4 (2009).

- Fukuda, K., Shimizu, Y., Amemiya, K., Kamoshida, M. & Hu, C. Random telegraph noise in flash memories-model and technology scaling. In *Electron Devices Meeting*, 2007. *IEDM IEEE International*, 169–172 (2007).

- 12. Schroder, D. K. & Babcock, J. A. Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing. J. Appl. Phys. 94, 1–18 (2003).

- Liang, M.-S., Chang, C., Yeow, Y. T., Hu, C. & Brodersen, R. Mosfet degradation due to stressing of thin oxide. *IEEE Trans. Electron Devices* 31, 1238–1244 (1984).

- 14. Heremans, P., Witters, J., Groeseneken, G. & Maes, H. E. Analysis of the charge pumping technique and its application for the evaluation of mosfet degradation. *IEEE Trans. Electron Devices* **36**, 1318–1335 (1989).

- Park, Y., Lee, J., Cho, S. S., Jin, G. & Jung, E. Scaling and reliability of nand flash devices. In *Reliability Physics Symposium*, IEEE International, 2E-1 (2014).

- 16. Ielmini, D. Reliability issues and modeling of flash and post-flash memory. Microelectron. Eng. 86, 1870-1875 (2009).

- Yang, H. et al. Reliability issues and models of sub-90nm nand flash memory cells. In Solid-State and Integrated Circuit Technology, ICSICT'06. 8th International Conference on, 760–762 (2006).

- 18. Meindl, J. D., Chen, Q. & Davis, J. A. Limits on silicon nanoelectronics for terascale integration. Science 293, 2044–2049 (2001).

- 19. Keyes, R. W. Fundamental limits of silicon technology. Proceedings of the IEEE 89, 227-239 (2001).

- Breuer, M. A., Gupta, S. K. & Mak, T. Defect and error tolerance in the presence of massive numbers of defects. *IEEE Des. Test. Comput.* 21, 216–227 (2004).

- 21. Griffiths, D. J. Introduction to quantum mechanics (Pearson Education India, 2005).

- 22. Jinyan, Z. Quantum mechanics. chin (1981).

- Chang, J., Register, L. F. & Banerjee, S. K. Topological insulator bi2se3 thin films as an alternative channel material in metal-oxidesemiconductor field-effect transistors. J. Appl. Phys. 112, 124511 (2012).

- Grasser, T., Reisinger, H., Wagner, P.-J. & Kaczer, B. Time-dependent defect spectroscopy for characterization of border traps in metal-oxide-semiconductor transistors. *Phys. Rev. B* 82, 245318 (2010).

- Asenov, A., Balasubramaniam, R., Brown, A. R. & Davies, J. H. Rts amplitudes in decananometer mosfets: 3-d simulation study. IEEE Trans. Electron Devices 50, 839–845 (2003).

- Kaczer, B., Roussel, P. J., Grasser, T. & Groeseneken, G. Statistics of multiple trapped charges in the gate oxide of deeply scaled mosfet devicesâ€"application to nbti. IEEE Electron Device Lett. 31, 411–413 (2010).

- 27. Landau, L. D., Lifshitz, E. M., Sykes, J. B., Bell, J. S. & Dill, E. Electrodynamics of continuous media (1961).

- Purwiyanti, S. et al. Dopant-induced random telegraph signal in nanoscale lateral silicon pn diodes at low temperatures. Appl. Phys. Lett. 103, 243102 (2013).

- 29. Li, Z. et al. Single carrier trapping and de-trapping in scaled silicon complementary metal-oxide-semiconductor field-effect transistors at low temperatures. Semicond. Sci. Technol. 32, 075001 (2017).

- Saito, S. et al. Effects of remote-surface-roughness scattering on carrier mobility in field-effect-transistors with ultrathin gate dielectrics. Appl. Phys. Lett. 84, 1395–1397 (2004).

- 31. Li, J. & Ma, T. P. Scattering of silicon inversion layer electrons by metal/oxide interface roughness. J. Appl. Phys. 62, 4212–4215 (1987).

- Vandamme, L. K. J., Sodini, D. & Gingl, Z. On the anomalous behavior of the relative amplitude of rts noise. Solid-State Electron. 42, 901–905 (1998).

- 33. Vandamme, L. K. J. & Macucci, M. 1/f and rts noise in submicron devices: Faster is noisier. In 4th International Conference on Unsolved Problems of Noise and Fluctuations in Physics, Biology and High Technology(UPoN 2005 in Gallipoli), 436–443 (AIP).

- Vandamme, E. P. & Vandamme, L. K. J. Critical discussion on unified 1/f noise models for mosfets. *IEEE Trans. Electron Devices* 47, 2146–2152 (2000).

- 35. Ando, T., Fowler, A. B. & Stern, F. Electronic properties of two-dimensional systems. Rev. Mod. Phys 54, 437 (1982).

- Hartstein, A. & Albert, N. F. Determination of the inversion-layer thickness from capacitance measurements of metal-oxidesemiconductor field-effect transistors with ultrathin oxide layers. *Phys. Rev. B* 38, 1235 (1988).

- Saito, S., Torii, K., Hiratani, M. & Onai, T. Analytical quantum mechanical model for accumulation capacitance of mos structures. IEEE Electron Device Lett. 23, 348–350 (2002).

- Toita, M., Vandamme, L. K. J., Sugama, S., Akinobu, T. & Ohmi, T. Geometry and bias dependence of low-frequency random telegraph signal and 1/f noise levels in mosfets. FNL 5, L539–L548 (2005).

- Amarasinghe, N. V. & Çelik-Butler, Z. Complex random telegraph signals in 0.06 µm 2 mdd n-mosfets. Solid-State Electron. 44, 1013–1019 (2000).

- 40. Mizuta, H. & Tanoue, T. The physics and applications of resonant tunnelling diodes, vol. 2 (Cambridge University Press, 2006).

- 41. Johnson, J. B. Thermal agitation of electricity in conductors. Phys. Rev. 32, 97 (1928).

- 42. Nyquist, H. Thermal agitation of electric charge in conductors. Phys. Rev. 32, 110 (1928).

- Miki, H. et al. Statistical measurement of random telegraph noise and its impact in scaled-down high-κ/metal-gate mosfets. In Electron Devices Meeting (IEDM), IEEE International, 19–1 (IEEE) (2012).

- 44. Belyakov, A. V., Vandamme, L. K. J., Perov, M. Y. & Yakimov, A. The different physical origins of 1/f noise and superimposed rts noise in light-emitting quantum dot diodes. *FNL* **3**, L325–L339 (2003).

- Costanzi, B. N. & Dahlberg, E. D. Emergent 1/f noise in ensembles of random telegraph noise oscillators. *Phys. Rev. Lett.* 119, 097201 (2017).

- Kirihara, M., Nakazato, K. & Wagner, M. Hybrid circuit simulator including a model for single electron tunneling devices. Jpn. J. Appl. Phys 38, 2028 (1999).

- Nuryadi, R. & Awrejcewicz, J. Master Equation Based Numerical Simulation in a Single Electron Transistor Using Matlab, Numerical Simulations of Physical and Engineering Processes, (Intech, 2011).

- 48. Nuryadi, R., İkeda, H., Ishikawa, Y. & Tabe, M. Current fluctuation in single-hole transport through a two-dimensional si multidot. *Appl. Phys. Lett.* **86**, 133106 (2005).

- 49. Golovach, V. et al. Single-dopant resonance in a single-electron transistor. Phys. Rev. B 83, 075401 (2011).

- 50. Villis, B. J. *et al.* Direct detection of a transport-blocking trap in a nanoscaled silicon single-electron transistor by radio-frequency reflectometry. *Appl. Phys. Lett.* **104**, 233503 (2014).

#### Acknowledgements

This work is supported by EPSRC Manufacturing Fellowship (EP/M008975/1), EU FP7 Marie-Curie Carrier-Integration-Grant (PCIG13-GA-2013-618116), and the University of Southampton. This work is also supported by the EMPIR programme co-financed by the Participating States and from the European Union's Horizon 2020 research and innovation programme. The authors would like to thank reviewers for useful discussions. The data from the paper can be obtained from the University of Southampton ePrint research repository:10.5258/SOTON/ D0120.

#### **Author Contributions**

H.Y., Y.S., and D.H. fabricated the MOSFET device and discussed results. Z.L., M.S., F.L., M.K.H., I.T., Y.T. and S.S. have contributed for measurements and analysed experimental results.

#### **Additional Information**

Supplementary information accompanies this paper at https://doi.org/10.1038/s41598-017-18579-1.

Competing Interests: The authors declare that they have no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2017