# (12) United States Patent

### Ledvina et al.

#### US 7,010,060 B2 (10) Patent No.:

#### (45) Date of Patent: Mar. 7, 2006

### (54) REAL-TIME SOFTWARE RECEIVER

(75) Inventors: **Brent M. Ledvina**, Ithaca, NY (US); Mark L. Psiaki, Brooktondale, NY (US); Steven P. Powell, Ithaca, NY (US); Paul M. Kintner, Jr., Ithaca, NY

(US)

Assignee: Cornell Research Foundation, Inc.,

Ithaca, NY (US)

Subject to any disclaimer, the term of this Notice:

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

Appl. No.: 10/753,927

(22)Filed: Jan. 8, 2004

(65)**Prior Publication Data**

> US 2004/0213334 A1 Oct. 28, 2004

### Related U.S. Application Data

- Provisional application No. 60/439,391, filed on Jan. 10, 2003.

- (51) Int. Cl. H03K 9/00 (2006.01)

- **U.S. Cl.** ...... **375/316**; 375/147; 375/343;

- (58) Field of Classification Search ..... 375/316, 375/147, 343; 455/130; 324/357.12 See application file for complete search history.

#### (56)References Cited

### U.S. PATENT DOCUMENTS

6,407,699 B1 \* 6/2002 Yang ...... 342/357.12

### FOREIGN PATENT DOCUMENTS

WO WO 2004/036238 10/2003

### OTHER PUBLICATIONS

Real-Time GPS Software Radio Receiver, Akos et al., ION NTM 2001, Jan. 22-24, 2001, Long Beach, CA, pp. 809-

Global Positioning System Software Receiver (gpSrx) Implementation in Low Cost/Power Programmable Processors, Akos et al., ION GPS 2001, Sep. 11-14, 2001, Salt Lake City, UT, pp. 2851-2858.

GPS Receivers, A.J. Van Dierendonck, Global Positioning System: Theory and Applications, B. W. Parkinson and J.J. Spilker, Jr., Eds., vol. I, American Institute of Aeronautics and Astronautics, 1996, Chapter 8, pp. 329-406.

A Coming of Age for GPS: A RTLINUX Based GPS Receiver, Ledvina et al., Proceedings of the Workshop on Real Time Operating Systems and Applications and Second Real Time Linux Workshop (in conjunction with IEEE RTSS 2000), Nov. 27-28, 2000\*\*, see http://gps.ece.cornell. edu/index.html.

The New L2 Civil Signal, R.D. Fontana et al., Proceedings of the ION GPS 2001, Sep. 11-14, 2001, Salt Lake City, UT, 617-631, see http://www.findarticles.com/cf\_dls/ m0BPW/9\_12/78573899/p8/article.jhtml?term=.

A 12-Channel Real-Time GPS L1 Software Receiver, B. M. Ledvina et al., Proceedings of the ION National Technical Meeting, Jan. 22-24, 2003\*\*, Anaheim, CA, see http://gps. ece.cornell.edu/index.html.

### (Continued)

Primary Examiner—Temesghen Ghebretinsae (74) Attorney, Agent, or Firm-Perkins Smith & Cohen LLP; Jacob N. Erlich; Kathleen Chapman

#### ABSTRACT (57)

A real-time software receiver that executes on a general purpose processor. The software receiver includes data acquisition and correlator modules that perform, in place of hardware correlation, baseband mixing and PRN code correlation using bit-wise parallelism.

### 27 Claims, 14 Drawing Sheets

### OTHER PUBLICATIONS

Bit-Wise Parallel Algorithms for Efficient Software Correlation Applied to a GPS Software Receiver, B.M. Ledvina et al., to appear in the IEEE Transactions on Wireless Communications, 2003.

Design and Practical Implementation of Multi-Frequency RF Front Ends Using Direct RF Sampling, M.L. Psiaki et al., Preprint from ION GPS/GNSS 2003.

Design and Implementation of a Direct Digitization GPS Receiver Front End, D.M. Akos, IEEE Transactions on Mocrowave Theory and Techniques, vol. 44, No. 12, Dec. 1996.

A High-Performance Real-Time GNSS Software Receiver and its Role in Evaluating Various Commercial Front End ASICs, Jona Thor, ION GPS 2002, Sep. 24-27, 2002, pp 2554-2560.

U.S. Provisional Appl. No. 60/439,391 filed Jan. 10, 2003. Title: Real-Time Software Receiver. Applicants: Brent M. Ledvina et al.

Software Solution of GPS Baseband Processing, Asai, et al., International Conference on Consumer Electronics, 1998 Digest of Technical Papers, Jun. 2-4, 1998, pp. 180-181.

\* cited by examiner

FIG. 1

DATA BUFFERING AND ACQUISITION SYSTEM 17

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 2D

FIG. 3B

FIG. 3C PRIOR ART

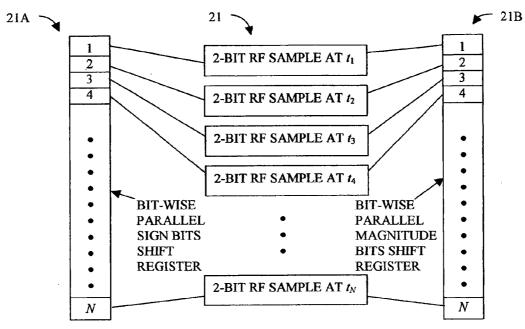

REPRESENT SAMPLE SIGNAL DATA 21 FROM AT LEAST ONE CHANNEL AS SIGNAL SIGN 21A AND, IF PRESENT, SIGNAL MAGNITUDE 21B AND SELECT CARRIER REPLICA 25 BASED ON ITS FREQUENCY'S PROXIMITY TO A DESIRED CARRIER REPLICA FREQUENCY, REPRESENT CARRIER REPLICA 25 AS CARRIER REPLICA SIGN 25A AND CARRIER REPLICA MAGNITUDE 25B, 101

MIX SIGNAL DATA 21 TO BASEBAND → COMPUTE BASEBAND MIXED SIGN 23A = XOR (CARRIER REPLICA SIGN 25A, SIGNAL SIGN 21A); COMPUTE BASEBAND MIXED MAGNITUDE 23B/C = f (CARRIER REPLICA MAGNITUDE 25B, SIGNAL MAGNITUDE 21B) 103

SELECT PRN CODE FROM PRN CODE TABLE 28 OR COMPUTE IT USING REAL-TIME OVER-SAMPLED PRN CODE GENERATOR 30A; REPRESENT PROMPT PRN CODE 29 AS PROMPT SIGN 29A; REPRESENT EARLY-MINUS-LATE PRN CODE 35 AS EARLY-MINUS-LATE PRN SIGN 35A AND EARLY-MINUS-LATE PRN ZERO MASK 35B 105

DE-SPREAD BY MIXING IN-PHASE AND QUADRATURE BASEBAND MIXED SIGNALS 23 WITH PROMPT PRN CODE 29 AND EARLY-MINUS-LATE PRN CODE 35: COMPUTE FULLY MIXED PROMPT INTEGRAND SIGN 31A = XOR (BASEBAND MIXED SIGN 23A, PROMPT PRN CODE SIGN 29A); COMPUTE FULLY MIXED PROMPT INTEGRAND MAGNITUDE 31B/C = f (BASEBAND MIXED MAGNITUDE 23B/C); COMPUTE FULLY MIXED EARLY-MINUS-LATE INTEGRAND SIGN 33A = XOR (BASEBAND MIXED SIGN 23A, EARLY-MINUS-LATE PRN CODE SIGN 35A); COMPUTE FULLY MIXED EARLY-MINUS-LATE INTEGRAND HIGH/LOW MAGNITUDE 33B/C= f (BASEBAND MIXED MAGNITUDE 23B/C); COMPUTE FULLY MIXED EARLY-MINUS-LATE ZERO MASK 33D= f (EARLY-MINUS-LATE PRN CODE ZERO MASK 35B); RESULT IS FULLY MIXED IN-PHASE AND QUADRATURE PROMPT INTEGRANDS 31 AND FULLY MIXED EARLY-MINUS-LATE INTEGRANDS 33 107

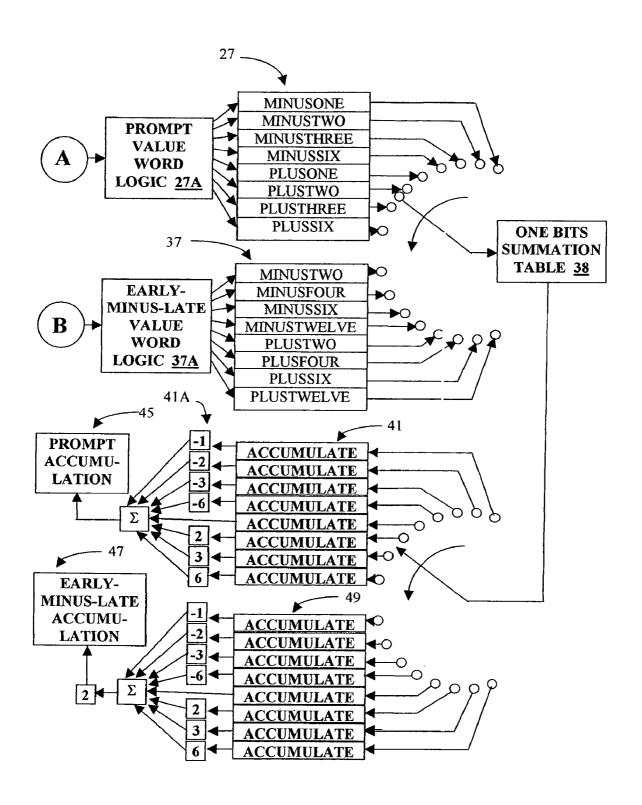

COMPUTE IN-PHASE AND QUADRATURE PROMPT INTEGRAND VALUE WORDS 27 AND EARLY-MINUS-LATE INTEGRAND VALUE WORDS 37: PROMPT INTEGRAND VALUE WORDS 27 = f (FULLY MIXED PROMPT INTEGRAND SIGN 31A, FULLY MIXED PROMPT INTEGRAND MAGNITUDE 31B/C); COMPUTE EARLY-MINUS-LATE INTEGRAND VALUE WORDS 37 = f (FULLY MIXED EARLY-MINUS-LATE INTEGRAND SIGN 33A, FULLY MIXED EARLY-MINUS-LATE INTEGRAND MAGNITUDE 33B/C, FULLY MIXED EARLY-MINUS-LATE INTEGRAND ZERO MASK 33D) 109

FIG. 4A

B

SUM OVER EACH INTEGRAND VALUE WORD 27/37 THE NUMBER OF ONE BITS (OR ZERO BITS) BY USING THE ONE BITS SUMMATION TABLE 38 OR A PROCESSOR COMMAND: COMPUTE PROMPT INTEGRAND VALUE-WORD ONE-BITS COUNTS = f (PROMPT INTEGRAND VALUE WORD 27); COMPUTE EARLY-MINUS-LATE INTEGRAND VALUE-WORD ONE-BITS COUNTS = f (EARLY-MINUS-LATE INTEGRAND VALUE WORD 37) 111

SUM OVER ACCUMULATION INTERVAL THE NUMBER OF ONE BITS (OR ZERO BITS) IN EACH PROMPT INTEGRAND VALUE WORD 27 AND EARLY-MINUS-LATE INTEGRAND VALUE WORD 37 TO PRODUCE ACCUMULATIONS 41 AND 49: COMPUTE PROMPT ACCUMULATIONS 41 =  $\Sigma$  (PROMPT VALUE-WORD ONE-BITS COUNTS); SUM IS OVER ALL WORDS IN ACCUMULATION INTERVAL; COMPUTE EARLY-MINUS-LATE ACCUMULATIONS 49 =  $\Sigma$  (EARLY-MINUS-LATE INTEGRAND VALUE WORD ONE-BITS COUNTS); SUM IS OVER ALL WORDS IN ACCUMULATION INTERVAL 113

MULTIPLY VALUE WORD ONES ACCUMULATIONS 41 AND 49 BY CORRESPONDING VALUES 41A AND SUM OVER ALL VALUE WORDS FOR INPHASE AND QUADRATURE PROMPT WORDS AND EARLY-MINUS-LATE WORDS: SUMMED PROMPT ACCUMULATION 45 =  $\Sigma$  (VALUE 41A\*[PROMPT ACCUMULATION 41]); SUM IS OVER ALL VALUES; SUMMED EARLY-MINUS-LATE ACCUMULATION 47 =  $\Sigma$  (VALUE 41A\*[EARLY-MINUS-LATE ACCUMULATION 49]); SUM IS OVER ALL VALUES; RESULTS ARE IN-PHASE AND QUADRATURE SUMMED PROMPT ACCUMULATION 45 AND SUMMED EARLY-MINUS-LATE ACCUMULATION 47 115

ROTATE THE IN-PHASE AND QUADRATURE PROMPT ACCUMULATIONS 45

AND EARLY-MINUS-LATE ACCUMULATIONS 47 117

YES

MORE

CHANNELS? 119

NO

RESET FOR ANOTHER ACCUMULATION INTERVAL 121

TIME PERIOD

ELAPSED? 123

YES

A

FIG. 4B

**FIG. 5**

**FIG.** 6

Mar. 7, 2006

COMPUTE TABLE OF CANDIDATE INTEGERS NECESSARY TO COMPUTE AN ARRAY INDEX (EQUATION (36)) BY ITERATING EQUATIONS (44a)-(44c) 201

COMPUTE DATA WORD MIDPOINT INDEX  $k_{fmid}$ , CODE DOPPLER CORRECTION CONSTANTS  $a_{fix}$  AND  $b_{fix}$ , NOMINAL CHIPS PER DATA WORD  $L_{typ}$ , NUMBER OF FINE TIME INCREMENTS PER CHIP  $\Delta k_{fc}$ , NOMINAL CHANGE IN FINE TIME OFFSET  $\Delta k_{flyp}$ , AND MINIMUM AND MAXIMUM FINE TIME OFFSET  $k_{fmin}$  and  $k_{fmax}$ , USING EQUATIONS 48a-48e AND 50a-50e THESE ARE USED TO DETERMINE THE INDEX INTO PROMPT SIGN, EML ZERO MASK, AND EML SIGN TABLES 203

INITIALIZE TIME OFFSET INDEX  $k_{fl}$  AND AUXILIARY TABLE INDEX  $\mu_I$  BY EVALUATING EQUATIONS 51a-52b 205

COMPUTE  $k_{fvnom}$ ,  $\mu_{vnom}$ ,  $\eta_{fv}$ ,  $k_{fv}$ ,  $\mu_{v}$ ,  $k_{v}$ , and  $i_{v}$ , FOR v = 1, ..., NBYITERATING EQUATIONS 53a, 53b, 57a-c, 49, 55, 45 TO COMPUTE INDICES INTO PROMPT SIGN, EARLY-MINUS-LATE ZERO MASK, AND EARLY-MINUS-LATE SIGN TABLES 207

COMPUTE  $x_{pv}$ ,  $x_{emlzmv}$ , and  $x_{eml2sv}$ . FOR v = 1, ..., NBYEVALUATING EQUATIONS 56a-c TO COMPUTE THE PROMPT SIGN, EARLY-MINUS-LATE ZERO MASK, AND EARLY-MINUS-LATE SIGN DATA WORDS 209

**END**

FIG. 7

**FIG. 8**

-0.6

-3

-2

FIG. 9B

l 0 Code Offset (chips) 2

3

### REAL-TIME SOFTWARE RECEIVER

## CROSS REFERENCE TO RELATED APPLICATIONS

The present application claims priority to U.S. Provisional Application No. 60/439,391 filed Jan. 10, 2003 entitled REAL-TIME SOFTWARE RECEIVER which is incorporated herein in its entirety by reference.

### STATEMENT OF GOVERNMENT INTEREST

This invention was made with United States Government support from the Office of Naval Research (ONR) under contract number N00014-02-J-1822 and from the National 15 Aeronautics and Space Administration (NASA) under contract numbers NCC5-563, NAG5-11819, and NAG5-12089. The United States Government has certain rights in the invention.

### BACKGROUND OF THE INVENTION

This invention relates generally to software radio receivers, and more specifically to a software receiver for positioning systems.

A typical positioning system receiver, such as is used in the Global Positioning System (GPS), includes an antenna, a radio frequency (RF) section, a correlator, a signal tracking and demodulation component, and a component to compute the navigation solution. The antenna, which is possibly 30 followed by a pre-amplifier, receives L-band GPS signals. The RF section filters and down converts the GHz GPS signal to an intermediate frequency in the MHz range. The RF section also digitizes the signal. The correlator separates the down-converted signal into different channels (ten or 35 more in modern receivers) allocated to each satellite. For each satellite, the correlator mixes the Doppler-shifted intermediate frequency signal to baseband by correlating it with a local copy of the carrier replica signal and it distinguishes the particular satellite by correlating the signal with a 40 pseudo-random number (PRN) code. Software routines cause the carrier replica and PRN replica signals to track the actual received signal, extract the navigation message, and compute the navigation solution.

Baseband mixing is a multiplication of an input signal by 45 a complex exponential where the frequency of the complex exponential approximately matches that of the input signal. The resultant signal is centered at baseband. A complex signal can be broken down into cosine and sine signal components, resulting in separate in-phase and quadrature 50 components. The frequency of the baseband mixed signal must be controllable to within a few millihertz in the case of a phase-locked loop for use in a precision navigation system, and the baseband mixed signal must have a continuously varying phase. In a hardware correlator, local oscillators 55 generate cosine and sine signal components that have precise frequency control and a continuous phase. Generating cosine and sine signal components on the fly with the correct frequency and phase is too time consuming to be feasible for a software correlator. Instead, the software correlator gen- 60 erates cosine and sine signal components on a grid of frequencies off-line. These signal components must be stored on a time grid of points sampled at the RF front-end sampling frequency, for example, at 5.714 MHz for one particular RF front-end hardware configuration, and the 65 signals must last for a typical accumulation period, e.g., for a 0.001 second coarse/acquisition (C/A) PRN code period

2

when working with GPS L1 civilian signals. It takes tens of gigabytes of memory or more in order to brute-force store all frequencies on a one mHz grid ranging from -10 KHz to +10 KHz, which is the needed frequency range when tracking GPS satellites from a terrestrial receiver, and additional storage is required to store a grid of possible starting phases at each frequency point.

PRN code mixing is a multiplication of a baseband mixed signal by a prompt +1/-1 PRN code or by a +2/0/-2 early-minus-late PRN code, where the code timing and frequency approximately match that of the input signal. The resultant signal is a constant in the case of prompt PRN code mixing, and an approximately linear function of the code timing error in the case of early-minus-late mixing. A receiver accumulates both of these correlation outputs. The magnitude of the prompt accumulation indicates signal strength and whether a signal has been detected, and its in-phase (real) and quadrature (imaginary) components are used to measure carrier phase and Doppler shift. The magnitude of the early-minus-late accumulation measures the code timing error; it will be zero when the timing error is zero.

The code phase of the baseband mixing signal must be controllable to within a percent or less of a PRN code chip for use in a precision navigation system. In a hardware correlator, local oscillators generate the prompt and early-minus-late PRN code replicas. A software correlator can either compute and store PRN code replicas, or compute them in real-time.

The current Global Positioning System is slated to realize expanded capabilities that include new civilian codes on the L2 frequency, a new L5 frequency, and new codes (M-code, CL and CM codes) on the L2 frequency. Some of these upgrades are slated to start within one to three years. A hardware correlator requires hardware modifications in order to use these new signals. In the near term, a receiver designer will be faced with a complex trade-off in order to decide whether the extra complexity is worth the improved performance that will accrue only very slowly as new GPS satellites replace older models. One way to avoid the complex trade-off is to use a software receiver that can receive and process new signals without the need for a new correlator chip set.

A software receiver is flexible because its software components can be easily modified. One application of a software receiver is to merge together numerous devices that use wireless digital communication protocols to form a single device. For example, a cell phone, GPS receiver, and Personal Data Assistant (PDA) could become a single device that plays the role of all three. Another use of a software receiver is to shorten development and to-market times for new wireless devices. For example, as new frequencies and codes are added to GPS, a software receiver having a software correlator simply needs to be reprogrammed, while a hardware approach would require a brand new correlator chip design. New PRN codes can be used simply by making software changes. Thus, software receiver technology lessens the risks involved for designers during the period of transition to the new signals. Furthermore, a software receiver could be reprogrammed to use the Galileo system (European GPS) or GLONASS (Russian GPS).

In the recent past, GPS software receivers have been developed that either post-process stored signals or operate in real-time. Previous real-time software receivers function with a limited number of channels (4–6) or require high-end computer speeds or digital signal processor (DSP) chips such as are disclosed in *Real-Time GPS Software Radio*

,

Receiver, Akos et al., ION NTM 2001, 22–24 Jan. 2001, Long Beach, Calif., pp. 809–816 (Akos 2001a), and Global Positioning System Software Receiver (gpSrx) Implementation in Low Cost/Power Programmable Processors, Akos et al., ION GPS 2001, 11–14 Sep. 2001, Salt Lake City, Utah, 5 pp. 2851–2858, both incorporated herein in their entireties by reference.

Therefore, it is an object of the present invention to create a software receiver that operates in real-time and is not restricted to a severely limited number of channels or to a 10 very fast processor.

Another object of the present invention is to minimize the number of sine and cosine signal components that must be stored.

A further object of the present invention is to process 15 incoming signals through bit-wise parallelism.

A still further object of the present invention is to process over-sampled signals by use of bit-wise parallelism.

A still further object of the present invention is to use very long over-sampled PRN codes efficiently in a bit-wise 20 include a table of pre-computed baseband mixing sine parallel software receiver.

The system and method of the present invention also include a table of pre-computed baseband mixing sine waves, algorithms that can produce correlation accumula-

### SUMMARY OF THE INVENTION

The objects set forth above as well as further and other 25 objects are addressed by the present invention. The solutions and advantages of the present invention are achieved by the illustrative embodiment described herein below.

The software receiver system and method of the present invention enable the efficient execution of a set of algo- 30 rithms, that perform software correlation on data sampled from incoming channels, on a general purpose processor. The system and method of the present invention provide for either PRN code storage or computation of PRN codes in real-time. PRN code storage is appropriate for PRN codes 35 that have short periods, such as the GPS coarse/acquisition codes, which are 1023 chips long. In this case, the system and method of the present invention pre-compute oversampled replicas of entire PRN code periods and store them for orderly and efficient retrieval, such as in a table. This 40 table can include a selection of code start times as measured relative to the sample times at which RF data are available from the receiver front end. There is a separate table for each unique PRN code.

The system and method of the present invention can also 45 generate over-sampled versions of the prompt and early-minus-late PRN codes in real-time through use of an over-sampling function described herein. The values of the over-sampling function can be located in a specially designed table that can be generic across PRN codes. The length of the specially designed table can be independent of the length of the PRN code whose replica is being used to process a given received signal. The system and method of the present invention include techniques for efficiently calculating indices into the specially designed table that enable rapid, 55 real-time table look-up.

The system of the present invention includes a software correlator that can mix the received signal to baseband, compute baseband/PRN correlations through bit-wise parallelism and look-up tables using either the tabulated or 60 real-time-generated PRN codes, and compute accumulations through bit-wise parallelism and processor instructions or look-up tables. Bit-wise parallelism allows the processing of multiple data samples simultaneously as the multiple bits of a given word of computer data. For example, for 32-bit 65 words, the software correlator can process up to 32 samples at a time. Bit-wise parallelism can optimally operate when

4

each signal in question can be represented by only a few bits, which is normally the case in RF digital signal processing of navigation signals.

The bit-wise parallel operations of the present invention can save computation time in comparison to integer mathematical correlation operations. If, for example, four accumulations are required per sample, integer mathematics requires six multiplications and four additions per sample (except for the last sample). At a sampling rate of, for example, 5.714 MHz this translates into 57,140 integer operations per PRN code period. In the illustrative embodiment, 33,500 bit-wise parallel operations are necessary per PRN code period when the RF signal has a 2-bit representation. This operation count is further reduced to approximately 16,750 bit-wise parallel operations per PRN code period when the RF signal has a 1-bit representation. Thus, there can be a savings of almost a factor of two to almost a factor of four in the operation count.

The system and method of the present invention also include a table of pre-computed baseband mixing sine waves, algorithms that can produce correlation accumulation outputs that are equivalent to what would be produced by a continuously variable sine wave, and a method of use of the table and algorithms. Thus, in the present invention, a relatively small set of sine wave values need to be pre-computed and saved, which can conserve computer memory and processing time.

The present invention also includes a system and method for tracking the phase of PRN code replicas in software in order to track the timing of any given "chip" of the PRN code replica as measured with respect to a pre-specified set of sample times at which the basic raw data comes out of the RF front end (a chip is an element of a PRN code). The PRN code phase is kept track of via a variable for each channel, that indicates the PRN code start time with respect to the RF sample times. The system and method of the present invention allow for the synchronization of the measurements of PRN code phase, carrier phase, and carrier frequency for each satellite relative to these sample times.

The method for tracking the phase of each PRN code replica and the phase of each carrier replica includes the steps of latching all the C/A code phases, carrier phases, epoch counters, and carrier frequencies for each satellite at a pre-specified time, and computing the pseudo range to each satellite using the C/A code phase and epoch counters. The method also includes the step of tracking and updating code and carrier phases by estimating code chipping rate and carrier Doppler shift inputs. The method further includes the step of computing the code phase at the pre-specified time for each satellite as a function of the updated code chipping rate and the pre-specified time. The method further includes the step of computing the carrier phase at the pre-specified time as a function of the updated carrier phase, the Doppler shift, and the pre-specified time. The timing of the PRN code phase (or chip location) is the most fundamental of GPS measurements for use in navigation data processing. The monitoring of these times in software allows complete control of the precision with which they can be measured, and it allows precise synchronization of these times with the measurement times of data from other sensors, such as inertial measurement units. This feature gives an enhanced ability to develop what are known as deeply coupled systems that must fuse GPS data with data from other types of sensor systems.

The software correlator of the present invention can advantageously be easily adapted to accept signals at any frequency, new PRN codes, or even signals for different

types of devices. Thus, the same processing hardware could use the software correlator to implement such devices as a GPS receiver, a cell phone, or both. To allow for new codes, new frequencies, and new types of functionality, small changes can be made in the software correlator, or different 5 versions of the software correlator can be run on the same processor. Hardware-correlator-based receivers of the prior art can deal only with frequencies and PRN codes that are hard-wired into their designs. Also, the system and method of the present invention could be implemented within systems such as GLONASS receivers, cell phones and cell base stations, pagers, wireless Ethernet (e.g. 802.11x standards), Bluetooth™, Blackberry® wireless internet devices, and satellite radio/phones (e.g. INMARSAT®). In fact, the system and method of the present invention are applicable to 15 any sort of telecommunication system/device that uses spread spectrum, code division multiple access (CDMA) PRN codes for the transmission of information, either wired or wireless

For a better understanding of the present invention, 20 together with other and further objects thereof, reference is made to the accompanying drawings and detailed description. The scope of the present invention is pointed out in the appended claims.

### DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

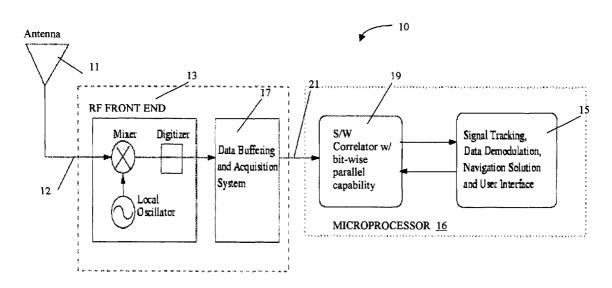

FIG. 1 is a schematic block diagram of the hardware environment of a typical software receiver;

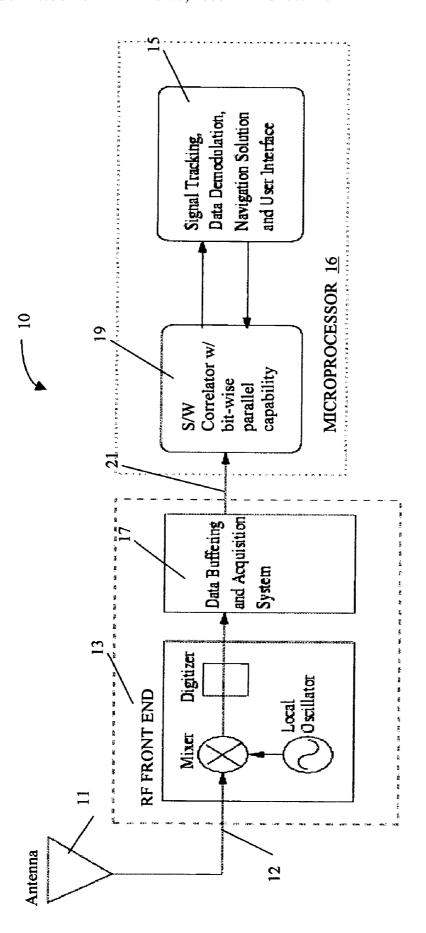

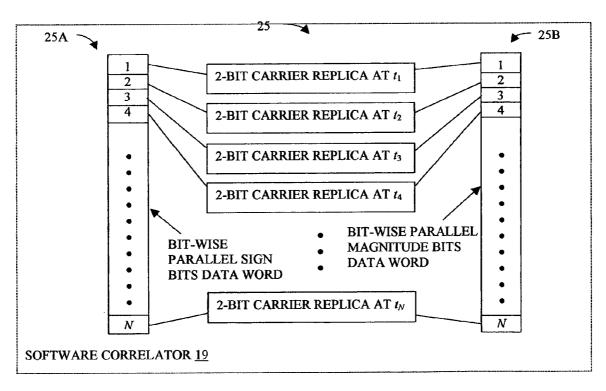

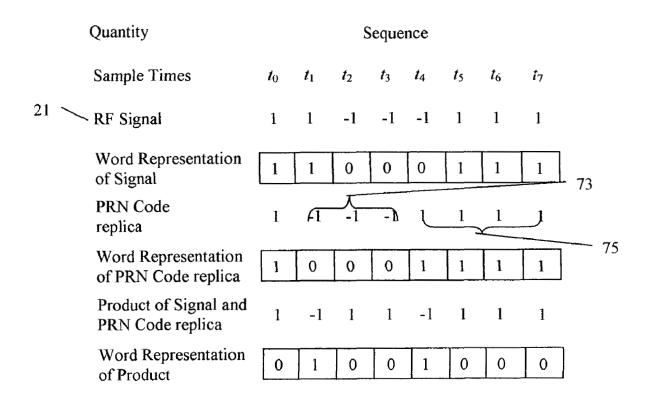

FIGS. 2A and 2B are schematic diagrams of bit-wise mappings of signal and carrier replica sign and magnitude bits to computer data words;

FIG. 2C is a graphic representation of a plot of bit-wise

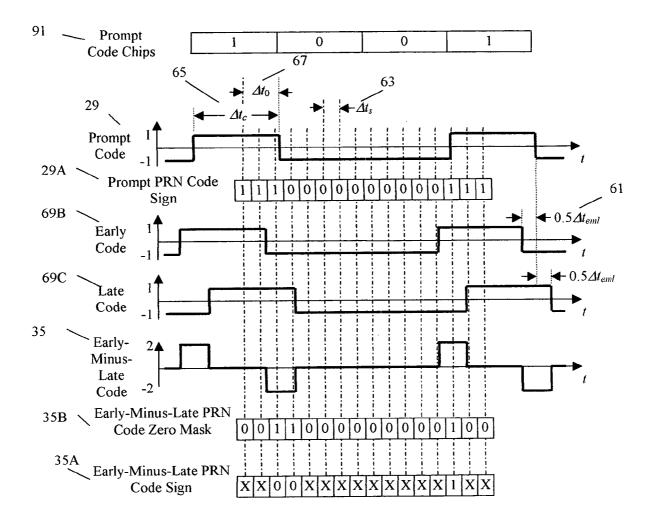

FIG. 2D is a graphic representation of a plot of sections of prompt, early, late, and early-minus-late PRN code signals and 16-bit word representations of their over-sampled

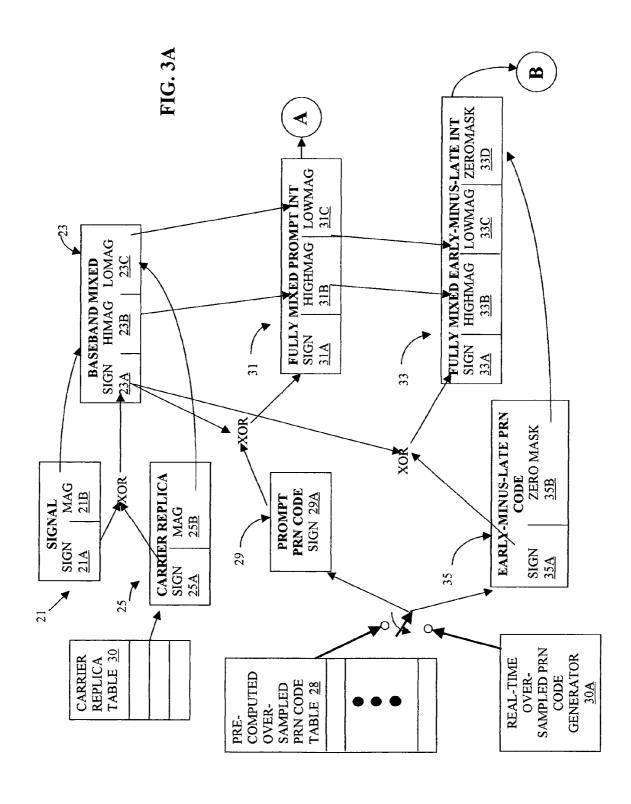

FIGS. 3A and 3B are data flow diagrams illustrating the bit-wise parallelism process (replicated twice, once for the in-phase carrier replica and once for the quadrature carrier replica) of the present invention;

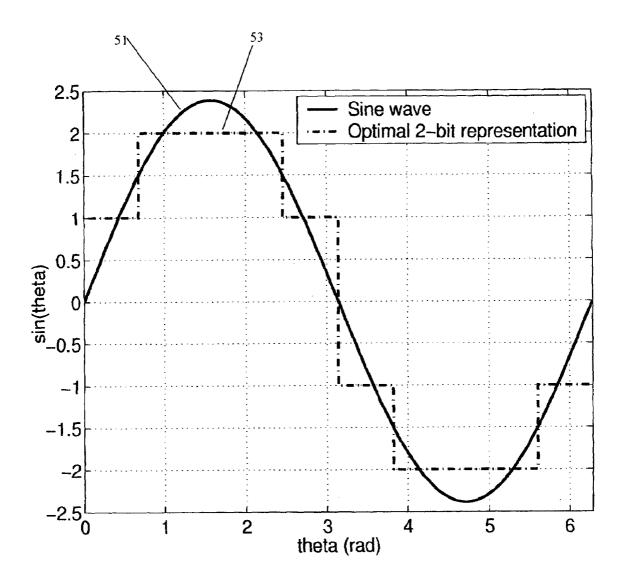

FIG. 3C is a graphic representation of a plot of a prior art 45 optimal 2-bit representation of a sine wave presented to enhance the reader's understanding of the present invention;

FIGS. 4A and 4B are flowcharts of the method for computing correlation accumulations through bit-wise parallel computations of the present invention;

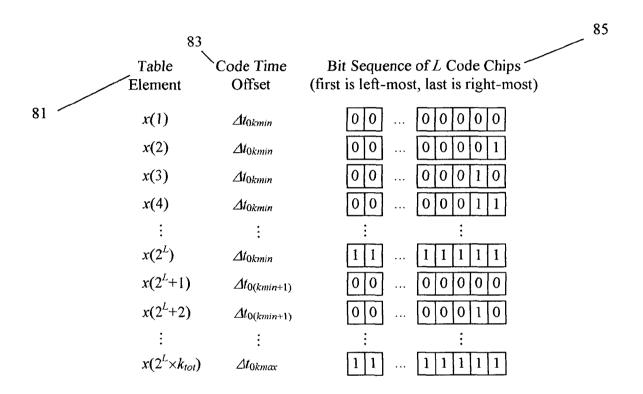

FIG. 5 is a schematic diagram of a look-up table layout as a function of code time offset and chip bit pattern;

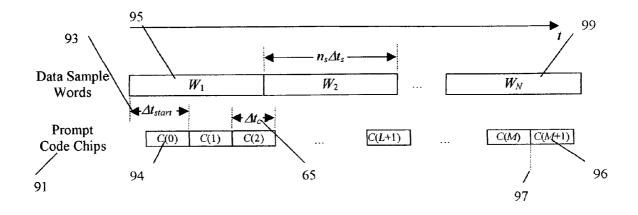

FIG. 6 is a graphic representation of a plot illustrating the timing relationship between data sample words and the sequence of prompt code chips that defines an accumulation 55 interval;

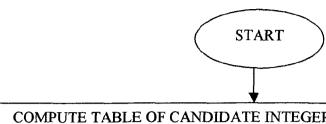

FIG. 7 is a flowchart of the method for computing bit-wise parallel representations of the over-sampled prompt PRN code replica and the over-sampled early-minus-late PRN code replica for an entire accumulation interval using the 60 real-time over-sampled PRN code generation algorithm.

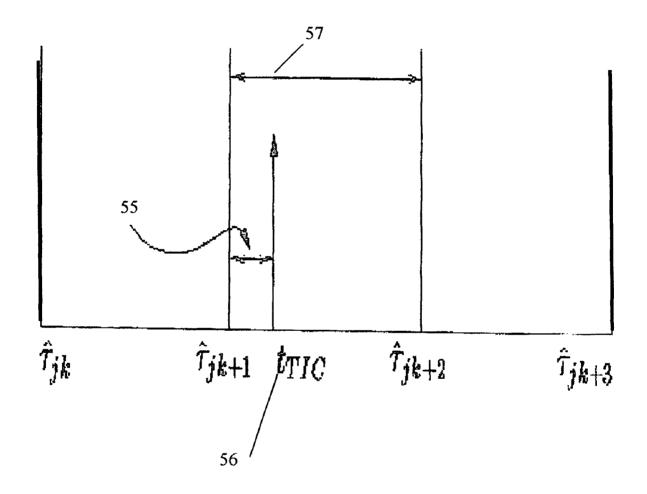

FIG. 8 is a graphic representation of a plot that illustrates the location in time at which the code phase of each signal is computed; and

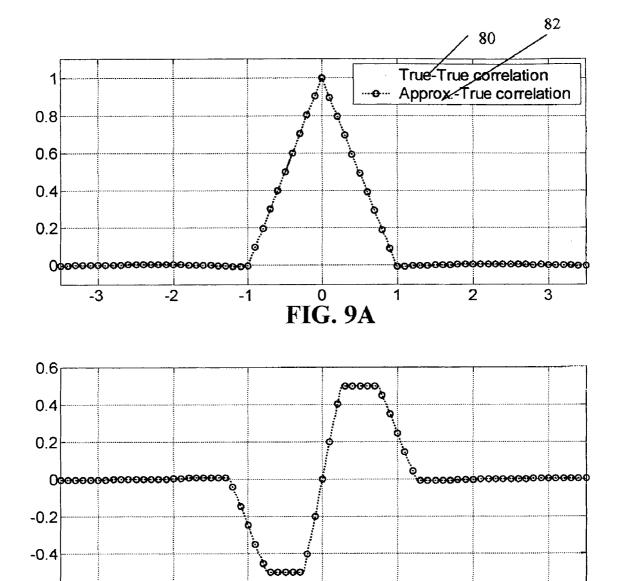

FIGS. 9A and 9B are graphic representations of plots of 65 correlations of the true sampled code with prompt (FIG. 9A) and early-minus-late (FIG. 9B) versions of the true and table

look-up codes, the latter being generated by the new realtime over-sampled PRN code generator.

### DETAILED DESCRIPTION OF THE INVENTION

The present invention is now described more fully hereinafter with reference to the accompanying drawings, in which the illustrative embodiment of the present invention is shown. The following configuration description is presented for illustrative purposes only. Any computer configuration satisfying the speed and interface requirements herein described may be suitable for implementing the system of the present invention. The equations herein are stated in general terms, but have parameters that are specific to the GPS L1 C/A signal for illustrative purposes only. For example, the 0.001 sec. accumulation interval seen in many of the equations is the nominal C/A code period. Also, the C/A PRN code of the illustrative embodiment can be replaced by the PRN code of any other CDMA signaling

By way of introductory explanation, RF signal processing equations and terms are herein provided. The time-domain L1 C/A signal received from, for example, a satellite, is 25 represented by:

$$y(t_i) = \sum_{j} A_j D_{jk} C_j \left[ 0.001 \left( \frac{t_i - \tau_{jk}}{\tau_{jk+1} - \tau_{jk}} \right) \right]$$

$$\cos[\omega_{IF} t_i - \phi_j(t_i)] + n_j$$

(1)

where  $t_i$  is the sample time,  $A_j$  is the amplitude,  $D_{jk}$  is the parallel radio frequency signal and PRN code replica storage and mixing; are the and mixing;  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of the received  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  and  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk+1} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  are the start times of  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  and  $\tau_{jk} = 1$  and  $\tau$  $\omega_{_{I\!F}}$  is the intermediate frequency corresponding to the L1 carrier frequency,  $\phi_i(t_i)$  is the carrier phase perturbation due to accumulated delta range, n<sub>i</sub> is the receiver noise, and the subscript j refers to a particular GPS satellite. The summation is over all visible GPS satellites. The negative sign in front of  $\phi(t_i)$  comes from the high-side mixing that occurs in the RF front-end that has been used in the illustrative embodiment. The signal in equation (1) is the output of a typical RF front end.

> A GPS receiver works with correlations between the received signal and a replica of it. The correlations are used to acquire and track the signal. The replica is composed of two parts, the carrier replica and the C/A PRN code replica. Two carrier replica signals are used, an in-phase signal and a quadrature signal. When mixed with the received signal from the RF front end they form the in-phase and quadrature baseband mixed signals represented by:

$$y_{Ij}(t_i) = C_j \left[ 0.001 \left( \frac{t_i - \hat{\tau}_{jk}}{\hat{\tau}_{jk+1} - \hat{\tau}_{jk}} \right) \right]$$

$$\cos \left\{ \omega_{IF} t_i - \left[ \hat{\phi}_{jk} + \hat{\omega}_{Doppjk} \left( t_i - \hat{\tau}_{jk} \right) \right] \right\}$$

(2)

$$\begin{aligned} y_{Qj}(t_i) &= -C_j \left[ 0.001 \left( \frac{t_i - \hat{\tau}_{jk}}{\hat{\tau}_{jk+1} - \hat{\tau}_{jk}} \right) \right] \\ & \sin \left\{ \omega_{IF} t_i - \left[ \hat{\phi}_{jk} + \hat{\omega}_{Doppjk} (t_i - \hat{\tau}_{jk}) \right] \right\} \end{aligned}$$

$$(3)$$

where equations (2) and (3) apply during the kth C/A code period. In these equations  $\tau_{ik}$  and  $\tau_{ik+1}$  are the receiver's estimates of the start times of the  $k^{th}$  and  $k+1^{st}$  code periods,  $\hat{\phi}_{jk}$  is the estimated carrier phase at time  $\hat{\tau}_{jk}$ , and  $\hat{\omega}_{Doppjk}$  is the estimated carrier Doppler shift during the  $k^{th}$  code period.

A typical receiver computes the estimates  $\hat{\tau}_{jk}$ ,  $\hat{\tau}_{jk+1}$ ,  $\hat{\phi}_{jk}$ , 5 and  $\hat{\omega}_{Doppjk}$  by various conventional means that are described in *GPS Receivers*, A. J. Van Dierendonck, *Global Positioning System: Theory and Applications*, B. W. Parkinson and J. J. Spilker, Jr., Eds., vol. I, American Institute of Aeronautics and Astronautics, 1996, Chapter 8, pp. 329–406 10 (Dierendonck), incorporated herein in its entirety by reference. These include open-loop acquisition methods and closed-loop signal tracking methods such as a delay-locked loop to compute  $\hat{\tau}_{jk}$  and  $\hat{\tau}_{jk+1}$  and a phase-locked loop or a frequency-locked loop to compute  $\hat{\phi}_{jk}$  and  $\hat{\omega}_{Doppjk}$ . The 15 software receiver developed herein uses conventional techniques for forming these estimates.

Both prompt and early-minus-late correlations are needed to track the carrier frequency, carrier phase, and code phase in a GPS receiver. A typical receiver uses the PRN code and 20 carrier replicas to compute the following in-phase and quadrature correlation accumulations:

$$I_{jk}(\Delta) = \sum_{i=i_k}^{i_k+N_k} y(t_i) C_j \left[ 0.001 \left( \frac{t_i + \Delta - \hat{\tau}_{jk}}{\hat{\tau}_{jk+1} - \hat{\tau}_{jk}} \right) \right]$$

$$\cos \left\{ \omega_{IF} t_i - \left[ \hat{\phi}_{jk} + \hat{\omega}_{Doppjk} (t_i - \hat{\tau}_{jk}) \right] \right\}$$

$$Q_{jk}(\Delta) = -\sum_{i=i_k}^{i_k+N_k} y(t_i) C_j \left[ 0.001 \left( \frac{t_i + \Delta - \hat{\tau}_{jk}}{\hat{\tau}_{jk+1} - \hat{\tau}_{jk}} \right) \right]$$

$$\sin \left\{ \omega_{IF} t_i - \left[ \hat{\phi}_{jk} + \hat{\omega}_{Doppjk} (t_i - \hat{\tau}_{jk}) \right] \right\}$$

(5)

where  $i_k$  is the index of the first RF front-end sample time that obeys  $\hat{\tau}_{jk} \leq t_{i_k}$  and  $N_k+1$  is the total number of samples that obey  $\hat{\tau}_{jk} \leq t_{i_k} \hat{\tau}_{jk+1}$ . The time offset  $\Delta$  causes the replica PRN code to play back early if it is positive and late if  $\Delta$  is negative. The prompt correlations are defined by equations 40 (4) and (5) with  $\Delta = 0$ . The early-minus-late correlations are  $I_{jk}(\Delta_{eml}/2) - I_{jk}(-\Delta_{eml}/2)$  and  $Q_{jk}(\Delta_{eml}/2) - Q_{jk}(-\Delta_{eml}/2)$ , where  $\Delta_{eml}$  is the spacing between the early and late PRN carrier replicas. The present invention described herein is an efficient technique for the receiver to accumulate  $I_{jk}$  and  $Q_{jk}$  in 45 software.

Referring now to FIG. 1, the operational platform of the software receiver 10 of the present invention includes an antenna 11, conventional RF front-end 13, a data acquisition (DAQ) system 17, a microprocessor 16, a software correla- 50 tor 19, and application-specific code 15. Conventional RF front-end 13 interfaces with antenna 11 and with (DAQ) system 17. DAQ system 17 includes a system of shift registers and a data buffer. Microprocessor 16 executes software correlator 19, which includes a set of specially 55 developed bit-wise parallel algorithms, and applicationspecific code 15, such as the GPS navigation and tracking functions. In the illustrative embodiment, conventional GPS software functions (signal tracking, data extraction, navigation solution, etc.) are provided by the MITEL® GPS 60 Architect software ported to RTLINUX® (see A Coming of Age for GPS: A RTLINUX BASED GPS RECEIVER, Ledvina et al., Proceedings of the Workshop on Real Time Operating Systems and Applications and Second Real Time Linux Workshop (in conjunction with IEEE RTSS 2000) Nov. 65 27-28, 2000), but can be provided by any equivalent configuration.

Continuing to refer to FIG. 1, conventional RF front-end 13 can, for example, be a MITEL® GP2015 RF front-end, which down converts the nominal 1.57542 GHz GPS signal 12 to an intermediate frequency of (88.54/63)×10° Hz≈1.4053968254 MHz and then performs analog-to-digital conversion. The resultant, digitized signal data 21 has a pre-determined number of bits/sample, such as two binary bits/sample, a sign bit and a magnitude bit, or one bit/ sample. The shift registers in the DAQ system 17 parallelize the magnitude and sign data bit streams into separate words, which the DAQ system 17 reads into the memory of microprocessor 16 using DMA. To make the process of reading data into the microprocessor 16 more efficient and to prepare for efficient correlation calculations, DAQ system 17 can read a pre-specified number of bits of buffered samples, such as thirty-two bits, at a time. The exemplary thirty-two bits include sixteen sign bits and sixteen magnitude bits.

Referring now to FIGS. 1 and 2A, the shift registers in DAQ system 17 (FIG. 1) buffer signal data 21 (FIGS. 1 and 2A) and pack signal sign 21A (FIG. 2A) and signal magnitude 21B (FIG. 2A) into separate words, that represent the integer values ±1 and ±3 as is shown in Table 1. In the case of a 1-bit signal, the bit stream representing the samples is packed into successive words to prepare the signal for bit-wise parallel processing. DAQ system 17 also provides for accurate timing by, for example, synchronizing signal sign 21A and signal magnitude 21B to a  $(40/7)\times10^6$ Hz≈5.714 MHz clock signal, which can be, for example, a third output from conventional RF front-end 13 (FIG. 1). DAQ system 17 can convert the 5.71424 MHz clock signal down to 357.14 KHz by use of, for example, a divide-by-16 counter for a 16-bit word, which can provide a signal indicating when the buffer is full. DAQ system 17 can use any method for providing a buffer full indication.

TABLE 1

The sign and magnitude combinations of the sample RF output of the conventional RF front-end and their corresponding values.

| Signal Sign 21A | Signal Magnitude 21B | RE Signal Value |

|-----------------|----------------------|-----------------|

| 0               | 0                    | -1              |

| 0               | 1                    | -3              |

| 1               | 0                    | +1              |

| 1               | 1                    | +3              |

|                 |                      |                 |

With further reference to FIG. 1, in the illustrative embodiment, the DAQ system 17 can consist of an interface card and driver software that can be compatible with, for example, a 1.73 GHz AMD ATHLON processor running RTLINUX®, but could be compatible with any operating system and any processor that can accommodate real-time operations. The interface card can, for example, be a NATIONAL INSTRUMENTS® PCI-DIO-32HS digital I/O card. Pertinent features of this card are the thirty-two digital input lines, DMA, and availability of a driver for RTLINUX®, perhaps gotten from the suite of open source drivers and application interface software for interface cards known as COMEDI (COntrol and MEasurement and Device Interface). Modifications to the conventional COMEDI driver for the PCI-DIO-32HS card include increasing the number of input bits from sixteen to thirty-two, enabling DMA, and modifying the driver to support continuous interrupt-driven acquisition.

With still further reference to FIG. 1, microprocessor 16 can be, for example, a 1.73 GHz AMD ATHLON™ proces-

sor running the RTLINUX® operating system, but any operating system and processor that can accommodate real-time operations can be used. Low latency interrupt responsiveness, the ability to execute threads at regular intervals, with the kernel having a possibility of being the lowest priority thread, and reliable execution of time-critical code are among features of an operating system that could enhance the performance of the system of the present invention. The use of RTLINUX® is presented herein for illustrative purposes only.

Continuing to refer to FIG. 1, analogous to a hardware correlator that takes input directly from the RF front end in serial fashion, software correlator 19 reads from a shared memory buffer that both software correlator 19 and DAQ 15 system 17 can access, the former to read data, and the latter to write data. The shared memory buffer can be implemented as a DMA memory space and a circular buffer. In the illustrative embodiment in which the system and method of the present invention are used in a GPS (or similar) envi- 20 ronment, microprocessor 16 can store the most recent twenty-one milliseconds of signal data 21 (FIGS. 1 and 2A) in the circular buffer, but could store more or less. The present invention does not fix the size of the circular buffer, nor the amount of RF data that can be stored there. The circular buffer allows the processing of code periods that start and stop at different times for different satellites during different iterations of a regularly scheduled program thread. DMA memory space can be written to directly by DAO system 17 using a DAO software driver, which fills the circular buffer. Communication between software correlator 19 and application-specific code 15 can be performed using operating system-provided shared memory capability. For example, the mbuff driver, included with RTLINUX®, can 35 be used to create and manage this shared memory space. Any memory management system that accommodates realtime processing can be used. If the mbuff driver is used, kernel modules can share memory and the kernel can be restricted from swapping the shared memory space to longterm storage.

Continuing with the analogy to hardware correlation, and still referring primarily to FIG. 1, in hardware correlation, the correlator receives frequency and phase information from tracking and acquisition loops that are part of application code, and Numerically Controlled Oscillators (NCOs) generate signals that correspond to the written frequencies and phases. In contrast, software correlator 19 includes simulated carrier and code NCOs that receive their frequency commands from application-specific code 15. Software correlator 19 uses these frequency commands to reconstruct carrier replica signal 25 (FIG. 3A) and prompt PRN code 29 and early-minus-late PRN code 35 (FIG. 3A) which it mixes with the signal data 21 (FIG. 2A) resulting in fully mixed prompt integrand 31 and fully mixed early-minus-late integrand 33 (FIG. 3A).

To further continue the analogy, a hardware correlator generates in real-time a particular C/A code replica at the correct Doppler shifted frequency and phase. In contrast, software correlator 19 can generate C/A codes off-line and 60 store them in a memory table, the pre-computed oversampled PRN code table 28 (FIG. 3A). The pre-computed over-sampled PRN code table 28 is used to select PRN codes with the correct timing relationship to the sample times of signal data 21 (FIG. 3A). The codes are then used to form 65 correlations with baseband mixed signals 23 (FIG. 3A), the result from which is summed to produce the standard

10

in-phase and quadrature, summed prompt accumulation 45 (FIG. 3B) and summed early-minus-late accumulation 47 (FIG. 3B) that are equivalent to what would be produced by a continuously variable sine wave. These are provided to application-specific code 15, such as conventional GPS software that executes signal tracking and navigation functions. In a second approach, software correlator 19 can generate the PRN carrier replicas on-line at the code chipping rate and can use tabulated functions to re-sample the code at the sample rate of the RF front-end for purposes of calculating accumulations. Real-time over-sampled PRN code generator 30A (FIG. 3A) is used in place of precomputed over-sampled PRN code table 28 (FIG. 3A) in this latter approach. This latter method can be used with longer PRN codes, such as the new civilian GPS L2 CL codes.

With still further reference to FIG. 1, since the received L1 raw signal 12 can have an uncertain carrier phase, software correlator 19 computes both in-phase (I) and quadrature (Q) accumulations, as defined in equations (4) and (5). Software correlator 19 begins the accumulation process by using carrier replica signal 25 (FIG. 3A), which it gets from pre-stored carrier replica table 30 (FIG. 3A). The carrier replicas in this table fall on a rough frequency grid, and they all start with a particular phase, for example a phase of zero. The baseband mixing process involves selecting a carrier replica signal 25 (FIG. 3A) from carrier replica table 30 (FIG. 3A) that is at the frequency that is as close to "ideal" as possible. In the case of a 175 Hz grid spacing, the baseband mixing process selects a signal that is maximally within ±87.5 Hz of the ideal signal. The rough frequency grid can have a spacing of, for example, 175 Hz but could be larger or smaller depending on (a) the frequency range needed to cover, for example, ±10 Khz, (b) the amount of space available for storing pre-computed signals, and (c) other design decisions. The pre-computed signals in carrier replica table 30 (FIG. 3A) each may occupy 180 32-bit words in order to be guaranteed to cover the full 5,714 RF front-end samples that occur in one PRN code period for any possible code period start time within the thirty-two samples of the initial word. Thus, 180\*4=720 bytes could be required for each bit of each pre-computed carrier replica signal 25 that is stored in the table. The sine and cosine waves of carrier replica signals 25 (FIG. 3A) each have 2-bit representations, which translates into a storage requirement of 2880 bytes for the carrier replica signals 25 at a given Doppler shift. There are 115 Doppler shifts that may be stored in order to cover the -10 KHz to +10 KHz range with a 175 Hz grid spacing. This translates into 323 Kbytes of storage for all of the carrier replica signals 25. This approach avoids the need to pre-compute sine waves with a prohibitively large number of possible frequencies and phase offsets and it avoids the need to compute sine waves in real-time. Instead, the errors created by using pre-defined sine wave replicas are compensated for by post-processing calculations, as described below.

In any case, and continuing to refer to FIG. 1, the resulting accumulations are  $\,$

$$I_{g,jk}(\Delta) = \sum_{i=i_k}^{i_k+N_k} y(t_i) C_j \left[ 0.001 \left( \frac{t_i + \Delta - \hat{\tau}_{jk}}{\hat{\tau}_{jk+1} - \hat{\tau}_{jk}} \right) \right]$$

$$\cos[(\omega_{IF} - \omega_{g,jk})(t_i - t_{0g,jk})]$$

(6)

$\sin[(\omega_{IF}-\omega_{gjk})(t_i-t_{0gjk})]$

11

$$Q_{g,jk}(\Delta) = -\sum_{i=i_k}^{i_k+N_k} y(t_i)C_j \left[ 0.001 \left( \frac{t_i + \Delta - \hat{\tau}_{jk}}{\hat{\tau}_{jk+1} - \hat{\tau}_{jk}} \right) \right]$$

$$\qquad \qquad (7) \qquad \qquad \Delta SNR = 20 \log_{10} \left( \frac{\sin(\pi \Delta f T)}{\pi \Delta f T} \right)$$

where  $\omega_{gjk}$  is the grid frequency that is closest to the estimated frequency  $\hat{\omega}_{Doppjk}$  and where  $t_{0gjk}$  is the time at which this carrier replica signal **25** (FIG. **3A**) has zero carrier phase. Software correlator **19** rotates these accumulations in order to create accurate approximations of what would have been computed had the estimated carrier phase time history in equations (4) and (5) been used:

$$I_{jk}(\Delta) = I_{gjk}(\Delta)\cos(\Delta \phi_{avgjk}) + Q_{gjk}(\Delta)\sin(\Delta \phi_{avgjk}) \tag{8}$$

$$Q_{jk}(\Delta) = -I_{gjk}(\Delta)\sin(\Delta\phi_{avgjk}) + Q_{gjk}(\Delta)\cos(\Delta\phi_{avgjk}) \tag{9}$$

where  $\Delta \phi_{avgjk}$  is the average phase difference between the 20 grid carrier phase and the estimated carrier phase averaged over the accumulation interval:

$$\Delta\phi_{avgjk} = \omega_{gjk} \left( \frac{\hat{\tau}_{jk} + \hat{\tau}_{jk+1}}{2} - t_{0gjk} \right) - \hat{\phi}_{jk} -$$

$$\hat{\omega}_{Doppjk} \left( \frac{\hat{\tau}_{jk+1} - \hat{\tau}_{jk}}{2} \right) + \omega_{IF} t_{0gjk}$$

$$(10)$$

Note that equations (8), (9), and (10) are an illustrative example of how software correlator (19) can rotate its I and Q accumulations in order to correct for phase and frequency errors in its table of pre-computed carrier replica signals. There exist other formulas that yield equivalent results, and <sup>35</sup> this patent disclosure covers all such techniques.

The validity of equations (8) and (9) is dependent on the assumption that

$$1 - \cos \left[ \frac{1}{2} (\omega_{g,ik} - \hat{\omega}_{Doppjk}) (\hat{\tau}_{jk+1} - \hat{\tau}_{jk}) \right] \ll 1$$

$$\tag{11}$$

For example, a 175 Hz grid spacing and a nominal C/A PRN 45 code period of 0.001 sec yields a value on the left-hand side of inequality (11) of 0.04, which respects the assumed limit.

Note that equations (8) and (9) can be derived from equations (4) and (5) as follows. First, the carrier phase of the grid signal in the arguments of the cosine and sine terms of equations (6) and (7) are added to and subtracted from the arguments of the cosine and sine terms in equations (4) and (5). Next, trigonometric identities are used to split the resulting cosine and sine terms into sums of products of cosine and sine functions. In each product, one of the terms involves an argument like the arguments in the trigonometric terms in equations (6) and (7). The other trigonometric terms are then approximated by either  $\cos(\Delta \Phi_{avgjk})$  or  $\sin(\Delta \Phi_{avgjk})$ . These approximations are valid because of the inequality in equation (11) and because the average of  $\sin\{(\omega_{gjk} - 60 \omega_{Doppjk})[t_i^{-1/2}(\hat{\tau}_{jk} + \hat{\tau}_{jk+1})]\}$  over the accumulation interval is

A decrease in the carrier to noise ratio  $C/N_0$ , which characterizes the receiver's sensitivity, is caused by the use of an inexact baseband mixing frequency. The worst-case decrease is expressed as a function of the frequency grid spacing  $\Delta f$  and is given by

where  $\Delta f$  is in units of Hz, and T is the integration period. Thus, a  $\Delta f$  of 175 Hz causes a worst-case C/N $_{\rm 0}$  loss of 0.11 dB for T=0.001 sec.

Referring now to FIGS. 2A, 2B, and 3A, PRN codes (composed of prompt PRN codes 29 (FIG. 3A) and earlyminus-late PRN codes 35 (FIG. 3A)) are either pre-computed or generated in real-time. Pre-computing involves, for each satellite, computing an entire PRN code, storing the 15 PRN code appropriately for easy retrieval, and referencing the PRN code, possibly by means of indices that are computed based on, for example, the incoming RF signal data 21 (FIGS. 2A and 3A). Pre-computing can be most advantageously used when the PRN code is not very long. Generating PRN codes in real-time can be a more appropriate solution when the PRN codes are very long (and thus would require an unacceptable amount of storage), or perhaps when too many PRN codes are required for the amount of storage available, or for any other reason, but real-time PRN code generation can entail an additional computational cost. Both pre-computing and real-time determination of PRN codes are described herein with respect to a bit-wise parallel implementation.

Continuing to refer primarily to FIGS. 2A, 2B, and 3A, in order to perform bit-wise parallel operations, software correlator 19 (FIG. 1) stores pre-computed carrier replica sign 25A (FIGS. 2B and 3A) and carrier replica magnitude 25B (FIGS. 2B and 3A) in data words. Simple representations of signal data 21 (FIGS. 2A and 3A) and carrier replica signal 25 (FIGS. 2B and 3A) in terms of one, two, or more bits are suitable for using bit-wise parallelism to perform the calculations described herein. Bit-wise parallel operations work with representations of the data that store successive samples in successive bits of a word. For example, thirty-40 two samples (bits) of the RF front-end output are stored in two N=32-bit words, signal sign 21A (FIGS. 2A and 3A) and signal magnitude 21B (FIGS. 2A and 3A), or simply a single 32-bit word if signal data 21 consists of a single data bit. Carrier replica sign 25A (FIGS. 2B and 3A) and carrier replica magnitude 25B (FIGS. 2B and 3A) are stored, for example in tables, in separate words, with each 32-bit word storing thirty-two sign or magnitude bits that tabulate to thirty-two successive samples of the corresponding cosine or sine wave. Similarly, tables can store prompt PRN code 29 (FIG. 3A) and early-minus-late PRN code 35 (FIG. 3A), which are composed of prompt PRN code sign 29A (FIG. 3A), early-minus-late PRN code sign 35A (FIG. 3A), and early-minus-late PRN code zero mask 35B (FIG. 3A). The data words that comprise the bit-wise parallel representations of these three signal types, the original RF signal data 21 (FIGS. 2A and 3A), the carrier replica signal 25 (FIGS. 2B and FIG. 3A), and the de-spreading prompt PRN code 29 (FIG. 3A) and early-minus-late PRN code 35 (FIG. 3A), are the inputs to the calculations of software correlator 19 (FIG.

Further continuing primarily to refer to FIGS. 2A, 2B, and 3A, many intermediate calculated quantities and at least three types of intermediate signals are also stored in bit-wise parallel format. First there are the in-phase and quadrature baseband mixed signals 23 (FIG. 3A), whose 3-bit representations for the illustrative embodiment are stored as baseband mixed sign 23A (FIG. 3A), baseband mixed high

12

magnitude 23B (FIG. 3A), and baseband mixed low magnitude 23C (FIG. 3A). The second bit-wise parallel signal type is the fully mixed integrand, of which there are four signals: in-phase and quadrature fully mixed prompt integrand 31 (FIG. 3A) and in-phase and quadrature fully mixed early-minus-late integrand 33 (FIG. 3A). The former are stored as 3-bit representations in the illustrative embodiment as fully mixed prompt integrand sign 31A (FIG. 3A), fully mixed prompt integrand high magnitude 31B (FIG. 3A), and fully mixed prompt integrand low magnitude 31C (FIG. 3A). The latter are stored as 3.5-bit representations in the illustrative embodiment as fully mixed early-minus-late integrand sign 33A (FIG. 3A), fully mixed early-minus-late integrand high magnitude 33B (FIG. 3A), fully mixed  $_{15}$ early-minus-late integrand low magnitude 33C (FIG. 3A), and fully mixed early-minus-late integrand zero mask 33D (FIG. 3A). This representation is called a 3.5-bit representation because the sign, high-magnitude, and low-magnitude bits are ignored if the corresponding zero mask bit has the 20 value zero. The third bit-wise parallel signal type is a value word, of which there are two types: prompt integrand value words 27 (FIG. 3B) and early-minus-late integrand value words 37 (FIG. 3B). Each fully mixed integrand is used to construct value words, one word for each possible value that 25 the integer integrand can take on. There are eight possible values for the integrands of the illustrative embodiment: -1, -2, -3, -6, 1, 2, 3, and 6 for the in-phase and quadrature fully mixed prompt integrands 31 (FIG. 3A) and -2, -4, -6, -12, 2, 4, 6, and 12 for the in-phase and quadrature fully mixed early-minus-late integrands 33 (FIG. 3A). Each bitwise parallel value word contains a one bit for each sample time when the integrand value equals the value of the value word, but it contains a zero bit for all other sample times. The storage of raw data and intermediate results in bit-wise parallel format allows the EXCLUSIVE OR operations that are involved in mixing to operate on thirty-two samples at a time if microprocessor 16 (FIG. 1) has a bit-wise EXCLU-SIVE OR command. Other bit-wise commands are used to 40 perform additional software correlation operations in paral-

At this point, the problem of over-sampling is introduced. Referring now to FIGS. 2C and 2D, the problem of oversampling is illustrated with respect to bit-wise parallelism as 45 follows. There is normally more than one RF data sample per PRN code chip. The three successive -1 values 73 (FIG. **2**C) at sample times  $t_1$  to  $t_3$  all occur during the same PRN code chip as do the four successive +1 values 75 (FIG. 2C) at times t<sub>4</sub> through t<sub>7</sub>. The difference in the number of 50 samples for the two code chips arises because the PRN code chip period is not an integer multiple of the sample period. Analogously, referring to FIG. 2D, where sample interval  $\Delta t$  63 is less than actual PRN code chip length  $\Delta t_c$  65, over-sampling is indicated because the RF sampling fre- 55 quency  $f_s \times 1/\Delta t_s$  is greater than the PRN code chipping frequency  $f_c=1/\Delta t_c$ . PRN codes for CDMA signaling are sequences of +1 and -1 values, the elements of which are chips. Over the time intervals of interest, a carrier replica progresses through its chips at a constant chipping rate of 60  $f_c = 1/\Delta t_c$  chips/second. The time interval  $\Delta t_c$  is the actual PRN code chip length 65 (FIG. 2D). Software correlator 19 (FIG. 1) normally receives PRN code, and attempts to align it with the prompt replica version of the code, prompt PRN code 29 (FIG. 2D). It makes use of the signal's correlation with prompt PRN code 29 (FIG. 2D) and with early-minuslate PRN code 35 (FIG. 2D) in order to determine a chipping

lel on sets of two thirty-two samples.

14

rate  $f_c$  that tends to align prompt PRN code **29** (FIG. 2D) as desired. Conventional methods for determining  $f_c$  are well-known in the art. Chips of early code **69**B (FIG. 2D) start and stop  $0.5\Delta t_{eml}$  seconds before the corresponding chips of prompt PRN code **29** (FIG. 2D), and the chips of late code **69**C (FIG. 2D) start and stop  $0.5\Delta t_{eml}$  seconds after prompt PRN code **29** (FIG. 2D). Early-minus-late PRN code **35** (FIG. 2D) is the difference between early code **69**B (FIG. 2D) and late code **69**C (FIG. 2D). Example segments of these four types of replica codes are depicted in FIG. 2D.

Referring to FIGS. 1, 2A, 2C, and 2D software correlator 19 (FIG. 1) receives, through conventional RF front end 13 and DAQ system 17, signal data 21 (FIG. 1), the raw data 12 (FIG. 1) source of which is sampled at the rate  $f_s=1/\Delta t_s$ Hz. In order to process the resulting RF signal data 21, software correlator 19 (FIG. 1) needs prompt PRN code 29 (FIG. 2D) and early-minus-late PRN code 35 (FIG. 2D) replicas sampled at the same times as raw signal 12 (FIG. 1). FIG. 2D depicts sixteen sample times as vertical dash-dotted lines. Referring to FIG. 2D, prompt PRN code 29 (FIG. 2D) can be represented by its prompt PRN code sign 29A (FIG. 2D) at the sample times. The bit value one represents +1, and the bit value zero represents -1. Prompt PRN code sign 29A (FIG. 2D), shown at the sixteen sample times—starting with three 1s, continuing with ten 0s, and finishing with another three 1s-is a 16-bit word stored as the integer  $2^{15}+2^{14}+2^{13}+2^2+2^1+2^0=57351$ . Early-minus-late PRN code 35 (FIG. 2D) requires a 1.5-bit representation. A zero mask bit is set to zero if early-minus-late PRN code 35 takes on the value zero, and it is set to one if early-minus-late PRN code 35 equals +2 or -2. Early-minus-late PRN code zero mask 35B (FIG. 2D) at sixteen sample times shown in FIG.  $^{35}$  2D is equivalent to  $2^{13}+2^{12}+2^2=12292$ . A 2's sign bit is set to one if early-minus-late PRN code 35 (FIG. 2D) equals +2 at the sample time, and it is set to zero if the code equals -2. The 2's sign bit is irrelevant if the corresponding earlyminus-late PRN code zero mask 35B (FIG. 2D) bit equals zero. Early-minus-late PRN code sign 35A (FIG. 2D) for sixteen sample times contains X values that indicate bits whose values are irrelevant because the corresponding earlyminus-late PRN code zero mask 35B (FIG. 2D) bits are zero. In an illustrative embodiment, all the X values become zero, thus the equivalent integer for early-minus-late PRN code sign **35**A (FIG. **2**D) is  $2^2=4$ .

Continuing to refer to FIG. 3A, an alternative to taking the prompt PRN code 29 and early-minus-late PRN code 35 from pre-computed over-sampled PRN code table 28 is to generate prompt PRN code sign 29A, early-minus-late PRN code sign 35A, and early-minus-late PRN code zero mask 35B using real-time over-sampled PRN code generator 30A (FIG. 3A). Shown in FIG. 3A are two circles and a loose arrow with a quarter circle pointer. These are the symbols for a switch and indicate the ability of the system to choose possible alternate sources of PRN code. Using the real-time over-sampled PRN code generator 30A includes a step of generating the PRN code chips in real-time by conventional means. For example, the GPS civilian L2 CL and CM codes are generated by a 27-bit feedback shift register (see The New L2 Civil Signal, R. D. Fontana et al., Proceedings of the ION GPS 2001, Sep. 11–14, 2001, Salt Lake City, Utah, pp. 617–631). The method further includes the steps of choosing chip values from the PRN code, where the chip values correspond to a data interval that contains the samples of a data word and where the chips have a known timing relative to the data interval, transforming the relative timing into a

time grid index, and translating the PRN code chip values and the time grid index for the data interval into the PRN code's over-sampled bit-wise parallel format. These latter steps can be carried out efficiently by using a table look up function. One table each for prompt PRN code sign 29A, 5 early-minus-late PRN code sign 35A, and early-minus-late PRN code zero mask 35B can include integer values that constitute the bit-wise parallel representation of the PRN code for the sample times associated with the data word in question. Indices into each 1-dimensional table are functions 10 of (a) the time offset between the first PRN code chip and the first sample time of the given data word, and (b) the bit pattern of the PRN code chips that span the sample times of the data word. The sizes of the tables are independent of the period of the PRN code that is being over-sampled. The 15 tables can be re-used for multiple PRN codes in a multi-

channel receiver. The computation and use of the tables are

discussed in more detail later.

Continuing with the description of bit-wise parallelism with respect to the operations of software correlator 19 (FIG. 20 1), and continuing to refer to FIG. 3A, the speciallydeveloped algorithms described herein make use of bit-wise parallelism so that a single programming language statement, such as a C code command, can partially process up to thirty-two samples at a time. Previously referred-to carrier 25 replica signal 25 in the form of cosine and sine signals are stored as binary carrier replica sign 25A and carrier replica magnitude 25B. The format of this representation is defined in Table 2 and illustrated in FIG. 3C which is a reconstructed carrier and carrier replica in the form of representative sine 30 signal 51 (FIG. 3C) shown in optimal 2-bit representation 53 (FIG. 3C) that has the minimum square error. The format of Table 2 assumes that the cosine and sine signals have an amplitude of approximately 2.4. Note that other representations, beyond 2-bit representation, are possible. In general, 35 more bits yield a better SNR, but can also require a larger number of computations for the correlation operations.

TABLE 2

| Sign and magnitude combinations of the st | ored intermediate- |

|-------------------------------------------|--------------------|

| frequency baseband mixing carrier sine    | wave replicas      |

| and the values that they repre            | sent               |

| Carrier Replica Sign<br>25A | Carrier Replica<br>Magnitude 25B | Carrier Replica Value |

|-----------------------------|----------------------------------|-----------------------|

| 0                           | 0                                | -1                    |

| 0                           | 1                                | -2                    |

| 1                           | 0                                | +1                    |

| 1                           | 1                                | +2                    |

Continuing to refer to FIG. 3A, multiplication of the RF front-end output representation, the signal sign 21A and signal magnitude 21B, of Table 1 by the sine wave representation, carrier replica sign 25A and carrier replica magnitude 25B, of Table 2 yields baseband mixed signals 23, 55 consisting of baseband mixed sign 23A, baseband mixed high magnitude 23B, and baseband mixed low magnitude **23**C, that can take on the values -6, -3, -2, -1, +1, +2, +3, and +6, as shown in Table 3. Baseband mixed high magnitude 23B is simply signal magnitude 21B, and baseband 60 mixed low magnitude 23C is carrier replica magnitude 25B. Thus, these two magnitude bits are available without the need for computation. Baseband mixed sign 23A is the result of an EXCLUSIVE OR operation between signal sign 21A and carrier replica sign 25A. Notice how the relationship of the sign bit value with the actual sign gets reversed from that of Tables 1 and 2.

TABLE 3

| Sign, | high-magnitude, and low-magnitude combination | ns |

|-------|-----------------------------------------------|----|

|       | of the baseband-mixed signal and their        |    |

|       | corresponding signal values.                  |    |

|   | Baseband<br>Mixed Sign<br>23A | Baseband Mixed<br>High Magnitude<br>23B | Baseband Mixed<br>Low Magnitude<br>23C | Baseband Mixed<br>Value |

|---|-------------------------------|-----------------------------------------|----------------------------------------|-------------------------|

| _ | 0                             | 0                                       | 0                                      | +1                      |

|   | 0                             | 0                                       | 1                                      | +2                      |

|   | 0                             | 1                                       | 0                                      | +3                      |

|   | 0                             | 1                                       | 1                                      | +6                      |

|   | 1                             | 0                                       | 0                                      | -1                      |

|   | 1                             | 0                                       | 1                                      | -2                      |

|   | 1                             | 1                                       | 0                                      | -3                      |

|   | 1                             | 1                                       | 1                                      | -6                      |

Continuing to refer to FIG. 3A, and continuing to describe the bit-wise parallel algorithms, the required amount of storage for tables of pre-computed prompt PRN code 29 and early-minus-late PRN code 35 can be greatly reduced by making two simplifications. First, the prompt PRN code 29 is stored as prompt PRN code sign 29A. This representation is shown in Table 4. The early-minus-late PRN code 35, on the other hand, is stored in a two-bit representation (actually a 1.5 bit representation): early-minus-late PRN code sign 35A and early-minus-late PRN code zero mask 35B, as denoted in Table 5. Note that the X in the first column of Table 5 indicates that zero or one can be placed in this location without affecting the corresponding code value. The X signifies a lack of effect of the sign bit on the code value when the zero mask bit equals zero. This is why the early-minus-late PRN code 35 representation is referred to as a 1.5-bit representation. This X value will affect the corresponding fully mixed early-minus-late integrand sign 33A, but it will not affect any of the early-minus-late value words because the zero value in the corresponding zero mask location will null out the corresponding bit of all early-minus-late value words.

TABLE 4

| Sign bits of the prompt C/A of prompt sign |                   |

|--------------------------------------------|-------------------|

| Prompt PRN Code<br>Sign 29A                | Prompt Code Value |

| 1                                          | +1<br>-1          |

### TABLE 5

Sign and zero mask bit combinations of the early-minus-late PRN code 35 and the corresponding signal values.

|   | Early-minus-late PRN<br>Code Zero Mask 35B | Early-Minus-Late Code<br>Value |

|---|--------------------------------------------|--------------------------------|

| X | 0                                          | 0                              |

| 0 | 1                                          | -2                             |

| 1 | 1                                          | +2                             |

Another simplification in the pre-computed over-sampled PRN code table 28, and continuing to refer to FIG. 3A, can be to ignore code Doppler shift variations. All signals in the table are assumed to have zero Doppler shift; i.e., all C/A codes in the table assume that  $\hat{\tau}_{jk+1} - \hat{\tau}_{jk} = 0.001$  sec. Note that the period of 0.001 is applicable for accumulations that use

the full 1023 chips of the C/A code only. Any other type of code or accumulation interval may have a different period. The code phase errors due to this assumption can be eliminated by choosing a replica code from the pre-computed over-sampled PRN code table 28 whose midpoint occurs at 5 the desired midpoint time  $(\hat{\tau}_{ik} + \hat{\tau}_{ik+1})/2$ . The only other effect of this assumption can be a small correlation power loss, which is no more than 0.014 dB if the magnitude of the Doppler shift is less than 10 KHz. The pre-computed oversampled PRN code table 28 should include a selection of 10 different phases, for example fourteen, as measured relative to a signal sample spacing of, for example, 175 nsec. This translates into a code phase spacing of, for example, 12.5 nsec, which equals a pseudo range measurement digitization level of 3.8 m, or a maximum measurement error of 1.9 m. 15 The number of phases in the pre-computed over-sampled PRN code table 28 is dependent upon the design of the system and no set number of phases is required by the present invention. Referring to FIG. 6, suppose that precomputed over-sampled PRN code table 28 stores over- 20 sampled bit-wise parallel representations of chips C(1) through C(M). The table must allow for the retrieval of over-sampled bit-wise parallel code replicas for a range of start times of code chip C(1) that span the entire first data sample word in the accumulation interval  $W_1$  95 (FIG. 6). <sup>25</sup> The table may contain code replicas whose different phases yield start times that span only a single sample interval of data word W<sub>1</sub> 95 (FIG. 6), which is only  $1/n_s$  of the required number of start times. In this case the software correlator may apply bit shift operations to a tabulated PRN code 30 replica from that sample interval in order to generate the over-sampled bit-wise parallel PRN code replica that applies when chip C(1) starts in a different sample interval of data word  $W_1$  95 (FIG. 6).

Continuing to refer to FIG. 3A, and further continuing to 35 describe the bit-wise parallel algorithms, prompt PRN code 29 and early-minus-late PRN code 35 replicas can be mixed with the baseband mixed signals 23 to form fully mixed prompt integrand 31 by an EXCLUSIVE OR operation and bit re-definitions. An EXCLUSIVE OR between prompt PRN code sign 29A and baseband mixed sign 23A produces fully mixed prompt integrand sign 31A given in Table 6. The fully mixed prompt integrand high magnitude 31B and fully mixed prompt integrand low magnitude 31C are baseband mixed high magnitude 23B and baseband mixed low magnitude 23C, also given in Table 6. Note that the Table 6 representation is identical to that of Table 3 except for the inversion in the meaning of the sign bits. The number of magnitude bits is dependent upon the design of the system and no set number of magnitude bits is required by the present invention. A change in the number of magnitude bits will cause a change in the number of entries of the equivalent of Table 6 and it will affect the possible values of the integrand.

TABLE 6

Sign, high-magnitude, and low-magnitude bit combinations of the fully

| Fully Mixed Prompt Integrand Sign 31A | Fully Mixed Prompt Integrand High Magnitude 31B | Fully Mixed Prompt Integrand L w Magnitude 31C | Fully Mixed Prompt Integrand Value |

|---------------------------------------|-------------------------------------------------|------------------------------------------------|------------------------------------|

| 0                                     | 0                                               | 0                                              | -1                                 |

| 0                                     | 0                                               | 1                                              | -2                                 |

| 0                                     | 1                                               | 0                                              | -3                                 |

TABLE 6-continued

Sign, high-magnitude, and low-magnitude bit combinations of the fully mixed prompt integrand 31 and its corresponding values.

| Fully Mixed<br>Prompt<br>Integrand Sign<br>31A | Fully Mixed Prompt<br>Integrand High<br>Magnitude 31B | Fully Mixed<br>Prompt<br>Integrand L w<br>Magnitude 31C | Fully Mixed<br>Prompt<br>Integrand<br>Value |

|------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|

| 0                                              | 1                                                     | 1                                                       | -6                                          |

| 1                                              | 0                                                     | 0                                                       | +1                                          |

| 1                                              | 0                                                     | 1                                                       | +2                                          |

| 1                                              | 1                                                     | 0                                                       | +3                                          |

| 1                                              | 1                                                     | 1                                                       | +6                                          |

Still continuing to refer to FIG. 3A, the mixing of the early-minus-late PRN code 35 with the baseband mixed signals 23 forms fully mixed early-minus-late integrands 33. Fully mixed early-minus-late integrand sign 33A is an EXCLUSIVE OR between early-minus-late PRN code sign 35A and baseband mixed sign 23A. Fully mixed early-minus-late integrand high magnitude 33B and fully mixed early-minus-late integrand low magnitude 33C are, as above, baseband mixed high magnitude 23B and baseband mixed low magnitude 23C. Fully mixed early-minus-late integrand zero mask 33D is early-minus-late PRN code zero mask 35B. The resulting representation is given in Table 7. As in Table 5, each X entry in the table indicates that the corresponding bit can be either zero or one without affecting the corresponding integrand value.

TABLE 7

Sign, high-magnitude, low-magnitude, and zero mask bit combinations of the fully mixed early-minus-late integrands 33 and their corresponding values.

| Early-Minus-<br>Late (EML)<br>Integrand<br>Sign 33A | EML<br>Integrand<br>High<br>Magnitude<br>33B | EML<br>Integrand<br>Low<br>Magnitude<br>33C | EML<br>Integrand<br>Zero Mask<br>33D | Early-<br>Minus-Late<br>Integrand<br>Value |

|-----------------------------------------------------|----------------------------------------------|---------------------------------------------|--------------------------------------|--------------------------------------------|

| X                                                   | X                                            | X                                           | 0                                    | 0                                          |

| 0                                                   | 0                                            | 0                                           | 1                                    | -2                                         |

| 0                                                   | 0                                            | 1                                           | 1                                    | -4                                         |

| 0                                                   | 1                                            | 0                                           | 1                                    | -6                                         |

| 0                                                   | 1                                            | 1                                           | 1                                    | -12                                        |

| 1                                                   | 0                                            | 0                                           | 1                                    | +2                                         |

| 1                                                   | 0                                            | 1                                           | 1                                    | +4                                         |