#### REAL TIME VIDEO STITCHING IMPLEMENTATION ON A ZYNQ FPGA SOC

By

#### Dhimiter Qendri, B.Eng , University Of Ontario Institute of Technology 2017

A Major Research Project

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Engineering

in the program of

Electrical and Computer Engineering

© Dhimiter Qendri, Toronto, Ontario, Canada 2019

#### Declaration of Authorship

I hereby declare that I am the sole author of this MRP. This is a true copy of the MRP, including any required final revisions.

I authorize Ryerson University to lend this MRP to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this MRP by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my MRP may be made electronically available to the public.

#### REAL TIME VIDEO STITCHING IMPLEMENTATION ON A ZYNQ FPGA SOC

#### DHIMITER QENDRI

Master of Engineering

#### Electrical and Computer Engineering Ryerson University

2019

### Abstract

This project details the design and implementation of an image processing pipeline that targets real time video-stitching for semi-panoramic video synthesis. The scope of the project includes the analysis of possible approaches, selection of processing algorithms and procedures, design of experimental hardware set-up (including the schematic capture design of a custom catadioptric panoramic imaging system) and firmware/software development of the vision processing system components. The goal of the project is to develop a frame-stitching IP module as well as an efficient video registration algorithm capable for synthesis of a semi-panoramic video-stream at 30 frames-per-second (fps) rate with minimal FPGA resource utilization. The developed components have been validated in hardware. Finally, a number of hybrid architectures that make use of the synergy between the CPU and FPGA section of the ZYNQ SoC have been investigated and prototyped as alternatives to a complete hardware solution.

#### Keyword: Video stitching, Panoramic vision, FPGA, SoC, vision system, registration

# Table of Contents

## Contents

| List of Tables vii                     |

|----------------------------------------|

| List of Figures viii                   |

| List of Acronyms xi                    |

| Chapter 1 Panoramic vision             |

| 1 Introduction                         |

| 1.1 Objective                          |

| 1.2 Motivation                         |

| 1.3 Tasks                              |

| 1.4 Panoramic Imaging                  |

| 1.5 Project Organization               |

| Chapter 2 Related works                |

| 2 Panoramic Imaging                    |

| 2.1 Problem Analysis                   |

| 2.2 Publications                       |

| 2.3 Patents 10                         |

| 2.4 Feature based methods              |

| 2.4.1 SIFT                             |

| 2.4.2 SURF                             |

| 2.4.3 Harris Corner detector           |

| 2.5 Feature based stitching algorithms |

| 2.6 Design decisions                   |

| Chapter 3 Proposed approach            |

| 3 Proposed Approach 17                 |

|    | 3.1 2                                                     | YNQ SOC Overview                                                                                                                                                                                                    | 17                                                                                                                                 |

|----|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|    | 3.2 I                                                     | roposed Hardware                                                                                                                                                                                                    | 17                                                                                                                                 |

|    | 3.3 I                                                     | xternal peripherals                                                                                                                                                                                                 | 20                                                                                                                                 |

|    |                                                           | 3.1 Camera sensors.                                                                                                                                                                                                 | 20                                                                                                                                 |

|    |                                                           | 3.2 WIFI BLE module                                                                                                                                                                                                 | 20                                                                                                                                 |

|    |                                                           | 3.3 VGA DAC                                                                                                                                                                                                         | 20                                                                                                                                 |

|    |                                                           | 3.4 USB                                                                                                                                                                                                             | 20                                                                                                                                 |

|    |                                                           | 3.5 JTAG and Serial Port                                                                                                                                                                                            | 21                                                                                                                                 |

|    | 3.4 \$                                                    | ystem BOOT                                                                                                                                                                                                          | 21                                                                                                                                 |

|    | 3.5 I                                                     | xperimental Setup                                                                                                                                                                                                   | 22                                                                                                                                 |

|    | 3.6 I                                                     | roposed Algorithm                                                                                                                                                                                                   | 25                                                                                                                                 |

|    | 3.7 \$                                                    | eam index identification                                                                                                                                                                                            | 26                                                                                                                                 |

|    |                                                           |                                                                                                                                                                                                                     | ~7                                                                                                                                 |

|    | 3.8                                                       | utomatic seam detection algorithm                                                                                                                                                                                   | 27                                                                                                                                 |

|    |                                                           | utomatic seam detection algorithm                                                                                                                                                                                   |                                                                                                                                    |

|    | 3.9 I                                                     |                                                                                                                                                                                                                     | 30                                                                                                                                 |

|    | 3.9 I<br>3.10I                                            | ectification                                                                                                                                                                                                        | 30<br>31                                                                                                                           |

|    | 3.9 I<br>3.10I                                            | ectification                                                                                                                                                                                                        | <ul><li>30</li><li>31</li><li>31</li></ul>                                                                                         |

|    | 3.9 I<br>3.10I                                            | ectification<br>roposed firmware modules<br>10.1 Camera controller                                                                                                                                                  | <ul><li>30</li><li>31</li><li>31</li><li>32</li></ul>                                                                              |

|    | 3.9 I<br>3.10I                                            | ectification<br>roposed firmware modules<br>10.1 Camera controller<br>10.2 Line Buffer                                                                                                                              | <ol> <li>30</li> <li>31</li> <li>31</li> <li>32</li> <li>32</li> </ol>                                                             |

|    | 3.9 I<br>3.10I                                            | ectification<br>roposed firmware modules<br>10.1 Camera controller<br>10.2 Line Buffer<br>10.3 Sobel Filter                                                                                                         | <ol> <li>30</li> <li>31</li> <li>31</li> <li>32</li> <li>32</li> <li>32</li> </ol>                                                 |

|    | 3.9 I<br>3.10I                                            | ectification<br>roposed firmware modules<br>10.1 Camera controller<br>10.2 Line Buffer<br>10.3 Sobel Filter<br>10.4 Seam identification IP                                                                          | <ul> <li>30</li> <li>31</li> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> </ul>                         |

|    | 3.9 I<br>3.10I                                            | ectification<br>roposed firmware modules<br>10.1 Camera controller<br>10.2 Line Buffer<br>10.3 Sobel Filter<br>10.4 Seam identification IP<br>10.5 Rectification IP                                                 | <ul> <li>30</li> <li>31</li> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> </ul>                         |

|    | 3.9 I<br>3.10I<br>3<br>3<br>3<br>3<br>3.110               | ectification<br>roposed firmware modules<br>10.1 Camera controller<br>10.2 Line Buffer<br>10.3 Sobel Filter<br>10.4 Seam identification IP<br>10.5 Rectification IP<br>10.6 Image Stitching                         | <ul> <li>30</li> <li>31</li> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> </ul>                         |

| CI | 3.9 I<br>3.10I<br>3<br>3<br>3<br>3<br>3.110<br>3.120      | ectification<br>roposed firmware modules<br>10.1 Camera controller<br>10.2 Line Buffer<br>10.3 Sobel Filter<br>10.4 Seam identification IP<br>10.5 Rectification IP<br>10.6 Image Stitching<br>penCV Implementation | <ul> <li>30</li> <li>31</li> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> </ul>             |

|    | 3.9 I<br>3.10I<br>3<br>3<br>3<br>3.110<br>3.120<br>napter | ectification                                                                                                                                                                                                        | <ul> <li>30</li> <li>31</li> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>37</li> </ul> |

| 4.2 Camera module                      | 38 |

|----------------------------------------|----|

| 4.2.1 Camera Configuration             | 39 |

| 4.2.2 Pixel parsing                    | 41 |

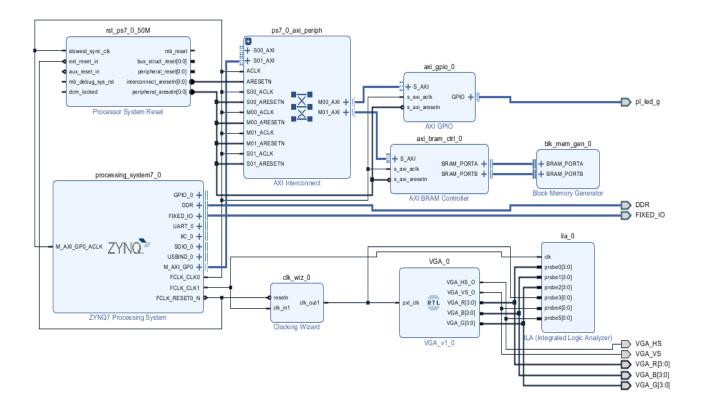

| 4.3 VGA Module                         | 43 |

| 4.4 Camera Testing                     |    |

| 4.5 PS implementation                  | 53 |

| 4.6 Image stitching IP                 | 56 |

| 4.7 Automatic seam registration        | 59 |

| 4.7.1 Sobel filter                     | 60 |

| 4.8 Key-point detector                 | 61 |

| Chapter 5 Analysis                     | 63 |

| 5 Analysis of results                  | 63 |

| 5.1 Performance analysis               | 63 |

| 5.2 Image Stitching IP                 | 63 |

| 5.3 VGA                                | 65 |

| 5.4 Seam identification HDL modules    | 66 |

| 5.4.1 Line buffer                      | 66 |

| 5.4.2 Sobel Filter                     | 68 |

| 5.5 Key-point detector                 | 69 |

| 5.6 Comparison with OpenCV stitching   |    |

| 5.6.1 Comparison with streaming method |    |

| Chapter 6 Summary                      | 71 |

| 6. Project summary                     | 71 |

| References                             | 74 |

# List of Tables

| Fable 3-1 Frame stitching execution time           | 35 |

|----------------------------------------------------|----|

| Fable 4-1 OV7670 Camera sensor resolutions and FPS | 38 |

| Fable 4-2 OV7670 Camera pinout interface           | 40 |

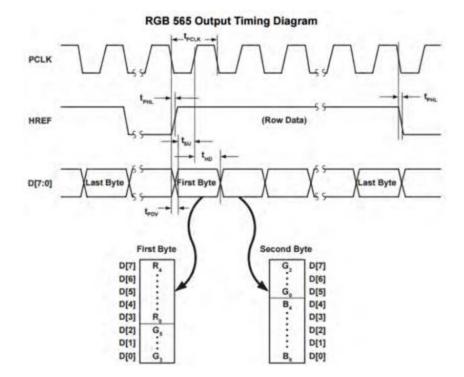

| Fable 4-3 First byte during first cycle            | 42 |

| Fable 4-4 Second byte during first cycle    4      | 42 |

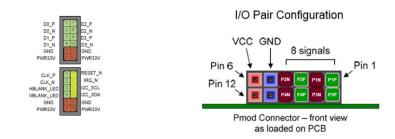

| Fable 4-5 J4 PMOD on Minized                       | 44 |

| Fable 4-6 J5 PMOD on Minized                       | 45 |

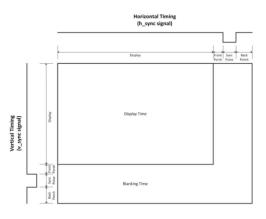

| Fable 4-7 VGA resolution parameters                | 46 |

| Fable 4-8 Image stitching IP interface             | 58 |

# List of Figures

| Figure 2-1 Algorithm only operating on tiles                                    | 16 |

|---------------------------------------------------------------------------------|----|

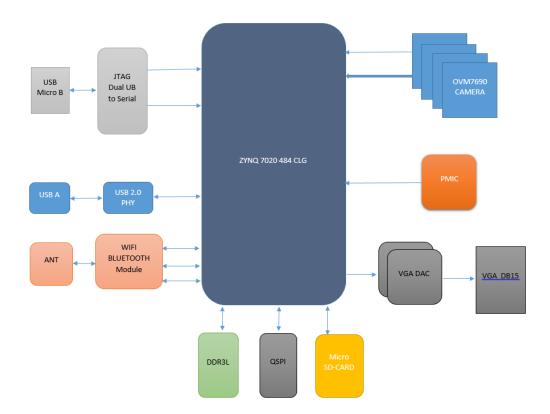

| Figure 3-1 Proposed block diagram of the custom hardware platform               | 18 |

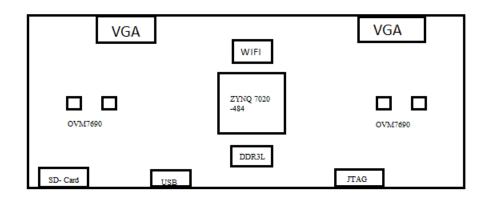

| Figure 3-2 Proposed placement for designed hardware                             | 21 |

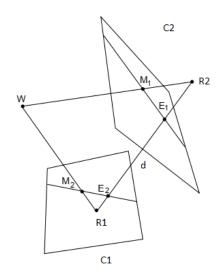

| Figure 3-3 General case for epipolar projection                                 | 22 |

| Figure 3-4 Simplified case of epipolar projection for lab setup                 | 23 |

| Figure 3-5 Catadioptric optical system for panoramic imaging                    | 24 |

| Figure 3-6 Two sample image matrices (1 left, 2 right) with overlapping columns | 28 |

| Figure 3-7 Stitched images                                                      | 28 |

| Figure 3-8 Calculated bins for each operation                                   | 29 |

| Figure 3-9 Determining seam index by Euclidean norm                             | 29 |

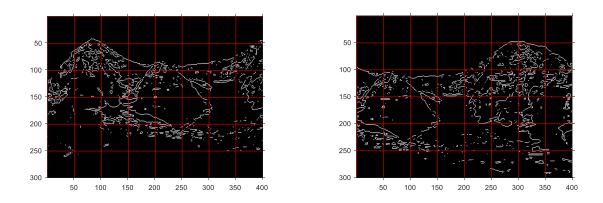

| Figure 3-10 Unrectified Sobel filtered adjacent frames                          | 30 |

| Figure 3-11 Two different perspective images of the same scene                  | 34 |

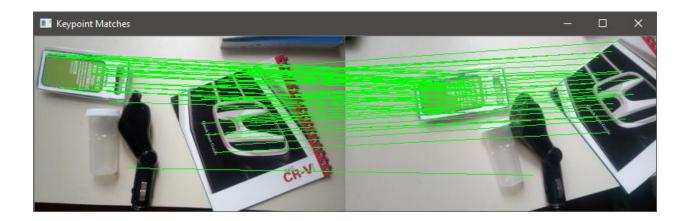

| Figure 3-12 Matching features with SIFT                                         | 35 |

| Figure 3-13 Synthesized panoramic image                                         | 35 |

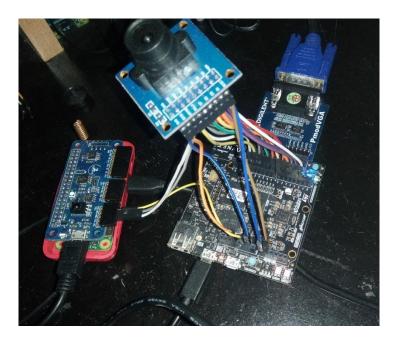

| Figure 4-1 Vision processing hardware setup                                     | 37 |

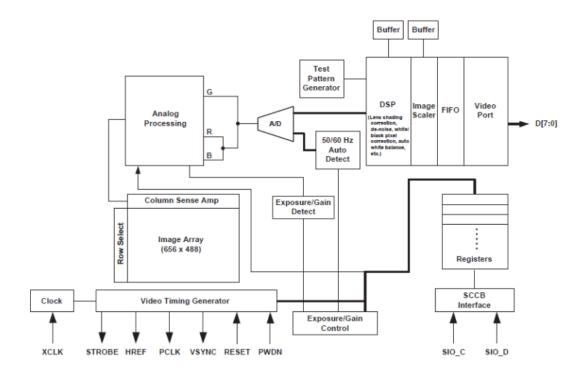

| Figure 4-2 OV7670 camera module                                                 | 38 |

| Figure 4-3 Functional Block diagram of the camera sensor                        | 41 |

| Figure 4-4 Data transmission of a single pixel RGB565 pixel data                | 43 |

| Figure 4-5 PMOD VGA interface connector                                         | 44 |

| Figure 4-6 VGA timing diagram                                                   | 46 |

| Figure 4-7 VGA setup with a test pattern and ILA                      |    |

|-----------------------------------------------------------------------|----|

| Figure 4-8 OV7670 Camera to VGA setup                                 | 49 |

| Figure 4-9 Logic analyzer data for OV7670 camera input capture module | 49 |

| Figure 4-10 Logic analyzer output for VGA module operation.           | 50 |

| Figure 4-11 OV7670 Camera to QVGA with soft IIC                       | 51 |

| Figure 4-12 Testing the camera interface.                             | 52 |

| Figure 4-13 OV7670 camera capture settings                            | 52 |

| Figure 4-14 Changing the gamma, brightness and saturation settings    | 53 |

| Figure 4-15 Simplified version of the VDMA system                     | 54 |

| Figure 4-16 Testing VDMA to VGA with video test pattern generator     | 55 |

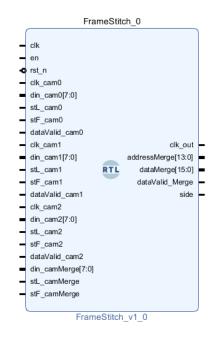

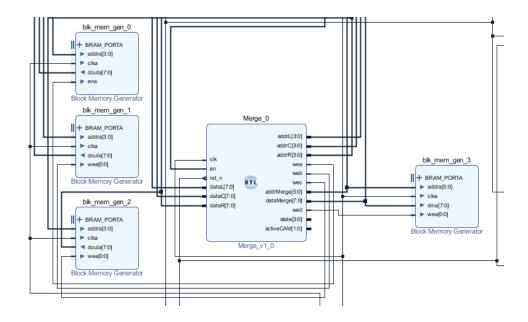

| Figure 4-17 Image stitching module                                    | 56 |

| Figure 4-18 Test setup for image stitching IP                         | 57 |

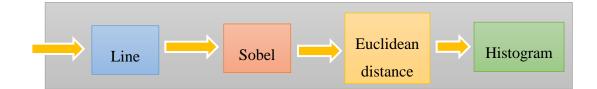

| Figure 4-19 Block diagram for automatic seam registration             | 60 |

| Figure 4-20 Line buffer interface                                     | 60 |

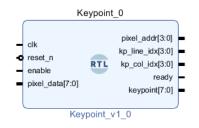

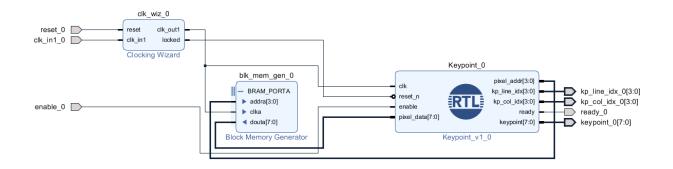

| Figure 4-21 Key-point detector interface                              | 62 |

| Figure 5-1 Frame stitching core interface                             | 64 |

| Figure 5-2 Simulation of core stitching IP                            | 65 |

| Figure 5-3 Resource utilization of frame stitching core IP            | 65 |

| Figure 5-4 Resource Utilization of VGA IP                             | 66 |

| Figure 5-5 Simulation of line buffer module                           | 67 |

| Figure 5-6 Simulation of line buffer module (continued)         | 67 |

|-----------------------------------------------------------------|----|

| Figure 5-7 Resource utilization of the synthesized line buffer. | 68 |

| Figure 5-8 Resource utilization of Sobel.                       | 68 |

| Figure 5-9 Test setup for basic key-point detector              | 69 |

| Figure 5-10 Test bench results                                  | 69 |

| Figure 5-11 Resource usage for Key point detector               | 70 |

# List of Acronyms

| ASIC | Application Specific Integrated Circuit |

|------|-----------------------------------------|

| ADAS | Advanced Driver Assistance System       |

| APU  | Application Processor Unit              |

| AXI  | Advanced eXtensible Interface           |

| BRAM | Block Random Access Memory              |

| DAC  | Digital Analog Converter                |

| DOG  | Difference of Gaussians                 |

| DDR  | Double Data Rate                        |

| EMIO | External Multiplexed Input /Output      |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| FIFO | First in First Out                      |

| FPGA | Field Programmable Gate Array           |

| FMC  | FPGA Mezzanine Connector                |

| FOV  | Field of View                           |

| FSBL | First Stage Boot loader                 |

| HDL  | Hardware description Language           |

| HLS  | High Level Synthesis                    |

| I2C  | Inter Integrated Circuit                |

| ILA  | Integrated Logic Analyzer               |

| I/O  | Input / Output                       |

|------|--------------------------------------|

| JTAG | Joint Test Access Group              |

| LDO  | Linear Drop-Out Regulator            |

| LED  | Light Emitting Diode                 |

| LSB  | Least Significant Bits               |

| LUT  | Look Up Table                        |

| MIO  | Multiplexed Input / Output           |

| MPU  | Micro Processor Unit                 |

| MP   | Mega Pixels                          |

| HDMI | High-Definition Multimedia Interface |

| SIFT | Scale Invariant Feature Transform    |

| SURF | Speeded up robust features           |

| SPI  | Serial Peripheral Interface          |

| SoC  | System on Chip                       |

| РСВ  | Printed Circuit Board                |

| PS   | Processing System                    |

| PL   | Programable Logic                    |

| PWM  | Pulse Width Modulation               |

| РНҮ  | Physical Layer Interface             |

| PMU  | Power Management Unit                |

- TRM Technical Reference Manual

- RANSAC Random sample consensus

- VGA Video Graphic Array

- VDMA Video Direct Memory Access

- XADC Xilinx Analog to Digital Converter

## Chapter 1 Panoramic vision

Machine vision is the capability of embedded systems with image sensors to extract useful information from acquired image parameters such as depth, color, 3D shape and geometric information in general. To extract the maximum amount of information from a scene, the vision system needs to have a wide field of view hence the need for panoramic imaging systems. This project focuses on the implementation and design of a real time video stitching system with semi-panoramic imaging capabilities.

# 1 Introduction

## 1.1 Objective

The main objective of this project is to explore the technical problems and find an efficient implementation of run time video image stitching from multiple camera sensors. The goal of the project is to implement on the fly merging of video streams from separate video sensors at a high frame rate in order to allow for real time tracking. The main challenges addressed in the implementation stage are the schematic capture design of a custom hardware platform with hyper-stereoscopic panoramic video capabilities, the design of custom HDL IP that implements run time video frame stitching as well as the design of IP modules used for automatic image registration which includes both rectification and seam identification.

## 1.2 Motivation

Panoramic image stitching has several commercial applications in diverse fields such as medical imaging, astrophotography, architecture, robotics, industrial inspection, advance driver assistance systems (ADAS) and of course in panoramic photography and film. Panoramic image mosaicking has already become a default feature on current mobile OS camera software.

Wide angle semi-panorama creation is based on image stitching. Image stitching is the process of taking a number of images from different perspectives, transforming them so that the same objects on all the images align with each other and then overlapping the images in such a way as to form a panorama based on the number of different perspectives of the same scene. The main issue faced when implementing image stitching is how to effectively remove the misalignments due to parallax which results in visible image feature duplication as well as aligning the adjacent images in such a manner so that there is no visible seam along the boundary between the two images.

Vision processing systems work with specific frame rates subject to requirements of response time. The response time is defined as the time interval to react to an external stimulus. The response time is directly linked with the camera sensor frame rate which is an intrinsic property of the sensor. The camera sensors used on this project allow the frame rate to be changed based on the selected resolution.

The requirements for the reaction time depend directly on system constrains such as the platform moving speed, the reaction time of any transducer interfaced with the vision system and the execution time of the image processing algorithms. To maximize the reaction time, the algorithm execution time has to be kept to a minimum.

The vision system pipeline makes use of CMOS camera sensors that incorporate a DSP image processing engine. These sensors are provided either with external optics or with integrated optics. The camera lens determines the optical properties of the sensors. The lens purpose is to focus the lights that is reflected or emitted from the object under the FOV. This light forms the image in the camera sensor. The lens size determines the FOV and the working distance.

The main limitation of current imaging systems is that most camera sensors have a very limited field of view which is typically 55-65 degrees. While there exist special optical imaging platforms with much wider field of view such setups are expensive and suffer from astigmatism. This incurs deformations on the acquired images which have to be fixed either by additional optics or by adding further steps in the image processing pipeline thereby decreasing reaction time.

To solve the issue of limited FOV as well as minimize reaction time one needs to implement an image stitching algorithm that executes fairly fast with regards to system reaction time in order to meet real time requirements. In general, this requires making use of hardware implementations which can parallelize calculations to speed up execution delays.

#### 1.3 Tasks

The difference between a video imaging system and a vison system is that the former contains no image processing. Vision systems on the other hand extract information from the acquired image frames and find sense from them. This in effect requires integrating an algorithm in the image processing pipeline. The main task of this project is the implementation of a vision image processing pipeline capable of run time stitching of video frames at 30 frames per second.

The primary task of the project was the implementation of a custom IP that receives the individual video streams from each camera and implements run time video stream stitching.

The second task was the schematic capture design of a custom hardware platform centered on the ZYNQ 7020 SOC. The platform main novelty is the implementation of a custom catadioptric system consisting of four separate cameras together with a mirror assembly forming a hyper-stereoscopic imaging system.

The third project task was the investigation and implementation of automatic image registration algorithm using a mixed approach by using a hybrid intensity and features-based approach. The main challenge of this task was the development of the algorithms for identification of correspondence points between adjacent image features. The registration process consists of image rectification and seam identification. For each of these steps a number of custom HDL IP modules were implemented. The simulation of each module as well as the Verilog code are included in Appendix A. The last task was the analysis of the developed modules.

## 1.4 Panoramic Imaging

The imaging systems are generally classified as active or passive. Passive imaging systems make use only of passive optical sensors and elements such as mirrors and lenses. Active imaging systems on the other side make use of active elements such as projectors, collimated light sources and active light sources. Active stereo system includes structured light systems which make use of a single projector and camera or time of flight systems make use of a

collimated light source such as a laser and a monocular camera. The imaging systems in this project fall under the passive systems since no use is made of any active light sources.

There exists a multitude of methods for creating panoramic images. These systems can be categorized on the number of imaging sensors they use; such as monocular cameras, stereoscopic cameras, hyper-stereoscopic cameras and so on.

Panoramic cameras in themselves are classified in two main categories, dioptric and catadioptric. Dioptric imaging systems use only refractive elements such as lenses. This includes rotating cameras, fish-eye based cameras and camera clusters. Catadioptric systems make use of single curved mirrors or flat mirrors paired with multiple cameras.

Current smartphone monocular camera systems support the creation of panoramic images by implementing on the fly software stitching of the acquired image. This requires that the user manually moves the camera in the direction of the panorama. A similar setup can be automated by using a motorized approach to manual movement. This approach however reduces the reaction time as well as the system reliability. In addition, it adds a host of other issues such as the need for image stabilization due to motion jitter.

As such preference is given to a catadioptric static imaging platforms that make use of multiple video sensors and reflective elements. Integration of mirrors in the optical setup increases the limited field of view of the camera sensors. If placed strategically, mirror elements can also simplify the algorithmic complexity of the system.

Recovering spatial information from a single 2D image is in general an ill-posed problem mathematically. To aid in the recovery of depth information stereo systems make use of the differences in between image key-point features on the same view in order to infer a depth disparity map. Inferring depth from a monocular camera is challenging so multiple camera sensor are needed.

Passive panoramic stereo systems use two monocular cameras to infer a depth map from difference in parallax. The setup of a stereo machine vision includes two cameras that are separated by a distance d called the baseline of the system. The projection of the same view on

4

two different surfaces allows the underlying algorithm to estimate the depth of the objects in the field of view. The baseline defines the depth resolution achieved by the system.

## 1.5 Project Organization

The remainder of this project report is organized as follows. Chapter II shows an exposition of the most common methods and techniques used in video stitching. A general survey of past image stitching implementations on FPGA platforms is included. The aim of this chapter is to select the most efficient approach for the selected hardware platform subject to the engineering constraints after analyzing the existing approaches. This section also presents an overview of the main milestones of the project as well as the original work contribution.

Chapter III is focused on the algorithm presentation and explanation. The first part of Chapter III presents an implementation of a software centric approach for image stitching. The main deficiencies of this approach are analyzed and identified with respect to the requirements and constraints. In the second part the architecture of the proposed HW image stitching algorithm is presented, together with block diagrams. This section also gives a description of the designed hardware platform.

Chapter IV describes the experimental setup and the specific implementation details on the selected FPGA SOC. Furthermore, a detailed explanation of each module is described together with simulation results. The experimental results together with the demonstration and comparison of algorithm with prior approaches are shown in Chapter V. This chapter also shows timing diagrams for each of the custom HDL modules. Finally, in Chapter VI, a summary of the main results from the project is provided together with potential avenues that require further optimization.

## Chapter 2 Related works

This chapter presents the main theory behind semi-panoramic vision covering the main techniques in use as well as a short survey of the field with applications to FPGA systems.

# 2 Panoramic Imaging

A panoramic image can be synthesized by stitching together multiple images. The images can be taken by a single rotating camera sensor, multiple camera sensors or special panoramic cameras.

In the most general case, when two images of the same scene are taken from two different cameras placed at arbitrary angles with respect to each other the pixel corresponding to the object 3D reference point gets mapped to different image coordinates. The pixel coordinate can be mathematically described as a combination of a Euclidean transform and a perspective transform.

The experimental setup designed for this project contains three cameras on a flat PCB spaced a distance d apart from each other. The differences in parallax with respect to each camera do not include changes in observation angle. For cameras placed on a flat plane such as the PCB, there is no projective transform so the setup is simplified. This simplifies the compositing surface since it's a simple plane and no projective 3D camera rotation transformations are needed so perspective transform can be removed from the calculations. In turn this simplifies the homography matrix.

Image stitching is the process of taking a number of images from different perspectives, transforming them so the features on all the images align with each other and then merging the images in such a way as to form a panorama based on the number of different perspectives of the same scene.

The main problem is the identification of the corresponding features on two adjacent images as well as transforming one image with respect to the adjacent one so that

There are a number of steps required to obtain a panoramic image from individual images. The cameras have to be line locked so that the same frame is acquired at the same moment from all

different cameras. The central procedure to image stitching is image registration. This is the process of aligning the images so that stitching can be performed.

There are a number of approaches to image registration which can broadly be categorized as direct that is intensity based or feature based [1].

Direct methods make use of an operator for image alignment. One example of direct methods are wavelet transform based techniques which consider the multiresolution representation of each image on different frequency sub-bands [18]. Feature based approaches are dominant in image stitching techniques. All feature-based techniques make use of key-points. The key-point is defined as a sparse set of features which is locally present on all the image perspectives. Key-point matching is the procedure of finding a correspondence between these features from image to image.

The homography matrix models the appropriate geometrical transformations to each respective image that relates the location of a specific pixel coordinates between different image perspectives. In this chapter a quick review of the two main methods is going to be covered. Then a number of recent and previous works that focus on hardware implementations of image stitching.

### 2.1 Problem Analysis

To stitch two images taken from different perspectives one has to determine the corresponding features that both images share. Then one of the images has to be transformed so that the perspective matches with the image that it will be stitched with. The two images then have to be positioned so that the overlapping areas are fully removed and the seam between the two images does not have any visible visual artifacts. To accomplish the above step a rectification procedure has to be applied so that the same feature pixel on both images is at the same level. Even if the rectification procedure is perfect and the images are aligned correctly, one can still observe visual artifacts along the seam if the two cameras are focused differently.

Estimating the seam where the two images start to share object features can applying multiband seam blending algorithms is one method of removing these visual artifacts. There are a number of seam estimation algorithms. Algorithms that optimize the pixels based on energy functions such as the color gradient along the seam. The naïve seam blending method uses the median value and the average of the overlapping pixels. Another method is to use center weighting or use multi band pixel blending. Automatic seam identification can be done independently from rectification and it can also be integrated as a precursor step to determining the epi-polar line.

Rectifying the two images basically requires determining a couple of corresponding pixels on both images. This can be accomplished by matching intensity features so that the two brightest pixels on the rights side of image A, correspond to the two leftmost side brightest pixels on image B.

These methods are classified as direct methods. The main disadvantage of intensity-based methods is that they do not offer the required accuracy due to differences in lighting. As such a naïve implementation will return many false positives which make the procedure inadequate.

The next approach is to determine features known as key-points. A key-point is defined as a sparse set of features which is locally present on all the image perspectives. This requires preprocessing of each image or at least sections of images in order to identify these descriptors.

A survey of the most common feature-based image stitching algorithms is given in the section below. The main disadvantage of feature-based techniques is the computational complexity of such approaches.

What can be observed by both aforementioned techniques is that there needs to be a balance between computational complexity of the applied algorithms and the accuracy and execution time that is required for the task at hand.

Another problem with cameras is lens distortion. This involves barrel distortion where the pixel coordinates are displaced away from the center of pincushion distortion where the pixel coordinates are displaced toward the center of the image. The approach taken in this thesis is to avoid any warping transformations and simply shift the images along the x and y directions relative to each other until they are fully aligned.

### 2.2 Publications

In [2] Popovic et al present an FPGA implementation of image blending using a hemispherical polydioptric system. The work mainly focuses on comparison of the blending techniques. Results show that the nearest neighbor technique results in visible artifacts. The linear blending technique is partially better at removing the visual artifacts. The best performance is obtained by applying a restricted Gaussian blending which applies a Gaussian filter only near the seam area.

In 2015 Disney Research [4] demonstrated an algorithm that uses local warping that allows for robust stitching with minimal parallax artifacts. This method allows for spatiotemporally stable panoramic video stitching. In [16] Lu et al. perform image warping using an efficient implementation of line buffers.

In [5] Shieh et al, present a video stitching algorithm that makes use of the OpenCV framework as well as applying the Difference of Gaussians method (DoG) to construct a scale space that shows the extreme points. After identifying the image descriptors and applying affiant transformation the stitched images are obtained.

In [7] Kawanishi et al make use of a six-camera setup coupled with a hexagonal pyramidal mirror in order to acquire stereo views. The camera system makes use of Tsai's method in order to restore the radial distortion of each camera image. In [8] Nayar presents a catadioptric omnidirectional camera system while in [13] and [14] the authors show applications of catadioptric system to robotic platforms.

In [12] Kar-han Tan et al present a panoramic camera that makes use of a mirror pyramid. The novelty of this approach is the mirror pyramid which forms a virtual camera with a very wide field of view.

### 2.3 Patents

There are plenty of patents that cover motion-based image stitching. While the patents are not open with regards to the algorithmic techniques, they still provide information on the applied methods. In [3] Apple shows how to implement motion-based image stitching. In addition, a number of fabless silicon providers also offer custom image stitching IP. The implementation details behind these IP cores however are not open. As an example, in [9] Omintek demonstrates an IP capable of warping the individual frames to allow seamless stitching. The IP is cable of dealing with a maximum of up to 8 different video sources.

## 2.4 Feature based methods

Fundamental to the procedure of image stitching in feature-based approaches is the detection of key-points. Image key-points are image features that contain particular criteria such as being invariant to image scaling, image rotation, 3D camera viewpoint, illumination of noise. The special point about these features is that they are invariant under transformations hence they are known as local invariant descriptors. Key-point matching is the procedure of finding a correspondence between these features from image to image. A number of different algorithms have been proposed for determining image key points.

Some of the most used techniques are a) Harris Corner Detector b) SIFT (Scale Invariant Feature Transform) c) Speeded up Robust features. It should be noted that SIFT and SURF algorithms are patented [24].

Feature based approaches for image stitching share the same algorithmic steps. The main differences reside in the types of algorithms that can be implemented in each step.

The primary step is the feature pointe detection. The next step is compiling the feature point descriptors. The third step is feature point matching. The fourth step is the calculation of the homography matrix. In general, this uses an algorithm that leverages the feature vectors to obtain a homography matrix. The homography matrix models the appropriate geometrical transformations to each respective image that relates the location of a specific pixel coordinates

between different image perspectives. It is used to apply transformations to the image so that the features in different images are aligned on the same plane.

The fifth step is implementation of image stitching by joining the warped images obtained from the previous step. The last step is image blending in order to remove any visual artifacts that are present. The next phase is matching the key-points on images taken from different perspectives.

The sixth step is applying the homography matrix to each image apart from the reference image and obtaining the warped images. The fifth step is rectifying the images so that each image is aligned along the same epi-polar line. This will require moving the images along the vertical direction until they are aligned.

The seventh step is merging the images so that on the generated panorama all the features in the different perspectives are closely aligned in such a manner so that no overlap or visual artifacts can be observed.

There are a number of methods used to obtain feature point descriptors. Corners, blobs, edges and ridges can be used as features. A quick summary of the most common methods is shown below.

#### 2.4.1 SIFT

The Scale Invariant Feature Transform (SIFT) algorithm is invariant to image scale and rotational transformations. This algorithm finds the scale space extremums and localizes the keypoint in an image frame. The algorithm is quite robust against changes in noise or image distortions. An FPGA implementation is shown in [19].

After finding a set of key-points, a region is selected around each key-point. The next step is to compute the gradient magnitudes and orientations around each key-point. From the computed gradients a histogram is created with each sample weighted by the gradient magnitude.

The rotational invariance of each descriptor is obtained by rotating the descriptor coordinates and the histogram orientation relatively to the dominant orientation. The key-points are then matched to a database of key-points by using the nearest neighbor criterion based on the Euclidean distance of the vector.

Four random points are selected and the Homography matrix is computed based on the solution of the linear equations. Then the image points are projected on the image plan of image I2 using the computed homography matrix Hi. The distance of inliers is then calculated based on a selected threshold.

These calculations are repeated k times by selecting the best homography matrix with the maximum number on inliers. An algorithm used for this computation is the RANSAC algorithms. An FPGA implementation of RANSAC is given in [20].RANSAC stands for Random Sampling with Consensus. The image stitching stage computes the homography transformation between two adjacent frames I<sub>j</sub> and I<sub>k</sub>. After transforming Image I<sub>j</sub> then the images I<sub>j</sub> and I<sub>k</sub> are blended together. The main issue is to find the optimal boundary between the regions of overlapped pixels between the two adjacent images that reduce the visual artifact.

#### 2.4.2 SURF

The main problem with SIFT is that it's fairly slow. Speeded Up Robust Features (SURF) is another patented local feature descriptor that speeds up the detection of features [25].

SURF makes use of blob detectors to determine image key-points. The main disadvantage of SIFT and SURF is the significant memory requirements and the fact they these algorithms are under patents. SURF has been implemented on FPGA platforms [23], [24].

#### 2.4.3 Harris Corner detector

The Harris corner detector is a mathematical procedure used to determine corresponding features between two different images. The elements are determined from patches of fixed size. The task essentially is to find the best similar patches on two frames that are taken from a different perspective. An efficient implementation is shown in [10]. The Harris Corner detector leverages the use of corners which are defined as junctures of contours. Corners are excellent feature key-points since they are very stable from changes of viewpoints. They can be recognized easily by looking at intensity values of a small patch.

Any shift of the patch location should yield a change in appearance. The Harris corner detector is given by Equation 2-1 below:

$$E(u,v) = \sum_{x,y}^{\infty} (w(x,y)[I(x+u,y+u) - I(x,y)]^2) \quad (Eq \ 2-1)$$

Where W is the window function and the second term represent the difference between a shifted version of Intensity and the original value.

The second term will be zero for constant patches while for distinctive patches this will be larger so it can be seen that E(u,v) will be large for corners. The Harris detector can be framed as a matrix multiplication operation between the windowing function and the components of the intensity gradient.

For small shifts using a bilinear approximation one can obtain the form shown in equation 2-2:

$$E(u,v) \approx [u,v]M \begin{bmatrix} u \\ v \end{bmatrix} (Eq \ 2-2)$$

The matrix M is a 2x2 matrix computed from image derivatives as shown in equation 2-3:

$$M = \sum_{x,y} w(x,y) \begin{bmatrix} I_x^2 & I_x I_y \\ I_x I_y & I_y^2 \end{bmatrix} (Eq \ 2-3)$$

The gradients  $I_x$  and  $I_y$  are computed using the Sobel operator. In practice the windowing function is Gaussian with sigma = 1. In algorithmic form the Harris corner detector is composed of the following steps:

a) The first step is the computation of the gradients. This requires computing the x and y derivatives of the image which is implemented by convolutions between the 3x3 pixel

window and the vertical and horizontal gradient mask. In this step the input image is converted into an x and y derivative map as given in equation 2-4 below:

$$I_x = G_{\sigma}^x * I \qquad \qquad I_x = G_{\sigma}^y * I \quad (Eq \ 2-4)$$

b) The second step is Gaussian smoothing. This is done by leveraging the gradient images computed on the previous steps. Computing the products of the derivative at every pixel as shown in equation set 2-5 below.

$$I_{x2} = I_x * I_x$$

$$I_{y2} = I_y * I_y \quad (Eq \ 2-5)$$

$$I_{xy} = I_x * I_y$$

c) The third step is computing the Harris measure which serves as an indicator of which pixel may be a corner pixel. This requires computing the sums of the products of the derivatives at each pixel as shown in equation 2-6.

$$S_{x2} = G_{\sigma'} * I_{x2}$$

$$S_{y2} = G_{\sigma'} * I_{y2} \quad (Eq \ 2-6)$$

$$S_{xy} = G_{\sigma'} * I_{xy}$$

For each pixel a Harris measure matrix H(x,y) is defined as in equation 2-7.

$$H(x,y) = \begin{bmatrix} S_{x2}(x,y) & S_{xy}(x,y) \\ S_{xy}(x,y) & S_{y2}(x,y) \end{bmatrix} (Eq\ 2-7)$$

d) The fourth step is the application of thresholding. The Harris Corner Detector uses the determinant and trace to find a factor R which represents the "corner score" for each pixel as given in equation 2-8.

$$R = Det(H) - k (Trace(H))^{2} (Eq 2 - 8)$$

e) The last step is the application of non-maximum suppression criterion. Based on the threshold of the computed R value one can compute the non-max suppression.

Implementations of Harris corner detector on FPGA platforms can be found in [1] and [2]. The main disadvantage of the algorithm is that it's computationally expensive due to its sequential nature. Since it is not known beforehand where the corners may be located on a captured image the algorithms need to run. On the other side this algorithm offers the most accurate detection of key-points even when images are noisy.

### 2.5 Feature based stitching algorithms

Feature based algorithms for synthesis of panoramic image from individual frames require a number of sequential steps. First the cameras have to be line locked so that the same frame is acquired at the same moment from all different cameras. The second step is to identify features in these images known as key-points. The special point about these features is that they are invariant under transformations hence they are known as local invariant descriptors. The next step is to match the key-points on images taken from different perspectives. The third step is to use an algorithm that leverages the obtained feature vectors to obtain a homography matrix. The homography matrix is used to apply transformations to the image so that the features in different images are aligned on the same plane. The fourth step is applying the homography matrix to each image apart from the reference image and obtaining the warped images.

The fifth step is rectifying the images so that each image is aligned along the same epi-polar line. This will require moving the images along the vertical direction until they are aligned.

The sixth step is to merge the images so that the generated panorama all the features in the different perspectives are closely aligned in such a manner so that no overlap or visual artifacts can be observed.

### 2.6 Design decisions

The main requirement for the implementation of frame stitching in this project is to meet reaction time constrains and real time operation.

The main issue with feature-based techniques is that they take considerable resources and execution time. Resource usage is directly related with power consumption which does not bode well for mobile implementations. On the other side execution time would violate the real time operation requirements of the system.

One idea is to pursue a mixed approach where one can calculate feature only on specific regions to decrease the computational complexity. Imagine both images are partitioned into tiles as shown in the Figure 2-1 below.

Figure 2-1 Algorithm only operating on tiles

The algorithm can then run only on specific tiles on both images. To avoid implementing feature-based algorithms such as SIFT, SIRF or equivalents one can borrow steps from the feature-based approach and then use intensity-based algorithm to perform the process.

As an example, one can apply an energy gradient filter to specific adjacent tiles of each image. Then a key-point search can be performed only on these tiles. Based on the detected highest energy gradient, key-points one can then perform rectification.

This removes the need for direct intensity-based key-point search which is suspect to erroneous results due to lighting conditions. On the other side this also removes the need to rely on resource intensive algorithms such as Harris corner detector and represents a middle ground that uses the least amount of resources while still operating within the real time requirements.

## Chapter 3 Proposed approach

# 3 Proposed Approach

## 3.1 ZYNQ SOC Overview

The lab prototyping system is based around a Zedboard development board which uses a ZYNQ 7010 SoC. The ZYNQ SoC couples a dual core ARM Cortex A9 denoted as the Processing System (PS) with the FPGA subsystem known as the Programming Logic (PL) in a single die. The ARM Cortex A-9 CPU includes 256 KB of On Chip Memory (OCM), including a number of peripherals as well as external memory interfaces such as DDR3L, NOR flash and SD-card.

The PS has a number of multiplexed I/O denoted as MIO and grouped in banks that start with a 50x designation. Some of the MIO can be routed to the PL I/O side via EMIO. The MIO are used to connect the ARM core to external peripheral and devices such as a) Serial Flash, b) NAND Flash c) UART d) I2C sensors e) USB PHY OTG f) Gigabit Ethernet PHY g) SD card.

The location of all these peripherals is pre-determined by the I/O map and specified in the ZYNQ TRM. The PL section itself provides a lot of I/O that are grouped in Banks denoted as BANKx where x is any of (13,34,35, 55).

The processor on the PS section always boots first and can be used independently from the PL section. The PL can be configured as part of the boot process using the First Stage Bootloader (FSBL) or it can be configured later from the PS. The PL supports partial reconfiguration.

# 3.2 Proposed Hardware

The lab hardware uses three OVM7690 cameras which interface with the ZYNQ via the FMC connector. The spacing of the cameras is close to 8 cm. This spacing was dictated by the size of the mirrors mounted between the cameras. The distance however represents a problem due to changes in parallax between adjacent cameras. In addition, this spacing incurs changes in intensity. A custom hardware platform was designed to overcome these limitations of the current hardware. The idea was to place the cameras much closer and use smaller mirrors.

Since the Zedboard is a relatively big development board it was required to design a custom solution that incorporated all the required hardware while taking the least amount of space.

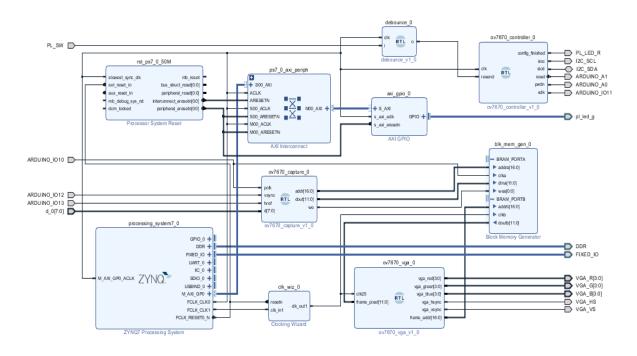

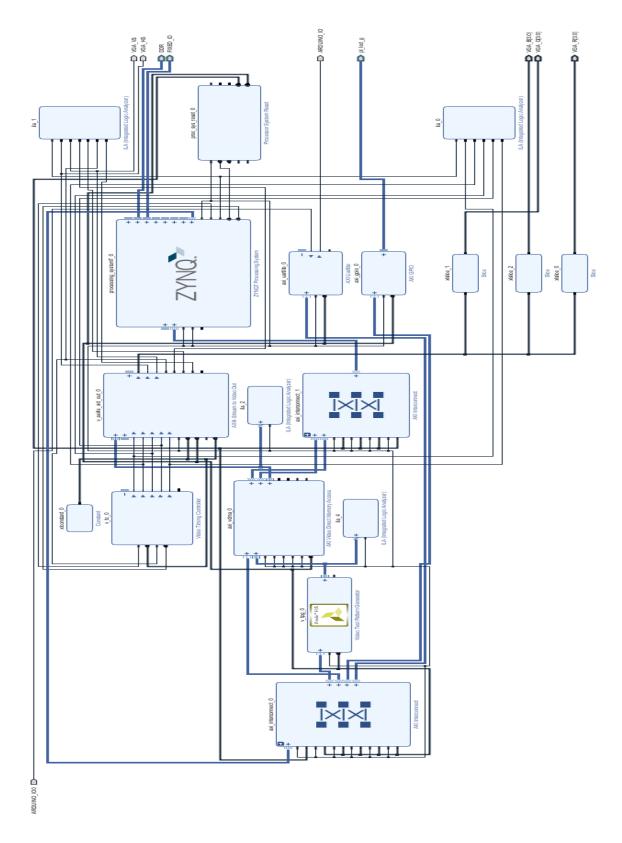

The hardware is designed around a ZYNQ XC7020 in a 10CLG484 package. This is the same SOC package that is located on the Zedboard. The block diagram in Figure 3-1 shows the main schematic design blocks of the system.

Figure 3-1 Proposed block diagram of the custom hardware platform

Bank 0 of the SOC contains the JTAG programming signals connected to the PS side, the XADC pins and the programming indicator pins. All JTAG signals use pull-up resistor and transient suppressing diodes. Bank 13 of the ZYNQ on the PL side is equipped with a number of pins which can be used to interface with differential signals. Both Banks 13 and 33 are used to interface with the external VGA DAC peripheral. Bank 34 and 35 of the ZYNQ are used to interface with the OVM7690 cameras. To simplify the hardware the voltage level for these banks

was set to 2.5V since this is within the operating limits of the camera I/O pins which specify from 1.8V to 2.8V.

Bank 502 is used to interface the DDR3L RAM with the PS side. Bank 500/501 contains user pins as well as the bootstrap pins. The bootstrap pins are sampled during bootup and allows the ZYNQ to boot from Quad SPI flash (QSPI), SD card or JTAG. SD card memory is connected to SDIO 0, pins 40-47.

A 33.33 MHz crystal oscillator is used to source the PS Clock. A 24 MHz clock is used to source the USB OTG PHY. A USB3320C PHY is used to add USB OTG to the system.

The I2C peripheral are used to configure the cameras and the PMU chips. Both I2C1 and I2C2 pins use 0ohm jumpers between each SDA and SCL line. Both lines then are pull up to VDDIO by 10 K resistors.

Two push-buttons are included, one is the PS reset push-button. The other is a PS switch. There are 2 external reset pins. PS\_SRTS\_B pin for soft reset. Bootstrap pins are not sampled and device is aware of previous status. PS\_POR\_B pin for reset. Bootstrap pins are sampled and BootROM runs from the APU. There are 7 boot mode strapping pins using MIO pins. Each of these pins are connected using 20K pull-ups or pull-downs. Pins [4:0] are used to select the BOOT mode.

Pins [1:0] VMODE are used to select the I/O voltage levels for the MIO voltage Banks. VMODE[0] controls MIO pins 15:0 while VMODE[1] controls MIO pins 53:16. A pull-up resistor selects the LVCMOS18 while pulldown selects LVCMOS25 which is compatible with LVCMOS33.

The PS section makes use of a DDR3L memory bank that is composed of one 16-bit width chip. The chip has a size of 2 GB and operates at a frequency of 533 MHz The DDR3L SDRAM is connected to the PS section via BANK 502. The termination resistors and a termination voltage LDO are also included as part of the schematic design.

The power management unit is composed of two highly integrated chipsets from Infineon specifically designed for ZYNQ SOC's. The power sequencing of the various PS and PL power rails is done automatically and can be configured via the I2C bus.

### 3.3 External peripherals

The rest of the design blocks describe the external peripheral of the system.

#### 3.3.1 Camera sensors.

The camera sensors make use of 4 OVM7690 cameras that are interfaced directly with the SOC. Configuration of the cameras is done directly from ZYNQ using an I2C switch. The camera has two power domains. The analog rail domain is fed by a 2.8V LDO with a current capacity of 200mA. The digital domain can run from 1.7V to 3V. Since the ZYNQ banks already run at 1.8V the camera I/O are also set to operate at 1.8V. Each camera is fed AVDD rail is connected to the filtered output of a single 2.8V LDO. The OVM7690 is controlled by an SCCB bus, which is functionally equivalent to the I2C bus. Since all cameras have the same I2C address an I2C switch is used to allows independent programming of each camera.

#### 3.3.2 WIFI BLE module

An WIFI / BLE combo module is used to allow the ZYNQ SOC to send images wirelessly via WIFI. The chip interfaces via the SDIO protocol with the ZYNQ. Configuration is done using a serial port with flow control. The schematic of this peripheral is comprised of the analog frontend with the antenna matching circuit and the digital section comprising the IC and two LED's used for activity notification.

#### 3.3.3 VGA DAC

Two VGA DAC with an 8-bit resolution were used. The DAC's are connected to DB15 VGA connectors. The decision to use VGA as opposed to HDMI was made simply on cost.

#### 3.3.4 USB

A USB PHY was added allowing the ZYNQ to interface will external USB 2.0 peripherals.

#### 3.3.5 JTAG and Serial Port.

The ZYNQ SOC is programmed from an FTDI2232 JTAG programmer. Port A of the FTDI chipset is configured as a JTAG programmer while port C is configured as a serial port. Port B and D are left un-used. The FTDI2232 is connected to an external EEPROM which is used to store configuration settings.

#### Figure 3-2 Proposed placement for designed hardware

The part placement for the PCB layout is suggested to follow the diagram shown in Figure 3-2 above.

## 3.4 System BOOT

The ZYNQ SOC follows a multi stage boot. The primary stage is the BOOT ROM that is not user accessible. The BOOT ROM reads the bootstrap MODE pins to determine from which memory device to boot, then it determines if the boot is secure or not and performs system cleanup and initialization. BOOTROM is executed from internal ROM code memory.

It copies the FSBL from external NOR flash memory to the internal SRAM. When the boot code is not available in SPI NOR FLASH the BOOTROM tries to boot from the JTAG. The next step is to jump to the FSBL which is executed from the on-chip SRAM.

### 3.5 Experimental Setup

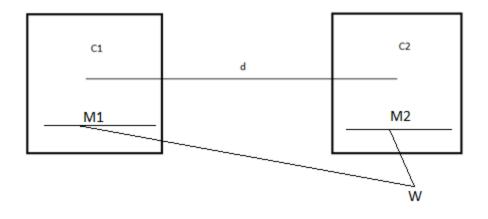

The most basic setup consists of two video camera sensors denoted as C1 and C2 placed a distance d apart as given in Figure 3-3. In the most general case the cameras occupy a position in 3D space which defines their angular relation with respect to one another. The projection of a 3D point in each camera plane corresponds to different points M1 and M2. Rectification consists of finding a common line through E1 and E2 called the epipole. Points R1 and R2 are the focal places of the camera and line R1R2 is called the baseline. When the baseline is parallel to the X axis in an XY coordinate system epipolar lines are horizontal and parallel with respect to each other.

Figure 3-3 General case for epipolar projection

To simplify the analysis from the general case, the setup dictates that both cameras are placed on a flat surface as shown in Figure 3-4. The distance d is typically in the range of 10-15 cm. Provided that the separation distance falls within the FOV of the camera sensor one can observe that the images taken by the two cameras at any time share some common parts.

Figure 3-4 Simplified case of epipolar projection for lab setup

Assuming camera C1 is positioned to the left and camera C2 is positioned to the right one can observe that the right side of camera C1 shares similar image features with the lefts side of camera C2. In panoramic video stitching, the problem is how to combine the two images in a single image so that the overlapping sections are merged in a single video frame. In addition, to properly implement rectification the same point must also have the same vertical coordinate in both projections.

Due to parallax, the location of the same feature as seen from the two cameras is different. The advantage offered by parallax is that the overlapping visual field is used to extract scene depth perception. Since the angle of projection of the same object is different for each of the two cameras, a number of image features such as intensity of pixels, light exposures and object alignment are also different.

In this project the main aim is to stitch the images without addressing issues like pixel intensity and light exposure and camera synchronization. The goal of the project is to implement image stitching so that the synthesized panoramic image does not exhibit any visual artifact.

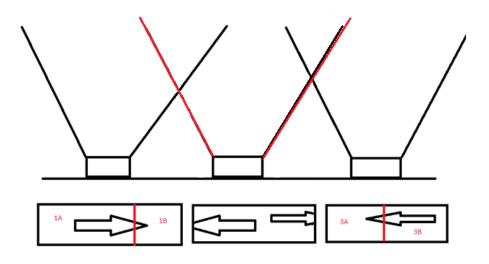

The experimental setup designed in the lab contains three cameras on a flat PCB spaced 10 cm apart from each other as shown in Figure 3-5. The parallax is defined as the angle between the two cameras FOV.

Figure 3-5 Catadioptric optical system for panoramic imaging

The sketch in Figure 3.5 presents the main idea behind the proposed catadioptric system. Three camera sensors are located on a planar surface equally spaced among each other. All cameras on the above setup are precisely positioned with respect to one another. The cameras operate at the same pixel clock and are sourced from clocks which are in phase with each other.

Between each camera there is a mirror slanted at an angle  $\alpha$  with respect to the normal. The angle is chosen in such a way as to minimize the overlapping features between the adjacent images but not completely remove them. The overlapping visual fields from each camera are used to extract features for stitching the images as well as extracting depth information.

In the most general case, when two images of the same object are taken from two different cameras placed at arbitrary angles with respect to each other, the pixel corresponding to the object 3D point gets mapped to different image coordinates. The pixel coordinate can be mathematically described as a combination of a Euclidean transform and a perspective transform. For cameras placed on a flat plane such as the PCB, there is no projective transform since the homography matrix is much simples compared to the general case which includes rotations so the setup is simplified. This simplifies the compositing surface since it's a simple plane and no perspective transform, i.e projective 3D camera rotation transformations are needed when implementing the algorithm. The differences in parallax with respect to each camera do not include changes in observation angle.

Another problem with cameras is lens distortion. This involves barrel distortion where the pixel coordinates are displaced away from the center or pincushion distortion where the pixel coordinates are displaced toward the center of the image. The approach taken in this thesis is to avoid any warping transformations and simply shift the images along the x and y directions relative to each other until they are fully aligned.

The task of the proposed image stitching algorithm is to create a panoramic image based on the above setup. To do so the image stitching IP has to discard part of sides images and join the remaining part with the central frame.

To implement the above task, the image stitching IP needs to have a-priori knowledge of the index location of the seam. This is the line that demarcates the overlapping features on the side images with the parts that need to be flipped from the part that needs to be discarded. This requires that the column index of the seam is provided as input to the module.

In addition, the left and right images need to be rectified with respect to the center image. All images must be rectified so that the same feature overlapping two images shows on the same scan line. The rectification procedure mitigates the vertical shift that is induced on the camera's sensors due to misalignments and from perspective changes.

# 3.6 Proposed Algorithm

The proposed image registration techniques for implementing image stitching are based on a hybrid approach making use of efficiently calculating image features by filtering the frames and using intensity changes to localize them. Due to the presence of mirrors, it is suggested to decouple the registration process in two separate steps. The first step is the determination of the seam index location. The second step is the rectification process which aligns the adjacent frames in the vertical position with respect to one another. While the above steps can be merged into one single module which outputs the x and y coordinates of a single feature shared between two adjacent images, the current work follows a decoupled approach. FPGA image rectification has been implemented in various forms as in [24], [25], [26], [27].

## 3.7 Seam index identification

The optimal boundary location for overlapping two adjacent image frames is defined as the seam. For cameras placed on a flat horizontal surface we assume that the seam is a vertical line that demarcates overlapping features between the two adjacent images. In the most general case, the cameras are undergoing relative motion so the seam index has to be recalculated to account for small differences due to vibration at periodic intervals. Image registration algorithm implemented in FPGA are shown in [17], [21], [22].

Other approaches include dynamic programming, graph cuts and Dijkstra shortest path algorithm. All these approaches however require significant resource utilization.

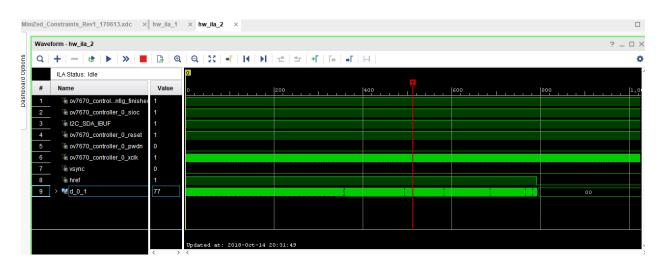

The proposed method implements seam index identification automatically on the FPGA. The idea is to implement an IP module that provides column indices that corresponds to the seam location on the corner frames. In addition, the seam column index of the right and the left frame is provided as an input to the image stitching IP. This allows the IP to be dynamically configured at runtime by using an AXI-Lite Wrapper around the image stitching IP. The PS can then write to the respective registers and update the seam index of each of the cameras.

One option that requires minimal resource utilization is to place an LED between the two cameras, mounted on the mirror. The LED serves as a key-point by being the brightest pixel in the FOV of each camera. Key-point detector modules are used to determine the brightest key-point on each frame. In theory, the column index of the feature should correspond to the seam index. The output of the key-point detector is the line and column of the key-point. This can be used for both rectification and seam coordinates estimation. In practice the implementation of this techniques has multiple shortcomings.

First, the light source should be mounted in the field of view of two cameras. Since a mirror is placed between the two cameras one needs to either mount the LED on the corner of the mirror so that it is still visible in both frames or on a horizontal bar that does not impede the FOV of either camera.

Second, while the LED intensity can be regulated by using a PWM, using a single key-point in practice proves inadequate since different image features on the two frames may have greater intensity than the LED. Third, the LED may obscure visual features.

Nevertheless, an HDL IP was implemented that searches for the brightest key-point in a frame area and returns the key-point column coordinates. A testbench and the IP code are shown in the Appendix A.

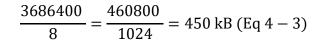

A second option for automatic seam column index identification is to pursue a pixel energybased approach. An energy map can be implemented using different methods such as the gradient magnitude or entropy. The pixel energy map is given by equation 3-1:

$$e(x,y) = \left|\frac{\partial I}{\partial x}\right| + \left|\frac{\partial I}{\partial y}\right| (Eq \ 3-1)$$

Each pixel is assigned an energy measure as given by the gradient operator. This can be any of the well-known filters such as Robert, Prewitt, Sobel, Laplacian coupled with erosion or dilation of the obtained features or using a more sophisticated edge detector such as the Canny edge detector. An efficient Sobel implementation is shown in warping.

Another approach to gradient energy is to compute the map of histogram of oriented gradients for each image area adjacent to each other and locate the indices of the highest energy. To implement this method, one need to add a streaming gradient operator at the output of two adjacent frames and search for the highest energy pixel on the output.

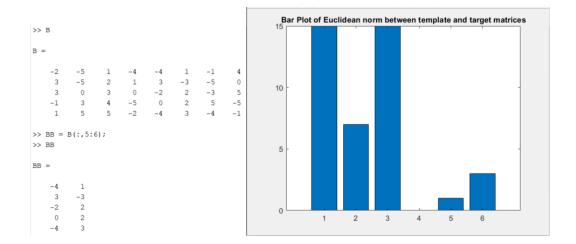

## 3.8 Automatic seam detection algorithm

To automatically determine the seam column index, the following algorithm is proposed to be implemented in the PL as a custom IP. Assuming two cameras C1 and C2, the first column of the C2 camera frame is taken as the reference template. From prior knowledge from mirror positioning we know that the overlap between camera C1 and C2 is 20-30% starting from rightmost side of frame C1 as shown in Figure 3-6.

The proposed algorithm steps are as follows:

1. Compute energy gradient of columns x to FRAME\_WIDTH for frame C1.

- 2. Compute energy gradient of column 1-2 for frame C2.

- 3. Calculate Euclidean norm between all column pixels of template and column i of C1

- 4. Calculate sum for each step i above and save it in memory

- 5. Implement a state machine that searches for the minimum value for each of the columns i to FRAME\_WIDTH.

Theoretically the entry for a match would be zero assuming the frames are vertically rectified. In practice one picks the histogram entry with the smallest value assuming a minor shift in the y direction. The bin index with the lowest value is the seam index where the frames from A1 and B1 start overlapping. Figure 3-7 shows how the two image matrices are stitched together assuming they are already rectified.

| 64  | 66  | 110 | 132 | 97  | 205 | 97  | 205 | 176 | 179 | 101 | 58  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 157 | 239 | 245 | 69  | 132 | 220 | 132 | 220 | 92  | 47  | 111 | 56  |

| 55  | 66  | 20  | 136 | 99  | 87  | 99  | 87  | 37  | 118 | 87  | 186 |

| 159 | 172 | 3   | 31  | 159 | 219 | 159 | 219 | 107 | 13  | 42  | 221 |

Figure 3-6 Two sample image matrices (1 left, 2 right) with overlapping columns

| 64  | 66  | 110 | 132 | 97  | 205 | 176 | 179 | 101 | 58  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 157 | 239 | 245 | 69  | 132 | 220 | 92  | 47  | 111 | 56  |

| 55  | 66  | 20  | 136 | 99  | 87  | 37  | 118 | 87  | 186 |

| 159 | 172 | 3   | 31  | 159 | 219 | 107 | 13  | 42  | 221 |

**Figure 3-7 Stitched images**

| 33  | 31   | -13  | -35 | 0 | -108 |

|-----|------|------|-----|---|------|

| -25 | -107 | -113 | 63  | 0 | -88  |

| 44  | 33   | 79   | -37 | 0 | 12   |

| 0   | -13  | 156  | 128 | 0 | -60  |

| 33  | 31   | -13  | -35 | 0 | -108 |

Figure 3-8 Calculated bins for each operation

Figure 3-8 above shows that the second entry has the lowest value hence it is identified as the seam index. The index of the seam is identified as  $I = IM_W - 2$ . This gives the index of the seam with respect to the image column itself.

Figure 3-9 Determining seam index by Euclidean norm

A simulation was implemented in MATLAB. Matrix B and BB are used as the target and template matrices respectively as given in Figure 3-9. The bar plot is a histogram representing the index of the column where the seam appears. The simulation above assumes that the images are fully rectified so that there is not discrepancy in the vertical direction.

# 3.9 Rectification

The lab hardware consists of three cameras soldered on the PCB. Each camera carries intrinsic distortions due to minor differences in lens geometry. In addition, there are extrinsic distortions arising from small mis-alignments from the PCB assembly. FPGA image rectification for stereo setups has been shown previously in [28].

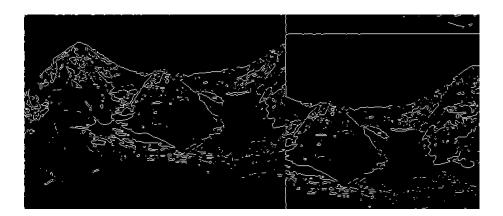

This results in a mismatch of the epi-polar lines which in practice results in adjacent image features which are shifted vertically when transitioning from one camera view to the adjacent as shown in Figure 3-10 Aligning the epipolar lines needs to be implemented automatically during runtime at periodic intervals to account for motion induced artifacts.

Figure 3-10 Unrectified Sobel filtered adjacent frames

The algorithm needs to determine a key-point feature and align the images such that the feature shows up on the same vertical dimension on the overlapped areas. The main idea behind the online rectification is to determine the coordinates and height of the key-point on two adjacent frames and shift the frame coordinates vertically automatically so that the epipolar lines are aligned along the y direction.

The procedure requires implementing a module that outputs the row coordinates of the key-point feature as well as the height of the key-point feature for both left, right and center images. The left and right frames are then shifted vertically to match with the center frame.

As seen on the diagram above the same image is shown on the left and center cameras as well as on the right and center camera. Two tasks need to be implemented to properly stitch the reflected images. First one needs to rectify the image so that the same features show up on the same scan line. This requires vertically translating the left and the right image with respect to the features on the center image.

Second one needs to determine the seam column index of the left and the right cameras where the image features overlap. This index is calculated separately for the left and the right cam. The image rectification task is considered independently from the seam index identification.

The IP assumes a camera assembly with three sensors as seen in the lab. In a camera assembly with four video sensors, the column index is calculated with respect the adjacent cameras as seen from left to right.

# 3.10 Proposed firmware modules

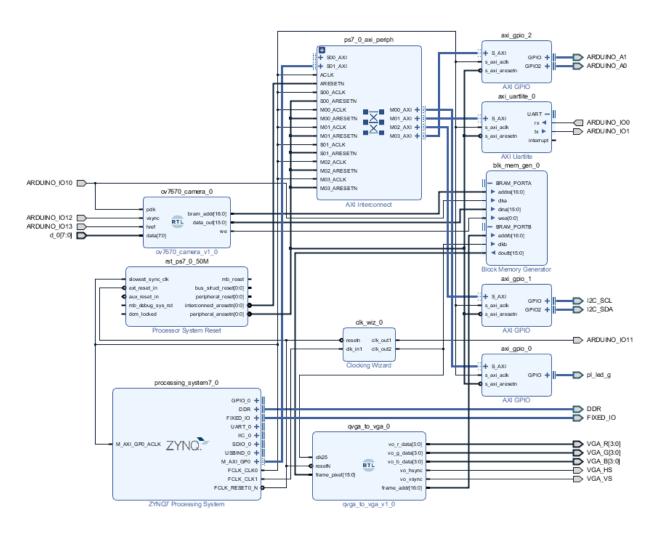

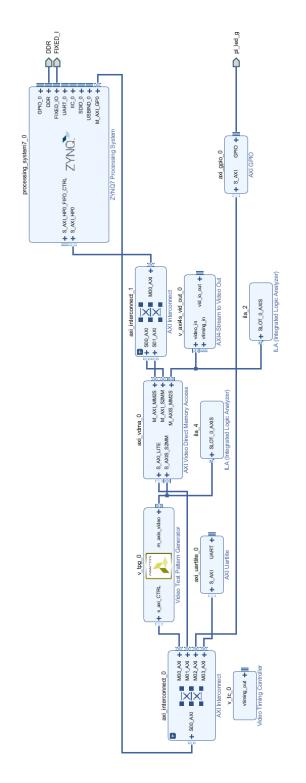

The main architecture of the image stitching system is shown on the block diagram below. The current system is designed for three cameras. The main firmware modules are:

- a) Camera input capture module

- b) Line buffer module

- c) Sobel filter

- d) Image stitching IP

- e) Seam identification IP

- f) Rectification IP

- g) VGA controller IP