# Realtime Ray Tracing on current CPU Architectures

### **Carsten Benthin**

Computer Graphics Group Saarland University 66123 Saarbrücken, Germany

Dissertation zur Erlangung des Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultät I der Universität des Saarlandes

#### Betreuender Hochschullehrer / Supervisor:

Prof. Dr.-Ing. Philipp Slusallek Universität des Saarlandes, Saarbrücken, Germany

#### Gutachter / Reviewers:

Prof. Dr.-Ing. Philipp Slusallek Universität des Saarlandes, Saarbrücken, Germany

Prof. Dr. rer. nat. Hans-Peter Seidel MPI Informatik, Saarbrücken, Germany

Research Assistant Professor Steven G. Parker University of Utah, Salt Lake City, UT, USA

#### Dekan / Dean:

Prof. Dr. rer. nat. Jörg Eschmeier Universität des Saarlandes, Saarbrücken, Germany

#### Eingereicht am / Thesis submitted:

30. Januar 2006 / Jan 30st, 2006

Carsten Benthin Lehrstuhl für Computergraphik, Geb. 36.1/E14 Im Stadtwald, 66123 Saarbrücken Germany benthin@graphics.cs.uni-sb.de

## **Abstract**

In computer graphics, ray tracing has become a powerful tool for generating realistically looking images. Even though ray tracing offers high flexibility, a logarithmic scalability in scene complexity, and is known to be efficiently parallelizable, its demand for compute power has in the past lead to its limitation to high-quality off-line rendering.

This thesis focuses on the question of how realtime ray tracing can be realized on current processor architectures. To this end, it provides a detailed analysis of the weaknesses and strengths of current processor architectures, for the purpose of allowing for highly optimized implementation. The combination of processor-specific optimizations with algorithms that exploit the coherence of ray tracing, makes it possible to achieve realtime performance on a single CPU.

Besides the optimization of the ray tracing algorithm itself, this thesis focuses on the efficient building of spatial index structures. By building these structures from scratch for every frame, interactive ray tracing of fully dynamic scenes becomes possible. Moreover, a parallelization framework for ray tracing is discussed that efficiently exploits the compute power of a cluster of commodity PCs. Finally, a global illumination algorithm is proposed that efficiently combines optimized ray tracing and the parallelization framework. The combination makes it possible to compute complete global illumination at interactive frame rates.

# Kurzfassung

In der Computer-Graphik hat sich Ray-Tracing längst als wichtiges Werkzeug zur realistischen Bildsynthese etabliert. Entscheidend dazu beigetragen haben dessen Flexibilität und logarithmische Skalierung in der Szenengröße, sowie die effiziente Parallelisierbarkeit. Aufgrund der hohen Anforderung an Rechenkapazität war die Verwendung bisher auf den qualitativ hochwertigen, aber nicht interaktiven Bereich der realistischen Bildsynthese beschränkt.

Diese Dissertation beschäftigt sich mit der Frage, wie die Geschwindigkeit von Ray-Tracing auf heutigen Prozessorarchitekturen derart gesteigert werden kann, dass es die Bildsynthese in Echtzeit ermöglicht. Dazu präsentiert die vorliegende Arbeit eine genaue Analyse der Stärken und Schwächen der heutigen Prozessorarchitekturen, um die benötigten Algorithmen entsprechend zu optimieren. Darauf aufbauend werden Algorithmen vorgestellt, die es im besonderen Maße erlauben, Kohärenz innerhalb des Ray-Tracing Verfahrens effizient auszunutzen. Diese Kombination von kohärenz-ausnutzenden Algorithmen mit einer prozessoroptimierten Implementierung ermöglicht sogar die interaktive Bildsynthese bei Ausnutzung der Rechenkapazität eines einzelnen Prozessors.

Darüber hinaus präsentiert die vorliegende Arbeit einen neuen Algorithmus, der die Zeit für den Aufbau der für das Ray-Tracing benötigten räumlichen Beschleunigungsdatenstrukturen erheblich verkürzt. Der beschleunigte Aufbau erlaubt sogar das interaktive Ray-Tracing von vollständig dynamischen Szenen. Daneben wird ein Parallelisierungsystem für Ray-Tracing vorgestellt, welches die Rechenkapazität eines Netzwerkes von Standardrechnern effizient kombiniert, um sogar Bildsynthese in Echtzeit zu erreichen. Abschließend wird ein Verfahren zur physikalisch korrekten Beleuchtungssimulation beschrieben, welches bereits vorgestellte Techniken wie optimiertes Ray-Tracing und effiziente Parallelisierung verbindet. Diese Kombination ermöglicht es letztendlich die physikalisch korrekte Beleuchtung mehrmals pro Sekunde komplett neu zu berechnen.

# Zusammenfassung

In der Computer-Graphik hat sich Ray-Tracing längst als wichtiges Werkzeug zur realistischen Bildsynthese etabliert. Entscheidend dazu beigetragen haben die Flexibilität und logarithmische Skalierung in der Szenengröße sowie die effiziente Parallelisierbarkeit des Ray-Tracing Verfahrens an sich. Aufgrund der langen Laufzeit und der hohen Anfordung an Rechenkapazität war die Verwendung von Ray-Tracing bisher auf den qualitativ hochwertigen, aber nicht interaktiven Bereich der realistischen Bildsynthese beschränkt.

Diese Dissertation beschäftigt sich mit der Frage, wie die Geschwindigkeit von Ray-Tracing derart gesteigert werden kann, dass Ray-Tracing auch für die interaktive Bildsynthese bzw. die Bildsynthese in Echtzeit geeignet ist. Als ersten Schritt dazu präsentiert die vorliegende Arbeit eine genaue Analyse der heutigen Prozessorarchitekturen, die die zugrundeliegende Hardware-Plattform bilden. Dabei werden deren Stärken und Schwächen detailliert aufgezeigt und daraus abgeleitet Implementierungs- und Optimierungsrichtlinien vorgestellt. Diese Richtlinien erlauben es, ineffizienten Code bei der Implementierung des Ray-Tracing Verfahrens zu vermeiden.

Einer der Hauptschwerpunkte der vorliegenden Disseration liegt auf der Entwicklung von Algorithmen, die es erlauben Kohärenz innerhalb des Ray-Tracing Verfahrens effizient auszunutzen. Gerade die Anwendung von Operationen auf kohärente Strahlbündel anstatt auf einzelne Strahlen ermöglicht eine erhebliche Steigerung der Geschwindigkeit von Ray-Tracing. Dies wird detailliert an den zwei fundamentalen Algorithmen des Ray-Tracing Verfahrens, der Traversierung von Strahlen durch eine räumliche Beschleunigungsdatenstruktur und dem Schnittpunkttest zwischen Strahl und geometrischem Primitive aufgezeigt. Beim Schnittpunkttest wird neben der Unterstützung für Dreiecke ein besonderes Augenmerk auf die effiziente Unterstützung von Freiformflächen gelegt. Im Gegensatz zur Beschreibung einer Szene mittels Dreiecken erlaubt die Beschreibung mittels Freiformflächen eine viel kompaktere und genauere Repräsentation. Allerdings gestaltet sich der benötigte Schnittpunkttest ungleich aufwendiger. Diese Arbeit stellt dazu verschiedene Algorithmen vor, die je nach Anwendungsgebiet und Genauigkeitsanforderungen unterschiedlich eingesetzt werden können. Die Kombination kohärenz-ausnutzender Algorithmen zur Traversierung und Schnittpunktberechnung mit einer effizienten und prozessornahen Implementierung ermöglicht sogar die interaktive Bildsynthese bei Ausnutzung der Rechenkapazität eines einzelnen Prozessors.

Neben der Optimierung des Ray-Tracing Verfahrens an sich, stellt diese Dissertation ein Algorithmus vor, um die für Ray-Tracing benötigten räumlichen Beschleunigungsdatenstrukturen effizient aufzubauen. Dabei wird auf dieselben Optimierungsstrategien zurückgegriffen, die bereits bei der Beschleunigung des Ray-Tracing Verfahrens zum Tragen kommen. Der optimierte Aufbaualgorithmus erlaubt sogar das interaktive Ray-Tracing von vollständig dynamischen Szenen, indem die Beschleunigungsdatenstrukturen mehrmals pro Sekunde komplett neu aufgebaut werden.

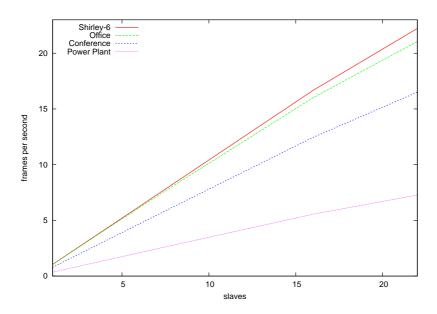

Weiterhin wird ein System zur Parallelisierung des Ray-Tracing Verfahrens präsentiert, das die Rechenkapazität eines Netzwerkes von Standardrechnern effizient kombiniert. Dabei wird das System mit dem Ziel entwickelt, die Nachteile einer solchen verteilten Architektur, wie beispielsweise getrennte Hauptspeicher und langsame Verbindungsbandbreiten, effizient zu kompensieren. So gelingt es, die Geschwindigkeit von Ray-Tracing linear mit der Anzahl der verbundenen Rechner zu steigern, wodurch Ray-Tracing sogar in Echtzeit ermöglicht wird.

Im letzten Teil der Dissertation wird ein Verfahren zur physikalisch korrekten Beleuchtungssimulation vorgestellt, welches die bereits vorgestellte Techniken, hoch optimierter Ray-Tracing Kern und Rahmenwerk zur Parallelisierung, effektiv verbindet. Die Kombination dieser Techniken mit einem auf Kohärenzausnutzung ausgelegtem Algorithmus zur Beleuchtungssimulation ermöglicht es letztendlich, die physikalisch korrekte Beleuchtung mehrmals pro Sekunde komplett neu zu berechnen.

# **Acknowledgements**

First of all, I would like to thank Prof. Dr. Philipp Slusallek for supervising this thesis. The open and encouraging atmosphere in his group and in particular his continuous support were invaluable for the success of my thesis.

Second, I have to thank Dr. Ingo Wald, who taught me basically everything I know about ray tracing. He has been an invaluable help in many projects related to this thesis. Without his encouraging support and a countless number of discussions through the years I would not have been able to complete my PhD thesis.

I would also like to thank my reviewers, Hans-Peter Seidel and Steven Parker, for kindly accepting the responsibility of reviewing my thesis.

Similarly, I have to thank (in random order) Andreas Dietrich, Heiko Friedrich, Johannes Günther, Jörg Schmittler, and Georg Demme and his administration group for many fruitful discussions, ideas and help in many projects. Special thanks goes to Michael Scherbaum for reducing my workload during writing this thesis. Furthermore, I would like to thank the current and former members and students of the computer graphics group.

I would also like to thank James T. Hurley for giving me the opportunity to do an internship at Intel Corp. Many thanks are due to Gordon Stoll and Alexander Reshetov for many helpful discussions, for introducing me to many new ideas, and for simply making the stay a great experience.

Special thanks goes to my sister Nicole Benthin, who helped me writing this thesis in 'readable' English.

Finally, and most importantly, I would like to thank my familiy, and in particular my wife Andrea for their great patience, their encouraging support and for bearing so many stressful times. Without their help this thesis would never have been possible.

# **Contents**

| 1        | Inti                         | roduction                                   | 1  |  |

|----------|------------------------------|---------------------------------------------|----|--|

|          | 1.1                          | Outline of this thesis                      | 3  |  |

| <b>2</b> | Introduction to Ray Tracing  |                                             |    |  |

|          | 2.1                          | The Ray Tracing Algorithm                   | 5  |  |

|          | 2.2                          | Ray Tracing for Rendering                   | 7  |  |

|          | 2.3                          | Ray Tracing Performance                     | 9  |  |

|          | 2.4                          | Coherence                                   | 10 |  |

|          | 2.5                          | Conclusions                                 | 13 |  |

| 3        | CP                           | U Architectures                             | 15 |  |

|          | 3.1                          | Performance Issues                          | 15 |  |

|          | 3.2                          | Coding Guidelines                           | 18 |  |

|          | 3.3                          | Data Level Parallelism by SIMD Instructions | 19 |  |

|          | 3.4                          | Tools and Hardware                          | 27 |  |

|          | 3.5                          | Conclusions                                 | 29 |  |

| 4        | Tracing Coherent Ray Bundles |                                             |    |  |

|          | 4.1                          | kd-Trees                                    | 32 |  |

|          | 4.2                          | Ray Bundle Traversal I                      | 34 |  |

|          | 4.3                          | Ray Bundle Traversal II                     | 49 |  |

|          | 4.4                          | Experiments and Results                     | 58 |  |

|          | 4.5                          | Conclusions and Future Work                 | 69 |  |

| 5        | Col                          | nerent Ray Tracing for Triangular Surfaces  | 71 |  |

|          | 5.1                          | Triangle Intersection I                     | 72 |  |

|          | 5.2                          | Triangle Intersection II                    |    |  |

|          | 5.3                          | Results                                     | 79 |  |

|          | 5.4                          | Conclusions and Future Work                 | 82 |  |

x CONTENTS

| 6                         | Coh    | erent Ray Tracing for Freeform Surfaces   | 83    |

|---------------------------|--------|-------------------------------------------|-------|

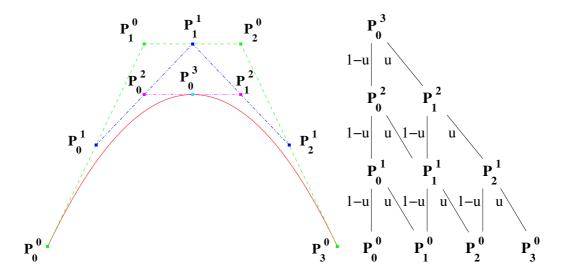

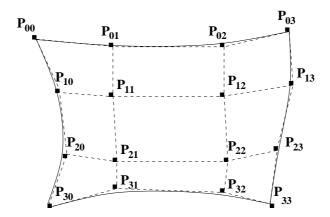

|                           | 6.1    | Bézier Fundamentals                       | . 85  |

|                           | 6.2    | The Ray-Patch Intersection Problem        | . 90  |

|                           | 6.3    | Uniform Refinement                        | . 91  |

|                           | 6.4    | Newton Iteration                          | . 97  |

|                           | 6.5    | Newton Iteration and Krawczyk Operator    | . 104 |

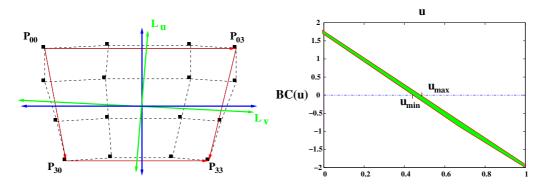

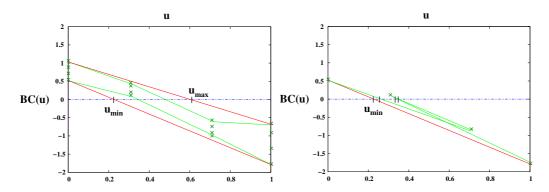

|                           | 6.6    | Bézier Clipping                           | . 113 |

|                           | 6.7    | Summary of Intersection Algorithms        | . 123 |

|                           | 6.8    | Spatial Index Structures for Patches      | . 125 |

|                           | 6.9    | Trimming Curves                           | . 125 |

|                           | 6.10   | Results                                   | . 128 |

|                           |        | Application                               |       |

|                           | 6.12   | Conclusions and Future Work               | . 138 |

| 7                         | Dyn    | namic Scenes                              | 139   |

|                           | 7.1    | Rapid Construction of kd-Trees            | . 140 |

|                           | 7.2    | Conclusions and Future Work               |       |

| 8                         | Dist   | cributed Coherent Ray Tracing on Clusters | 149   |

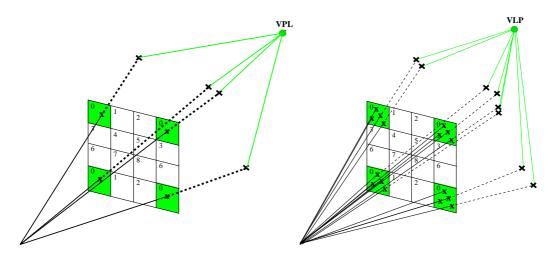

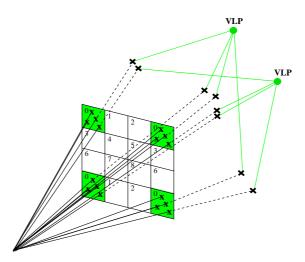

|                           | 8.1    | Introduction                              | . 149 |

|                           | 8.2    | Distribution Strategies                   | . 150 |

|                           | 8.3    | The OpenRT Distribution Framework         |       |

|                           | 8.4    | Communication and Dataflow                | . 157 |

|                           | 8.5    | Results                                   | . 159 |

|                           | 8.6    | Conclusions and Future Work               | . 159 |

| 9                         | App    | olications                                | 163   |

|                           | 9.1    | Instant Global Illumination               | . 163 |

|                           | 9.2    | Exploiting Coherence                      | . 165 |

|                           | 9.3    | Streaming Computations                    | . 167 |

|                           | 9.4    | Efficient Anti-Aliasing                   | . 169 |

|                           | 9.5    | Distributed Rendering                     | . 170 |

|                           | 9.6    | Results                                   | . 171 |

|                           | 9.7    | Conclusions and Future Work               | . 173 |

| 10                        | Fina   | al Summary, Conclusions, and Future Work  | 175   |

| $\mathbf{A}$              | List   | of Related Papers                         | 179   |

| $\mathbf{B}^{\mathrm{i}}$ | ibliog | graphy                                    | 183   |

# **List of Figures**

| 2.1<br>2.2 | Recursive ray tracing                                              | 8<br>11 |

|------------|--------------------------------------------------------------------|---------|

| 3.1        | SOA data layout                                                    | 20      |

| 3.2        | Intel's streaming SIMD extension (SSE)                             | 21      |

| 3.3        | AOS vs. SOA                                                        | 22      |

| 3.4        | Parallel dot products using SSE instructions                       | 22      |

| 3.5        | Parallel dot products using SSE intrinsics                         | 24      |

| 3.6        | SSE utility functions                                              | 26      |

| 3.7        | ${\rm SSE}$ inverse computation using Newton-Raphson approximation | 26      |

| 3.8        | SSE horizontal operations                                          | 27      |

| 3.9        | Data structure for single rays and ray bundles                     | 28      |

| 3.10       | Data structure for an axis-aligned bounding box                    | 29      |

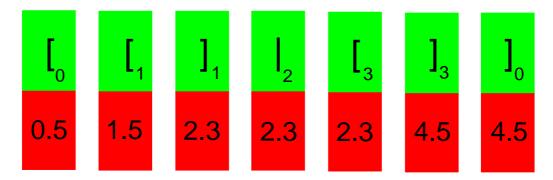

| 4.1        | Layout of a kd-tree node                                           | 34      |

| 4.2        | Traversal order for single rays                                    | 35      |

| 4.3        | Traversal algorithm for single rays                                | 36      |

| 4.4        | Traversal algorithm for ray bundles                                | 37      |

| 4.5        | Ray bundle initialization                                          | 39      |

| 4.6        | Traversal order look-up table                                      | 40      |

| 4.7        | Traversal implementation for a single four-ray bundle              | 42      |

| 4.8        | Traversal implementation without branches                          | 45      |

| 4.9        | Traversal implementation for four-ray bundles                      | 46      |

| 4.10       | Alternative traversal implementation for four-ray bundles          | 48      |

| 4.11       | Inverse frustum culling algorithm                                  | 50      |

|            | Offset look-up table for extremal traversal                        | 52      |

| 4.13       | Extremal traversal implementation by inverse frustum culling.      | 53      |

|            | Alternative extremal traversal algorithm                           | 54      |

|            | Alternative ray-segment traversal implementation for extremal      |         |

|            | traversal                                                          | 55      |

| 4 16       | Finding kd-tree entry points                                       | 56      |

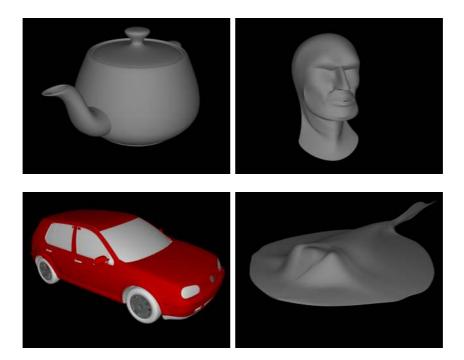

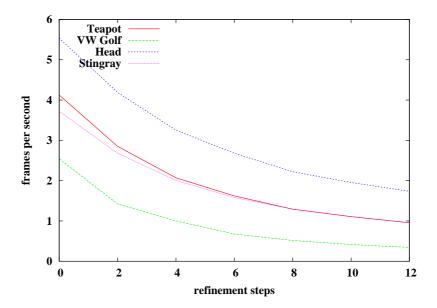

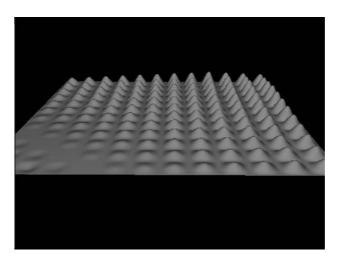

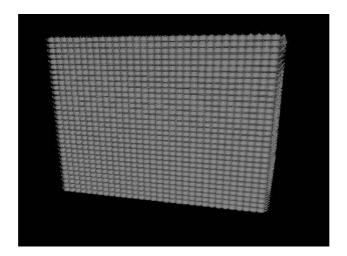

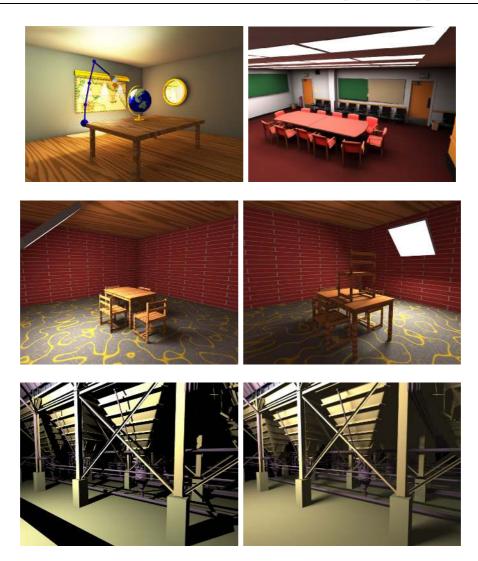

| 4.18<br>4.19                                                                                 | Triangular example scenes                            |

|----------------------------------------------------------------------------------------------|------------------------------------------------------|

| 5.1<br>5.2<br>5.3                                                                            | Data structure for preprocessed triangle data        |

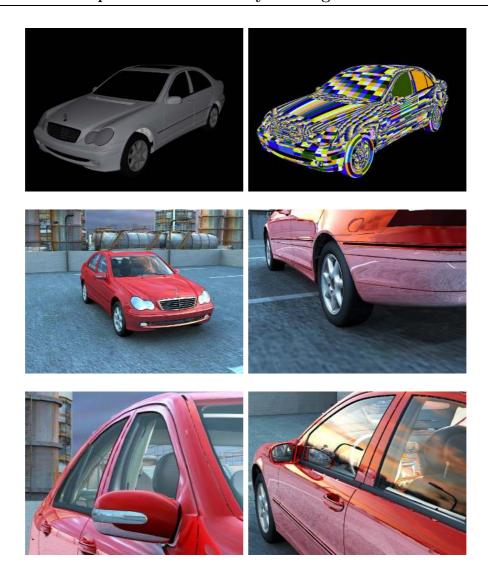

| 6.11<br>6.12<br>6.13<br>6.14<br>6.15<br>6.16<br>6.17<br>6.18<br>6.19<br>6.20<br>6.21<br>6.22 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6                                                       | Sorted list of split plane candidates                |

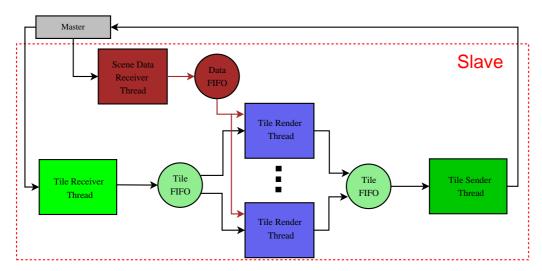

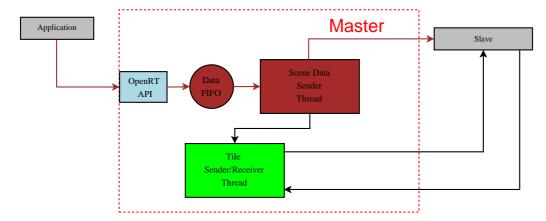

| 8.1<br>8.2                                                                                   | Slave implementation                                 |

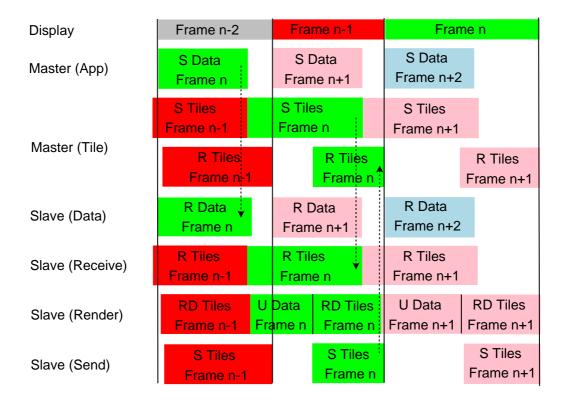

| 8.3 | Master/slave timing diagram                                     |

|-----|-----------------------------------------------------------------|

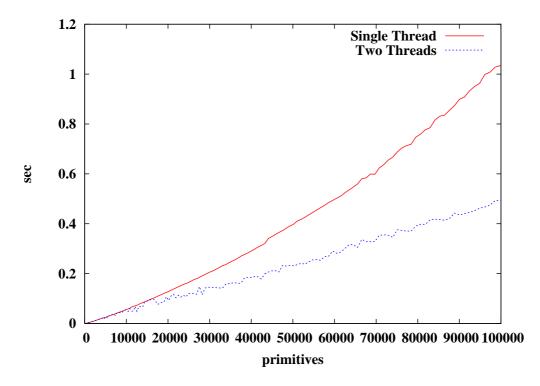

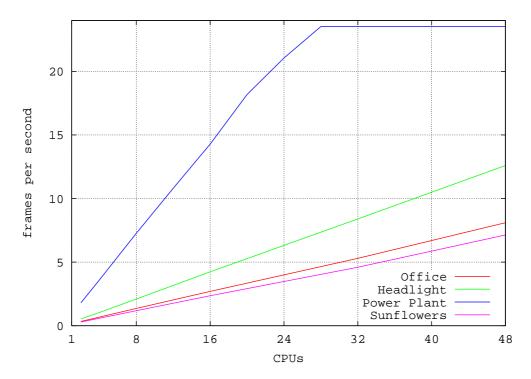

| 8.4 | Scalability in the number of CPUs                               |

| 9.1 | Instant radiosity and interleaved sampling 165                  |

| 9.2 | Combing primary and shadow rays                                 |

| 9.3 | Programmable procedural shading                                 |

| 9.4 | Efficient anti-aliasing                                         |

| 9.5 | Quality comparison with and without efficient anti-aliasing 170 |

| 9.6 | Scalability of the new instant global illumination system 173   |

| 9.7 | Interactive global illumination 174                             |

# **List of Tables**

| 3.1  | Current CPU architectures                                       |

|------|-----------------------------------------------------------------|

| 4.1  | Traversal and intersection steps in relation to bundle size 59  |

| 4.2  | Comparison of different traversal algorithms 62                 |

| 4.3  | Complexity of kd-tree entry point search 63                     |

| 4.4  | Mailboxing statistics                                           |

| 4.5  | Comparison between hashed and standard mailboxing 68            |

| 5.1  | Exit point probabilities                                        |

| 5.2  | Probability of full intersection test execution                 |

| 5.3  | Cycle cost for different triangle intersection tests 80         |

| 5.4  | Performance speedup by kd-tree entry point search 81            |

| 6.1  | Cycle cost for core operations (uniform refinement) 95          |

| 6.2  | Cycle cost of core operations (Newton iteration) 101            |

| 6.3  | Cycle cost of core operations for a four-ray bundle (Newton     |

|      | iteration)                                                      |

| 6.4  | Cycle cost for core operations (Bézier clipping)                |

| 6.5  | Reduction of patch data accesses in relation to bundle size 128 |

| 6.6  | Speedup by tracing ray bundles (uniform refinement) 130         |

| 6.7  | Speedup in relation to the resolution (uniform refinement) 130  |

| 6.8  | Single ray statistics (Newton iteration)                        |

| 6.9  | Single ray statistics (Bézier clipping)                         |

| 6.10 | Single ray statistics (Krawczyk-Moore)                          |

| 6.11 | Four-ray bundle statistics (Newton iteration)                   |

| 9.1  | Performance comparison between the two instant global illu-     |

|      | mination systems                                                |

| 9.2  | Performance of the new instant global illumination system 172   |

# Chapter 1 Introduction

In the context of computer graphics, the term *rendering* refers to the process of generating a two-dimensional image from a three-dimensional virtual scene. Rendering forms the basis for many fields of today's computer graphics, e.g. computer games, visualization, and graphical effects used for movie productions. Based on the algorithm used for the rendering process, two major rendering categories can be classified: rasterization-based rendering and ray tracing-based rendering.

For decades, ray tracing has been used exclusively for high-quality rendering, where it has been known for its long rendering times. Therefore, ray tracing's sole application has been off-line rendering. On the other hand, the field of interactive rendering has been dominated by rasterization-based hardware rendering.

Beyond any doubt, the key factor for the non-existence of ray tracing in terms of interactive rendering has been its poor performance. Researchers have long argued that thanks to its logarithmic behavior in scene complexity, ray tracing could eventually become faster than rasterization-based rendering; nevertheless its performance has been far from challenging. However, if enough parallel compute power was available, even the performance of ray tracing has been able to reach interactivity [Keates95, Muuss95a, Muuss95b, Parker99b]. Unfortunately, a large scale supercomputer was required to provide enough compute power.

In recent years, researchers have once again focused on the performance of ray tracing [Wald01c, Wald03e, Wald04, Reshetov05], in particular with a focus on off-the-shelf hardware. They have concentrated on an efficient and optimized implementation of the ray tracing algorithm and its data structures with respect to the advantages and disadvantages of current hardware architectures. The efficient combination of algorithmic and hardware-specific

optimizations has allowed ray tracing's performance to be lifted to an interactive level while running on off-the-shelf hardware [Wald04].

Note that implementations of ray tracing exist for other architectures such as GPUs [Purcell02, Foley05], or even custom hardware [Schmittler02, Schmittler04, Woop05]. However, they are still too slow (GPUs) or not widely available (custom hardware), so the current processor architectures are considered as the most suitable hardware platform.

The main difficulty when using processor-specific optimized algorithms in order to achieve high performance ray tracing is that they are not easy to explain in general, especially not from a high-level view.

This thesis presents the latest approaches and algorithms for realtime ray tracing on current processor architectures. The intention when writing this thesis was to avoid a strictly high-level view but to give exact and detailed information about low-level implementation issues and optimizations. Where possible, example code is provided for each illustrated algorithm.

The main contributions of this thesis to the field of ray tracing are

- SIMD-optimized algorithms for the traversal of coherent rays,

- a detailed analysis and SIMD-optimized implementation of intersection algorithms for rays with different geometric primitives such as triangles and bicubic Bézier patches,

- an algorithm for handling fully dynamic scenes by fast building of spatial index structures,

- a parallelization framework for ray tracing that achieves linear scalability in the number of connected computing nodes,

- and a ray tracing-based system that allows for interactively computing global illumination.

All algorithms illustrated in this thesis are an integral part of the OpenRT ray tracing library [Wald02a, Dietrich03, Wald04].

Even though some of the techniques discussed in this thesis have already been sketched in [Wald04], they will be discussed here in more detail, while, in particular, focusing on low-level implementation aspects.

The code examples provided in this thesis have already been optimized for high performance, but there is still much room for further optimization. Even though optimizing might take time and "cost nerves", it can sometimes be the key factor in order to lift algorithms to a new performance level.

### 1.1 Outline of this thesis

The thesis starts with a brief introduction to ray tracing and its use for rendering in Chapter 2. The chapter also provides a high-level performance analysis of the ray tracing algorithm and introduces the benefits of coherence and CPU architecture-specific optimizations.

Chapter 3 discusses current CPU architectures in detail. As these architectures build the underlying hardware platform for the implementation of all algorithms proposed in this thesis, special emphasis is put on performance issues and useful coding guidelines. The chapter introduces SIMD instructions, which will be an essential tool for exploiting the full compute power of current CPU architectures.

Increasing ray tracing performance in particular requires an efficient traversal through a spatial index structure. Therefore, Chapter 4 proposes highly optimized algorithms for efficient traversal of coherent sets of rays. In combination with optimized triangle-intersection algorithms that have been modified to efficiently support coherent sets of rays, as illustrated in Chapter 5, interactive ray tracing performance for ray tracing of triangular scenes will be achieved on a single processor.

Chapter 6 shows that interactive ray tracing is not limited to triangular scenes and presents various highly efficient intersection algorithms for bicubic Bézier patches in detail. These algorithms will be discussed in depth showing their advantages and disadvantages in terms of performance and accuracy.

Chapter 7 demonstrates that even the construction algorithm for spatial index structures can be efficiently optimized. A highly optimized implementation in particular allows for handling fully dynamic scenes by reconstructing the corresponding kd-tree from scratch for every frame.

Compensating the need of ray tracing for compute power means combining the compute power of multiple processors. Chapter 8 thus proposes a parallelization framework that effectively distributes the rendering work to a cluster of off-the-shelf PCs. As this framework has been designed for handling high-latency interconnections, linear scalability in the number of connected PCs will be achieved, increasing the performance of ray-tracing to a realtime level.

If the techniques for achieving realtime ray tracing, as discussed in the previous chapters, are combined with a global illumination algorithm that has been exclusively modified to exploit these techniques, it becomes possible to achieve interactive global illumination. Chapter 9 illustrates this modified global illumination algorithm and the surrounding framework.

Finally, this thesis ends with a short summary, and an outlook on the future of realtime ray tracing on future processor architectures.

# **Chapter 2**

# Introduction to Ray Tracing

This chapter starts with a brief review of the basic ray tracing algorithms (see Section 2.1) in order to provide a quick introduction to the field of high performance ray tracing. For a more detailed introduction to the field of ray tracing, please refer to one of the classical ray tracing books [Glassner89, Glassner95, Shirley03, Pharr04].

After illustrating how ray tracing is efficiently applied as a rendering algorithm (see Section 2.2), general performance and optimization techniques are discussed (see Section 2.3). These consolidated findings on ray tracing performance allows better access to the role of coherence (see Section 2.4). Besides hardware-specific optimizations, coherence in all its appearances (see Section 2.4.1 and Section 2.4.2) is the key factor for increasing ray tracing performance to a realtime level.

# 2.1 The Ray Tracing Algorithm

In order to avoid confusion, the term ray tracing or core ray tracing is defined here as an algorithm for finding the closest intersection between a ray and a set of geometric primitives, e.g. triangles [Glassner89, Badouel92, Erickson97, Möller97, Shoemake98, Shirley02, Wald04] or freeform patches [Sweeney86, Parker99b, Nishita90, Martin00, Wang01, Benthin04]. According to the ray equation R(t) = O + t \* D, where O is the ray origin and D the ray direction, the ray tracing algorithm returns the intersection with the smallest distance  $t_{min} \in [0, \infty)$ . Other ray tracing algorithms that, for example, return all intersections along a ray will not be considered in this thesis. The smallest distance  $t_{min} \geq 0$  corresponds to the closest intersection with respect to the ray origin. The actual intersection point can be easily obtained by evaluating

the ray equation using  $t_{min}$ . Note that the algorithm can easily be adapted so as to accept only intersections that lie in a given distance range  $[t_{start}, t_{end}]$ .

Using a brute force approach by testing all primitives within a scene against the ray and comparing the resulting intersection distances, is only an option if the number of primitives is small. Unfortunately, the typical number of primitives per scene ranges from thousands to millions making the brute force approach for realtime rendering impractical.

A well-known optimization technique consists in applying spatial subdivision. Spatial subdivision splits the virtual scene into spatial cells and stores for each cell the geometric primitives contained within. Note that only those primitives that are contained in the spatial cells intersected by the ray need to be tested. The advantage of this approach is that only a small subset of all spatial cells has to be considered for a given ray. Moreover, a typical scene includes large regions of empty space, so that for most rays only a small number of non-empty cells have to be considered. Exploiting spatial subdivision allows for significantly reducing the required primitive tests per ray, but also introduces the new problem of quickly identifying those cells that are intersected by the ray. The data structures required for the spatial sorting of geometry are called spatial index or spatial acceleration structures.

Algorithms for quickly identifying intersected cells are called ray traversal algorithms. Note that only those spatial cells have to be traversed which are pierced by the ray when starting from its origin and following the ray direction. Keeping to such a traversal "direction" allows for efficiently finding the closest intersection without touching any cells beyond that point. Exiting the traversal at the closest intersection is called early ray termination. Early ray termination can save many traversal and intersection steps (for the cells beyond the closest intersection point), but also requires a front-to-back traversal order of all cells that are intersected by the ray.

Researchers have proposed many different spatial index structures such as bounding volume hierarchies [Rubin80, Kay86, Haines91, Smits98], uniform, non-uniform, and hierarchical grids [Fujimoto86, Amanatides87, Gigante88, Jevans89, Hsiung92, Cohen94, Klimaszewski97], octrees [Glassner84, Samet89, Cohen94, Whang95], axis-aligned BSP (binary space partitioning) trees, short kd-trees [Sung92, Subramanian90a, Bittner99, Havran01], and ray direction sorting techniques such as ray classification [Arvo87, Simiakakis95]. These techniques either sort the primitives within a scene hierarchically (bounding volume hierarchies) or subdivide the space spanned by the primitives hierarchically (grids, octrees, kd-trees).

As a result, finding the closest intersection point between a ray and a set of geometric primitives includes the front-to-back traversal of a spatial index structure and the intersection tests for the corresponding primitives.

## 2.2 Ray Tracing for Rendering

The core ray tracing algorithm represents the fundamental basis for many ray tracing-based rendering algorithms. The common task of all these rendering algorithms is to compute a two-dimensional image from a three-dimensional virtual scene. As ray tracing is well suited for accurately simulating the distribution of light by simulating the propagation of photons, most ray tracing-based rendering algorithms focus on providing high image realism by closely simulating the illumination within the virtual scene. The realism within the generated image largely depends on how accurately the rendering algorithm takes into account both the illumination (by light sources) and the surface properties (of the scene's geometry). As a general rule, the higher the desired accuracy, the more rays have to be shot during simulation.

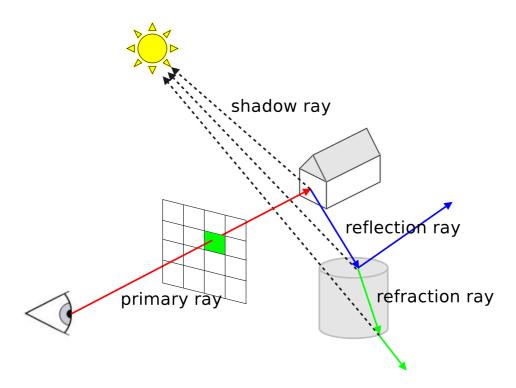

In order to give a better understanding of how rendering algorithms rely on the core ray tracing algorithm, a brief illustration of the standard *recursive* ray tracing approach [Whitted80] (see Figure 2.1) is presented next.

Generating a two-dimensional image from a three-dimensional scene using recursive ray tracing comprises several steps: From a virtual camera (typically corresponding to a one-eyed imaginary observer), rays are created and shot through each pixel of a virtual image plane. These rays are called primary rays, because they are created first. For each primary ray, the core ray tracing algorithm returns the closest intersection, in the following simply called hit or intersection point, with the geometry of the scene.

In order to determine the light at an intersection point that is reflected in the (inverse) direction of the ray, the illumination at a given point has to be computed first. Afterwards, the illumination must be combined with the material properties of the underlying geometry. The process of determining the interaction of light with the material properties at an intersection point is called *shading*. Note that the light reflected at the intersection points of primary rays determines the final pixel color.

The decision of whether a light source contributes illumination to a given hit point or not can be based on a simple occlusion test: A ray is shot from a hit point towards a virtual light source (or vice versa), and only if no intersection occurs along the way, the light source will contribute to the illumination. As these rays determine whether a given hit point lies in shadow or not, they are called shadow rays. For the occlusion test itself, the core ray tracing algorithm can be used once more, but it might be useful to slightly modify the algorithm. For shadow rays, the determination of the intersection with the smallest distance  $t_{min} \in [0, distance(light source)]$  is not mandatory; instead, any intersection with a distance  $t \in [0, distance(light source)]$  will be sufficient. This allows for more efficient ray termination because as soon

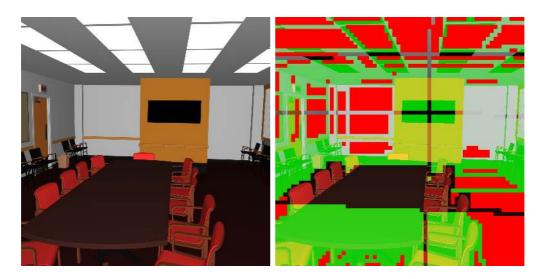

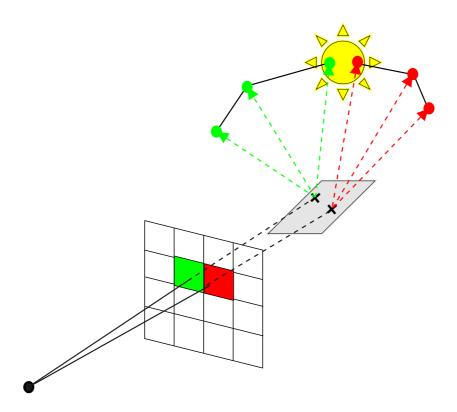

Figure 2.1: Simplified illustration for recursive ray tracing: A primary ray is generated from a virtual camera and shot through each pixel of the image plane. The intersection closest to the ray origin is determined and tested for illumination by the light sources (the green shadow rays). Depending on the material properties of the intersected geometry and the incoming illumination, the current intersection point is shaded and potential reflection or refraction rays are generated. For each of these secondary rays, the contribution is recursively evaluated in the same way as for primary rays.

as an appropriate intersection is found, the ray tracing algorithm can be terminated.

Based on the material properties of the geometry and the underlying rendering model, additional secondary rays can be generated to simulate effects such as reflection or refraction. Depending on their purpose, these rays are also called *reflection rays* or *refraction rays*. The contribution of secondary rays to the current hit point is recursively evaluated. Even though these rays are called secondary rays, they are essentially treated the same way as primary rays.

Apart from this traditional and simple approach to recursive ray tracing, countless variations exists for ray tracing-based rendering [Glassner89,

Glassner95, Shirley03]. For example, Cook extended the recursive ray tracing approach to support additional effects such as glossy reflection, illumination by area light sources, motion blur, and depth of field. This extended approach is called distribution ray tracing [Cook84a]. More advanced algorithms even compute the complete global illumination within a scene, including indirect illumination and caustic effects [Cook84b, Lafortune93, Cohen93, Veach94, Veach97, Jensen01, Shirley03, Dutre03]. Even though the purpose and supported accuracy of each algorithm is different, the key point is that they all heavily rely on the core ray tracing algorithm as their fundamental base.

# 2.3 Ray Tracing Performance

Looking at the organization of ray tracing-based rendering, it becomes clear that all algorithms require to trace a massive number of rays. Casting only a single primary ray per pixel at a resolution of  $1024 \times 1024$  results in over one million rays per image. In particular, each ray must locate the correctly intersected primitive in a scene of (typically) millions of primitives. A performance level that allows for generating multiple images per second requires therefore a very fast implementation of the core ray tracing algorithm.

Section 2.1 illustrated that the core ray tracing algorithm basically consists of two coupled operations: traversal of a spatial index structure and ray primitive intersection tests. This is why the performance of the core ray tracing algorithm largely depends on the total number of required traversal and intersection operations. Obviously, the cost of these operations is closely related to their implementation in terms of the underlying hardware architecture.

If one has a closer look at the core ray tracing algorithm in terms of computational and memory-related operations, it becomes clear that a ray traversal step mainly involves data-dependent computations. Given the current traversal state, which corresponds to a location within a spatial index structure, a new state (location) is computed based on the ray data and the data loaded from the spatial index structure. As traversal states depend on data from the spatial index structure, a data dependency exists.

For a single intersection computation, the same data dependency applies (loading primitive data from memory first, then performing intersection computation). However, multiple intersection tests in a given spatial cell do not depend on each other, so that the loading of primitive data and intersection computation can be interleaved or even done in parallel.

The main problem of memory-related operations is that the data access latency might be the limiting factor. Prior to any traversal or intersection

operation, the required data has to be loaded from memory first. For an implementation on a current CPU architecture, this could become critical due to the discrepancy between the memory latency of on-chip cache and system memory (a more detailed discussion will be given in Chapter 3). Ensuring a large number of data accesses to the on-chip cache is essential to achieve high performance.

#### 2.4 Coherence

Defining the term *coherence* is not a trivial matter, as its meaning depends to a great extent on the environment where it is applied. Nevertheless, the following definition illustrates the term *coherence* in a non-restricting way:

**Definition**: Coherence is the degree of which parts of an environment or its projections exhibit local similarities [Foley97].

Transferring the definition of coherence into the context of ray tracing, raises the question of which parts of ray tracing exhibits local similarities. In order to answer this question step by step, the search for coherence is first restricted to the core ray tracing algorithm. Later, the search is extended to the shading process which forms another major part of a ray tracing-based rendering system.

## 2.4.1 Ray Coherence

Defining ray coherence as the degree of spatial deviation within a set of rays, a statement on coherence in the context of traversal and primitive intersection becomes possible.

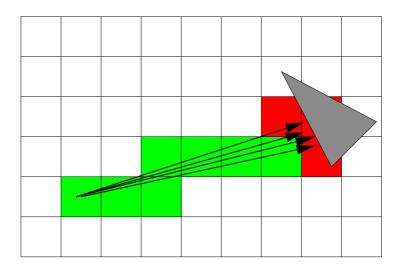

More precisely, a set of coherent rays (see Figure 2.2) will basically travel through the same spatial regions, and thus access the same data of the spatial index structure. The same holds true for the intersection test, where a set of coherent rays will basically test similar primitives. As a result, one can define traversal coherence for a set of rays as the ratio between the number of spatial cells traversed by all rays (as entity) and the sum of cells traversed by any ray. In the same manner, one can define intersection coherence for a set of rays as the ratio between the number of intersection tests performed by all rays (as entity) and the number of intersection tests performed by any rays.

The higher the traversal and intersection coherence the higher the probability of loading the same data, exploiting the memory cache hierarchy of current CPU architectures. In this case, traversal and intersection coherence translate into *memory coherence*.

2.4 Coherence

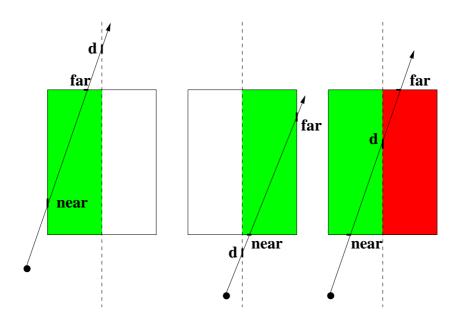

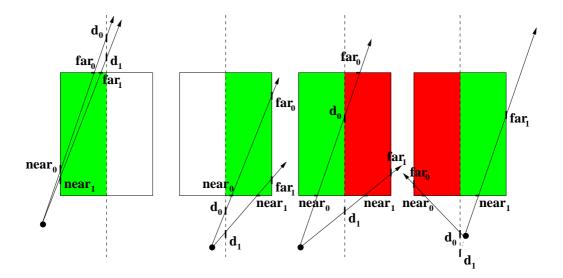

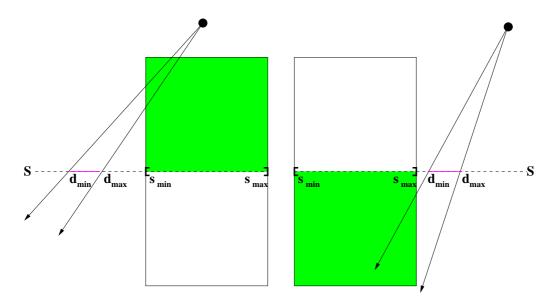

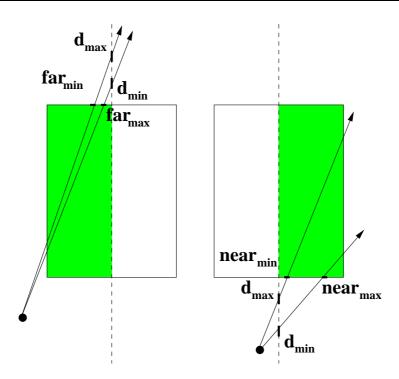

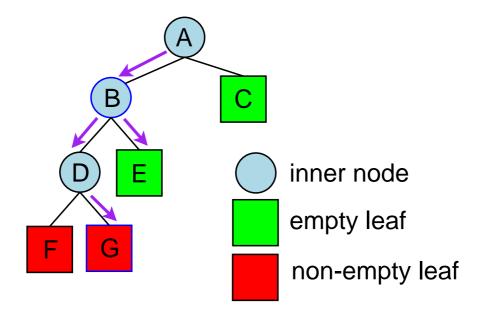

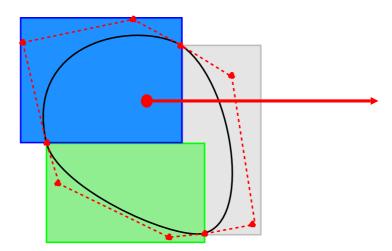

Figure 2.2: Exploiting ray coherence for ray tracing: A set of coherent rays will essentially follow the same path through the spatial index structure (green cells = accessed by all rays, red cells = accessed by some rays), and will essentially test the same primitives for intersection. This allows for efficiently amortizing memory accesses over all rays in a set.

Having data in the cache shortens the access latency for the individual rays within a set, but does not reduce the required number of memory accesses itself. A simple way of approaching this problem is a change in the way in which rays are handled. Instead of tracing rays individually, it is more beneficial to trace them together as a set.

As illustrated in Section 2.3, the core ray tracing algorithm involves many data-dependent computations and therefore numerous memory accesses. Coherent sets of rays allow for efficiently reducing the number of memory accesses due to the high probability that all rays within the set request the same memory (memory coherence), while the cost of the memory access itself is amortized over all rays within a set. As no dependency exists between the rays of a set, the traversal and intersection operations are suitable for parallel processing. In the following, a set of coherent rays is called a *coherent bundle*, *bundle* or *packet*.

Special attention must be given to the fact that an algorithmic or implementation-based overhead for supporting ray bundles does not offset the corresponding benefit. Therefore, the following three requirements must be fulfilled in order to fully exploit the advantages of coherent ray bundles for the core ray tracing algorithm:

- **Spatial Index Structure:** The spatial index structure and the corresponding traversal algorithm must efficiently support ray bundles. The traversal algorithm in particular should avoid any complex computations.

- Ray Bundle Traversal: An implementation of ray bundle traversal (with respect to a chosen spatial index structure) must minimize any overhead due to inefficient mapping to the underlying hardware architecture. Ideally, the hardware architecture and its corresponding instruction set should optimally support an implementation.

- Ray Bundle Intersection: Similar to a traversal implementation, an intersection implementation has to efficiently support ray bundles. As different types of geometric primitives can exist in the same scene, ray bundle intersection algorithms should efficiently support various primitive types.

In the case no efficient ray bundle intersection algorithm can be found for a given primitive type, the fall-back solution of intersecting the rays sequentially might be acceptable.

Chapters 4, 5, and 6 will provide a detailed discussion of data structures, algorithms, and the corresponding implementations that fulfill all these requirements.

## 2.4.2 Shading Coherence

Besides the actual core ray tracing algorithm, the shading process also benefits from local similarities. Considering for example the hit points of neighboring primary rays which are likely to intersect the same primitive. Even if this is not the case, it is very likely that the hit points are in the same spatial region. In addition, the probability that the intersection points share the same shader, and therefore perform similar shading operations is very high. Similar shading operations could be performed in parallel, again allowing for processing the shading of intersection points in bundles.

Sharing the same shader implies additionally that the loaded data exhibits similarities as well. For example, look-ups to the same texture for neighboring intersection points are likely to provide a high degree of memory coherence, which in turn allows for the efficient use of caches.

As a result, the shading process itself can benefit from coherence; however, similar to the core ray tracing algorithm, bundle shading for intersection points is prone to overhead caused by inefficient implementation.

2.5 Conclusions 13

### 2.5 Conclusions

This chapter has demonstrated that the key to pushing ray tracing performance to a realtime level is an efficient support of coherent ray bundles combined with a highly optimized implementation. A sub-optimal implementation in particular is likely to offset any benefit offered by tracing bundles. Unfortunately, current CPU architectures in combination with their supporting compilers are not intended to support the required degree of efficiency out of the box. On the contrary, without any manual effort in optimizing algorithms and implementation code, there is only little chance of ever reaching the desired performance level.

In order to avoid hardware and software-specific implementation pitfalls, it is beneficial to examine the architecture of current CPUs more closely (see Chapter 3). Taking specific CPU-related issues into account allows for an efficient implementation of the core ray tracing algorithm. In particular, the optimized implementation includes the extension of the traversal algorithm (see Chapter 4) and the primitive intersection tests (see Chapter 5 and Chapter 6) for efficiently supporting ray bundles.

A difficult task for a ray tracing-based rendering system is to gather coherent ray bundles. Coherent bundles of primary rays can easily be generated when relying on a typical (perspective) camera model, where primary rays of neighboring pixels exhibit a large degree of coherence. The same holds true for the shadow rays generated towards a single point on a light source. However, for most secondary rays, e.g. those generated by reflection off of curved surfaces and even refraction rays, coherence will be significantly lower than for primary rays. In the case of low coherence, coherence-based regrouping or even falling back to tracing individual rays may be necessary.

Instead of trying to extract coherent ray bundles out of a traditional ray tracing-based rendering system, one can design the rendering system in such a way that the majority of rays can be combined directly in coherent bundles (see Chapter 9). Such a system allows for minimizing the overhead for generating coherent bundles. If for such a system the majority of rendering time is spent in the core ray tracing algorithm, total system performance will directly benefit from fast ray bundle tracing.

# Chapter 3 CPU Architectures

Optimizing program code basically consists of two steps: Identifying the program's hot spots and trying to modify the corresponding code sequences. The difficulty thereby is to modify the code in such a way that the modified version shows better run-time behavior (with respect to the underlying hardware architecture) than the original one. This requires identifying code structures that cannot be efficiently executed. Identifying and modifying makes code optimization a difficult and time-consuming task which requires in-depth knowledge of the underlying architecture. Apart from architectural issues, code optimization additionally depends on the chosen compiler.

Nevertheless, the benefits of code optimization can be tremendous. Statistics have shown that the increase in performance between optimized and non-optimized code can range from a few percent to entire orders of magnitude.

In order to avoid costly performance penalties in critical code sequences, it is essential to have a detailed knowledge of the execution flow within the underlying CPU architecture. Therefore, a brief overview of performance-related issues of today's CPU architectures will be given in Section 3.1. Having identified the architecture related issues allows for formulating the general coding guidelines of Section 3.2. Section 3.3 introduces the concept of SIMD instructions, while Section 3.4 discusses compiler and performance profiling-related tools.

## 3.1 Performance Issues

For historical reasons, the majority of today's software has been designed for non-parallel execution. Because of this, current CPU architectures are designed to execute serial program code as fast a possible. With every new CPU generation, designers have tried to achieve a continuous performance increase by introducing small architectural enhancements to optimize serial execution. The key factor to increase performance has been the raising of the CPU clock rate (up to 3.8 GHz for latest Pentium-IV [Intel01]). Having a higher clock rate allows for (potentially) executing more instructions within a fixed time period. Raising the clock rate could only be realized through smaller micro structure designs which require extremely long executing pipelines (the Pentium-IV uses a pipeline with more than 30 stages).

These long executing pipelines are the major drawback of the high clock rate architectures. If the utilization of the execution pipeline is low, the performance of the CPU itself will be low, too. Even though the analysis and optimization of execution bottlenecks is a quite complex topic, the main reasons for low pipeline utilization, and thus low performance, can be roughly classified into the following categories:

Cache Misses: The difference in access latency between on-chip memory cache and main memory itself is tremendous, e.g. the Pentium-IV has an L1 cache latency of 1-4 cycles, an L2 cache latency of 20-27 cycles, and a latency to main memory of over 200-300 cycles. Obviously, this can result in pipeline stalls whenever data does not reside in the memory cache hierarchy. CPU architectures follow multiple ways of reducing the impact of cache misses by having large and multiple cache levels to reduce the probability of cache misses, and by executing independent program code during idle periods. For serial program code, the search for, and the execution of, independent instructions is often referred to as out-of-order execution. On the other hand, techniques such as simultaneous multi-threading or hyper-threading [Intel02c] use the implicit parallelism of thread execution to fill pipeline stalls with independent instructions.

Branches: The negative impact of long executing pipelines comes into play when dealing with conditional branches. Every time a branch is wrongly predicted, the complete pipeline has to be flushed. Branch prediction (over multiple levels) and even branch prediction by branch hint instructions are able to lower the probability. Nevertheless, every mispredicted branch means a "waste" of up to 30 cycles for a 30-stage execution pipeline. Even though the negative performance impact is lower than for cache misses it is still significant. This particularly affects complex and branch-intensive code.

Low Instruction Level Parallelism: Multiple instruction pipelines and functional units combined with out-of-order execution even allow the serially operating CPU to execute multiple independent instructions in

| Processor         | Intel Pentium-IV      | AMD Opteron              |

|-------------------|-----------------------|--------------------------|

| Pipeline Stages   | 20-31                 | 12-17                    |

| Reorder Buffer    | 126 Entries           | 72 Entries               |

| Units             | 2 Int, 1 FP, 3 LS     | 3 Int, 3 FP, 2 LS        |

| SIMD              | MMX, SSE, SSE2, SSE3  | MMX, SSE, SSE2, SSE3     |

| Register          | 16 Int, 8 FP, 16 SIMD | 16 Int, 8 FP, 16 SIMD    |

| Caches (I, D, L2) | 12k $\mu$ OPs, 8-16k, | 64k, 64k,                |

|                   | 512k-2M               | 1M                       |

| Branch Prediction | 4k BTB                | 16k BHT + 2k BTB         |

| Memory Bandwidth  | $6.4~\mathrm{GB/s}$   | $6.4~\mathrm{GB/s}$ +    |

|                   |                       | 3x  HyperTP  (3.2  GB/s) |

| Frequency         | 1.5-3.8 GHz           | 1.4-2.6 GHz              |

Table 3.1: Specifications of current 64-bit processor architectures, e.g. Intel's Pentium-IV (EM64T) and AMD's Opteron (X64). Both architectures feature a high pipeline length (varying due to different lengths for integer and floating pipelines) and large caches. Both architectures include special hardware units, such as Branch Target Buffers (BTB) and Branch History Tables (BHT), to achieve a better branch prediction rate. Large caches and advanced branch prediction units are the most effective components (of these architectures) to keep the long pipelines busy.

parallel (within a single clock cycle). This feature is typically called instruction level parallelism (ILP). Code dependencies appear when an instruction requires the output of a preceding instruction as input, while the output is not available at this point (mostly due to instruction latency). A sequence of dependent instructions is called a dependency chain. Dependency chains frequently appear in inefficient and complex code, but long latency instructions such as divisions, function calls, operating system-related or input/output instructions can also contribute to these chains.

In order to lower the effect of the three above-mentioned bottleneck categories, the most recent CPU architectures feature large on-chip caches and special hardware components to keep pipeline utilization high (see Table 3.1). Unfortunately, the improved hardware support is not able to overcome the effects of inefficiently written code. Even though modern compilers [Intel02a, GNU] try to rearrange the instructions in a more suitable way, the optimum in run-time performance can only be achieved by optimizing data structures and algorithms manually to the underlying hardware architecture.

The road map of the leading CPU manufacturers makes it clear that the length of the pipeline, and thus the frequency of future CPUs is not likely to grow significantly, and may even decrease. Therefore, future CPU designs will rely on increased execution parallelism such as multiple pipelines and functional units, execution threads, and in particular many cores in order to increase performance. Introducing multiple cores will widen the gap between memory latency/bandwidth and compute power dramatically. As each core will access the main memory via the same memory interconnect, future algorithms will need to reduce their required memory bandwidth.

# 3.2 Coding Guidelines

The performance impact of inefficiently written code ranges from a few percent to entire orders of magnitude, largely depending on the code itself. Even though the following coding guidelines seem obvious, it is worth outlining them to reduce the probability of significant performance penalties:

Data Locality and Memory Access Pattern: Localizing memory access ensures high cache hit probability. In situations where large chunks of memory need to be loaded, a qualified memory access pattern such as pure sequential access should be applied. Sequential access is efficiently supported by the hardware prefetching unit, available on all current CPU architectures. In certain situations, it is beneficial to manually apply CPU-supported prefetch instructions in order to load chunks of memory in advance. As memory prefetching is done asynchronously to the execution flow, the loading latency can be hidden by working on data already residing in the cache hierarchy. Obviously, the mechanism only works if the memory loading latency is smaller than the computation time between subsequent prefetches.

Simple Control Flow: Replacing branch-frequent code by conditional move sequences avoids mis-predicted branches. However, if the probability of a branch mis-prediction is sufficiently low (something which depends largely on the code), applying branches can be faster than applying conditional moves, because the execution of a correctly predicted branch has almost no costs. In contrast, conditional move sequences may require the computation of results which may not even be used later. On a more higher level, critical run-time loops should be kept as small and as simple as possible. Simply dropping or replacing complex instructions such as divisions or functions calls in inner loops can dramatically speed up performance. Having only a minimum of code dependency

chains within the inner-most loop body can additionally increase instruction throughput. Furthermore, small and simple inner-loops can be more easily optimized and maintained.

Data Level Parallelism: In order to maximize performance, data level parallelism by SIMD (single instruction multiple data) instructions should be applied. SIMD instructions offer a simple and easy way to manipulate multiple data elements at once. In particular, Intel's SSE instruction set [Intel01, Intel02b, Intel02a] allows for manipulating four single precision floating point or integer values using a single instruction. The main issues when using SIMD instructions are the required layout changes of input data and the necessary recoding of the algorithm (see Section 3.3).

Data level parallelism via SIMD instructions is currently the only way of explicitly performing parallel operations on a sequentially operating CPU (see Section 3.3). Instruction level parallelism, on the other hand, is performed internally by the CPU (out-of-order execution). It can only be influenced implicitly by reordering code for a more appropriate out-of-order executing flow.

In contrast to single-threaded applications, coding guidelines for multithreaded applications should also contain guidelines for thread synchronization. In order to efficiently exploit multiple CPUs (or CPU cores), synchronization points (such as mutex lock/unlocks [Nichols96]) should be kept to a minimum. Roughly speaking, synchronization means serialization, and long serialization periods dramatically reduce the positive effect of parallel execution.

Multi-threaded performance is further affected whenever *implicit synchronization* is required. Implicit synchronization occurs when caches on different CPUs need to be synchronized. Even though the interconnects between CPUs offer a high bandwidth for synchronizing cache areas, the performance impact can still be very high. Due to the fact that the synchronization granularity is based on cache-lines, unintended cache synchronization can be avoided by assuring that synchronization-relevant data exclusively occupies complete cache-lines.

# 3.3 Data Level Parallelism by SIMD Instructions

The basic concept behind SIMD instructions is the idea that many algorithms (see Figure 3.1) could work on multiple data elements in parallel. Instead of processing each data element by a single instruction in a sequential manner,

Figure 3.1: Computing a dot product of four three-component floating point vectors with standard C/C++ code. As no dependencies exists, the computation (for each component of 'dest') can be performed in parallel. Note that the code does not implement a generic dot product, but rather a simplified version where only one input vector is used for both dot product elements.

one could apply the same operation to multiple elements in parallel using a single instruction.

Applying SIMD requires that no dependencies exist between the data elements in a processing group. Moreover, controlling program execution by conditional branches brings about certain changes: Instead of basing the branch on the result of a single condition, SIMD instructions compute the results of multiple conditions in parallel. Obviously, one could extract the result of a single condition and perform the branch with respect to it, but very often it is more beneficial to perform the branch based on a condition regarding all results.

SIMD features are available on almost all current processor architectures [Intel02b, AMD03, AltiVec, IBM05], but only *Intel's Streaming SIMD Extension* will be considered in the following. Nevertheless, all code examples in this thesis can be easily ported to a different SIMD extension.

## 3.3.1 Intel's Streaming SIMD Extension (SSE)

For historical reasons, floating point operations on x86 architectures have been executed using the FPU (floating point unit). FPU registers have been

organized in a stack-like structure, causing reorganization overhead for executing floating point operations. With the introduction of the Pentium-III, Intel for the first time offered SIMD features with its Streaming SIMD Extension (SSE) [Intel02b].

| $X_{0}$   | $X_{\scriptscriptstyle 1}$ | $X_{2}$   | $X_3$     | xmm0            |

|-----------|----------------------------|-----------|-----------|-----------------|

| $Y_0$     | Y <sub>1</sub>             | $Y_2$     | $Y_3$     | xmm1            |

| $X_0+Y_0$ | $X_1+Y_1$                  | $X_2+Y_2$ | $X_3+Y_3$ | addps xmm0,xmm1 |

Figure 3.2: Intel's streaming SIMD extension allows for manipulating four data elements via a single instruction, e.g. adding four single precision floating point values.

SSE allows for operating on multiple data elements, usually on four 32-bit data elements, for the cost of one. Besides the advantage of data level parallelism, dropping the stack-like register organization in favor of a linear addressing model further accelerates operations further.

The standard SSE instruction set allows for operating on four single precision floating point values via a single instruction. SSE implementations of current processors, e.g. Pentium-IV internally execute only two single precision floating point operations in parallel, i.e. four operations in a  $2 \times 2$  way. This hardware implementation is currently limiting the SSE instruction throughput, but is likely to be removed from future architectures [Intel05].

The latest extension to the instruction set, called SSE2 [Intel01] and SSE3 [Intel03], also makes it possible to manipulate four 32-bit integer, eight 16-bit integer, sixteen 8-bit integer, or two 64-bit double precision floating point values via a single instruction. As these instruction do not play a major role in the example implementations, they are not discussed in any more detail.

All SSE registers (8 to 16, depending on the architecture version) are 4 \* 32 = 128-bit wide. These registers are usually referenced by xmm0 to xmm7 (or xmm15). Figure 3.2 shows a simple example of adding two SSE registers (four single precision floating point values per register) using a single instruction.

SSE introductions work most effectively in the vertical way, as shown by Figure 3.2. The horizontal way is more difficult due to the lack of appropriate horizontal instructions. For example, a short sequence of instructions is required to sum up all four register elements (see Section 3.3.3). Even though

the latest architectures [Intel03] offer direct support for horizontal operations, they are not as efficient implemented as vertical operating instructions.

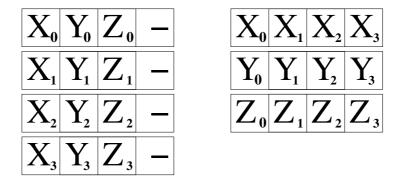

Figure 3.3: Left: For many algorithms, e.g. computing dot products, the standard array-of-structure (AOS) layout does not ensure optimal SSE utilization (the right-most element is not used). Right: The structure-of-array (SOA) layout is more beneficial as it optimally supports vertically operating SSE instructions.

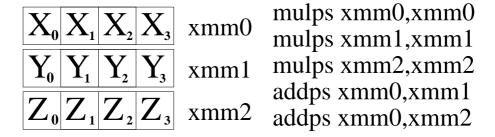

As a consequence, the layout of data and the implementation of algorithms should be rearranged to allow for as many vertical instructions as possible. As an example, vertex data should be stored in the *structure-of-array* (SOA) format instead of the *array-of-structure* (AOS) format (see Figure 3.3). Figure 3.4 shows that using the structure-of-array data layout, four dot products can be efficiently implemented by using only five instructions. The array-of-structure data layout would require more than double the number of instructions (because of the required shuffle operations).

Figure 3.4: The structure-of-array (SOA) data layout allows for efficiently using SSE instructions, e.g. computing four (simple) dot products in parallel (similar to the code in Figure 3.1) using only 5 instructions.

If the array-of-structure layout as input format cannot be avoided, a corresponding transposition into the structure-of-array can be performed on-the-fly. The transposition code consists of a sequence of shuffle and load instructions. The decision of whether the overhead introduced by the rearrangement of register elements is tolerable or not largely depends on the code. If the code following the transposition is sufficiently long, the introduced overhead can be effectively amortized.

Another important factor concerning efficient coding with SSE instructions relates to the rearrangement of instructions in terms of their throughput and latency. In particular, conditional branches based on a comparison between SSE registers require a manual transfer of the resulting bit mask (see Section 3.3.2) from an SSE register to a general purpose register. This transfer suffers from an high latency and should therefore be used carefully. On the other hand, coding in terms of instruction throughput is essential for avoiding resource conflicts of computational units. Throughput and latency vary across x86 architectures (and their variants), making general coding optimizations difficult. Fortunately, modern compilers allow for reordering code with respect to a specific processor without much manual effort.

Another important limitation of SSE instructions is the lack of scatter/gather operations for loading and storing data. Loading or storing individual register elements requires a sequence of loading and shuffle operations, because only the lowest register element can be handled as a standard scalar register.

### 3.3.2 SSE Intrinsics

One possible way to benefit from SSE instructions is to directly rely on assembly programming, but this procedure would be too inflexible and error-prone. On the other hand, modern C/C++ compilers (see Section 3.4) offer autovectorization of standard C/C++ program code. Even though this allows for programming in standard C/C++ code, the output typically will not reach the quality of hand-written code. Furthermore, the compilers often fail to auto-vectorize loops because of unresolvable dependencies (from the compiler's view) within the loop body. A more efficient way that combines both the quality of hand-written assembly code and the high-level interface of C/C++ code are SSE intrinsics [Intel02a]. Intrinsics are C/C++ function-style macros, which can be used directly with C/C++ constructs and variables. During compilation, the compiler automatically takes care of register allocation, result propagation, intermediate usage, etc.

Due to the fact that the compiler takes care of SSE register and memory allocation, the programmer can focus on the algorithmic implementation

Figure 3.5: Intrinsics allow for effectively using SIMD instructions with C/C++ constructs. This small routine computes four (simple) dot products (similar to the code in Figure 3.1) in parallel using SSE intrinsics.

itself (see Figure 3.5). Moreover, the compiler is able to perform architecture-specific optimizations, e.g. considering throughput and latency optimizations. Most SSE intrinsics map to a single SSE instruction, others are composed of a short sequence of SSE instructions.

Given the importance of SSE instructions for efficient coding, the most frequently used instructions will be discussed in more detail. Note that scalar operating intrinsics, operating only on the lowest register element, differ from their full counterpart only through the \_ss-suffix instead of the \_ps-suffix.

**Arithmetic Instructions** For addition, multiplication, subtraction, and division of four single precision floating point values, the intrinsics  $\_mm\_add\_ps$ ,  $\_mm\_mul\_ps$ ,  $\_mm\_sub\_ps$ ,  $\_mm\_div\_ps$  are used. Reciprocal operations are also useful, e.g.  $\_mm\_rcp\_ps$  and  $\_mm\_rsqrt\_ps$ , which perform the 1/x and 1/sqrt(x) operations. These special instructions are faster than a real division or square root. The speed increase comes at the expense of reduced accuracy because the result is computed based on approximating algorithms. Nevertheless, the reduced accuracy can be increased afterwards by performing a Newton-Raphson iteration [Intel02b] (resulting in a short sequence of additional instructions). Breaking up costly long-latency instructions such as real divisions or square roots into a short sequence of short-latency instructions is more advantageous for exploiting instruction level parallelism.

**Load/Store Instructions** Loading one single or four single precision floating point values can be performed using the intrinsics <code>\_mm\_load\_ss</code> and <code>\_mm\_load\_ps</code>. Note that the argument of <code>\_mm\_load\_ss</code> and <code>\_mm\_load\_ps</code> is a pointer to a float or float array. Additionally, <code>\_mm\_load\_ps</code> requires that the address is aligned on a 16-byte boundary to ensure maximum performance (less efficient non-aligned access can be implemented by <code>\_mm\_loadu\_ps</code>). The intrinsics <code>\_mm\_set\_ps</code> and <code>\_mm\_set\_ps1</code> use immediate float values as arguments. <code>\_mm\_set\_ps1</code> copies a single value into all four register elements. Note that loading four different float values into a single register by applying <code>\_mm\_set\_ps</code> and <code>\_mm\_rset\_ps</code> involves a sequence of shuffle instructions. Returning the lowest SSE register element as scalar float value can be performed by using the <code>\_mm\_cvtss\_f32</code> intrinsic.

**Comparison Instructions** Comparisons between two SSE registers using the  $\_mm\_cmpXX\_ps$  (XX can be eq,lt,gt,...) return a mask where all bits of each register element are set to one if the result of the comparison is true and are set to zero otherwise. In combination with a sequence of logical instructions, the returned bit mask can be used to implement an element-based conditional move sequence.

Miscellaneous Instructions The \_mm\_shuffle\_ps intrinsic shuffles register elements within one single or across two registers (with certain restrictions). It is often necessary to apply a conditional jump based on the values of all four register elements. Therefore, \_mm\_movemask\_ps transfers the highest bit (the sign bit) of each register element to the four lowest bits of a general purpose register. If all register elements contain a comparison's bit mask, the transferred bits correspond to the comparison result. In order to quickly obtain the maximum and minimum values per register element, the \_mm\_max\_ps and \_mm\_min\_ps intrinsics can be used.

**Logical Instructions** The logical operations *or*, *and*, *xor*, and *notand* are realized by  $\_mm\_or\_ps$ ,  $\_mm\_and\_ps$ ,  $\_mm\_xor\_ps$ , and  $\_mm\_andnot\_ps$ .  $\_mm\_setzero\_ps$  allows for quickly setting all register elements to zero using a simple xor operation.

# 3.3.3 Using Intrinsics and Basic Data Structures

As discussed in Section 3.2, the performance impact of mis-predicted branches due to pipeline flushes can be critical. This holds especially true for SSE code sequences. In many cases, a conditional branch construct looks like:

IF condition THEN C=A ELSE C=B. An efficient way to realize these ifelse-constructs per SSE register element without branching is to apply bit masking (returned by an SSE-comparison) using a short sequence of logical instructions (see Figure 3.6).

Figure 3.6: Small utility functions increase the readability of SSE code significantly. The routine implements an - IF condition THEN C=A ELSE C=B - construct on register element level.

For the operation of computing the inverse of four single precision values in parallel, it is often beneficial to not apply a real division, but to use a reciprocal approximation combined with a Newton-Raphson iteration in order to increase the result's accuracy later on. Figure 3.7 shows the actual SSE implementation.

Figure 3.7: Fast inverse computation by using reciprocal approximation combined with a Newton-Raphson step in order to increase IEEE precision to 24 bits. In many cases, splitting up inverse computation into multiple instructions is faster than using an explicit division, because the instruction level parallelism of current CPUs allows for a efficient parallel execution with surrounding instructions.

Up to the latest Pentium-IV [Intel03] and Opteron processor generations, SSE instructions have been lacking direct hardware support for horizontal operations. Horizontal operations work on all elements of a single register and store the result in the lowest element. However, horizontal operations can be simulated using a sequence of instructions. As shown in Figure 3.8, a horizontal add requires at least four instructions. Similar utility functions compute horizontal sub, min, and max operations.

```

inline sse_t sseHorizontalAdd(const sse_t &a)

{

const sse_t ftemp = _mm_add_ps(a, _mm_movehl_ps(a, a));

return _mm_add_ss(ftemp,_mm_shuffle_ps(ftemp, ftemp, 1));

}

```

Figure 3.8: Many architectures do not offer SSE instructions for performing horizontal operations, e.g. adding all four register elements and storing the result in the lowest element. Instead, a short sequence of instructions emulates these horizontal operations.

Given the seamless integration of intrinsics into C/C++ code, it is beneficial to implement useful code sequence as small utility functions. These utility functions increase the readability of the SSE code significantly.

Another important point to consider is the fact that even coherence is highly important for implementing algorithms through SSE code. This is especially true for conditional branching based on the values of all four register elements (using the \_mm\_movemask\_ps instruction). In this case, decision-coherence which is defined as the probability that the comparison result in all four register elements is equal, is essential. Testing the sixteen possibilities by if-else or switch statements, where each case has equal probability, would typically result in many branch mis-predictions. Therefore, a high decision-coherence allows for arranging the comparison statements based on their probability. This efficiently reduces the amount of mis-predicted conditional branches.