# **Recent Developments in p-type Oxide Semiconductor Materials and Devices**

Zhenwei Wang, Dr. Pradipta K. Nayak, Dr. Jesus A. Caraveo-Frescas, and Prof. Husam N. Alshareef\*

Materials Science & Engineering, King Abdullah University of Science & Technology (KAUST), Thuwal 23955-6900, Saudi Arabia

E-mail: husam.alshareef@kaust.edu.sa

Keywords: p-type oxides, transparent electronics, thin-film transistors, oxide diodes, oxide CMOS

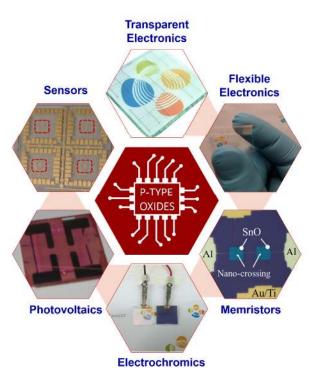

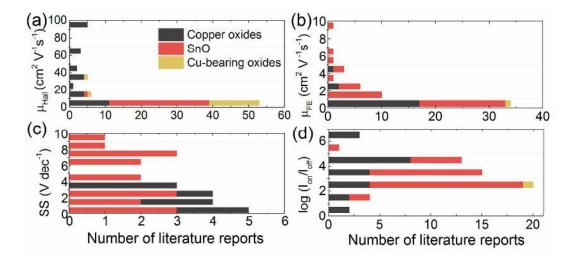

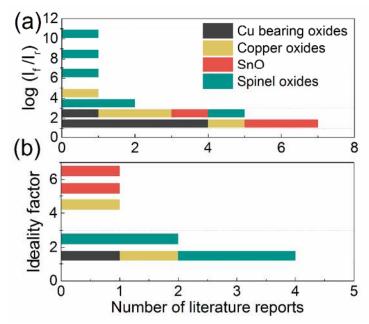

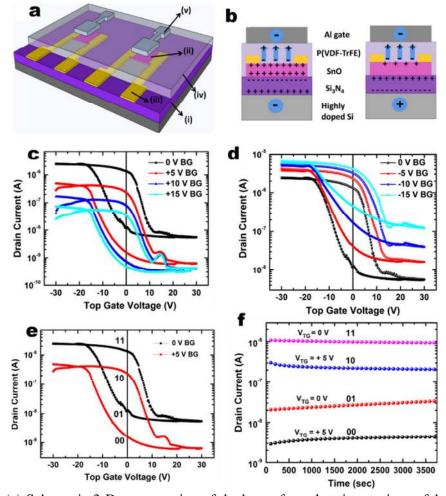

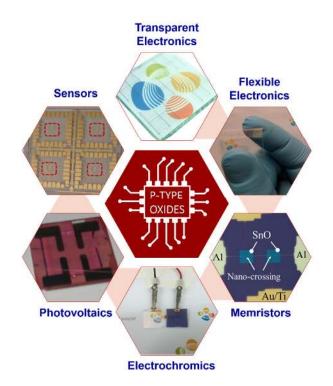

The development of transparent p-type oxide semiconductors with good performance could be a true enabler for a variety of applications, where transparency, power efficiency and more circuit complexity are needed. Such applications include transparent electronics, displays, sensors, photovoltaics, memristors, and electrochromics. Hence, we review recent developments in materials and devices based on p-type oxide semiconductors, including ternary Cu-bearing oxides, binary copper oxides, tin monoxide, spinel oxides and nickel oxides. The crystal and electronic structures of these materials are reviewed, along with approaches to enhance valence band dispersion to reduce effective mass and increase mobility. Strategies to reduce the interfacial defects, off state current, and material instability are discussed. Furthermore, we show that promising progress has been made in the performance of various type of devices based on p-type oxides. For example, transparent oxide-based p-n junction diodes have experienced significantly improved performance, where rectification ratios  $>10^7$  have been achieved. The performances of thin-film transistors and inverters have also been modestly improved. For example, thin-film transistors with field-effect mobilities exceeding 5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> have been reported. In addition, several innovative approaches were developed to fabricate transparent complementary metal oxide semiconductor (CMOS)

devices. These approaches include novel device fabrication schemes and utilization of surface chemistry effects, resulting in good inverter gains (as high as 120 has been demonstrated). Some progress has also been made in reducing the interfacial defects and off state currents using capping layers, high quality dielectrics and surface treatments. Resistive memory devices and hole transport layer in optoelectronic devices, mostly based on nickel oxide, have made decent progress. Transparent ferroelectric memory devices comprising p-type oxides have also been reported recently showing good hole mobilities (~3.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) and good retention characteristics. This even includes multistate memory devices that show good stability. Nanoscale (e.g. nanowire) devices have now been reported using p-type oxides and do show performance improvements at scaled device geometry. New process developments have been reported, and some p-type oxides can now be deposited using atomic layer deposition and chemical routes, with promising performances. However, despite these recent developments, p-type oxides still lag in performance behind the n-type counterparts, which have entered volume production in the display market. The recent successes along with the hurdles that stand in the way of commercial success of p-type oxide semiconductors are presented in this review.

#### Index

| 1. Introduction                                                 | 5  |

|-----------------------------------------------------------------|----|

| 2. Discovery and Synthesis of Hole-Transporting (p-type) Oxides | 7  |

| 2.1. Ternary Cu-bearing oxides                                  | 7  |

| 2.2. Binary copper oxides                                       | 12 |

| 2.3. Tin monoxide                                               | 14 |

| 2.4. Spinel type oxides                                         | 17 |

| 2.5. Nickel oxide                                               | 19 |

| 3. Device Basics for p-Type Oxides                              | 21 |

| 3.1. Thin-film transistors                                      | 21 |

| 3.2. CMOS inverters                                             | 27 |

| 3.3. p-n Junction diodes                                        | 29 |

| 4. Performance of p-Type Oxide Thin-Film Transistors            | 31 |

| 4.1. Ternary Cu-bearing oxide thin-film transistors             | 31 |

| 4.2. Binary copper oxide thin-film transistors                  | 31 |

| 4.3. Tin monoxide thin-film transistors                         |    |

| 4.4. Nickel oxide thin-film transistors                         | 50 |

| 4.5. Stability of p-type oxide thin-film transistors            | 52 |

| 5. Performance of Oxide Based CMOS Inverters                    | 57 |

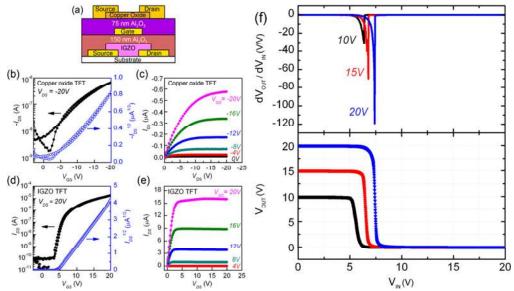

| 5.1. Binary copper oxide CMOS inverters                         | 58 |

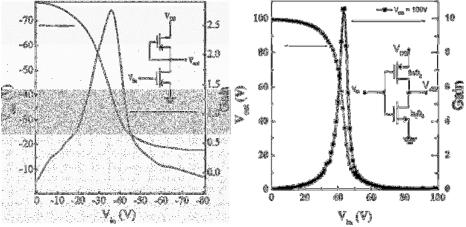

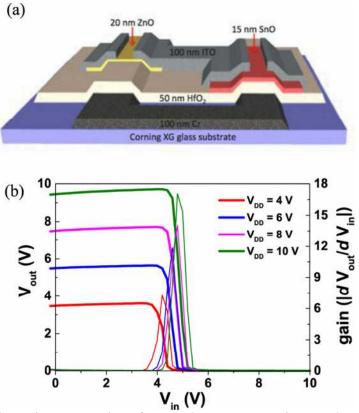

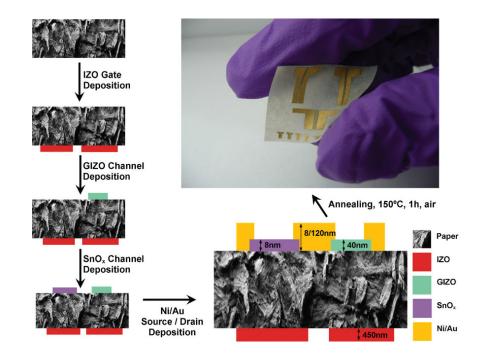

| 5.2. Tin monoxide CMOS inverters                                | 58 |

| 6. Performance of Oxide Based p-n Junctions                     | 63 |

| 6.1. Ternary copper bearing oxide p-n junctions                 | 64 |

| 6.2. Binary copper oxide p-n junctions                          | 65 |

| 6.3. Tin monoxide p-n junctions                                 | 66 |

| 6.4. Spinel oxide p-n junctions                                 | 68 |

| 6.5. Nickel oxide p-n junctions                | 69 |

|------------------------------------------------|----|

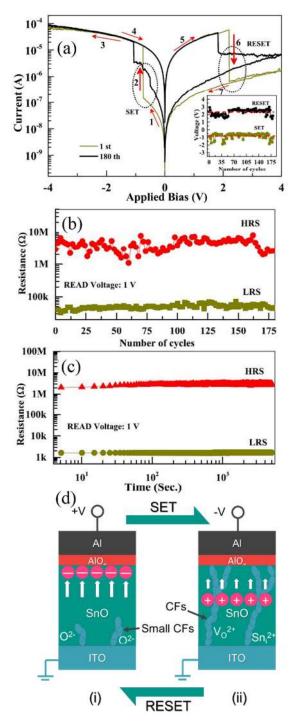

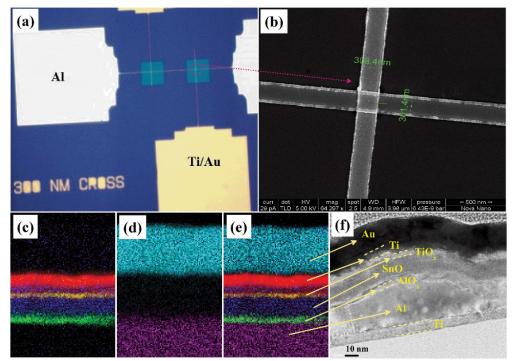

| 7. Memory Devices using p-Type Oxides          | 70 |

| 7.1. Resistive switching memory                | 70 |

| 7.2. Ferroelectric field-effect memory devices | 72 |

| 8. Miscellaneous applications of p-type oxides | 74 |

| 8.1. Hole-transporting layer                   | 74 |

| 8.2. Electrochromics                           | 75 |

| 8.3. Gas sensors                               | 76 |

| 9. Conclusions and Perspective                 | 78 |

| Acknowledgements                               | 80 |

| References                                     | 81 |

#### **1. Introduction**

Combining the visible range transparency and electrical conductivity, transparent conducting oxides (TCOs) and transparent semiconducting oxides (TSOs) in principle hold great potential in a variety of applications, including solar cells, solid-state sensors, flat panel displays, smart windows, electrochromics, transparent and flexible electronic devices. <sup>[1-5]</sup> For example, by employing high performance TSOs, transparent displays with higher pixel density (higher resolution) and higher refreshing frequency can be realized. <sup>[1, 6]</sup> In addition, using TSOs and TCOs, energy-efficient displays can be constructed which operate in standard lighting environments, where they may allow getting rid of the panel backlight which accounts for around 90% power consumption in current displays.<sup>[1, 6]</sup> Further, a variety of transparent electronic devices that may be deployed in security or entertainment applications will benefit greatly from developing better performing TSOs and TCOs (**Figure 1**).

However, many of the potential transparent electronic applications are limited by the lack of the availability of high performance p-type oxide semiconductors.<sup>[6-9]</sup> Hence, only applications which can be realized by using unipolar devices (based on n-type semiconductors) are currently able to capitalize on the promise of transparent semiconducting oxides. If equally well performing p-type TSOs were also available, more energy efficient and more complex transparent devices and circuits can be fabricated. For example, if a transparent CMOS device with good performance can be realized, similar types of circuits can be fabricated like in silicon technology. This would usher in an era of transparent gadgets that could affect many facets of our daily lives.<sup>[10]</sup> This is because CMOS circuit holds many advantages when compared to unipolar transistors, including: low power consumption, low waste heat generation, high noise margin, high logic swing output, high circuit integration density and architectural simplicity.<sup>[11-15]</sup>

The difficulty in achieving p-type TSOs with similar performance to the n-type ones comes from the unique electronic configuration of oxide materials. For n-type oxides, oxygen vacancies produce enough electrons and the electrons transport path in the conduction band minimum (CBM) is mainly composed of metal s orbitals. These s orbitals are spatially spread and could result in sufficient hybridization even in amorphous structure by employing heavy metal cations, where the highly dispersed and delocalized CBM facilitates a low electron effective mass and thus high mobility.<sup>[2, 16]</sup> In contrast, in p-type oxides, the creation of positive carriers (holes) is limited by (i) the high formation energy of native acceptors that produce holes, such as cation vacancies; (ii) the low formation energy of native donors that annihilate holes, such as anion vacancies.<sup>[17]</sup> Even when a certain concentration of holes is available, the transport path for holes, valence band maximum (VBM), consists mainly of anisotropic and localized oxygen 2p orbitals, resulting in a large hole effective mass and low mobility. All these effects render the realization of high performance p-type oxides more challenging.<sup>[15, 18]</sup> The chemical design concept for obtaining p-type TSOs was proposed by Kawazoe et al. in 1997.<sup>[15, 19, 20]</sup> According to this concept, promising p-type oxides should hold cationic species with (i) closed shell (i.e.  $d^{10}s^{0}$ ) configuration to avoid coloration due to intra-atomic excitations and (ii) a comparable energy level to the oxygen 2p orbitals. The energy level of the d<sup>10</sup> closed shell electrons is expected to overlap with that of the oxygen 2p electrons in order to form covalent bond, which could alleviate the localization of VB edge. The essence of this concept is to delocalize the VBM by forming the hybridization level between d levels of metal cations and 2p levels of oxygen anions. Also, tetrahedral coordination of oxide ions in some layered structures (e.g. delafossites) is believed to further reduce the localization of VB edge and avoid colorization from the d-d transition of adjacent Cu atoms. Following this principle, a series of novel p-type oxides with delafossite structure were discovered, namely CuMO<sub>2</sub> (M= Al, Ga and In, etc) and SrCu<sub>2</sub>O<sub>2</sub> (non-delafossite structure). However, due to the presence of high VBM tail state, these Cu based oxides

suffered from either low hole mobility or unsuitable carrier concentrations.<sup>[15, 21-30]</sup> As a consequence, the chemical design concept was extended to the layered compounds with higher covalency of the Cu-chalcogen (Ch) interactions (LaCuOCh);<sup>[30-33]</sup> however, these materials still exhibited relatively high hole densities, which indicates that the p-channel cannot be effectively depleted and that these materials are not suitable for electrical switching applications like thin-film transistor (TFT). An alternative approach to attain high performance p-type oxides is to employ pseudo-closed ns<sup>2</sup> orbitals of metal cations that have similar energy levels close to the oxygen 2p orbitals and form strong hybridization. Such candidates include lead oxide (PbO), beryllium oxide (Bi<sub>2</sub>O<sub>3</sub>), and tin monoxide (SnO). While Bi<sub>2</sub>O<sub>3</sub> exhibited low hole mobility and PbO was reported with n-type conductivity,<sup>[8, 9]</sup> SnO has shown a promising p-type performance and has attracted more attention. The relatively higher hole mobility in SnO is largely due to the low defect formation energy of Sn vacancies (V<sub>Sn</sub>), which serve as acceptors, and to the creation of a suitable dispersed VBM by the hybridization of Sn 5s and oxygen 2p orbitals. At the very top of VBM, contribution from the spatially spread Sn 5s orbitals dominates, which results in a potentially promising p-type transparent oxide.<sup>[18, 34, 35]</sup> In fact, soon after the theoretical discovery of hole-transporting nature of SnO, p-type TFTs were successfully fabricated with relatively high hole field-effect and Hall mobility values.<sup>[6-9, 36, 37]</sup> Along with SnO, cuprous oxide (Cu<sub>2</sub>O) has also been known as a promising p-type oxide for long time and still holds the best p-type Hall mobility value, which exceeds 100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>[38]</sup> The p-type character of Cu<sub>2</sub>O has been theoretically studied and is largely attributed to the formation of copper vacancies. Cu<sub>2</sub>O holds a unique band structure, where the VB is composed of fully occupied hybridized levels from the Cu 3d and O 2p orbitals. The very top of VBM is mainly composed of the Cu d-states, which creates less localized hole transport pathway.<sup>[17, 39-42]</sup> Beyond the delafossites, Cu<sub>2</sub>O, and SnO, Hautier et al. recently reported a new class of ternary oxides which they have predicted to be very good p-type oxide candidates, but few studies exist on these oxides.<sup>[43, 44]</sup>

#### 2. Discovery and Synthesis of Hole-Transporting (p-type) Oxides

#### 2.1. Ternary Cu-bearing oxides

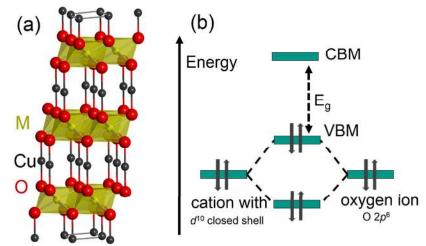

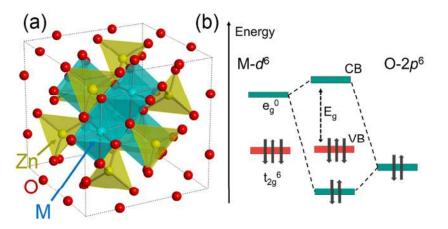

As discussed in the introduction, the valence band (VB) in oxide materials is made of the deep and localized oxygen 2p orbitals, which are responsible for the poor hole transport in oxide materials. Introducing covalent bonds between metal cations and oxygen anions is believed to alleviate this localization at the VB edge in accordance with the chemical design concept (CDC) proposed by Kawazoe et al.<sup>[15, 20]</sup> From the point of forming considerable covalency, the energy level of the d shell electrons should be comparable with that of the oxygen 2p levels. For better transparent device applications, cations with closed shell levels  $(d^{10}s^{0})$  are good candidates since this kind of electronic configuration can avoid the absorption in the visible range from the so-called d-d transitions.<sup>[20]</sup> Cu and Ag have the appropriate d<sup>10</sup>s<sup>0</sup> states for the above mentioned requirements. The edge of VB becomes the antibonding level after the formation of considerable covalency, since both cation and anion hold closed shell electronic configurations (Figure 2b).<sup>[19]</sup> In this way, a more dispersed VB and a small hole effective mass can be achieved. Another factor that must be considered in the search for optimal p-type oxides is the crystal structure, which determines the coordination and the spatial stacking of the cations and anions. For one, the oxygen coordination is critical, since oxygen anion is the main contributor (O 2p) to the localization of holes. Tetrahedral coordination is preferred due to the fact that in this kind of system all eight electrons (including  $2s^2$ ) of oxygen are participating in the four  $\sigma$  bonds, i.e. sp<sup>3</sup> hybridization.<sup>[15, 19, 20]</sup> In this manner, further delocalization at VB edge can be achieved. The second factor for crystal structure consideration is related to the transparency. The layered Cu-bearing delafossite oxides (with the general formula CuMO<sub>2</sub> and space group  $R\bar{3}m$ ) consist of an alternating stack of Cu ion layers and MO<sub>2</sub> octahedral layers along the c axis (Figure 2a). This structural arrangement made them an interesting group of oxides to study due to the

significant decrease in crosslinking between the  $Cu^+$  ions from three dimensions (as in  $Cu_2O$ ) to two dimensions (as in delafossites). This made it possible to enlarge the bandgap in these oxides by reducing the interaction between  $d^{10}$  electrons in neighboring  $Cu^+$  ions.<sup>[45]</sup> Based on these considerations,  $Cu^+$  based delafossites were identified as potentially promising transparent p-type oxides (**Figure 2**).

Following this material selection criteria, the first batch of p-type transparent delafossite oxide thin films were successfully demonstrated by pulsed laser deposition (PLD), reactive frequency or direct current magnetron sputtering (RF/DCMS), chemical vapor deposition (CVD), thermal evaporation (TE) and hydrothermal methods. The general chemical formula for these oxides can be expressed as  $CuMO_2$  (M=Al<sup>[15, 19, 46-48]</sup>,  $Ga^{[19, 22, 23, 49]}$ ,  $In^{[25, 50, 51]}$ ,  $Sr^{[49, 50, 51]}$ <sup>52]</sup>,  $Y^{[49, 52, 53]}$ ,  $Sc^{[49, 54-56]}$  and  $Cr^{[49, 53]}$ ). The validity of CDC model was also confirmed experimentally in CuAlO<sub>2</sub> by mapping the valence band structure using spectroscopic methods, leading to the discovery that the resultant VBM is dominated by Cu 3d level.<sup>[19, 45]</sup> Among the above mentioned Cu<sup>+</sup> based delafossites, CuInO<sub>2</sub> was reported with both a large optical band gap (3.9 eV) and bipolar property, where p- or n-doping can be achieved by Ca or Sn substitutions, which paved the way to build transparent oxide based p-n homojunctions.<sup>[24, 25]</sup> The physics behind the bipolar property and the large band gap was explained by Nie et al., where a large disparity between the fundamental indirect band gap and apparent direct band gap contribute to the bipolar doping.<sup>[57]</sup> For the p-type character of CuAlO<sub>2</sub>, Pellicer-Porres et al. and Tate et al. separately detected defect absorptions in the optical absorption spectra showing the copper vacancy  $(V_{Cu})$  to be responsible for the p-type conductivity.<sup>[58, 59]</sup> Nolan calculated the defect formation energy in CuAlO<sub>2</sub> by density functional theory (DFT) and found the V<sub>Cu</sub> with small formation energy was the most likely origin of the p-type character.<sup>[60]</sup> Scanlon et al. stated that the V<sub>Cu</sub> or Cu on Al antisites defect was the dominant defect under Cu-poor or Al-poor conditions, respectively.<sup>[61]</sup> Fang et al. and Luo et al. reported that the oxygen interstitial (O<sub>i</sub>) was a deep level defect and would not

contribute to the p-type conductivity.<sup>[62, 63]</sup> However, even after extensive efforts to search for  $Cu^+$  based delafossite materials, the conductivity of the delafossite films remained low, only ~10<sup>-2</sup> S cm<sup>-1</sup>. This was attributed to the fact that doping was ineffective in increasing the hole concentration and thus the conductivity of the delafossite oxides.

Another ternary Cu-bearing oxide material,  $\text{CuSr}_2\text{O}_2$ , was subsequently proposed.<sup>[26, 64]</sup> The p-type nature of  $\text{CuSr}_2\text{O}_2$  was studied by DFT, and the VBM was found to be formed by the hybridization between Cu 3d, 4s and 4p with O 2p levels.<sup>[64]</sup> It should be noted that  $\text{CuSr}_2\text{O}_2$  did not possess the delafossite structure but it held similar dumbbell-like Cu-O bonding, with an even lower dimension of Cu<sup>+</sup> ions crosslinking (only single chain), which should improve the transparency in the visible range. Another structural feature of this compound is that the strontium (Sr) ion is located inside an octahedron of six oxygen atoms, which could be substituted by elements such as potassium (K) to enhance the conductivity.<sup>[20, 26]</sup> As expected, K was successfully doped into  $\text{CuSr}_2\text{O}_2$  films, but the carrier concentration turned out to be lower than anticipated, and the conductivity of  $\text{CuSr}_2\text{O}_2$  remained low, ~10<sup>-2</sup> S cm<sup>-1</sup>. An advantage for the CuSr<sub>2</sub>O<sub>2</sub> is that the maximum processing temperature was only 300 °C, which could be extended to fabricate p-n junctions. Soon afterwards,  $\text{CuSr}_2\text{O}_2$  was successfully used in the fabrication of transparent oxide based p-n junctions with rectifying effect.<sup>[65]</sup> UV electroluminescent effect was also detected in p-n junctions of heteroepitaxially grown p-CuSr<sub>2</sub>O<sub>2</sub> on n-ZnO.<sup>[27-29]</sup>

However, these Cu<sup>+</sup>-based ternary p-type transparent oxides still suffered from low hole concentration and low carrier mobility, although considerable efforts has been exerted into the optimization of their electrical properties.<sup>[30]</sup> As a consequence, the chemical design principle was extended by using chalcogen (Ch) element p orbitals to replace the oxygen ones, since a more dispersed VB edge was theoretically expected from the hybridization between Cu 3d orbitals and the Ch p orbitals, due to the increasing covalency between Cu and ch atoms in the sequence of O, S, Se and Te.<sup>[33]</sup> Following this approach, the first attempt was shown using

sulfur to replace oxygen to reduce the localization of VBM. A layered oxysulfide LaCuOS was demonstrated with p-type conductivity and a large band gap of 3.1 eV.<sup>[31, 32, 66-70]</sup> The controllable cation substitution of LaCuOCh was also reported, and degenerate p-type conduction in LaCuOS<sub>1-x</sub>Se<sub>x</sub> (x=0 to 1) was shown with relatively high hole conductivity ( $\sigma$ ) and the hole concentration was around 2.2×10<sup>20</sup> cm<sup>-3</sup>. Further, a conductivity of 140 S cm<sup>-1</sup> was achieved by doping Mg<sup>2+</sup> ions at the La<sup>3+</sup> sites, while maintaining a Hall mobility of 4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>[71-73]</sup> Details about the fabrication technique for LnCuOCh (Ln = La, Pr or Nd; Ch = S<sub>1-x</sub>Se<sub>x</sub>) epitaxial films and related optical or electrical properties were reported by Hiramatsu et al.<sup>[74]</sup> Although p-n junctions were demonstrated using p-type LnCuOCh semiconductors, the high carrier concentrations (>10<sup>18</sup> cm<sup>-3</sup>) impeded their further application in thin-film transistor (TFT) devices, in spite of the high carrier mobility.<sup>[23, 71]</sup>

Recently, a remarkable Hall mobility of 39.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for p-type delafossite CuAlO<sub>2</sub> was reported by Yao et al., where a new strategy of alloying non-isovalent Cu-O dimer inside CuAlO<sub>2</sub> host was demonstrated.<sup>[75]</sup> The CuAlO<sub>2</sub> thin films were deposited from radio frequency magnetron sputtering (RFMS) with a CuAl alloy target at substrate temperature of 940 °C under various oxygen partial pressures. The Cu<sup>2+</sup>/Cu<sup>+</sup> ratio was tuned between 4.2 and 22.8% by controlling the RF power, while the optical band gap was also tuned from 3.36 to 3.87 eV. Hall mobility values from 8.6 to 39.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> were obtained, with the mobility values being inversely related to the Cu<sup>2+</sup>/Cu<sup>+</sup> ratio. The temperature-dependence resistivity measurement of all thin films showed similar behavior to pure CuAlO<sub>2</sub>, and the authors concluded that CuO clusters were embedded into the CuAlO<sub>2</sub> host lattice as Cu-O dimmers. The high Hall mobility was thus attributed to the modulation of the electronic structure of the host CuAlO<sub>2</sub> by the hybridization of Cu-O dimers, i.e. the partial substitution of less-dispersive Cu<sup>+</sup> 3d<sup>10</sup> (from CuAlO<sub>2</sub>) with more dispersive Cu<sup>2+</sup> 3d<sup>9</sup> (from CuO) orbitals in the VBM. Such film was also used to build a p-type TFT exhibit a field-effect mobility of 0.97 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.

The electrical and optical properties of p-type ternary Cu-bearing oxide or chalcogenide thin films are summarized in **Table 1**. It should be noted that the table only covered reports with reliable Hall mobility data.

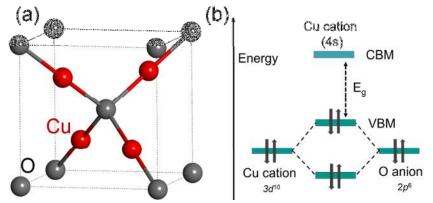

#### 2.2. Binary copper oxides

Copper oxides have two well-known forms, cuprous oxide (Cu<sub>2</sub>O) and cupric oxide (CuO). Cu<sub>2</sub>O has a cubic crystal structure (space group pn3m, a=4.27 Å), which consists of two interpenetrating diamond-like oxygen and copper networks, where Cu atoms are inserted between two consecutive body centered cubic (bcc) arrayed oxygen layers (Figure 3a). Each oxygen atom is surrounded by a tetrahedron of Cu atoms and each metal atom is two-fold coordinated.<sup>[39, 40, 78]</sup> For CuO, Cu<sup>2+</sup> forms four coplanar bonds with oxygen in the tenorite structure (monoclinic space group C2/c) with the lattice parameters of a = 4.684 Å, b = 3.425Å, c = 5.129 Å and  $\beta$  = 99.28°.<sup>[79, 80]</sup> It is reported that the optical band gap is 2.1-2.6 eV for Cu<sub>2</sub>O and 1.9-2.1 eV for CuO.<sup>[81]</sup> Both of them are reported to be p-type oxides, with several reports showing that Cu<sub>2</sub>O holds Hall mobility exceeding 100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>[38, 82]</sup> The p-type character of the Cu<sub>2</sub>O is attributed to the presence of Cu vacancy ( $V_{Cu}$ ), which introduces an uncompensated acceptor level. Interstitial oxygen (O<sub>i</sub>) atoms have also been pointed out as possible acceptor defects.<sup>[17, 40, 41, 78, 83]</sup> The high p-type mobility of Cu<sub>2</sub>O is related to the band structure near the top of VB. In the majority of metal oxides, the valence band is mainly formed by the localized and anisotropic O 2p orbitals, which leads to a low hole mobility.<sup>[15, 17,</sup> <sup>18]</sup> In contrast, the VB in Cu<sub>2</sub>O is composed of fully occupied level which is formed by the hybridization of Cu 3d and O 2p orbitals (Figure 3b). The very top of VBM is mainly composed of the Cu d sates, which creates less localized hole transport pathway.<sup>[17, 39-42]</sup> The p-type behavior of CuO has also been studied theoretically and is attributed to the presence of  $V_{Cu}$ <sup>[17, 40, 84-86]</sup> In the band structure of Cu<sub>2</sub>O, it has been reported that the most significant

defect levels were one acceptor level at 0.3 eV and a deep donor level at 0.9 eV from the VB edge.<sup>[78, 87]</sup> Due to the high solar spectral absorption coefficient, special energy band configuration, abundance and nontoxicity, copper oxides have been used in photovoltaic devices<sup>[88-98]</sup>, gas sensors<sup>[99, 100]</sup>, high T<sub>c</sub> superconductors<sup>[101, 102]</sup>, memory devices<sup>[103, 104]</sup> and lithium ion batteries<sup>[105, 106]</sup>. Due to the high Hall mobility of Cu<sub>2</sub>O<sup>[38]</sup>, the applications in TFTs<sup>[107]</sup> were also extensively studied after Matsuzaki et al. successfully demonstrated the first high field-effect mobility Cu<sub>2</sub>O p-type TFT by pulsed laser deposition (PLD).<sup>[82, 108]</sup>

The research on Cu<sub>2</sub>O has a long history and the fabrication of Cu<sub>2</sub>O thin films or nanostructures has been widely reported by various techniques, such as PLD<sup>[82, 108-115]</sup>, magnetron sputtering<sup>[38, 87, 92, 116-138]</sup> and thermal oxidation<sup>[94, 139, 140]</sup>; and chemical routes, such as electrodeposition<sup>[96, 141]</sup>, spin coating<sup>[142-146]</sup>, atomic layer deposition<sup>[147-149]</sup>, spray coating<sup>[150, 151]</sup>, molecular beam epitaxy<sup>[152]</sup>, microwave irradiation from Cu precursor<sup>[153]</sup>, chemical vapor deposition<sup>[154, 155]</sup> and ink printing<sup>[156]</sup>. A summary of the most promising studies on binary copper oxide thin films is shown in **Table 2**.

In **Table 2**, some of the Cu<sub>2</sub>O films grown by physical vapor deposition routes show pronounced Hall mobility ( $\mu_{Hall}$ ) values. Li et al.<sup>[38]</sup> reported a high  $\mu_{Hall}$  of 256 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in their Cu<sub>2</sub>O thin film deposited by magnetron sputtering at substrate temperature of 600 °C. Such a high mobility was achieved by introducing a low temperature buffer Cu<sub>2</sub>O layer, which controlled the growing preference and enlarged the grain size. Matsuzaki et al.<sup>[82, 108]</sup> optimized the growth temperature and oxygen partial pressure using PLD route, achieved a  $\mu_{Hall}$  of 90 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in epitaxial Cu<sub>2</sub>O thin films on (110) MgO substrate. Zou et al.<sup>[112]</sup> studied the deposition temperature of Cu<sub>2</sub>O by the PLD route, and a pure phase polycrystalline Cu<sub>2</sub>O was achieved at 500 °C, with a  $\mu_{Hall}$  of 107 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. However, the above mentioned high quality films were all deposited at high substrate temperature, which could complicate the device fabrication process. An alternative strategy was demonstrated by Fortunato et al.<sup>[87]</sup>, where the films were deposited at room temperature followed by a post

deposition annealing (PDA) process. The Cu<sub>2</sub>O phase composition was adjusted by tuning the oxygen partial pressure and the PDA process was shown to increase the crystallinity and grain size. A Hall mobility of 18.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> was achieved after annealing at 200 °C in air for 10 hrs. Chemical routes have also been demonstrated in fabricating Cu<sub>2</sub>O thin films with promising electrical performances. Jeong et al.<sup>[154]</sup> reported a Cu<sub>2</sub>O film with  $\mu_{Hall}$  over 30 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> by metal organic chemical vapor deposition (MOCVD) on ZnO coated glass at 400 °C. An increasing Hall mobility was found with larger grain sizes, indicating that the grain boundary scattering is a major contributor in limiting the electrical properties. Kim et al.<sup>[145]</sup> and Yu et al.<sup>[146]</sup> reported sol-gel methods to fabricate Cu<sub>2</sub>O thin films followed by a two-step thermal treatment in oxygen and nitrogen, where a  $\mu_{Hall}$  of 18.9 and 31.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> were reported, respectively. Kwon et al.<sup>[132]</sup> successfully fabricated Cu<sub>2</sub>O films in a plasma enhanced atomic layer deposition system, showing a Hall mobility of 37 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The successful fabrication of high mobility thin films using chemical routes was an encouraging development for p-type oxides.

However, for all reported Cu<sub>2</sub>O thin films, despite the encouraging Hall mobility values, a major concern is the low carrier concentration ( $\sim 10^{14}$  cm<sup>-3</sup>) and low optical band gap ( $\sim 2.4$  eV), which have limited the potential for Cu<sub>2</sub>O thin films in fully transparent electronics. **Table 2** summarizes the performance of binary copper oxide thin films reported in the past fifteen years.

#### 2.3. Tin monoxide

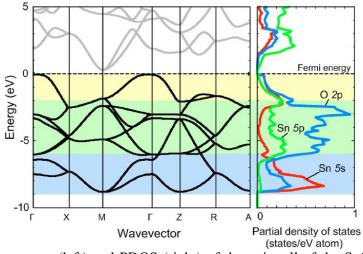

Two stoichiometric tin oxides with large optical band gaps and useful transparency have been identified for quite a long time (SnO and SnO<sub>2</sub>). The stable phase of SnO has a tetragonal litharge structure (P4/nmm space group), four O atoms and one Sn atom form a pyramid structure. The Sn atoms and O atoms arranged alternatively with layered structure in a  $Sn_{1/2}$ –O– $Sn_{1/2}$  layer sequence, van der Waals gap (lone pair electrons) exist in the open

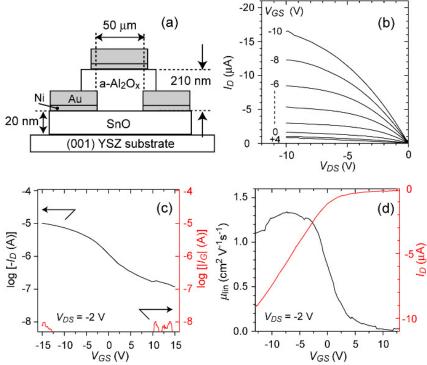

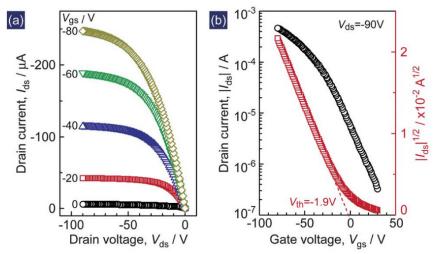

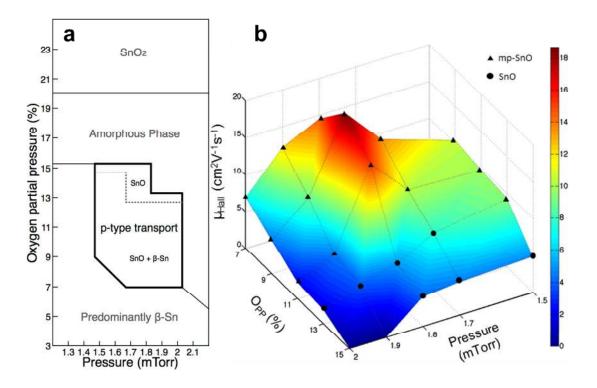

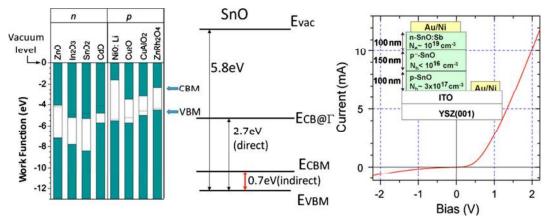

space between the Sn layers along the [001] crystallographic direction (Figure 4a).<sup>[9, 18, 34, 157,</sup> <sup>158]</sup> Before the discovery of p-type charge transport in SnO, most research activities were focused on SnO<sub>2</sub>, which held great potential in gas sensing, transparent passive and active electronic applications.<sup>[159-161]</sup> On the other hand, SnO was mainly targeted as anode material for Lithium batteries<sup>[162]</sup>, catalyst in organic synthesis<sup>[163]</sup>, and precursor for obtaining high quality  $SnO_2^{[164, 165]}$ . However, this situation changed after the publication of theoretical studies that revealed the p-type nature of SnO, which is attributed to the low formation energy of V<sub>Sn</sub> and a more dispersed VBM caused by the hybridization between oxygen 2p and spherical Sn 5s orbitals (Figure 4b and 5).<sup>[18, 34, 35]</sup> Soon afterwards, SnO was epitaxially grown on (001) yttria stabilized zirconia (YSZ) substrate by Ogo et al., showing a Hall mobility of 2.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and field-effect mobility of 1.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the first time.<sup>[8, 9]</sup> Since then, SnO has been receiving increasing attention because of its relatively high Hall mobility and the abundance, non-toxic nature of tin.<sup>[166]</sup> However, it is known that SnO has a fundamental stability issue, and it is very challenging to deposite it as a pure phase thin film.<sup>[7,</sup> <sup>8, 167-169]</sup> The physical properties were mainly reported from epitaxial SnO thin films deposited on (001) YSZ substrate by Ogo et al., including the optical band gap (Eg) of 2.7 eV by optical absorption measurement, and the fundamental (indirect) Eg of 0.7 eV by diffuse reflectance spectrum from SnO powder.<sup>[8]</sup> More detailed electronic properties were also studied by Ogo et al., including the ionization potential (5.8 eV), hole effective mass  $(2.05m_e)$ , and the thermal activation energy (45 meV).<sup>[9]</sup> Fortunato et al. reported p-type oxide TFTs using SnO deposited by room-temperature radio frequency magnetron sputtering (RFMS) process followed by an air ambient annealing. The annealed thin film and device exhibited a high Hall  $(4.8 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1})$  and field-effect  $(1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1})$  mobilities, suggesting that there was room to improve in the performance of SnO based device.<sup>[6, 7]</sup> This was followed by Guo et al. and Liang et al., who performed very detailed structural, optical and electrical studies on SnO thin films grown by e-beam evaporation (EBE).<sup>[36, 170-172]</sup>

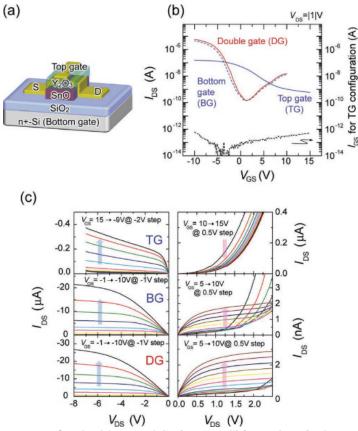

Although there have been several materials demonstrating ambipolar behavior, i.e. conducting both electrons and holes in the same channel, SnO is the only one that has been successfully used as a channel conducting both electron and hole currents in thin-film transistors.<sup>[173-176]</sup> Due to the co-contribution of spherically spread Sn 5s orbitals to the valence band maximum (VBM); Sn 5p orbitals to the conduction band minimum (CBM), and the suitable electronic structure, SnO is endowed with ambipolar property even without doping.<sup>[18, 173, 177, 178]</sup> There are two factors that contribute to the ambipolar behavior of SnO: valence/conduction band structure and energy band configuration. As mentioned before, the VBM of SnO is composed by hybridized Sn 5s and O 2p, the spherically spread Sn 5s orbital endows SnO with a relatively high hole mobility. At the same time, the CBM of SnO comes mainly from Sn 5p orbitals and the partial density of state (PDOS) curve shows a freeelectron-like band which indicates that electrons can also be conducted in SnO if enough electrons exist.<sup>[18, 179]</sup> Furthermore, in SnO, a small fundamental (indirect) band gap of ~0.7 eV and an optical (direct) band gap of 2.7 eV have been confirmed. Due to the presence of these two band gaps, both the large electron affinity and small ionization potential are attained, which are the desired criteria for n- and p-doping. <sup>[173, 177-179]</sup>

Fabrication of SnO thin films has been extensively evaluated using a series of methods, including physical vapor deposition (PVD) routes, such as PLD<sup>[8,9,21,173,177,178,180,181]</sup>, EBE<sup>[36,170,171,176]</sup>, RFMS<sup>[6,7,37,168,182-194]</sup> and DCMS<sup>[167,195-200]</sup> using Sn<sup>[6,7,14,167,168,180,183,185,187-189,191,193,197,201-213]</sup>, SnO<sup>[8,9,21,37,173,177,178,181,182,186,192,214-216]</sup>, SnO<sub>2</sub><sup>[36,165,169-171,175,179,190,217]</sup> targets on both rigid and flexible substrates. The Hall mobility, carrier (hole) concentrations, along with deposition conditions are listed in **Table 3** for relatively recent studies. It should be noted that only reports with reliable Hall mobility values are summarized in this table. Meanwhile, among the contents of **Table 3**, atomic layer deposition (ALD) method has been demonstrated by Han et al. for growing p-type SnO thin films, showing a polycrystalline structure and Hall mobility of 2.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>[218]</sup> Besides ALD, chemical routes like chemical vapor deposition

(CVD) and aerosol-assisted CVD were also successfully employed in the fabrication of the SnO thin films, however, no Hall measurement results were shown.<sup>[219, 220]</sup>

From **Table 3**, it is obvious that there are quite limited reports about the fundamental (indirect) Eg of SnO, although it is one of the most important parameters for a semiconductor. The weak optical absorption from the indirect transition is behind the difficulty in evaluating the indirect Eg, since not only a photon but also a phonon are needed to complete this transition. As already mentioned above, Ogo et al. firstly measured the indirect Eg to be 0.7 eV from powder SnO sample by diffuse reflectance spectroscopy.<sup>[8]</sup> After this, more efforts had been exerted to measure the indirect Eg values from thin film samples. Liang et al. measured a small indirect  $E_g$  of 0.5 eV by optical absorption from a polycrystalline SnO thin film capped by Al<sub>2</sub>O<sub>3</sub>.<sup>[172]</sup> Toyama et al. successfully demonstrated the measurement of indirect Eg of SnO by photoacoustic spectrum and photothermal deflection spectroscopy, with the result of 0.7 and 0.6 eV, respectively.<sup>[182, 215]</sup> Quackenbush et al. also studied this indirect Eg on SnO thin films using hard X-ray photoelectron spectroscopy (HAXPES) and the O Kedge X-ray emission/absorption spectroscopy (XES/XAS), where the occupied states (by HAXPES and XES) and unoccupied states (by XAS) could be measured separately. An indirect Eg of 0.7 eV was confirmed.<sup>[178]</sup> The optical properties of SnO are also presented in Table 3, including both the average transmittance in the visible range and  $E_g$  information (direct and indirect). The Seebeck measurement was also used to detect the majority charge carrier type in SnO thin films. Rather large Seebeck coefficients (S) were reported: +1.99 mV K<sup>-1</sup> (by Ogo et al.<sup>[9]</sup>), +479 uV K<sup>-1</sup> (by Hosono et al.<sup>[177]</sup>), +763 uV K<sup>-1</sup> (by Hayashi et al.<sup>[180]</sup>), and +1.69 mV K<sup>-1</sup> (by Jiang et al.<sup>[193]</sup>). This variation is likely due to the differences in carrier concentration and the variation in band structure originates from different deposition methods, film crystalline quality and orientations.

#### 2.4. Spinel type oxides

As previously discussed, the chemical design concept is based on combining closed shell metal d<sup>10</sup> orbitals with the oxygen p orbitals to achieve significantly delocalized VBM. Using closed shell metal cations can effectively avoid colorization from metal d-d or oxygen 2pmetal d transitions.<sup>[15]</sup> Considering the fact that transition metal ions (Co<sup>3+</sup>, Rh<sup>3+</sup>, Ir<sup>3+</sup>) with d<sup>6</sup> configuration in an octahedral crystal field will behave in low-spin configuration (ground state), i.e. the so-called "quasi-closed shell", these ions are expected to behave similarly to Cu<sup>+</sup> (d<sup>10</sup> closed shell) when bonding with oxygen.<sup>[30, 221-223]</sup> Due to the hybridization between oxygen 2p levels and metal d states, the latter will split into sixfold degenerate  $t_{2g}$  and fourfold degenerate  $e_g$  states, and a band gap between the above mentioned levels will emerge.<sup>[222, 224]</sup> Following this idea, a new class of p-type oxides named spinel oxides ( $ZnM_2O_4$ , M= Co, Rh and Ir) was discovered. The crystal structure of  $ZnM_2O_4$  spinel oxides (space group: cubic Fd3m) is shown in **Figure 6a**, where Zn and M atoms are tetrahedrally and octahedrally bonded with oxygen atoms, respectively. The band configuration is shown in Figure 6b.<sup>[225]</sup> Mizoguchi et al. reported a magnetron sputtered ZnRh<sub>2</sub>O<sub>4</sub> thin film of p-type conducting character with band gap of 2 eV and conductivity of 0.7 S cm<sup>-1.[222]</sup> The temperature dependent magnetic susceptibility showed that the electronic configuration of Rh 4d<sup>6</sup> was in the low spin state  $(t_{2g}^{6}e_{g}^{0})$ . The spectroscopic measurements revealed that the band gap was defined by the empty  $e_g^0$  (CB) and the fully filled  $t_{2g}^6$  (VB) subshell, the latter hybridizing with O 2p. Soon afterwards, Narushima et al. and Ohta et al. demonstrated high performance p-n junction diodes based on amorphous and epitaxial p-type ZnRh<sub>2</sub>O<sub>4</sub>, respectively, which attracted a wide attention to this new class p-type oxides.<sup>[226, 227]</sup> Kamiya et al. studies amorphous ZnRh<sub>2</sub>O<sub>4</sub> and proposed that the p-type conduction in the amorphous structure originated from the isotropic nature of spinel structure and the edge-sharing RhO<sub>6</sub> networks, which were less affected by the structural disorder and even stable in amorphous network.<sup>[228]</sup> In 2004, Kim et al. reported spinel oxide  $ZnCo_2O_4$  thin films prepared by magnetron sputtering with p-type conductivity.<sup>[229]</sup> In 2007, Dekkers et al. demonstrated the p-type nature

of spinel ZnM<sub>2</sub>O<sub>4</sub> (M= Co, Rh and Ir) thin films prepared by pulsed laser deposition (PLD), where an increase in both band gap and conductivity was reported with increasing quantum numbers (Co, Rh, Ir), with maximums of 2.97 eV and 3.39 S cm<sup>-1</sup> for ZnIr<sub>2</sub>O<sub>4</sub>.<sup>[230]</sup> In 2010, Kim et al. fabricated p-type ZnCo<sub>2</sub>O<sub>4</sub> thin film and related p-n junction diode by PLD with controllable electrical performance, showing band gap of 2.3 eV and conductivity of 21 S cm<sup>-1</sup>, while the carrier density could be tuned from 10<sup>16</sup> to 10<sup>20</sup> cm<sup>-3</sup> by controlling the oxygen pressure.<sup>[231]</sup> Recently, Grundmann and coworkers demonstrated high performance amorphous p-n junction diodes and junction field-effect transistors using p-type spinel oxide ZnCo<sub>2</sub>O<sub>4</sub> deposited at room temperature, indicating great potential for this material, despite its low hole mobility (< 0.1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>).<sup>[232-236]</sup>

Along with these experimental results, theoretical studies of  $ZnM_2O_4$  (M = Co, Rh, Ir) spinel oxides were also reported. The theoretical studies of electronic structure in these material were consistent with the experimental results, showing that, for example, the band gap was created from the crystal field splitting M d<sup>6</sup> orbitals.<sup>[224, 237-242]</sup> However, the theoretical band gap studies also showed discrepancies with experiments in both the magnitude and trend of band gap values. Specifically, Dekkers et al.<sup>[230]</sup> reported an experimental result of increasing band gap with the quantum number, while Scanlon et al.<sup>[241]</sup>, Amini et al.<sup>[243]</sup> and Samanta<sup>[242]</sup> found different trend in their theoretical works. The p-type character of  $ZnM_2O_4$  spinel oxides was found to originate from the acceptor-like antisite defect  $Zn_M$  (Zn replacing M, M = Co, Rh, Ir) and cation vacancy  $V_{Zn}$ .<sup>[225, 240, 243-245]</sup> However, no significant dispersion in VBM was found in theoretical studies, which indicated the presence of large effective mass or polaron conduction, limiting the p-type conductivity of spinel oxides.<sup>[224, 225, 238, 241, 243]</sup> A large hole effective mass of 7me was reported by Nagaraja et al.<sup>[225]</sup> Perkins et al. studied the hole doping in  $ZnCo_2O_4$  by both minimizing the formation of intrinsic hole-killers and increasing concentration of hole producers, thus increasing the conductivity of resultant thin films by 20 times.<sup>[246]</sup> Singh et al. found S doping in ZnIr<sub>2</sub>O<sub>4</sub>

decreases the band gap, making the material an efficient photocatalyst in the visible range by enhancing the optical absorption.<sup>[239]</sup> Ramo et al. demonstrated that amorphization in  $ZnIr_2O_4$  would lead to a large decrease of the band gap and localized states at the VB edges which limit the p-type conduction.<sup>[240]</sup>

#### 2.5. Nickel oxide

Nickel oxide (NiO) has been known as p-type TCO for long time, with reporting large work function of 5.4 eV and optical  $E_g$  from 3.6 to 4.0 eV.<sup>[247]</sup> However, the visible range transparency had been hindered by the minor absorption due to low oscillator strength d-d transitions<sup>[248]</sup>. NiO has a cubic structure (space group: Fm3m), similar as NaCl (rock salt structure) with octahedral  $Ni^{2+}$  and  $Q^{2-}$  occupations. From the proposed band structure model<sup>[249-251]</sup>, the VB of NiO is hybridized by O 2p and partially filled metal d orbitals, thus a metallic conduction is expected. However, giving the fact that stoichiometric NiO is an electrical insulator, some models are used to describe the conducting behavior, namely, Mott-Hubbard insulator<sup>[252-255]</sup> and charge-transfer insulator model<sup><math>[251, 256]</sup>. In the former, the E<sub>g</sub> is</sup> formed by the splitting d bands by strong electron correlation; in the latter, the  $E_{\rm g}$  is defined between higher metal site and ligand site (O 2p). The p-type character for NiO is attributed to the spontaneously formed Ni vacancies (V<sub>Ni</sub>) and this p-type character is stable.<sup>[257]</sup> Theoretically, this acceptor level was shown insufficiently close to the VBM, which limits the free hole density and thus the conductivity in stoichiometric NiO ( $\sim 10^{-13}$  S cm<sup>-1</sup>).<sup>[257]</sup> However, the conductivity can be effectively enhanced by intentionally doped extrinsic monovalent atoms like Li or increasing the concentration of Ni<sup>3+</sup> ions.<sup>[257-259]</sup> NiO is also showing electrochromic properties and mainly used as anode electrochromic materials along with WO<sub>3</sub> at the cathode.<sup>[260]</sup> After connected to the anode, the NiO (bleached state) is oxidized to  $NiO(OH)_x$  (colored state) along with the insertion of OH<sup>-</sup> and extraction of e<sup>-[261]</sup>. To date, NiO thin films can be fabricated by both physical methods like magnetron sputtering<sup>[262]</sup>,

pulsed laser deposition<sup>[263]</sup>, electron beam evaporation<sup>[264, 265]</sup>, and chemical methods like solgel processing<sup>[266]</sup>, spray pyrolysis<sup>[267]</sup> and atomic layer deposition<sup>[268]</sup>. High p-type Hall mobility had been achieved by both RF sputtering<sup>[262]</sup> (28.56 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) and spray pyrolysis method<sup>[267]</sup> (11.96 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), with typical carrier concentrations of  $10^{17} \sim 10^{18}$  cm<sup>-3</sup>. Similar as previously discussed p-type oxides, NiO had also been used in conventional electronic devices, such as TFTs<sup>[269-273]</sup>, p-n diodes<sup>[274-277]</sup>. Apart from these, NiO also shows promise in electrochromic<sup>[260, 261]</sup>, resistive switching memory<sup>[278-280]</sup> and optoelectronic<sup>[272, 281-283]</sup> or photovoltaic (PV)<sup>[263, 282, 284, 285]</sup> applications.

#### 3. Device Basics for p-Type Oxides

#### **3.1.** Thin-film transistors

Thin-film transistors (TFTs) are widely studied semiconductor devices, primarily due to their simple structure and dominant application in the display industry, where TFTs serve as the basic units that control pixels in flat panel displays including liquid crystal displays (LCD) and active matrix organic light-emitting diode (AMOLED) screens.<sup>[286-288]</sup> Even though high performance n-type oxide TFTs have already been used in commercial display applications<sup>[1, 10, 289, 290]</sup>, the search for equally good p-type oxides and TFTs has lagged behind. On the one hand, p-type oxide TFTs hold several potential benefits to the related sensing or memory applications, if reasonable performance can be achieved. On the other hand, achieving high performance p-type oxides holds the promise for the implementation of the oxide based complementary metal oxide semiconductor (CMOS) devices, which are known for their power efficiency.<sup>[6]</sup>

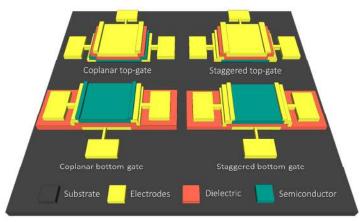

Thin-film transistors are three-terminal field-effect devices comprised of three components, namely, semiconductor, dielectric and electrodes (source, drain and gate). The source and drain electrodes (S&D) are spatially separated with the gate electrode (G) by the dielectric layer. The structures of TFTs can be divided into coplanar (C) and staggered (S)

type, depending on the relative locations of the three electrodes to the semiconductor layer. Within each TFT type, two further classifications can be defined depending on the position of the gate electrode (on the top or bottom of the whole TFT stack), namely, top-gate (-TG) or bottom gate (-BG). These typical structures of TFTs are illustrated in **Figure 7**, classified as mentioned above.<sup>[11]</sup> The current flow directions differ from structure to structure. For example, in the C-TG or C-BG TFT structures, the semiconductor/dielectric interface directly contacts the S&D, meaning that the current flows horizontally in a single plane. In contrast, in the staggered configurations (S-TG and S-BG), the S&D contact the opposite side of the semiconductor/dielectric interface, meaning that the current flows in two planes: first vertically to the channel then horizontally from S to D.<sup>[288]</sup>

The structure selected to build TFTs mainly depends on the materials involved in the fabrication and the working conditions of the TFT devices.<sup>[1]</sup> The TG structures are normally preferred when a given material (e.g. semiconductor) requires high processing temperatures that may damage the previously deposited layers (e.g. dielectric and/or source and drain electrodes). The TG configuration is also preferred when semiconductor with high-quality crystal structure (epitaxial) is desired, which benefits from a small lattice mismatch between semiconductor and the single crystal substrate. The BG structures are more popular in TFT fabrications, mostly due to the simple fabrication process and the fact that most researchers use commercial high quality indium tin oxide (ITO)/glass substrates (where the gate electrodes are already grown on the substrates). Another point for using BG structure is the TFT working conditions, such as instability caused by the back light in the case of hydrogenated amorphous silicon (a-Si:H) TFTs, which are widely used in LCD displays.<sup>[1, 291]</sup> Consequently, the S-BG structure TFT configuration was chosen for both simplifying the fabrication process and blocking the backlight by the metal gate electrodes on TFTs. It is noted that the semiconductor surfaces are exposed to air in the BG structured TFTs, which can be either advantageous or disadvantageous, depending on the material itself. In some

cases, this structure is preferred when the as-deposited oxides need further processing to attain the desirable stoichiometry and crystal structure, for instance, a post-deposition annealing process in a controlled atmosphere or a surface treatment under plasma exposure.<sup>[288, 292]</sup>

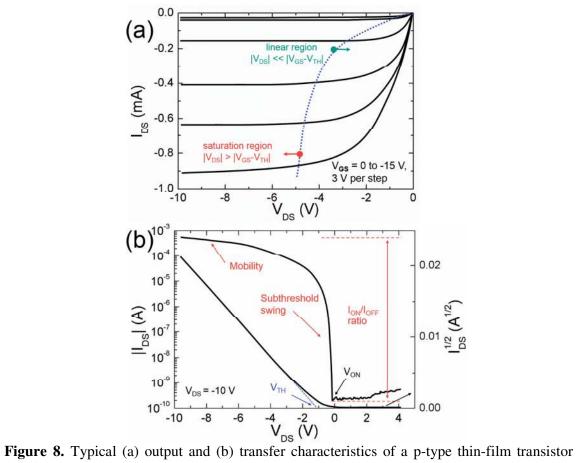

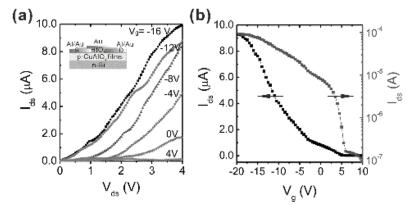

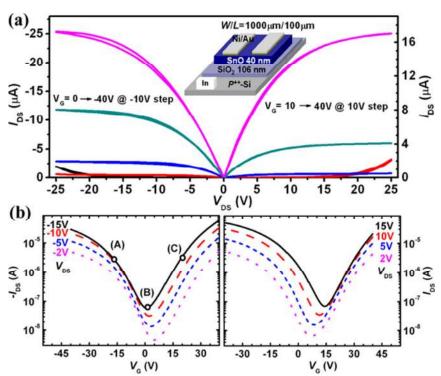

The basic principle of a field-effect device is to control the flow of electrons (or holes) between the source and drain by the modulation of a semi-conducting channel. This modulation is achieved by the injection of carriers near the semiconductor/dielectric interface<sup>[293]</sup>, through the voltage applied on the gate electrode, which forms a parallel plate capacitor structure along with the gate dielectric and semiconductor. The modulation layer, i.e. holes accumulated at the p-type semiconductor/dielectric interface. The static characteristics of p-type thin-film transistors can be evaluated by their output and transfer characteristics as shown in **Figure 8**. The output characteristics are obtained by measuring the drain to source current ( $I_{DS}$ ) as a function of drain-source voltage ( $V_{DS}$ ) for various gate-source voltages ( $V_{GS}$ ), as shown in **Figure 8a**, where both the linear and saturation regions are illustrated. Transfer characteristics are obtained by sweeping  $V_{GS}$  at a constant  $V_{DS}$ , as shown in the logarithmic plot in **Figure 8b**.

The output characteristic (**Figure 8a**) of p-type TFT can be described in two regimes according to the value of the drain-source voltage ( $V_{DS}$ ): <sup>[3, 288, 292, 294-297]</sup>

1. Linear region. A conductive channel is formed and current flows between the source and drain. In this regime (which is also known as the pre-pinch-off regime), the accumulated charges are uniformly distributed throughout the channel. The TFT behaves as a resistor, with a linear increment in the current with respect to  $V_{DS}$ .

This regime occurs when  $|V_{DS}| \ll |V_{GS} - V_{TH}|$  and the drain to source current (I<sub>DS</sub>) is modeled as:

$$I_{DS} = -\mu_{FE} C_{ox} \frac{W}{L} \left[ \left( V_{GS} - V_{TH} \right) V_{DS} - \frac{1}{2} V_{DS}^{2} \right]$$

(1)

where  $\mu_{FE}$  is the field-effect mobility,  $C_{ox}$  is the gate dielectric capacitance per unit area, W and L is the channel width and length.

2. Saturation region. In this regime, the drain voltage is higher than the gate voltage causing the carriers to spread out from the narrow channel created during the linear regime. Current flows in a broader region than just the semiconductor/dielectric interface. Near the drain electrode a lack of channel region results from the depletion of the charges in the accumulation layer near this electrode, and is defined as pinch-off.

This regime occurs when  $|V_{DS}| > |V_{GS} - V_{TH}|$ . I<sub>DS</sub> saturates (also defined as the postpinch-off regime) and is primarily controlled by the V<sub>GS</sub>, and described approximately by:

$$I_{DS} = -\mu_{Sat} C_{ox} \frac{W}{2L} (V_{GS} - V_{TH})^2$$

<sup>(2)</sup>

where  $\mu_{sat}$  is the saturation mobility.

TFTs can operate as enhancement-mode or depletion-mode devices. The former is defined as *normally off* device, that is, negligible  $I_{DS}$  flows at  $V_{GS} = 0$  V; while the latter is defined as *normally on* device, where some  $I_{DS}$  flows at  $V_{GS} = 0$  V. Turning off a depletion-mode device can be done by applying a  $V_{GS}$  of the opposite polarity (i.e. positive  $V_{GS}$  for p-type TFTs). Although both operation modes are useful for certain applications, the enhancement-mode is preferred, since it requires no extra power to turn off, facilitating circuit design and dissipating less power in the standby mode.

Typical transfer characteristic of p-type TFT is shown in **Figure 8b**. Depending on the value of applied  $V_{DS}$ , the transfer curve will show the performance at the linear or saturation region. The transfer characteristics permit *quantitative assessment* of a large number of important TFT operating parameters<sup>[1]</sup>, including: On-to-off current ratio (I<sub>on</sub>/I<sub>off</sub>), threshold voltage (V<sub>th</sub>), turn-on voltage (V<sub>on</sub>), subthreshold swing (SS), interface trap density (D<sub>it</sub>) and mobility ( $\mu$ ). The definition and evaluation for these important parameters are introduced below.

$I_{on}/I_{off}$ , defined as the ratio of drain current in the on state ( $I_{on}$ ) to current in the off state ( $I_{off}$ ).  $V_{th}$ , defined as the value of  $V_{GS}$  when the conductive channel (or an accumulation layer near the dielectric/semiconductor interface) just begins to connect the source and drain electrodes. In ideal case, the channel readily forms on the presence of a very small  $V_{GS}$ . In the real case,  $V_{th}$  will deviate from the ideal value (close to 0 V).  $V_{th}$  can be estimated by different methodologies, linear extrapolation being the most widely used. In this method, the  $V_{th}$  can be estimated from the intercept of a straight-line fit of the  $I_{DS}$ - $V_{GS}$  transfer curve (linear operation region).  $V_{th}$  can also be estimated from a ( $I_{DS}$ )<sup>1/2</sup>- $V_{GS}$  plot for high  $V_{DS}$  (saturation region). The  $V_{th}$  estimation in the linear region (obtained at low  $V_{DS}$ ) is preferred, as series resistance is usually negligible at low drain currents<sup>[298]</sup>.  $V_{on}$  is simply defined as the  $V_{GS}$  for the onset of drain current conduction, i.e. the  $V_{GS}$  at which the drain current rises. SS is defined as the gate voltage required to increase the drain current by one decade. SS is obtained by the inverse of the maximum slope of the transfer characteristics in the subthreshold region ( $|V_{GS}| <|V_{th}|$ ). Low values of SS result in high operating speed and low power consumption<sup>[1, 299]</sup>.

$$SS = \left(\frac{\partial \log I_{DS}}{\partial V_{GS}}\Big|_{\max}\right)^{-1}$$

(3)

D<sub>it</sub> can be obtained from the SS and is given by

$$D_{it} = \frac{1}{q} \left( \frac{qSS}{2.3kT} - 1 \right) C_{ox} \tag{4}$$

where q is the magnitude of electron charge, k is the Boltzmann constant and T is temperature in kelvin scale.

Mobility ( $\mu$ ), defined as the efficiency of the majority carrier transport in a semiconducting material, it is obtained from a field-effect measurement. In an ideal TFT, mobility is assumed to be constant and shows no change with V<sub>GS</sub>. In a real TFT, the channel mobility may not be constant and can vary with V<sub>DS</sub> and V<sub>GS</sub>.<sup>[1, 298]</sup> Several scattering mechanisms (lattice vibrations, ionized impurities, grain boundaries, interface surface

roughness, lattice strain and other structural defects<sup>[298]</sup>), velocity saturation, and electron trapping can affect the mobility of field-effect devices. In a real TFT, an increment of mobility is observed above threshold voltage, reaching a maximum value at a saturation peak, and finally decreasing as the gate-source voltage increases. The voltage dependence of mobility requires the definition of several types of mobilities to evaluate. The most common ones used in the TFT community are effective mobility ( $\mu_{eff}$ ), field-effect mobility ( $\mu_{FE}$ ) and saturation mobility ( $\mu_{sat}$ ).

The  $\mu_{eff}$  can be obtained in the linear operation region, as shown in **Equation 5**;  $\mu_{eff}$  may be found using the measured linear region output conductance. Effective mobility is normally considered the most accurate estimation of mobility as it includes the effect of  $V_{GS}^{[298]}$ . Nevertheless, errors in the threshold voltage determination can lead to inaccuracies in the effective mobility evaluation.

$$\mu_{eff} = \frac{g_d L}{WC_{ox} \left( V_{GS} - V_{TH} \right)} \tag{5}$$

where  $g_d$  is the output conductance,

$$g_{d} = \frac{\partial I_{DS}}{\partial V_{DS}} \bigg|_{V_{GS} = cons.}$$

(6)

The  $\mu_{FE}$  is the most commonly used mobility to describe the performance of TFTs. It is obtained at a low  $V_{DS}$ , but it does not depend on  $V_{th}$  determination,

$$\mu_{FE} = \frac{g_m L}{W C_{ox} V_{DS}} \tag{7}$$

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}} \bigg|_{V_{DS} = cons.}$$

(8)

where  $g_m$  is the transconductance and defined as the change in  $I_{DS}$  for a unit change in  $V_{GS}$  at a constant  $V_{DS}$ .

The  $\mu_{sat}$  can be obtained using the measured saturation region transconductance (at high  $V_{DS}$ ) according to **Equation 9**.

$$\mu_{Sat} = \frac{2L}{WC_{ox}} \left(\frac{\partial \sqrt{I_D}}{\partial V_{GS}}\right)^2 \tag{9}$$

Other definitions of mobility include the ones proposed by Hoffman<sup>[300]</sup>, defined as average and incremental mobility,  $\mu_{avg}$  and  $\mu_{inc}$ , respectively.  $\mu_{avg}$  indicates the average mobility of the total carriers in the channel, while  $\mu_{inc}$  reflects the mobility of the carriers added to the channel as  $|V_{GS}|$  increases. The fact is that most of the reported p-type oxide TFTs operate in the depletion mode, i.e. significant I<sub>DS</sub> exists when V<sub>GS</sub>=0 V, hence care must be taken to make sure channel mobility is not overestimated due to the inevitable contribution from the bulk mobility ( $\mu_{bulk}$ ). Recently, a comprehensive depletion-mode model was proposed by Zhou et al.,<sup>[301]</sup> which could help better evaluate the actual interface mobility ( $\mu_{interface}$ ) from a depletion-mode operating TFT by subtracting the contributions from the  $\mu_{bulk}$ .

#### **3.2. CMOS inverters**

As transistors are the elementary building block for circuit design, the ultimate objective of developing high performance p-type transistors is to create circuits with more complex functionality and low power consumption for the emerging transparent electronics industry. This is done by developing a robust complementary metal oxide semiconductor (CMOS) device. The reasons behind the significant importance of the CMOS devices include low power consumption, low waste heat generation, high noise margin, high logic swing output, high circuit integration density and architectural simplicity.<sup>[11-14]</sup>

As its name suggests, an inverter is used to reverse the high and low voltages corresponding to binary signal of 1 and 0 in digital electronics, where a binary 0 input becomes a binary 1 output and vice versa. Although the inverting function can be realized using NMOS devices, the high power dissipation, lower logic switching performance and high waste heat generation make them less attractive.<sup>[11, 13]</sup> The low power consumption in CMOS inverter can be understood from basic device operation.

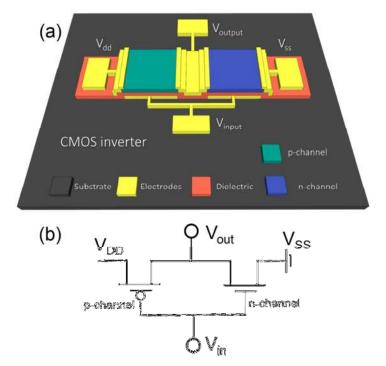

A CMOS inverter (the NOT gate) is the basic building block of a CMOS circuit, it contains two serially connected n- and p-type transistors drain to drain. Typical structure and schematic circuit diagram of a CMOS inverter are presented in **Figure 9**. The input signal is applied simultaneously to the gate electrodes of both transistors, while the output signal is taken from the common drain electrode.<sup>[11]</sup> A typical voltage transfer curve (VTC) of CMOS inverter is shown in **Figure 10a**, which is acquired by measuring the voltage from the output electrode ( $V_{out}$ ) when sweeping the applied voltage in the input terminal ( $V_{in}$ ). Important parameters of CMOS inverters include  $I_{dd}$ , gain, and noise margins, which will be briefly introduced below.

$I_{dd}$  is defined as the static current from the supply rail to the ground, which is related to the power consumption of a CMOS inverter. The functional quality of a CMOS inverter is evaluated by the gain value, which is defined as negative slope in the VTC curve,

$$Gain = -\frac{\partial V_{out}}{\partial V_{in}} \tag{10}$$

The noise margin (NM) is an important parameter for logic circuits, representing the threshold value for a circuit to distinguish the proper signal between '0' or '1', i.e. the amount of noise that a circuit can withstand. The NM of CMOS inverter can be extracted from the unity gain positions ( $\partial V_{out} / \partial V_{in} = -1$ ) from the VTC curve (**Figure 10b**), where the corresponding coordinates of these positions are defined as V<sub>OH</sub>, V<sub>OL</sub> in V<sub>out</sub> axis; V<sub>IH</sub>, V<sub>IL</sub> in V<sub>in</sub> axis. The high NM (NM<sub>H</sub>) and low NM (NM<sub>L</sub>) can be calculated as follows,

$$NM_{H} = \left| V_{OH} - V_{IH} \right| \tag{11}$$

$$NM_{L} = \left| V_{IL} - V_{OL} \right| \tag{12}$$

A basic CMOS operation can be understood from five different regimes presented in the VTC curve, as shown on the top of **Figure 10b**.<sup>[302, 303]</sup> When a small  $V_{in}$  is applied [regime (a) in **Figure 10b**], the p-channel operates in the linear mode while n-channel is turned off. In this regime, the  $V_{out}$  can be expressed as

$$V_{out} = V_{SD,n} = V_{DD} - V_{SD,p} \tag{13}$$

Further increase in the input voltage  $(V_{in})$  would forward the operation into regime b, where the n-channel is in saturation mode and p-channel remains in the linear operation mode. Since the current through both TFTs is the same, the turning on of the n-channel TFT (decreasing resistance of n-channel) leads to a drop in  $V_{out}$ , the operation in this regime can be described as

$$V_{out} = (V_{in} - V_{th,p}) + \left[ (V_{in} - V_{DD} - V_{th,p})^2 - \frac{g_{m,n}}{g_{m,p}} (V_{in} - V_{th,n})^2 \right]^{1/2}$$

(14)

where,  $V_{th,n}$  and  $V_{th,p}$  are the threshold voltages of the n- and p-channel TFTs, respectively, and  $g_{m,n}$  and  $g_{m,p}$  are the transconductances of n- and p-channels, as we previously discussed in the TFT operation part.

The conduction in the n-channel TFT leads to a current path from the  $V_{dd}$  to  $V_{ss}$  through the n- and p-TFT channels. As  $V_{in}$  further increased, this current increases, leading to a higher voltage drop across the p-channel TFT, which will eventually be turned on (saturation mode). This is indicated as regime c in **Figure 10b**, where the static current ( $I_{dd}$ ) across the  $V_{dd}$  and  $V_{ss}$  terminals is very large, since both TFTs are in saturation mode. Consequently, the  $I_{dd}$ climbs to its maximum (**Figure 10a**) and the gain value reaches its peak. Further increase in the  $V_{in}$  leads to the n-channel TFT moving into the linear region (regime d). The analysis of this regime is similar to that of regime b, except that the operation regions of the n- and pchannel TFTs are reversed. Eventually when  $V_{in}$  is raised beyond the  $V_{th,p}$ , the inverter enters regime e, where the p-channel is turned off and n-channel device operates in the linear region.

At this point, the ideal V<sub>out</sub> should be zero.

In summary, the low power consumption of CMOS inverter can be understood as follows, under a high input voltage (1 signal), p-channel is switched off while n-channel is on, and only a negligible  $I_{dd}$  (defined by the off current of p-channel) flows from  $V_{ss}$  to  $V_{dd}$ . This situation is reversed when a low input (0 signal) is applied, where the negligible  $I_{dd}$  is defined by the off current of n-channel transistor. In both of the above-mentioned cases, power consumption of CMOS inverters is almost negligible, except for the on/off switching period, which corresponds the peak  $I_{dd}$  in **Figure 10a**.<sup>[11, 14]</sup> Thus, a small overall power consumption can be achieved using CMOS inverters. The low power dissipation results in lower heat generation, which avoids the damage of circuits from overheated devices, cuts down the budget for cooling systems and makes it possible to fabricate more complex circuits at high building density.<sup>[11]</sup>

#### 3.3. p-n Junction diodes

The p-n junction is a simple yet powerful device that consists of two oppositely doped semiconductor films (p- and n-type). It has been used in many applications including rectification, surge protection, light emission, and receiving or generating radio frequency signals. Apart from the rectifying effect, p-n junction devices have also been widely used in sensor applications, such as thermometers, photodetectors and radiometers. <sup>[302, 303]</sup>

The rectifying operation of p-n junctions can be understood from the formation of the depletion region, where free electrons in the n-layer diffuse across the junction and recombine with the holes in p-layer, leaving the charged ions in both sides. A built-in voltage is formed due to the difference in work function of p- and n-semiconductors, which impedes further free carrier diffusion across the junction. A reverse bias (i.e. high voltage on n-side, the same direction as the built-in voltage) increases the barrier for electron flow across the junction and reduces diode current. However, a forward bias (i.e. high voltage at the p-type, against the

built-in voltage) assists the electrons in overcoming the Coulomb barrier of the space charge in depletion region. Electrons thus flow with very small resistance in the forward direction.

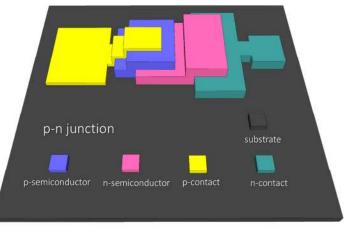

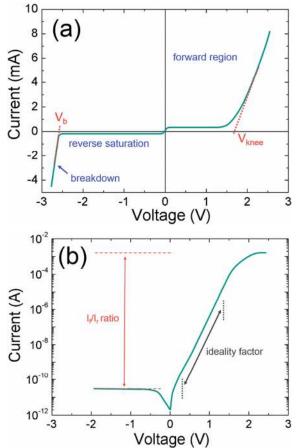

The schematic structure for typical p-n junction is shown in **Figure 11**. Typical voltagecurrent characteristic curve of diode operation is shown in **Figure 12a**, which clearly indicates the forward bias, reverse bias and breakdown regions. The characteristic curve in log scale is shown in **Figure 12b**, from which important parameters in diode operation can be extracted, including knee voltage (or cutting voltage, turn on voltage), breakdown voltage, reverse saturation current, forward/reverse rectifying ratio and ideality factor.

The knee voltage ( $V_{knee}$ ) is the applied voltage which can overcome the potential barrier from the depletion region and allow the flow of charged carriers across the junction. From device point of view,  $V_{knee}$  is the voltage at which the forward current starts to increase sharply from its leakage (almost zero) value. The  $V_{knee}$  can be extracted by taking the voltage axis intercept from extrapolating the linear part of the current-voltage curve in forward operation, as indicated in **Figure 12a**. Breakdown voltage ( $V_b$ ) is defined by the largest reverse voltage that can be applied to a diode without causing an exponential increase in the current. Reverse saturation current ( $I_s$ ) is the current formed by the drifting of minority carriers from the neutral regions to the depletion region. This current is almost independent of the reverse voltage, as shown in **Figure 12a**. Forward/reverse rectifying ratio ( $I_f/I_r$ ) is the maximum ratio of the forward current to the reverse saturation current in the diode operation, as shown in **Figure 12b**. Ideality factor (*n*) is the most important parameter of diode operation, it can be used to evaluate how closely the diode behavior matches the ideal diode equation. An acceptable ideality factor for diode device is between 1 and 2. The *n* can be extracted from the slope of the InI-V curve,

$$n = \frac{q}{kT} \left(\frac{\partial \ln I}{\partial V}\right)^{-1}$$

(15)

where q is the electron charge, k is the Boltzmann constant and T is the device operating temperature in Kelvin scale.

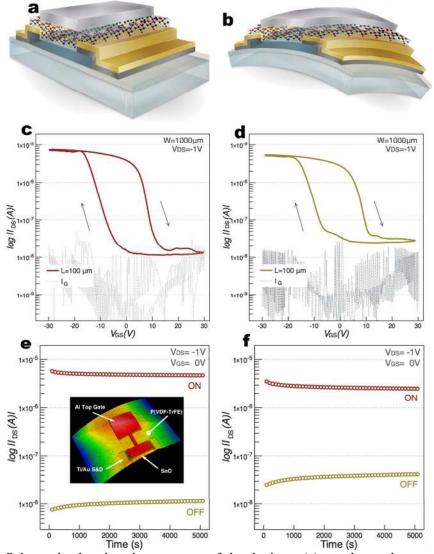

#### 4. Performance of p-Type Oxide Thin-Film Transistors

#### **4.1. Ternary Cu-bearing oxide thin-film transistors**

In 2012, Yao et al. successfully fabricated a coplanar top-gate structured TFT based on CuAlO<sub>2</sub> delafossite<sup>[75]</sup>. This was the first demonstration of TFT application for CuAlO<sub>2</sub> delafossite, even though this material had been extensively studied since  $1997^{[15]}$ . (Figure 13) Here, the active layer was a mixed phase of Cu-O dimmer inside CuAlO<sub>2</sub> host lattice rather than a pure phase. The mixed phase thin film showed an encouraging peak Hall mobility of 39.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, which was attributed to the synergistic effects of energy band offset and hybridization of less-dispersive Cu<sup>+</sup> 3d<sup>10</sup> with the Cu<sup>2+</sup> 3d<sup>9</sup> level at the VBM. The active layer ( $\mu_{Hall} = 8.4 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) was deposited using RFMS at a substrate temperature of 940 °C. The TFT showed a typical p-type behavior with a  $\mu_{FE}$  of 0.97 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, V<sub>on</sub> of 5 V and I<sub>on</sub>/I<sub>off</sub> modulation of  $8 \times 10^2$ . The high  $\mu_{FE}$  and large optical E<sub>g</sub> (>3.46 eV) revived interest in Cu based delafossite oxides.

#### 4.2. Binary copper oxide thin-film transistors

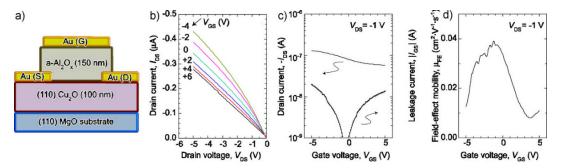

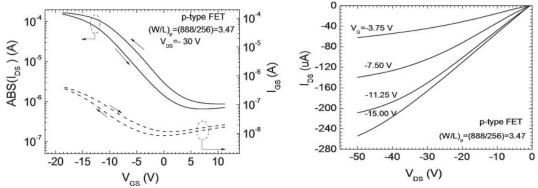

In 2008, Matsuzaki et al. reported a high Hall mobility of ~90 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in p-type Cu<sub>2</sub>O thin films, which was grown by PLD and successfully used in a p-type Cu<sub>2</sub>O TFT.<sup>[82]</sup> By varying the oxygen partial pressure ( $P_{O2}$ ) and substrate temperature during deposition, a narrow process window for high mobility Cu<sub>2</sub>O was found, which was centered about 0.5 Pa and 700 °C. The narrow process window indicated that the nonstoichiometric nature of the metastable Cu<sub>2</sub>O greatly influenced the electrical properties. According to atomic force microscope (AFM) surface morphology measurement, the growth mechanism of Cu<sub>2</sub>O thin films was shown to be strongly dependent on  $P_{O2}$ , which affected the grain size. Specifically,

at small P<sub>02</sub> (< 0.5 Pa), small crystallite size was observed; when P<sub>02</sub>=0.50-0.65 Pa, the film growth was dominated by two-dimensional growth mechanism; at P<sub>02</sub>=0.80 Pa, a threedimensional granular growth mechanism dominated. The low Hall mobility at low P<sub>02</sub> or high P<sub>02</sub> range was attributed to grain boundary scattering. Eventually, a high Hall mobility of 90 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> was achieved using a 650 nm Cu<sub>2</sub>O thin film which was grown at 700 °C under P<sub>02</sub> of 0.65 Pa. It should be noted that this high Hall mobility was in large part due to the large grain size (two-dimensional growth region) since the 100 nm Cu<sub>2</sub>O thin film from the same condition only showed a lower Hall mobility of 70 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. Finally, a coplanar top gate structured TFT was fabricated by depositing the AlO<sub>x</sub> by PLD and Au source and drain electrodes by e-beam evaporation (**Figure 14**). The TFT exhibited a  $\mu_{FE}$  of 0.26 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> <sup>1</sup>and I<sub>on</sub>/I<sub>off</sub> ratio of 6. A further detailed research<sup>[108]</sup> on post deposition thermal treatments revealed that the origin of low  $\mu_{FE}$  was mainly from the subgap traps formed by extra defects (V<sub>0</sub> or secondary CuO phase), where the density of subgap states was increased by the thermal treatment. The subgap states even existed in the films grown at the optimum conditions, and showed a rather high density of 10<sup>18</sup> cm<sup>-3</sup>.

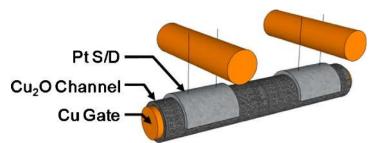

In 2009, Liao et al. presented a Cu<sub>2</sub>O nanowire (NW) FET with encouraging  $\mu_{FE}$  and large drain current swing ratio.<sup>[304]</sup> The polycrystalline Cu<sub>2</sub>O NWs were fabricated by an Ar/H<sub>2</sub> atmosphere reduction from the CuO nanowires, which were made by annealing a Cu foil in air at 400 °C for 24 hrs.<sup>[305]</sup> An optical band gap of 2.17 eV was acquired from photoluminescence (PL) spectrum. After transferring the Cu<sub>2</sub>O NWs onto SiO<sub>2</sub>/Si substrate, 100 nm Au electrodes were deposited and patterned by e-beam lithography. The staggered bottom-gate structured NW FETs exhibited encouraging  $\mu_{FE}$  of 95 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and large I<sub>on</sub>/I<sub>off</sub> ratio of 10<sup>6</sup>, with V<sub>th</sub> and V<sub>on</sub> of 15 and 32 V, respectively.

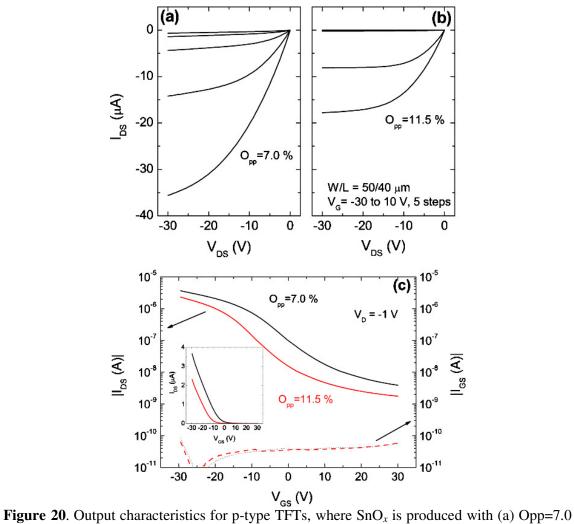

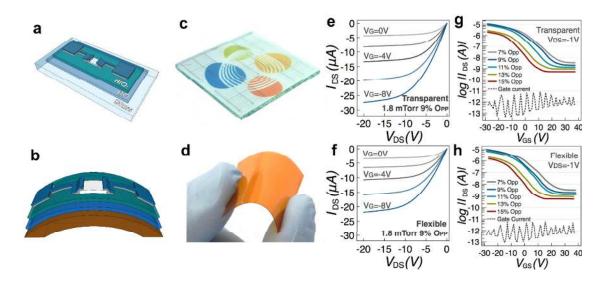

Fortunato et al. reported the first fabrication of p-type  $Cu_2O$  TFT by RF magnetron sputtering, where the substrate was kept at room temperature, followed by an ambient annealing at 200 °C.<sup>[87, 306]</sup> This study was important due to the successful fabrication of p-

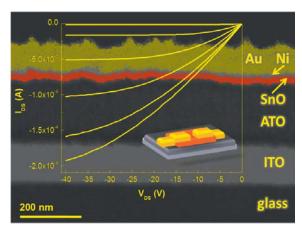

type oxide TFTs using an industry-compatible method and abundant, non-toxic source (Cu). The process window was narrow and films deposited at oxygen partial pressure [Opp,  $P_{O2}/(P_{O2}+P_{Ar})$  of 9% were found to show good crystalline quality with relatively high Hall mobility. Interestingly, the XRD results showed no difference in peak position after postdeposition annealing for 10 hours. At the same time, the full width half maximum (FWHM) decreased, resulting in an enlargement of the average grain size from 8.3 nm for the asdeposited films to 15.7 nm for annealed Cu<sub>2</sub>O films. The Hall mobility of thin film also increased (to 18.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) after post deposition annealing, which indicated that the carrier transport was limited by the grain boundary scattering.<sup>[87, 306]</sup> The same trend was also reported by Jeong et al.<sup>[130]</sup> and Matsuzaki et al.<sup>[108]</sup> A staggered bottom-gate structured TFT was built on commercial ATO (Al<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub> superlattice)/ ITO (tin doped indium oxide)/glass substrate using a 40 nm Cu<sub>2</sub>O film as active layer, while the IZO (indium zinc oxide) top gate was grown by RF magnetron sputtering and patterned by the lift-off technique. After annealing at 200 °C in air, the TFT showed a  $\mu_{FE}$ , V<sub>th</sub>, and I<sub>on</sub>/I<sub>off</sub> ratio of  $1.2 \times 10^{-3}$  cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup>, -12 V and 2×10<sup>2</sup>, respectively. A further report from Figueiredo et al. showed a  $\mu_{FE}$  of  $7 \times 10^{-3} \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ,  $V_{on}$  of 7 V and  $I_{on}/I_{off}$  ratio of  $10^3$ .<sup>[125]</sup>

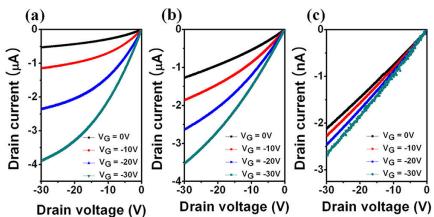

Sung et al. reported a p-type CuO TFT by oxidizing the as-deposited Cu<sub>2</sub>O film.<sup>[121]</sup> The active layer was deposited by RF magnetron sputtering using a Cu<sub>2</sub>O target, and the as-deposited Cu<sub>2</sub>O film was oxidized to CuO at 300 °C in air. The measured optical band gaps were 2.44 and 1.41 eV for Cu<sub>2</sub>O and CuO, respectively. The staggered bottom-gate TFT was finished by e-beam evaporated Au/Ni source and drain electrodes. The TFT exhibited a  $\mu_{FE}$  of 0.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, V<sub>on</sub> of 12 V and I<sub>on</sub>/I<sub>off</sub> ratio of 10<sup>4</sup>.

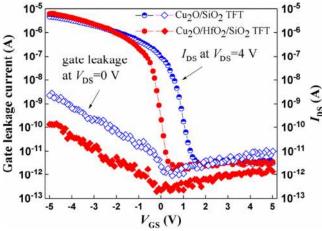

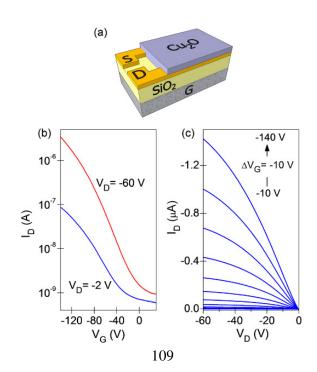

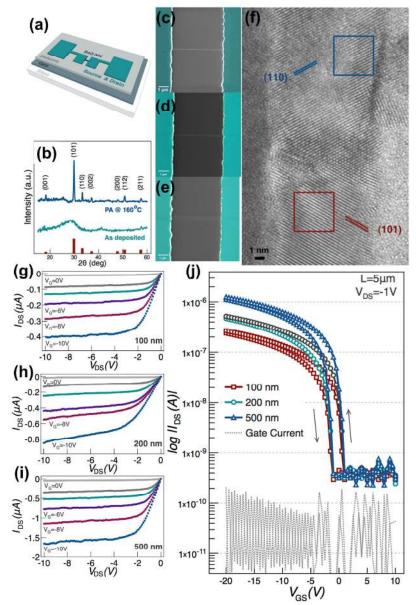

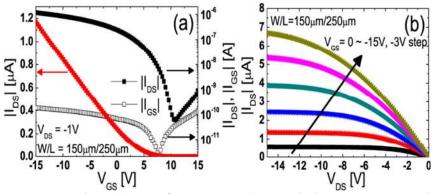

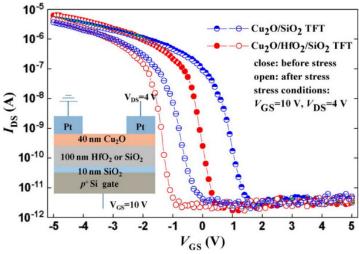

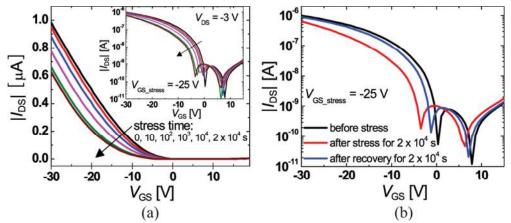

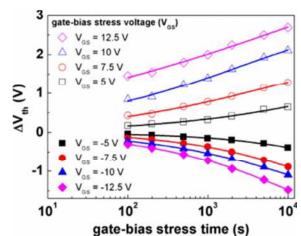

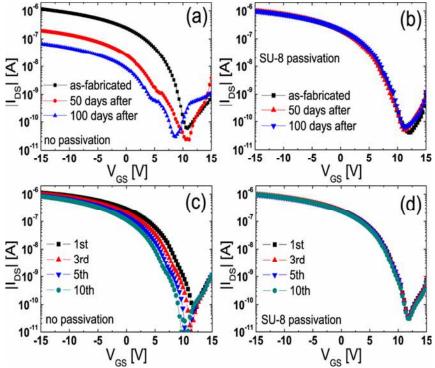

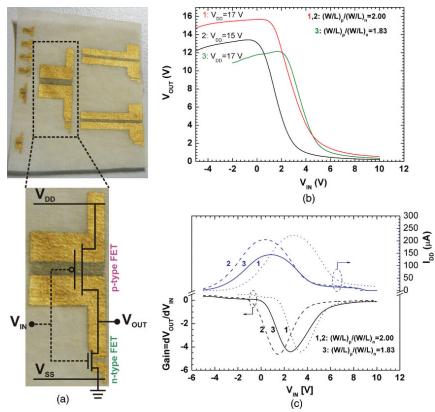

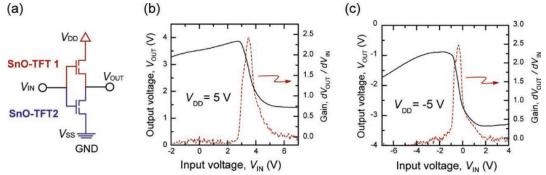

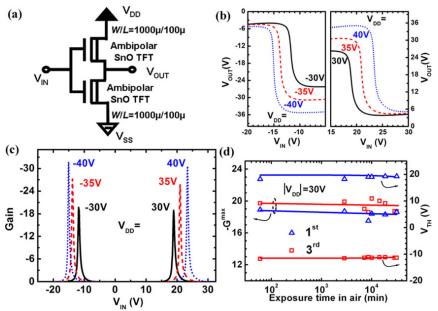

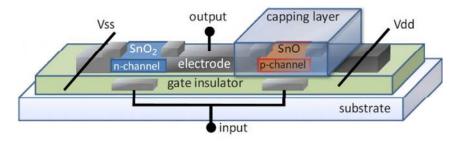

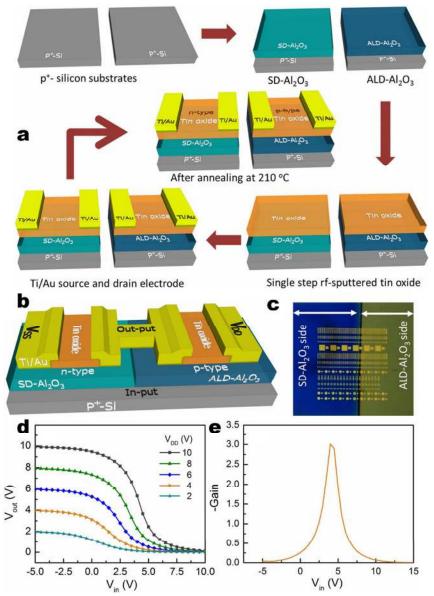

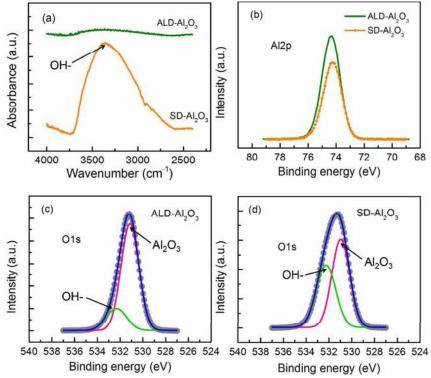

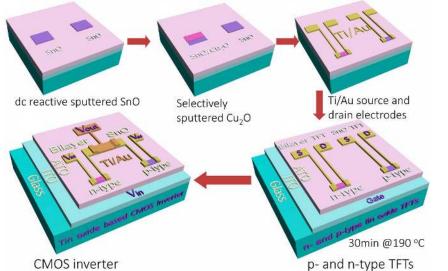

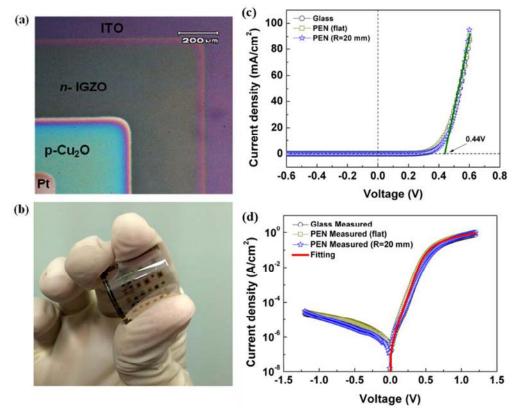

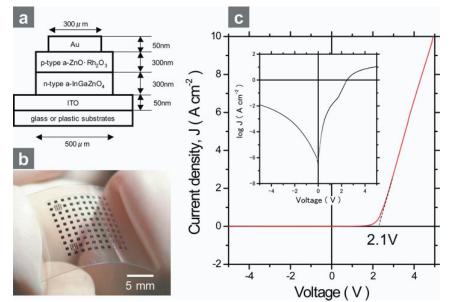

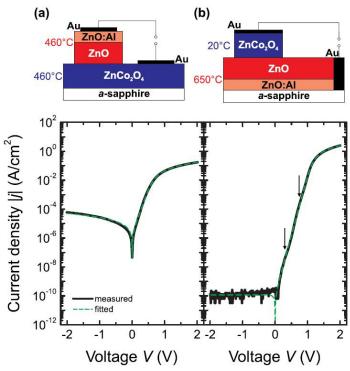

Another significant achievement in p-type  $Cu_2O$  TFTs was presented by Zou et al. in 2010.<sup>[112]</sup> The  $Cu_2O$  films were deposited by PLD at various substrate temperatures ranging from 400 to 700 °C. The XRD results showed a clear increase of average valence state of Cu with increasing substrate temperature ( $T_{subs}$ ). Specifically, the  $Cu^0$  state dominates at