MDPI

Review

# Recent Progresses and Perspectives of UV Laser Annealing Technologies for Advanced CMOS Devices

Toshiyuki Tabata \* D, Fabien Rozé, Louis Thuries, Sébastien Halty, Pierre-Edouard Raynal, Imen Karmous and Karim Huet

Laser Systems & Solutions of Europe (LASSE), 145 Rue Des Caboeufs, 92230 Gennevilliers, France \* Correspondence: toshiyuki.tabata@screen-lasse.com

Abstract: The state-of-the-art CMOS technology has started to adopt three-dimensional (3D) integration approaches, enabling continuous chip density increment and performance improvement, while alleviating difficulties encountered in traditional planar scaling. This new device architecture, in addition to the efforts required for extracting the best material properties, imposes a challenge of reducing the thermal budget of processes to be applied everywhere in CMOS devices, so that conventional processes must be replaced without any compromise to device performance. Ultraviolet laser annealing (UV-LA) is then of prime importance to address such a requirement. First, the strongly limited absorption of UV light into materials allows surface-localized heat source generation. Second, the process timescale typically ranging from nanoseconds (ns) to microseconds (µs) efficiently restricts the heat diffusion in the vertical direction. In a given 3D stack, these specific features allow the actual process temperature to be elevated in the top-tier layer without introducing any drawback in the bottom-tier one. In addition, short-timescale UV-LA may have some advantages in materials engineering, enabling the nonequilibrium control of certain phenomenon such as crystallization, dopant activation, and diffusion. This paper reviews recent progress reported about the application of short-timescale UV-LA to different stages of CMOS integration, highlighting its potential of being a key enabler for next generation 3D-integrated CMOS devices.

**Keywords:** UV laser annealing; CMOS; 3D integration; thermal budget; FEOL; MOL; BEOL; dopant activation; interconnect; ferroelectricity

# Academic Editor: Kiat Seng Yeo

Citation: Tabata, T.: Rozé, F.: Thuries,

L.; Halty, S.; Raynal, P.-E.; Karmous, I.; Huet, K. Recent Progresses and

Perspectives of UV Laser Annealing

Technologies for Advanced CMOS Devices. *Electronics* **2022**, *11*, 2636. https://doi.org/10.3390/ electronics11172636

Received: 4 July 2022 Accepted: 20 July 2022 Published: 23 August 2022

check for

updates

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Nowadays, sustainable, high-performance, and energy-efficient nanoelectronics drive the further development of CMOS technologies, not only by traditional planar scaling, called "More Moore", but also by opening the integration dimension towards the third axis perpendicular to the silicon (Si) wafer plane. This three-dimensionally (3D) stacked device architecture alleviates the difficulties possibly encountered in the way of pursuing the traditional planar scaling of transistors, while allowing the continuous increment of effective chip density and performance thereby. Here, a "monolithic" or "sequential" approach is talked about, but not a "packaging" one, where interlayer connectivity is dominated by chip bonding alignment accuracy. It also brings another benefit of implementing additional functionalities in CMOS devices, being called "More Than Moore". Furthermore, over the coming end of the current CMOS scaling, "Beyond CMOS" is preconized to determine the best means for continuing technological advancements, having new materials, concepts, and architectures.

Among these three axes of evolution, "More Than Moore" would be the one which has been the most investigated over the last several years, in parallel with the evolution of ultra-violet laser annealing (UV-LA) technologies in the semiconductor industry. To realize 3D-integrated CMOS devices, a new electrically functional Si (or other semiconductor materials) layer must be fabricated directly on the underlayer components, either by wafer

Electronics **2022**, 11, 2636 2 of 25

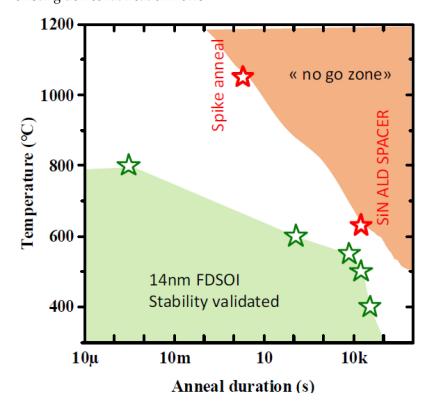

bonding [1] or by deposition [2]. Of course, it also requires other steps. For instance, to form a source and drain (S/D), recrystallization and dopant activation are necessary after ion implantation. Otherwise, epitaxy enables in situ doping with good crystal quality. To form a gate stack, dielectric and work function metal deposition, sometimes followed by reliability annealing, are required. Some of them typically need high-temperature processing. Those steps must be accomplished by reducing the thermal budget, which is empirically discussed as a simple combination of temperature (i.e., activation energy) and time (i.e., kinetics) effects, while avoiding any drawback in terms of the performance of each module. Today, as shown in Figure 1, the thermal budget acceptable for 3D-integrated CMOS devices is known as 500 °C for a few hours [1,3,4], and might be further reduced in future developments. UV-LA is then of prime importance to address such requirements for the following reasons. First, the use of a UV light enables strongly limited absorption into materials, and thereby surface-localized heat source generation. Second, the UV-LA process timescale, typically ranging from nanoseconds (ns) to microseconds (µs), efficiently prevents the generated heat from diffusing deeply in the vertical direction. In a given 3D stack, these specific features allow the actual process temperature to be elevated in the top-tier layer without introducing any drawback in the bottom-tier one. In fact, although UV-LA itself has existed for decades, most of the studies of those precedent eras were conducted in a laboratory-scale experiment but not in real industrial-quality devices. This is certainly because there was no UV-LA equipment ready to be implemented in high-volume manufacturing. On the other hand, in the current era, our 300 mm process-compatible UV-LA equipment is commercialized [5], with the capability of UV-LA process simulation [6] to support the UV-LA integration into existing device fabrication flows.

**Figure 1.** Acceptable thermal budget to preserve the performance of bottom-tier devices. Reprinted with permission from Ref. [3]. 2017, IEEE.

Considering the large freedom of designing applications in 3D integration (e.g., logic-on-logic [3], memory-on-logic [7–9], and sensor-on-logic [3,9]), the thermal budget would have to be managed application-by-application. Furthermore, in some cases components are inserted into interconnect (i.e., the back-end-of-line (BEOL)) layers to enhance the benefits of energy efficiency and look to future neuromorphic computing [10–13]. In such a

Electronics **2022**, 11, 2636 3 of 25

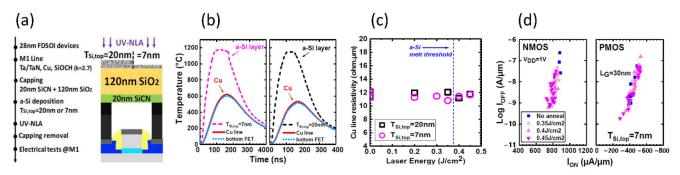

context, a clear need to freely control the thermal budget is rising. An interesting study is reported in Ref. [14], where the impacts of the buried-oxide (i.e., a Si dioxide (SiO<sub>2</sub>) layer separating the top and bottom layers in a 3D stack) thickness and applied thermal budget on the dopant activation in an ion-implanted top and bottom Si layers (i.e., a Si substrate as the bottom layer, whereas an amorphous Si thin layer as the top layer) are systematically investigated. It is noteworthy that a thicker  $SiO_2$  interlayer results in more efficient thermal isolation. Moreover, with a given UV light, laser fluence can be another knob of thermal isolation management. As shown in Figure 2, a more realistic study is conducted using a 28 nm fully depleted Si-on-insulator (FDSOI) CMOS integration, where the impacts of UV-LA on underlying components (i.e., bottom MOS devices and BEOL) are assessed in terms of the performance of transistors and copper (Cu)-based interconnects [4]. The results show no significant degradation in both, confirming the advantage and thermal budget compatibility of UV-LA in 3D integration.

**Figure 2.** (a) Process flow and schematic figure of the 3D structure treated by UV-LA, (b) Simulated time–temperature profiles of the applied UV-LA processes, (c) Cu line resistivity evaluated before and after UV-LA, (d) I<sub>ON</sub>-I<sub>OFF</sub> distribution of the bottom n- and p-type MOS devices before and after UV-LA. Reprinted/adapted with permission from Ref. [4]. 2020 IEEE.

In the following sections, we aim at highlighting the potential benefits of short-timescale UV-LA in materials engineering, crossing over diverse applications from the front-end-of-line (FEOL) to BEOL.

#### 2. FEOL Applications

#### 2.1. Reliability Annealing for High-k/SiO<sub>2</sub>/Si Gate Stacks

In recent planar transistors (e.g., 7 nm node CMOS technology, as shown in Ref. [15]), the  $SiO_2/Si$  interface is still utilized in the gate stack (generally a stack of a few nm thick high-permittivity (high-k) hafnium dioxide (HfO<sub>2</sub>) film on a Si substrate with a subnanometer-thick  $SiO_2$  interlayer), requiring a lot of efforts to further scale the equivalent oxide thickness (EOT) in a subnanometer region. This gate stack needs to be exposed to a high-temperature annealing process, typically ranging from 800 °C to 1000 °C, for a few seconds in order to ensure temperature instability (BTI) improvement [16–18].

The origin of the BTI is the electrical traps existing at the gate stack interface and within the dielectric films [19]. In the  $HfO_2/SiO_2/Si$  stack, there are different BTI sources. One of them is  $HfO_2$  bulk traps, and it is proposed to insert a dipole between the  $HfO_2$  and  $SiO_2$  layers [18] so that the Si channel does not electrically communicate with such defect levels in device operation. Another source is the traps within the interfacial  $SiO_2/Si$  system (i.e., the bulk of the thin film and interface), where  $SiO_2$  is often chemically grown to have a very thin film thickness (i.e., ~1 nm or less). Although annealing is necessary to cure or passivate those electrical traps, it must comply with the thermal budget limitations. Recently, low-temperature (from 100 °C to 450 °C) hydrogen-based annealing [20] and plasma treatment [21] have been proposed as an alternative to the conventional high-temperature annealing.

In fact, short timescale UV-LA may also address this problem. A chemically grown  $SiO_2$  thin film is known to have a smaller density than thermally grown films, as well

Electronics **2022**, 11, 2636 4 of 25

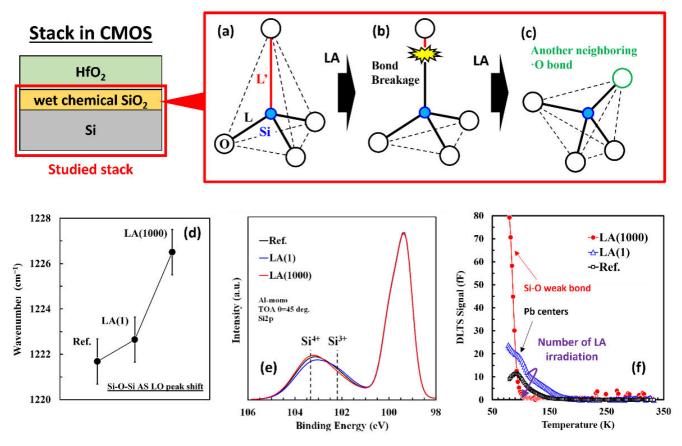

as some impurities remaining inside [22]. Such a situation would also be the case for a subnanometer-thick SiO<sub>2</sub> thin film grown by wet chemical cleaning for a CMOS gate stack. High-temperature processing enabled by UV-LA is then expected to help the removal of the remaining impurities in parallel with the nonequilibrium atomic bonding rearrangement possibly occurring thanks to its short timescale. We have conducted a preliminary study [23] relevant to the potential BTI source annihilation in the wet chemically grown SiO<sub>2</sub>/Si system by ns UV-LA (Figure 3), where the effective process temperature is set at 900 °C and the dwell time is in the order of  $10^{-7}$  s. Interestingly, by accumulating the applied ns UV-LA process up to 1000 times, the rearrangement of the Si-O-Si network is observed by attenuated total reflectance (ATR) Fourier transform infrared (FTIR) spectroscopy and X-ray photoelectron spectroscopy (XPS). This coincides with the evolution of the electrical traps captured by a temperature-scan deep-level transient spectroscopy (DLTS). Then, the P<sub>b</sub> center-type traps seem annihilated, but it competes with the formation of another type of trap, so-called "tail states" or "U-shaped continuum", which could be associated to Si-O weak bonds formed at the SiO<sub>2</sub>/Si interface. It is therefore supposed that UV-LA alone may not be sufficient to perfectly build up the  $SiO_2/Si$  system, but a potential of the nonequilibrium SiO<sub>2</sub>/Si system engineering is clearly demonstrated.

**Figure 3.** (**a**–**c**) Schematic figures of a possible local rearrangement procedure of the tetrahedral SiO<sub>4</sub> network. (**d**) Shift of the longitudinal optic (LO) phonon peak of the Si–O–Si asymmetric stretching (AS) vibration as a function of the number of LA irradiation, where LA(1) and LA(1000) stand for 1 and 1000 times irradiation, respectively. (**e**) Normalized Si 2p XPS spectra of the as-grown (Ref.), LA(1), and LA(1000) samples. (**f**) Comparison of the DLTS signals taken for the as-grown (Ref.), LA(1), and LA(1000) samples. Reprinted/adapted with permission from Ref. [23]. 2020, The Japan Society of Applied Physics.

Electronics **2022**, 11, 2636 5 of 25

#### 2.2. Channel Doping Engineering to Mitigate Short Channel Effects

The short channel effects (SCE) are known as one of the most critical issues when scaling CMOS devices [24]. To alleviate the SCEs, shallow junction has been conceived, introducing source and drain extension doping beside the channel [25]. Therefore, the control of dopant diffusion in this extension area is critical for device performance. To that end, ns UV-LA may be an ideal solution because, in such a short timescale, dopant diffusion would be strongly limited (or even negligible). Indeed, for conventional dopants such as boron (B), phosphorus (P), and arsenic (As) in Si, it is the case under the Si melting point (i.e., ns UV-LA process does not melt the Si substrate) [26]. When melting the doped Si substrate, although the diffusivity of the dopants strongly enhances (typically towards the order of  $10^{-4}$  cm<sup>2</sup> s<sup>-1</sup>, as reported in Ref. [27]), their diffusion is limited within the melted region, having a box-like profile [28–31].

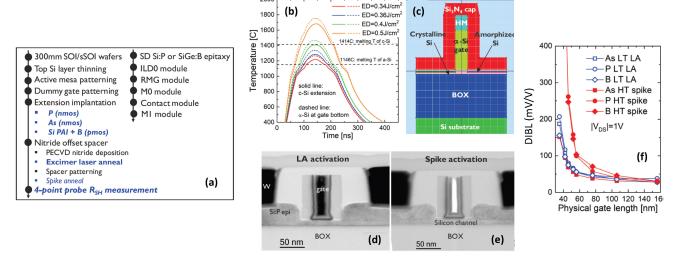

A practical example taken in real devices is reported in our previous work [32], where top planar FDSOI transistors having an 11 nm thick Si channel were fabricated (see Figure 4a for their process flow). After the ion implantation in the extension part, ns UV-LA was applied to fully melt the from 5 to 7 nm thick amorphized Si layer (Figure 4b,c) that regrows into the monocrystalline state (Figure 4d,e). After this Si channel regrowth, a raised S/D is properly formed by epitaxy, indicating that ns UV-LA does not seriously degrade the surface morphology of the regrown Si thin layer. In terms of the impact on the SCE, ns UV-LA clearly shows a benefit for suppressing the drain-induced barrier lowering (DIBL) compared to high-temperature spike annealing (Figure 4f), especially with the dopants such as B and P, which are easier to diffuse in Si than As [26].

2000

**Figure 4.** (a) Process flow of the FDSOI transistors treated by UV-LA; (b) Simulated time–temperature profiles of the applied UV-LA processes; (c) Structure used for the simulation; (d,e) Cross-sectional transmission electron microscopy (TEM) images of the EDSOI transistors after UV-LA and spike annealing; (f) DIBL extracted for different physical gate lengths. Reprinted/adapted with permission from Ref. [32]. 2020, IEEE.

#### 3. MOL Applications

The word "middle-of-line (MOL)" stands for the set of processes relevant to the formation of the electrical connection of transistors prior to the BEOL modules. Especially, the low resistive "contact" formation has become one of the biggest challenges in recent years because it is a dominant parasitic factor in scaled transistors. This is a Schottky contact formed by a metal–semiconductor interface. Therefore, to reduce the resistivity, increasing the active carrier concentration in the semiconductor side is supposed to be a strategy of choice. In fact, the required level of specific contact resistivity for future nodes is going to be less than  $1\times 10^{-9}~\Omega$  cm² [33,34]. To achieve such a low resistivity of the contact, the active carrier concentration needs to be close to  $1\times 10^{21}$  at./cm³ [35,36], or

Electronics 2022, 11, 2636 6 of 25

even higher [37]. Then, the carrier transport at the Schottky interface should be dominated by the field-emission model [38].

From the viewpoint of the UV-LA processes, there are two approaches. The first one is the liquid phase epitaxial regrowth (LPER), where the doped semiconductor is once melted and epitaxially regrown while activating the dopants. Typically, ns UV-LA enables this approach [34,39–43]. In this article, when discussing LPER, we have a regime so-called "Secondary Melting (SM)" in mind rather than the one so-called "Explosive Melting (EM)". In SM, the melted (i.e., liquid) layer forms at the surface of the semiconductor substrate and simply extends downward [31,44]. On the other hand, in EM, a thin liquid layer (typically a few to 10 nm of thickness [45]) formed at the surface travels in the depth direction, inducing recrystallization into a polycrystalline state [31,44]. The LPER-induced rapid solidification leads to the metastable incorporation of the dopants into the regrown semiconductor crystal. The melting of a doped semiconductor substrate may result in the degradation of the regrown surface morphology [1,40,42], and subsequent steps in a transistor fabrication flow might suffer from it. The second approach is the solid phase epitaxial regrowth (SPER), where the semiconductor layer amorphized by the ion implantation of the dopants can be regrown into the monocrystalline state without melting. Although ns UV-LA can achieve SPER and metastable dopant activation thereby, it requires multiple processes (i.e., more than 20 times the irradiation of the laser pulse) [46]. Therefore, in terms of the productivity, ns UV-LA might not be an optimal option. To address it, extending the process timescale towards  $\mu$ s scale may help [47]. In the previously reported ns UV-LA SPER, the surface morphology does not show serious degradation [46].

# 3.1. Dopant Activation by Liquid Phase Epitaxial Regrowth (LPER)

A potential advantage of LPER on contact resistivity lowering is that, if a doping element is properly selected, its segregation towards the surface occurs during the solidification of the melted semiconductor material. This may enhance the active carrier concentration near the metal/semiconductor interface.

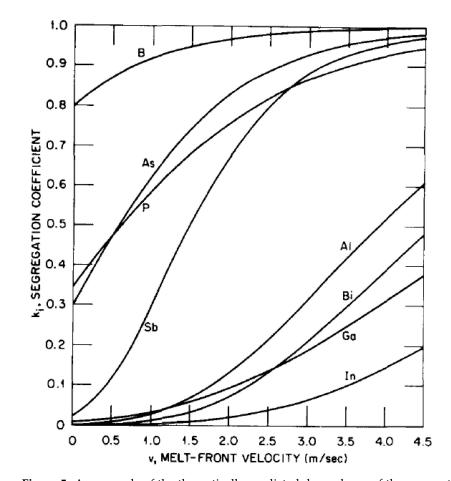

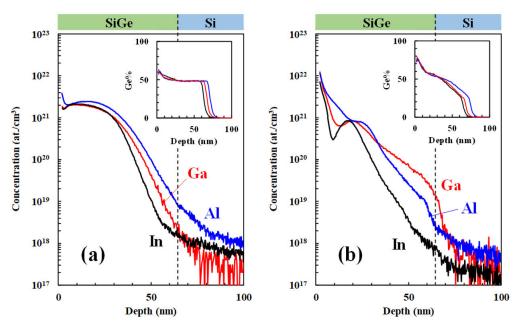

For that, the segregation coefficient of a doping element ( $k = C_S/C_L$ , where  $C_S$  and  $C_L$  stand for the dopant concentrations in the solid (s) and liquid (l) phases at the vicinity of the moving l/s interface) must be less than the unity (i.e., k < 1). It should be noted that this k value is a function of the solidification front velocity (V) as shown in Figure 5 [48,49], and increasing V makes k become closer to the unity. For instance, antimony (Sb) in Si (i.e., n-type contact) shows such a surface segregation during ns UV-LA-induced LPER [42], and gallium (Ga) [39–41,43], aluminum (Al) [41], and indium (In) [41] in SiGe (i.e., p-type contact) also do (see Figure 6a,b) as experimental examples.

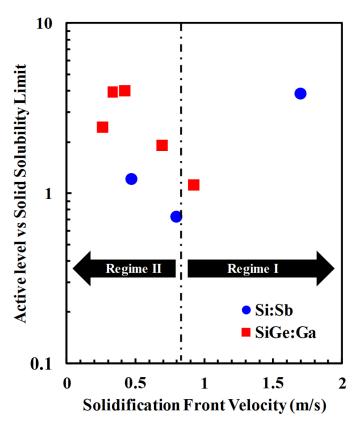

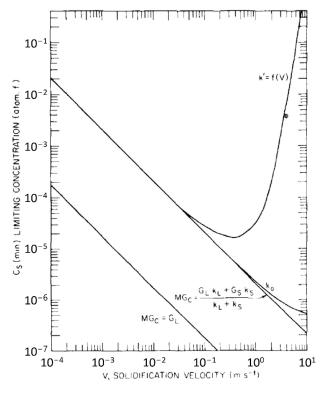

On the other hand, the activation of these segregated dopants seems not so simple. Firstly, when comparing the ratio of the LPER-induced active carrier concentration to the solid solubility limit of each doping case, that of Al in SiGe is almost unity at different melt conditions. This might be related to the self-compensation of the Al atoms (i.e., electrical deactivation due to lack of a bond between them when their doping concentration becomes extremely high) [50]. Therefore, not every small *k* dopant may work. Secondly, as shown in Figure 7, the activation also depends on *V*, drawing a downward convex shape as an overall trend given by the whole red and blue data points. In fact, there is an interesting theoretical prediction about the minimum substitutional concentration (of In in Si) as a function of V [51]. If the nonequilibrium feature of the segregation coefficient (k) is considered (i.e., k = f(V)), the relation between this concentration and V is also drawn by a downward convex shape (Figure 8). Hence, increasing *V* is suggested to enhance the active carrier concentration in LPER. However, it should be noted that it is in a trade-off with the efficiency of surface segregation (i.e., k becomes closer to the unity when increasing V), and a compromise would have to be found when integrating ns UV-LA LPER into real CMOS contact modules.

Electronics **2022**, 11, 2636 7 of 25

**Figure 5.** An example of the theoretically predicted dependence of the segregation coefficient  $(k_i)$  of dopants in Si on the solidification front velocity (i.e., the melt–front velocity, v). Reprinted with permission from Ref. [48]. 1980, AIP Publishing.

**Figure 6.** Secondary ion mass spectrometry (SIMS) profiles of Ga, In, and Al taken in the (a) asimplanted and (b) ns UV-LA-induced full SiGe epilayer melt samples. Reprinted with permission from Ref. [41]. 2019, The Japan Society of Applied Physics.

Electronics **2022**, 11, 2636 8 of 25

**Figure 7.** Plots of the degree of surpassing the solid solubility limit as a function of the simulated solidification front velocity (*V*) for the Sb-implanted Si and Ga-implanted SiGe samples. Reprinted with permission from Ref. [42]. 2020, AIP Publishing.

**Figure 8.** Theoretical prediction of the minimum substitutional concentration (of In in Si) as a function of *V*. The downward convex shape curve represents the case considering the nonequilibrium feature of the segregation coefficient. Reprinted/adapted with permission from Ref. [51]. 1981, AIP Publishing.

Electronics 2022, 11, 2636 9 of 25

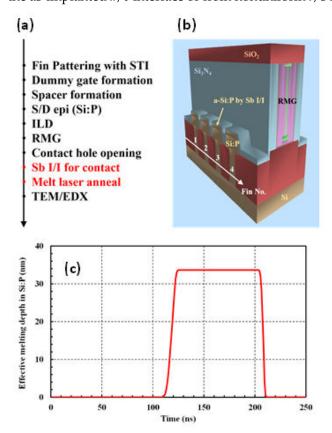

Recently, we have accessed it by using Sb doping for 14 nm node generation FinFET's Si-based contact (Figure 9) [52]. Although there is no electrical data, the segregation of ion-implanted Sb atoms at the top of the fin structure is clearly evidenced (Figure 9d,e, see the position indicated by the arrow "S/D epi top surface"). The V extracted by 3D TCAD simulation is about 4 m/s (Figure 9c). In fact, in real devices, the volume of the S/D parts is negligible compared to the underlying Si substrate, so that heat dissipation becomes fast, and V increases thereby. This value is in a promising range to have a high active carrier concentration, considering the Sb solid solubility limit in Si ( $\sim$ 6.8  $\times$  10<sup>19</sup> at./cm<sup>3</sup> [53]) and the expected gain from Figure 7 (more than 10 times at 4 m/s). Furthermore, other promising results are obtained in the p-type contacts of planer FDSOI transistors, receiving high-dose B ion implantation in in situ B-doped SiGe epilayers, then applying ns UV-LA to melt and regrow it [54]. A remaining concern would be crystal defects left after LPER. It is mandatory to melt the ion-implanted region down to the end tail of the dopant profile. Otherwise, the residual point defects and impurities originated from ion implantation precipitate in the form of extended defects in the top of the nonmelted region [30]. Moreover, stacking faults starting from the initial amorphous/crystalline (a/c) interface can be observed even at such a full melt condition [43]. They might come either from possible nonuniformity of the as-implanted a/c interface or from nonuniform l/s interface during UV-LA [55,56].

Figure 9. Cont.

**Figure 9.** (a) Process flow of the FinFET contact modules; (b) Structure used for the 3D TCAD simulation; (c) Simulated time vs. melting Si fin depth profile during ns UV-LA; (d) Cross-sectional TEM image of the Si-based contact module after ns UV-LA; (e) Energy-dispersive X-ray spectroscopy line scan taken along the annealed Si fin (the carbon signal comes from the structures surrounding the contact hole). Reprinted/adapted under CC BY 4.0 from Ref. [52]. 2020, T. Tabata et al.

# 3.2. Dopant Activation by Solid Phase Epitaxial Regrowth (SPER)

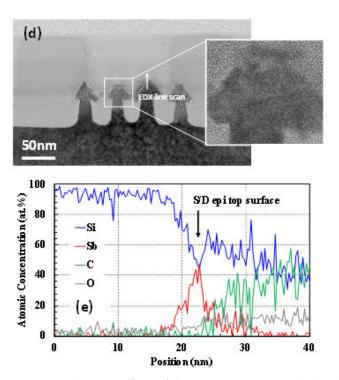

As already mentioned above, another way of enabling the metastable activation of the dopants is SPER. In our previously reported ns UV-LA SPER processes [46], multiplying thermally independent laser shots is necessary to fully crystallize a Si layer amorphized by ion implantation (Figure 10a–c). Then, the moving amorphous/crystalline (a/c) interface maintains a good flatness, resulting in a small root-mean-square value of surface roughness (about 0.10 nm) after SPER completion. An extracted maximum crystallization rate is from 0.8 to 1.8 nm per shot in roughly 10 nm thick amorphous Si layers with different dopants such as B, P, and As (Figure 10d). A rough estimation of film resistivity is also provided based on sheet resistance measurements and an assumption that the conducting layer thickness is equal to the amorphization depth. The calculated film resistivity values imply that the active carrier concentration achieved by ns UV-LA SPER could be higher than that of ns UV-LA LPER.

**Figure 10.** (a–c) Progressive SPER with ns UV-LA multiple pulses in a structure of amorphous Si/SiO<sub>2</sub>/Si substrate. (d) Estimated recrystallization rates for each sample as a function of laser energy density. Reprinted/adapted under CC BY 4.0 from Ref. [46]. 2021, P. Acosta Alba et al.

Electronics **2022**, 11, 2636 11 of 25

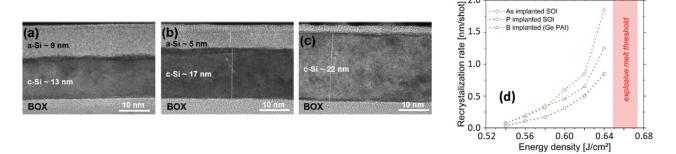

We have reported similar attempts also for  $\mu s$  UV-LA SPER processes [47,57], where the monocrystalline regrowth and flat surface morphology are basically reproduced as in ns UV-LA ones. Interestingly, as shown in Figure 11a,  $\mu s$  UV-LA SPER processes introduce the surface segregation of dopants (indeed, it is known for furnace SPER of As-implanted Si, as reported in Ref. [58]). It is uncertain if our previously reported ns UV-LA processes also induce it. There might be an impact of the SPER rate, which could be different between the reported ns and  $\mu s$  UV-LA processes because of their different ramp-up and cool-down rates. The active carrier concentration measured by the differential Hall effect methodology (DHEM) [59] outperforms  $1 \times 10^{21}$  at./cm³ near the surface. The thermal stability of these active carriers is investigated by using ns UV-LA as deactivation annealing (Figure 11b). The applied deactivation conditions are those which are reported for copper (Cu) or ruthenium (Ru) based the industrial BEOL interconnect annealing by using ns UV-LA. Up to a submillisecond processing, the maximum sheet resistance degradation is limited to about 5%, encouraging UV-LA integration into different stages of the CMOS devices.

**Figure 11.** (a) SIMS and differential Hall effect methodology (DHEM) profiles taken after  $\mu$ s UV-LA SPER. The initial a/c interface position and the As solid solubility in c-Si at  $\sim$ 1000 °C reported in Ref. [60] are also indicated. (b) Ratio of sheet resistance degradation as a function of the accumulated deactivation annealing time by using the ns UV-LA processes giving different maximum temperatures. Reprinted/adapted under CC BY 4.0 from Ref. [47]. 2022, T. Tabata et al.

#### 4. BEOL Applications

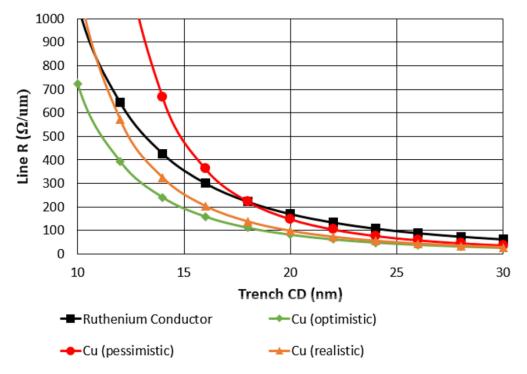

The geometry of the BEOL interconnects (i.e., a trench filled with a highly conductive metal) continuously shrinks. As it limits the growth of metallic grains and results in the increasing density of grain boundaries, electron scattering starts to bring a serious demerit in line resistivity. In fact, there is an exponential relationship between the increase of the line resistivity and the scaling of the cross-sectional area of the BEOL lines (Figure 12) [61–64]. Beyond the 7 nm technology node, alternative metals such as Ru [61,63,65] and cobalt (Co) [61,66,67] start to be considered because of their potential benefit in line resistivity. The figure of merit is determined by a complex combination among bulk resistivity, the cross-sectional area of lines, the mean-free-path of electrons, electro-migration reliability (i.e., melting point of metals), integration compatibility (e.g., availability of raw materials, process uniformity), and the impacts from a barrier and liner. However, some efforts to extend the Cu-based BEOL technologies are found [61,68,69], and indeed Cu-based lines can give lower line resistivity than the alternative metals, even in scaled BEOL modules [61,68]. In addition, it is not realistic to replace all Cu lines in the whole BEOL modules, especially for large interconnects (e.g., semiglobal and global lines [70]).

**Figure 12.** Theoretical trends of line resistance vs. line scale (i.e., trench CD) for Cu- and Ru-based interconnects. Reprinted with permission from Ref. [64]. 2020, American Vacuum Society.

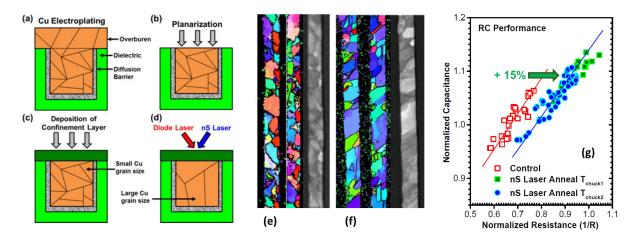

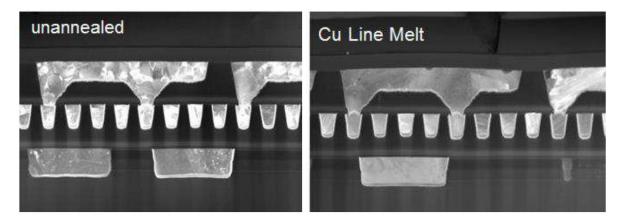

In recent years, the impacts of LA have started to be investigated in real BEOL modules or blanket thin films. Its expected benefit is to enable a bamboo-like structure (i.e., reduction of electron scattering spots) in scaled BEOL lines thanks to the capability of processing wafers at a higher temperature (possibly melting Cu but not Ru) than in typical BEOL furnace annealing (e.g., less than 420 °C up to 1 h [71–74]). As shown in Figures 13 and 14, ns LA (non-UV) indeed shows such a potential [75,76].

**Figure 13.** (a–d) Schematics of ns LA process flow, (e,f) grain analysis performed in the control and Cu melt ns LA lines, (g) RC performance measured in the control and Cu melt ns LA lines. Reprinted/adapted with permission from Ref. [75]. 2018, IEEE.

**Figure 14.** Examples of Cu BEOL lines prior to and after Cu melt LA. Reprinted with permission from Ref. [76]. 2018, The Electrochemical Society (ECS).

#### 4.1. Cu Interconnect

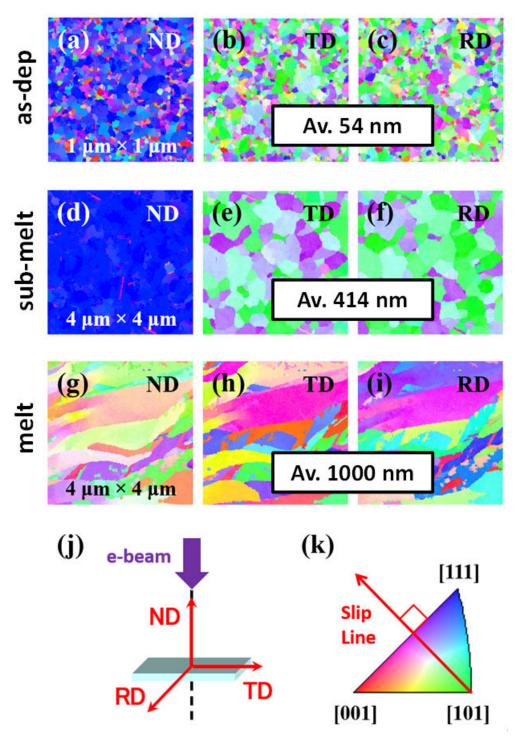

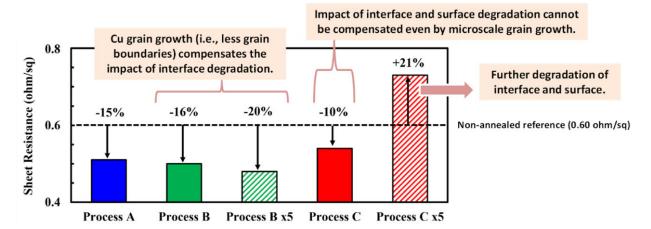

Unfortunately, there is no published work yet about the use of UV-LA in real Cu BEOL modules. However, we have recently conducted some preliminary works by using blanket Cu thin (roughly 50 nm thick) films. Firstly, it has been demonstrated that  $\mu s$  UV-LA enables much greater grain growth than furnace annealing at both Cu submelt and melt conditions. A furnace process at 600 °C typically gives a mean grain size (Av.) of about 100 nm in 50 nm thick Cu films [77,78], whereas it becomes approximately four times and ten times greater in the Cu submelt and melt  $\mu s$  UV-LA, respectively (Figure 15) [79]. Secondly, it has been revealed that even in such a short timescale of process, the structure (i.e., a typical Cu-based BEOL stack of dielectric/Cu/tantalum (Ta)/SiO $_2$ /Si substrate) can be degraded due to interlayer atomic diffusion (Figure 16). Although a process window already exists (e.g., Process A in the Cu submelt shows a 15% reduction of sheet resistance), improving the thermal stability of the Cu-based BEOL structure, for instance, by using an alternative barrier and/or liner (e.g., tantalum nitride (TaN)/Co [68,69], TaN/Ru [68], or tantalum-manganese oxides (TaMn $_x$ O $_y$ ) [68]) would further extend the merit of using UV-LA.

Figure 15. Images of electron diffraction mapping taken for the nonannealed (a–c) and annealed Cu thin films (d–f) are for a Cu submelt µs UV-LA condition, whereas (g–i) are for a Cu melt µs UV-LA condition. As depicted in (j), ND, TD, and RD stand for normal direction, transverse direction, and reference direction, respectively. Moreover, a standard triangle of grain orientations is shown in (k). Reprinted/adapted with permission from Ref. [79]. 2021, IEEE.

Electronics 2022, 11, 2636 15 of 25

| Process | Regime           | (i) Cu diffusion<br>into SiO <sub>2</sub> | (ii) O diffusion<br>into Cu | (iii) Cu/Ta interface<br>degradation | (iv) Cu surface<br>degradation |

|---------|------------------|-------------------------------------------|-----------------------------|--------------------------------------|--------------------------------|

| Α       | Sub-melt @800°C  |                                           |                             |                                      |                                |

| В       | Sub-melt @1000°C | x                                         | x                           | x                                    |                                |

| С       | Melt             |                                           |                             | x                                    | X                              |

**Figure 16.** Sheet resistance measured in the Cu-based BEOL blanket structure (dielectric/Cu/Ta/SiO<sub>2</sub>/Si substrate) before and after μs UV-LA (Processes A, B, and C). Reprinted/adapted with permission from Ref. [80]. 2022, IEEE.

#### 4.2. Ru Interconnect

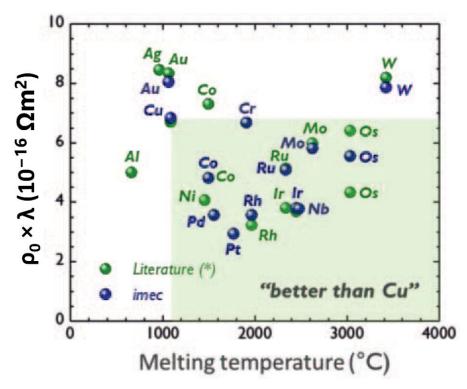

Replacement of Cu with an alternative metal in BEOL interconnects is attractive, especially in local lines [70]. One of the listed candidates is Ru, as shown in Figure 17 [81]. Its smaller mean free path of electrons ( $\lambda$ ) than Cu reduces electron scattering and compensates a disadvantage of bulk resistivity ( $\rho_0$ ). Moreover, its higher melting point than Cu is expected to improve electro-migration performance. Furthermore, Ru is already used in industry-like Cu-based BEOL interconnects as a liner material [82]. Although it is not a focus of this review article, Ru-based BEOL processes (e.g., deposition, CMP, and etching) could therefore rapidly mature.

We have previously evaluated the impact of ns UV-LA on the line resistance of Ru lines fabricated by a 21 nm half-pitch dual-damascene process [83]. Then, although the Ru lines are not supposed to be melted because of its much higher (more than two times) melting point than Cu, the line resistance is reduced for up to 25% by multiple ns UV-LA processes compared to the as-deposited Ru lines.

On the other hand, in a way of further scaling in BEOL interconnects, semidamascene processing (also called "subtractive") is emerging for Ru-based BEOL interconnects [84,85]. This new approach might be more adapted for UV-LA because it allows to anneal the metal before line patterning, and thereby may alleviate the challenge of controlling the effects of light pattern interference. In this context, we have also evaluated grain growth in deposited Ru thin films having a similar thickness to the Cu studies [74,83,86], demonstrating effective grain enlargement and the associated sheet resistance drops with multiple ns UV-LA processes.

Electronics **2022**, 11, 2636 16 of 25

**Figure 17.** Figure of merit defined as mean free path  $(\lambda)$  × bulk resistivity  $(\rho_0)$  vs. melting point for different metals. Reprinted/adjusted with permission from Ref. [81]. 2018, IEEE.

#### 5. "More Than Moore" Applications

Not only in 3D-integrated devices but also in planar ones is the BEOL module the place where the applicable thermal budget is strongly restricted. It often makes material engineering difficult and narrows the range of applications. However, if this restriction is removed, then the diversification of applications will start like cutting a weir. We hereafter present a couple of examples of material engineering in BEOL allowed by short timescale UV-LA.

#### 5.1. Large Poly-Si Grain Formation from Amorphous Si Thin Film

The formation of an electrically active layer (i.e., doped semiconductor with a monocrystalline or polycrystalline state) in BEOL may open a chance for disruptive innovation to boost CMOS performance. However, the maximum process temperature in BEOL is generally much lower than the one enabling solid phase crystallization (SPC) of amorphous Si on SiO<sub>2</sub> (e.g., 600  $^{\circ}$ C for several hours [87,88]). Therefore, there is a clear need for utilizing short timescale UV-LA, with which both liquid phase crystallization (LPC) and SPC will become accessible.

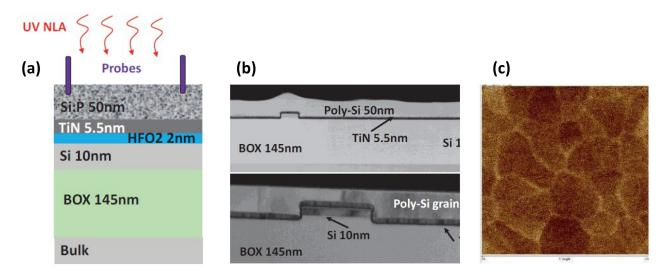

Recently, FinFET device integration into BEOL has been demonstrated with the aim of reducing chip size and power consumption [2]. In this work, a LA (non-UV) process is performed as a key process for crystallizing amorphous Si via LPC. Such a potential has been also demonstrated by ns UV-LA, as shown in Figure 18 [1]. Si-based photonic device integration in BEOL via ns UV-LA LPC can be also found in the literature [89].

Electronics **2022**, 11, 2636 17 of 25

**Figure 18.** (a) Schematic of ns UV-LA in a 3D type structure having an amorphous Si layer on the top, (b) cross-sectional TEM images taken in the test structure followed by ns UV-LA and top amorphous Si melting then by CMP to planarize the top surface, (c) atomic force microprobe image taken after the CMP planarization. Reprinted/adjusted with permission from Ref. [1]. 2018, IEEE.

It should be noted that melting materials in a device structure may engender drawbacks in subsequent processes. As already shown in Figure 18b, Si LPC clearly presents hillocks on the just-crystallized poly-Si surface, and they must be planarized by CMP to follow the device fabrication process flow. It occurs due to the collision of the solidification front among grains crystallizing from the liquid Si, and the hillocks are formed on the final grain boundaries [90]. Interestingly, in the case of the LPER (i.e., no poly grain boundaries) in Si channel extension, shown in Figure 4d, the regrown Si surface keeps a good flatness and does not impact the subsequent S/D epitaxy. Although the surface tension [91] induced on the top of the liquid Si may induce roughening of the regrown surface [92], a thick (tens of nanometers) dielectric capping layer deposited on the partially amorphized Si channel seems to help to avoid the degradation of the surface morphology. Therefore, one may suppose that a similar capping approach could work also for the Si LPC. However, careful consideration would be necessary, because it is known that a periodic surface pattern (called "wrinkles") emerges and evolves in a stack having an elastic layer on a liquid substrate [93]. Our recent study has revealed that the Si melt induced by ns UV-LA in SiO<sub>2</sub>/Si stacks indeed triggers the formation of wrinkles and they grow in a spatial wavelength and height as the maximum melted Si depth increases [94]. As this phenomenon is described by dimensional, mechanical, and viscoelastic parameters of the materials involved in the system, the stack to be treated by ns UV-LA should be carefully designed.

# 5.2. Hf-Based Ferroelectric Layer Formation

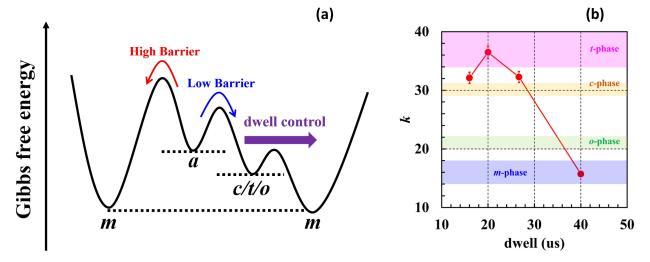

Another application in BEOL which a short timescale UV-LA may enable is the formation of a high relative permittivity or ferroelectric layer (e.g., capacitors integrated into 130 nm CMOS BEOL in Ref. [12]). Hf-based oxides are today well-known as a CMOS technology compatible with ferroelectric thin films [12,95,96]. Their dielectric functionalities (i.e., high relative permittivity or ferroelectricity) rely on crystal phases, and cubic (c), tetragonal (t), orthorhombic (t), and monoclinic (t) ones are typical. The ferroelectricity of HfO2 thin films is related to the t-phase (e.g., Pca21 space group), which emerges during the transition from the t-phase to the t-phase [97,98]. Therefore, it is critical to control the kinetics of nucleation and crystal phase transformation.

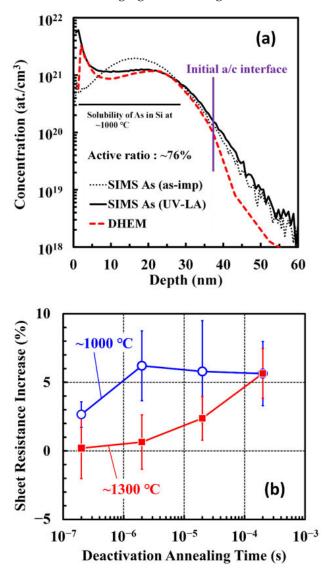

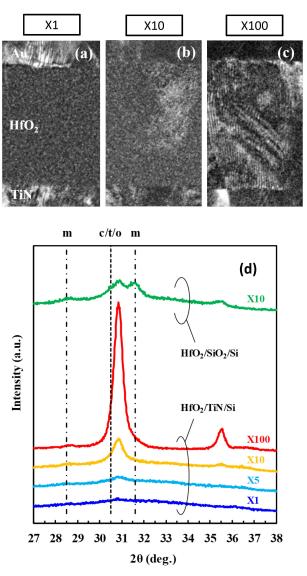

Inspired by previous studies [99,100], we have come up with an idea of shedding a light on it by exploring different process timescales (i.e., dwell time) with ns [101] and  $\mu$ s [102] UV-LA. The expected impact of controlling the dwell time is depicted in Figure 19a. Then, the relative permittivity of the annealed HfO<sub>2</sub> thin film evolves with µs-scale dwell times, as shown in Figure 19b, supporting the proposed idea. The appearance of ferroelectricity is also experimentally evidenced in this study by means of PUND (Positive Up Negative Down)-corrected polarization-voltage (P-V) measurements [103]. When squeezing the dwell timescale toward the ns range, it is expected that HfO2 phase control comes to rely on nucleation rather than phase transformation. Indeed, repetition of the ns UV-LA process results in a cumulative crystallization of the same phase, as shown in Figure 20. The selectivity of the phase to nucleate in the ns UV-LA seems dependent on the maximum process temperature [12], doping content [12], and stack [101]. As a temperature range of interest is the one near or beyond the Si melting point [12], it is necessary to insert additional layers for efficient UV laser absorption and heat confinement. An example is a stack of metal/HfO<sub>2</sub>/metal/SiO<sub>2</sub>/Si, as shown in Ref. [12], where the metal layers work for UV laser absorption and the SiO<sub>2</sub> layer does for heat confinement in the upper metal/HfO<sub>2</sub>/metal part. Silicon (amorphous, polycrystalline, or monocrystalline) can also be used instead of the metal layers. Some doping elements are known to stabilize the ferroelectric phase in HfO<sub>2</sub> [104,105]. At a given process temperature, the cooling profile may be slightly modulated by the stack and allow partial phase transformation within the nuclei (but their growth with a single ns laser shot would be almost negligible because of limited atomic diffusion in the ns-scale [101]).

**Figure 19.** (a) Schematic Gibbs free energy diagram of different HfO<sub>2</sub> crystal phases, where the character "a" stands for the amorphous state, "c" for the c-phase, "t" for the t-phase, "o" for the o-phase, and "m" for the m-phase, respectively. (b) Relative permittivity (k) values of the 10 nm thick HfO<sub>2</sub> films as a function of the UV-LA dwell time. The theoretically predicted k-value range of each phase is shown together. Reprinted/adjusted with permission from Ref. [102]. 2021, The Japan Society of Applied Physics.

**Figure 20.** (a–c) Cross-sectional dark-field TEM images and (d) XRD patterns taken on 50 nm thick  $HfO_2/TiN/Si$  samples after single or multiple ns UV-LA processing. Reprinted/adjusted with permission from Ref. [101]. 2020, The Japan Society of Applied Physics.

# 6. Conclusions

In this review, recent progresses of ns and µs UV-LA technologies have been reviewed, focusing on applications relevant to CMOS devices. The selectivity of heating in the vertical direction that short timescale UV-LA provides is highlighted as a key feature for 3D integration. The presented applications vary from FEOL to BEOL, indicating the high potential of integrating UV-LA processes into different stages of a CMOS fabrication flow. From the viewpoint of materials science, short timescale UV-LA opens new fields of research, especially related to its nonequilibrium aspect. Although the reported range of process timescale from ns to µs is long enough to be at thermal equilibrium [106], it is still chemically and mechanically out of equilibrium. Therefore, phenomena such as atomic bonding rearrangement, diffusion, activation, crystallization (including grain growth), and stress relaxation show interesting behaviors. From them, module-level major improvements to boost the entire CMOS performance may be achieved. Even if there is still a lot of effort required to integrate the presented UV-LA processes into the industrial CMOS devices, the technological maturity of short-timescale UV-LA is steadily progressing.

Electronics **2022**, 11, 2636 20 of 25

**Author Contributions:** Writing—original draft preparation, T.T.; writing—review and editing, F.R., L.T., S.H., P.-E.R., I.K. and K.H. All authors have read and agreed to the published version of the manuscript.

**Funding:** This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement no. 875999. The JU receives support from the European Union's Horizon 2020 research and innovation programme, and the Netherlands, Belgium, Germany, France, Austria, Hungary, United Kingdom, Romania, and Israel.

**Institutional Review Board Statement:** Not applicable.

**Informed Consent Statement:** Not applicable.

Data Availability Statement: Not applicable.

**Acknowledgments:** The authors thank their former colleagues, Joris Aubin and Fulvio Mazzamuto, for their contribution to the works cited in this review article, as well as all other LASSE employees for their contribution to the development of ns and μs UV-LA platforms.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Brunet, L.; Fenouillet-Beranger, C.; Batude, P.; Beaurepaire, S.; Ponthenier, F.; Rambal, N.; Mazzocchi, V.; Pin, J.-B.; Acosta-Alba, P.; Kerdilès, S.; et al. Breakthroughs in 3D Sequential technology. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 7.2.1–7.2.4. [CrossRef]

- 2. Hsieh, P.-Y.; Chang, Y.-J.; Chen, P.-J.; Chen, C.-L.; Yang, C.-C.; Huang, P.-T.; Chen, Y.-J.; Shen, C.-M.; Liu, Y.-W.; Huang, C.-C.; et al. Monolithic 3D BEOL FinFET switch arrays using location-controlled-grain technique in voltage regulator with better FOM than 2D regulators. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 3.1.1–3.1.4. [CrossRef]

- 3. Batude, P.; Brunet, L.; Fenouillet-Beranger, C.; Andrieu, F.; Colinge, J.-P.; Lattard, D.; Vianello, E.; Thuries, S.; Billoint, O.; Vivet, P.; et al. 3D Sequential Integration: Application-driven technological achievements and guidelines. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 3.1.1–3.1.4. [CrossRef]

- 4. Cavalcante, C.; Fenouillet-Beranger, C.; Batude, P.; Garros, X.; Federspiel, X.; Lacord, J.; Kerdilès, S.; Royet, A.S.; Acosta-Alba, P.; Rozeau, O.; et al. 28nm FDSOI CMOS Technology (FEOL and BEOL) Thermal Stability for 3D Sequential Integration: Yield and Reliability Analysis. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [CrossRef]

- 5. Huet, K.; Mazzamuto, F.; Tabata, T.; Toqué-Tresonne, I.; Mori, Y. Doping of semiconductor devices by Laser Thermal Annealing. *Mater. Sci. Semicond. Process.* **2017**, *62*, 92–102. [CrossRef]

- 6. Lombardo, S.F.; Fisicaro, G.; Deretzis, I.; La Magna, A.; Curver, B.; Lespinasse, B.; Huet, K. Theoretical study of the laser annealing process in FinFET structures. *Appl. Surf. Sci.* **2019**, 467–468, 666–672. [CrossRef]

- 7. Shen, C.-H.; Shieh, J.-M.; Wu, T.-T.; Huang, W.-H.; Yang, C.-C.; Wan, C.-J.; Lin, C.-D.; Wang, H.-H.; Chen, B.-Y.; Huang, G.-W.; et al. Monolithic 3D chip integrated with 500ns NVM, 3ps logic circuits and SRAM. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 9.3.1–9.3.4. [CrossRef]

- 8. Shulaker, M.M.; Wu, T.F.; Pal, A.; Zhao, L.; Nishi, Y.; Saraswat, K.; Wong, H.-S.P.; Mitra, S. Monolithic 3D integration of logic and memory: Carbon nanotube FETs, resistive RAM, and silicon FETs. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 27.4.1–27.4.4. [CrossRef]

- 9. Wu, T.-T.; Shen, C.-H.; Shieh, J.-M.; Huang, W.-H.; Wang, H.-H.; Hsueh, F.-K.; Chen, H.-C.; Yang, C.-C.; Hsieh, T.-Y.; Chen, B.-Y.; et al. Low-cost and TSV-free monolithic 3D-IC with heterogeneous integration of logic, memory and sensor analogy circuitry for Internet of Things. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 25.4.1–25.4.4. [CrossRef]

- 10. Yang, C.-C.; Hsieh, T.-Y.; Huang, P.-T.; Chen, K.-N.; Wu, W.-C.; Chen, S.-W.; Chang, C.-H.; Shen, C.-H.; Shieh, J.-M.; Hu, C.; et al. Location-controlled-grain Technique for Monolithic 3D BEOL FinFET Circuits. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 11.3.1–11.3.4. [CrossRef]

- 11. Francois, T.; Grenouillet, L.; Coignus, J.; Blaise, P.; Carabasse, C.; Vaxelaire, N.; Magis, T.; Aussenac, F.; Loup, V.; Pellissier, C.; et al. Demonstration of BEOL-compatible ferroelectric Hf0.5Zr0.5O2 scaled FeRAM co-integrated with 130 nm CMOS for embedded NVM applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 15.7.1–15.7.4. [CrossRef]

Electronics **2022**, 11, 2636 21 of 25

12. Grenouillet, L.; Francois, T.; Coignus, J.; Kerdilès, S.; Vaxelaire, N.; Carabasse, C.; Mehmood, F.; Chevalliez, S.; Pellissier, C.; Triozon, F.; et al. Nanosecond Laser Anneal (NLA) for Si-Implanted HfO<sub>2</sub> Ferroelectric Memories Integrated in Back-End of Line (BEOL). In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [CrossRef]

- 13. Srimani, T.; Hills, G.; Bishop, M.; Lau, C.; Kanhaiya, P.; Ho, R.; Amer, A.; Chao, M.; Yu, A.; Wright, A.; et al. Heterogeneous Integration of BEOL Logic and Memory in a Commercial Foundry: Multi-Tier Complementary Carbon Nanotube Logic and Resistive RAM at a 130 nm node. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [CrossRef]

- 14. Morin, P.; Tabata, T.; Rozé, F.; Saib, M.; Thielens, H.; Thuries, L.; Huet, K.; Mazzamuto, F. Impact of the buried oxide thickness in UV laser heated 3D stacks. In Proceedings of the 2021 Solid State Devices and Materials (SSDM), Virtual, 6–9 September 2021; p. A-6-03.

- 15. Ragnarsson, L.-Å.; Dekkers, H.; Matagne, P.; Schram, T.; Conard, T.; Horiguchi, N.; Thean, A.V.-Y. Zero-thickness multi work function solutions for N7 bulk FinFETs. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [CrossRef]

- 16. Bury, E.; Kaczer, B.; Arimura, H.; Toledano Luque, M.; Ragnarsson, L.Å.; Roussel, P.; Veloso, A.; Chew, S.A.; Togo, M.; Schram, T.; et al. Reliability in gate first and gate last ultra-thin-EOT gate stacks assessed with CV-eMSM BTI characterization. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. GD.3.1–GD.3.5. [CrossRef]

- 17. Rzepa, G.; Franco, J.; Subirats, A.; Jech, M.; Chasin, A.; Grill, A.; Waltl, M.; Knobloch, T.; Stampfer, B.; Chiarella, T.; et al. Efficient physical defect model applied to PBTI in high-κ stacks. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. XT-11.1–XT-11.6. [CrossRef]

- Franco, J.; Wu, Z.; Rzepa, G.; Vandooren, A.; Arimura, H.; Ragnarsson, L.-Å.; Hellings, G.; Brus, S.; Cott, D.; De Heyn, V.; et al. BTI Reliability Improvement Strategies in Low Thermal Budget Gate Stacks for 3D Sequential Integration. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 34.2.1–34.2.4. [CrossRef]

- 19. Denais, M.; Huard, V.; Parthasarathy, C.; Ribes, G.; Perrier, F.; Revil, N.; Bravaix, A. Interface trap generation and hole trapping under NBTI and PBTI in advanced CMOS technology with a 2-nm gate oxide. *IEEE Trans. Device Mater. Reliab.* **2004**, *4*, 715–722. [CrossRef]

- 20. Franco, J.; Arimura, H.; de Marneffe, J.-F.; Wu, Z.; Vandooren, A.; Ragnarsson, L.-Å.; Dentoni Litta, E.; Horiguchi, N.; Croes, K.; Linten, D.; et al. Low-temperature atomic and molecular hydrogen anneals for enhanced chemical SiO<sub>2</sub> IL quality in low thermal budget RMG stacks. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 31.4.1–31.4.4. [CrossRef]

- 21. Franco, J.; de Marneffe, J.-F.; Vandooren, A.; Arimura, H.; Ragnarsson, L.-Å.; Claes, D.; Dentoni Litta, E.; Horiguchi, N.; Croes, K.; Linten, D.; et al. Low Temperature Atomic Hydrogen Treatment for Superior NBTI Reliability—Demonstration and Modeling across SiO<sub>2</sub> IL Thicknesses from 1.8 to 0.6 nm for I/O and Core Logic. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2.

- 22. Sometani, M.; Hasunuma, R.; Ogino, M.; Kuribayashi, H.; Sugahara, Y.; Uedono, A.; Yamabe, K. Variation of Chemical Vapor Deposited SiO<sub>2</sub> Density Due to Generation and Shrinkage of Open Space During Thermal Annealing. *Jpn. J. Appl. Phys.* **2012**, 51, 021101. [CrossRef]

- 23. Tabata, T.; Inoue, K.; Yoshida, Y.; Takahashi, H. Non-equilibrium engineering of chemically grown SiO<sub>2</sub>/Si by UV nanosecond pulsed laser annealing from the viewpoint of bias temperature instability sources. *Appl. Phys. Express* **2020**, *14*, 011003. [CrossRef]

- 24. Khanna, V.K. Short-Channel Effects in MOSFETs. In *Integrated Nanoelectronics*. *NanoScience and Technology*, 1st ed.; Springer: New Delhi, India, 2016; pp. 73–93. [CrossRef]

- 25. Yau, L.D. A simple theory to predict the threshold voltage of short-channel IGFET's. *Solid-State Electron.* **1974**, 17, 1059–1063. [CrossRef]

- 26. Bracht, H. Advanced dopant and self-diffusion studies in silicon. *Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. At.* **2006**, 253, 105–112. [CrossRef]

- 27. Kodera, H. Diffusion Coefficients of Impurities in Silicon Melt. Jpn. J. Appl. Phys. 1963, 2, 212–219. [CrossRef]

- 28. Huet, K.; Boniface, C.; Fisicaro, G.; Desse, F.; Variam, N.; Erokhin, Y.; La Magna, A.; Privitera, V.; Schuhmacher, M.; Besaucele, H.; et al. Experimental and theoretical analysis of dopant activation in double implanted silicon by pulsed laser thermal annealing. In Proceedings of the 17th International Conference on Advanced Thermal Processing of Semiconductors, Albany, NY, USA, 29 September–2 October 2009; pp. 1–16. [CrossRef]

- 29. Venturini, J. Laser Thermal Annealing: Enabling ultra-low thermal budget processes for 3D junctions formation and devices. In Proceedings of the 12th International Workshop on Junction Technology, Shanghai, China, 14–15 May 2012; pp. 57–62. [CrossRef]

- 30. Qiu, Y.; Cristiano, F.; Huet, K.; Mazzamuto, F.; Fisicaro, G.; La Magna, A.; Quillec, M.; Cherkashin, N.; Wang, H.; Duguay, S.; et al. Extended Defects Formation in Nanosecond Laser-Annealed Ion Implanted Silicon. *Nano Lett.* **2014**, *14*, 1769–1775. [CrossRef]

- 31. Lombardo, S.F.; Lombardo, S.F.; Boninelli, S.; Cristiano, F.; Deretzis, I.; Grimaldi, M.G.; Huet, K.; Napolitani, E.; La Magna, A. Phase field model of the nanoscale evolution during the explosive crystallization phenomenon. *J. Appl. Phys.* **2018**, 123, 105105. [CrossRef]

Electronics **2022**, 11, 2636 22 of 25

32. Vandooren, A.; Wu, Z.; Parihar, N.; Franco, J.; Parvais, B.; Matagne, P.; Debruyn, H.; Mannaert, G.; Devriendt, K.; Teugels, L.; et al. 3D Sequential Low Temperature Top Tier Devices using Dopant Activation with Excimer Laser Anneal and Strained Silicon as Performance Boosters. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [CrossRef]

- 33. Ni, C.-N.; Rao, K.V.; Khaja, F.; Sharma, S.; Tang, S.; Chen, J.J.; Hollar, K.E.; Breil, N.; Li, X.; Jin, M.; et al. Ultra-low NMOS contact resistivity using a novel plasma-based DSS implant and laser anneal for post 7 nm nodes. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [CrossRef]

- 34. Van Dal, M.J.H.; Vellianitis, G.; Doornbos, G.; Duriez, B.; Holland, M.C.; Vasen, T.; Afzalian, A.; Chen, E.; Su, S.K.; Chen, T.K.; et al. Ge CMOS gate stack and contact development for Vertically Stacked Lateral Nanowire FETs. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 21.1.1–21.1.4. [CrossRef]

- 35. Yu, H.; Schaekers, M.; Hikavyy, A.; Rosseel, E.; Peter, A.; Hollar, K.; Khaja, F.A.; Aderhold, W.; Date, L.; Mayur, A.J.; et al. Ultralow-resistivity CMOS contact scheme with pre-contact amorphization plus Ti (germano-)silicidation. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [CrossRef]

- 36. Wang, L.-L.; Yu, H.; Schaekers, M.; Everaert, J.-L.; Franquet, A.; Douhard, B.; Date, L.; del Agua Borniquel, J.; Hollar, K.; Khaja, F.A.; et al. Comprehensive study of Ga activation in Si, SiGe and Ge with  $5 \times 10^{-10} \,\Omega \cdot \text{cm}^2$  contact resistivity achieved on Ga doped Ge using nanosecond laser activation. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 22.4.1–22.4.4. [CrossRef]

- 37. Niimi, H.; Liu, Z.; Gluschenkov, O.; Mochizuki, S.; Fronheiser, J.; Li, J.; Demarest, J.; Zhang, C.; Liu, B.; Yang, J.; et al. Sub-10<sup>-9</sup> Ω-cm<sup>2</sup> n-Type Contact Resistivity for FinFET Technology. *IEEE Electron Device Lett.* **2016**, 37, 1371–1374. [CrossRef]

- 38. Schroder, D.K. Contact Resistance and Schottky Barriers. In *Semiconductor Material and Device Characterization*, 3rd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2006; pp. 127–184. [CrossRef]

- 39. Everaert, J.-L.; Schaekers, M.; Yu, H.; Wang, L.-L.; Hikavyy, A.; Date, L.; del Agua Borniquel, J.; Hollar, K.; Khaja, F.A.; Aderhold, W.; et al. Sub-10<sup>-9</sup> Ω·cm² contact resistivity on p-SiGe achieved by Ga doping and nanosecond laser activation. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T214–T215. [CrossRef]

- 40. Tabata, T.; Aubin, J.; Huet, K.; Mazzamuto, F. Segregation and activation of Ga in high Ge content SiGe by UV melt laser anneal. *J. Appl. Phys.* **2019**, 125, 215702. [CrossRef]

- 41. Tabata, T.; Huet, K.; Mazzamuto, F.; La Magna, A. Surface segregated Ga, In, and Al activation in high Ge content SiGe during UV melt laser induced non-equilibrium solidification. *Jpn. J. Appl. Phys.* **2020**, *58*, 120911. [CrossRef]

- 42. Tabata, T.; Raynal, P.-E.; Huet, K.; Everaert, J.-L. Segregation and activation of Sb implanted in Si by UV nanosecond-laser-anneal-induced non-equilibrium solidification. *J. Appl. Phys.* **2020**, *127*, 135701. [CrossRef]

- 43. Tabata, T.; Aubin, J.; Mazzamuto, F. Multilayered highly-active dopant distribution by UV nanosecond melt laser annealing in Ga and B co-implanted high Ge content SiGe:B epilayers. *Jpn. J. Appl. Phys.* **2020**, *59*, 050903. [CrossRef]

- 44. Tabata, T.; Huet, K.; Rozé, F.; Mazzamuto, F.; Sermage, B.; Kopalidis, P.; Roh, D. Dopant Redistribution and Activation in Ga Ion-Implanted High Ge Content SiGe by Explosive Crystallization during UV Nanosecond Pulsed Laser Annealing. ECS J. Solid State Sci. Technol. 2021, 10, 023005. [CrossRef]

- 45. Albenze, E.J.; Thompson, M.O.; Clancy, P. Atomistic computer simulation of explosive crystallization in pure silicon and germanium. *Phys. Rev. B* **2004**, *70*, 094110. [CrossRef]

- 46. Acosta Alba, P.; Aubin, J.; Perrot, S.; Mazzamuto, F.; Grenier, A.; Kerdilès, S. Solid phase recrystallization induced by multi-pulse nanosecond laser annealing. *Appl. Surf. Sci. Adv.* **2021**, *3*, 100053. [CrossRef]

- 47. Tabata, T.; Rozé, F.; Thuries, L.; Halty, S.; Raynal, P.-E.; Huet, K.; Mazzamuto, F.; Joshi, A.; Basol, B.M.; Acosta Alba, P. Microsecond non-melt UV laser annealing for future 3D-stacked CMOS. *Appl. Phys. Express* **2022**, *15*, 061002. [CrossRef]

- 48. Wood, R.F. Model for nonequilibrium segregation during pulsed laser annealing. Appl. Phys. Lett. 1980, 37, 302. [CrossRef]

- 49. Galenko, P. Solute trapping and diffusionless solidification in a binary system. Phys. Rev. E 2007, 76, 031606. [CrossRef]

- 50. Poulton, J.T.L.; Bowler, D.R. An Ab Initio Study of Aluminium self-compensation in Bulk Silicon. *arXiv* **2019**, arXiv:1907.03636. [CrossRef]

- 51. Narayan, J. Interface instability and cell formation in ion-implanted and laser-annealed silicon. *J. Appl. Phys.* **1981**, *52*, 1289. [CrossRef]

- 52. Tabata, T.; Curvers, B.; Huet, K.; Chew, S.A.; Everaert, J.-L.; Horiguchi, N. 3D Simulation for Melt Laser Anneal Integration in FinFET's Contact. *IEEE J. Electron Devices Soc.* **2020**, *8*, 1323–1327. [CrossRef]

- 53. Trumbore, F.A. Solid solubilities of impurity elements in germanium and silicon. Bell Syst. Tech. J. 1960, 39, 205–233. [CrossRef]

- 54. Vandooren, A.; Tabata, T.; Eyben, P.; Roseel, E.; Hikavyy, A.; Huet, K.; Mazzamuto, F.; Dentoni Litta, E.; Horiguchi, N. Potential benefits of S/D HDD activation by melt laser annealing in 3D-inte-grated top-tier FDSOI FETs. In Proceedings of the 2021 Solid State Devices and Materials (SSDM), Virtual, 6–9 September 2021; p. A-6-02.

- 55. Dagault, L.; Acosta-Alba, P.; Kerdilès, S.; Barnes, J.P.; Hartmann, J.M.; Gergaud, P.; Nguyen, T.T.; Grenier, A.; Papon, A.M.; Bernier, N.; et al. Impact of UV Nanosecond Laser Annealing on Composition and Strain of Undoped Si<sub>0.8</sub>Ge<sub>0.2</sub> Epitaxial Layers. *ECS J. Solid State Sci. Technol.* **2019**, *8*, P202. [CrossRef]

- 56. Dagault, L.; Kerdilès, S.; Acosta Alba, P.; Hartmann, J.-M.; Barnes, J.-P.; Gergaud, P.; Scheid, E.; Cristiano, F. Investigation of recrystallization and stress relaxation in nanosecond laser annealed Si<sub>1-x</sub>Ge<sub>x</sub>/Si epilayers. *Appl. Surf. Sci.* 2020, 527, 146752. [CrossRef]

Electronics **2022**, 11, 2636 23 of 25

57. Tabata, T.; Roze, F.; Alba, P.A.; Halty, S.; Raynal, P.-E.; Karmous, I.; Kerdiles, S.; Mazzamuto, F. Solid Phase Recrystallization in Arsenic Ion-Implanted Silicon-On-Insulator by Microsecond UV Laser Annealing. *arXiv* 2022, arXiv:2204.12167. [CrossRef]

- 58. Hopstaken, M.J.P.; Tamminga, Y.; Verheijen, M.A.; Duffy, R.; Venezia, V.C.; Heringa, A. Effects of crystalline regrowth on dopant profiles in preamorphized silicon. *Appl. Surf. Sci.* **2004**, *231*–232, 688–692. [CrossRef]

- 59. Joshi, A.; Basol, B.M. Sub-nm Near-Surface Activation Profiling for Highly Doped Si and Ge Using Differential Hall Effect Metrology (DHEM). *ECS Trans.* **2020**, *98*, 405. [CrossRef]

- 60. Lietoila, A.; Gibbons, J.F.; Sigmon, T.W. The solid solubility and thermal behavior of metastable concentrations of As in Si. *Appl. Phys. Lett.* **1980**, *36*, 765. [CrossRef]

- 61. Nogami, T.; Zhang, X.; Kelly, J.; Briggs, B.; You, H.; Patlolla, R.; Huang, H.; McLaughlin, P.; Lee, J.; Shobha, H.; et al. Comparison of key fine-line BEOL metallization schemes for beyond 7 nm node. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T148–T149. [CrossRef]

- 62. Nogami, T. Overview of interconnect technology for 7nm node and beyond-New materials and technologies to extend Cu and to enable alternative conductors. In Proceedings of the 2019 Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; pp. 38–40. [CrossRef]

- 63. Nogami, T.; Gluschenkov, O.; Sulehria, Y.; Nguyen, S.; Huang, H.; Lanzillo, N.A.; DeSilva, A.; Mignot, Y.; Church, J.; Lee, J.; et al. Advanced BEOL Interconnects. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020; pp. 1–3. [CrossRef]

- 64. Simon, A.; van der Straten, O.; Lanzillo, N.A.; Yang, C.-C.; Nogami, T.; Edelstein, D.C. Role of high aspect-ratio thin-film metal deposition in Cu back-end-of-line technology. *J. Vac. Sci. Technol. A* **2020**, *38*, 053402. [CrossRef]

- 65. Murdoch, G.; Tokei, Z.; Paolillo, S.; Varela Pedreira, O.; Vanstreels, K.; Wilson, C.J. Semidamascene Interconnects for 2nm node and Beyond. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020; pp. 4–6. [CrossRef]

- 66. Hu, C.-K.; Kelly, J.; Chen, J.H.-C.; Huang, H.; Ostrovski, Y.; Patlolla, R.; Peethala, B.; Adusumilli, P.; Spooner, T.; Gignac, L.M.; et al. Electromigration and resistivity in on-chip Cu, Co and Ru damascene nanowires. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017; pp. 1–3. [CrossRef]

- 67. Bhosale, P.; Parikh, S.; Lanzillo, N.; Tao, R.; Nogami, T.; Gage, M.; Shaviv, R.; Huang, H.; Simon, A.; Stolfi, M.; et al. Composite Interconnects for High-Performance Computing beyond the 7 nm Node. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [CrossRef]

- 68. Nogami, T.; Briggs, B.D.; Korkmaz, S.; Chae, M.; Penny, C.; Li, J.; Wang, W.; McLaughlin, P.S.; Kane, T.; Parks, C.; et al. Through-Cobalt Self Forming Barrier (tCoSFB) for Cu/ULK BEOL: A novel concept for advanced technology nodes. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 8.1.1–8.1.4. [CrossRef]

- 69. Lanzillo, N.A.; Yang, C.-C.; Motoyama, K.; Huang, H.; Cheng, K.; Maniscalco, J.; Van Der Straten, O.; Penny, C.; Standaert, T.; Choi, K. Exploring the Limits of Cobalt Liner Thickness in Advanced Copper Interconnects. *IEEE Electron Device Lett.* **2019**, 40, 1804–1807. [CrossRef]

- 70. Ezz-Eldin, R.; El-Moursy, M.A.; Hamed, H.F.A. Interconnection. In *Analysis and Design of Networks-on-Chip Under High Process Variation*, 1st ed.; Springer: Berlin/Heidelberg, Germany, 2015; pp. 45–56. [CrossRef]

- 71. Yang, C.-C.; Witt, C.; Wang, P.-C.; Edelstein, D.; Rosenberg, R. Stress control during thermal annealing of copper interconnects. *Appl. Phys. Lett.* **2011**, *98*, 051911. [CrossRef]

- 72. Yang, C.-C.; Spooner, T.; McLaughlin, P.; Hu, C.K.; Huang, H.; Mignot, Y.; Ali, M.; Lian, G.; Quon, R.; Standaert, T.; et al. Microstructure modulation for resistance reduction in copper interconnects. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017; pp. 1–3. [CrossRef]

- 73. Dutta, S.; Moors, K.; Vandemaele, M.; Adelmann, C. Finite Size Effects in Highly Scaled Ruthenium Interconnects. *IEEE Electron Device Lett.* **2018**, 39, 268–271. [CrossRef]

- 74. Sil, D.; Sulehria, Y.; Gluschenkov, O.; Nogami, T.; Cornell, R.; Simon, A.; Li, J.; Demarest, J.; Haran, B.; Lavoie, C.; et al. Impact of Nanosecond Laser Anneal on PVD Ru Films. In Proceedings of the 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 6–9 July 2021; pp. 1–3. [CrossRef]

- 75. Lee, R.T.P.; Petrov, N.; Kassim, J.; Gribelyuk, M.; Yang, J.; Cao, L.; Yeap, K.B.; Shen, T.; Zainuddin, A.N.; Chandrashekar, A.; et al. Nanosecond Laser Anneal for BEOL Performance Boost in Advanced FinFETs. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 61–62. [CrossRef]

- 76. Gluschenkov, O.; Jagannathan, H. Laser Annealing in CMOS Manufacturing. ECS Trans. 2018, 85, 11. [CrossRef]

- 77. Sun, T.; Yao, B.; Warren, A.P.; Barmak, K.; Toney, M.F.; Peale, R.E.; Coffey, K.R. Surface and grain-boundary scattering in nanometric Cu films. *Phys. Rev. B* **2010**, *81*, 155454. [CrossRef]

- 78. Chawla, J.S.; Gstrein, F.; O'Brien, K.P.; Clarke, J.S.; Gall, D. Electron scattering at surfaces and grain boundaries in Cu thin films and wires. *Phys. Rev. B* **2011**, *84*, 235423. [CrossRef]

- 79. Tabata, T.; Raynal, P.-E.; Rozé, F.; Halty, S.; Thuries, L.; Cristiano, F.; Scheid, E.; Mazzamuto, F. Copper Large-Scale Grain Growth by UV Nanosecond Pulsed Laser Annealing. In Proceedings of the 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 6–9 July 2021; pp. 1–3. [CrossRef]

Electronics **2022**, 11, 2636 24 of 25

80. Demoulin, R.; Daubriac, R.; Thuries, L.; Scheid, E.; Rozé, F.; Cristiano, F.; Tabata, T.; Mazzamuto, F. Failure Mode Analysis in Microsecond UV Laser Annealing of Cu Thin Films. In Proceedings of the 2022 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 27–30 June 2022; p. 5.5.

- 81. Croes, K.; Adelmann, C.; Wilson, C.J.; Zahedmanesh, H.; Varela Pedreira, O.; Wu, C.; Leśniewska, A.; Oprins, H.; Beyne, S.; Ciofi, I.; et al. Interconnect metals beyond copper: Reliability challenges and opportunities. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 5.3.1–5.3.4. [CrossRef]

- 82. Motoyama, K.; van der Straten, O.; Maniscalco, J.; Huang, H.; Kim, Y.B.; Choi, J.K.; Lee, J.H.; Hu, C.-K.; McLaughlin, P.; Standaert, T.; et al. Ru Liner Scaling with ALD TaN Barrier Process for Low Resistance 7 nm Cu Interconnects and Beyond. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 40–42. [CrossRef]

- 83. Jourdan, N.; Rozé, F.; Tabata, T.; Lariviere, S.; Contino, A.; Mazzamuto, F.; Zsolt, T. UV nanosecond laser annealing for Ru interconnects. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020; pp. 163–165. [CrossRef]

- 84. Wan, D.; Paolillo, S.; Rassoul, N.; Kutrzeba Kotowska, B.; Blanco, V.; Adelmann, C.; Lazzarino, F.; Ercken, M.; Murdoch, G.; Bömmels, J.; et al. Subtractive Etch of Ruthenium for Sub-5nm Interconnect. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 10–12. [CrossRef]

- 85. Na, M.H.; Jang, D.; Baert, R.; Sarkar, S.; Patli, S.; Zografos, O.; Chehab, B.; Spessot, A.; Sisto, G.; Schuddinck, P.; et al. Disruptive Technology Elements, and Rapid and Accurate Block-Level Performance Evaluation for 3nm and Beyond. In Proceedings of the 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Chengdu, China, 8–11 April 2021; pp. 1–3. [CrossRef]

- 86. Nogami, T.; Gluschenkov, O.; Sulehria, Y.; Nguyen, S.; Peethala, B.; Huang, H.; Shobha, H.; Lanzillo, N.; Patlolla, R.; Sil, D.; et al. Advanced BEOL Materials, Processes, and Integration to Reduce Line Resistance of Damascene Cu, Co, and Subtractive Ru Interconnects. In Proceedings of the 2022 Symposium on VLSI Technology, Honolulu, HI, USA, 13–17 June 2022; p. TFS2-1.

- 87. Shimizu, T.; Ishihara, S. Effect of SiO<sub>2</sub> Surface Treatment on the Solid-Phase Crystallization of Amorphous Silicon Films. *J. Electrochem. Soc.* **1995**, 142, 298. [CrossRef]

- 88. Ryu, M.-K.; Hwang, S.-M.; Kim, T.-H.; Kim, K.-B. The effect of surface nucleation on the evolution of crystalline microstructure during solid phase crystallization of amorphous Si films on SiO<sub>2</sub>. *Appl. Phys. Lett.* **1997**, *71*, 3063. [CrossRef]

- 89. Lee, Y.H.D.; Lipson, M. Back-End Deposited Silicon Photonics for Monolithic Integration on CMOS. *IEEE J. Sel. Top. Quantum Electron.* **2013**, *19*, 8200207. [CrossRef]

- 90. He, M.; Metselaar, W.; Beenakker, K. (100)-textured self-assembled square-shaped polycrystalline silicon grains by multiple shot excimer laser crystallization. *J. Appl. Phys.* **2006**, *100*, 083103. [CrossRef]

- 91. Eustathopoulos, N.; Drevet, B. Surface tension of liquid silicon: High or low value? J. Cryst. Growth 2013, 371, 77–83. [CrossRef]

- 92. Choi, D.; Shin, J. Study of phosphorus-doped Si annealed by a multi-wavelength laser. Results Phys. 2022, 38, 105632. [CrossRef]

- 93. Huang, R.; Im, S.H. Dynamics of wrinkle growth and coarsening in stressed thin films. Phys. Rev. E 2006, 74, 026214. [CrossRef]

- 94. Karmous, I.; Rozé, F.; Raynal, P.-E.; Huet, K.; Acosta-Alba, P.; Tabata, T.; Kerdilès, S. Wrinkles Emerging in SiO<sub>2</sub>/Si Stack during UV Nanosecond Laser Anneal. *ECS Trans.* **2021**, *102*, 125–137. [CrossRef]

- 95. Böscke, T.S.; Müller, J.; Bräuhaus, D.; Schröder, U.; Böttger, U. Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 24.5.1–24.5.4. [CrossRef]

- 96. Müller, J.; Schröder, U.; Böscke, T.S.; Müller, I.; Böttger, U.; Wilde, L.; Sundqvist, J.; Lemberger, M.; Kücher, P.; Mikolajick, T.; et al. Ferroelectricity in yttrium-doped hafnium oxide. *J. Appl. Phys.* **2011**, *110*, 114113. [CrossRef]

- 97. Huan, T.D.; Sharma, V.; Rossetti, G.A.; Ramprasad, R. Pathways towards ferroelectricity in hafnia. *Phys. Rev. B* **2014**, *90*, 064111. [CrossRef]

- 98. Park, M.H.; Schenk, T.; Fancher, C.M.; Grimley, E.D.; Zhou, C.; Richter, C.; LeBeau, J.M.; Jones, J.L.; Mikolajick, T.; Schroeder, U. A comprehensive study on the structural evolution of HfO<sub>2</sub> thin films doped with various dopants. *J. Mater. Chem. C* **2017**, *5*, 4677–4690. [CrossRef]

- 99. Nakajima, Y.; Kita, K.; Nishimura, T.; Nagashio, K.; Toriumi, A. Phase transformation kinetics of HfO<sub>2</sub> polymorphs in ultra-thin region. In Proceedings of the 2011 Symposium on VLSI Technology, Kyoto, Japan, 14–16 June 2011; pp. 84–85.

- 100. Mori, Y.; Nishimura, T.; Yajima, T.; Migita, S.; Toriumi, A. Impacts of doped element on ferroelectric phase stabilization in HfO<sub>2</sub> through non-equilibrium PDA. In Proceedings of the 2018 Solid State Devices and Materials (SSDM), Tokyo, Japan, 9–13 September 2018; p. PS-10-18.

- 101. Tabata, T. Nucleation and crystal growth in HfO<sub>2</sub> thin films by UV nanosecond pulsed laser annealing. *Appl. Phys. Express* **2019**, 13, 015509. [CrossRef]

- 102. Tabata, T.; Halty, S.; Rozé, F.; Huet, K.; Mazzamuto, F. Non-doped HfO<sub>2</sub> crystallization controlled by dwell time in laser annealing. *Appl. Phys. Express* **2021**, *14*, 115503. [CrossRef]

- 103. Fina, I.; Fàbrega, L.; Langenberg, E.; Martí, X.; Sánchez, F.; Varela, M.; Fontcuberta, J. Nonferroelectric contributions to the hysteresis cycles in manganite thin films: A comparative study of measurement techniques. *J. Appl. Phys.* **2011**, *109*, 074105. [CrossRef]

Electronics **2022**, 11, 2636 25 of 25

104. Xu, L.; Shibayama, S.; Izukashi, K.; Nishimura, T.; Yajima, T.; Migita, S.; Toriumi, A. General relationship for cation and anion doping effects on ferroelectric HfO<sub>2</sub> formation. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 25.2.1–25.2.4. [CrossRef]

- 105. Xu, L.; Nishimura, T.; Shibayama, S.; Yajima, T.; Migita, S.; Toriumi, A. Kinetic pathway of the ferroelectric phase formation in doped HfO<sub>2</sub> films. *J. Appl. Phys.* **2017**, 122, 124104. [CrossRef]

- 106. Sundaram, S.K.; Mazur, E. Inducing and probing non-thermal transitions in semiconductors using femtosecond laser pulses. *Nat. Mater.* **2002**, *1*, 217–224. [CrossRef]