# **Reconciling fault-tolerant distributed computing and systems-on-chip**

Matthias Függer · Ulrich Schmid

Received: 17 August 2010 / Accepted: 10 November 2011 / Published online: 11 December 2011 © The Author(s) 2011. This article is published with open access at Springerlink.com

Abstract Classic distributed computing abstractions do not match well the reality of digital logic gates, which are the elementary building blocks of Systems-on-Chip (SoCs) and other Very Large Scale Integrated (VLSI) circuits: Massively concurrent, continuous computations undermine the concept of sequential processes executing sequences of atomic zerotime computing steps, and very limited computational resources at gate-level make even simple operations prohibitively costly. In this paper, we introduce a modeling and analysis framework based on continuous computations and zerobit message channels, and employ this framework for the correctness & performance analysis of a distributed faulttolerant clocking approach for Systems-on-Chip (SoCs). Starting out from a "classic" distributed Byzantine fault-tolerant tick generation algorithm, we show how to adapt it for direct implementation in clockless digital logic, and rigorously prove its correctness and derive analytic expressions for worst case performance metrics like synchronization precision and clock frequency. Rather than on absolute delay values, both the algorithm's correctness and the achievable synchronization precision depend solely on the ratio of certain path delays. Since these ratios can be mapped directly to placement & routing constraints, there is typically no need

This work originates in our DARTS project, which has been a joint effort of Vienna University of Technology and RUAG Space, see http://ti.tuwien.ac.at/darts for details. It has been supported by the Austrian bm:vit FIT-IT project *DARTS* (809456-SCK/SAI) and the Austrian FWF projects Theta (P17757), PSRTS (P20529) and FATAL (P21694).

M. Függer (⊠) · U. Schmid

Technische Universität Wien, Embedded Computing Systems Group (E182/2), Treitlstraße 3, 1040 Vienna, Austria e-mail: fuegger@ecs.tuwien.ac.at

U. Schmid e-mail: s@ecs.tuwien.ac.at for changing the algorithm when migrating to a faster implementation technology and/or when using a slightly different layout in an SoC.

**Keywords** Clock synchronization · Fault-tolerant distributed systems · Modeling approaches · VLSI

# **1** Introduction

Shrinking feature sizes and increasing clock speeds are the most visible signs of the tremendous advances in VLSI design, which will accommodate billions of transistors on a single chip in the near future [34]. This comes at the price of increased system-level complexity, however: With today's deep submicron technology with GHz clock speeds, wiring delays dominate transistor switching delays, and electrical signals cannot traverse the whole chip within a single clock cycle any more. Consequently modern VLSI chips can no longer be viewed as monolithic blocks of synchronous hardware, where all the chip's state-holding gates simultaneously perform state transitions: The engineering of the clock tree, which disseminates the high-speed clock-typically generated by a quartz oscillator in conjunction with a clock multiplier-throughout the whole chip with zero skew is becoming more and more difficult [6,22,52,64] and ineffective. Large VLSI chips are hence nowadays increasingly being considered as more or less loosely-coupled systems of interacting subsystems—the advent of Systems-on-Chip (SoC) and Networks-on-Chip (NoC).

Moreover, the smaller feature sizes and the reduced voltage swing needed for high clock speeds and low power consumption dramatically increase the adverse effects of upsets due to  $\alpha$ -particle or neutron hits [4,15,29,36,57,73], crosstalk and ground bouncing [50]. The resulting increase of the transient failure rate (soft-error rate) [46] and crosstalk sensitivity [59] has hence raised concerns about the dependability of future generation VLSI chips [11]. Mitigation techniques exist at different levels of abstraction, including replication of a chip's functional units at system-level. Since in synchronous hardware designs the oscillator and its clock tree make up a non-negligible single point-of-failure [70], consequent fault-tolerant designs, too, comprise SoCs and NoCs of interacting functional units that independently perform state-transitions.

Modern SoCs have hence much in common with looselycoupled distributed systems that have been studied by the fault-tolerant distributed algorithms community for decades. Recent work e.g. on scheduling of memory requests [54], transactional memory in multicores [19], and self-stabilizing microprocessors [13], as well as our own work introduced below, confirms that it is indeed possible to utilize distributed algorithms research in the VLSI context. Conversely, results and methods from VLSI-related research, as error-correcting codes, have proved useful e.g. for tolerating Byzantine adversaries [14], and blend nicely with distributed algorithms research on fault-tolerant consensus [23], for example. Attempts to systematically bridge the gap between distributed algorithms and VLSI design are lacking, however, [9,67]; our paper makes a first step in this direction.

This work originates in our DARTS project, which is devoted to fault-tolerant clock generation in SoCs: As the zero-skew clock requirement had to be dropped in modern VLSI circuits anyway, replacing the classic centralized clock generation approach (an obvious single-point-of-failure) by a distributed solution becomes a feasible option. Like standard GALS (globally asynchronous, locally synchronous) architectures [8], DARTS replaces the traditional common clock source by multiple clock sources. In sharp contrast to GALS, however, which employs multiple unsynchronized clock devices (typically quartz oscillators), DARTS utilizes a Byzantine fault-tolerant distributed tick generation algorithm, which guarantee some bounded clock skew also between the different clock sources and their clock domains. Such multi-synchronous [72,78] GALS systems are beneficial from a designers point of view, since they combine the convenient local synchrony with a global time base across the whole chip. It has been shown in [61] that these properties facilitate even metastability-free high-speed communication across clock domains via bounded-size buffers.

The DARTS clocking scheme has been implemented both in an FPGA [20] and in a custom radiation-hardened ASIC [24,27], which proves that the approach is feasible in practice and indeed works very well. Although the implementation complexity of DARTS is definitely not negligible, it must be considered as the price for a fault-tolerant clocking system. Moreover, it is not clear how an improved and fully engineered version of DARTS, which consists of standard gates and wires only, would actually compare w.r.t. area to traditional carefully balanced clock trees with their many strong clock drivers.

In our attempts to devise a rigorous correctness proof for DARTS, we realized that classic distributed computing abstractions do not match well the peculiarities of hardware implementations:

- (i) Inherent fine-grained parallelism, which is caused by a large number of digital logic gates that *concurrently* and *continuously* compute their outputs based on their inputs. This undermines the abstraction of a (typically small) collection of processors that perform atomic computing steps at discrete points in time, which is common to (almost) all existing distributed computing models.

- (ii) Very limited resources, which make even apparently simple operations like addition or comparison of *k*-bit numbers, as well as sending such numbers via messages, prohibitively costly. This is in conflict with the basic atomic operations that are typically used in existing distributed algorithms.

**Contributions:** This paper introduces a novel framework for modeling and analysis of distributed algorithms implemented in VLSI, which explicitly addresses the above issues. Using this framework, we present a complete and rigorous correctness proof and worst case performance analysis of DARTS. The detailed contributions of our paper are the following:

- (1) We introduce a novel modeling and analysis framework based on *signals*, which allow modeling of continuous computations and binary message channels with delay. The framework facilitates "switching" between different—but consistent—abstractions of the same signal (e.g., state view). In sharp contrast to existing modeling frameworks capable of expressing timed executions,<sup>1</sup> these features allow to express the properties—and reason about correctness and performance—of faulttolerant distributed algorithms designed for a direct implementation in digital logic in a very natural and simple way.

- (2) We adapt the simple Byzantine fault-tolerant distributed tick generation algorithm introduced in [82] for a direct implementation in clockless digital logic. Major modifications concern the enforcement of certain atomic actions ("interlocking") via implicit handshaking between parts of the algorithm, and by replacing the *k*-bit messages used for communication in the original

<sup>&</sup>lt;sup>1</sup> Our framework is substantially different from existing modeling frameworks for clockless VLSI circuits ("trace theory"), which are time-free and hence cannot deal with failures [21].

algorithm by zero-bit messages, i.e., by up/down signal transitions.

(3) We prove that the adapted algorithm is correct, and derive worst case bounds for its performance metrics like synchronization precision and minimum/maximum clock frequency. Since our system-level proof rests on fundamental properties of certain elementary building blocks only, it effectively reduces the complex problem of guaranteeing system correctness to the problem of guaranteeing the correctness of fairly simple basic blocks. Consequently, in sharp contrast to classic distributed algorithms and their correctness proofs, our low-level modeling approach leaves only a small "proof gap" with respect to the actual implementation.

The paper is organized as follows: Following an overview of related work in Sect. 2, we informally explain the original tick generation algorithm and the required modifications in Sect. 3. Section 4 introduces our modeling framework and provides the system and failure model used in the subsequent analysis, as well as the detailed specification of our hardware tick generation algorithm and its (elementary) building blocks. Section 5 provides the detailed correctness proof and the worst case performance analysis. Some conclusions and directions of further research in Sect. 6 complete the paper. A glossary of our notation can be found in (Table 1).

## 2 Related work

**VLSI clock generation:** There exists a huge body of work on classic fault-tolerant clock synchronization [63, 74], including hardware-assisted clock synchronization [68], where a set of free-running physical clocks are to be synchronized. In contrast to these approaches, DARTS does *not* compute adjustment values for synchronizing free-running (e.g., driven by a quartz oscillator) local hardware clocks, but generates clock ticks that are inherently synchronized (by means of a distributed algorithm) in a closed-loop fashion. Note that there is research on "extracting" clock synchronization from the actual communication in a distributed computation [1,31,58,60] that bears some relation to our approach.

The few approaches for distributed clock generation without local clock sources we are aware of are essentially based on a (distributed) ring oscillator, which is formed by gates arranged in a feedback loop. Instead of being dictated by a quartz, the frequency of the generated clock signal is determined by the end-to-end delay of the feedback loop. In [51], a regular structure of closed loops of an odd number of inverters is used for distributed clock generation. Similarly, [17,18] employs local tick generation cells, arranged in a two-dimensional grid, with each cell inverting its output signal when its four inputs (from the up, down, left and right neighbor) match the current clock output value. Since clock synchronization theory [12] reveals that high connectivity is required for bounded synchronization tightness in the presence of failures, however, the sparsely connected designs proposed in [17,18,51] are not fault-tolerant.

**Modeling approaches:** The theory of asynchronous (clockless) distributed systems—in the absence of failures—has been used in the VLSI community for decades [10]: Research on transition signaling [7,71], delay-insensitivity [16,49], micropipelines [77], etc. has established a sound basis for dealing with self-timed systems [32]. Since then, much research has been conducted on benefits and limitations of clockless circuits. There is a wealth of literature on the arbiter problem [41,47], which is—like the latch, the inertial delay and the mutex—impossible to solve in a delay-insensitive way [3,49]. Both arbiter-free problems [43] and a few ways to circumvent the impossibility of implementing arbiters by adding (some) timing properties [48] or order properties [76] have been thoroughly investigated.

Existing modeling approaches for clockless circuits are based on algebraic trace theory [16,49] or Petri-nets [43,83]; such specifications are time-free. Time-augmented clockless circuits can be handled by using timed Petri-nets, which assign time intervals to each transition [5,55,65,84]. However, to the best of our knowledge, none of these modeling frameworks deals with failures. On the other hand, modeling frameworks developed in distributed algorithms research, like timed I/O automatons [37] or TLA [42], can deal with failures, but are not tailored to the specific needs of VLSI circuits.

**Fault-tolerance in VLSI:** Dependability concerns have also stimulated a large body of research work devoted to fault-tolerance and fault-prevention in VLSI systems [40]. Fine-grained fault tolerance, e.g. at transistor and gate level, encoding, error detection & recovery/reconfiguration, and radiation hardening techniques are the methods of choice here, see e.g. [35,53,56,79,80] for some examples. The proposed techniques are very different from the "systemlevel approach" employed in fault-tolerant distributed algorithms, which we will exploit in this paper. We note, however, that those approaches are complementary, in the sense that VLSI fault-tolerance techniques can reduce component failure rates and, hence, the required system-level redundancy.

Although we are not aware of any work that deals with the fine-grain parallelism inherent in VLSI implementations, there is a sizeable body of work devoted to hardware implementations of fault-tolerant algorithms. Well-known examples are MAFT [38], SAFEBUS [33], GUARDS [62] and TTP [39]. However, in sharp contrast to our problem, these systems incorporate hardware *assistance* only. The major part of the algorithms is still implemented in conventional software and executed on general-purpose processors. As a consequence, minimizing the gate-level resource Table 1Glossary of ourNotation

| Name                                                                                         | Description                                           | Definition |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------|------------|

| В                                                                                            | Maximum node booting completion times                 | Sect. 4.2  |

| $\#b_p(t)$                                                                                   | # Ticks generated by node $p$                         | Sect. 4.2  |

| $b^{max}(t)$                                                                                 | # Ticks generated by first correct node               | Sect. 5.2  |

| $b^{min}(t)$                                                                                 | # Ticks generated by last correct node                | Sect. 5.2  |

| С                                                                                            | Set of correct nodes in the system                    | Sect. 4.2  |

| $#d_{p,q}(t)$                                                                                | #Ticks commonly removed from $(p, q)$                 | Sect. 4.2  |

| $\delta(X;t)$                                                                                | Value of channel $X$ 's delivery function at time $t$ | Sect. 4.1  |

| F                                                                                            | Set of faulty nodes in the system                     | Sect. 4.2  |

| f                                                                                            | Maximum number of faulty nodes                        | Sect. 4.2  |

| FCR                                                                                          | Fault-containment region                              | Sect. 4.2  |

| n                                                                                            | Total number of nodes in the system                   | Sect. 4.2  |

| Р                                                                                            | Set of all <i>n</i> nodes in the system               | Sect. 4.2  |

| (p,q)                                                                                        | Pipepair for remote $q$ at local node $p$             | Sect. 4.2  |

| $\widetilde{\mathcal{P}}^{GEQ,o/e}_{p,q}(t)$                                                 | Status $(p, q)$ : # ticks remote $\geq$ local         | Sect. 4.2  |

| $\widetilde{\mathcal{P}}_{p,q}^{GR,o/e}(t)$                                                  | Status $(p, q)$ : # ticks remote > local              | Sect. 4.2  |

| π                                                                                            | Precision bound                                       | Sect. 4.4  |

| $\#r_{p,q}^{loc}(t)$                                                                         | #Ticks stored in local pipe of $(p, q)$               | Sect. 4.2  |

| $\#r_{p,a}^{rem}(t)$                                                                         | #Ticks stored in remote pipe of $(p, q)$              | Sect. 4.2  |

| $ \begin{aligned} &\#r_{p,q}^{loc}(t) \\ &\#r_{p,q}^{rem}(t) \\ &\widehat{S} \end{aligned} $ | Event trace representation of signal S                | Sect. 4.1  |

| $\widetilde{S}(t)$                                                                           | Status representation of signal S                     | Sect. 4.1  |

| #S(t)                                                                                        | Counting function representation of signal S          | Sect. 4.1  |

| Sloc                                                                                         | Maximum size local pipes                              | Sect. 4.2  |

| Srem                                                                                         | Maximum size remote pipes                             | Sect. 4.2  |

| $\#s_{p,q}^{loc}(t)$                                                                         | Current size local pipe of $(p, q)$                   | Sect. 4.2  |

| $\#s_{p,q}^{rem}(t)$                                                                         | Current size remote pipe of $(p, q)$                  | Sect. 4.2  |

| $T_{BS}(k)$                                                                                  | Booting-induced tick $k$ generation time              | Eq. 42     |

| $T_{first}^{-}$                                                                              | Minimum tick generation interval                      | Eq. 39     |

| $T_{max}$                                                                                    | Maximum local loop delay                              | Constr. 1  |

| T <sub>min</sub>                                                                             | Minimum local loop delay                              | Constr. 1  |

| T <sub>min,dis</sub>                                                                         | Stripped minimum local loop delay                     | Constr. 1  |

| $T_P$                                                                                        | Maximum tick generation interval                      | Eq. 40     |

| $T_{QS}$                                                                                     | Maximum tick catchup time                             | Eq. 41     |

| $T_{del}$                                                                                    | Maximum time until removal of tick                    | Eq. 70     |

| $T_{del}^{loc}$                                                                              | Maximum time until removal of tick, 2nd bound         | Eq. 75     |

| t <sub>first,k</sub>                                                                         | Time when first correct node sends tick $k$           | Sect. 4.2  |

| t <sub>last,k</sub>                                                                          | Time when last correct node sends tick $k$            | Sect. 4.2  |

| t <sub>b</sub>                                                                               | Time when first correct node completes booting        | Lem. 9     |

| $t_{p,b}$                                                                                    | Time when node $p$ completes booting                  | Sect. 4.2  |

| $t_{rmv,k}$                                                                                  | Time of removal of tick k from $(p, q)$               | Sect. 4.2  |

| $\left[ \tau_{GEQ}^{-}, \tau_{GEQ}^{+} \right]$                                              | Min./max. delay GEQ rule                              | Sect. 4.2  |

| $\begin{bmatrix} \tau_{GR}^-, \tau_{GR}^+ \end{bmatrix}$                                     | Min./max. delay GR rule                               | Sect. 4.2  |

| $\left[\tau_{loc}^{-}, \tau_{loc}^{+}\right]$                                                | Min./max. delay local channel + pipe                  | Sect. 4.2  |

| $\left[\tau_{rem}^{-}, \tau_{rem}^{+}\right]$                                                | Min./max. delay remote channel + pipe                 | Sect. 4.2  |

| $\begin{bmatrix} \tau_{TH}^{-}, \tau_{TH}^{+} \end{bmatrix}$                                 | Min./max. delay threshold modules                     | Sect. 4.2  |

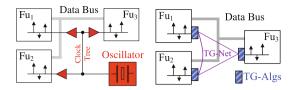

Fig. 1 Replacing synchronous clocking by fault-tolerant distributed tick generation

consumption implied by these algorithms has never been considered. A notable exception is [2], however, where it has been shown that consensus can be solved with 1-bit messages.

# **3 DARTS informal overview**

As shown in Fig. 1, the basic idea of DARTS is to replace the common quartz oscillator and the clock tree by a fully distributed GALS-like approach [8]: Every functional unit Fu<sub>i</sub> has attached a dedicated fault-tolerant tick generation block (TG-Alg) here, which generates Fu<sub>i</sub>'s local clock signal. To accomplish this, all TG-Alg blocks communicate with each other over a simple "network" of clock signals (TG-Net). In contrast to standard GALS, however, DARTS ensures that the local clock signals of different Fu's are synchronized to each other to within a few clock cycles (termed multi-synchronous clocking [72,78]). It has been proved elsewhere [62] that even such loose synchrony suffices for implementing metastability-free high-speed communication between different Fu's using bounded-size buffers.

DARTS clocks (patented in [69]) provide a number of additional advantages, which makes them particularly promising for critical applications in the aerospace domain: First of all, the approach entirely circumvents quartz oscillators, which are fairly big and sensitive devices (shock, vibration, temperature etc.), as well as the cumbersome clock tree engineering issue [6,22,52,64]. It is fault-tolerant, in the sense that the correctness of the clock signals supplied by correct TG-Algs is not affected by transient and permanent failures occurring in other TG-Algs and/or in the TG-Net. DARTS clocks can also be guaranteed to indeed start operating at booting time, a feature that is difficult to ensure for oscillatorbased clocking approaches in space applications. Moreover, the clocks always run at the maximum speed and adapt to the current communication delays within the TG-Algs and the TG-Net, both of which may vary with the current operating conditions, such as supply voltage and temperature. And last but not least, since different Fus are driven by slightly different clock signals, DARTS clocks alleviate EM radiation and ground bouncing problems [50] that typically plague devices using synchronous clocking.

The TG-Algs developed and analyzed in this paper derive from a simple synchronizer algorithm for the  $\Theta$ -Model  /\* Initialization \*/

VAR k : integer := 0;

initially send tick(0) to all;

if received tick(ℓ) from at least f + 1 distinct nodes with ℓ > k then

send tick(k + 1), ..., tick(ℓ) to all; k := ℓ;

if received tick(k) from at least 2f + 1 distinct nodes then

send tick(k + 1) to all; k := k + 1;

Fig. 2 Algorithm for generating approximately simultaneous tick(k) messages

[44,81,82] introduced in [82]. The (core of this) algorithm, which is based on Srikanth and Toueg's consistent broadcasting primitive [75], is shown in Fig. 2. It assumes a message-driven system (where nodes make atomic receivecompute-send steps whenever they receive a message) of n = 3f + 1 nodes (= TG-Alg instances), at most f of which may behave arbitrarily faulty, i.e., Byzantine. The number of nodes n is equal to the number of Fus the SoC is partitioned into, and also depends on the intended number of faults f the SoC should sustain. Typical DARTS systems will probably have some f in the order of 1 to 4, resulting in some *n* in the range of 4 to 13 TG-Algs. All correct nodes are connected by a reliable<sup>2</sup> point-to-point message-passing network (= TG-Net): No spurious messages are ever generated, no messages are lost or altered, and all messages sent at time t are eventually received within the interval  $t + [\tau^-, \tau^+]$ , where  $\tau^-$  respectively  $\tau^+$  denote the (possibly unknown) lower respectively upper bound on the end-to-end delay of messages exchanged between correct nodes. Let  $\varepsilon = \tau^+ - \tau^-$  be the maximum uncertainty of the message delay, and  $\Theta = \tau^+ / \tau^-$  the maximum delay ratio.

The idea of the algorithm is the following: Initially, every node broadcasts tick(0) in line 3. If a correct node preceives f + 1 tick( $\ell$ ) messages (line 5), it can be sure that at least one of those was broadcast by a correct node. Therefore, p can safely catch up and send tick(k + 1), ..., tick( $\ell$ ). If some node p receives 2f + 1 tick(k) messages (line 7) and thus sends tick(k + 1), one can be sure that all tick(k) messages broadcast by correct nodes, i.e., at least f + 1, will be received within time  $\varepsilon$  by every other correct node. Hence, every correct node will execute line 5 and send tick(k), if it has not already done so.

In conjunction with the fact that the fastest correct node cannot send consecutive tick(k), tick(k + 1),...arbitrarily fast, this implies a bound on the synchronization precision: Our detailed analysis will reveal that correct nodes generate a sequence of consecutive messages tick(k),  $k \ge 1$ , in

<sup>&</sup>lt;sup>2</sup> Note that this reliable network assumption is not unduly restrictive, since communication failures can be mapped to failures of the sending node.

a synchronized way (see Sect. 4.4): If  $\#b_p(t)$  denotes the number of tick(k) messages broadcast by node p by realtime t (which is identical to the value of variable k at realtime t, cf. Fig. 2), it will turn out that  $(t_2 - t_1)\alpha_{\min} \le$  $\#b_p(t_2) - \#b_p(t_1) \le (t_2 - t_1)\alpha_{\max}$  for any correct node p and  $t_2 - t_1$  sufficiently large ("accuracy"); the constants  $\alpha_{\min}$ and  $\alpha_{\max}$  depend on  $\tau^-, \tau^+$ . Moreover, every two correct nodes p, q maintain  $|\#b_p(t) - \#b_q(t)| \le \pi$  ("precision"), for all  $t \ge 0$  with a small constant  $\pi$  that depends on  $\Theta$ only. Note carefully that the algorithm automatically adapts to the instantaneous timing characteristics of any involved computation and communication.

Since the algorithm in Fig. 2 looks very simple, it is tempting to conclude that it is easily translated into a hardware description language: Node p's TG-Alg just needs to drive a Boolean-valued clock signal, where it outputs the k-th signal transition when the algorithm sends its tick(k) message; the TG-Net is formed by feeding all clock signals to all TG-Algs. It turns out, however, that a number of challenging issues must be solved to actually accomplish this:

- How to implement the TG-Net efficiently? The algorithm assumes a fully connected network, consisting of  $n^2$  links,<sup>3</sup> so anything beyond a single wire per link is unacceptable [26]. Moreover, for implementation simplicity and performance, the information transmitted via the TG-Net must be kept to a minimum. Ideally, and almost mandatory, the TG-Net should just feed the emitted clock ticks, i.e., signal transitions, of every TG-Alg node to every other TG-Alg node.

- *How to adapt the original algorithm for zero-bit messages*? By just sending signal transitions, no information except the occurrence time can be conveyed over the TG-Net. Thus, the tick number *k* contained in the messages of Fig. 2 must be maintained at every receiver, individually for every sender.

- *How to map hardware faults to node failures?* Given that the algorithm shown in Fig. 2 tolerates Byzantine failures, we are on the safe side here. Interestingly, there is evidence [30] that assuming less severe failures is inappropriate in the presence of real hardware faults: Even simple stuck-at faults could produce early and/or inconsistently perceived signal transition, and cannot hence be modeled as a crash or omission node failure. More severe hardware faults, like delay faults or early/spurious clock transitions induced e.g. by particle hits or crosstalk, can also easily lead to Byzantine failures.

- *How to ensure atomicity of actions in a VLSI implementation?* This turned out to be the most demanding challenge: All fault-tolerant distributed computing models assume

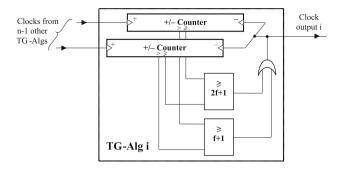

Fig. 3 Basic architecture of a TG-Alg

atomic computing steps at the level of a single node. For example, the algorithm presented in Fig. 2 assumes that: (i) messages are received, (ii) the number of received messages is checked with respect to a threshold, and (iii) possibly a new message is broadcast and variable k is updated; all this happens in one atomic computing step. This abstraction does not apply when the algorithm is implemented via clockless digital logic gates, which concurrently and continuously compute their outputs based on their inputs. Explicit synchronization (serialization of actions/interlocking) must be introduced if two local computations must not interfere with each other.

# 3.1 Informal overview of the TG-Alg design problems

Taking into account the above issues, we arrived at the basic architecture of a single TG-Alg shown in Fig. 3.

The major building blocks of a single TG-Alg are the (n-1) + / - counters, one for each of the n-1 other TG-Algs in the system. Each such device counts the difference of (i) the number of clock ticks seen from the respective peer, and (ii) the number of clock ticks generated locally so far. Counting the difference between these two numbers is sufficient to implement the algorithm of Fig. 2: To decide when to broadcast the next message, the algorithm needs to know when there are enough remote messages  $tick(\ell)$  for which  $\ell > k$  or  $\ell \ge k$ . Since  $\ell > k \Leftrightarrow \ell - k > 0$  and  $\ell \ge k \Leftrightarrow \ell - k \ge 0$ , it suffices to know when the difference  $\ell - k$  is > 0 or  $\geq 0$ . Thus, the +/- counters are supposed to provide two binary status functions,  $\overline{GR}$  and GEQ, which are true when the counter's actual value is > 0 and  $\ge 0$ , respectively. In addition,  $a \ge f + 1$  and  $a \ge 2f + 1$  threshold circuit is required for implementing the rules in (line 5) and (line 7) in Fig. 2, respectively. Finally, there is a device (shown as an OR-gate in Fig. 3), which is responsible for generating every local clock tick exactly once when the  $\geq f + 1$ or the > 2f + 1 threshold circuit triggers the generation of a new tick message.

Again, the above architecture is deceptively simple. The major problem encountered when trying to implement Fig. 3 in hardware is the lack of a common clock signal that could

<sup>&</sup>lt;sup>3</sup> Note that a bus of n broadcast links that provide every TG-Alg with the messages from all other TG-Algs is in fact sufficient here.

be used for a synchronous design. Obviously, such a clock signal is not available here. Hence, one has to resort to a (quasi) delay insensitive clockless implementation [32] of the algorithm depicted in Fig. 3, which raises a number of intricate problems:

**How to reconcile transition signaling and fault-tolerance?** The probably most elegant paradigm for clockless logic is *transition signaling*, where information is conveyed exclusively via signal transitions, rather than via signal states as in conventional logic. Any reasonable delay-insensitive clockless circuit can be composed from a small set of elementary building blocks here, which includes the Muller C-Element that forms the equivalent of the logical AND of two input signals, see [7,48,77] for details.

The "expressive" power of transition signaling is restricted to time-free systems, however, where causality is the only meaningful relation between events. Consequently, there is no full equivalent to the conventional logical OR of two input signals: If only one of the two inputs can provide a transition, the EXOR (exclusive OR) gate can safely be used for this purpose. However, there is no meaningful transition signaling OR if both inputs could—but need not—provide a (somehow related) transition. In fact, generating an OR output transition when the first input transition arrives would destroy the causality relation of the second input transition and the generated output transition.

Unfortunately, incorporating fault-tolerance, as instantiated by our threshold gates, requires exactly this semantics: The clock signal generated by some TG-Alg must not depend causally on the clocks generated by faulty TG-Algs, since this may lead to blocking. Hence, there is no way but to "switch" from transition signaling to state signaling and vice versa to circumvent this problem.

How to manage a clean switch between transition signaling and state signaling? In our implementation of Fig. 3, transition signaling logic is used for processing clock ticks (+/- counters). The +/- counters, on the other hand, output signals with status  $\widehat{GR}$  and  $\widehat{GEQ}$ . These signals are then processed by the threshold circuits, which themselves output signals with status  $\widehat{THGR}$  (respectively  $\widehat{THGEQ}$ ), signalling whether the  $\widehat{GR}$  signals have reached the f + 1 threshold or not (respectively whether the  $\widehat{GEQ}$  signals have reached the 2f + 1 threshold or not). This information is finally fed into a circuit (depicted by the OR-gate in Fig. 3) responsible for generating exactly one state transition tick k for any k, which is again implemented in transition logic.

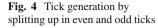

The intermediate switching to status signalling performed by the +/- counters, however, bears a problem: it is not feasible to decrement all +/- counters at the same time, since it is inevitable that a local tick(*k*) message is received at slightly different times by a node's +/- counters. This results in the fact that some of the +/- counters produce a status of  $\widetilde{GR}$  and GEQ based on local tick(k) and others based on the old local tick(k - 1), at least until they finally receive local tick(k). This problem is solved as follows: We will see during the paper that by proper constraints it can be enforced that no three +/- counters set their ports' status based on local ticks k, k - 1 and k - 2 or even less at the same time. Thus it suffices to distinguish whether  $\widetilde{GR}$  and  $\widetilde{GEQ}$  is based on k or on k - 1, which is done by simply duplicating both signals  $\widetilde{GR}$  and  $\widetilde{GEQ}$ , one for status that is based on even local ticks and one for odd local ticks.

More specifically, since transitions of binary-valued clock signals must strictly alternate between low-to-high (= odd clock tick) and high-to-low (= even clock tick), it is obvious that the next tick to be generated after an even tick must be odd, and vice versa. Hence, in our solution, we just (i) duplicate the signals  $\widetilde{GEQ}$ ,  $\widetilde{GR}$ , obtaining the signals  $\widetilde{GEQ}^e$ ,  $\widetilde{GR}^e$ ,  $\widetilde{GEQ}^o$  and  $\widetilde{GR}^o$ , (ii) duplicate the two threshold circuits, (iii) duplicate the signals  $TH\widetilde{GEQ}^e$  and  $TH\widetilde{GR}^e$ , obtaining the four signals  $TH\widetilde{GEQ}^e$ ,  $TH\widetilde{GR}^e$ ,  $TH\widetilde{GEQ}^o$  and  $\widetilde{THGR}^o$ , generated by one of the threshold circuits each, and (iv) use the rules:

- Generate an even tick  $k + 1 \in \mathbb{N}_{even} := 2\mathbb{N}$  if the last tick generated was odd ( $k \in \mathbb{N}_{odd} := 2\mathbb{N} + 1$ ) and either (a) the same or a greater number of ticks have been seen from  $\geq 2f + 1$  TG-Algs ( $\widetilde{GEQ}^o$  true), thereby enabling  $T\widetilde{HGEQ}^o$ , or (b) a greater number of ticks have been seen from  $\geq f + 1$  TG-Algs ( $\widetilde{GR}^o$  true), thereby enabling  $\widetilde{THGR}^o$ . Note that condition (a) ensures that the odd tick k has been seen from  $\geq 2f + 1$  remote TG-Algs, whereas (b) guarantees that the even tick k + 1 has already been seen from  $\geq f + 1$  ones.

- Generate an odd tick  $k + 1 \in \mathbb{N}_{odd}$  if the last tick generated was even  $(k \in \mathbb{N}_{even})$  and either (a) the same or a greater number of ticks have been seen from  $\geq 2f + 1$  TG-Algs  $(\widetilde{GEQ}^e$  true), thereby enabling  $T\widetilde{HGEQ}^e$ , or (b) a greater number of ticks have been seen from  $\geq f + 1$  TG-Algs  $(\widetilde{GR}^e$  true), thereby enabling  $T\widetilde{HGEQ}^e$ . Again, condition (a) ensures that the even tick k has been seen from  $\geq 2f + 1$  remote TG-Algs, whereas (b) guarantees that the odd tick k + 1 has already been seen from  $\geq f + 1$  ones.

Glitches<sup>4</sup>, due to the non-simultaneous arrival of clock signal transitions from the peers, are masked by simply ignoring the output of the threshold circuits (say,  $THGR^{\circ}$  and  $THGEQ^{\circ}$ ) that generated the even tick k when the next tick

<sup>&</sup>lt;sup>4</sup> A glitch is a wrong state transition.

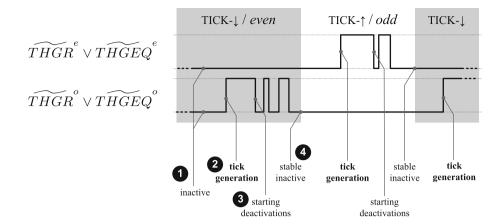

k + 1 to be generated is odd<sup>5</sup>. This "gap" thus allows  $\widetilde{GR}^{o}$ and  $\widetilde{GEQ}^{o}$  (which were responsible for activating  $\widetilde{THGR}^{o}$ or  $\widetilde{THGEQ}^{o}$ ) for tick *k* to first become inactive and then become active again for tick k + 2. As will be revealed by Lemma 3, this is sufficient to avoid mixing up old and new instances of  $\widetilde{GR}^{o}$  (respectively  $\widetilde{GEQ}^{o}$ ).

As an example consider Fig. 4. It depicts a trace of signal  $\widetilde{THGR}^e \lor \widetilde{THGEQ}^e$ , responsible for generating odd ticks, as well as signal  $\widetilde{THGR}^o \lor T\widetilde{HGEQ}^o$ , responsible for generating even ticks: (1) at the beginning of a new even tick generation, both signals are inactive. (2)  $THGR^{\circ}$  or  $THGEQ^{\circ}$ becomes active due to the arrival of sufficiently many remote ticks, thereby enabling the signal  $\widetilde{THGR}^{o} \lor T\widetilde{HGEO}^{o}$  that generates an even tick k. (3) The first local tick k arrive at p's +/- counters, which thus disable their  $\widetilde{GEQ}^{o}$  and  $\widetilde{GR}^{o}$  signals, and hence finally  $\widetilde{THGR}^o$  and  $\widetilde{THGEQ}^o$ . Note that  $\widetilde{THGR}^{o} \vee \widetilde{THGEQ}^{o}$  may intermittently become enabled again, due to the arrival of remote ticks from other TG-Algs. (4) After some time, all of p's +/- counters have received the local tick k and  $\widetilde{THGR}^o \lor T\widetilde{HGEQ}^o$  has stabilized being inactive. Now the next odd tick k + 1 is generated as soon as  $\widetilde{THGR}^e \vee T\widetilde{HGEQ}^e$  becomes active.

How to implement the +/- counters? This task turned out to be the most delicate part of the hardware design work. Actually, implementing a clockless up/down counter is inherently difficult due to the fact that the up-clock ("+ port") and the down-clock ("- port") transitions are totally unrelated. They can hence occur arbitrarily close in time to each other, which usually causes metastability problems [77]. Another problem is how to correctly generate the status of  $\widehat{GR}^{o}$  and  $\widehat{GEQ}^{o}$  (respectively  $\widehat{GR}^{e}$  and  $\widehat{GEQ}^{e}$ ). They should truly reflect the current counter value, at least during times when they are used. We will specify the detailed properties that must be maintained by these signals in Sect. 4. Note that our correctness proof and performance analysis will only rely on these properties, i.e., is valid for every implementation of the +/- counters that fulfills these properties.

Our particular implementation of the +/- counters consists of two elastic pipelines [77], which can be seen as shift registers/FIFO buffer for signal transitions. One of the elastic pipelines is attached to the remote clock signal ("+ port"), the other one is fed by the local clock signal ("- port"). They are fitted together at their ends via a special *Diff-Gate*, which removes "matching" transitions, that is, transitions representing the same tick number, as soon as they traveled through the pipelines. The signals with status  $\widehat{GR}^o$ ,  $\widehat{GEQ}^o$ ,  $\widehat{GR}^e$  and  $\widehat{GEQ}^e$  are derived from monitoring the last few stages of both pipes. Further details are provided in Sect. 4 and in the descriptions of our implementations [20,24,27].

# 4 Modeling and analysis framework

In this section, we introduce a modeling framework for fault-tolerant distributed algorithms that are implemented by means of clockless digital circuits, which is amenable to mathematical correctness proofs and worst-case performance analysis. The presented framework addresses the multitude of issues raised in the previous section: It is based on a continuous model of computation and time, and avoids the use of design elements and abstractions that are not available or too costly at the hardware implementation level. To handle the design complexity challenge at such low levels of abstraction, it also supports hierarchical modeling: At the top-level of DARTS, for example, there is the entire system, consisting of n TG-Algs interconnected via the clock signal wires making up the TG-Net; every TG-Alg can be further partitioned into several building-blocks (like the +/- counters), which are interconnected in some non-regular way. Before we formally state the framework, we give an informal overview of the main ingredients.

$<sup>^5\,</sup>$  Of course, no further glitches may occur as soon as this next tick has occurred.

Our modeling framework is based on *modules*, which possess input and output *ports*. An *execution* of a module's ports is an assignment of a *signal* (which captures continuous computation over time) to each of the module's ports. A module's *allowed behavior* is specified by a set of executions of the module's ports. Note that modules differ from classic distributed computing abstractions like timed automatons [45] primarily in that they *continuously* compute their outputs.

*Compound modules* consist of multiple sub-modules and their interconnect, which specifies how sub-module ports are connected to each other and to the module's input and output ports. The interconnect specification itself assumes zero delays; modeling non-zero interconnect delays, e.g., for real wires, requires intermediate channels: A *channel* is a module that possesses a single input port and a single output port, and its behavior specifies delayed FIFO delivery of input port signal transitions at the output port. Modules that are not further refined are called *basic modules*. Elementary basic modules are those that calculate zero-delay Boolean functions (AND, OR, ...) and channels.

Clearly, the behavior of a (non-faulty) compound module is determined by the behavior of its constituent sub-modules; the behavior of a basic module must be given *a priori*. Correctness proofs establish properties of the behaviors of higher-level compound modules, based on the assumption that (1) the system and failure model holds, and (2) that the implementations of (non-faulty) basic modules indeed satisfy their behavioral specification.

#### 4.1 Signals and zero-bit message channels

Since we target implementations using clockless circuits, our formal framework will be based on a continuous notion of real-time  $t \in \mathbb{R}_0^+$ . We assume that the system initialization (reset) is triggered at time t = 0; different modules may complete their reset at different times, however.

**Signal:** A signal *S* is an event trace, i.e., a set of time/value tuples. Formally,

$S \subseteq \mathbb{R}_0^+ \times \{0, 1\},$

where event  $(t, 1) \in S$  respectively  $(t, 0) \in S$  means that *S* takes on value 1 respectively 0 at time *t*. We require non-simultaneity of contradicting events on a single signal, i.e.,

$$((t, x) \in S) \land ((t, y) \in S) \Rightarrow x = y,$$

and assume that the initial event (0, I), with either I = 0 or I = 1, is always present in S. We also disallow alternating Zeno behavior in our event traces, i.e., we require that at most finitely many events with different value can occur in any finite time interval, cp. [45, p. 737f]. Note, however,

that *S* may still contain arbitrarily many idempotent events.<sup>6</sup> Consequently, if

$$pre(S, t) := \{(t', v') \in S \mid t' \le t\}$$

suff(S, t) :=  $\{(t', v') \in S \mid t' \ge t\}$

denotes the prefix and suffix of *S* at time *t*, respectively, there need not be a maximum element  $(v_{max}, t_{max})$ —with respect to the time component—in pre(S, t) and/or no minimum element  $(v_{min}, t_{min})$  in suff(S, t). However,

last-val

$$(S, t) := v'$$

such that  $\exists (t', v') \in \operatorname{pre}(S, t) :$

$\forall (t'', v'') \in \operatorname{pre}(S, t) : (t'' \ge t') \Rightarrow (v'' = v')$

is well-defined.<sup>7</sup>

Since our modeling framework is primarily devoted to "real" systems like DARTS, we will restrict our attention to systems made up of well-formed circuits only. A well-formed circuit does not contain zero-delay wires, branches with infinite fan-in/out and other non-implementable assumptions. We say a signal *S* is *well-formed* if (i) it does not show alternating Zeno behavior and (ii) the function  $t \mapsto last-val(S, t)$ is right-continuous. It can be shown that well-formed circuits never produce signals that are not well-formed, unless their input signals are not well-formed. Therefore, during this paper, we may safely assume that all signals by which the behavior of DARTS is modeled, are well-formed. Wellformed signals allow for more abstract representations than just event traces, which we will now introduce.

In fact, specifying systems in terms of event traces is sometimes overly complicated. More convenient in this regard are two higher-level representations of signals: (i) status, and (ii) counting function. All three representations will be consistent, in a well-defined way, and can hence be used interchangeably.

**Status:** The status representation of a signal *S*, denoted by  $\widetilde{S}$ , is a function

$$S: \mathbb{R}_0^+ \to \{0, 1\}$$

from real-time to its instantaneous Boolean value, defined by

$$\forall t \ge 0 : S(t) := \text{last-val}(S, t).$$

Since S is well-formed, the resulting  $\tilde{S}(t)$  is obviously rightcontinuous.

Status functions may be composed out of already defined status functions by using arbitrary Boolean predicates, e.g.,  $\widetilde{A} := \widetilde{B} \wedge \widetilde{C}$ , with status function  $\widetilde{B}$ ,  $\widetilde{C}$ , is defined as  $\widetilde{A}(t) := \widetilde{B}(t) \wedge \widetilde{C}(t)$ .

<sup>&</sup>lt;sup>6</sup> This is the reason why we use the term "event" here, rather than the more common term "transition".

<sup>&</sup>lt;sup>7</sup> If alternating Zeno traces were not forbidden, one could construct event traces *S* where last-val(*S*, *t*) is not well-defined. For instance, this happens in a Zeno-trace with alternating  $0, 1, 0, \ldots$  events approaching, but not reaching, some time *t*.

**Counting function:** Finally, a signal *S* can be represented by the number of non-idempotent events (excluding the initial event) that occur during (0, t], denoted as the signal's *counting function* #S(t). For example, if *S*'s event trace is given by  $S = \{(0, 0), (1, 1), (1.5, 1), (2, 0)\}$  and I = 0, then #S(0) = 0, #S(0.5) = 0, #S(1) = 1, #S(1.5) = 1, and #S(2) = 2. Sometimes, we will also employ generalized counting functions #S'(t) that have an initial value other than 0: We define  $\#S'(t) := \#S(t) + S_0$ , where #S is the standard counting function of *S* and  $S_0$  an arbitrary offset. It follows immediately from the properties of signals that  $t_1 \le t_2 \Rightarrow$  $\#S(t_1) \le \#S(t_2)$  for any counting function #S, and that #Sis right-continuous at any point of discontinuity since *S* is well-formed.

In the sequel, we will use the most convenient representation of a signal S interchangeably, namely S itself,  $\tilde{S}$  or #S.

**Execution:** We begin with the formal definition of a system. A system is a set  $\mathcal{P}$  of ports, whereby a *port* can be thought of as a measurement point on a digital chip. An execution (of ports  $\mathcal{P}$ ) is a function that assigns each  $p \in \mathcal{P}$  a signal  $\hat{p}$ . To avoid cluttered notation we simply write  $\tilde{p}$  respectively #p when we refer to the abstract signal representations  $\hat{p}$ respectively  $\#\hat{p}$ . To specify a system's allowed executions in a convenient way, modules are introduced: a module is a triple comprising (i) a set of input ports  $\mathcal{I}$ , (ii) a set of output ports  $\mathcal{O}$ , and (iii) a set of allowed executions  $\mathcal{E}$  of ports  $\mathcal{I} \cup \mathcal{O}$ . It is the specification of  $\mathcal{E}$ , where the convenience of a threefold representation of signals comes into play, and it will be extensively used in Sect. 4.3. For example, to specify a module with no input port and a single output port o that produces a constant-0 signal at o, we simply require that  $\mathcal{E}$  comprises all executions of ports  $\{o\}$  that fulfill  $\tilde{o} = 0$ .

The system's allowed executions can thus be specified by stating a set of ports  $\mathcal{P}$  together with a set of modules that have input/output ports in  $\mathcal{P}$ .

Channel: A channel models a reliable FIFO channel for signal transitions with finite delay. Since signal transitions must be alternating, only the occurrence time but no data can be conveyed over a single channel ("zero-bit messages"). Formally, the semantics of a channel X is as follows: Let  $X^s$  be the channel's single input port [which will be connected to an output port of a single sender module], and  $X^r$  be its single output port [which will be connected to the input ports of some receiver module(s)]. Intuitively a channel maps events at the input port occurring at some time t to (delayed) events at the output port occurring at some delivery time t', where the delay t' - t is not necessarily the same for each event, if the channel has non-constant delay. Formally, we demand that there exists a continuous and strongly monotonically increasing delivery function  $\delta : \mathbb{R}_0^+ \to \mathbb{R}_0^+$  for X, which maps sending time t to delivery time  $\delta(t)$ . Note that we will use  $\delta(X; t)$  to refer to  $\delta(t)$  when the corresponding channel

*X* is not clear from the context. We assume that the channel delay is within  $[\tau_X^-, \tau_X^+]$ , i.e., for all times *t* in  $\mathbb{R}_0^+$ ,

$$\delta(t) - t \in \left[\tau_X^-, \tau_X^+\right]. \tag{1}$$

From the properties of  $\delta$ , it follows immediately that  $\delta$  is a bijection from  $\mathbb{R}_0^+$  to its codomain  $\delta(\mathbb{R}_0^+)$ . More specifically,  $\delta$  maps every closed interval  $[t_1, t_2]$  bijectively to the closed interval  $[\delta(t_1), \delta(t_2)]$ . Clearly, the inverse function  $\delta^{-1}$  of  $\delta$  also exists and has the same properties. In addition, we will assume that the channel output has some well-defined initial state (is initialized to)  $I \in \{0, 1\}$ , which is I = 0 if not specified otherwise.

Given  $\delta$ , the channel's behavior in terms of event traces is specified by two properties, namely

$$(0, I) \in \widehat{X}^r \land \nexists(t, v) \in \widehat{X}^r \text{ with } v \in \{0, 1\}, t \in [0, \delta(0))$$

which ensures that before the first event is delivered from the input port to the output port, i.e., before  $\delta(0)$ , only one event occurs at the output port: the event which sets the channel output port to its initial value *I*. Secondly we demand that

$$(\delta(t), x) \in \widehat{X}^r \Leftrightarrow (t, x) \in \widehat{X}^s.$$

<sup>(2)</sup>

Since  $\delta$  carries over the total order of the events (t, x) in  $\widehat{X}^s$  to the events  $(\delta(t), x)$  in  $\widehat{X}^r$  [called *matching* events in the sequel], it follows immediately that  $\widehat{X}^r$  is an event trace.

A more abstract specification of a channel in terms of states is by,

$$\forall t \in [0, \delta(0)) : \widetilde{X}^{r}(t) := \widetilde{X}^{r}(0) = I \text{ and}$$

$$\forall t > 0 : \widetilde{X}^{r}(\delta(t)) := \widetilde{X}^{s}(t).$$

Note that this definition is consistent in the sense that an execution fulfilling the event trace specification from above fulfills the abstract state definition.

When considering the counting functions of a constant delay channel's ports, we observe that the output counting function is obtained by shifting the input counting function in time by the constant delay, say  $\tau_X$ , obtaining  $\#X^r(t + \tau_X) = \#X^s(t)$ . For non-constant delay channels, this equality does not hold in general, but has to be replaced by inequalities (Pmax) and (Pmin) of the following lemma, summarizing important channel properties:

**Lemma 1** If X is a channel with sending port  $X^s$ , receiving port  $X^r$  and delays in  $[\tau_X^-, \tau_X^+]$ , then the following properties hold:

$\begin{aligned} (Ps) t_1 &\leq t_2 \Rightarrow \#X^s(t_1) \leq \#X^s(t_2) \\ (Pr) t_1 &\leq t_2 \Rightarrow \#X^r(t_1) \leq \#X^r(t_2) \\ (Pmax) \#X^r(t + \tau_X^+) \geq \#X^s(t) \\ (Pmin) \#X^r(t + \tau_X^-) \leq \#X^s(t) \end{aligned}$

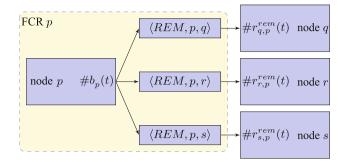

Fig. 5 Fault-containment region for TG-Alg p

*Proof* (Ps) and (Pr) follow immediately from the definition of a counting function and the fact that both  $\widehat{X}^s$  and  $\widehat{X}^r$  are event traces. (Pmax) and (Pmin) follow from the fact that  $\delta$ bijectively maps the (non-idempotent) events occurring in  $\widehat{X}^s$ by time *t* to the (non-idempotent) events occurring in  $\widehat{X}^r$  by time  $\delta(t)$ , in conjunction with  $\delta(t) \in t + [\tau_X^-, \tau_X^+]$  according to (1).

### 4.2 System model

Having introduced the basics of our formal framework, we can now define our system model. A DARTS system consists of a set *P* of n := |P| top-level modules, where  $n \in \mathbb{N}$ . The top-level modules will interchangeably be called TG-Alg or node, and are usually denoted by letters p, q etc. Every TG-Alg p in *P* has exactly one output port with the counting function  $\#b_p(t)$ , where it broadcasts its clock, and one input port per remote TG-Alg  $q \in P \setminus \{p\}$  with the counting function  $\#r_{p,q}^{rem}(t)$ , where it *receives* q's clock. We assume a fully connected system, i.e., from every TG-Alg p to every TG-Alg  $q \in P \setminus \{p\}$ , there is a channel  $\langle REM, p, q \rangle$  with input  $\#b_p(t)$ , output  $\#r_{q,p}^{rem}(t)$ , and delay in  $[\tau_{rem}^{-}, \tau_{rem}^{+}]$ . Figure 5 shows the resulting outbound channels of TG-Alg p.

The following notation will be used throughout the paper: For a function f, let  $f(t^{\rightarrow})$  be its *left limit* at time t, i.e.,  $f(t^{\rightarrow}) := \lim_{\xi \to t} f(\xi)$  and  $\xi$  approaches t from the left. For any  $k \ge 1$ , we say that node p sends tick k, at time  $t_{p,k}$ , if the kth event (without counting idempotent events) occurs at  $t_{p,k}$ . In terms of counting functions:  $t_{p,k}$  is the time for that  $\#b_p(t_{p,k}) = \#b_p(t_{p,k}^{\rightarrow}) + 1 = k$ . The time when the first (respectively the last) correct node sends tick k is denoted by  $t_{first,k}$  (respectively  $t_{last,k}$ ); note that the node who is the first (respectively last) one to send tick k may be different for different k.

**Failure model:** Since hardware faults easily lead to Byzantine failures [30], we assume this failure semantics here: The adverse power of Byzantine failures in our context lies in the ability of a faulty node to generate wrong clock ticks (early timing failures or even spurious) that are perceived inconsistently at different remote nodes. Such failures could be the consequence of manufacturing defects or electrostatic breakdown [40], particle hits [4,57], or electromagnetic noise [50], which may affect any module in a TG-Alg. Due to different wire lengths and signal-level detection thresholds, such faults typically propagate differently to different receivers. Note that we allow faulty nodes to create even metastability [41], but we must assume that metastability cannot propagate beyond FCRs (see below); we have already some convincing evidence [25] that this is ensured by the elastic pipelines in the +/- counters with large probability.

We partition our system into multiple *fault-containment* regions (FCRs), i.e., sets of (sub-)modules that are potentially affected by a single fault like a particle hit and thus cannot be assumed to fail independently. More specifically, we define FCR p to consist of the single TG-Alg p together with all its outgoing channels, as depicted in Fig. 5. If FCR p is faulty, any of its (sub-)modules may behave arbitrarily (Byzantine).<sup>8</sup> Since every FCR is associated with exactly one TG-Alg, we will also use these terms interchangeably.

Throughout the paper, let C be the set of correct FCRs, and F, with f := |F|, the set of faulty FCRs. Clearly  $P = C \cup F$ and  $C \cap F = \emptyset$ , i.e., C and F are partitions of P. We will prove that correct nodes behave as specified in Sect. 4.4 in the presence of up to f Byzantine faulty FCRs, provided that the total number of nodes is  $n \ge 3f + 2$ . Note that this is slightly more than the required lower bound of  $n \ge 3f + 1$  for clock synchronization [12], but facilitates a considerably better precision and accuracy (attained by counting only remote messages when calculating the f + 1 respectively 2f + 1thresholds; including self-reception would lead to  $\tau_{rem}^-$  =  $\tau_{loc}^{-}$  in Theorem 2 and hence spoil the achievable worst-case precision). In case one does not want to spend an extra node to the required 3f + 1 nodes, an alternative is to add selfreception and to artificially increase its delay, e.g., by feeding the signal through inverter chains, so that  $\tau_{loc}^{-}$  becomes of the order of remote delays. Note that both a 3f + 2 node system without and a 3f + 1 node system with self-reception have about the same overall size for reasonably small f, since the extra digital logic needed for self-reception at 3f + 1 nodes is about the size of a node without self-reception. This allows the designer to choose between a system with a slightly larger number of nodes and a system which is slightly more resilient, without changing the overall system size. While, throughout this paper, we focus on the solution using 3f + 2 nodes without self-reception, an adaptation of the algorithm and its correctness proof to the alternative solution can be done in a straightforward manner.

**Booting:** We assume that the whole system is simultaneously reset at time t = 0. However, we allow the modules to

<sup>&</sup>lt;sup>8</sup> In terms of standard failure models for distributed algorithms, our assumption corresponds to mapping link failures to sender node failures.

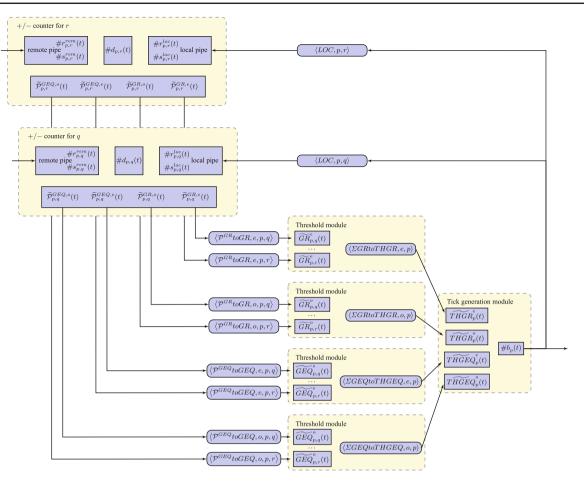

Fig. 6 Architecture of node p

complete booting at (slightly) different times: If  $t_{p,b}$  denotes the time by which all modules in a correct FCR p have completed booting, we require that  $t_{p,b} \in [0, B]$  for some constant  $B \le \tau_{rem}^-$ . Note that the latter condition will ensure that messages sent by p are never lost at a correct node q because of late booting.

# 4.3 TG-Alg architecture and module specification

In this section, we will describe the architecture of a TG-Alg, i.e., its sub-modules and interconnect, and formally specify their behaviors. It is important to note here that the behavioral properties defined in this subsection are *assumed* properties, i.e., basic properties that must a priori be guaranteed by the implementation of the modules. (Modules in FCRs hit by a failure may deviate (arbitrarily) from their correct behavior, however.) Based on these basic properties, the correctness proofs provided in Sect. 5 will show that the system of TG-Algs will maintain the system-level properties (precision and accuracy) as specified in Sect. 4.4.

Figure 6 shows the general architecture of the TG-Alg p, cp. Fig. 3. It consists of one +/- counter module per remote TG-Alg (only two are depicted), four threshold modules

implementing the f + 1 and 2f + 1 rules in Fig. 2, and a tick broadcast module that finally generates p's clock ticks  $\#b_p(t)$ . Every +/- counter is refined into several additional sub-modules: A pair of elastic pipes (remote pipe, local pipe) that form FIFO buffers for (remote, local) clock ticks, a Diff-Gate module that removes matching remote and local ticks from the pipes, and a Pipe Compare Signal Generator (PCSG) module that generates the signals' status reflecting the difference of the number of ticks present in the local and remote pipe.

We will now specify the ports and the behavior of all these modules in detail.

(i) Pairs of elastic pipes: Every TG-Alg p incorporates n-1 pairs of elastic pipelines [77], each of which corresponds to a single remote TG-Alg  $q \in P \setminus \{p\}$ . We will denote the pair of pipes at p corresponding to q by (p, q) in the sequel. (p, q) consists of a remote pipeline that can store up to  $S_{rem}$  clock ticks sent by q, and a local pipeline that can hold up to  $S_{loc}$  clock ticks sent by p locally. Note that the numbers  $S_{rem}$  and  $S_{loc}$  are implementation parameters that have to be chosen in accordance with Theorems 4 and 6; in the specifications of this section, they are just assumed to be unbounded (= always sufficiently large).

The local pipe in (p, q) has a single input port that is fed by TG-Alg *p*'s local clock ticks, i.e.,  $\#b_p(t)$ , supplied via the channel  $\langle LOC, p, q \rangle$ , and a single output port represented by the counting function  $\#r_{p,q}^{loc}(t)$ . Similarly, the remote pipe in (p, q) has a single input port that is fed by TG-Alg *q*'s local clock ticks supplied via the channel  $\langle REM, q, p \rangle$ , cp. Fig. 5, and a single output port represented by the counting function  $\#r_{p,q}^{rem}(t)$ .

We say that *p* receives tick *k* from the remote node *q* at time *t*, or, equivalently, that remote tick *k* is received in the pipepair (p, q) at *p* if  $\#r_{p,q}^{rem}(t) = \#r_{p,q}^{rem}(t^{\rightarrow}) + 1 = k$ . Analogously, we say that local tick *k* is received in the pipepair (p, q) at *p*, if  $\#r_{p,q}^{loc}(t) = \#r_{p,q}^{loc}(t^{\rightarrow}) + 1 = k$ .

**Behavioral description:** Both pipes in the pair (p, q) have the behavior of a zero-delay<sup>9</sup> channel: For any  $t \ge 0$ ,  $\#r_{p,q}^{loc}(t)$ respectively  $\#r_{p,q}^{rem}(t)$  gives the number of clock ticks that reached the end of the local respectively remote pipe by time t. Upon reset, both pipes are pre-filled with the virtual tick 0 (such a tick is called virtual since it has never been sent), and  $\#r_{p,q}^{rem}(t_{p,b}) = \#r_{p,q}^{loc}(t_{p,b}) := 0.$

(ii) **Diff-Gate module:** To avoid pipes with infinite capacity, each pair of pipes is equipped with a special Diff-Gate circuit that removes matching clock ticks, i.e., clock ticks contained in both pipes. However, it deletes matching ticks only if at least one tick remains in both the local and remote pipe. The Diff-Gate for (p, q) has two input ports connected to  $\#r_{p,q}^{rem}(t)$  and  $\#r_{p,q}^{loc}(t)$ , and a single output port represented by the counting function  $\#d_{p,q}(t)$ , which gives the largest tick number that has been removed from both the remote and local pipe of (p, q) by time t. To allow removal of the virtual tick 0, the initial value is  $\#d_{p,q}(t_{p,b}) = -1$ .

**Behavioral description:** Recall that virtual tick 0 shows up at the output of the local and the remote pipe at booting completion time  $t_{loc.0} = t_{p.b}$ .

Ticks are removed from the pipes as follows:

- k = 0: If

- tick k + 1 shows up at the output  $\#r_{p,q}^{rem}(t_{rem,k+1})$  of the remote pipe of (p,q) at time  $t_{rem,k+1}$ , and

- tick k+1 shows up at the output #r<sup>loc</sup><sub>p,q</sub>(t<sub>loc,k+1</sub>) of the local pipe of (p, q) at time t<sub>loc,k+1</sub>,

then tick k = 0 is removed at time  $t_{rmv,k}$  within

$$\max\{t_{rem,k+1}, t_{loc,k+1}\} + \left[\tau_{Diff}^{-}, \tau_{Diff}^{+}\right].$$

•

$$k \ge 1$$

: If

- tick k + 1 shows up at the output  $\#r_{p,q}^{rem}(t_{rem,k+1})$  of the remote pipe of (p,q) at time  $t_{rem,k+1}$ , and

tick k + 1 shows up at the output #r<sup>loc</sup><sub>p,q</sub>(t<sub>loc,k+1</sub>) of the local pipe of (p, q) at time t<sub>loc,k+1</sub>, and

- tick k - 1 has been removed at time  $t_{rmv,k-1}$ ,

then tick k is removed at time  $t_{rmv,k}$  within

$$\max\{t_{rem,k+1}, t_{loc,k+1}, t_{rmv,k-1}\} + \left[\tau_{Diff}^{-}, \tau_{Diff}^{+}\right].$$

Thereby  $\tau_{Diff}^-$  and  $\tau_{Diff}^+$  are timing parameters of the Diff-gate that specify how fast it removes matching ticks. On top of  $\#r_{p,q}^{rem}(t), \#r_{p,q}^{loc}(t)$  and  $\#d_{p,q}(t)$ , we define the size of the local and remote pipe of (p, q) at time *t* as

Note that our definitions imply that a tick occupies space in a pipe only after it reached its end, i.e., when it shows up in  $\#r_{p,q}^{rem}(t)$  after some delay  $\in [\tau_{rem}^-, \tau_{rem}^+]$ , for example.

(iii) Pipe Compare Signal Generator (PCSG) module: The signals provided by the pair of pipes (p, q) and its Diff-Gate are connected to the PCSG, which generates four signals with status  $\tilde{\mathcal{P}}_{p,q}^{GEQ,o}(t)$ ,  $\tilde{\mathcal{P}}_{p,q}^{GEQ,e}(t)$ ,  $\tilde{\mathcal{P}}_{p,q}^{GR,o}(t)$  and  $\tilde{\mathcal{P}}_{p,q}^{GR,e}(t)$  that characterize the difference of the number of clock ticks stored in the remote and local pipes by time *t*. Different signals are provided for odd and even clock ticks. For example, status  $\tilde{\mathcal{P}}_{p,q}^{GEQ,o}(t)$  signals when the number of remote clock ticks, provided that the last clock tick that showed up in the local pipe was odd;  $\tilde{\mathcal{P}}_{p,q}^{GR,o}(t)$  does the same for "greater" replacing "greater or equal".

All these signals are fed, via dedicated channels that add some delay, to the threshold modules of the TG-Alg p.

**Behavioral description:** The signals generated by the PCSG associated with (p, q) must satisfy the following properties:

$$\begin{aligned} \widetilde{\mathcal{P}}_{p,q}^{GEQ,o}(t) &:= [\#r_{p,q}^{rem}(t) \ge \#r_{p,q}^{loc}(t)] \\ & \wedge [\#r_{p,q}^{loc}(t) \in \mathbb{N}_{odd}] \wedge [\#s_{p,q}^{loc}(t) = 1] \end{aligned}$$

$$\begin{aligned} \widetilde{\mathcal{P}}_{p,q}^{GEQ,e}(t) &:= [\#r_{p,q}^{rem}(t) \ge \#r_{p,q}^{loc}(t)] \\ & \wedge [\#r_{p,q}^{loc}(t) \in \mathbb{N}_{even}] \wedge [\#s_{p,q}^{loc}(t) = 1] \end{aligned}$$

$$\begin{aligned} \widetilde{\mathcal{P}}_{p,q}^{GR,o}(t) &:= [\#r_{p,q}^{rem}(t) > \#r_{p,q}^{loc}(t)] \\ &\wedge [\#r_{p,q}^{loc}(t) \in \mathbb{N}_{odd}] \wedge [\#s_{p,q}^{loc}(t) = 1] \end{aligned}$$

$$\begin{aligned} \widetilde{\mathcal{P}}_{p,q}^{GR,e}(t) &:= [\#r_{p,q}^{rem}(t) > \#r_{p,q}^{loc}(t)] \\ &\wedge [\#r_{p,q}^{loc}(t) \in \mathbb{N}_{even}] \wedge [\#s_{p,q}^{loc}(t) = 1] \end{aligned}$$

<sup>&</sup>lt;sup>9</sup> Actually, the pipe delays are accounted for in the delays of the real channels in the signal path, namely,  $\langle REM, q, p \rangle$  and  $\langle LOC, p, q \rangle$ .

Note that these signals need to be true only if the local pipes contain exactly one tick ( $\#s_{p,q}^{loc}(t) = 1$ ), which makes it easier for an implementation to fulfill these properties.

The above signals are fed into four dedicated channels that connect the PCSG with the threshold modules, all of which are initialized to 0:

- Channel  $\langle \mathcal{P}^{GEQ} to GEQ, o, p, q \rangle$  with input  $\widetilde{\mathcal{P}}_{p,q}^{GEQ,o}(t)$ and output  $\widetilde{GEQ}_{p,q}^{o}(t)$  and delay in  $\left[\tau_{GEQ}^{-}, \tau_{GEQ}^{+}\right]$ .

- Channel  $\langle \mathcal{P}^{GEQ} to GEQ, e, p, q \rangle$  with input  $\widetilde{\mathcal{P}}_{p,q}^{GEQ,e}(t)$ , • output  $\widetilde{GEQ}_{p,q}^{e}(t)$  and delay in  $\left[\tau_{GEQ}^{-}, \tau_{GEQ}^{+}\right]$ .

- Channel  $\langle \mathcal{P}^{GR} t o GR, o, p, q \rangle$  with input  $\widetilde{\mathcal{P}}_{p,q}^{GR,o}(t)$ , output  $\widetilde{GR}_{p,a}^{o}(t)$  and delay in  $[\tau_{GR}^{-}, \tau_{GR}^{+}]$ .

- Channel  $\langle \mathcal{P}^{GR} to GR, e, p, q \rangle$  with input  $\widetilde{\mathcal{P}}_{p,q}^{GR,e}(t)$ , output  $\widetilde{GR}^{e}_{p,q}(t)$  and delay in  $[\tau^{-}_{GR}, \tau^{+}_{GR}]$ .

(iv) Threshold modules:  $\widetilde{GEQ}_{p,q}^{o/e}(t)$  and  $\widetilde{GR}_{p,q}^{o/e}(t)$  are further processed at four threshold modules: If the number of active  $\widetilde{GEQ}_{p,q}^{o/e}(t)$  respectively  $\widetilde{GR}_{p,q}^{o/e}(t)$  signals exceeds the threshold of 2f + 1 respectively f + 1, the corresponding threshold signal  $T\widetilde{HGEQ}_{p}^{o/e}(t)$  respectively  $\widetilde{THGR}_{p}^{o/e}(t)$ becomes active within  $[\tau_{TH}^{-}, \tau_{TH}^{+}]$ . This property will be formalized below as a submodule which continuously computes a Boolean predicate [which is a function of time here], involving the sum of the status functions of a threshold module's input ports, and feeding the result into a channel.

Behavioral description: The threshold modules comprise of modules with the threshold modules' input ports and outputs

$$\Sigma T \widetilde{HGEQ}_{p}^{o}(t) = \sum_{q \in Q} \widetilde{GEQ}_{p,q}^{o}(t) \ge 2f + 1$$

$$\Sigma T \widetilde{HGEQ}_{p}^{e}(t) = \sum_{q \in Q} \widetilde{GEQ}_{p,q}^{e}(t) \ge 2f + 1$$

$$\begin{split} &\widetilde{\Sigma THGR}_{p}^{o}(t) = \sum_{q \in \mathcal{Q}} \widetilde{GR}_{p,q}^{o}(t) \geq f + 1 \\ &\widetilde{\Sigma THGR}_{p}^{e}(t) = \sum_{q \in \mathcal{Q}} \widetilde{GR}_{p,q}^{e}(t) \geq f + 1, \end{split}$$

as well as successive channels, which are all initialized to 0 and have delay within  $[\tau_{TH}^{-}, \tau_{TH}^{+}]$ :

- Channel  $\langle \Sigma G E Q t o T H G E Q, o, p \rangle$  whose input port is

- $\Sigma T \widetilde{HGEQ}_p^o$  and the output port is  $T \widetilde{HGEQ}_p^o$ . Channel  $\langle \Sigma G E Q to T H G E Q, e, p \rangle$  whose input port is  $\Sigma T \widetilde{HGEQ}_{p}^{e}$  and the output port is  $T \widetilde{HGEQ}_{p}^{e}$ .

- Channel  $\langle \Sigma GRtoTHGR, o, p \rangle$  with input  $\Sigma \widetilde{THGR}_{p}^{o}$ and output port  $THGR_{n}$ .

Channel  $\langle \Sigma GRtoTHGR, e, p \rangle$  with input  $\Sigma THGR_{p}$ and output port  $THGR_{n}$ .

(v) Tick generation module: The TG-Alg p generates the next clock tick, at some time t, when (i) both threshold outputs for the previously generated tick, say,  $T \widetilde{HGEQ}_{p}^{o}(t)$  and  $\widetilde{THGR}_{p}^{o}(t)$ , are inactive again, and (ii) at least one threshold output  $T \widetilde{HGEQ}_{p}^{e}(t)$  or  $\widetilde{THGR}_{p}^{e}(t)$  for the current tick becomes active. We will refer to (i) as the disabling path and to (ii) as the *enabling path* in the sequel. The Tick broadcast module hence has four input ports connected to the threshold outputs, and a single output port represented by the counting function  $\#b_p(t)$ , which is the number of ticks broadcast by p by time t. Finally,  $\#b_p(t)$  is distributed to the local pipe in (p, q) at TG-Alg p and to the remote pipe in (q, p) at TG-Alg q, for all  $q \in P \setminus \{p\}$ , via dedicated channels (LOC, p, q)and  $\langle REM, p, q \rangle$ , respectively.

**Behavioral description:** Let the signal  $\hat{b}_p$  be the set for which

$$\begin{split} (0,0) \in \widehat{b}_{p}, \\ (t,0) \in \widehat{b}_{p} \Leftrightarrow (T\widetilde{HGEQ}_{p}^{o}(t) \vee \widetilde{THGR}_{p}^{o}(t)) \\ & \wedge \neg (T\widetilde{HGEQ}_{p}^{e}(t) \vee \widetilde{THGR}_{p}^{e}(t)), \\ (t,1) \in \widehat{b}_{p} \Leftrightarrow T\widetilde{HGEQ}_{p}^{e}(t) \vee \widetilde{THGR}_{p}^{e}(t)) \\ & \wedge \neg (T\widetilde{HGEQ}_{p}^{o}(t) \vee \widetilde{THGR}_{p}^{o}(t)). \end{split}$$

Then,  $\#b_p(t)$  is defined as the counting function of  $\hat{b}_p$ , with the initial value  $\#b_p(0) = 0$ .

(vi) Interconnect: The n-1 channels, one for each  $q \in P \setminus \{p\}, \langle LOC, p, q \rangle$  and  $\langle REM, p, q \rangle$  for distributing  $\#b_p(t)$  are all initialized to 0 and adhere to the following specifications:

- Local channel (LOC, p, q) with input signal  $\#b_p(t)$ , output  $\#r_{p,q}^{loc}(t)$  and delay in  $[\tau_{loc}^-, \tau_{loc}^+]$ . • Remote channel  $\langle REM, p, q \rangle$  with input signal  $\#b_p(t)$ ,

- output  $\#r_{q,p}^{rem}(t)$  and delay in  $[\tau_{rem}^-, \tau_{rem}^+]$ .

Recall that the channel delays also include the delays of the pipelines.

4.4 System-level properties

In all executions complying to the system and failure model introduced in the previous sections, the following properties must be guaranteed:

(P) **Precision:** (Theorem 2) There is a constant  $\pi$ , such that for every pair of correct nodes p, q in C:

$$\forall t : |\#b_q(t) - \#b_p(t)| \le \pi. \tag{3}$$

(A) Accuracy: (Theorem 3) There are constants  $R^-$ ,  $O^-$ ,  $R^+$ ,  $O^+ > 0$ , such that for every correct node *p* in *C*:

$$O^{-}(t_{2} - t_{1}) - R^{-} \leq \#b_{p}(t_{2}) - \#b_{p}(t_{1})$$

$$\leq O^{+}(t_{2} - t_{1}) + R^{+}.$$

(4)

(S) Size: (Theorems 4 and 6) There are constants  $S_{rem}$  and  $S_{loc}$ , such that for every pair or correct nodes p, q in C:

$$\#s_{p,q}^{loc}(t) \leq S_{loc} \text{ and } \#s_{p,q}^{rem}(t) \leq S_{rem}$$

Informally, the *precision requirement* (P) just states that the difference of the number of clock ticks generated by any two different correct nodes is bounded, whereas the *accuracy requirement* (A) guarantees some relation of the progress of the clock ticks with respect to the progress of real-time. Note that (A) is also called *envelope requirement* in literature, and effectively bounds the frequency of the generated clock ticks. Finally, the *size requirement* guarantees that the size of the pipelines remains bounded.

In the following Sect. 5, we will show that the system of TG-Algs indeed satisfies the above properties in all executions complying to our system and failure model, provided that (a) the implementations of non-faulty basic modules specified in Sect. 4.3 indeed fulfill their specifications, and (b) the additional "global" Constraints 1–3 introduced later hold. Our Theorems 2, 3, 4 and 6 will also establish numerical values for all the constants introduced above, which only depend on the delay parameters introduced in the specifications of the TG-Alg basic modules in Sect. 4.3.

# **5** Correctness proofs

Our correctness proof and performance analysis has a layered structure, where the lemmas and theorems in a layer establish higher-level abstractions atop of the lower-level abstractions provided by the layer below:

1. The lowest proof layer (Sect. 5.1) deals with the problem of creating the abstraction of uniquely labeled tick k messages atop of anonymous up/down transitions: Provided that Constraint 1 (which bounds the relative speed ratio of all local channels) holds, the pivotal Interlocking Lemma 3 proves that ticks k - 2, k - 4, ... are never falsely interpreted as tick k by the algorithm.

The result of the Interlocking Lemma allows us to bound any correct node's maximum tick frequency (Lemma 4), and to rule out the possibility of unbounded queueing effects in the pipes (Lemma 5); the latter requires Constraint 2 to hold, which ensures that the Diff-Gate can digest ticks at the maximum clock frequency. Atop of these results, it is possible to prove that both the f + 1-rule (GR, Lemma 6) and the 2f+1-rule (GEQ, Lemma 7) work as expected.