# Reconfigurable complementary logic circuits with ambipolar organic transistors

*Citation for published version (APA):* Yoo, H., Ghittorelli, M., Smits, E. C. P., Gelinck, G. H., Lee, H. K., Torricelli, F., & Kim, J. J. (2016). Reconfigurable complementary logic circuits with ambipolar organic transistors. *Scientific Reports*, *6*, 1-11. [35585]. https://doi.org/10.1038/srep35585

DOI: 10.1038/srep35585

# Document status and date:

Published: 20/10/2016

# Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

# Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

# General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

# Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# SCIENTIFIC REPORTS

Received: 22 August 2016 Accepted: 03 October 2016 Published: 20 October 2016

# **OPEN** Reconfigurable Complementary **Logic Circuits with Ambipolar Organic Transistors**

Hocheon Yoo<sup>1,\*</sup>, Matteo Ghittorelli<sup>2,\*</sup>, Edsger C. P. Smits<sup>3</sup>, Gerwin H. Gelinck<sup>3</sup>, Han-Koo Lee<sup>4</sup>, Fabrizio Torricelli<sup>2</sup> & Jae-Joon Kim<sup>1</sup>

Ambipolar organic electronics offer great potential for simple and low-cost fabrication of complementary logic circuits on large-area and mechanically flexible substrates. Ambipolar transistors are ideal candidates for the simple and low-cost development of complementary logic circuits since they can operate as n-type and p-type transistors. Nevertheless, the experimental demonstration of ambipolar organic complementary circuits is limited to inverters. The control of the transistor polarity is crucial for proper circuit operation. Novel gating techniques enable to control the transistor polarity but result in dramatically reduced performances. Here we show high-performance non-planar ambipolar organic transistors with electrical control of the polarity and orders of magnitude higher performances with respect to state-of-art split-gate ambipolar transistors. Electrically reconfigurable complementary logic gates based on ambipolar organic transistors are experimentally demonstrated, thus opening up new opportunities for ambipolar organic complementary electronics.

Organic and polymeric materials deposited at low cost on large-area mechanically flexible substrates are the basis for ubiquitous and imperceptible electronic surfaces integrated in smart objects, thus opening new application opportunities in several fields, including for example entertainment, wellness, security, communication, mobility, healthcare, etc1-5. The great potential offered by organic technologies can meet the application requirements in terms of robustness<sup>6</sup>, low-power consumption<sup>7</sup>, and high-functionality<sup>8,9</sup> by adopting complementary logic circuits, which rely on the availability of both hole-channel (p-type) and electron-channel (n-type) transistors.

The fabrication of p- and n-type organic thin-film transistors (OTFTs) requires the development and deposition of two different semiconductors<sup>10-12</sup>. In addition, each of them has to be carefully optimized by suitable temperature annealing<sup>13</sup> and appropriate engineering of both the insulator-semiconductor<sup>14-16</sup> and the metal-semiconductor interfaces<sup>17-21</sup>. Typically, a proper selection of orthogonal solvents coupled with additive patterning techniques<sup>22</sup>, such as inkjet-printing<sup>23,24</sup>, is employed to provide patterned p- and n-regions in solution-processed devices. However, the resulting fabrication process is complex and the device density is low.

A promising alternative approach is to use ambipolar OTFTs where both electrons and holes can be injected and transported in the same ambipolar organic semiconducting layer<sup>25</sup>. Depending on the applied voltages, ambipolar transistors can operate as p- or n-type transistors, or as p-n junctions<sup>26-30</sup>. Novel gating techniques based on split-gate or tri-gate architectures allow to set the transistor polarity by preventing the charge injection of one of the carrier type (holes or electrons) from the drain<sup>31–34</sup>. Unfortunately, the spacing between the multiple gate electrodes (named gap) severely limits the drain current<sup>34</sup>. The maximum drain current obtained in ambipolar OTFTs with gaps can be up to one order of magnitude lower than that of full-gate ambipolar OTFTs fabricated in the same technology. To maximize the transistor performances the gap size has to be as small as possible. This is technologically demanding because nanometre-size gaps are difficult to obtain. In addition, a small variation of the gap size may result in a large variation of the drain current since the transistor characteristics are strongly affected by the gaps. While multiple gate transistors are a very promising approach, the aforementioned issues are currently hampering their use for the development of ambipolar complementary organic circuits.

<sup>1</sup>Department of Creative IT Engineering, Pohang University of Science and Technology (POSTECH), Pohang 790-784, Korea. <sup>2</sup>Department of Information Engineering, Università degli Studi di Brescia, via Branze 38, 25123 Brescia, Italy. <sup>3</sup>Holst Centre, TNO-The Dutch Organization for Applied Scientific Research, High Tech Campus 31, 5656 AE Eindhoven, The Netherlands. <sup>4</sup>Pohang Accelerator Laboratory, Pohang 790-784, Korea. <sup>\*</sup>These authors contributed equally to this work. Correspondence and requests for materials should be addressed to F.T. (email: fabrizio. torricelli@unibs.it) or J.-J.K. (email: jaejoon@postech.ac.kr)

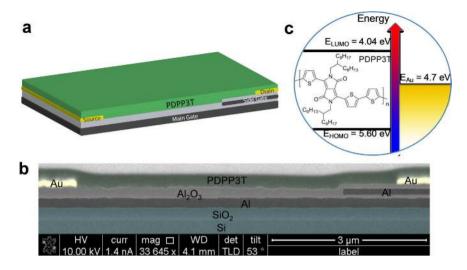

**Figure 1.** Non-planar split-gate ambipolar transistor. (a) Three-dimensional structure. (b) SEM image (c) Schematic band diagram of poly[{2,5-bis(2-hexyldecyl)-2,3,5,6-tetrahydro-3,6-dioxopyrrolo[3,4-c]pyrrole-1,4-diyl}- alt -{[2,2':5',2''-terthiophene]-5,5''-diyl}] (PDPP3T) in relation with gold (Au).

By depositing two metal layers, one for the main gate and one for the side gate, here we show high-performance ambipolar organic transistors with electrical control of the polarity. Owing to the non-planar structure, the gap(s) between the gates are avoided and a continuous full-accumulated channel is formed. Non-planar gate ambipolar transistors show efficient operation and the maximum hole and electron drain currents, normalized by the transistor geometries, are more than one order of magnitude higher than state-of-art split-gate ambipolar transistors, thus providing inverters with superior performances. By means of two-dimensional numerical simulations we provide a comprehensive understanding of non-planar gate ambipolar transistors, shedding light on the key device parameters. Finally, reconfigurable complementary logic gates – the basic building blocks of digital integrated circuits – based on ambipolar organic transistors are experimentally demonstrated for the first time. The superior performance of non-planar split gate combined with the design optimization ensured by reconfigurable organic logic gates opens up new opportunities for the development of large area flexible circuits and smart sensors.

# Results

Non-planar gated ambipolar organic transistor. The simplified cross-section of the non-planar splitgate ambipolar OTFTs (NPA-OTFTs) is shown in Fig. 1a. The transistors are based on the bottom gate bottom contacts structure where an additional metal layer, named side gate, is located in between the gate and drain electrodes. The side gate is used to control the charge injection at the drain electrode. The gate and the side gate are separated along the vertical direction and not horizontally as in coplanar split-gate transistors<sup>31-34</sup>. A typical cross-section SEM image of the transistors is shown in Fig. 1b. Aluminum gate and side gate electrodes are patterned using photolithography. Thereafter we apply atomic layer deposited aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), followed by Ti-Au source and drain electrodes patterned by a lift-off process. The channel length and width are  $L = 6 \mu m$ and  $W = 810 \,\mu\text{m}$ , respectively. The side gate overlaps with the drain electrode and it extends over the drain electrode for  $L_{SG} = 1 \,\mu m$ . The Al<sub>2</sub>O<sub>3</sub> is treated with octadecylphosphonic acid (ODPA) and poly[{2,5-bis(2-hexyldecyl)-2,3,5,6-tetrahydro-3,6-dioxopyrrolo[3,4-c]pyrrole-1,4-diyl}- alt -{[2,2':5',2"-terthiophene]-5,5"-diyl}] (PDPP3T) is deposited by spin coating<sup>35,36</sup>. Further details are reported in the Methods Section. The molecular structure and the energy band diagram of the ambipolar semiconducting polymer PDPP3T are shown in Fig. 1c. The highest occupied molecular orbital (HOMO) and the lowest unoccupied molecular orbital (LUMO) levels measured by means of ultraviolet photoelectron spectroscopy are 5.60 and 4.04 eV, respectively (Supplementary Fig. 1). Gold was used for both the hole and electron injecting electrodes for practical convenience, owing to its environmental stability and its ease of patterning by photolithography.

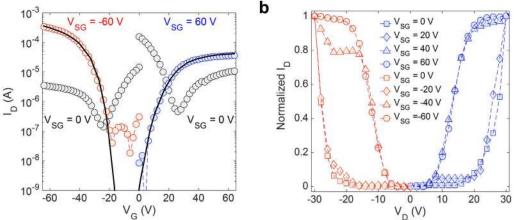

Measured transfer and output characteristics are shown in Fig. 2. Depending upon the voltage applied to the side gate  $V_{side}$  non-planar ambipolar transistors can operate as conventional ambipolar, p-type, or n-type OTFTs. Figure 2a shows that at  $V_{side} = 0$  V both electrons and holes can be injected and typical V-shape characteristics (grey symbols) are measured. In contrast, when  $V_{side} = -60$  V electron injection at the drain contact is prevented and the NPA-OTFTs show p-type operation (red symbols). Analogously, when  $V_{side} = 60$  V hole injection at the drain contact is prevented and the NPA-OTFTs show n-type operation (blue symbols). The output characteristics shown in Fig. 2b confirm that the polarity of NPA-OTFTs can be set by the side gate voltage  $V_{side}$ . In order to provide an easy comparison, in Fig. 2b the drain current is normalized with respect to its maximum. Typical ambipolar characteristics are measured at small  $|V_{side}|$  while, at large  $|V_{side}|$ , the unwanted charge injection from the drain electrode is prevented and unipolar characteristics with flat current saturation are obtained.

When the NPA-OTFTs work in unipolar regime, the on/off current ratio is about 10<sup>4</sup> for both electrons and holes, the turn-on voltages are  $V_{on,h} \approx -20$  V and  $V_{on,e} \approx 0$  V, and the average transconductance for p-type and n-type operation are  $g_{m-p} = 1.60 \,\mu\text{S}$  and  $g_{m-n} = 0.19 \,\mu\text{S}$ , respectively. For comparison, we fabricated

а

**Figure 2.** Electrical characteristics of non-planar split-gate ambipolar transistor. The transistors channel length and width are  $L = 6 \mu m$  and  $W = 810 \mu m$ , respectively. (a) Measured (symbols) transfer characteristics  $(I_D - V_G)$  at  $|V_D| = 60 V$ , of PDPP3T operated in ambipolar  $V_{side} = 0 V$ , and unipolar p-type  $V_{side} = -60$  or n-type  $V_{side} = 60 V$  transistor. Full lines are calculated by means of 2D numerical simulations. (b) Normalized output characteristics  $(I_D - V_D)$  as a function of the side gate voltage  $V_{side}$ .  $|V_G| = 20 V$ .

conventional (viz. single gate) ambipolar and co-planar split-gate OTFTs with 1  $\mu$ m gate-gap in the same technology (Supplementary Fig. 3). The average transconductance obtained in conventional ambipolar OTFTs are  $g_{m-p} = 1.40 \,\mu$ S and  $g_{m-n} = 0.16 \,\mu$ S, while in coplanar split-gate OTFTs are  $g_{m-p} = 0.40 \,\mu$ S and  $g_{m-n} = 0.04 \,\mu$ S. The transconductance of NPA-OTFTs are even slightly higher than in conventional ambipolar OTFTs. In contrast, the transconductance obtained from coplanar split-gate architectures is three times smaller. A comparison of the gate configurations, semiconductors, transistor architectures, and experimental application demonstrations is provided in Table 1. Avoiding the gap, the non-planar configuration offers the highest on-current and transconductance.

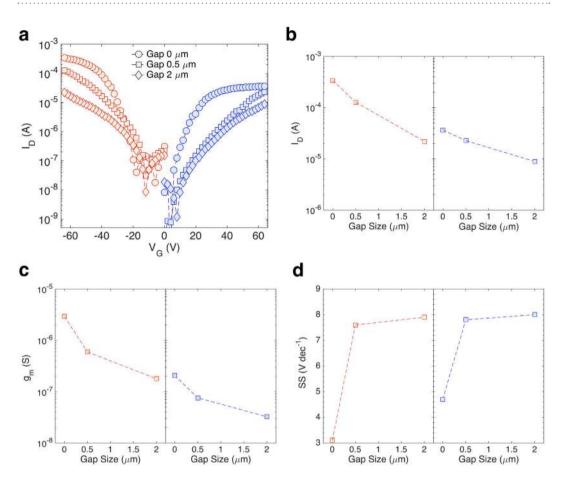

**Impact of the gaps on the transistor performance.** In order to further assess the impact of the gap on the performance of ambipolar OTFTs, we intentionally fabricated NPA-OTFTs with a gap between the gate and the side gate (Supplementary Fig. 4). Figure 3a shows the measured transfer characteristics of NPA-OTFTs with  $2\mu$ m size gap,  $0.5\mu$ m size gap, and without gap. Figure 3b-d show the main transistor parameters, namely the maximum on-current, the transconductance, and the subthreshold slope, as a function of the gap size. The best performances are obtained when using NPA-OTFTs without gap. The measurements confirm that the transistor performances are dramatically affected by the gap size. By increasing the gap size the on-current and the transconductance become smaller and the subthreshold slope increases. More in detail, when the NPA-OTFTs is operated in p-type mode, the on-current (Fig. 3b, left panel) decreases by a factor of 3 and 15 when the gap size is  $0.5 \mu m$  and  $2 \mu m$ , respectively. Analogously, the maximum transconductance (Fig. 3c, left panel) is  $2.97 \mu S$ in NPA-OTFTs without the gap, while it lowers to  $0.54 \,\mu\text{S}$  and  $0.11 \,\mu\text{S}$  when the gap size is  $0.5 \,\mu\text{m}$  and  $2 \,\mu\text{m}$ , respectively. Therefore, the transconductance is reduced by a factor of 25. In addition, the subthreshold slope (Fig. 3d, left panel) increases from 3 V/dec up to 7.6 V/dec by increasing the gap size. In the case of n-type operation, the on-current (Fig. 3b, right panel) decreases by a factor of 1.4 and 4 when the gap size is  $0.5 \,\mu\text{m}$  and  $2 \,\mu\text{m}$ , respectively, while the transconductance (Fig. 3c, right panel) reduces by a factor of 7. On the other hand, the subtreshold slope (Fig. 3d, right panel) increases from 4.7 V/dec to 8 V/dec when the gap size is  $0.5 \mu\text{m}$  and  $2 \mu\text{m}$ .

**2D** numerical simulations. To gain more insight on the key physical, material and geometrical parameters of the non-planar ambipolar OTFTs we reproduced the measurements with numerical simulations (Fig. 2a, full lines). The continuity, Poisson, and drift-diffusion transport equations are solved on a two-dimensional (2D) grid. Charge flow at the metal-semiconductor interface is calculated with the thermionic field emission equations accounting for the actual 2D energy barriers, and electric field distributions at the interface<sup>37,38</sup>. The simulation input parameters are given in Supplementary Table 1. In reproducing the measurements with 2D numerical simulations, we estimated the gold work function to be 4.7 eV, which is in good agreement with the 4.5-5.5 eV energy range<sup>39-41</sup>. Consequently, the charge injection barriers to electrons and holes were estimated to be approximately  $\Phi_{Be} = 0.66 \text{ eV}$  and  $\Phi_{Bb} = 0.90 \text{ eV}$ . The density of states (DOS) of the PDPP3T semiconductor is calculated by fitting the measurements over the whole range of applied voltages. We found that both the electron and hole DOS can be well approximated by the sum of two Gaussian functions defined by the total density of tail and deep states and disorder energy width. The hole and electron DOS are shown in the Supplementary Fig. 5. The DOS parameters show that the total number of LUMO and HOMO states is similar for both electrons and holes, while the energetic disorder ( $\sigma$ ) is larger for electrons ( $\sigma_e = 90 \text{ meV}$  and  $\sigma_h = 60 \text{ meV}$ ). This suggests that in PDPP3T the hole transport is easier than the electron transport. Dipoles due to the ODPA treatment are also included by means of surface charges at the insulator-semiconductor interface ( $N_{is} = 2 \times 10^{11} \text{ cm}^{-2}$ ). ODPA is an alkane phosphonic acid-based SAM with positive charges facing the semiconductor<sup>11,42</sup>. This explains the different hole and electron on-voltages ( $V_{on,h} \approx -20 \text{ V}, V_{on,e} \approx 0 \text{ V}$ ) obtained from the transfer characteristics shown in Fig. 2a.

| Gate structure        | Semiconductor                       | Transistor<br>architecture    | # of gaps | Gap size<br>[µm] | $(L/W) \times I_{ON-p}$<br>[nA] | $(L/W) \times I_{ON-n}$<br>[nA] | $\begin{array}{c} (L/W) \times g_{m\text{-}p} \\ [pS] \end{array}$ | $\begin{array}{c} (L/W) \times g_{m\text{-}n} \\ [pS] \end{array}$ | Experimental application      | Ref.      |

|-----------------------|-------------------------------------|-------------------------------|-----------|------------------|---------------------------------|---------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------|-----------|

| Coplanar split-gate   | PCDTBT:PC <sub>70</sub> BM<br>blend | Bottom-gate<br>top-contact    | 1         | 4                | 41                              | 3                               | 267                                                                | 258                                                                | _                             | [31]      |

| Coplanar split-gate   | F8BT                                | Bottom-gate<br>top-contact    | 1         | 4                | 11                              | 7                               | 0.8                                                                | 0.2                                                                | Light-emitting<br>transistors | [32]      |

| Coplanar tri-gate     | PDPPTPT                             | Bottom-gate<br>bottom-contact | 2         | 1.5              | 4                               | 4                               | 11                                                                 | 18                                                                 | _                             | [33]      |

| Coplanar split-gate   | PDPP-TT-T                           | Bottom-gate<br>bottom-contact | 1         | 1                | 320                             | 32                              | 810                                                                | 405                                                                | CMOS inverter                 | [34]      |

| Non-planar split-gate | PDPP3T                              | Bottom-gate<br>bottom-contact | 0         | 0                | 2960                            | 296                             | 12400                                                              | 1400                                                               | Reconfigurable<br>logic gates | This work |

Table 1. Comparison of the transistor structures, (L/W) normalized on-current and transconductance, and application demonstrations.

Figure 3. Impact of the gap on the transistors performance. (a) Measured transfer characteristics as a function of the gap size.  $|V_D| = 60 \text{ V}$ , and  $|V_{side}| = 60 \text{ V}$ . (b) Maximum on-current (viz. at  $|V_G| = 65 \text{ V}$ ) as a function of the gap size when the transistor is operated as p-type (left panel) or n-type (right panel). (c) Maximum transconductance as a function of the gap size. (d) Maximum subthreshold slope as a function of the gap size.

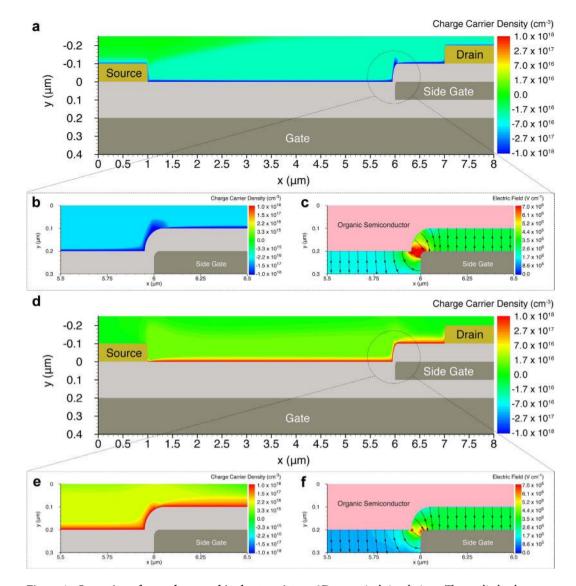

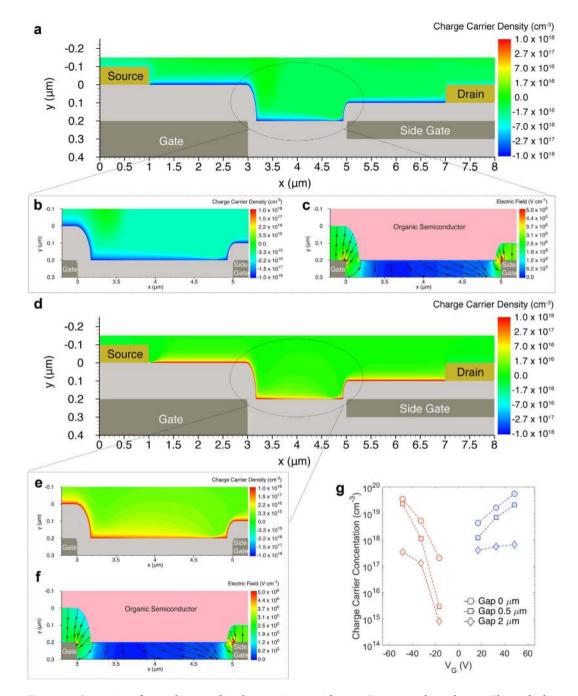

The simulated transistor geometries are derived from the SEM cross-sections shown in the Supplementary Fig. 4. The charge concentration in the PDPP3T semiconductor and the electric field distribution in the gate insulator are shown when the NPA-OTFT without gap operates as n-type (Fig. 4a–c) or p-type transistor (Fig. 4d–f). In both cases a continuous charge accumulation is obtained along the whole channel (Fig. 4a,d). Figure 4b,e show a zoom of the charge concentration at the edge of the side gate. The side gate is deposited on top of the gate insulator and hence the semiconductor is spin-coated on a non-planar structure. Despite the non-planar structure of the transistor, full accumulation is attained also at the edge of the side gate. The charge concentration at the edge of the side gate is larger than the channel concentration owing to the 2D electric field distribution due to the non-planar geometry, as shown in Fig. 4c,f. Moreover, the charge concentration accumulated by side gate is larger

**Figure 4. Operation of non-planar ambipolar transistors.** 2D numerical simulations. The applied voltages are  $|V_G| = 50 \text{ V}$ ,  $|V_D| = 30 \text{ V}$ ,  $V_S = 0 \text{ V}$ ,  $|V_{side}| = 60 \text{ V}$ . Physical and geometrical parameters are given in the Supplementary Fig. 3 and the SEM images in the Supplementary Fig. 4, respectively. (a) N-type operation. Electron concentration into the organic semiconductor. (b) Zoomed image of the electron concentration accumulated at the side gate edge. (c) Zoomed image of the 2D distribution and streamline of the electric field at the side gate edge. (d) P-type operation. Hole concentration into the organic semiconductor. (e) Zoomed image of the hole concentration accumulated at the side gate edge. (f) Zoomed image of the 2D distribution and streamline of the electric field at the side gate edge.

.....

than the charge concentration accumulated by the gate region because  $|V_{side}| > |V_G|$  and the side gate insulator thickness is the half of the main gate. This explains the higher on-current and transconductance obtained for NPA-OTFTs compared with conventional ambipolar OTFTs fabricated in the same technology (Supplementary Fig. 3).

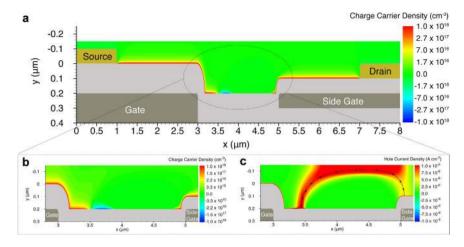

Figure 5 shows the charge concentration and the electric field distribution when the NPA-OTFT with  $2\mu m$  gap is operated as n-type (Fig. 5a–c) or p-type transistor (Fig. 5d–f). The electron and hole concentration are shown in Fig. 5a,d, respectively. The charge carriers are accumulated in correspondence of the gate and the side gate and, owing to the lateral fringing of the electric field (Fig. 5c,f), good charge accumulation is also attained at both sides of the gap region. Despite the similar electric field distribution shown in Fig. 5c,f, Fig. 5b shows that in the case of n-type operation electrons are well-confined and almost completely accumulated in the gap region. In contrast, Fig. 5e shows that in the case of p-type operation holes are weakly accumulated and poorly confined in the central region of the gap. The smaller hole accumulation is inherently due to the alkane-based SAM dipoles orientation: the positive charges of the SAM dipole face the PDPP3T semiconductor, giving rise to a more favourable electron accumulation. Therefore, in the case of p-type operation the parasitic resistance due to the gap is large and about 50% of V<sub>D</sub> drops on the gap region. This has also a negative impact on the charge injection which strongly depends on the drain voltage in a bottom-gate bottom-contact structure<sup>43</sup>. The larger

**Figure 5.** Operation of non-planar ambipolar transistors with gap. 2D numerical simulations. The applied voltages are  $|V_G| = 50 \text{ V}$ ,  $|V_D| = 30 \text{ V}$ ,  $V_S = 0 \text{ V}$ ,  $|V_{\text{side}}| = 60 \text{ V}$ . Physical and geometrical parameters are given in the Supplementary Figs. 3 and 4, respectively. (a) N-type operation. Electron concentration into the organic semiconductor. (b) Zoomed image of the electron concentration accumulated in the gap region. (c) Zoomed image of the 2D distribution of the electric field in the gap region. (d) P-type operation. Hole concentration into the organic semiconductor. (e) Zoomed image of the hole concentration accumulated in the gap region. (f) Zoomed image of the 2D distribution of the electric field in the gap region. (g) The charge concentration at the insulator/semiconductor interface in the middle of the gaps as a function of VG for NPA-OTFTs with different gap size.

injection barrier and the reduced  $V_D$  result in an inefficient charge injection, and hence a hole depletion close to the source contact is readily visible in Fig. 5d. This reveals that the gap has a double detrimental effect on the transistor performance since it causes increase in parasitic series resistance and reduced charge injection. The detrimental effect of the gap is also strictly related to the SAM treatment. For example, fluorinated-alkyl SAMs would result in negative interface charges and thus hole accumulation. In addition, the SAM dipole strength can vary several orders of magnitude and, depending on the process conditions, it gives rise to interface charges in the range  $10^{11}$ – $10^{13}$  cm<sup>-242,44</sup>.

Figure 6. Impact of the SAM treatment and charge carrier concentration in the gate-gap region on the transistor operation. The interface charges due to the dipoles of the SAM are deliberately increased from  $2 \times 10^{11}$  cm<sup>-2</sup> (as in Figs 4 and 5) to  $7 \times 10^{11}$  cm<sup>-2</sup>. (a) Hole and electron concentration into the organic semiconductor. (b) Zoomed image of the hole and electron concentration into the gap region. (c) Zoomed image of the hole current density distribution into the gap region. Holes transport in the bulk of the semiconductor and the drain current is lower than  $10^{-12}$  A.

To further investigate the impact of the SAM on the gaps, we deliberately increase the interface charges from  $2 \times 10^{11}$  cm<sup>-2</sup> to  $7 \times 10^{11}$  cm<sup>-2</sup>. Figure 6 shows the charge carrier concentration and the hole current density when the transistor is operated as p-type. Surprisingly, we found that p-type operation is prevented. The weak electric field in the central part of the gap is not large enough to compensate the electron accumulation. Figure 6b shows that a reversed biased p-n junction is formed at the left side of the gap, while the right side is fully depleted. Although the transistor is operated in the on-state (V<sub>G</sub> = -30 V, V<sub>D</sub> = -30 V, V<sub>side</sub> = -60 V), the charge carriers transport in the bulk of the semiconductor and the drain current is lower than  $10^{-12}$  A (Fig. 6c). Therefore, we can conclude that the presence of the gap in split-gate ambipolar transistors not only limits the performances but may also result in non-functional devices when the fabrication process is not properly optimized.

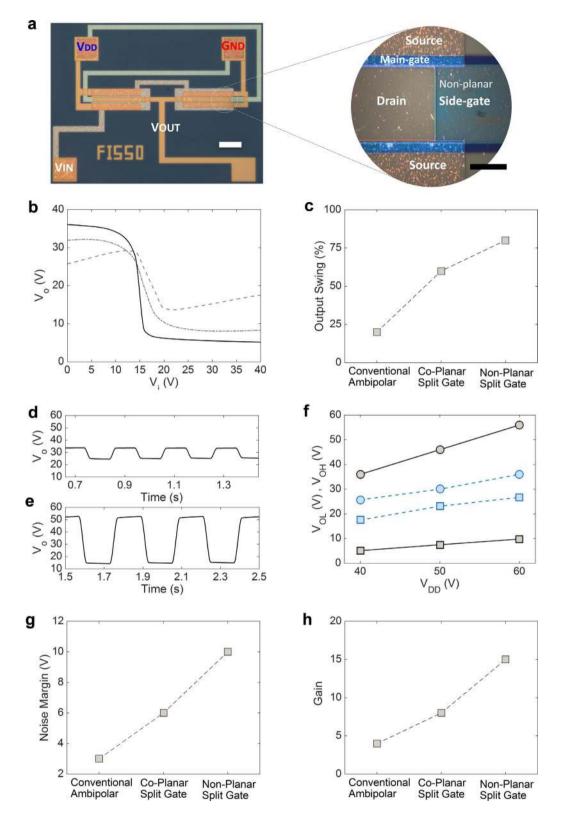

High-performance complementary inverters. Next, we fabricated the inverters with various transistor structures. Figure 7a shows the optical image of NPA-OTFT-based inverter and the zoomed image of the channel region to confirm the absence of gate-gap. Typical transfer characteristics of complementary inverters based on conventional ambipolar OTFTs (dashed line), split-gate ambipolar OTFTs (dot-dashed line) and NPA-OTFT (full line) are shown in Fig. 7b. All the inverters are fabricated in the same technology. The main figures of merit of the inverters, viz. output swing, noise margin, and gain, are displayed in Fig. 7c-h, respectively. The inverters based on the proposed NPA-OTFTs show the best characteristics. The maximum gain is 15, noise margin is 10 V, and the output swing is larger than 75% of  $V_{DD}$ . As shown in Fig. 7f the low and high output voltages ( $V_{OL}$  and  $V_{OH}$ ) measured in NPA-OTFTs based inverters are very close to  $V_{DD}$  and  $G_{ND}$  showing a three-fold improvement of the output swing  $(V_{OH}-V_{OL})$  with respect to inverters fabricated with conventional ambipolar transistors. Moreover, in NPA-OTFTs inverters the output swing increases with the supply voltage since the side gates of the NPA-OTFTs operated in n-type and p-type mode are connected to  $V_{DD}$  and  $G_{ND}$ , respectively. Hence, with respect to inverters based on conventional ambipolar OTFTs, the overall performances are improved by a factor of 3. The low performance of the conventional ambipolar inverters OTFTs in terms of noise margin and output swing are inherently related to the Z-shaped characteristic (dashed line Fig. 7b) due to the ambipolar conduction. Furthermore, the experimental results show that modest noise margin - which is crucial for the development of robust electronics - of split-gate inverters is due to the gap between the gate and the side gate, and this is in agreement with other previous works<sup>33</sup>.

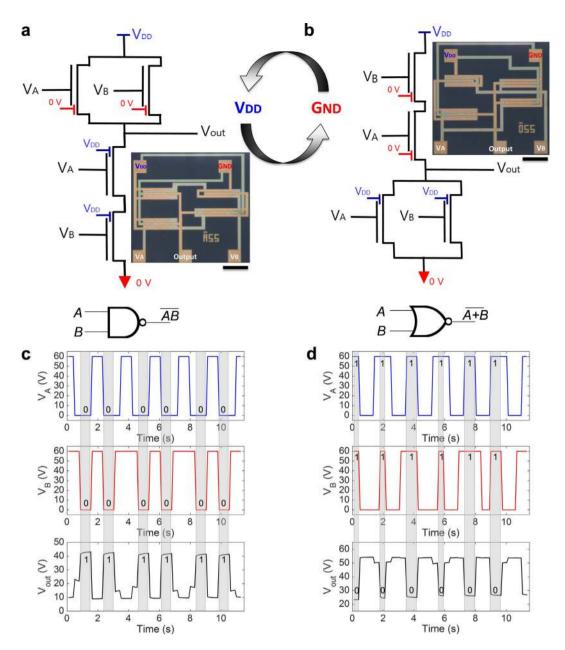

**Reconfigurable complementary logic gates.** NAND and NOR circuits are key components for digital integrated circuits. A logic operation of any complexity can be built using NAND or NOR gates only<sup>45</sup> and hence NAND and NOR gates are universal gates. In addition, the efficiency in terms of function complexity per transistor count can be improved when both NAND and NOR are available. NAND and NOR logic circuits based on NPA-OTFTs are shown in Fig. 8a,b, respectively. P- and n-type transistor operations are obtained by simply connecting the side gate to  $G_{ND} = 0 V$  and  $V_{DD}$ , respectively. This prevents the undesired charge injection from the drain electrode. Since the polarity of the transistors depends on the side gate voltage, a NAND circuit can be electrically reconfigured into a NOR circuit and vice versa. Electrically reconfigurable gates find relevant application for the development of programmable logic circuits, field-programmable gate arrays, and microprocessors<sup>9,46,47</sup>. Moreover, the availability of both NAND and NOR gates provides a more efficient implementation in terms of number of logic gates and mapping functions. By the way of example, in a NAND-only design the NOR function can be obtained with four NANDs. Figure 8c,d show the NAND and NOR gates showed that a corresponding as a function of time and the switching characteristics of NAND and NOR gates showed that a corresponding

Figure 7. Impact of the transistor structure on the inverters performance. (a) Optical microscopy image of non-planar ambipolar inverter, scale bar is 200  $\mu$ m (white) and zoom of the channel region, scale bar is 20  $\mu$ m (black). (b) Measured inverter characteristics (V<sub>o</sub>-V<sub>i</sub>) of conventional (dashed line), co-planar split gate with gap (dotted line), and non-planar without gap (full line) ambipolar organic transistors. (c) Output swing as a function the transistor structure. Output voltage response of (d) conventional ambipolar and (e) non-planar ambipolar inverters at V<sub>DD</sub> = 60 V. (f) Low (squares, V<sub>OL</sub>) and high (circles, V<sub>OH</sub>) output voltage of conventional (dashed lines) and non-planar without gap (full lines) ambipolar inverters as a function of the supply voltage V<sub>DD</sub> (G<sub>ND</sub> = 0 V). (g) Noise margin and (h) gain as a function of the transistor structure.

Figure 8. Electrically reconfigurable complementary logic gates. (a) Schematic, symbol, and top-view image of a complementary logic NAND, scale bar is 400  $\mu$ m. (b) Schematic, symbol, and top-view image of a complementary logic NOR, scale bar is 400  $\mu$ m. (c) Inputs and measured output of the NAND circuits. (d) Inputs and measured output of the NOR circuits. The NAND circuits can be electrically reconfigured in NOR circuits by simply swapping V<sub>DD</sub> and G<sub>ND</sub> = 0V.

output voltages changed properly. This is the first demonstration, at least to the authors' knowledge, of complementary logic circuits fabricated with ambipolar organic transistors.

In summary, non-planar ambipolar OTFTs offer the simple fabrication of ambipolar organic reconfigurable complementary logic circuits. NPA-OTFTs can electrically control the transistor polarity providing orders of magnitude superior performances with respect to state-of art coplanar multiple gate ambipolar transistors. 2D numerical simulations provide insight on the transistor operation and the key design and material parameters. The simulations reveal that, in contrast to the NPA-OTFTs, coplanar multiple gate ambipolar transistors have to be carefully optimized and the insulator-semiconductor interface plays a key role for the proper transistor operation. This is critical for the development of practical applications. Electrically reconfigurable complementary logic gates based on NPA-OTFTs are experimentally demonstrated for the first time. This opens up new opportunities for simple and low-cost fabrication of large-area complementary logic organic circuits.

# Methods

**Devices fabrication.** Bottom gate/bottom contact ambipolar TFTs were fabricated on having 300 nm SiO<sub>2</sub> on Si substrate. Bottom gate electrodes (aluminum, 200 nm) and middle gate electrodes (aluminum, 100 nm) were deposited using an e-beam evaporator and were patterned using the dry metal etching method. Two gate dielectric layers, aluminum oxide (100 nm), were deposited on top of patterned bottom and middle aluminum gate electrodes using the atomic layer deposition method. The source/drain electrodes (Au, 100 nm) were deposited on top of the aluminum oxide using e-beam evaporation and lift-off lithography. Inductively Coupled Plasma (ICP) etching was used for oxide etching to form via-holes from bottom and middle gate electrodes to source/drain electrodes. All the transistors have the same channel lengths and widths equal to  $L = 6\mu m$  and  $W = 810\mu m$ , respectively. For the surface treatment on top of channel region, the samples were dipped in a solution of 10 mM of octadecylphosphonic acid (ODPA) in Isopropyl alcohol (IPA) for 3–5 days after being exposed to UV-ozone for 15 min. Then, PDPP3T, from Solarmer, was dissolved in 1, 2-dichlorobenzene (ODCB) to obtain 13 mg mL<sup>-1</sup> and spin-coated. The samples were vacuum-dried at 100 °C for longer than 12 hours to remove any residue of the solvent and then annealed at 150 °C for 1 hour in ultra-high vacuum (<10<sup>-6</sup> torr).

**Electrical characterizations.** All devices were measured in a vacuum probe station (Keithley 4200-SCS) and LCR meter (E4980A). The transconductance was extracted in the saturation regime using the following equations:  $g_m = dI_D/dV_G$ .

**Two-dimensional numerical simulations.** The coupled drift-diffusion, Poisson, and current continuity equations are solved together<sup>33,37,38</sup>. The electron and hole DOS are well approximated by the sum of two Gaussian functions. The DOS is shown in Supplementary Fig. 5 and the DOS parameters are listed in the Supplementary Table S1. The simulation parameters are the following: relative permittivity of semiconductor  $\varepsilon_{rs}$ = 3, relative permittivity of insulator  $\varepsilon_{ri}$ = 9, highest occupied molecular orbital (HOMO) energy level  $E_{HOMO}$ = 5.60 eV, lowest unoccupied molecular orbital (LUMO) energy level  $E_{LUMO}$ = 4.04 eV, holes mobility  $\mu_h$ = 0.5 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, electrons mobility  $\mu_e$ = 0.1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, gold electrodes work function  $\Phi_{Au}$ = 4.7 eV (the hole and electron energy barrier at the source/drain metal-semiconductor are  $\Phi_{Bh}$ = 0.9 eV and  $\Phi_{Be}$ = 0.66, respectively), Schottky barrier lowering  $\Delta \Phi_B$ = e [e E/(4  $\pi \varepsilon_0 \varepsilon_{rs}$ )]<sup>1/2</sup>, where e is the elementary charge, E is the electric field, and  $\varepsilon_0$  is the vacuum permittivity.

### References

- 1. Gelinck, G. H. *et al.* Flexible active-matrix displays and shift registers based on solution-processed organic transistors. *Nat. Mater.* **3**, 106–110 (2004).

- 2. Sekitani, T. *et al.* A large-area wireless power-transmission sheet using printed organic transistors and plastic MEMS switches. *Nat. Mater.* **6**, 413–417 (2007).

- 3. Schwartz, G. et al. Flexible polymer transistors with high pressure sensitivity for application in electronic skin and health monitoring. Nat. Commun. 4, 1859 (2013).

- 4. Kaltenbrunner, M. et al. An ultra-lightweight design for imperceptible plastic electronics. Nature 499, 458-463 (2013).

- Jung, S., Sou, A., Gili, E. & Sirringhaus, H. Inkjet-printed resistors with a wide resistance range for printed read-only memory applications. Org. Electron. 14, 699–702 (2013).

- Myny, K. et al. Unipolar organic transistor circuits made robust by dual-gate technology. IEEE J. Solid-State Circuits 46, 1223–1230 (2011).

- 7. Klauk, H., Zschieschang, U., Pflaum, J. & Halik, M. Ultralow-power organic complementary circuits. Nature 445, 745-748 (2007).

- Torsi, L., Magliulo, M., Manoli, K. & Palazzo, G. Organic field-effect transistor sensors: a tutorial review. Chem. Soc. Rev. 42, 8612-8628 (2013).

- 9. Sou, A. et al. Programmable logic circuits for functional integrated smart plastic systems. Org. Electron. 15, 3111–3119 (2014).

- Baeg, K.-J. et al. Flexible Complementary Logic Gates Using Inkjet-Printed Polymer Field-Effect Transistors. IEEE Electron Device Lett. 34, 126–128 (2013).

- Zhang, Z. et al. Direct Patterning of Self-Assembled Monolayers by Stamp Printing Method and Applications in High Performance Organic Field-Effect Transistors and Complementary Inverters. Adv. Funct. Mater. 25, 6112–6121 (2015).

- Kraft, U. et al. Flexible low-voltage organic complementary circuits: Finding the optimum combination of semiconductors and monolayer gate dielectrics. Adv. Mater. 27, 207–214 (2015).

- 13. Yoo, H. et al. Self-assembled, millimeter-sized TIPS-pentacene spherulites grown on partially crosslinked polymer gate dielectric. Adv. Funct. Mater. 25, 3658–3665 (2015).

- 14. James, D. T. *et al.* Thin-Film Morphology of Inkjet- Printed Single-Droplet Organic Transistors Using Polarized Raman Spectroscopy: Effect of Blending TIPS- Pentacene with Insulating Polymer. *ACS Nano* **5**, 9824–9835 (2011).

- Shin, N. et al. Vertically Segregated Structure and Properties of Small Molecule-Polymer Blend Semiconductors for Organic Thin-Film Transistors. Adv. Funct. Mater. 23, 366–376 (2013).

- 16. Cho, J. et al. Facile and Fine Polarity-Tuning of Polymeric Semiconductors: The Effects of Nitrile Groups on Polymer-Polymer Blend Systems. Adv. Electron. Mater. 2 (2016).

- 17. Benor, A. & Knipp, D. Contact effects in organic thin film transistors with printed electrodes. Org. Electron. 9, 209-219 (2008).

- Timmreck, R., Olthof, S., Leo, K. & Riede, M. K. Highly doped layers as efficient electron-hole recombination contacts for tandem organic solar cells. J. Appl. Phys. 108 (2010).

- 19. Lee, J. et al. Ionic self-assembled monolayer for low contact resistance in inkjet-printed coplanar structure organic thin-film transistors. Org. Electron. 15, 2021–2026 (2014).

- Xu, Y. et al. Regulating charge injection in ambipolar organic field-effect transistors by mixed self-assembled monolayers. ACS Appl. Mater. Interfaces 6, 14493–14499 (2014).

- Bock, C. *et al.* Improved morphology and charge carrier injection in pentacene field-effect transistors with thiol-treated electrodes. *J. Appl. Phys.* 100, 114517 (2006).

- Kwon, J., Kyung, S., Yoon, S., Kim, J.-J. & Jung, S. Solution-Processed Vertically Stacked Complementary Organic Circuits with Inkjet-Printed Routing. Adv. Sci. 3 (2016).

- Chung, S., Kim, S. O., Kwon, S.-K., Lee, C. & Hong, Y. All-Inkjet-Printed Organic Thin-Film Transistor Inverter on Flexible Plastic Substrate. *IEEE Electron Device Lett.* 32, 1134–1136 (2011).

- 24. Myny, K. et al. A thin-film microprocessor with inkjet print-programmable memory. Sci. Rep. 4, 7398 (2014).

- Bisri, S. Z., Piliego, C., Gao, J. & Loi, M. A. Outlook and emerging semiconducting materials for ambipolar transistors. Adv. Mater. 26, 1176–1199 (2014).

- Lei, T., Dou, J. H., Cao, X. Y., Wang, J. Y. & Pei, J. A BDOPV-based donor-acceptor polymer for high-performance n-type and oxygen-doped ambipolar field-effect transistors. *Adv. Mater.* 25, 6589–6593 (2013).

- 27. Deng, Y. et al. Black Phosphorus-Monolayer MoS2 van der Waals Heterojunction P-N Diode. ACS Nano 8, 8292-8299 (2014).

- Buscema, M., Groenendijk, D. J., Steele, G. a., van der Zant, H. S. J. & Castellanos-Gomez, A. Photovoltaic effect in few-layer black phosphorus PN junctions defined by local electrostatic gating. *Nat. Commun.* 5, 4651 (2016).

- Maruyama, K. *et al.* Ambipolar light-emitting organic single-crystal transistors with a grating resonator. *Sci. Rep.* 5, 10221 (2015).

Zhou, X. *et al.* Balanced ambipolar organic thin-film transistors operated under ambient conditions: Role of the donor moiety in

- BDOPV-based conjugated copolymers. *Chem. Mater.* 27, 1815–1820 (2015).

31. Hsu, B. B. Y. *et al.* Split-gate organic field effect transistors: Control over charge injection and transport. *Adv. Mater.* 22, 4649–4653 (2010).

- Hsu, B. B. Y. *et al.* Control of efficiency, brightness, and recombination zone in light-emitting field effect transistors. *Adv. Mater.* 24, 1171–1175 (2012).

- Torricelli, F. et al. Ambipolar Organic Tri-Gate Transistor for Low-Power Complementary Electronics. Adv. Mater. 28, 284–290 (2016).

- 34. Yoo, H. et al. Asymmetric Split-Gate Ambipolar Transistor and Its Circuit Application to Complementary Inverter. Adv. Mater. Technol. 1 (2016).

- Bijleveld, J. C. et al. Poly(diketopyrrolopyrrole-terthiophene) for Ambipolar Logic and Photovoltaics. J. Am. Chem. Soc. 131, 16616–16617 (2009).

- 36. Roelofs, W. S. C. *et al.* Fast ambipolar integrated circuits with poly(diketopyrrolopyrrole- terthiophene). *Appl. Phys. Lett.* **98**, 96–98 (2011).

- Torricelli, F., Colalongo, L., Raiteri, D., Kovács-Vajna, Z. M. & Cantatore, E. Ultra-high gain diffusion-driven organic transistor. Nat. Commun. 7, 10550 (2016).

- Lenz, T. et al. Downscaling and Charge Transport in Nanostructured Ferroelectric Memory Diodes Fabricated by Solution Micromolding. Adv. Funct. Mater. 26, 5111–5119 (2016).

- Chen, Z. et al. High-Performance Ambipolar Diketopyrrolopyrrole-Thieno[3,2- b] thiophene Copolymer Field-Effect Transistors with Balanced Hole and Electron Mobilities. Adv. Mater. 24, 647–652 (2012).

- Khim, D. et al. Control of Ambipolar and Unipolar Transport in Organic Transistors by Selective Inkjet-Printed Chemical Doping for High Performance Complementary Circuits. Adv. Funct. Mater. 24, 6252–6261 (2014).

- 41. Braun, S., Salaneck, W. R. & Fahlman, M. Energy-level alignment at organic/metal and organic/organic interfaces. Adv. Mater. 21, 1450–1472 (2009).

- 42. Pernstich, K. P. et al. Threshold Voltage Shift in Organic Field Effect Transistors by Dipole-Monolayers on the Gate Insulator. J. Appl. Phys. 96, 6431 (2004)

- Torricelli, F., Ghittorelli, M., Colalongo, L. & Kovacs-Vajna, Z. M. Single-transistor method for the extraction of the contact and channel resistances in organic field-effect transistors. *Appl. Phys. Lett.* 104, 1–5 (2014).

- 44. Kobayashi, S. *et al.* Control of carrier density by self-assembled monolayers in organic field-effect transistors. *Nat. Mater.* **3**, 317–322 (2004).

- 45. Myny, K. *et al.* An 8-Bit, 40-Instructions-Per-Second Organic Microprocessor on Plastic Foil. *IEEE J. Solid-State Circuits* 47, 284–291 (2012).

- Ishida, K. et al. User Customizable Logic Paper (UCLP) with Sea-of Transmission-Gates (SOTG) of 2-V organic CMOS and ink-jet printed interconnects. IEEE J. Solid-State Circuits 46, 285–292 (2011).

- Li, X. et al. Programmable polymer light emitting transistors with ferroelectric polarization-enhanced channel current and light emission. Org. Electron. 13, 1742–1749 (2012).

# Acknowledgements

This research was supported by the MSIP (Ministry of Science, ICT and Future Planning), Korea, under the "ICT Consilience Creative Program" (IITP-R0346-16-1007) supervised by the IITP (Institute for Information & communications Technology Promotion). Author F. T. acknowledges funding from the Fondazione Cariplo e Regione Lombardia, project "New Opportunities and ways towards ERC" (NOW-ERC), no. 2014- 2256.

# **Author Contributions**

H.Y. designed and fabricated the transistor devices and circuits. H.Y. collected data. F.T. and M.G. performed the 2D numerical simulations. H.L. performed UPS experiments. H.Y., J.K., H.L., F.T. and M.G. analyzed data. G.G. and E.S. contributed to the performance analysis. All authors wrote the manuscript.

# **Additional Information**

Supplementary information accompanies this paper at http://www.nature.com/srep

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Yoo, H. *et al.* Reconfigurable Complementary Logic Circuits with Ambipolar Organic Transistors. *Sci. Rep.* **6**, 35585; doi: 10.1038/srep35585 (2016).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

© The Author(s) 2016