# Reducing Design Time to Develop Portable Image Processing Applications Using SDAccel

Uttam kumar Elango

CE-MS-2017-11

## Abstract

Interventional X-Ray (iXR) systems require specialized accelerators and advanced image processing techniques to reduce noise levels in the output image produced by machine components and low radiation doses. Currently, the image processing chains are implemented on PCs which have an average life cycle of 3 to 5 years whereas, the life cycle of X-Ray systems is expected to be up to 20 or 25 years. This mismatch introduces the need to change the PC architecture during the lifetime of the medical system, for which the image processing chain has to be redeveloped and retested increasing the maintenance costs. A solution to the life cycle management challenge is to use Field Programmable Gate Arrays (FPGAs) since certain FPGAs are considered to have longer life cycles than PCs. However, the process of programming and integrating the FPGA hardware into existing systems is challenging for software developers. Moreover, portability needs to be ensured to reduce the development time when moving to different compute devices for improved functionality or performance. This thesis investigates the possibility to reduce the design time for FPGAs while maintaining portability. To achieve this, the SDAccel framework and a workflow combining Halide (a Domain Specific Language) and SDAccel were proposed and analyzed. The results indicate that high-performance image processing solutions can be implemented on FPGAs in a fraction of the time it takes to create manual RTL designs, while maintaining functional and performance portability.

# Reducing Design Time to Develop Portable Image Processing Implementations on FPGAs

### THESIS

submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

$\mathrm{in}$

#### EMBEDDED SYSTEMS

by

Uttam kumar Elango born in Akividu, India

Embedded Systems Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# Reducing Design Time to Develop Portable Image Processing Implementations on FPGAs

#### by Uttam kumar Elango

#### Abstract

Interventional X-Ray (iXR) systems require specialized accelerators and advanced image processing techniques to reduce noise levels in the output image produced by machine components and low radiation doses. Currently, the image processing chains are implemented on PCs which have an average life cycle of 3 to 5 years whereas, the life cycle of X-Ray systems are expected to be up to 20 or 25 years. This mismatch introduces the need to change the PC architecture during the lifetime of the medical system, for which the image processing chain has to be redeveloped and retested increasing the maintenance costs.

A solution to the life cycle management challenge is to use FPGAs since certain FPGAs are considered to have longer life cycles than PCs. However, the process of programming and integrating the FPGA hardware into existing systems is challenging for software developers. Moreover, portability needs to be ensured to reduce the development time when moving to different compute devices for improved functionality or performance. This thesis investigates the possibility to reduce the design time for FPGAs while maintaining portability. To achieve this, the SDAccel framework and a workflow combining Halide (a Domain Specific Language) and SDAccel were proposed and analyzed. The results indicate that high-performance image processing solutions can be implemented on FPGAs in a fraction of the time it takes to create manual RTL designs, while maintaining functional and performance portability.

| Laboratory        | : | I I I I I I I I I I I I I I I I I I I        |

|-------------------|---|----------------------------------------------|

| Codenumber        | : | CE-MS-2017-11                                |

| Committee Members | : |                                              |

| Advisor:          |   | Dr. ir. Zaid Al-Ars, CE, TU Delft            |

| Member:           |   | Dr. ir. Rene van Leuken, CAS, TU Delft       |

| Member:           |   | ir. Steven van der Vlugt, Philips Healthcare |

| Member:           |   | ing. Rob de Jong, Philips Healthcare         |

Dedicated to:

My parents for their motivation and support My brother-in-law and sister for their helpful advice My friends in Netherlands and India for their help and support

# Contents

| List of Figures  | ix  |

|------------------|-----|

| List of Tables   | xi  |

| List of Acronyms | xiv |

| Acknowledgements | xv  |

| 1        | Intr | oduction 1                    |

|----------|------|-------------------------------|

|          | 1.1  | Context                       |

|          |      | 1.1.1 Philips healthcare      |

|          |      | 1.1.2 ALMARVI                 |

|          | 1.2  | Imaging system                |

|          | 1.3  | Problem discussion            |

| <b>2</b> | Bac  | kground 7                     |

|          | 2.1  | Hardware architectures        |

|          |      | 2.1.1 CPU                     |

|          |      | 2.1.2 GPU                     |

|          |      | 2.1.3 FPGA                    |

|          |      | 2.1.4 Memory architecture     |

|          |      | 2.1.5 Discussion              |

|          | 2.2  | Image processing              |

|          |      | 2.2.1 Imaging operations      |

|          |      | 2.2.2 Processing requirements |

|          |      | 2.2.3 Algorithm selection     |

| 3        | Soft | ware to Hardware 19           |

|          | 3.1  | Challenges                    |

|          | 3.2  | High level synthesis          |

|          | 3.3  | RTL generation                |

|          |      | 3.3.1 Scheduling              |

|          |      | 3.3.2 Allocation and binding  |

|          |      | 3.3.3 Controller synthesis    |

|          |      | 3.3.4 Optimizations           |

|          | 3.4  | Tools and techniques          |

|          | 3.5  | OpenCL                        |

|          |      | 3.5.1 Platform model          |

|          |      | 3.5.2 Memory model            |

|          |      | 3.5.3 Execution model         |

|   |      | 3.5.4          | Discussion                                           | 28         |

|---|------|----------------|------------------------------------------------------|------------|

|   | 3.6  | Domai          | n Specific Languages                                 | 29         |

|   |      | 3.6.1          | Halide                                               | 29         |

|   |      | 3.6.2          | Halide design philosophy                             | 30         |

|   | 3.7  | Relate         | d study                                              | 30         |

| 4 | Solı | ition w        | vorkflow                                             | 33         |

|   | 4.1  | SDAcc          | el                                                   | 33         |

|   |      | 4.1.1          | Memory mapping                                       | 33         |

|   |      | 4.1.2          | OCL region                                           | 34         |

|   |      | 4.1.3          | SDAccel design                                       | 34         |

|   | 4.2  | Halide         | on FPGA                                              | 35         |

|   | 4.3  |                | lows                                                 | 36         |

|   | 4.4  |                | tions and solutions                                  | 38         |

|   |      | 4.4.1          | SDAccel                                              | 38         |

|   |      | 4.4.2          | Halide                                               | 39         |

| 5 | Imn  | lement         | tation                                               | 41         |

| 0 | 5.1  |                | choices                                              | <b>4</b> 1 |

|   | 0.1  | 5.1.1          | GPU                                                  | 41         |

|   |      | 5.1.1<br>5.1.2 | Halide                                               | 43         |

|   |      | 5.1.2<br>5.1.3 | SDAccel                                              | 43         |

|   | 5.2  |                | bility                                               | 43<br>44   |

|   | 0.2  | 5.2.1          | Sobel kernel                                         | 44         |

|   |      | 5.2.1<br>5.2.2 | Gaussian kernel                                      | 44<br>45   |

|   | 5.3  | -              |                                                      | 43<br>47   |

|   | 5.3  |                |                                                      | 47<br>48   |

|   | 0.4  | 5.4.1          | Buffers                                              | 48<br>48   |

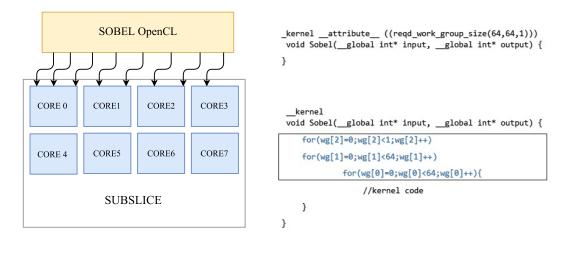

|   |      | 5.4.1<br>5.4.2 | Work group sizes                                     | 40<br>49   |

|   |      | 5.4.2<br>5.4.3 |                                                      | 49<br>50   |

|   |      | 5.4.3<br>5.4.4 | Memory partitioning                                  | 50<br>50   |

|   |      | 5.4.4<br>5.4.5 | Implementation                                       | 50<br>51   |

| 0 | D    | 1.             | -                                                    |            |

| 6 | Res  |                |                                                      | 55         |

|   | 6.1  |                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 55         |

|   | 6.2  |                | bility                                               | 55         |

|   |      | 6.2.1          | Parallelism                                          | 56         |

|   |      | 6.2.2          | Branching                                            | 58         |

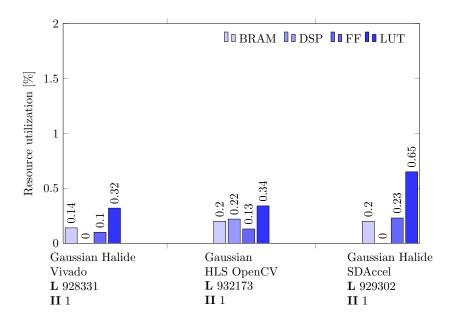

|   |      | 6.2.3          | Gaussian                                             | 58         |

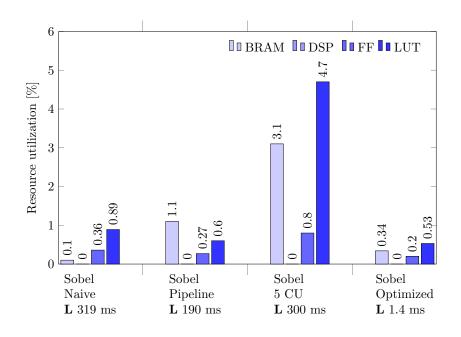

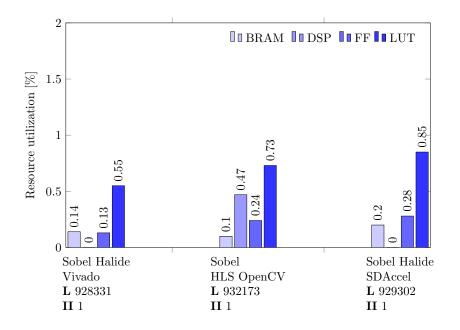

|   | 6.3  |                | -HLS                                                 | 59         |

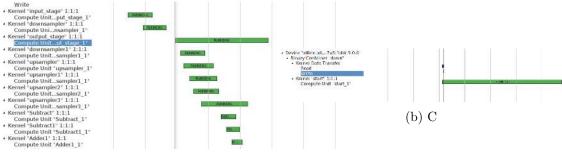

|   | 64   | MRA            |                                                      | 62         |

| <b>7</b> | Disc  | cussior | 1               |        |   |       |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 67 |

|----------|-------|---------|-----------------|--------|---|-------|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

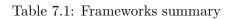

|          | 7.1   | Summ    | ary             |        |   |       |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 67 |

|          | 7.2   | Resear  | ch question re- | visite | d |       |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 67 |

|          |       | 7.2.1   | Requirement 1   |        |   |       |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 68 |

|          |       | 7.2.2   | Requirement 2   | 2      |   |       |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 68 |

|          |       | 7.2.3   | Requirement 3   | 8      |   | <br>• |  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 68 |

| 8        | Con   | clusio  | n               |        |   |       |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 71 |

| Bi       | bliog | raphy   |                 |        |   |       |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 76 |

# List of Figures

| 1.1 | Azurion Interventional X-ray system [1]                             | 3  |

|-----|---------------------------------------------------------------------|----|

| 1.2 | iXR – processing chain                                              | 3  |

| 2.1 | Memory architecture on Central Processing Unit (CPU) (Intel Nehalem |    |

|     | Quad-Core CPU) [4] $\ldots$                                         | 9  |

| 2.2 | Memory Architecture of Graphic Processing Units (GPUs) [5]          | 10 |

| 2.3 | Memory architecture on FPGAs [6]                                    | 11 |

| 2.4 | Comparison chart CPUs, GPUs, and FPGAs                              | 12 |

| 2.5 | (a) Point Operation (b) Window Operation (c) Global Operation       | 13 |

| 2.6 | Image Pyramids [12]                                                 | 15 |

| 2.7 | Gaussian and Laplacian pyramids [13]                                | 16 |

| 3.1 | Front-end of HLS                                                    | 22 |

| 3.2 | Hardware generation from RTL [12]                                   | 23 |

| 3.3 | SDKs and DSLs used for High Level Synthesis                         | 25 |

| 3.4 | OpenCL platform model[23]                                           | 26 |

| 3.5 | OpenCL memory model [23]                                            | 28 |

| 3.6 | Halide Framework                                                    | 29 |

| 4.1 | SDAccel environment [20]                                            | 33 |

| 4.2 | Xilinx-OpenCL memory mapping [31]                                   | 34 |

| 4.3 | Xilinx-OpenCL region [31]                                           | 35 |

| 4.4 | Halide compilation flow $[25]$                                      | 37 |

| 4.5 | Solution Workflow                                                   | 37 |

| 4.6 | Streaming process in the device side                                | 39 |

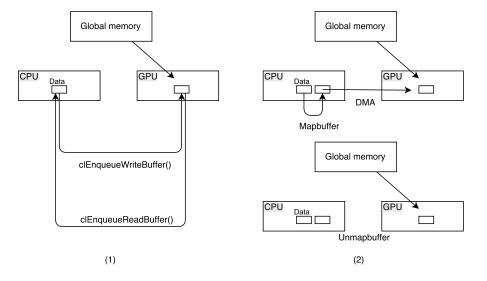

| 5.1 | OpenCL Data Transfer (1) Read/Write buffers (2) Map/Unmap           | 42 |

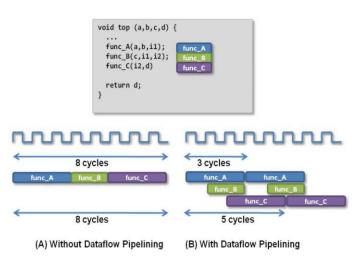

| 5.2 | Dataflow model [37]                                                 | 44 |

| 5.3 | Sobel multiple compute units                                        | 45 |

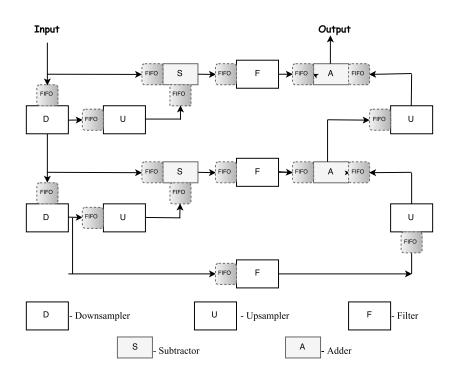

| 5.4 | MRA model                                                           | 48 |

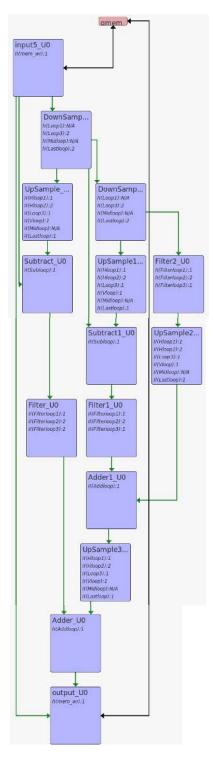

| 5.5 | Dataflow view generated by SDAccel                                  | 53 |

| 6.1 | Mapping of OpenCL on GPU and FPGA                                   | 57 |

| 6.2 | Sobel-SDAccel                                                       | 58 |

| 6.3 | Sobel on FPGA                                                       | 61 |

| 6.4 | Gaussian on FPGA                                                    | 62 |

| 6.5 | Timeline trace results                                              | 64 |

# List of Tables

| 2.1 | Features overview                                        |

|-----|----------------------------------------------------------|

| 2.2 | Classes of image processing algorithms                   |

| 4.1 | SDAccel Optimization Techniques                          |

| 5.1 | Workgroup sizes effect on resource usage                 |

| 6.1 | Device details                                           |

| 6.2 | Sobel Filter - Latency Estimates                         |

| 6.3 | Sobel Filter - Resource utilization                      |

| 6.4 | Gaussian Filter - Latency Estimates                      |

| 6.5 | Resource utilization on FPGA - Sobel                     |

| 6.6 | Resource utilization on FPGA - Gaussian                  |

| 6.7 | MRA C version - Resource utilization and Latency         |

| 6.8 | MRA OpenCL version - Resource utilization and Latency 65 |

| 7.1 | Frameworks summary 69                                    |

# List of Acronyms

#### **ALAP** As Late As Possible

- **ALMARVI** Algorithms, Design methods, and Many-Core Execution Platform for Low-Power Massive Data-Rate Video and Image Processing

- **API** Application Programming interface

- **ASAP** As Soon As Possible

**ASIC** Application Specific Integrated Circuit

**AST** Abstract Syntax Tree

**BRAM** Block Random Access Memory

CDFG Control/Data Flow Graph

- CFG Control Flow Graph

- **CLB** Configurable logic block

- **CPU** Central Processing Unit

**CT** Computed Tomography

CUDA Compute Unified Device Architecture

DFG Data Flow Graph

- **DRAM** Dynamic Random Access Memory

- **DSL** Domain Specific Language

- **DSP** Digital Signal Processor

EU Execution unit

- FIFO First in First Out

- FPGA Field Programmable Gate Array

- **FSM** Finite State Machine

- ${\bf GP}\,$  General Purpose

- GPU Graphic Processing Unit

- HDL Hardware Description Language

- HIPAcc Heterogeneous Image Processing Acceleration

**HLL** Higher Level Language **HLS** High Level Synthesis **IGT** Image Guided Therapy **ILP** Instruction Level Parallelism **IP** Intellectual Property **IR** Intermediate Representation iXR Interventional X-ray Systems LCM Life Cycle Management LUT Look-up Table MRA Multi Resolution Analysis **MRI** Magnetic Resonance Imaging NDRange N-dimensional range **OpenCL** Open Computing Language **OS** Operating System  ${\bf PC}\,$  Personal Computer **PCIe** Peripheral Component Interconnect Express QoR Quality of Results **RTL** Register Transfer Level **SDK** Software Development Kit **SIMD** Single Instruction Multiple Data **SM** Streaming Multiprocessor **SP** Streaming Processor SRAM Static Random Access Memory

VHDL Very High Speed Integrated Circuit Hardware Description Language

# Acknowledgements

This thesis marks the end of my master study programme at TU Delft. These past two years have been instrumental in my academic and personal growth. I would like to reflect on the people who have helped and supported me during this period.

First and foremost, I would like to thank my supervisor at the university, Zaid Al-Ars, for his guidance and support throughout my work. His door was always open for questions, and his advice helped me in making the right choices during my study.

This thesis was performed at Philips healthcare in Netherlands. My experience at Philips has been nothing short of amazing. I have been incredibly fortunate to have Steven van der Vlugt and Rob de Jong from Philips as my supervisors during my thesis work. I thank them for making me feel welcome and steering me in the right direction during my research. Their enthusiasm towards their work was inspiring. Rob's amazing insights and Steven's general advice helped me grow both personally and academically.

I would like to extend my gratitude to my colleagues Aries Thio Gunawan, Ruben Guerra Marin, Rachana Arun Kumar for their helpful advice and support. I thank my friends at TU Delft, for providing me the much-needed distraction during my thesis to blow off some steam.

Finally, I must express my profound gratitude to my family for providing me support and encouragement throughout my life without whom this accomplishment would not be possible.

Uttam kumar Elango Delft, The Netherlands Image processing, mainly digital image processing is finding numerous applications in several industrial and research domains. Processing an image requires performing complex operations that are expensive both in time and resource usage. Images represent a large data set, and many tasks require several operations to be performed on each pixel in the image. Furthermore, when real-time constraints are specified, they must be performed at live video rates. Such requirements demand careful selection of hardware architectures and programming techniques.

In the computing world, there exists a plethora of different devices such as Central Processing Units (CPUs), Graphic Processing Units (GPUs), Field Programmable Gate Arrays (FPGAs), Digital Signal Processors (DSPs) etc. Each device has its own set of advantages and disadvantages that the programmer has to leverage to obtain maximum performance. This brings a need to create a unifying specification that enables the programmer to write the code once, and use it everywhere. This is called functional portability and has seen decades of research. One key issue here is that even though programs run functionally correct on different architectures, it doesn't necessarily mean that they obtain the maximum achievable performance. User intervention is still required to ensure that the program is leveraging the device capabilities to the maximum extent possible. A dream scenario would be to develop the application once and execute it on different platforms at the maximum achievable performance, automatically.

In this work, the focus will be on reconfigurable architectures, particularly FPGAs. FPGAs are reconfigurable devices that contain several programmable logic blocks that can be customized to generate the required hardware. However, hardware generation on the FPGA fabric is quite difficult, in the sense that, the effort it takes to implement the design, verify and validate is quite complex when compared to its software counterpart. The skill set required for a hardware programmer is vastly different than a software programmer. This results in a steep learning curve for a general-purpose software programmer to move to hardware programmer. To address this issue, an abstraction layer is required that ensures that the programmer requires minimal (or ideally none) knowledge of the hardware, but is still able to perform hardware synthesis. As we achieve higher abstraction levels, we can also manage to unify CPU, GPU, and FPGA programming.

The focus of this thesis is to investigate the current state of tools that are available to abstract the low-level hardware details from the programmer, thereby facilitating ease of development on FPGAs. The rest of the report will describe the context within which the research will take place, provide background on the subject, and finally outline the implementation and results.

### 1.1 Context

This section will describe the context within which this thesis was written.

#### 1.1.1 Philips healthcare

Koninklijke Philips N.V. (Royal Philips Electronics of the Netherlands, commonly known as Philips) is a Dutch technology company headquartered in Amsterdam. It was founded in Eindhoven in 1891 by Gerald Philips and Frederik Philips [1]. Philips is organized into two divisions: Philips Consumer Lifestyle and Philips Healthcare. As the main division in the enterprise, Philips Healthcare focuses on improving people's lives through meaningful innovation in the healthcare industry. Some of the popular health care products are Interventional X-Ray Systems, Computed Tomography (CT)-scan, Ultrasound, Magnetic Resonance Imaging (MRI), and Clinical Management Systems. Philips brand line is "innovation and you" which highlights its mission to innovate while understanding people's needs. Philips Healthcare, in particular, saves millions of lives through its exceptional innovation and state of the art healthcare systems.

This work was performed in the Image Guided Therapy (IGT) department of Philips Healthcare at Best, the Netherlands, where the focus is on development of real-time applications for minimally invasive medical procedures.

#### 1.1.2 ALMARVI

Almarvi stands for: Algorithms, Design Methods, and Many-core Execution Platforms for Low-Power Massive Data-Rate Video and Image Processing. Almarvi is a European project with many different parties contributing deliverables worldwide. Philips Healthcare and TU Delft are also part of this project.

To reduce the overall system design cost, time-to-market, and to enable low-cost solutions for high volume markets, the Almarvi project was conceived [2]. Almarvi project focuses on: enabling cross domain re-use and interoperability for different product categories and application domains, facilitate predictable system and product properties, develop joint hardware-software techniques for resource and power management. The main goal of this thesis is to ease the programming effort for FPGAs and to ensure portability among different architectures which combines perfectly with the Almarvi mission statement: "to ease the programming of new technologies and cut production costs by reducing design time".

## 1.2 Imaging system

Fig. 1.1 shows an Interventional X-ray Systems (iXR) system designed at Philips. It generates high quality images at a fast rate with the help of advanced image processing techniques.

X-radiation, which is composed of X-rays, is a form of electromagnetic radiation. X-rays with high energies (> 10 keV) are called hard X-rays. These hard X-rays can

Figure 1.1: Azurion Interventional X-ray system [1]

penetrate the skin and are often used in medical radiography, like in the iXR medical X-ray systems.

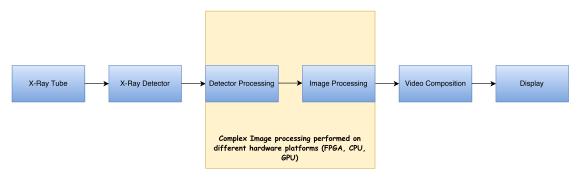

Figure 1.2: iXR – processing chain

Fig. 1.2 shows the iXR image processing chain. First, the X-ray tube generates the X-rays which fall on the patient lying on a detector plate. Based on the subjects X-ray absorption properties, a "shadow image" is formed on the detector plate. Some imperfections may exist during the capture of a raw X-ray image, but they can be removed by imaging algorithms. The detector processing block provides a dose control feedback loop for regulating the X-ray dose [3] and performs a minimal clean up of the raw images. Next, more advanced image processing algorithms are applied to improve the image quality, examples include noise reduction and contrast enhancement. After the image has been processed, it is streamed to the output to be viewed directly by the physician treating the patient. This video stream is either sent directly to an external monitor or to another PC which distributes the signal to different monitors. Both functional correctness and latency are crucial requirements for such an X-ray system. The physician needs to have timely feedback of the patient under study to avoid making potentially disastrous mistakes.

## 1.3 Problem discussion

Interventional X-Ray systems currently use PCs to implement the image processing pipelines. PCs are expected to have shorter life cycles (3 to 5 years) due to regular advancements in hardware architectures whereas X-Ray systems have an average life cycle of up to 20 or 25 years. Hence there is a need to redevelop and retest the imaging algorithms to target the next generation PCs during the life cycle of the medical system which increases the time to market and maintenance costs.

FPGAs are considered to be an attractive choice to address the Life Cycle Management (LCM) challenge since certain FPGAs have a much longer life cycle (15 years or more) than PC based platforms. They also offer deterministic performance benefits to satisfy real-time constraints. But to effectively use FPGAs, the designer has to be aware of low-level hardware details, which are unfamiliar to many application programmers. To ease the development process on FPGAs, research has focused on High Level Synthesis (HLS) tools, and several industries have come up with their own set of tools to bridge the gap between software and hardware synthesis. A common goal of these tools is to hide the low-level details from the developer. However, if software programs are directly mapped to hardware, then the generated design might not be the best model on FPGAs. Thus an efficient tool flow is required that could generate hardware with minimal knowledge of low-level implementation details.

Moreover, portability must be ensured among different platforms (CPU, GPU and FPGA) so that the same application can be used on other platforms, ideally without modifications. Providing separation between application and hardware will reduce redevelopment time and costs when using different computing platforms for improved functionality or performance.

From the above discussion, the following research question can be formulated,

#### Is it possible to generate hardware structures on FPGAs from higher level programming languages for image-processing algorithms, resulting in ease of development for programmers and ensuring portability among CPUs and GPUs?

To answer the above question the following sub-questions must be explored:

- What are the architectural differences between CPUs, GPUs, and FPGAs?

- What are the characteristics of image processing algorithms and what challenges are involved in porting these algorithms to FPGAs?

- What are the challenges involved in generating hardware from Higher Level Languages (HLLs)?

- What are the current tools available to achieve hardware generation on FPGAs from HLLs and do these tools result in an easier development cycle?

- What are the current research trends in obtaining portability across CPUs, GPUs and FPGAs?

Based on the above problems, we can formulate a set of global requirements for the project.

- A workflow in terms of tools and strategies needs to be developed. The output must be similar to the original working solution.

- The algorithm must be implemented once, and ideally be able to execute correctly on different accelerators with acceptable latency and throughput requirements. Since the domain is medical image processing, any changes to the algorithm itself might lead to undesirable outcomes.

- The workflow needs to ensure that complex hardware challenges are abstracted from the programmer and result in an easier development cycle.

This project aims to investigate tools and techniques available to quickly obtain hardware designs on Field Programmable Gate Arrays (FPGAs) for image processing algorithms while maintaining portability. Ideally, the work flow should be adaptable to generalpurpose tasks and should meet the requirements of the Philips use-case. To do this, it is necessary to look into the different computational platforms to understand the architectural requirements. This chapter starts with the analysis of different computational platforms namely Central Processing Units (CPUs), Graphic Processing Units (GPUs), and FPGAs. This is followed by analyzing the general characteristics of image-processing algorithms and selecting a suitable representation that emulates the Philips use-case.

# 2.1 Hardware architectures

We discussed that FPGAs might be a suitable platform to address the Life Cycle Management (LCM) challenge, but we also want the flexibility to move to other computational platforms like CPUs and GPUs with minimal development efforts. FPGAs are preferred since a custom-built hardware design will often have a higher throughput than its software counterpart which is a major factor in real-time applications. Secondly, several commonly used functions are available as Intellectual property (IP) cores which are highly optimized and can be readily integrated into existing designs alleviating design costs.

There is, of course, no "one platform fits all" solution available since all of them have very different capabilities and limitations. We will perform a short study to understand and compare these differences.

# 2.1.1 CPU

CPUs are the most well-known and widely used devices. The fundamental operation of CPUs is to execute a sequence of stored instructions. CPUs have grown from single-core to multi-core processors capable of exploiting parallelism both in data and instructions. They are capable of executing enormous amounts of different operations and tasks. A large unit is dedicated for managing and scheduling tasks which effectively optimizes performance bottlenecks such as branch prediction and instruction ordering. The development time on CPUs is relatively low. They can be targeted with a large range of programming languages making it easier to program.

## 2.1.2 GPU

GPUs are gaining popularity due to their ability to exploit massive parallelism in certain tasks. The capability of GPUs to be used as accelerators are being widely exploited in all

compute intensive applications. The advantages of using GPUs are attributed to its high memory bandwidth and a large number of programmable cores. Graphics processors are either integrated with CPU or placed separately with the ability to communicate via a Peripheral Component Interconnect Express (PCIe) bus. The development time on GPUs is also low, thanks to the introduction of Compute Unified Device Architecture (CUDA) and Open Computing Language (OpenCL) which provides a C-based programming environment for programming GPUs.

### 2.1.3 FPGA

CPUs and GPUs are off-the-shelf products whose architectures cannot be changed, whereas FPGAs are reconfigurable devices. FPGAs are based around a matrix of Configurable logic blocks (CLBs) connected via programmable interconnects. FPGAs can be programmed (and reprogrammed) to the desired application for functionality requirements after manufacturing. FPGAs are programmed using Hardware Description Languages (HDLs) like Very High Speed Integrated Circuit Hardware Description Language (VHDL) or Verilog which mandates knowledge of low-level hardware details. A synthesis, implementation and routing tool can translate a hardware design to digital logic that can be implemented in this array. Table 2.1 provides a comparative overview of the three hardware platforms.

|                 | CPU                                                     | GPU                                                                                | FPGA                                                              |  |  |  |  |

|-----------------|---------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| Computation     | Fixed Arithmetic Units<br>2 - 8 cores                   | Fixed Arithmetic Units<br>600 - 4000 cores                                         | User-configurable Logic                                           |  |  |  |  |

| Parallelization | MultiThreading (Pthreads/OpenMP)<br>Vector Instructions | Highly Parallel<br>Single Instruction Multiple Data (SIMD)                         | Pipeline Execution<br>Multiple hardware units                     |  |  |  |  |

| Arithmetic      | Versatile<br>Floating-point and Integers                | Faster than CPUs in certain operations single-precision $FP > double-precision FP$ | Integer and fixed-point work well<br>floating-point not advisable |  |  |  |  |

| Programmability | Easy to program<br>C,C++,Java etc.                      | Relatively easier to program<br>CUDA, OpenCL                                       | Complicated<br>HDLs-low-level details required                    |  |  |  |  |

| I/O             | Fixed I/O                                               | Fixed I/O                                                                          | user-configurable I/O                                             |  |  |  |  |

| Debugging       | Many tools available<br>Gdb, Valgrind etc.              | Relatively easier to debug than FPGAs<br>Intel Vtune amplifier, NVVP etc.          | Complicated                                                       |  |  |  |  |

| Upgrades        | Easy                                                    | Moderate                                                                           | Complicated                                                       |  |  |  |  |

Table 2.1: Features overview

#### 2.1.4 Memory architecture

In this part, we explore the memory subsystem of the different computational devices discussed above. In almost all platforms, at the top of the memory hierarchy, there are on-chip storage elements called registers which have the lowest read/write latency. Registers are usually used to store intermediate results of operations for fast access. The second layer is formed by cache memories which also provide low latency accesses. Caches are split into multiple hierarchies named as L1, L2, and L3 caches. Each level in the cache is progressively slower. Thus L2 cache has a higher access time than L1

cache. This is followed by the Dynamic Random Access Memory (DRAM) (also called main memory) which are optimized for capacity but have relatively slower access times. Finally, the last layer in the hierarchy is referred to as the secondary memory (also named hard disks) that can be used to store huge amounts of data but has high access latency. All the different memories except secondary memory are volatile memories (data is remove once the device powers off).

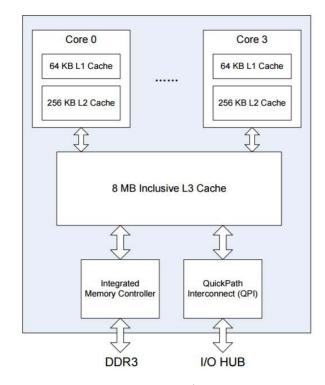

In CPUs, registers are located within the processing units. There are general-purpose registers that the programmer can use and special-purpose registers (program counter, status register etc.) that are internal to the CPU. Fig. 2.1 shows the typical memory organization of modern CPUs.

Figure 2.1: Memory architecture on CPU (Intel Nehalem Quad-Core CPU) [4]

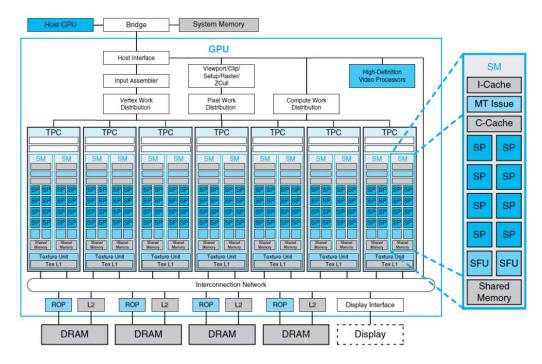

Fig. 2.2 shows the memory organization on GPUs. The global memory is shared by the entire GPU. It is used for communication among cores and also for communication with the host (typically CPUs). Transferring data to and from the global memory is the most time-consuming operation on the GPUs. The global memory is implemented on off-chip DRAM. The shared memory is local to each Streaming Multiprocessor (SM) and can be shared by all the Streaming Processor (SP) in that SM. The access latency for this memory is quite low, and they are usually implemented in Static Random Access Memories (SRAMs). The next level is the local or private memory, which is specific to a single SP core. They are part of the global memory and are used when the registers are not capable of holding the thread data (a phenomenon called as register spilling). To achieve better access latency, modern GPUs cache portions of the local memory on-chip. There are also two read-only memories (read-only for threads, CPU can read/write on these memories) named "constant memory" and "texture memory". Constant memory is usually used to fill data during compile time to reduce the amount of data transfer between the host and GPUs during program execution. On the other hand, texture memories exhibit two-dimensional locality (spatial locality) thereby aiding in transferring blocks of data for fast access. Both constant and texture memory can be cached on-chip.

Figure 2.2: Memory Architecture of GPUs [5]

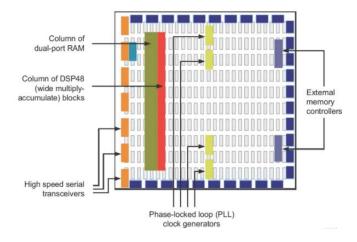

FPGAs are reconfigurable devices which the user can program to fit his application needs. On FPGAs, configurable logic blocks typically consists of Look-up Tables (LUTs) and Flip Flops (FFs). LUTs are made out of logic gates and can be used to store all possible outcomes of a particular function, thereby allowing fast access times. Memory modules on FPGAs are typically Block Random Access Memories (BRAMs) which are on-chip memory resources that can be configured for read or write accesses. Finally, there is the DRAM which is off-chip and can store relatively large amounts of data but has higher access latency.

Figure 2.3: Memory architecture on FPGAs [6]

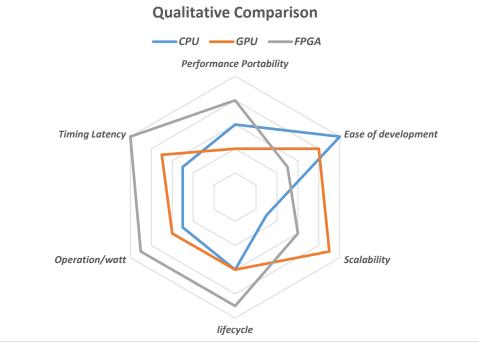

To make things clear, we will draw comparisons between the different platforms for some of the important metrics that will be considered throughout this work.

- *Performance portability*: This metric indicates the "performance maintainability" when the design is ported to a different device of the same kind.

- *Ease of development*: This metric indicates the development effort required to run applications on the platform.

- *Life cycle*: This metric indicates the average life cycle of the hardware platforms (average time before the product become obsolete).

- *Scalability*: This metric indicates whether adding more resources will increase the performance.

- *Energy efficiency*: This metric indicates the number of operations (GFLOPs) performed for one watt of power consumption (Operations/Watt). [7].

- *Timing latency*: This metric indicates the capability of achieving deterministic timing requirements [8].

Figure 2.4: Comparison chart CPUs, GPUs, and FPGAs

Fig. 2.4 shows the comparison between the parameters discussed above for CPUs, GPUs and FPGAs. All comparisons are made with devices in the same price range. Please note that the farther the line is from the center, the better the device performs on that metric (e.g. FPGAs provide better timing latency followed by GPUs and then CPUs).

#### 2.1.5 Discussion

The study performed in the previous sections shows that memory architecture is different for all the three platforms. E.g. GPUs provide shared memory (also known as scratchpad memory) local to an SM, which is unavailable on CPUs. Thus in CPUs, local variables (in registers) spill to caches which have higher access latency than shared memory in GPUs [9]. FPGAs, on the other hand, are user configurable. This means that the programmer can generate hardware structures and decide on the memory hierarchy. Multiple hardware structures can be created with memory elements between them, and data can be directly transferred without the need for off-chip memory. Understanding memory access patterns to effectively leverage temporal (once a memory word has been accessed, it is likely to be re accessed) or spatial locality (once a memory word has been accessed, nearby words are likely to be accessed) will lead to achieving good performances. Therefore either the programmer or the tool must be capable of identifying such patterns.

## 2.2 Image processing

In order to generate a good representation of an algorithm that is suitable for medical imaging and one that is representative for the Philips use-case, we need to understand the characteristics of image processing algorithms. In this section we will look at some of the characteristics, and classes of image processing algorithms.

#### 2.2.1 Imaging operations

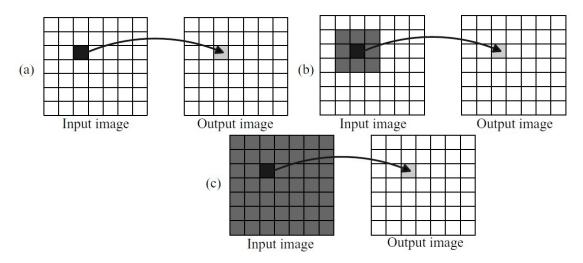

Medical image processing, and image processing in general, is mostly performed by applying a number of processing steps to an image, altering the contents of the image to the needs of the user. Image processing operations can be classified into three types: *point, window* and *global* operations. Fig. 2.5 shows how these operations are performed on an image.

- Point operations: In these type of operations, the output pixel value depends only on the value of the corresponding input pixel (e.g. Threshold operations).

- Window operations: In global operations, each pixel in the output image is produced by sliding an  $N \times M$  window over the input image and computing an operation according to the input pixels under the window and the chosen window operator (e.g. Convolution filters).

- Global operations: In these operations, the output value of a pixel is dependent on the entire input image (e.g. Fast Fourier Transform (FFT) operations).

Figure 2.5: (a) Point Operation (b) Window Operation (c) Global Operation

There are also two types of image processing characterizations: spatial and temporal. Spatial characterization involves analyzing a single image (e.g. edge detection), whereas temporal characterization involves analyzing a series of images taken at different time instances (e.g. motion detection). The above discussed operations (point, window and global) are commonly used in these characterizations.

| Classes            | Processing                                                               | Example                 |  |  |

|--------------------|--------------------------------------------------------------------------|-------------------------|--|--|

| Image Scaling      | Algorithms are capable of resizing the image either by adding new pixels | Bi-linear interpolation |  |  |

| image scamig       | (upsample) between existing pixels or by removing pixels (downsample).   | Di-miear merpolation    |  |  |

|                    | These algorithms alter the colour information in the image or            |                         |  |  |

| Colour conversion  | enhance the colour information.                                          | Grayscale conversion    |  |  |

|                    | Point based operations                                                   |                         |  |  |

|                    | These algorithms are used to remove unwanted artifacts from the image    |                         |  |  |

| Filters            | resulting in smoothed, brightened image                                  | Gaussian blur           |  |  |

|                    | Window based operations.                                                 |                         |  |  |

|                    | These algorithms are used to detect and isolate various desired          |                         |  |  |

| Feature extraction | portions of an image.                                                    | Canny edge detection    |  |  |

|                    | Window based operations.                                                 |                         |  |  |

Table 2.2 summarizes the common classes of image processing algorithms that will be used to represent our use-case.

Table 2.2: Classes of image processing algorithms

#### 2.2.2 Processing requirements

Since images are made out of pixels, it naturally lends itself to massive parallelism since each pixel can be processed independently. But when part or entire image (window and global) is used to compute an output pixel, we need to analyze the algorithm to exploit parallelism efficiently.

To adhere to real-time processing constraints, image data must be processed at high data rates. On CPUs and GPUs due to large memory sizes, data can be processed in frames at very high speeds. On FPGAs, due to resource constraints, data is usually processed as streams. This means that data is processed as soon as it is received, rather than waiting for the entire input image to be buffered before processing starts. Computations on a stream of data are performed by kernels, which are functions that operate on all elements of the input stream. Since stream elements are independent, kernels can operate in parallel exploiting data-level parallelism [10]. Moreover, in medical imaging, multiple algorithms are used to form the image processing chain. These can be implemented as multiple kernels running in parallel exploiting task level parallelism. A kernel can potentially take an arbitrary number of inputs and produce one or more output streams. Thus, generating the hardware in a streaming fashion would be beneficial to achieve a high throughput. Making the algorithm to work in a streaming fashion is a challenge since data needs to be buffered (memory considerations), and data order must be maintained.

#### 2.2.3 Algorithm selection

To obtain a good representation of the image processing domain, we chose to implement Sobel and Gaussian filters. These filters are selected owing to their widespread use in the imaging domain. The operations performed by these filters can be extrapolated to other commonly used imaging filters thereby giving us a heuristic representation.

Sobel filter is a convolution filter that uses two kernels to calculate intensity changes in the horizontal and vertical direction. This information can be used to detect edges in the input image. The Gaussian filter is a low-pass filter that uses a single kernel to blur an image which reduces the noise in the input image. These two filters will serve as a good base case for our analysis of the tools and will help us understand portability challenges.

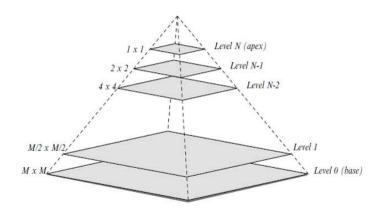

To obtain a good representation of a medical imaging algorithm, we looked at some of the commercial grade algorithms. First, most of the operations used in the algorithms are frame-based or pixel based. Since there are no global operations performed, the parallelization requirements on the workload are reduced because the entire image need not be buffered for the processing to start. Second, the image processing pipelines are often implemented in a pyramid fashion. A gray-scale image is used as an input to the imaging system. This image is then scaled down in multiple stages. In each stage, the image size is reduced by a factor of 2, thereby enabling working with a smaller dataset. The lowest resolution is then used to reconstruct the image in a pyramid fashion.

This is similar to the Multi Resolution Analysis (MRA) used in popular literature [11]. MRA is a mathematical method that is based on working on a problem at different levels of resolution. This method is currently being used in signal detection applications, PDEs solving, computer vision and image processing.

Figure 2.6: Image Pyramids [12]

Fig. 2.6 illustrates the MRA concept. As shown in the figure, the method starts at the full resolution (called the base) and continues to create a more coarse-grained representation of the data set. In each level, the same computational operations can be applied, affecting a different relative region size. Since they have the structure of a pyramid, they are also called image pyramids when used in image processing applications. Some advantages of using image pyramids are: First, they reduce computational costs of various image operations because the operations can be applied to a smaller dataset rather than the complete image. Second, pyramids enable image features to interact locally at higher levels of the pyramid, even though the features are far apart in the original image. Third, this algorithm can generate sets of low pass and band-pass filtered images at a fraction of the cost of performing Fast Fourier Transforms [11].

In MRA, at the input stage, downsampling is performed to scale down the image. Since downsampling introduces aliasing effects, the image is sent through a low-pass filter. This operation can be represented by the formula shown in Eqn. 2.1 for (2-D image).  $G_0$  is the original image and  $G_N$  is the image at the top level of the pyramid.

$$G_l(i,j) = \sum_m \sum_n w(m,n) G_{l-1}(2i+m,2j+n) \quad (0 < l <= N)$$

(2.1)

The weighing function w(m,n) is called the "generating kernel". The above formula can be simply represented as a "reduce" equation since each stage is scaled down by a factor of two. Reduce is a function that performs filtering and correspondingly downsamples the image.

$$G(l) = \begin{cases} I_0 & \text{if } l = 0\\ Reduce[G_{l-1}] & \text{if } l > 0 \end{cases}$$

Since the weighing function resembles the gaussian density function, the decomposition phase is simply referred to as "Gaussian pyramid" in common literature.

A second operation "expand", is defined to be the inverse of reduce. It expands an image by interpolating sample values between the given values. Let  $G_{l,k}$  be the image obtained by applying "expand" to  $G_l$ , k times

$$G_{l,k} = Expand[G_{l,k-1}] \quad given \quad that \quad G_{l,0} = G_l \tag{2.2}$$

Note that the gaussian filter is a low-pass filter that removes the high frequency components at each successive level.

Bandpass images can be quite useful for image analysis. They can be obtained by subtracting each gaussian pyramid level from the next lower level in the pyramid. Because the resolutions are different, it is necessary to interpolate to expand the image (Expand operation can be used here). Since these operations resemble laplacian operators, they are named as "laplacian pyramid". The image pyramid is then constructed by repeated application of reduce and expand operations as shown in Fig. 2.7.

Figure 2.7: Gaussian and Laplacian pyramids [13]

Once we have the bandpass images from Laplacian pyramids, we can then use any filter to remove noise or extract information at different resolutions.

## Analysis

The first insight we develop as mentioned above is that all algorithms used in the image processing pipeline use window based operations. This makes "parallel capability" analysis relatively easier since the entire image need not be stored and operated on (like global operations). Second, we see that the different stages can operate in a streaming fashion. This would allow concurrent execution and improve the arithmetic intensity of the kernel, thereby increasing the throughput. FPGAs offer massively parallel hardware architectures which can achieve best results with data streaming and pipelining. Each computational kernel in the MRA algorithm can be converted to hardware modules and laid out in parallel on FPGAs. The modules can then be interconnected by data streams to form a pipeline, through which data is streamed form one module to another. This structure can then effectively supply a continuous flow of output from a continuous delivery of input data achieving high throughout and low latency. As discussed previously, designing hardware is time consuming and resource intensive. Moreover a completely different approach than traditional software programming is required, which introduces a steep learning curve for software programmers. This chapter deals with the challenges of moving to higher level languages [14] followed by a study in the current state of tools to help with our research.

# 3.1 Challenges

Today computing systems are designed as a mix of hardware and software. Computeintensive and real-time problems are offloaded to hardware (Field Programmable Gate Arrays (FPGAs) or Application Specific Integrated Circuits (ASICs)) for speed and "timing predictability" advantages. Using Higher Level Languages (HLLs) for both architectures simplifies the work, but there are several challenges in moving to higher layers of abstraction for hardware programming. The following lists some of the challenges.

- Concurrency

- Algorithms developed using HLLs are traditionally sequential. Concurrency can be exposed in higher-level languages through the use of so called "pragmas" that help the compiler in optimizing the code effectively. Even with these features, the programmer has to analyze the code carefully to understand where to place the pragmas.

- Datatypes

- The base types in HLLs allow a minimum of one or more bytes (integer is usually 4 bytes) to be stored in memory. This is in contrast to hardware where single bit manipulations are performed frequently.

- Timing

- The ability to specify detailed timing (clock cycles) is another fundamental requirement in hardware. Applications that should work real-time are usually implemented directly in hardware, and can lead to unwanted effects if timing requirements are not met. This is something that cannot be explicitly manipulated in HLLs.

- Communication

- As discussed in Section 2.1, memory architectures of various platforms are quite different. When it comes to hardware design, the programmer can use

various techniques to build effective communication channels. In software programming, the programmer is faced with a limited set of interfaces.

- Multiple design choices

- Every operation on hardware can be implemented in a variety of ways. E.g. multiplication on hardware can be implemented using DSP blocks (or) LUT and FF pairs. It all depends on trade-offs between area, cost and performance. Therefore, the translation process for hardware is more complicated than software.

# 3.2 High level synthesis

Elaborate research has led to the development of several tools that abstract the hardware and ease the development process on FPGAs [15][16][17]. The process of generating hardware from HLLs is termed as high-level synthesis in common literature.

High-level synthesis has been under research for many decades, and major vendors have come up with their own set of tools to achieve High Level Synthesis (HLS). This is an important direction of research since HLS will improve designed productivity and will make the use of FPGA technology viable for software programmers [12]. Since these tools predominately target FPGAs, let us look at some important requirements that must be satisfied for hardware generation on FPGAs [18].

- The implemented algorithm must use the resources properly. If the pipelined operations are not "speed matched", then the slowest operation will dominate the execution time. This is analogous to the problem of load balancing in a parallel computing model where, if a single thread operates on a large amount of data, then the other threads (in many applications) have to wait for its completion.

- Using appropriate precision for representing data allows a proportional increase in parallelism and hence performance. Moreover alternatives to perform floating point operations must be developed since these operations are costly in terms of area, time, and power.

- Timing is very important in FPGA designs (real-time processing) and timing constraints are to be considered as hard requirements.

# 3.3 RTL generation

This section briefly explains the HLS process for hardware generation.

The first step is identical to the traditional software flow model. It involves the compilation stage that performs common lexical and syntactic analysis that generates an Intermediate Representation (IR) which is an Abstract Syntax Tree (AST) that represents the source code. Several optimizations are applied to the IR for optimal FPGA mapping. IR is usually a Control/Data Flow Graph (CDFG) which is formed by combining a Control Flow Graph (CFG) and Data Flow Graph (DFG). CFG indicates the

flow of control between basic blocks which are defined as a sequence of instructions which have a single entry point and which are executed until the end with a single exit point. If data dependencies exist between basic blocks then such dependencies are represented in a data flow graph.

The next step is the synthesis stage. The Register Transfer Level (RTL) design specifies the exact timing, and moreover data and operations are mapped to concrete hardware units. To implement the final digital system, HLS has to solve the following tasks:

### 3.3.1 Scheduling

In this step, all operations of the input CDFG are mapped to control steps. A schedule will be generated such that all the data and control dependencies are not violated and performance constraints are satisfied. Since scheduling determines the operation sequence, it affects the degree of concurrency of the resulting design. All operations that map to the same control step are executed in parallel thereby exploiting Instruction Level Parallelism (ILP). Different types of scheduling algorithms (As Soon As Possible (ASAP), As Late As Possible (ALAP), list scheduling) are used based on different requirements such as high performance or low resource usage.

## 3.3.2 Allocation and binding

After scheduling, hardware resources are bound to operations. Allocation determines the type and number of hardware resources for a given design. In the binding stage, the different operations in the application are mapped to individual cores from technology libraries. Optimizations on the number of hardware resources and registers required to execute the functions are performed. E.g., arithmetic units (Adder, multiplier) can be shared if two operations are not executed in the same clock cycle. One trade-off to note here is that even though resource sharing may reduce area usage, it may introduce delays (due to the usage of multiplexers) and increase the number of interconnects. HLS tools can be guided by programmer to customize resource allocation and binding to fit the user needs.

### 3.3.3 Controller synthesis

This step involves the derivation of the controller that sequences the design and controls the functional and storage units in the datapath. Finite State Machines (FSMs) are used as a basis to implement controllers for the design. First, the controller selection (single or hierarchical controllers) and the number of FSMs required is selected. Next, the controller generation stage decides whether to implement the FSM as a Moore or Mealy machine. Finally, the controller is implemented with registers holding the current state and combinational logic to generate the next state based on the machine model.

### 3.3.4 Optimizations

To obtain an optimal design, the programmer needs to expose high-levels of fine-grained as well as coarse-grained parallelism. The programmer can expose parallelism by understanding the underlying architecture and carefully exposing concurrent execution possibilities, but the idea is to allow the compiler to automatically find optimizations and apply them to generate effective hardware. Some of them are constant propagation, constant folding, loop transformations like unrolling, tiling, fusion, distribution, and strip-mining. Fig. 3.1 illustrates the process for RTL generation.

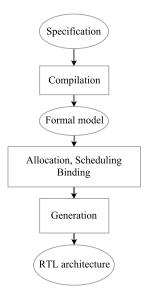

Figure 3.1: Front-end of HLS

After the RTL has been generated, the next phase is obtaining the bitstream to be uploaded on the FPGA. Fig. 3.2 shows the backend process. The first step performs lower-level synthesis. This results in a graph representation of hardware components such as gates and connecting signals called the netlist. The next step maps the netlist to hardware resources on FPGAs. Finally the hardware units are connected using the configurable routing resources in the "placement and routing stage". All the component and connection information is stored in a bitstream file which can be used to configure the FPGAs.

The separation of the synthesis process into frontend and backend can be attributed to easy generalization of frontend synthesis, whereas backend synthesis is bound to the technology. Frontend can be easily adapted to a different design environment, but backend has a short life cycle, because technologies change frequently.

## **3.4** Tools and techniques

We already discussed the various challenges involved in going from software to hardware. Extensive research has been done to address these challenges and many tools and frame-

Figure 3.2: Hardware generation from RTL [12]

works have emerged in the market. In this section we will discuss and compare some of these tools to select suitable frameworks for our study.

The Altera OpenCL Software Development Kits (SDKs) [19] delivers a complete development to deployment solution for software programmers to design FPGA hardware using OpenCL language. To enable easy integration, the subsystem design is packaged into an OpenCL Board Support Package (BSP) and distributed along with the hardware. The SDK enables software emulation to verify the functionality of the design and also contains profiling tools for analyzing and debugging the design.

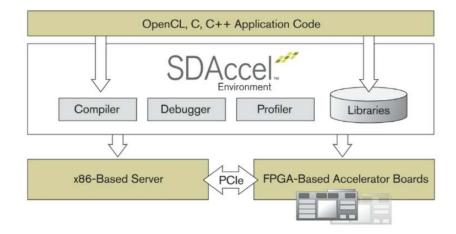

SDAccel [20] is a Xilinx framework that can accept OpenCL/C/C++ as input languages. This is also a complete development to deployment environment for hardware designs. We will discuss the framework in detail in Chapter 4.

Vivado HLS [21] is a Xilinx tool that accepts C/C++/System C as input languages to obtain hardware designs. It supports arbitrary-precision and fixed-point data-types using Xilinx libraries which is an advantage since the bit-width of compute variables can be customized resulting in reduced resource usages.

LegUP [16] is an open source tool developed at the university of toronto. LegUP accepts C programs as inputs, with constraints specified in a Tcl file. The tool can operate in two modes: pure hardware and hybrid. In hardware mode the input program is synthesized to a hardware circuit. In the hybrid mode, the program is synthesized, to target heterogeneous systems with a processor and an accelerator.

HIPAcc [12] provides a C++ based embedded DSL for the image processing domain. Several primitives are provided to implement imaging operations. The framework uses the clang/LLVM compiler infrastructure to generate an Abstract Syntax Tree (AST) that is operated on to produce a host code for managing kernels and device code for specific architectures (e.g CUDA, OpenCL). Recently, support for FPGAs was extended using the Vivado-HLS framework.

Halide [22] is also an image-processing DSL. It adopts a functional style description of image processing algorithms. The main feature of Halide is its separation between algorithm and schedule which will be discussed in detail in Section 3.6. They can target several architectures and recently, Halide was extended to support FPGA using the Vivado-HLS tool.

Table 3.3 summarizes the main features of the SDKs and Domain Specific Languages (DSLs) discussed above. Since exposing concurrency in the program is a fundamental requirement of HLS, these frameworks approach the problem in two ways. They either add parallel constructs to the programming language thereby forcing the programmer to expose concurrency or contain sophisticated compilers that automatically identify parallelizable functions in the source code. To enable working with fixed-point data these HLS tools provide features to specify the bit-width of variables. Design space exploration is also automatically performed based on tradeoffs specified by the user.

Although design tools start from a High-level language, they are rather a hardware description language than a high level tool. This is because of the additional features that are added to the language, that require hardware knowledge for effective utilization. Such HLS tools are given a low rating (-) for the level of abstraction they provide.

HLS tools that can automatically identify ILP and loop-level parallelism (loop unrolling, software pipelining) are marked with a high rating (++). A "+" rating is given for tools that cannot efficiently express parallelism in the user code.

Advanced coding transformations for efficient data-reuse can increase the degree of parallelism. Tools which are created for specific domains with highly optimized instructions are given a very high level of abstraction rating (+++).

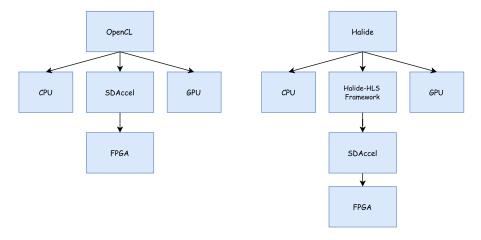

On studying the state of the art tools, we see that using Open Computing Language (OpenCL) as the base specification would be a good starting point because of its platform-independent model and active support by both industries and academia. Since OpenCL is a generic HLL, we also discussed about DSLs that can possibly perform better on our requirements. Halide and HIPAcc are two popular image processing DSLs. We chose to use Halide for this study because of its unique algorithm and schedule separation philosophy which will be discussed in the forthcoming sections.

# 3.5 OpenCL

The OpenCL standard is being developed by the Khronos Group industry consortium to address the challenges of programming multi-core and heterogeneous compute platforms. In 2013, Khronos released the OpenCL 2.0 specification in which a number of additional features such as nested parallelism, shared virtual spaces were added which simplify parallel application development and improves performance portability of applications. The OpenCL specification defines a single programming model that is supported by all hardware platforms conforming to the standard. The OpenCL specification is defined in three parts namely:

- Platform model

- Memory model

| SDK        | Open-<br>Source (O) /<br>Commercial<br>(C) | Input<br>Language | Features                                                                                                                                                | Portable | Abstraction<br>level |

|------------|--------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|

| Altera SDK | С                                          | OpenCL            | <ul> <li>Support on SoC<br/>Altera FPGA</li> <li>Streaming input<br/>to FPGA</li> <li>CPU emulation</li> <li>Targets data<br/>centers</li> </ul>        | Yes      | ++                   |

| SDAccel    | С                                          | C/C++/OpenCL      | <ul> <li>CPU emulation</li> <li>Fixed Point<br/>support (C<br/>workflow)</li> <li>Provided by<br/>Xilinx; Goals<br/>aligned with<br/>Philips</li> </ul> | Yes      | ++                   |

| Vivado HLS | С                                          | C/C++/SystemC     | <ul> <li>CPU emulation</li> <li>Fixed point<br/>support</li> <li>IP blocks have to<br/>be connected<br/>separately</li> </ul>                           | No       | +                    |

| LegUP      | Ο                                          | C/C++             | <ul> <li>Constraints<br/>specified in Tcl<br/>file</li> <li>Supports<br/>Pthreads/OpenMP</li> <li>No streaming<br/>support among<br/>kernels</li> </ul> | Yes      | -                    |

| DSL    |   |              |                                                                                                           |     |     |

|--------|---|--------------|-----------------------------------------------------------------------------------------------------------|-----|-----|

| HIPAcc | О | Embedded C++ | <ul> <li>Subset of C++<br/>constructs</li> <li>Code variants for<br/>CPU, GPU,<br/>FPGA</li> </ul>        | Yes | +++ |

| Halide | 0 | Embedded C++ | <ul> <li>Algorithm and<br/>Schedule<br/>Separation</li> <li>Active support<br/>and development</li> </ul> | Yes | +++ |

Figure 3.3: SDKs and DSLs used for High Level Synthesis

• Execution model

## 3.5.1 Platform model

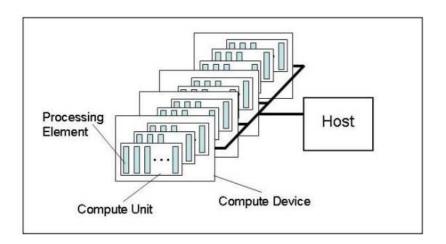

The platform model is defined by a combination of a host processor and one or more OpenCL compute devices. An OpenCL program always starts with a host processor. The host is responsible for managing the Operating System (OS), enabling drivers for all devices, setting up the global memory buffers, manage data transfers between host and device, and monitor the status of all the compute units in the system. The device is the hardware element on which the compute kernels of an OpenCL application are executed. An OpenCL kernel is often a compute-intensive function that the programmer wants to execute on an accelerator (OpenCL device). Each device is further divided into a set of compute units which are further subdivided into processing elements. A processing element is the fundamental computing engine in the compute unit, which is responsible for executing the operations of one work item. Fig. 3.4 illustrates the OpenCL platform model.

Figure 3.4: OpenCL platform model[23]

## 3.5.2 Memory model

As discussed previously, memory architecture varies widely between computing platforms. To overcome this challenge, OpenCL defines an abstract memory model that programmers can target when writing code, and that vendors can map to their actual memory.

### 3.5.2.1 Memory objects

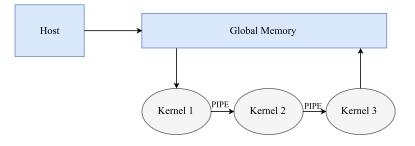

OpenCL defines three types of memory objects namely: buffers, images and pipes. The memory for these objects are allocated using the host Application Programming interface (API). Buffers and images act as data storage that can be accessed by the host, whereas pipes serve as First in First Out (FIFO) objects between kernels and cannot be accessed by host.

## • Buffers

With buffers, data elements are stored contiguously in memory. The OpenCL clCreateBuffer() API allocates space for a buffer and returns a memory object.

## • Images

- Images are multidimensional structures that are limited to a range of types. Image objects exist in OpenCL to offer access to "special function hardwares" on graphics processor that support highly efficient access to image data. Image objects are created using the clCreateImage() API.

- Pipes

- Pipes allow transfer of data between kernels. It organizes data in a FIFO structure. Pipes are created using the clCreatePipe() API.

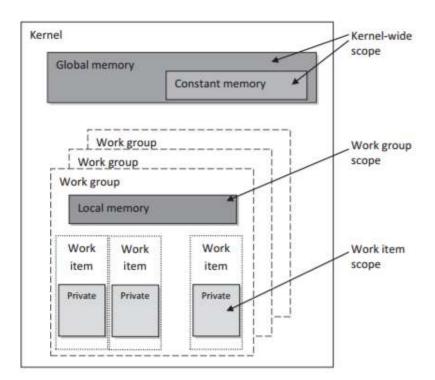

## 3.5.2.2 Memory regions

OpenCL divides device memory into four regions namely: Global memory, constant memory, Local memory and private memory.

- Global memory

- Data in Global memory is accessible by both the host and device units. Transfer of data between the host and device takes place from the global memory. Global memory usually has the longest access time.

### • Constant Memory

Constant memory is part of the global memory space that the host can readwrite whereas the device can only read. It is typically used to store values that are used by all work-items (constant values).

## • Local Memory

- Local memory is a memory that is shared between work-items in a work group. Accesses to local memory has much shorter latency and much higher bandwidth than global memory. Operations on local memory are unordered between work-items but synchronization can be achieved using barriers.

### • Private memory

Private memory is unique to a work-item. This memory is usually mapped to registers.

Fig. 3.5 illustrates the memory model

Figure 3.5: OpenCL memory model [23]

### 3.5.3 Execution model

The OpenCL execution model defines how kernels execute. A work-item is a unit of concurrent execution in OpenCL. Work-items map to processing elements and each work-item executes the kernel. When an OpenCL device begins executing a kernel, it provides intrinsic functions that allow the work-item to identify itself. OpenCL kernels execute within a predefined index space called N-dimensional range (NDRange) which can be one, two or three dimensional index space of work-items. The work-items are further divided into work groups. Work-items in a work group have access to a shared memory space as mentioned before.

Some key concepts in the OpenCL execution model are contexts, command queues and events. Contexts are used for managing all the objects specified for an accelerator device. Command-queues are the communication mechanism that the host uses to request action by a device. The host creates a command-queue for each device and submits commands to the proper command-queue. Events are used to specify dependencies between commands. Events also enable querying the execution status (Queued, submitted, ready, running, ended and complete) at any time.

### 3.5.4 Discussion

Since OpenCL is actively supported by many vendors and used commercially, it was chosen to accelerate the imaging algorithms on CPU, GPU, and FPGA. To achieve

hardware generation from FPGA using OpenCL we have commercial tools from Altera and Xilinx. Since Philips and Xilinx have aligned goals and agreed to provide support, SDAccel was chosen as the development environment for this study.

# 3.6 Domain Specific Languages

In the previous section, we discussed HLS which is usually approached from generic programming languages (C/C++). Even though they provide a good abstraction over Hardware Description Languages (HDLs), the programmer still has to be aware of the lower-level details.

To address the programming and portability challenges DSLs provide higher levels of abstraction by utilizing domain knowledge and platform specific knowledge. The optimizations performed by DSLs are more involved than the optimizations performed by generic HLLs because of their targeting specific domains. Thus DSLs could be an attractive solution to mitigate portability and programmability challenges.

### 3.6.1 Halide

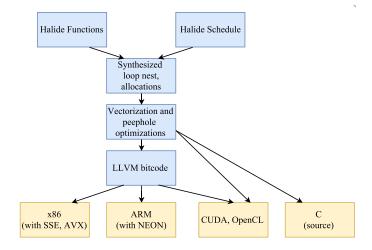

Halide [24] is an image-processing DSL designed to write high-performance image processing code on modern machines. Its front-end is coded in embedded C++ and targets a variety of hardware devices. Fig. 3.6 illustrates the compilation process for Halide language. Listing 3.1 shows a minimal example of a halide program. The algorithm

Figure 3.6: Halide Framework

description is coded in a functional style where images are pure functions that define the value at each point in terms of arithmetic operations. Different schedules can be explored to obtain optimal performance on target platforms.

```

1 Halide Algorithm:

2 blurx(x,y) = (in(x-1, y) +in(x, y) + in(x+1, y))/3;

3 blury(x,y) = (blurx(x, y-1) + blurx(x, y) + blurx(x, y+1))/3;

4 5 Halide Schedule:

6 blury.tile(x, y, xi, yi, 256, 32).vectorize(xi, 8).parallel(y);

7 blurx.comput_at(blury, x).store_at(blury,x).vectorize(x, 8);

```

Listing 3.1: Halide Description

## 3.6.2 Halide design philosophy

Writing efficient image processing implementation involves performing several platform specific optimizations on the algorithm which makes it complicated, unreadable and difficult to maintain.

Halide deals with this problem by separating the algorithm (what is computed) from the concerns of efficiently mapping to machine execution (decisions about storage and the ordering of computation) [22]. The choices of how to map an algorithm onto resources for a specific target platform is called the schedule.

This feature of separating the algorithm and schedule is interesting to our study because once the programmer has specified the algorithm, implemented it and tested the solution, a separate architecture expert can define the schedule without making modifications to the algorithm. In the medical domain, this will reduce the development cycle time thereby reducing development effort and costs. Design space exploration with different schedules can be performed quickly and easily with the assurance that the functional correctness of the program is not affected. Moreover, the Halide compiler can target different architectures ensuring performance portability. The above mentioned arguments provide compelling reasons to use Halide in our research.

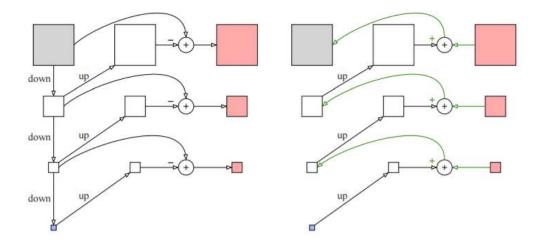

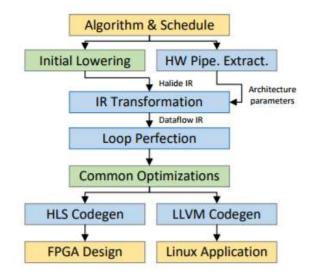

A parallel research was conducted at Philips healthcare focusing on generating hardware structures on FPGAs from Halide. They analyzed a study [25] which proposed and implemented a Halide-HLS framework for generating image processing pipelines for heterogeneous systems (CPU-FPGA).

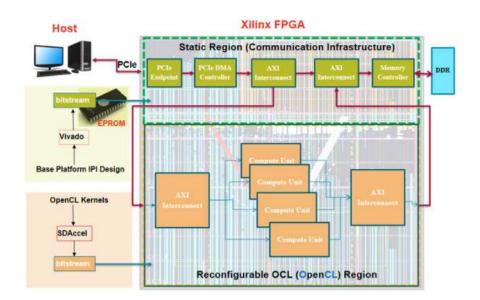

The research conducted at Philips looked at the limitations of the Halide-HLS framework and addressed some limitations. They used Vivado-HLS tool to synthesize the design on FPGA. In this study, we will look at adopting the framework for the SDAccel tool. The advantage of using SDAccel is the flexibility offered by the model to swap kernels dynamically on the OCL region allowing dynamic partial reconfiguration. Moreover, we will have a single entry point to design hardware, where as the Vivado generated Intellectual Property (IP) blocks have to be connected outside the tool.

# 3.7 Related study