Aalborg Universitet

## Reliability Improvement of Voltage Regulator Modules by a Virtual Series Voltage Source

Zhao, Zhaoyang: Zhou, Dao: Wang, Huai: Davari, Pooya: Blaabjerg, Frede

Published in: I E E E Transactions on Industrial Electronics

DOI (link to publication from Publisher): 10.1109/TIE.2022.3140525

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Zhao, Z., Zhou, D., Wang, H., Davari, P., & Blaabjerg, F. (2022). Reliability Improvement of Voltage Regulator Modules by a Virtual Series Voltage Source. *I E E E Transactions on Industrial Electronics*, *69*(12), 12641-12652. [9677949]. https://doi.org/10.1109/TIE.2022.3140525

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Reliability Improvement of Voltage Regulator Modules by a Virtual Series Voltage Source

Zhaoyang Zhao, Member, IEEE, Dao Zhou, Senior Member, IEEE, Huai Wang, Senior Member, IEEE, Pooya Davari, Senior Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—Output voltage deviation is a key performance index of voltage regulator modules (VRMs) with consecutive load transients. Usually, a large-capacity filter capacitor bank is used in VRMs to reduce the voltage deviation and stabilize the output voltage during transients. However, capacitors are one of the most vulnerable links in power electronic converters. For reliability reasons, it is essential to reduce the capacitance requirement while guaranteeing the transient performances of VRMs. Focusing on this, many efforts have been made to optimize the design of VRMs, where the transient auxiliary circuit-based scheme is a popular one. Unfortunately, there exists a large number of additional components in the existing auxiliary circuits. Considering this issue, this paper presents a virtual series voltage source (VSVS) based auxiliary circuit scheme, which has minimum component counts. By using a controlled coupled inductor as the VSVS, the proposed scheme enables VRMs to have a relatively small transient voltage overshoot and without needing large bulk capacitance. Moreover, considering different control schemes with the same designing aim, the number and the electro-thermal stress of critical components (e.g., capacitors) of VRMs are different, it is difficult to compare directly their advantages and disadvantages. Regarding this issue, this paper investigates the converter-level reliability of VRMs with different control schemes. Taking a 12-3.3-V VRM as a case study, the reliability benchmarking results illustrate that the proposed scheme can significantly improve the reliability of VRMs.

Index Terms—Voltage regulator module (VRM), auxiliary circuit, reliability benchmarking, transient performance.

#### I. INTRODUCTION

VOLTAGE regulator modules (VRMs) are being widely used to power modern electronic devices with continuously load transient events, such as central processing units (CPUs), digital signal processors (DSPs), microprocessors, and network-application integrated circuits [1], [2]. In order to store energy and stabilize the output voltage during load transients, a large-capacity filter capacitor bank is commonly used at the output side of VRMs [3]. Unfortunately, capacitors are one of the most vulnerable links in power electronic converters [4]–[6]. For reliability reasons, it is essential to reduce the capacitance

Manuscript received xxxx: revised xxxx: accepted xxxx.

Z. Zhao is with the School of Electrical Engineering, Zhengzhou University, Zhengzhou 450001, China (e-mail: zhaoyang.z@foxmail.com).

D. Zhou, H. Wang, P. Davari, and F. Blaabjerg are with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: zda@energy.aau.dk; hwa@energy.aau.dk; pda@energy.aau.dk; fbl@energy.aau.dk).

| TABLE I                                               |

|-------------------------------------------------------|

| ADDITIONAL COMPONENTS IN UNLOADING AUXILIARY CIRCUITS |

| Types    | Auxiliary circuits                            | Addition components                        |  |  |  |

|----------|-----------------------------------------------|--------------------------------------------|--|--|--|

| T        | gyrator circuit <sup>[2]</sup>                | $S \times 5, L \times 1, C \times 2$       |  |  |  |

| 1        | output-side buck-boost circuit <sup>[9]</sup> | $S \times 2, L \times 1, C \times 1$       |  |  |  |

|          | small auxiliary phase [10]                    | $S \times 2, L \times 1$                   |  |  |  |

| II       | buck-boost circuit <sup>[7],[11]</sup>        | $S \times 1, L \times 1, D \times 1$       |  |  |  |

|          | resonant circuit <sup>[12]</sup>              | $S \times 2, L \times 2, C \times 1$       |  |  |  |

| III      | parallel-inductor circuit <sup>[13]</sup>     | $S \times 4, L \times 1, R \times 1$       |  |  |  |

|          | parallel-coupled-inductor circuit [14]        | $S \times 3$ , $D \times 1$ , $R \times 1$ |  |  |  |

|          | series-coupled-inductor circuit [15]          | $S \times 2$                               |  |  |  |

| Proposed | virtual series voltage source                 | $S \times 1$                               |  |  |  |

Note: S-switch, L-inductor, D-diode, C-capacitor, R-resistor.

requirement while guaranteeing the steady-state and transient performances of VRMs.

Voltage deviation including the voltage overshoot and undershoot is a key performance index of VRMs, where voltage overshoot has been widely concerned in popular low-duty-cycle conversion applications (e.g.,  $12 V_{dc} \rightarrow 3.3 V_{dc}$ ) [7]. From the perspective of control strategy, a traditional linear control, such as proportional-integral (PI) control, could achieve the system's steady-state performance well. However, a large-capacity filter capacitor bank is required to reduce the voltage overshoot due to its inferior transient performance [7]. Although the advanced nonlinear control, e.g., time-optimal control (TOC), could push the transient performance of a converter near to its physical limit, undesired large voltage overshoots during unloading transients still dominate the capacitance requirement [8].

On the basis of the TOC scheme, some auxiliary circuits consisting of auxiliary switches, auxiliary inductors, etc., have been presented to further reduce the capacitance requirement while suppressing the transient voltage overshoot of VRMs [2], [9]–[15]. In terms of connection style, they can be divided into three types, i.e., the shunt-output style (Type I), bridge-connection style (Type II), and inductance-switching style (Type III), as summarized in Table I. These schemes could efficiently reduce the transient voltage overshoot of VRMs, thereby reducing the capacitance requirement. However, the number of additional auxiliary components is relatively high. Considering this issue, this paper proposes a virtual series voltage source (VSVS) based auxiliary circuit scheme, which has minimum component counts, as shown in Table I.

On the other hand, although the proposed VSVS scheme can reduce the capacitance requirement, it may bring new reliability risks due to the use of an additional power switch. It is essential to conduct the reliability performance benchmarking of the proposed VSVS scheme (using additional power switches and a small volume of capacitance) with traditional schemes (using a large volume of capacitance). Recently, many efforts have been made to investigate the reliability of power electronic converters, and the mission profile-based method is the state-of-the-art one [16]. Considering actual mission profiles of converters, the lifetime of capacitors in adjustable speed drives, wind power converters, and metro traction drives are investigated in [17]–[19], respectively. Similarly, the reliability of power semiconductor switches in some converters has been evaluated by using the same mission profile-based methods [20]–[22]. Furthermore, based on the reliability analysis of discrete components or modules, the converter- or system-level reliability can be investigated using a reliability block diagram [23]–[25].

The above-mentioned reliability analysis methods provide a reference for lifetime evaluation and reliability-oriented design of power converters. However, it is not suitable to apply these methods in VRMs with frequent loading transients (the loading step frequency is usually larger than 1 kHz [26]). Because of the sampling frequency of mission profiles in traditional schemes is usually smaller than 1 Hz (the sampling rate is 1 hour in [17]), which easily results in missing important transient information. Although Zhao *et al.* investigated the reliability of capacitors in VRMs [27], in which transient stresses have been considered. However, there is a lack of research efforts focusing on the converter-level reliability evaluation of VRMs with frequent loading transients.

To overcome the above-mentioned limitations, this paper proposes a VSVS based auxiliary circuit scheme and conducts the reliability performance benchmarking with traditional TOC and PI schemes. The main contributions are given as follows.

- A VSVS based auxiliary circuit scheme is proposed to improve the reliability while guaranteeing the performance of VRMs. Comparing with the existing auxiliary circuit-based schemes, the proposed scheme has minimum component counts.

- Investigate the converter-level reliability of the proposed VSVS scheme and conduct its performance benchmarking with traditional PI and TOC schemes. Here, the effect of transient stress on capacitors is considered, in order to improve the evaluation accuracy.

The rest of this paper is organized as follows. Section II presents the VSVS scheme and a case study for reliability benchmarking is introduced. Section III describes the electro-thermal model, lifetime and cumulative damage models. Section IV presents the matchmaking results. Finally, the conclusion is drawn in Section V.

## II. PROPOSED VSVS SCHEME AND THE DESCRIPTION OF A CASE STUDY

#### A. Proposed VSVS Scheme

#### 1) Circuit Topology

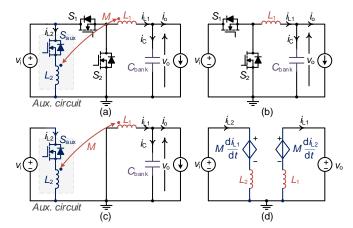

Fig. 1(a) shows the topology of the proposed VSVS scheme. A coupled inductor  $L_1$  is used as the output inductor, and another coupled inductor  $L_2$  is connected with the input source  $v_i$  by an auxiliary MOSFET  $S_{aux}$ . The coupling coefficient  $\sigma$  is calculated as  $\sigma = M/\sqrt{L_1L_2}$ , where *M* represent the mutual inductance. During steady state and loading transients, the auxiliary switch  $S_{aux}$  is disabled, then the converter works with a large inductance  $L_1$ , and a classical TOC control method is used [11]. The

Fig. 1. Topology of the proposed VSVS scheme. (a) Proposed circuit topology. (b) Equivalent circuit during steady-state and loading transient. (c) Equivalent circuit during unloading transient. (d) Equivalent circuit of controlled source during unloading transient.

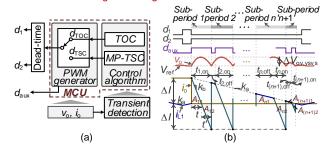

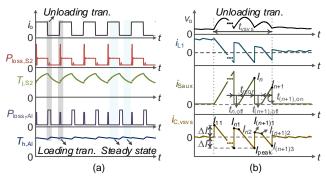

Fig. 2. Block diagram and unloading transient waveforms of the proposed scheme. (a) Block diagram. (b) Unloading transient waveforms.

equivalent circuit is shown in Fig. 1(b).

During unloading transients,  $S_1$  turns OFF and  $S_2$  turns ON. The auxiliary circuit is enabled, as shown in Fig. 1(c). When  $S_{aux}$  turns ON, the coupled inductor works as a virtual series voltage source. The equivalent circuit of the converter is shown in Fig. 1(d). Based on Kirchhoff's circuit law, the slew rate of inductor current  $i_{L1}$  is

$$k_{\rm b} = \left| di_{\rm L1} / dt \right| = \left( v_{\rm o} + M v_{\rm i} / L_2 \right) / \left( L_1 - M^2 / L_2 \right)$$

(1)

where  $v_0$  is the output voltage. Assuming the slew rate of the inductor current is  $k_a$  when  $S_{aux}$  is disabled (i.e., classical TOC scheme), we have

$$k_{\rm a} = v_{\rm o} / L_{\rm I} \,. \tag{2}$$

From (1) and (2), it is easily found that  $k_b >> k_a$ , which means that the inductor current decreases much faster when  $S_{aux}$  turns ON.

#### 2) Control Strategy

Fig. 2(a) shows the block diagram of the proposed VSVS scheme, where  $d_1$ ,  $d_2$ ,  $d_{aux}$  represent the driving signals of  $S_1$ ,  $S_2$ , and  $S_{aux}$ . The control algorithms including the TOC strategy and a multi-period frame transient switching control (MP-TSC) strategy are implemented in a microcontroller unit (MCU). The TOC strategy is used for steady state and loading transients [11], the MP-TSC strategy is designed for unloading transients [15]. Notice that the transient detection circuit is implemented by an *RC* differential circuit and a comparator, as discussed in [15].

The transient event of the MP-TSC scheme for a negative load step (the step amplitude is  $\Delta I$ ) is shown in Fig. 2(b), where  $v_0$ ,  $i_{L1}$ ,  $i_0$  are the output voltage, inductor current, and load current, respectively. Using the capacitor-charge balance principle, the

Fig. 3. Reliability benchmarking procedure.

unloading transient event is divided into n+1 sub-periods. In each sub-period, the charge area equals the discharge area, i.e.,

$$\begin{cases} A_{11} = A_{12} = A_{n1} = A_{n2} \\ A_{(n+1)1} = A_{(n+1)2} \end{cases}, n \ge 2$$

(3)

where  $A_{11}-A_{(n+1)1}$ ,  $A_{12}-A_{(n+1)2}$  represent the charge area and discharge area in each sub-period, respectively. The MP-TSC strategy enables the former *n* sub-periods to have the same output voltage overshoot  $\Delta V_{\text{ov,vsvs}}$ , and the last one to have a smaller overshoot [15]. The system voltage overshoot is defined as  $\Delta V_{\text{ov,vsvs}}$ .

Taking Sub-period 1 as an example, it is easily found that  $i_{L1}$  decreases rapidly and much faster than that for the classical TOC scheme due to  $k_b \gg k_a$ , which results in the system having a smaller voltage overshoot  $\Delta V_{ov,vsvs}$ . In order to satisfy the capacitor charge balance (CCB) principle, the time period *t* should equal *t'*, i.e.,  $t = t' = \Delta I/k_b$ . Furthermore,  $\Delta V_{ov,vsvs}$  can be calculated using  $A_{11}$  and  $C_{bank}$ , i.e.,

$$\Delta V_{\text{ov,vsvs}} = A_{11}/C_{\text{bank}} = \Delta I \cdot t / (2C_{\text{bank}}) = \Delta I^2 / (2k_b C_{\text{bank}})$$

(4)

where  $C_{\text{bank}}$  represents the output capacitance [14].

Referring to Fig. 2(b), the turn-ON duration of Sub-period 1 is calculated as  $t_{1,on}=2t=2\Delta I/k_b$ . Furthermore, using the CCB principle, the turn-ON duration  $t_{n,on}$  and turn-OFF duration  $t_{n,off}$  of *n*-th sub-period are derived as

$$\begin{cases} t_{n,\text{on}} = 2\Delta I/k_{\text{b}} - x'_{n} \\ t_{n,\text{off}} = x_{n} + x'_{n} \end{cases}, n \ge 2$$

(5)

where  $x_n$  and  $x'_n$  represent the intermediate, which are detailed discussed in [15]. Similarly, the turn-ON duration  $t_{(n+1),on}$  and the turn-OFF duration  $t_{(n+1),off}$  of (n+1)-th sub-period can be derived in the same way.

Notice that a hybrid capacitor bank consisting of polymer aluminum electrolytic capacitors (Al-Caps) and multi-layer ceramic capacitors (MLC-Caps) is usually used at the output side of VRMs, in order to reduce the total equivalent series resistance (ESR) and equivalent series inductance (ESL).

Fig. 4. Unloading transient waveforms of the TOC and PI schemes (a) TOC scheme. (b) PI scheme.

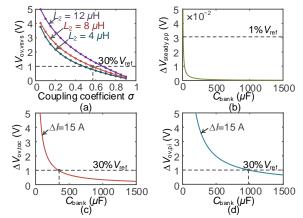

Fig. 5. The relationship between voltage overshoot, steady-state ripple, and circuit parameters. (a)  $\Delta V_{\text{ov,vsvs}}$  versus  $\sigma$  in the VSVS scheme. (b)  $\Delta V_{\text{steady,pp}}$  versus  $C_{\text{bank}}$  in the VSVS, TOC and PI schemes. (c)  $\Delta V_{\text{ov,toc}}$  versus  $C_{\text{bank}}$  in the TOC scheme. (d)  $\Delta V_{\text{ov,pi}}$  versus  $C_{\text{bank}}$  in the PI scheme.

Therefore, the ESR and ESL are not considered in (4).

## B. Case Study for the Reliability Benchmarking

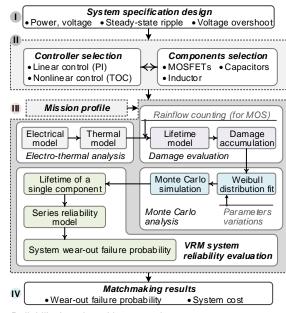

In order to evaluate the reliability of the proposed VSVS scheme, a classical VRM with a linear control scheme (i.e., PI scheme) and a nonlinear control scheme (i.e., TOC scheme) are chosen as benchmarks. Fig. 3 shows the reliability benchmarking procedure, where Steps I and II are introduced in this part. Steps III and IV are given in the next section.

### 1) Classical VRMs with TOC and PI Schemes

Fig. 4(a) and Fig. 4(b) show the transient waveforms of VRMs with the classical TOC and PI schemes. Here a traditional synchronous buck converter without auxiliary circuits is considered, the inductance is the same as that in Fig. 1, i.e.,  $L_1$ .

According to the derivation in [8], the voltage overshoot  $\Delta V_{\text{ov,toc}}$  of a TOC-controlled VRM is calculated as

$$\Delta V_{\rm ov,toc} = \Delta I^2 / (2k_{\rm a}C_{\rm bank})$$

(6)

where,  $k_a$  is the slew rate of the inductor current, as derived in (2). Because the duty cycle *d* of the PI scheme usually cannot reach 0 or 1 during transients, its transient period is relatively long, as shown in Fig. 4(b). Assuming an unloading transient occurs at  $t_0$ , and the inductor current reaches the new load current at *t'*. To simplify the analysis process, the transient period is defined as  $t_{pi} = t'-t_0$ . Assuming the mean value of *d* is  $d_{mean}$  during  $t_{pi}$ , it is approximated as

$$t_{\rm pi} = \Delta I L_{\rm l} / \left[ v_{\rm o} \left( 1 - d_{\rm mean} \right) - \left( v_{\rm i} - v_{\rm o} \right) d_{\rm mean} \right]$$

(7)

Then, the voltage overshoot  $\Delta V_{\rm ov,pi}$  is approximated as

$$\Delta V_{\rm ov,pi} = \Delta I t_{\rm pi} / (2C_{\rm bank})$$

(8)

The peak-to-peak value  $\Delta V_{\text{steady,pp}}$  of capacitor voltage ripple (i.e., the output voltage ripple) is calculated as

$$\Delta V_{\text{steady,pp}} = \left(v_{\text{i}} - v_{\text{o}}\right) v_{\text{o}} / \left(8v_{\text{i}}L_{1}f_{\text{s}}^{2}C_{\text{bank}}\right)$$

(9)

where  $f_s$  is the switching frequency.

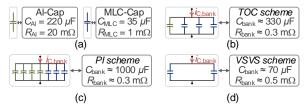

Fig. 6. Capacitor configuration for different schemes. (a) Parameters of a single Al-Cap and a single MLC-Cap. (b) Capacitor bank of the TOC scheme. (c) Capacitor bank of the PI scheme. (d) Capacitor bank of the VSVS scheme.

TABLE II SPECIFICATIONS AND PARAMETERS OF CAPACITORS Polymer Al-Cap [28]: MLC-Cap [29]:

| Domomotor            |                         | mile cup [27].          |

|----------------------|-------------------------|-------------------------|

| Parameter            | WCAP-PSLP875105144008   | GRM31CR60J107MEA8       |

| Dimension            | 43.6×5.8 mm             | 5.1×0.6 mm              |

| Capacity             | 220 µF/6.3 V            | 100µF/6.3 V, 35µF/3.3 V |

| ESR                  | 20 mΩ @ 100 kHz, 20 °C  | 1 mΩ @ 100 kHz, 25 °C   |

| Lifetime             | 2000 h @ +105 °C, 6.3 V | 1000 h @ +85 °C, 12.6 V |

| R <sub>ha</sub> [27] | 133.1 °C/W              | 22.9 °C/W               |

| $\tau_{\rm ha}$ [27] | 83.9 s                  | 0.14 s                  |

#### 2) Circuit Parameters Design

A 12–3.3-V VRM is chosen as a case study, the main circuit parameters are  $v_i = 12$  V,  $v_o = 3.3$  V, f = 100 kHz, steady-state inductance  $L_1 = 10 \ \mu$ H. Assuming a 70- $\mu$ F capacitor bank is selected in the proposed VSVS scheme. Using (5), Fig. 5(a) shows the relationship between  $\Delta V_{\text{ov,vsvs}}$  and  $\sigma$ . Here, three different coupled inductances are chosen as exam0825ples, i.e.,  $L_2$  equals to 4  $\mu$ H, 8  $\mu$ H, and 12  $\mu$ H, respectively. For a 15 A unloading transient, our design aims are  $\Delta V_{\text{steady,pp}} \leq 1\% V_{\text{ref}}$  and  $\Delta V_{\text{ov,vsvs}} \leq 30\% V_{\text{ref}}$ . According to the calculation results in Fig. 5(a),  $L_2$ , M can be designed as 4  $\mu$ H and 3  $\mu$ H, respectively. Moreover, the steady-state ripple also meets the design aim in this case, as shown in Fig. 5(b).

For comparison, a TOC scheme and a PI scheme with the same steady-state and transient performance indexes are designed. Using (6) and (8), Figs. 5(c) and 5(d) show the relationship between capacitance and the voltage overshoot  $\Delta V_{ov}$  for TOC - and PI-controlled VRMs. Here, the mean duty cycle of PI-controlled VRM during unloading transients is assumed as 0.2. According to the calculated results in Fig. 5,  $C_{\text{bank}}$  for the TOC and PI schemes can be designed as 330  $\mu$ F and 1000  $\mu$ F, respectively. The design results illustrate that the proposed VSVS scheme can enable the converter to have the same voltage overshoot when using a small capacitance, which can reduce the capacitance requirement.

#### 3) Simulation and Experimental Verifications

In order to verify the effectiveness of the proposed VSVS scheme, a converter is carried out in the power electronics simulator (PSIM) simulation environment. With the same design aim, Fig. 6 shows the capacitor configurations of the proposed VSVS scheme, TOC scheme, and PI scheme. Here, two types of different capacitors are considered. The detailed capacitor parameters are listed in Table II. Notice that polymer Al-Caps are used in priority to reduce the number of employed capacitors. In Fig. (6),  $C_{Al}$ ,  $R_{Al}$  represent the capacitance and ESR of a single Al-Cap.  $R_{MLC}$  denote the capacitance and ESR of a single MLC-Cap.  $R_{bank}$  is the total ESR of a capacitor bank.  $i_{C,bank}$  represents the current of capacitor banks. In the simulation, the parasitic parameters of inductors and MOSFETs are also

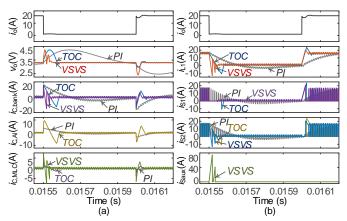

Fig. 7. Simulated response for VRMs with a 15-A repetitive load transient. (a) Output voltage and capacitor current. (b) Current of MOSFETs and  $L_1$ .

considered. Referring to the datasheet of AUIRF1324 [30], the on-state resistance  $R_{ds}$  of MOSFETs is 1.5 m $\Omega$ . The parasitic resistance of  $L_1$  (i.e., steady-state inductance) and  $L_2$  are about 13.2 m $\Omega$  and 5.3 m $\Omega$ , respectively.

Fig. 7 shows VRMs' transient response to a repetitive load transient of 15 A, where  $i_{C,bank}$ ,  $i_{C,A1}$  and  $i_{C,MLC}$  represent the current of capacitor banks, a single Al-Cap and a single MLC-Cap, respectively.  $i_{L1}$ ,  $i_{S1}$ ,  $i_{S2}$ ,  $i_{Saux}$  denote the current of  $L_1$ ,  $S_1$ ,  $S_2$ , and  $S_{aux}$ , respectively. Referring to (5) and the detailed design guideline of MP-TSC strategy in [15], the number of switching times of  $S_{aux}$  in the VSVS scheme is 2 during unloading transient. The turn-ON duration of Sub-period 1 is 18  $\mu$ s, the turn-OFF and turn-ON duration of Sub-period 2 are 5.6  $\mu$ s and 10  $\mu$ s, respectively. In the PI-controlled VRM, the proportion and integral coefficients are 0.3 and 0.008, respectively. Moreover, the control timing of TOC-controlled VRM are derived from [7].

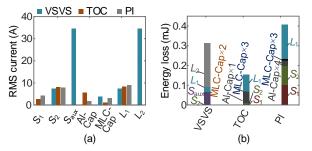

Referring to Fig. 7, it can be seen that the voltage deviation of these three schemes are less than 30% of the reference voltage, which satisfies the expected designing aim. Compared with the TOC and PI schemes, the proposed VSVS scheme has the shortest settling time during unloading transient. Moreover, Fig. 7 illustrates that the electrical stress of capacitors and MOSFETs in different schemes are different. According to the simulation results, Fig. 8(a) shows the root mean square (rms) current of key components during one time of unloading transient [15]. It can be seen that the rms current of  $S_2$  in the VSVS scheme is smaller than that in the TOC and PI schemes. And, the rms current of  $S_1$  equals to 0 due to it is turned OFF during unloading transient. However, the electrical stress of  $S_{aux}$  and MLC-Caps in the proposed scheme is relatively large.

Furthermore, Fig. 8(b) shows the energy loss of key components during one time of unloading transient [15]. It is found that the total energy loss of VSVS-based VRM is larger than that of the TOC-based VRM. Its energy loss is dominated by the loss of auxiliary circuits, i.e.,  $S_{aux}$  and  $L_2$ . Moreover, the most influential factor to the energy loss during unloading transient is the conduction loss of inductors. If the loss of inductors is not considered, the total energy loss of MOSFETs and capacitors in the proposed VSVS scheme is similar to that in the TOC scheme, and it is far smaller than that in the PI scheme.

Fig. 8. Simulated rms current and energy loss of key components during one time of unloading transient. (a) RMS current of single components. (b) Energy loss.

Fig. 9. Built experimental platform. (a) Experimental platform. (b) Photo of the used capacitor bank in the VSVS scheme. (b) Photo of the proposed auxiliary circuit in the VSVS scheme

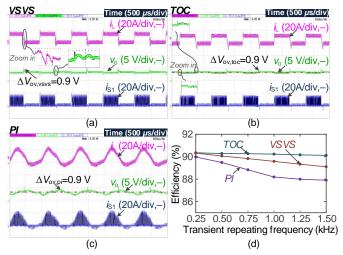

In order to further evaluate the proposed scheme, VRMs with the VSVS scheme as well as the traditional TOC and PI schemes are carried out in experiments, as shown in Fig. 9(a). Here, a microcontroller unit (MCU) TMS320F28377D is used to implement the digital control. The parameters of circuits and controllers are the same as those in simulation. The photos of the capacitor bank and auxiliary circuits of the proposed VSVS scheme are shown in Fig. 9(b) and Fig. 9(c), respectively. Using the MP-TSC strategy, the experimental result of the VSVS scheme is shown in Fig. 10(a). It can be seen that the voltage overshoot satisfies the expected designing aim, i.e.,  $\Delta V_{ov,vsvs}$  $<30\% V_{ref}$ . For comparison, Fig. 10(b) and Fig. 10(c) show the experimental waveforms of the conventional TOC and PI schemes. The experimental results illustrate that the proposed scheme can significantly reduce the capacitance requirement when compared with the TOC and PI schemes, in order to achieve the same voltage overshoot.

Fig. 10(d) shows the measured efficiency curves of the VSVS, TOC, and PI schemes, where the load transient repeating frequency  $f_{tr}$  is varied from 0.25 kHz to 1.5 kHz with a 50% load duty ratio. The results demonstrate that the efficiency of the proposed scheme is larger than that for the PI scheme, however, it is smaller than that for the TOC scheme. Usually, the efficiency of VRMs decreases as  $f_{tr}$  increases. And, the efficiency of the VSVS scheme is closer to that of the TOC scheme when the load transient frequency is lower. However, it is lower when  $f_{tr}$  is higher, which is similar to that in the existing auxiliary circuit-based schemes [9], [12].

The simulation and experimental results illustrate that the number and electrical stress of critical components (i.e., capacitors and MOSFETs) in different schemes are different. In order to conduct the reliability performance benchmarking of the proposed VSVS scheme with traditional schemes, a mission-profile-based reliability evaluation method is

Fig. 10. Experimental results. (a) Experimental waveforms of the proposed VSVS scheme. (b) Experimental waveforms of the TOC scheme. (c) Experimental waveforms of the PI scheme. (d) Efficiency measurement results under repetitive load transients.

introduced, as discussed in the following sections.

## III. ELECTRO-THERMAL MODELING AND ACCUMULATED DAMAGE ANALYSIS

MOSFETs and capacitors are the weakest links in power electronic converters. Generally, the wear-out failure of MOSFETs is mainly caused by the junction temperature fluctuation  $\Delta T_j$ , and the failure of capacitors is dominated by the rise of hot-spot temperature [16]. In this section, the electro-thermal modeling of MOSFETs and capacitors is introduced. Then, the accumulated damage is analyzed based on the mission profile of a VRM used in a data center.

## A. Electro-Thermal Modeling of Critical Components

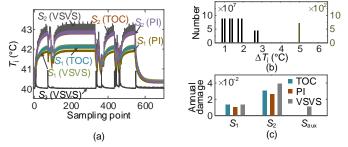

Taking the TOC-controlled VRM as an example, Fig. 11(a) shows the typical electro-thermal waveforms of a converter with consecutive load transients, which is a simplified simulation result of VRMs carried out in PSIM 2021a. Here,  $i_0$ ,  $P_{loss,S2}$ ,  $T_{j,S2}$ ,  $P_{loss,A1}$ , and  $T_{h,A1}$  represent the load current, power loss of  $S_2$ , junction temperature of  $S_2$ , power loss of Al-Caps, and host-spot temperature of Al-Caps, respectively.

Fig. 11(a) shows that there exist power loss steps on  $S_2$  during transients, however, the junction temperature fluctuation of  $S_2$  is mainly caused by load change [17]. Therefore, the effect of transient on the lifetime damage of  $S_2$  can be ignored. Similarly, the transient stress of  $S_1$  does not need to be considered. Notice that  $S_{aux}$  in the proposed topology is only enabled during transients, the power loss during transient should be calculated.

Different from that for junction temperature fluctuation, the rise of hot-spot temperature is mainly caused by the average power loss. Referring to Fig. 11(a), it can be seen that the power loss of Al-Caps during transients is significantly larger than that for steady state. Therefore, the power loss of capacitors is dominated by transient stress, which should be considered in the reliability evaluation.

## 1) Electrical Stress of MOSFETs and Capacitors

The power loss of MOSFETs is comprised of conduction loss and switching loss. The conduction loss  $P_{\text{con,S}}$  is calculated as

$$P_{\rm con,S} = I_{\rm S,rms}^2 R_{\rm ds} \tag{10}$$

Fig. 11. Electro-thermal waveforms. (a) Electro-thermal waveforms of a TOC-controlled VRM. (b) Electrical response waveform of the proposed VSVS scheme.

Fig. 12. Capacitor current of the TOC and PI schemes. (a) TOC scheme. (b) PI scheme.

where  $I_{S,rms}$  represent the rms currents of MOSFETs. During steady state, the rms current  $I_{S1,rms}$ ,  $I_{S2,rms}$  of  $S_1$  and  $S_2$  for these three schemes are the same, i.e.,

$$I_{\rm S1,rms} = \sqrt{di_{\rm o}^2}, I_{\rm S2,rms} = \sqrt{(1-d)i_{\rm o}^2}.$$

(11)

In the proposed VSVS scheme, the auxiliary switch  $S_{aux}$  is enabled during unloading transients. Referring to Fig. 11(b), the rms current  $I_{Saux,rms}$  of  $i_{Saux}$  is calculated as

$$I_{\text{Saux,rms}} = \sqrt{\sum_{n+1} \left( \frac{1}{3} \left( I_{n+1}^2 t_{(n+1),\text{on}} \right) / t_{\text{vsvs}} \right)}$$

(12)

where  $I_{n+1}$  represents the peak current, and  $t_{vsvs}$  is the transient period of the VSVS scheme.

In (10),  $R_{ds}$  is the on-state resistance of MOSFETs, which is dependent on the junction temperature  $T_{j}$ , i.e.,

$$R_{\rm ds}(T_{\rm j}) = R_{\rm ds,25^{\circ}C,max} (1 + \alpha/100)^{T_{\rm j}-25}.$$

(13)

Here,  $R_{ds,25 \, \text{°C,max}}$  denotes the maximum value of  $R_{ds}$  at 25 °C,  $\alpha$  is the temperature coefficient, which can be obtained from the datasheet [31].

The switching loss  $P_{sw,S}$  is calculated as

$$P_{\rm sw,S} = \left(E_{\rm on} + E_{\rm off}\right) f_{\rm s} \tag{13}$$

where  $E_{on}$  and  $E_{off}$  are the turn-on and turn-off energy loss of MOSFETs, which are detailed derived in [31].

Referring to Fig. 11(b), the rms value  $I_{C,rms,vsvs}$  of transient capacitor current  $i_{C,vsvs}$  in the proposed scheme is calculated as

$$I_{\rm C,rms,vsvs} = \sqrt{I_{\rm inter,(n+1)} + \sum_{n} I_{\rm inter,n}}$$

(15)

where, the intermediary variables  $I_{inter,n}$  and  $I_{inter,(n+1)}$  are

$$\begin{cases}

I_{\text{inter},n} = \frac{1}{3} \left( I_{n1}^{2} + I_{n2}^{2} + I_{n1} I_{n2} \right) t_{n,\text{off}} / t_{\text{vsvs}} \\

+ \frac{1}{3} \left( I_{n2}^{2} + I_{peak}^{2} + I_{n2} I_{peak} \right) t_{n,\text{on}} / t_{\text{vsvs}} \\

I_{\text{inter},(n+1)} = \frac{1}{3} \left( I_{(n+1)1}^{2} + I_{(n+1)2}^{2} + I_{(n+1)1} I_{(n+1)2} \right) t_{(n+1),\text{off}} / t_{\text{vsvs}} \\

+ \frac{1}{3} \left( I_{(n+1)2}^{2} + I_{(n+1)3}^{2} + I_{(n+1)2} I_{(n+1)3} \right) t_{(n+1),\text{on}} / t_{\text{vsvs}}

\end{cases}$$

(16)

In (16),  $I_{\text{peak}}$  is the peak current,  $I_{11}-I_{(n+1)3}$  are the current values at each switching instant, which are detailed derived in [14].

Fig. 13. Electro-thermal models of MOSFETs. (a) Thermal model of MOSFETs. (b) Electro-thermal waveforms of MOSFETs.

Fig. 14. Electro-thermal models of capacitors. (a) Thermal model of capacitors. (b) Electro-thermal waveforms of capacitors.

For comparison, Figs. 12(a) and 12(b) show the capacitor current in TOC and PI schemes. Referring to Fig. 12(a), the rms current  $I_{C,rms,toc}$  is calculated as

$$I_{\rm C,rms,toc} = \sqrt{1/3 \left( I_{\rm p}^2 + I_{\rm n}^2 + I_{\rm p} I_{\rm n} \right) t_{\rm toc,1} / t_{\rm toc} + 1/3 I_{\rm n}^2 t_{\rm toc,2} / t_{\rm toc}}$$

(17)

where the current peak values  $I_p$ ,  $I_n$ , and the transient durations  $t_{\text{toc},1}$  and  $t_{\text{toc},2}$  are detailed derived in [8]. Referring to Fig. 12(b), the rms current  $I_{\text{C,rms,pi}}$  is approximately calculated as

$$I_{\rm C,rms,pi} = \sqrt{\Delta I^2/3}$$

(18)

During steady state, the rms current  $I_{C,rms,s}$  of capacitor bank in these three schemes are the same, i.e.,

$$I_{\rm C,rms,s} = v_{\rm o} \left(1 - d\right) / \left(2\sqrt{3}f_{\rm s}L_{\rm 1}\right)$$

(19)

where  $f_s$  represents switching frequency.

Considering the current distribution of individual capacitor in capacitor banks, the rms current of the *k*-th capacitor is [27]

$$I_{C,rms,k} = I_{C,rms} \times \frac{1}{Z_k} / \sum_{i=1}^n \frac{1}{Z_n}$$

(20)

where  $I_{C,rms}$  represents the rms current of capacitor bank during steady state or transient,  $Z_k$  is the impedance of the *k*-th capacitor in the bank, and *n* is the number of capacitors. Using (19), the power loss of capacitors is calculated as

$$P_{\mathrm{C,rms},k} = I_{\mathrm{C,rms},k}^2 \mathrm{ESR}_k.$$

(21)

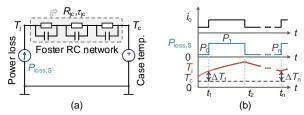

## 2) Thermal Stress of MOSFETs

Fig. 13(a) shows the typical thermal model of MOSFETs, where  $T_j$  and  $T_c$  represent the junction temperature and case temperature, respectively [23]. Usually, a high-order Foster network can be implied as a first-order network by means of curve fitting [25]. Here, the total equivalent thermal resistance and thermal time constant from the junction  $(T_j)$  to case  $(T_c)$  are defined as  $R_{jc}$  and  $\tau_{jc}$ , respectively.

Ignoring the power loss during transients, Fig. 13(b) shows the detailed electro-thermal response waveforms of MOSFETs, where  $P_{\text{loss},S}$  represents the power loss. According to the thermal model in Fig. 13(a), the junction temperature fluctuation  $\Delta T_n$  can be calculated by interaction as

$$\Delta T_n = \Delta T_{n-1} e^{-(t_n - t_{n-1})/\tau_{jc}} + P_n R_{jc} \left( 1 - e^{-(t_n - t_{n-1})/\tau_{jc}} \right)$$

(22)

Fig. 15. Mission profile of a VRM in a data center. (a) Daily ambient temperature. (b) Loading profile of a VRM in a specified period.

Fig. 16. Temperature profile, junction temperature fluctuation, and annual damage of MOSFETs. (a) Temperature profile in the specified period. (b) Statistical junction temperature fluctuation of  $S_2$  in the TOC scheme. (c) Annual damage.

where  $\Delta T_{n-1}$  is the previous temperature,  $P_n$  represent the power loss [25].

#### 3) Thermal Stress of Capacitors

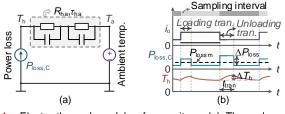

Fig. 14(a) shows the typical thermal model of capacitors, where  $T_{\rm h}$  and  $T_{\rm a}$  represent the hotspot temperature and ambient temperature, respectively [27].  $R_{\rm ha}$  and  $\tau_{\rm ha}$  are the total equivalent thermal resistance and thermal time constant from  $T_{\rm h}$  to  $T_{\rm a}$ , respectively. Fig. 14(b) shows the electro-thermal response waveforms of capacitors during two sampling intervals. It is easily found that the power loss during transients is larger than that for steady state.

Taking the unloading transient interval as a case study, the hotspot temperature fluctuation caused by step loss  $\Delta P_{\text{loss}}$  is calculated as

$$\Delta T_{\rm h} = \Delta P_{\rm loss} R_{\rm ha} \left( 1 - e^{-t_{\rm tran}/\tau_{\rm ha}} \right) \tag{23}$$

where  $t_{ran}$  is the transient duration. Referring to Fig. 14(b),  $T_h$  during one sampling interval is approximately calculated as

$$T_{\rm h} = T_{\rm a} + P_{\rm lossm} R_{\rm ha} + 0.5\Delta T_{\rm h}$$

(24)

where  $P_{\text{lossm}}$  is the mean loss of one sampling interval. The analysis in [27] demonstrates that  $T_{\text{h}}$  and  $P_{\text{lossm}}$  can be calculated using the mean value of one or multiple loading sampling intervals, the results are the same. Usually,  $\tau_{\text{ha}}$  is larger than the transient duration, i.e.,  $\tau_{\text{ha}} >> t_{\text{ran}}$ , then the hotspot temperature fluctuation  $\Delta T_{\text{h}}$  can be ignored.  $T_{\text{h}}$  can be approximated as  $T_{\text{h}} = T_{\text{a}} + P_{\text{lossm}} R_{\text{ha}}$ .

### B. Accumulated Damage Analysis

#### 1) Description of the Mission Profile

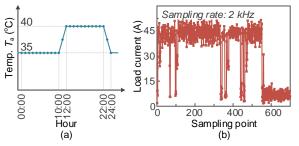

Taking a VRM used in data centers as a case study, Fig. 15(a) shows the daily ambient temperature, where the sample rate is one hour [32]. The loading profile of a node component in data centers is shown in Fig. 15(b), where the sampling rate is 2 kHz [26], [27].

#### 2) Static Annual Damage of MOSFETs

As shown in Fig. 15(a), the temperature of a data center is usually constant. Assuming the case temperature (i.e., ambient temperature  $T_a$ ) of a VRM is 40 °C, Fig. 16(a) shows the simulated temperature profile during the specified period, where the circuit parameters are same as that in Fig. 7. The simulation environment is PSIM 2021a. The type of MOSFETs is AUIRF1324, its  $R_{jc}$  and  $\tau_{jc}$  are 1.031 °C/W and 0.00107s, respectively [30]. Referring to the simulation results, it is found that the junction temperature of  $S_2$  is larger than that of  $S_1$  due to its relatively large electrical stress.

According to the simulation results in Fig. 16(a), the short-term junction temperature fluctuation of MOSFETs (caused by loading power fluctuation) can be counted with the help of a Rainflow counting algorithm [16]. Referring to the typical temperature profile shown in Fig. 16(a), it is found that the ambient temperature is changed 2 times in one day (the change amplitude is 5 °C). For simplification,  $\Delta T_i$  caused by ambient temperature fluctuation is defined as 5 °C (2 times every day). Assuming the temperature profile and loading profile are repeated every 24 h and 0.35 s, respectively, the long-time-scale temperature fluctuation (caused by ambient temperature fluctuation) and the short-time-scale temperature fluctuation (caused by loading power fluctuation) can be counted. Taking  $S_2$ in the TOC scheme as an example, Fig. 16(b) shows the statistical results of  $\Delta T_i$  for 1-year operation. Similarly,  $\Delta T_i$  of MOSFETs in other schemes can be obtained using the same method. Although damage consumption caused bv small-amplitude  $\Delta T_i$  is relatively small, it has a non-negligible effect on component aging [33] [34]. In this case study, the temperature fluctuation larger than 0.5  $^{\circ}$ C is considered.

Furthermore, Fig. 16(c) shows the annual damage of MOSFETs, which are obtained based on the Coffin-Manson reliability model and Miner's rule [23], [24], i.e.,

$$N_k = a \times \left(\Delta T_{j,k}\right)^{-b}, D_{\text{MOS}} = \sum_k n_k / N_k$$

(25)

where,  $N_k$ ,  $\Delta T_{j,k}$ , and  $D_{MOS}$  represent the cycle-to-failure, thermal stress and accumulated damage, respectively.  $n_k$  is the number of cycles with the thermal stress  $\Delta T_{j,k}$ . *a* and *b* represent the scaling factor and exponential factor, which can be identified by fitting the experimental data of accelerated stress tests. According to the fitting results in [35], *a* and *b* are  $5 \times 10^{11}$  and 5.3, respectively.

Referring to Fig. 16(c), it is found that the damage consumption of  $S_2$  is largest than  $S_1$ , due to its electro-thermal stress is relatively large in low-voltage high-current applications, i.e., low duty-cycle converters. The damage consumption of MOSFETs in the proposed scheme is slightly larger than that for TOC and PI schemes, the converter-level reliability needs to be further considered in order to evaluate the proposed scheme. 3) Static Annual Damage of Capacitors

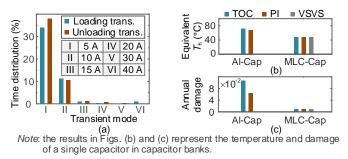

In the foregoing analysis, the hotspot temperature is calculated using the sampling interval as a unit. For simplification, the loading profile is divided into six typical modes based on the step amplitudes of load current, i.e., Mode

Fig. 17. Transient-mode distribution, equivalent hotspot temperature and annual damage of capacitors. (a) Transient-mode distribution. (b) Equivalent hotspot temperature. (c) Annual damage.

I-Mode VI. The step amplitudes are 5 A, 10 A, 15 A, 20 A, 30 A, and 40 A, respectively. Assuming the loading profile is repeated every 0.35 s, the time distribution of different modes is shown in Fig. 17(a). Moreover, the long-term temperature profile is considered in the reliability evaluation processes. Referring to Fig. 17(a), the ambient temperature can be divided into three typical levels, i.e., 35 °C, 37.5 °C, and 40 °C. Assuming the temperature profile is repeated every 1 day, durations are account for 42%, 8%, and 50%, respectively.

Considering the above-mentioned distributions of ambient temperature and transient modes as well as the effect of damage level on ESR and capacitance of capacitors [36], [37], the damage of capacitors can be estimated using the following lifetime model and damage model [22], [23], i.e.,

$$L_{x} = L_{0} \times m^{\frac{T_{0} - T_{h}}{n_{1}}} \times (V_{x}/V_{0})^{-n_{2}}, D_{CAP} = \sum l_{x}/L_{x}$$

(26)

where  $l_x$ ,  $L_x$ ,  $V_x$  represent the operation time, calculated lifetime, capacitor voltage under the case that the thermal stress is  $T_h$ .  $L_0$ ,  $V_0$ ,  $T_0$  are the rated lifetime, rated voltage under the reference

condition. Generally, the typical values of coefficients m,  $n_1$ , and  $n_2$  are provided by capacitor manufactures based on accelerated aging tests. As reported in [38], m,  $n_1$ , and  $n_2$  for polymer Al-Caps are 10, 20, and 0, respectively. For MLC-Caps, m,  $n_1$ , and  $n_2$  are 2, 8, and 3, respectively [39].

Figs. 17(b) and 17(c) show the equivalent hotspot temperatures and annual damage of capacitors. It can be seen that the thermal stress of Al-Caps is larger than that for MLC-Caps, and the equivalent hotspot temperature of MLC-Caps in different schemes are similar due to its relatively small ESR and  $R_{th}$ . The results in Fig. 17(c) illustrate the damage consumption of MLC-Caps in the proposed scheme is similar to that for TOC and PI schemes due to the degradation of MLC-Caps is dominated by the voltage stress. Although the TOC scheme has superior transient performance when compared with the PI scheme, the damage consumption of Al-Caps is larger than that for PI schemes.

## IV. RELIABILITY BENCHMARKING

## A. Monte Carlo Simulation

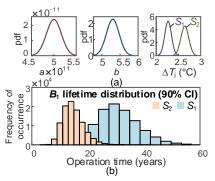

Generally, the lifetime model shown in (26) describes the wear-out failure of capacitors at the 1% lifetime percentile (i.e.,  $B_1$  lifetime). However, the lifetime model given in (25) is used to describe the wear-out failure of power switches at the 10% lifetime percentile (i.e.,  $B_{10}$  lifetime) [16]. In order to estimate the lifetime of MOSFETs and capacitors at the same probability

Fig. 18. Monte Carlo simulation for MOSFETs in the TOC scheme. (a) PDFs of the parameters. (b)  $B_1$  lifetime distribution with 90% CI.

Fig. 19. Monte Carlo simulation for capacitors in the TOC scheme. (a) PDFs of the parameters. (b)  $B_1$  lifetime distribution with 90% CI.

of failure level, the Weibull distribution is considered [40], i.e.,

$$f(t) = (\beta/\eta) \cdot (t/\eta)^{\beta-1} e^{-(t/\eta)^{\beta}}, F(t) = 1 - e^{-(t/\eta)^{\beta}}$$

(27)

where f(t) and F(t) are the probability density function (pdf) and cumulative distribution function (CDF),  $\beta$  and  $\eta$  represent the shape and scale parameters, respectively. Assuming the shape parameter is  $\beta = 3$ ,  $\eta$  can be calculated using the estimated  $B_{10}$ lifetime (i.e., the reciprocal of annual damage in Fig. (16) and (27). Then, the obtained CDF is used to estimate the  $B_1$  lifetime.

Considering the uncertainty of lifetime model coefficients, component parameters, and mission profiles, a statistical approach is introduced to the evaluation process, i.e., Monte Carlo simulation [23], [24]. Referring to Fig. 18(a), assuming all the parameters (e.g.,  $a, b, \Delta T_j$ ) have a 10% variation, 100000 samples are chosen to analyze the lifetime distribution of MOSFETs in the TOC scheme. The results of the Monte Carlo analysis are shown in Fig. 18(b), which illustrates that the  $B_1$  lifetime (i.e., 1% probability of failure) of  $S_2$  is between about 5 and 30 years, with a 90% confidence interval (CI). Due to a lower electro-thermal stress of  $S_1$ , its failure ranging between approximately 15 and 60 years.

Similarly, the lifetime distribution of capacitors can be calculated, as shown in Fig. 19. It can be seen that the Al-Cap seems to be more prone to failure when compared with the MLC-Cap. Furthermore, the lifetime distribution of MOSFETs and capacitors in the PI scheme and the proposed scheme can be obtained using the same method.

## B. Converter-Level Reliability Benchmarking

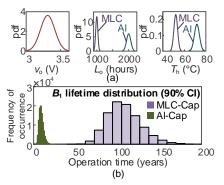

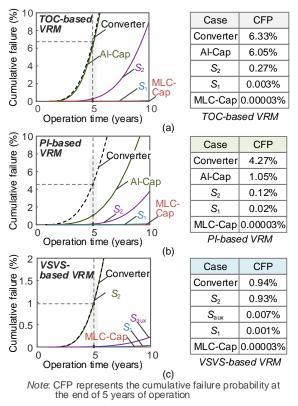

The CDF curves of MOSFETs and capacitors in TOC, PI, and VSVS schemes are shown in the left parts of Fig. 20. Based on the reliability block diagram (RBD) method [23], the

Fig. 20. Cumulative wear-out failure probability curves and failure probability at the end of 5 years of operation. (a) Classical TOC scheme. (b) Classical PI scheme. (c) Proposed VSVS scheme.

converter-level reliability curves are obtained to analyze the failure probability (FP) of VRMs, which are also shown in Fig. 20. Assuming the target service lifetime of VRMs is 5 years [41], the right parts of Fig. 20 give the probability that the components and systems fail before the target service life. Notice that the CFP in the right part of Fig. 20 represents the failure probability of a single component. The component count should be considered in the converter-level reliability evaluation.

It can be seen that given 5 years of operation, the cumulative wear-out failure probability for the TOC, PI, and VSVS schemes are approximately 6.33%, 4.27%, and 0.94%, respectively, which illustrates that the proposed scheme can significantly improve the converter-level reliability under the same design aim. Comparing with the TOC and PI schemes, the failure probability at the end of 5 years of operation has decreased by 85% and 78%, respectively. The results also illustrate that Al-Cap is the weakest link in the classical TOC and PI schemes, however, MOSFET (i.e.,  $S_2$ ) is the weakest one in the proposed scheme.

Furthermore, Table III lists the cumulative failure probability (CFP), component counts, and total costs of these three schemes, where the types of capacitors are shown in Table II. The types of MOSFETs, synchronous driver, and auxiliary driver are AUIRF 1324, IRF21844, and MCP1401, respectively. Notice that the total costs of different schemes are calculated based on the price (for 1 quantity) provided by Digi-Key Electronics [42]. It is found that the cost of the proposed VSVS scheme is slightly higher than that for the TOC and PI schemes with the same design aim (i.e., the transient voltage overshoot and stead-state ripple amplitude). However, its reliability is significantly larger

| TABLE III                                   |               |               |                |  |  |  |

|---------------------------------------------|---------------|---------------|----------------|--|--|--|

| COMPARISON RESULTS OF DIFFERENT VRM SCHEMES |               |               |                |  |  |  |

| Schemes                                     | TOC           | PI            | VSVS           |  |  |  |

| CFP at the end                              |               |               |                |  |  |  |

| of 5 years of                               | 6.33%         | 4.27%         | 0.94%          |  |  |  |

| operation                                   |               |               |                |  |  |  |

|                                             | MOSFET×2,     | MOSFET×2,     | MOSFET×3,      |  |  |  |

| Main                                        | Al-Cap×1,     | Al-Cap×4,     | MLC-Cap×2,     |  |  |  |

| components                                  | MLC-Cap ×3,   | MLC-Cap×3,    | syn. driver×1, |  |  |  |

|                                             | syn. driver×1 | syn. driver×1 | aux. driver ×1 |  |  |  |

| Total cost [42]                             | 9.84 \$       | 11.52 \$      | 12.44 \$       |  |  |  |

| Note: CEP-cumulative failure probability    |               |               |                |  |  |  |

Note: CFP-cumulative failure probability

than TOC and PI schemes, which illustrates that the proposed scheme has a relatively high economy and reliability.

#### V. CONCLUSION

This paper presents a virtual series voltage source (VSVS) based auxiliary circuit scheme, in order to reduce the capacitance requirement while guaranteeing the performance of VRMs. Then, its reliability performance benchmarking with classical TOC and PI schemes is conducted. The main conclusions are given as follows.

- 1) In order to achieve the same transient performance index (mainly refers to the small transient voltage overshoot) for VRMs with different control schemes, the system configuration and reliability are different. Although the capacitance requirement and cost of the state-of-the-art TOC scheme are less than that of the classical PI scheme, it has inferior reliability due to its electro-thermal stress is relatively large.

- 2) By using the proposed VSVS scheme, the converter-level reliability can be significantly improved. Comparing with the existing auxiliary circuit-based schemes, the component counts of the proposed scheme are minimum. However, the cost is slightly higher when compared with the classical TOC and PI schemes.

- 3) For VRMs with different system configurations, control strategies, and auxiliary circuits, the converter-level reliability can be evaluated using the same method. Moreover, the idea of the proposed auxiliary circuit could be applied in multi-phase non-coupled-inductor and coupled-inductor VRMs. However, the circuit topology and control strategy need to be further investigated in future work.

#### REFERENCES

- [1] V. Li, Q. Li, F. C. Lee, and P. Liu, "State-trajectory control with single-cycle response for point-of-load converters," IEEE Trans. Ind. Electron., vol. 67, no. 4, pp. 3157-3166, April 2020.

- O. Kirshenboim, A. Cervera, and M. M. Peretz, "Improving loading and [2] unloading transient response of a voltage regulator module using a load-side auxiliary gyrator circuit," IEEE Trans. Power Electron., vol. 32, no. 3, pp. 1996-2007, Mar. 2017.

- [3] Z. Zhao, W. Lu, P. Davari, X. Du, H. H. Iu, and F. Blaabjerg, "An online parameters monitoring method for output capacitor of buck converter based on large-signal load transient trajectory analysis," IEEE J. Emerg. Sel. Topics Power Electron., vol. 9, no. 4, pp. 4004-4015, Aug. 2021.

- [4] S. Yang, D. Xiang, A. Bryant, P. Mawby, L. Ran, and P. Tavner, "Condition monitoring for device reliability in power electronic converters: A review," IEEE Trans. Power Electron., vol. 25, no. 11, pp. 2734–2752, Nov. 2010.

- [5] Z. Zhao, P. Davari, W. Lu, H. Wang, and F. Blaabjerg, "An overview of condition monitoring techniques for capacitors in dc-link applications," IEEE Trans. Power Electron., vol. 36, no. 4, pp. 3692–3716, April 2021.

- [6] US Department of Defense, Military Handbook, Reliability Prediction of Electronic Equipment (MIL-HDBK-217F), Washington, DC, USA, 1991.

- [7] E. Meyer, Z. Zhang, and Y. F. Liu, "Controlled auxiliary circuit to improve the unloading transient response of buck converters," *IEEE Trans. Power Electron.*, vol. 25, no. 4, pp. 806–819, Apr. 2010.

- [8] E. Meyer, Z. Zhang, and Y. F. Liu, "An optimal control method for buck converters using a practical capacitor charge balance technique," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 1802–1812, Jul. 2008.

- [9] Z. Shan, S. C. Tan, and C. K. Tse, "Transient mitigation of dc-dc converters for high output current slew rate applications," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2377–2388, May 2013.

- [10] D. Kim, M. Hong, J. Baek, J. Lee, J. Shin and J. W. Shin, "Soft-switching auxiliary current control for improving load transient response of buck converter, *IEEE Trans. Power Electron.*, vol. 36, no. 3, pp. 2488–2494, March 2021.

- [11] L. Jia, Z. Hu, Y.-F. Liu and P. C. Sen, "Predictable auxiliary switching strategy to improve unloading transient response performance for dc-dc buck converter," *IEEE Trans. Ind. Appl.*, vol. 49, no. 2, pp. 931–941, Mar. 2013.

- [12]Z. Shan, S. C. Tan, C. K. Tse and J. Jatskevich, "Augmented buck converter design using resonant circuits for fast transient recovery," *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5666-5679, Aug. 2016.

- [13] W. Lu, Y. Ruan, Z. Zhao, and H. H. C. Iu, "Auxiliary parallel inductor switching control for improving the load transient response performance of buck converters," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 1, pp. 96–100, Jan. 2019.

- [14] W. Lu, Z. Zhao, Y. Ruan, S. Li, and H. H.-C. Iu, "Two-period frame transient switching control for buck converter using coupled-inductor auxiliary circuit," *IEEE Trans. Ind. Electron.*, vol. 66, no. 10, pp. 8040–8050, Oct. 2019.

- [15] Z. Zhao, W. Lu, W. Chen, X. Du and H. H. Iu, "Multi-period frame transient switching control for low-voltage high-current buck converter with a controlled coupled inductor," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9743–9757, Oct. 2019.

- [16] F. Blaabjerg, H. Wang, I. Vernica, B. Liu and P. Davari, "Reliability of power electronic systems for EV/HEV applications," *Proc. IEEE*, vol. 109, no. 6, pp. 1060-1076, June 2021.

- [17] D. Zhou, Y. Song, Y. Liu, and F. Blaabjerg, "Mission profile based reliability evaluation of capacitor banks in wind power converters," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4665–4677, May 2019.

- [18] H. Wang, P. Davari, H. Wang, D. Kumar, F. Zare, and F. Blaabjerg, "Lifetime estimation of dc-link capacitors in adjustable speed drives under grid voltage unbalances," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4064–4078, May 2019.

- [19] B. Yao, X. Ge, H. Wang, H. Wang, D. Zhou, and B. Gou, "Multi-timescale reliability evaluation of dc-link capacitor banks in metro traction drive system," *IEEE Trans. Transport. Electrific.*, vol. 6, no. 1, pp. 213–227, Mar. 2020.

- [20] S. Ye, D. Zhou, X. Yao, and F. Blaabjerg, "Component-level reliability assessment of a direct-drive PMSG wind power converter considering two terms of thermal cycles and the parameter sensitivity analysis," *IEEE Trans. Power Electron.*, vol. 36, no. 9, pp. 10037-10050, Sept. 2021.

- [21]J. V. M. Farias, A. F. Cupertino, V. d. N. Ferreira, H. A. Pereira, S. I. Seleme, and R. Teodorescu, "Reliability-oriented design of modular multilevel converters for medium-voltage STATCOM, *IEEE Trans. Ind. Electron.*, vol. 67, no. 8, pp. 6206–6214, Aug. 2020.

- [22] P. D. Reigosa, H. Wang, Y. Yang, and F. Blaabjerg, "Prediction of bond wire fatigue of IGBTs in a PV inverter under a long-term operation," *IEEE Trans. Power Electron.*, vol. 31, no. 10, pp. 7171–7182, Oct. 2016.

- [23] D. Zhou, H. Wang, and F. Blaabjerg, "Mission profile based system-level reliability analysis of dc/dc converters for a backup power application," *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 8030–8039, Sept. 2018.

- [24] Y. Shen, A. Chub, H. Wang, D. Vinnikov, E. Liivik, and F. Blaabjerg,

"Wear-out failure analysis of an impedance-source PV microinverter based on system-level Electro-thermal modeling," *IEEE Trans. Ind. Electron.*, vol. 66, no. 5, pp. 3914–3927, May 2019.

- [25] Y. Zhang, H. Wang, Z. Wang, F. Blaabjerg, and M. Saeedifard, "Mission profile-based system-level reliability prediction method for modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 35, no. 7, pp. 6916–6930, July 2020.

- [26] M. Rashti, G. Sabin, and B. Norris, "Power and energy analysis and modeling of high performance computing systems using WattProf," in *Proc. Nat. Aerosp. Electron. Conf.*, Dayton, OH, USA, 2015, pp. 367–373.

- [27] Z. Zhao, D. Zhou, P. Davari, J. Fang, and F. Blaabjerg, "Reliability analysis of capacitors in voltage regulator modules with consecutive load transients," *IEEE Trans. Power Electron.*, vol. 36, no. 3, pp. 2481–2487, March 2021.

- [28] Wurth Electronics Group, Niedernhall, Germany, "Aluminum electrolytic/aluminum polymer capacitors," 2021. [Online]. Available: https:// https://redexpert.we-online.com/redexpert/#/module/20/productdata/=8751 05144008/code/asc/contains:875105144008

- [29] "Multilayer ceramic capacitor,"Murata Manuf, Nagaokakyo, Japan, 2021. [Online]. Available: https://ds.murata.co.jp/simsurfing/mlcc.html?partnum ber=GRM31CR60J107MEA8%20&focuspartnumberonlist=true&lcid=enus

- [30] Infineon Datasheet, "AUIRF1324 HEXFET Power MOSFET," 2010. [Onli ne] Available: https://www.infineon.com/cms/en/product/power/mosfet/aut omotive-mosfet/auirf1324/

- [31] Infineon Application Note, "MOSFET power losses calculation using the datasheet parameters," 2006.

- [32] J. M. Shah, "Reliability challenges in airside economization and oilimmersion cooling," M.Sc. thesis, Dept. Mech. Eng., The University of Texas at Arlington, Arlington, TX, USA, May 2016.

- [33]K. Ma, M. Liserre, F. Blaabjerg, and T. Kerekes, "Thermal loading and lifetime estimation for power device considering mission profiles in wind power converter," *IEEE Trans. Power Electron.*, vol. 30, no. 2, pp. 590–602, Feb. 2015.

- [34] Y. Zhang, H. Wang, Z. Wang, and F. Blaabjerg, "Computational-efficient thermal estimation for IGBT modules under periodic power loss profiles in modular multilevel converters," *IEEE Trans. Ind Appl.*, vol. 55, no. 5, pp. 4984–4992, Sept./Oct. 2019.

- [35] A. Testa, S. De Caro, and S. Russo, "A reliability model for power MOSFETs working in avalanche mode based on an experimental temperature distribution analysis," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 3093–3100, Jun. 2012.

- [36] Rubycon, Corp., Nagano, Japan, "Conductive polymer aluminum solid electrolytic capacitors PZ-CAP introduction," 2013. [Online]. Available: https://www.digikey.co.uk/en/pdf/r/rubycon/pz-cap-introduction

- [37]TDK, Tokyo, Japan, "Capacitor aging characteristics: what is MLCC aging?" 2020. [Online]. Available: https://product.tdk.com/info/en/contact/faq/faq\_ detail\_D/1432616874018.html

- [38] Nichicon, Corp., Kyoto, Japan, "Estimated life calculator for capacitors," 2 020. [Online]Available:https://www.nichicon.co.jp/english/products/lifetim e/solid01.html?sr=PCF

- [39] muRata, Nagaokakyo, Japan, "Ceramic capacitors FAQ: Are there any met hods for estimating the lifetime of a capacitor?" 2020. [Online]. Available: https://www.murata.com/en-global/support/faqs/capacitor/ceramiccapacito r/qlty/0010

- [40] P. O'Connor and A. Kleyner, *Practical Reliability Engineering*. Hoboken, NJ, USA: Wiley, 2012.

- [41] "The lifespan of a PSU", Feb. 15, 2019. [Online]. Available: https://netbit.com/the-lifespan-of-a-psu/, Accessed: Mar. 2021.

- [42] Digi-Key Electronics, Minnesota, USA. [Online]. Available: https://www.digikey.com/, Accessed: Nov. 2, 2021.