Review

# Reliability of NAND Flash Memories: Planar Cells and Emerging Issues in 3D Devices

#### Alessandro S. Spinelli \*, Christian Monzio Compagnoni and Andrea L. Lacaita

Dipartimento di Elettronica, Informazione e Bioingegneria, Politecnico di Milano, 20133 Milano, Italy; christian.monzio@polimi.it (C.M.C.); andrea.lacaita@polimi.it (A.L.L.)

\* Correspondence: alessandro.spinelli@polimi.it; Tel.: +39-02-2399-4001; Fax: +39-02-2399-3574

Academic Editors: Rino Micheloni and Cristian Zambelli

Received: 3 March 2017; Accepted: 18 April 2017; Published: 21 April 2017

Abstract: We review the state-of-the-art in the understanding of planar NAND Flash memory reliability and discuss how the recent move to three-dimensional (3D) devices has affected this field. Particular emphasis is placed on mechanisms developing along the lifetime of the memory array, as opposed to time-zero or technological issues, and the viewpoint is focused on the understanding of the root causes. The impressive amount of published work demonstrates that Flash reliability is a complex yet well-understood field, where nonetheless tighter and tighter constraints are set by device scaling. Three-dimensional NAND have offset the traditional scaling scenario, leading to an improvement in performance and reliability while raising new issues to be dealt with, determined by the newer and more complex cell and array architectures as well as operation modes. A thorough understanding of the complex phenomena involved in the operation and reliability of NAND cells remains vital for the development of future technology nodes.

Keywords: Flash memory; NAND Flash reliability; NAND Flash scaling; 3D NAND Flash

#### 1. Introduction

The concept of electrically programming and erasing a semiconductor memory cell dates back to the 1970s, when a floating-gate device with a thinned oxide layer in a portion of the channel area was successfully demonstrated [1] as a viable alternative to ultra-violet erasable cells. However, it was not until the development of the one-transistor Flash memory device [2], in which the entire chip could be erased at once, that solid-state non-volatile code and data storage began to experience a tremendous growth. Data storage, in particular, was fostered by the invention of the NAND Flash [3], which is possibly one of the most successful semiconductor devices ever developed. Thanks to its extremely compact area occupation and to clever system design and optimization, it benefited from the market explosion of digital cameras first, followed by smartphones and tablets and culminating in the development of NAND solid-state drives (SSDs) [4], that have recently overtaken hard-disk drives (HDDs) in terms of areal storage density [5]. Although the discussion on whether SSDs will eventually replace HDDs aside from small consumer devices is far from settling, it is indubitable that more and more applications are falling within reach of SSDs, that are now targeting enterprise-class storage [6,7].

The NAND success story is the result of continuous scaling of the planar cell dimensions, that has led all major NAND Flash manufacturers to reach the 15 nm planar node [8–11]. However, several constraints have severely challenged the latest nodes development [12–14], eventually putting an end to the scaling of the planar Flash technology. Some of these constraints are process-based and reflect the increasing difficulty in patterning smaller and smaller features with the ArF immersion lithography. Then, traditional device design issues arise, such as the need to curb short-channel effects (exacerbated by the thick gate oxide, which has very limited scaling possibilities) and avoid degradation of the subthreshold slope (reducing the operation margin) while limiting junction leakage (which impairs

channel boosting during program). Finally, there are issues that are specific to memories, such as cell-to-cell interference and program noise, as discussed in detail in [15]. On top of all this, reliability issues, to be discussed in the following, played a key role in challenging further scaling.

This increasingly dramatic scenario prompted all major NAND Flash manufacturers to seek an alternative way to continue to deliver increasing storage capacity, that has resulted in the demise of the planar technology and the pursuit of three-dimensional (3D) memory arrays. In this field, a pioneering proposal was put forward in 2001 [16], evolving into early proposals based on layer stacking [17–19] and reaching the first cost-effective solution of a 3D-integrated array in 2007 [20]. From there on, 3D NAND based on vertical channels have taken the lead in the quest for higher density, resulting in the first commercial product in 2013 [21,22] and reaching a capacity of 786 Gb with a density of 4.29 Gb/mm² [23] while stacking up to 64 layers [23–25]. Chip capacity was boosted not only by 3D integration, but also by multi-bit storage: while two bit-per-cell (i.e., multi-level cells, MLCs) were used in the first prototype [21], today's technology relies on storing three bit-per-cell (triple-level cells or TLCs) and quadruple-level cells (QLCs) are under active development. Recent reviews of the different 3D NAND technologies and architectures can be found in [26–28].

The revolutionary move to 3D memories was not without problems, as discussed in [29]. In fact, while traditional device reliability issues must still be accounted for, new phenomena came to prominence, which are not merely an extension of what has already been observed on planar devices, but rather a consequence of the different device and array fabrication. The aim of this paper is then to review the main reliability issues that play a key role in planar NAND Flash devices and discuss the main experimental data and current understanding. Then, 3D NAND reliability is addressed, highlighting the role of such "traditional" mechanisms in the new cell size and geometry and introducing issues that are specific to the new memory cell. The analysis of the literature—though selected—reveals on the one hand the complexity of Flash reliability and, on the other hand, the huge efforts undertaken by the scientific community to understand the root causes of the experimental observations and develop effective predictive models that allowed a successful product design. Three-dimensional NAND bring further challenges to the table, with tighter requirements in an increasingly complex device, meaning that Flash reliability will offer an exciting field for scientific investigation for many years to come.

## 2. The NAND Memory Array

This Section contains a brief discussion on the planar NAND memory array architecture and program operations, with the aim of providing the basic knowledge to understand the rest of the paper. We will not discuss in detail the different array operations but rather restrict ourselves to the general principles, referring to specific literature for more details [27,30,31].

#### 2.1. Array Architecture and Layout

The basic element at the heart of the NAND memory is the floating-gate (FG) transistor, in which a polysilicon island is sandwiched between a gate (or tunnel) oxide and an interpoly dielectric, in turn connected to a control gate. Whenever a charge Q is stored in the floating gate, simple electrostatics [32] shows that the threshold voltage  $V_T$  of the cell becomes

$$V_T = V_{T0} - \frac{Q}{C_{vv}},\tag{1}$$

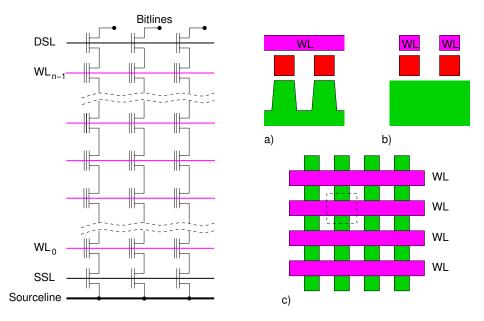

where  $V_{T0}$  is the so-called *neutral* threshold voltage, corresponding to zero charge on the floating gate, and  $C_{pp}$  is the interpoly dielectric capacitance. As charge cannot easily leak from the isolated floating gate, a non-volatile memory element is achieved. In the NAND array, transistors are connected in series along *strings*, while their control gates, connected across different strings, constitute the wordlines (WLs), each making a *page*, as schematically depicted on the left of Figure 1 (more than one page can be associated to the same WL, but this is irrelevant for our purposes). Strings are connected to the

Computers **2017**, *6*, 16 3 of 55

bitlines (BLs) and the common sourceline via select transistors driven by a drain select line (DSL) or a source select line (SSL). This array constitutes a *block*, whose size is a key element in NAND array organization.

**Figure 1.** (**Left**) Schematic view of a NAND Flash array. Vertical strings of series-connected devices are attached to the bitlines and the sourceline via select transistors driven by a drain select line (DSL) and a source select line (SSL); (**Right**) schematic cross-sections of the array along the WL direction (**a**) and the string direction (**b**) (green = silicon, red = floating gate, magenta = WL, white = silicon oxide). Inset (**c**) shows the layout of the array with the elementary cell (dashed square).

Cross-sections of a current planar NAND array are shown on the right of Figure 1: Figure 1a depicts a typical cut along the WL (green = silicon, red = floating gate, magenta = WL, white = silicon oxide), highlighting the shallow trench isolation used to separate the active area of adjacent devices [33] and the planar structure of the cell, without any wrapping of the control gate along the floating gate sidewalls [34]. Figure 1b depicts instead the cross-section along the string direction. Figure 1c shows the layout of the memory array, which becomes extremely compact thanks to these solutions. In particular, given the feature size F of a given technology, i.e., the size of the smallest feature that can be created on silicon, the elementary memory cell (shown as a dashed square in Figure 1c) occupies the ideal area of  $4F^2$ . However, the *effective* cell area, i.e., total chip area divided by the number of cells, is somewhat larger than that because of the overhead circuitry, string contacts with BLs, dummy cells and select transistors. To decrease such overhead, the number of cells in a NAND string has reached the impressive number of 150 in the latest planar nodes [10].

# 2.2. Array Operation

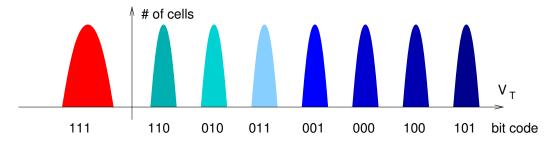

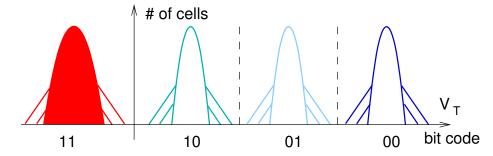

As mentioned above, digital information is stored as charge onto the floating gate of a NAND cell. While the first devices relied on two discrete charge levels to store a single bit (the so-called single-level cells, SLCs), it was soon realized that the linear relation between floating-gate charge and cell  $V_T$  could be exploited to store more than one bit per cell [35,36]. Nowadays, TLCs are in production and used in SSDs [6], while quadruple-level cells (QLCs) are under active development [37]. Figure 2 shows the  $V_T$  distribution of a TLC NAND array: eight different levels are necessary to encode three bits. In the NAND architecture, all but one  $V_T$  level are positive (shown in different shades of blue) and are referred to as the *programmed* levels. The negative (red)  $V_T$  level is instead the *erased* one.

Computers **2017**, *6*, 16 4 of 55

**Figure 2.** Pictorial view of the threshold voltage ( $V_T$ ) distribution in a TLC cell. A three-bit code is associated to each of the  $V_T$  levels.

#### 2.2.1. Read

Reading the state of a cell means discriminating one  $V_T$  level against another and irrespective of the  $V_T$  levels of all other cells in the string. To accomplish this, the string has first to be connected to the sensing circuit, i.e., the select lines are high and the BL is biased; therefore, a current can flow to the (grounded) sourceline. Unselected cells are then placed in a pass-transistor mode, biasing their WLs at a *pass voltage* larger than the maximum  $V_T$ . The actual read operation is then performed, sensing the cell current and comparing it against fixed reference values to assess the corresponding binary code [38]. The operation is performed more than one time for MLC and TLC cells. To increase parallelism, strings are read in parallel across a page (typically 8–16 kB), resulting in a throughput higher than 150 MB s<sup>-1</sup>.

### 2.2.2. Program

NAND Flash cells adopt channel Fowler–Nordheim (FN) tunneling to store electrons onto their floating gates [39]. To this aim, the selected cell is first connected to the external circuitry by biasing the unselected WLs to a pass voltage and turning on the DSL, while the BL is grounded and the SSL is left off. A high voltage is then applied to the desired WL, resulting in tunnel electron injection from the inverted substrate to the floating gate. In MLCs or TLCs, fine placement of the  $V_T$  levels is needed because of the reduced distance between adjacent distributions (see Figure 2). This is achieved via an *incremental step-pulse programming* (ISPP) technique [40], in which fast pulses of increasing amplitude are used to inject a constant, controlled amount of charge onto the floating gate at each step, interleaved with *program verify* phases in which  $V_T$  is monitored. Several refinements are applied to this basic concept in 8- or 16-level cells [38].

Since the program operation is controlled by the WL bias, it acts on a page of the array. However, not all cells must be programmed at the same level (or programmed at all), which means that a program-inhibit strategy must be implemented for those cells. Inhibiting programming means reducing the gate-channel bias of such cells, thereby lowering their tunnel oxide field responsible for the electron injection. In NAND arrays, this is achieved via a *self-boosting* procedure [36], where the inhibited strings are first floated and their potential is temporarily raised via capacitive coupling to the WLs, that are raised at the passing voltage [38]. Program throughput in excess of 50 MB s<sup>-1</sup> has been reported [10].

# 2.2.3. Erase

Erase operation is performed on blocks, i.e., a set of pages that can be 4–8 MB in size, exploiting the same FN mechanism used in program. As NAND chips do not allow the use of high negative voltages, WLs are grounded and a high positive voltage is applied to the p and n wells of the array. A verify phase follows, aimed at ensuring that all cells have negative  $V_T$ , which triggers another erase pulse if the condition is not met: the technique is similar to what is used during program, and is called *incremental step-pulse erasing*. Floating WLs are used to inhibit erase on unselected blocks.

Computers **2017**, *6*, 16 5 of 55

#### 3. NAND Flash Memory Reliability

From a general standpoint, the reliability of a product is related to its capability to continue to work as expected as a function of time. Reliability is enhanced by screening, testing and qualification and, eventually, by error management procedures. In all these respects, Flash memories are peculiarly different from other semiconductor devices, as they intrinsically operate under high-field conditions that other devices purposely avoid. Moreover, reliability is usually extrapolated from accelerated tests, that should replicate as close as possible the real operating conditions. Unfortunately, the development of such tests is complicated by the many different patterns of program/erase and read cycles under which Flash memories usually operate.

As a matter of fact, there are a number of failure modes and mechanisms that are specific to Flash, not to mention error-management procedures that are put forward by the manufacturers to increase reliability and yield. These depend on the type of failure, which can be recoverable (i.e., it can be fixed by erase and reprogram) or not. Recoverable errors are usually dealt with via error-correction codes (ECC). Initially, when SLCs were prevalent, simple Hamming algorithms were employed, which could correct single-bit errors and detect two-bit ones. Later, more efficient BCH (Bose, Ray-Chaudhuri and Hocquenghem) algorithms were implemented in the Flash controller [41]. However, as Flash capacity continued to rise and MLCs gave way to TLCs, more efficient ECCs were needed, resulting in a transition to soft decoding schemes. Low-density parity-check (LDPC) ECCs [42–45] are gaining traction in modern SSDs, while concatenated codes for NAND Flash have been also proposed [46–49].

Non-recoverable errors, or errors exceeding the ECC capabilities, result in *bad blocks* [50], i.e., blocks that are excluded from the memory operation and are replaced by available valid blocks. A small number of initial bad blocks is allowed, which can increase with use. Eventually, when the number of bad blocks exceeds the device specifications, the entire chip fails. It is worth mentioning that both ECC and bad blocks management require extra cells/blocks, thereby contributing to an increase of the cell effective area as discussed in Section 2.1, i.e., a reduction in the array efficiency.

Reliability specification by the manufacturers typically includes the number of bad blocks, the endurance and retention properties of the array and the number of error-correction code bits. In the following, however, we will go beyond the manufacturer specifications and look at the basic physical mechanisms at the heart of the reliability issues. Since this is an extremely large field, we restrict our discussion to issues that develop with memory usage, neglecting for example defect-related issues, time-zero problems such as  $V_T$  placement, cell-to-cell interference and many others, for which we refer the reader to other overviews of Flash memory reliability that are available in the literature, leaning either toward a device/technology [27,51–59] or user [60–62] viewpoint.

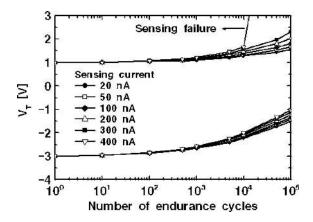

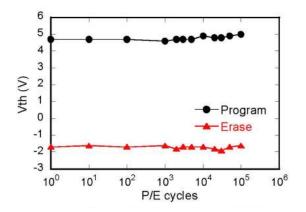

#### 3.1. Endurance

This parameter specifies the maximum number of program/erase (P/E) cycles  $N_C$  that the memory chip can tolerate. The onset of this limitation can be observed by repeating simple, single-pulse P/E operations on a cell and monitoring the resulting  $V_T$ . An example of such a dependence in a NAND device is shown in Figure 3 [63]: the  $V_T$  levels experience an increase for high values of  $N_C$ , eventually leading to a read failure. Higher increase is usually observed on the erased level.

Like most reliability concerns for Flash memories, this phenomenon is one consequence of the electron flow through the oxide during FN tunneling, which has been observed to generate oxide traps and fixed charge in MOS (Metal-Oxide-Semiconductor) devices since the 1980s [64–69]. At first glance, such charges should result in a constant shift of both  $V_T$  levels, while the actual behavior features a milder dependence on  $N_C$  by the programmed  $V_T$  with respect to the erased one, pointing toward an interplay among different mechanisms. This picture is confirmed by early results on different non-volatile memory technologies, where different P/E schemes (i.e., different electron injection conditions into the oxide) resulted in different  $V_T$  dependences on  $N_C$  [70].

Computers **2017**, *6*, 16 6 of 55

Figure 3. Endurance characteristics of a NAND cell [63], © 2004 IEEE.

A thorough analysis of the phenomenon was first conducted in [71], using charge-pumping and  $V_T$  measurements to assess the roles of interface and oxide charges, and was later corroborated by subsequent studies [72]. The authors' conclusion was that trapped oxide charge should not influence the programmed  $V_T$  value because tunnel injection from the channel during the program pulse is controlled by the oxide field at the cathode interface, meaning that the final condition reached by the cell will be of equal field, irrespective of the starting  $V_T$  and trapped charge (if not too close to the cathode interface). In turn, the same oxide field at the channel interface means the same final  $V_T$ , explaining the experimental behavior of a nearly constant programmed  $V_T$  level. Simply put, as trapped negative oxide charge builds up, it reduces injection, giving a negative  $V_T$  shift that is balanced by the positive  $V_T$  shift given by the charge itself. This "converging" behavior of the FN tunneling operation has been in fact exploited to tighten the  $V_T$  distribution after erase [73].

The same reasoning holds for the erase operation, but now the final condition is the one with the same field at the oxide-floating gate interface (the cathode during erase), which does not translate into the same  $V_T$ , now dictated by the oxide trapped charge: a larger increase in  $V_T$  vs.  $N_C$  is then expected. This model was then refined [63] to include the effect of charged stress-generated interface states, that provide an additional positive  $V_T$  shift for both levels (while not influencing injection) for high cycling conditions, explaining the slight increase in the programmed  $V_T$ . Finally, the effect of non-uniform tunneling current flow and oxide charge distribution over the area of scaled NAND devices have been investigated in [74,75], pointing out their effect on the endurance curve and on the assessment of the endurance degradation with scaling. A recent technique for separating the endurance degradation components, including subthreshold slope and transconductance, which also influence the  $V_T$  values, has been reported in [76].

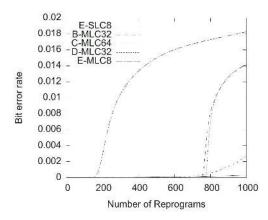

From the product viewpoint, the  $V_T$  window degradation is managed by the program and verify ISPP algorithm, meaning that any variation in the P/E characteristics of the cell will result in a change in the number of ISPP pulses. Eventually, when — say — the number of erase pulses will become higher than the maximum allowed by the erase time specifications, an erase failure will be signaled. This is an unrecoverable error, resulting in the block being marked as *bad* (overprovisioning ensures that failed blocks do not reduce the device capacity). When the number of bad blocks exceeds the device specifications, the entire chip fails. Several techniques of *wear leveling* [77] are adopted by current NAND suppliers to distribute the number of P/E cycles among the blocks and make degradation uniform. Typical endurance values for SLC cells are in the  $10^5$  P/E cycles range, which drops by an order of magnitude or even more when moving to MLC [62]. An even lower value (around 1000) can be expected for TLCs. For SSDs, this specification translates into the total amount of writable data in — say — five years for a given workload.

Computers **2017**, *6*, 16 7 of 55

#### 3.2. Random Telegraph Noise (RTN)

## 3.2.1. RTN Amplitude

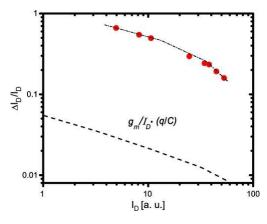

Random telegraph noise (RTN) in MOS transistors is an abrupt two-level fluctuation in drain current  $I_D$  following trapping and release of a single electron by an oxide defect. This well-known phenomenon has been observed and studied since the 1980s [78–86], resulting in a prediction for the RTN amplitude [79] equal to

$$\frac{\Delta I_D}{I_D} = \frac{q}{C_{ox}WL(V_G - V_T)} + \frac{\Delta \mu_n}{\mu_n} \frac{\Delta A}{WL},\tag{2}$$

where q is the electron charge,  $C_{ox}$  the oxide capacitance per unit area, W and L the channel width and length, respectively, and  $\mu_n$  the electron mobility in the inversion channel, which experiences a fluctuation  $\Delta\mu_n$  over an area  $\Delta A$  as a consequence of the additional scattering with the trapped electron. Typical values for the first term are smaller than 10%, while the scattering part is typically negligible in the subthreshold regime, where NAND cells are usually read; therefore, RTN has long been regarded as a curious scientific phenomenon not constituting a noticeable reliability threat. This held true even if unusually large values for the RTN amplitude had been consistently reported on some devices, together with complex time behaviors [79,82,87–89], that seemed to defy Equation (2). When Flash memories made a large quantity of data readily available, making it possible to pinpoint and study anomalous behaviors occurring with extremely low probability, larger and larger fluctuation amplitudes emerged [90,91], and RTN became a serious reliability constraint in static random-access [92–94] and Flash memories [90,91,95–99], prompting an intensive research effort to understand its root cause and impact on memory array operation.

**Figure 4.** RTN fluctuation amplitude measured on a decananometer Flash cell (points = experimental data, dashed line = predictions from (2) when mobility modulations are neglected) [91], © 2007 IEEE.

An example of the relevance of RTN is shown in Figure 4, where results obtained on a selected decananometer Flash cell are reported [91]: current fluctuations up to 60% were detected, which cannot be explained with the above theory. Though early explanations pointed to multiple carrier emissions [88,89], change in defect properties [87] or interacting quantum wells [82], a different approach based on the percolative nature of the current conduction around the charged trap site had been mentioned in [100] and thoroughly revisited in [101], exploiting a concept applied to amorphous semiconductors [102]. The authors pointed out that no uniform conduction in a MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) channel could account for the anomalous RTN amplitudes. Rather, a non-uniform conduction with filamentary current flow was needed as a starting point; therefore, an RTN trap could effectively modulate a current-crowding path, resulting in a large current fluctuation. Fixed oxide and interface charges were proposed as sources of percolation,

Computers **2017**, *6*, 16 8 of 55

following earlier studies [103,104]. This is now regarded as the correct interpretation of the RTN amplitudes, with the caution to add the actual main source of percolation: random dopant fluctuation (RDF). In fact, statistical variation in number and position of dopants was known to affect MOSFET parameters such as  $V_T$  and subthreshold slope [105–108], and was shown to have a significant impact on RTN in [109] and in [110,111], where large amplitude values compatible with experimental data were reported.

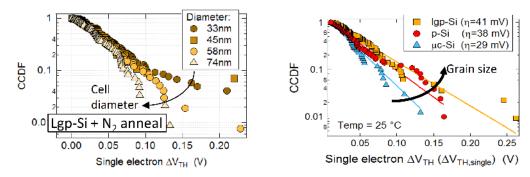

For the evaluation of the RTN effects in Flash memories, the statistical distribution of its amplitude is needed, accounting for realistic device geometry and doping. This task was undertaken in [112,113], where 3D Monte Carlo simulations of electron transport were carried out, accounting for randomized doping and trap positions. Simulations were conducted within the drift-diffusion framework, neglecting the field dependence of mobility to avoid unphysical effects close to the ionized dopants and RTN trap. The impact of Coulomb scattering on the RTN and variability characteristic of such MOSFETs has been studied in [114–117], showing that those effects are barely relevant for NAND Flash, that are read in the subthreshold regime. Charge quantization was instead accounted for via the density-gradient correction to the drift-diffusion formalism [118,119]. Its relevance from the variability viewpoint was discussed in [120].

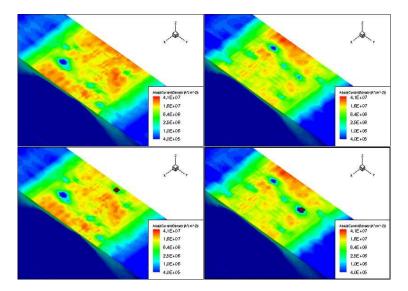

Figure 5 shows results for the current density profile in the channel of a decananometer Flash memory biased around a threshold. The two figures on the left-hand side correspond to a case of high  $V_T$  shift: transport in the empty trap case (upper figure) has a percolative nature because of RDF and field intensification around the active area corners. The RTN trap (black square in the lower figure) is located right above one main percolation path, close to one edge: its charging will shut off such path, leading to a large variation in current and  $V_T$ . On the other hand, if the trap is located over a region in which the current density is already negligible, its charging and discharging will barely affect the overall current flow, as shown by the figures on the right-hand side.

**Figure 5.** Current density profiles in the channel of decananometer Flash memories with and without a charged RTN trap. Left-hand side = high  $V_T$  shift case, right-hand side = low  $V_T$  shift case. Upper figures represent the empty trap case, lower figures the charged trap ones. The trap position is marked by the black squares in the lower figures.

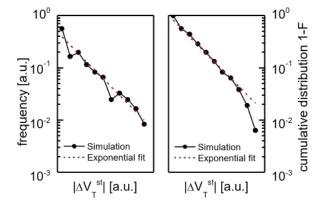

Monte Carlo results for the statistical distribution of the  $V_T$  shift due to a single RTN trap,  $\Delta V_T^1$ , are shown in Figure 6: an exponential distribution was found, which can be easily characterized by

Computers **2017**, *6*, 16 9 of 55

its slope  $\lambda$ , usually expressed in mV/decade. A thorough parametric analysis of  $\lambda$  was carried out in [113,121], resulting in the following dependence:

$$\lambda = \frac{K}{\alpha_G} \frac{t_{ox}^{\alpha} \sqrt{N_A}}{W \sqrt{L}},\tag{3}$$

where  $t_{ox}$  is the tunnel oxide thickness, $N_A$  the average substrate doping,  $\alpha_G$  the control-gate coupling coefficient and K is a constant dependent on device design, doping profile and so on. This relation has proven itself to reproduce quite successfully the scaling dependence of the RTN slope over several different technologies.

**Figure 6.** Probability density function (**left**) and cumulative distribution (**right**) for the threshold voltage shift determined by the charging of a single interfacial trap,  $\Delta V_T^1$ , in a decananometer NAND Flash cell [112], © 2008 IEEE.

# 3.2.2. Main Experimental Data

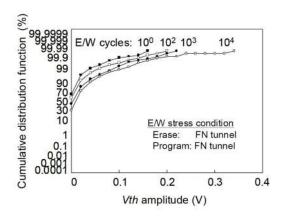

The first experimental data on the statistical distribution of RTN amplitude in Flash memory arrays were published in 2006 [95]. For each cell in the array, the authors applied a staircase control-gate bias, recording the  $V_T$  value at which the cell switched from on to off state. Because of RTN, different  $V_T$ s are recorded every time the experiment is repeated, and their maximum and minimum values will give the amplitude of the RTN fluctuation (two staircases are actually employed, with increasing and decreasing control-gate bias, but the working principle does not change). Results for the fluctuation amplitude on a 90 nm cell are reported in Figure 7: note that the majority of cells exhibit negligible  $V_T$  fluctuations, but a small number of them can reach  $V_T$  shifts of a few hundred mV. Moreover, the number of cells exhibiting this behavior increases with P/E cycling.

Computers 2017, 6, 16 10 of 55

**Figure 7.** Experimental cumulative distribution function for the  $V_T$  shift induced by RTN in a Flash array [95], © 2007 IEEE.

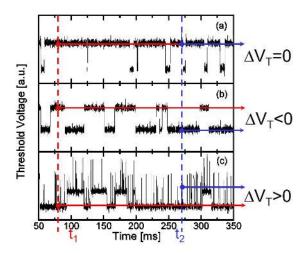

A simpler characterization technique for RTN is reported in Figure 8 [96], where the  $V_T$  values at two different times are recorded for each cell. The RTN amplitude is now defined as the  $V_T$  difference between the two values. Note that this technique does not measure the *maximum* RTN fluctuation amplitude, as accomplished by [90,95,97,99], because a noisy cell can give either positive, negative or zero fluctuation, depending upon the sampling time (see the different cases Figure 8). However, this technique will return the actual RTN amplitude distribution that matters under real operating conditions, when a cell is read after being programmed.

**Figure 8.** Time dependence of  $V_T$  for three Flash cells affected by RTN.  $V_T$  is sampled at times  $t_1$  and  $t_2$  and the RTN amplitude is defined as the  $V_T$  difference. Note that (a) null, (b) negative and (c) positive  $\Delta V_T$  can result.

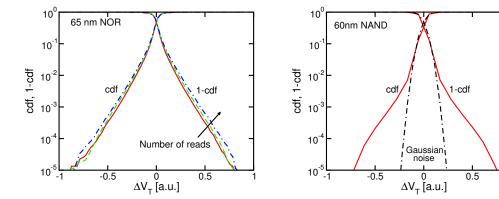

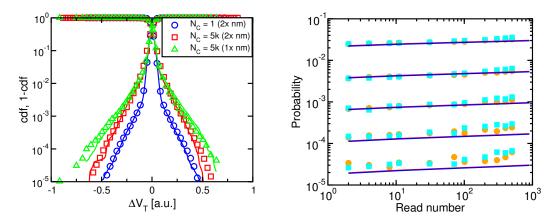

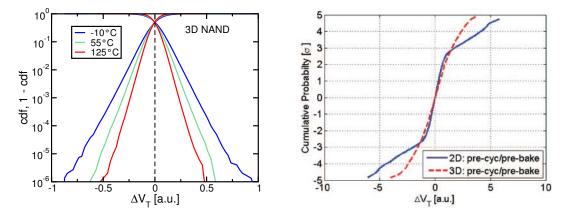

Typical results obtained with this technique are shown in Figure 9 for NOR (left) and NAND (right) Flash arrays [96,122,123]. Figures show the cumulative density function (cdf) and its complement, highlighting clear exponential tails down to very low probability values [124] for both high and low  $\Delta V_T$  values. The region around  $\Delta V_T = 0$  is affected by Gaussian noise, and the exponential tails depart from such region at different probabilities. Note also that when  $\Delta V_T$  is evaluated between the nth and the first read operation, the tails slightly increase with n. Differences between NOR and NAND RTN levels and amplitude are determined by cell design parameters (see Equation (3)) as well as by the cycling conditions.

**Figure 9.** Experimental results for the  $\Delta V_T$  statistical distribution on a 65 nm NOR (**left**) and a 60 nm NAND (**right**) Flash array, obtained following the procedure highlighted in Figure 8. Both the cumulative distribution function (cdf) and its complement are displayed, to highlight the exponential tails. Results for different numbers of reads are also shown for the NOR case.

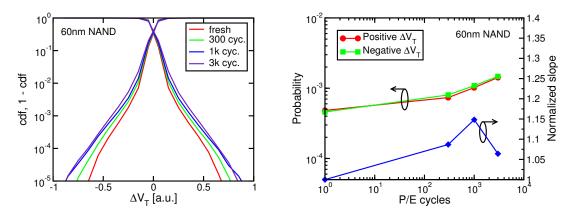

Figure 7 shows that RTN depends on P/E cycling. An increase in the tail height was also reported in [98,123,125], where different technologies were compared. Figure 10 (left) shows experimental data for RTN in a NAND array for different cycling conditions: note that the exponential tails grow while their slope is hardly affected. This is reported in the right-hand side of Figure 10 where the slope  $\lambda$  of the exponential tails and the probability at a fixed  $|\Delta V_T|$  value are shown as a function of  $N_C$ , for the same technology. Note the negligible dependence of  $\lambda$  on  $N_C$ , confirming that cycling results in a parallel shift of the RTN tails. The increase in tail height follows a power-law dependence with exponent 0.29 for this technology [123]. Different values were found in NOR arrays, owing once more to differences in cell design and cycling conditions. Such dependences prompted several works and studies on the optimization of the cell process/architecture in order to reduce the extent of the RTN [124,126–134]. In the NAND array, moreover, the RTN amplitude was shown to depend on the cell position and state along the string [135,136] (because of the different transconductances, depending on the source and drain series resistances) and on the state of cells on adjacent BLs [137] (because of the modification in the electron density profile induced by electrostatic interference).

**Figure 10.** Experimental data for the RTN distribution in NAND arrays as a function of  $N_C$  (**left**) and RTN tail height at a fixed  $|\Delta V_T|$  value and slope as a function of  $N_C$  for a 60 nm NAND (**right**) Flash array [123], © 2008 IEEE.

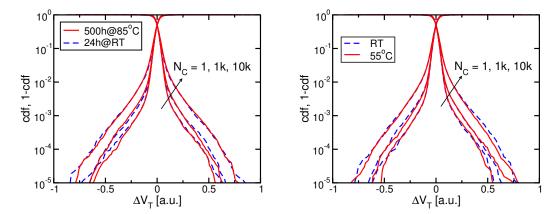

The cycling dependence was also investigated in [138], in connection with the temperature dependence of RTN. Two cycling schemes were adopted, involving different temperatures and cycling times in accordance with the activation energy of damage recovery which will be discussed in Section 3.4. Then, RTN was read at room temperature. Figure 11 (left) shows that no significant

difference can be detected in the RTN cdfs, meaning that the high-temperature phase applied during the 500 h scheme is not annealing any defect responsible for RTN. The right-hand side of Figure 11 shows instead the dependence upon the read temperature. Again, no dependence appears when the temperature is changed from room temperature to 55°C. This result may seem surprising, as it is well known that trap capture and emission times are temperature-dependent [136,139,140], but comes from the distribution of such times among the cells, as discussed in the next section.

**Figure 11.** RTN cdfs for two cycling schemes and room-temperature read (**left**) and for one cycling scheme and different read temperatures (**right**). No significant differences appear in all cases.

## 3.2.3. Models

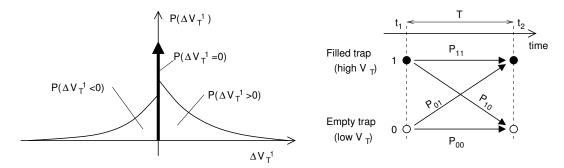

The experimental data just reported call for a consistent model able to explain the different features of the phenomenon. While data shown in Figure 7 can be reproduced by a simple exponential fit [98], the explicit time dependence captured by Figures 8 and 9 requires a time-dependent analysis, that was first put forward in [96,122]. The starting point is the exponential distribution of  $V_T$  shift extracted from simulation results described in Section 3.2.1. Such a distribution describes a positive  $V_T$  shift between time  $t_1$  and  $t_2$  if an empty trap at  $t_1$  is filled at  $t_2$  and a negative shift if the opposite is true. If the trap state does not change, a zero  $V_T$  shift holds. The final time-dependent distribution is then the one shown in Figure 12 (left), where the positive and negative exponentials and the zero-shift delta function must be weighted by their occurrence probabilities, representing their areas. This is accomplished describing the RTN process as a two-state Markov process [141,142], as depicted in Figure 12 (right). The two states correspond to the empty (low- $V_T$ , state 0) and filled (high- $V_T$ , state 1) trap. Considering constant capture and emission times  $\tau_c$  and  $\tau_e$ , the transition probabilities between state i and j,  $P_{ij}$ , over a time interval T become:

$$P_{11}(\tau_c, \tau_e) = \frac{1}{\tau_c + \tau_e} \left( \tau_c \, e^{-T/\tau_{eq}} + \tau_e \right) \tag{4a}$$

$$P_{10}(\tau_c, \tau_e) = 1 - P_{11} = \frac{\tau_c}{\tau_c + \tau_e} \left( 1 - e^{-T/\tau_{eq}} \right)$$

(4b)

$$P_{00}(\tau_c, \tau_e) = \frac{1}{\tau_c + \tau_e} \left( \tau_e \, e^{-T/\tau_{eq}} + \tau_c \right) \tag{4c}$$

$$P_{01}(\tau_c, \tau_e) = 1 - P_{00} = \frac{\tau_e}{\tau_c + \tau_e} \left( 1 - e^{-T/\tau_{eq}} \right),$$

(4d)

where  $\tau_{eq}^{-1} = \tau_c^{-1} + \tau_e^{-1}$ . Note that these expressions describe the probabilities to find the trap in a certain state after a time interval T, given the initial condition, irrespective of the number of transitions taking place in-between.

**Figure 12.** PDF (Probability Density Function) of the single-trap threshold voltage shift  $P(\Delta V_T^1)$  (**left**) and Markov process view of the single-trap RTN waveform between times  $t_1$  and  $t_2 = t_1 + T$  (**right**).

From (4), the probability for a single trap to provide a  $V_T$  shift,  $\Delta V_T^1$ , can be easily calculated:

$$P(\Delta V_T^1 > 0 | \tau_c, \tau_e) = P_0^{t_1} P_{01}(\tau_c, \tau_e)$$

(5a)

$$P(\Delta V_T^1 < 0 | \tau_c, \tau_e) = P_1^{t_1} P_{10}(\tau_c, \tau_e)$$

(5b)

$$P(\Delta V_T^1 = 0 | \tau_c, \tau_e) = P_0^{t_1} P_{00}(\tau_c, \tau_e) + P_1^{t_1} P_{11}(\tau_c, \tau_e), \tag{5c}$$

where  $P_i^{t_1}$  is the probability for the trap to be in state i = 0, 1 at time  $t_1$ .

Once the analysis for a given set of  $\tau_c$ ,  $\tau_e$  is assessed, we must account for their statistical distribution among the traps. The original approach in [122] relied on the classical theory of direct tunneling into oxide defects [80,81], explicitly linking  $\tau_c$  and  $\tau_e$  to the space and energy position of the trap inside the oxide. Later results have, however, shown that capture/emission times in MOSFETs are not compatible with such a description [143,144], due to device variability effects on the time constants [145–147] and structural relaxation of defects [140,148], generating a large spread in time constants even for traps located close to the silicon/oxide interface and disrupting the classical correlation between  $\tau_c$  and  $\tau_e$ . The study of the microscopic properties of RTN traps is still an active research topic [149–156], but for our purposes we will adopt a pragmatic approach, assuming given distributions of capture/emission time constants that may be consistent with observations, without linking them to any particular trap location. A constant PDF on a log-time scale was successfully assumed in [138], such as the one that will be used to describe detrapping after cycling in Section 3.4.2. It is worth noting that the constant trap density adopted in [122] implicitly provides a similar time constant distribution, due to the exponential nature of the tunneling probability, the only difference being the lack of correlation between  $\tau_c$  and  $\tau_e$  and between the time constant and the spatial location of traps. Within this framework, the expression for the single-trap  $V_T$  shift pdf,  $P(\Delta V_T^1)$ , becomes

$$P(\Delta V_T^1) = \int \int P(\Delta V_T^1 | \tau_c, \tau_e) p(\tau_c, \tau_e) d\tau_c d\tau_e, \tag{6}$$

where  $p(\tau_c, \tau_e)$  is the probability for a trap to possess such capture/emission time constants.

Once  $P(\Delta V_T^1)$  is computed, multiple trap effects can be easily accounted for assuming statistical independence of their  $V_T$  shifts. This means that the overall  $V_T$  shift is the sum of the individual contributions, which translates into a convolution operation for pdfs. In particular, for  $N_t$  independent traps, each with the same  $P(\Delta V_T^1)$  pdf, we have

$$P(\Delta V_T^{N_t}) = \bigotimes_{1}^{N_t} P(\Delta V_T^1) \tag{7}$$

and, since the number of traps per cell can be assumed to be statistically distributed according to a Poisson statistics  $p(N_t)$ , we finally get the RTN pdf:

$$P(\Delta V_T) = \sum_{N_t=1}^{\infty} P(\Delta V_T^{N_t}) p(N_t).$$

(8)

**Figure 13.** (Left) Comparison between experimental data and model for the RTN distribution in  $1 \times$  and  $2 \times$  NAND arrays and different  $N_C$ ; (**Right**) same comparison for the tail probability at a fixed  $|\Delta V_T|$  as a function of the number of reads for a 65 nm NOR Flash array.

Typical comparisons between model results and experimental data are reported in Figure 13 for NAND [138] and NOR [122] arrays. The left-hand side shows that a nice agreement can be achieved for different technologies and cycling conditions. In particular, because of the exponential nature of  $P(\Delta V_T^1)$ , its slope  $\lambda$  matches what is obtained from array data and resulting from the convolution operation in (8). The right-hand size is instead related to data reported in Figure 9 (left), where RTN distributions for increasing read operations (i.e., time) are reported, and shows the probabilities at fixed  $|\Delta V_T|$  values as a function of the number of read operations. The increase in the RTN figure is well reproduced by the model and can now be explained: the increase in the elapsed time between the read operations (i.e., T in Equation (4)) allows for more and more traps to be activated, as their  $\tau_{eq}$  becomes comparable with T. This increases the randomness of  $V_T$ , enlarging the RTN distribution. This effect was nicely shown in [96,122] as an extension with time of the oxide region whose traps are sampled by RTN.

Finally, the temperature-independent RTN behavior observed in [138] was explained in terms of a lack in correlation between the time constants and their activation energy values; therefore, temperature will not affect the overall time constant distribution. Of course, different defects will contribute to the RTN fluctuations, as some are accelerated and will end up being filtered by the read time while slow ones will come into play as a result of thermal activation.

**Figure 14.**  $V_T$  distribution of an MLC array in the presence of RTN. Dashed lines represent the reference levels used during read.

#### 3.2.4. Effect on Programmed $V_T$ Distribution

Figure 14 shows pictorially what the effect of RTN on the  $V_T$  levels is and how it affects the array reliability, for the case of an MLC array. Exponential tails due to RTN extend from the ideal Gaussian distribution, their magnitude increasing with  $N_C$  and time. This results in a reduced separation between adjacent  $V_T$  levels (the so-called window), compromising the accuracy of the read operation and leading eventually to a read failure: the dashed lines in Figure 14 indicate the reference  $V_T$  levels used during read, to which the cell  $V_T$  is compared. When a distribution crosses a reference level, a read error is bound to occur.

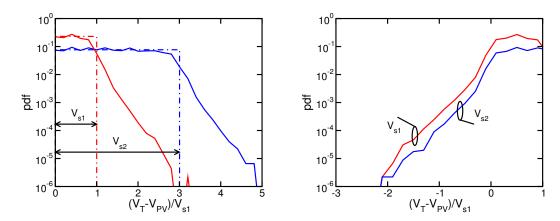

To investigate this issue in more detail, Figure 15 shows the effects of RTN on the programmed  $V_T$  distribution [157] following ISPP and successive read. The left-hand side shows the  $V_T$  pdf right at the end of the ISPP algorithm, for two values of the ISPP step:  $V_{s1}$  and  $V_{s2} > V_{s1}$ . In the ideal case, the algorithm is expected to result in a  $V_T$  distribution exceeding the program-verify level PV by an amount at most equal to the ISPP step (dashed lines in Figure 15). In reality, the distributions are widened by the program noise (not discussed here, see [158,159]) and by RTN and display the characteristic exponential tails. Note that no cell can have  $V_T$  values below the program-verify level, as the algorithm would apply an additional step to them. However, a negative RTN tail also arises as soon as the cells are read (right-hand side of Figure 15). This figure also shows that the RTN tail height is smaller for larger values of the ISPP step; however, increasing its value will lead to an overall larger  $V_T$  distribution. On the other hand, reducing the ISPP step is effective—apart from the increase in program time—only until its value becomes comparable with the RTN distribution width.

**Figure 15.**  $V_T$  pdf at the end of the ISPP operation (**left**) and after a successive read operation (**right**). Results are shown for two values of the ISPP step,  $V_{s1}$  and  $V_{s2} > V_{s1}$ .

#### 3.3. Retention after Cycling and SILC

Data retention specifies the maximum period of time that allows a correct retrieval of stored data, and is determined by the faint but nonzero leakage of electrons from the floating gate. Early experimenters ascribed such leakage to electron tunneling through the dielectric and realized that temperature [160] or bias [161] could be used to accelerate the phenomenon, while devising appropriate design criteria [162-164]. In particular, it was found that a ten-year retention requirement could be satisfied with a minimum tunnel oxide thickness around 3.5–4.5 nm [56,165], much thinner than the 7-8 nm usually adopted. However, the oxide thickness has barely scaled over the many Flash technology generations, remaining far away from its theoretical limit, because it was soon realized [70,166,167] that repeated P/E cycles led to degradation of the tunnel oxide characteristics, enhanced leakage and worse retention. The enhanced oxide leakage at low fields after electrical stress is known as stress-induced leakage current, or SILC [168,169]. SILC has been largely studied on capacitors and described in terms of a trap-assisted tunneling (TAT) process through oxide traps [170–179] (see Figure 17a for a pictorial view of the process), in agreement with experimental evidence [180,181]. In the realm of non-volatile memories, SILC can lead to charge loss/gain from/to the floating gate after stress and to retention errors. To keep this contribution negligible, the oxide thickness of Flash cells has barely scaled with the technology generations, going from about 10 nm in the first prototype [3] to about 7–8 nm in the latest nodes [182]. However, experimental data [183–188] have demonstrated that, even if the SILC is reduced, there is a small number of cells that can exhibit a high leakage after stress, in analogy with the statistical behavior of RTN. An example of this effect is reported in Figure 16, where thin-oxide (6.5 nm) NOR Flash arrays were cycled heavily (10<sup>4</sup> P/E cycles) before being subjected to positive (left) or negative (right) oxide field to induce a  $V_T$  shift [189]: note the distribution tails made up of cells featuring an enhanced leakage with respect to the main part of the distribution, whose shift is due to the intrinsic FN tunnelig current.

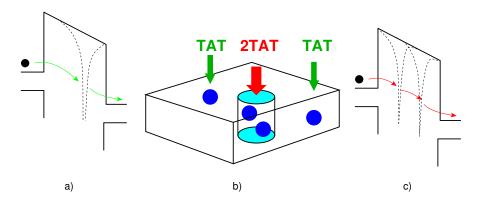

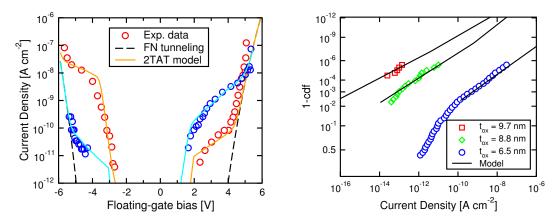

This enhanced leakage, called *anomalous SILC*, has been also identified as a trap-related phenomenon, because of its low activation energy [188,189] and fluctuations resulting from capture/emission processes [185,190]. However, a two-trap assisted tunneling process (2TAT) has now been invoked to explain the experimental data of individual cells [191,192], as depicted in Figure 17c. From this view, a picture of the SILC distribution in a Flash array can be built, assuming a statistical distribution of stress-generated oxide defects (Figure 17b): those cells that happen to have two traps close enough to allow significant tunneling will be affected by anomalous SILC [193,194], while the majority will only experience SILC or the FN tunneling current. Figure 18 shows an example of gate leakage current of two cells affected by anomalous SILC compared with the 2TAT model predictions (left), and (right) the statistical distribution of SILC at a given control-gate bias for different oxide thicknesses, again compared with results of the statistical model. From there, reliability extrapolations can be performed to estimate the number of failures. Other extrapolations procedures have been proposed, based on the same model or on empirical approximations [195–203], while addressing the optimization of the P/E waveforms and cell design [204–207].

**Figure 16.**  $V_T$  cdf over time for 6.5 nm NOR Flash cells arrays after cycling. Positive control-gate bias (5.5 V) was applied in the left-hand side figure, while the right-hand side shows results of a retention experiment [189], © 2001 IEEE.

**Figure 17.** Pictorial view of the SILC distribution in Flash cells. The center picture (**b**) shows a trap distribution in the tunnel oxide region of the cell. One- and two-trap-assisted tunneling mechanisms (respectively TAT and 2TAT) are depicted as (**a**) and (**c**), respectively.

**Figure 18.** (**Left**) average gate current density vs. floating-gate bias for two cells affected by anomalous SILC, together with model predictions; (**Right**) cdf of the array leakage currents at fixed bias for different gate oxide thicknesses and model results. In all cases, symbols = experimental data, lines = model results.

Like all reliability issues, SILC becomes more of a concern in scaled MLCs or TLCs, because of the reduced separation between  $V_T$  levels and smaller floating-gate capacitance, meaning that fewer electrons are stored into the floating gate and that even microscopic leakage currents can cause significant damage. In today's technologies, SILC remains dominant in tail cells [208], that are usually

covered by ECC, while its importance as a reliability issue is somewhat decreased with respect to phenomena affecting the entire distribution, such as the next one [209].

#### 3.4. Charge Detrapping

Early investigators of SILC in stressed oxides observed a transient component in the leakage current, that was attributed to charging and discharging of oxide traps [210–214] and was exploited to extract information on the oxide quality [215,216]. The detrapping current followed a 1/t dependence down to very short times [217], in agreement with tunneling models [218]. The impact of this phenomenon on Flash reliability was first discussed in [219,220], pointing out that the log-time dependence of the  $V_T$  shift could lead to retention errors even in the absence of SILC and could dominate the charge loss with respect to SILC itself [63]. Moreover, as charge is trapped into the oxide during P/E cycling and detrapped in-between, a dependence on the cycling pattern arises, which complicates the development of comprehensive models. Such task began in [221,222] and developed into a full model accounting for the major experimental evidence in [223–225].

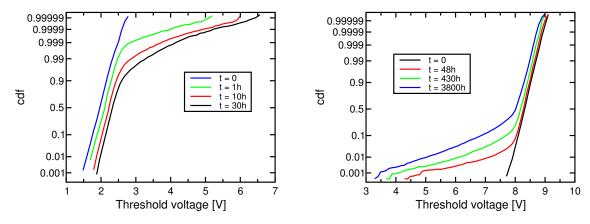

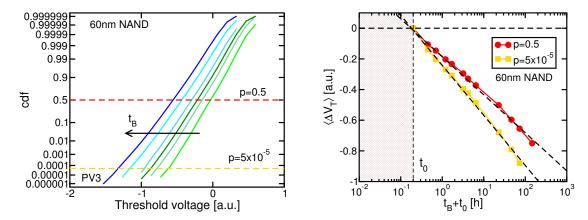

**Figure 19.** (**Left**)  $V_T$  cdf over time for 60 nm NAND Flash cell arrays after cycling; (**Right**)  $V_T$  shift vs. time extracted from the cdfs at fixed probability levels [226], © 2011 IEEE.

## 3.4.1. Main Experimental Data

Figure 19 shows experimental data from a retention experiment at room temperature on a 16 nm NAND vehicle after  $10^4$  P/E cycles [226]. Note the difference with respect to Figure 16 (right): no specific tail is detected here, but rather the entire distribution is affected, although different charge loss rates can be detected between the main part and the lower extreme of the distribution (see right-hand side of Figure 19). Note also the logarithmic dependence on time of  $\Delta V_T$ , which can be fully characterized by its slope  $\alpha$ .

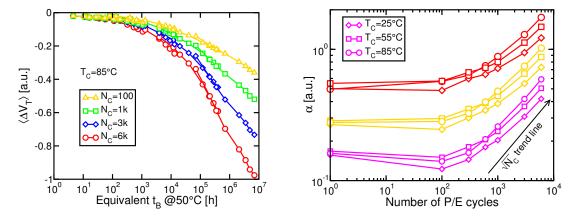

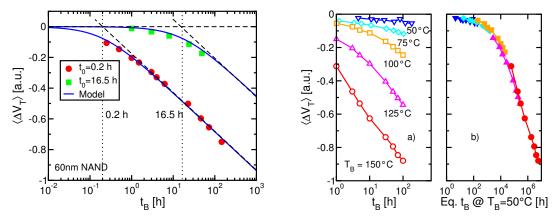

The dependence of charge detrapping on the cycling conditions is reported in Figure 20: its left-hand side shows that  $\Delta V_T$  increases with  $N_C$ , as more electrons are trapped during P/E operations and emitted afterwards. The right-hand side reports the dependence of  $\alpha$  on  $N_C$ : a square-root law was found as soon as the cycling-induced damage overcomes the native detrapping, in agreement with observations on RTN-related defects [138]. This dependence is also independent of the programmed level and temperature (note that the curves for different programmed levels have been vertically shifted to highlight the square-root law and avoid excessive overlap). Figure 21 shows instead the dependence on the bake conditions: note that the detrapping dynamics depend on the time  $t_0$  elapsing between the last program and the first read operation (left-hand side), resulting in a shift of the detrapping curve along the log-time axis by a quantity exactly equal to  $t_0$ . Also,  $\Delta V_T$  depends upon the bake temperature  $T_B$  (right-hand side of Figure 21), demonstrating that detrapping is thermally activated: the  $\Delta V_T$  curves at different  $T_B$  are shifted according to an Arrhenius law with activation energy  $E_A \approx 1.1$  eV [221,222,228,229], a single detrapping curve can be obtained for an equivalent  $T_B$ .

Computers 2017, 6, 16 19 of 55

This value of activation energy had been also observed in earlier retention experiments [51]. Careful account of additional effects which may compromise a reliable extraction of  $E_A$ , such as interface-state and mobility recovery [230,231] or disturbs [232], is required.

**Figure 20.** (**Left**) average  $\Delta V_T$  transients measured on 16 nm NAND Flash arrays for increasing number of P/E cycles [227], © 2016 IEEE; (**Right**) dependence of the slope  $\alpha$  on  $N_C$  for different programmed levels (colors) and temperatures (symbols). Curves for different programmed levels have been vertically shifted for better clarity.

Figure 21. Dependence of  $\Delta V_T$  on bake conditions, namely time  $t_0$  [226], © 2011 IEEE (left) and bake temperature  $T_B$  (right). Data are referred to 60 and 16 nm NAND Flash vehicles. Data on the right-hand side show a) experimental data for different  $T_B$  and b) the same data when  $t_B$  is shifted on log scale according to  $E_A$ .

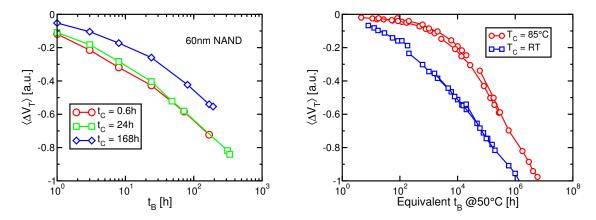

The last data to be discussed relate to the cycling conditions dependence. Figure 22 shows  $\Delta V_T$  for different values of the cycling time  $t_C$  (left) and temperature  $T_C$  (right). Note that a smaller  $\Delta V_T$  is detected if cycling is distributed over a longer period of time or performed at higher temperatures. This is consistent with a picture that assumes electron detrapping between one cycle and the next one, reducing the number of trapped electrons at the end of the last cycle that are then lost during the bake phase. Coherently with this interpretation, the activation energy for cycling was found to be the same as for bake. These findings have important implications for the device reliability, that will be discussed after reviewing the quantitative understanding of the phenomenon together with other experimental data.

Computers **2017**, *6*, 16 20 of 55

**Figure 22.** Dependence of  $\Delta V_T$  on cycling conditions, namely total cycling time  $t_C$  (**left**) and cycling temperature  $T_C$  [227], © 2016 IEEE (**right**).

#### 3.4.2. Models

We start this Section with the description of a compact model [221,222,226] that captures the main features of the data and can be used for some first-order extrapolations, while moving to more refined descriptions of the underlying physics later on. To this aim, we assume a log-time dependence of the  $V_T$  shift that, considering that the first read operation is performed at time  $t_0$  after the end of the cycling phase, leads to

$$\Delta V_T(t_B) = V_T(t_0 + t_B) - V_T(t_0) = -\alpha \ln(t_0 + t_B) + \alpha \ln(t_0) = -\alpha \ln\left(1 + \frac{t_B}{t_0}\right),\tag{9}$$

which is what we observe. The dependences of  $\Delta V_T$  on  $N_C$  and probability level (see Figure 19) can then be simply inserted into the expression of  $\alpha$ . To account for the thermal activation of detrapping during bake, which results in a rigid shift of the detrapping curve in a semilog plot (see right-hand side of Figure 21), we can now modify the expression of the term  $t_0$ , which is the zero-loss intercept of the log-time  $V_T$  curve (see Figure 21, left). This results in:

$$t_0^* = t_0 e^{E_A(1/k_B T_B - 1/k_B T_{ref})}; \quad \Delta V_T(t_B) = -\alpha \ln\left(1 + \frac{t_B}{t_0^*}\right),$$

(10)

where  $t_0$  is now the initial wait time at the reference temperature  $T_{ref}$  and  $k_B$  is the Boltzmann constant. Following this line of thought, even data in Figure 22 can be represented by a dependence of the intercept  $t_0^*$  on cycling conditions. To do this, it is assumed that damage creation during P/E cycles and recovery between them can be described as a fast-cycling experiment (i.e., with negligible delay between cycles) generating the whole oxide damage, followed by a single recovery phase of a certain duration. Combined with the thermal activation term, this results in the final expression

$$t_B^* = t_0^* + At_c e^{E_A(1/k_B T_B - 1/k_B T_C)}; \quad \Delta V_T(t_B) = -\alpha \ln\left(1 + \frac{t_B}{t_B^*}\right),$$

(11)

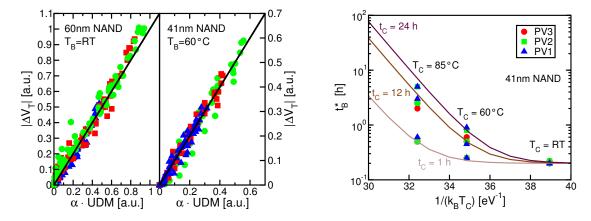

which allows to completely describe the  $\Delta V_T$  dynamics as a function of the various experimental parameters once the fitting parameter A is selected. This means that the term  $\ln(1+t_B/t_B^*)$ , called the *universal damage metric* or UDM, should now account for all  $\Delta V_T$  transients measured on a specific technology, irrespective of cycling and bake conditions. This is demonstrated in Figure 23 (left). Figure 23 (right) shows instead the value of  $t_B^*$  for different cycling conditions.

Computers **2017**, *6*, 16 21 of 55

Figure 23. (Left)  $\Delta V_T$  transients as a function of the UDM term (symbols represent the different programmed levels); (**Right**) Values of the parameter  $t_B^*$  extracted from experimental data (symbols) and Equation (11) (lines) [226], © 2011 IEEE.

The experimental data presented so far and the physical understanding leading to Equation (11) led to the recognition that traditional testing procedures based on fast cycling and long retention times were magnifying the  $V_T$  loss with respect to real usage conditions, when cycling takes place over the functional life of the device (see the effect of increasing  $t_C$  in Figure 22, left). The concept of *distributed cycling* conditions was then proposed in [221] as a way to better emulate the real array behavior by performing either a uniform cycling over a longer time or several groups of fast cycles preceded by bake times, usually at high temperature to accelerate the charge loss. However, the previous model shows its limitations when dealing with highly non-uniform cycling patterns, calling for a more comprehensive interpretation of the trapping/detrapping physics, that was pursued in [223–225,227,233]. Such a model was built upon a few phenomenological assumptions: a Poisson distribution for the number of trapped electrons  $n_t$  and a uniform distribution over a log-time axis of their detrapping time constant  $\tau_d$ . This led to an expression for  $\alpha$  [223,224]

$$\alpha \propto \langle \Delta V_T^1 \rangle \langle n_t \rangle,$$

(12)

which directly links the slope of the  $\Delta V_T$  transient to the product of the average (indicated by the operator  $\langle \cdot \rangle$ )  $\Delta V_T^1$  and  $n_t$ . Via a clever analytical manipulation, an expression for the entire statistical distribution of  $\Delta V_T$  can be obtained:

$$p(\Delta V_T(t)) = \mathscr{F}^{-1} \left\{ e^{\langle n_d(t) \rangle} \left( \mathscr{F} \left\{ p(\Delta V_T^1) \right\} - 1 \right) \right\}, \tag{13}$$

where  $\mathscr{F}$  and  $\mathscr{F}^{-1}$  are the Fourier transform and its inverse and the average number of detrapped electrons,  $\langle n_d(t) \rangle$ , is given by

$$\langle n_d(t) \rangle = \int \langle n_t(\log_{10} \tau_d) \rangle \left( 1 - e^{-t/\tau_d} \right) d \log_{10} \tau_d, \tag{14}$$

an activation energy  $E_A = 1.1$  eV being embedded into  $\tau_d$ . Charge trapping is also inserted in a phenomenological manner, in agreement with the observed square-root dependence on  $N_C$  [221,222], resulting in the following expression for the average number of electrons being trapped at cycle  $N_C$ :

$$\Delta n_t(\tau_d) = \frac{\eta^2}{2\langle n_t(\tau_d, N_C - 1)\rangle}.$$

(15)

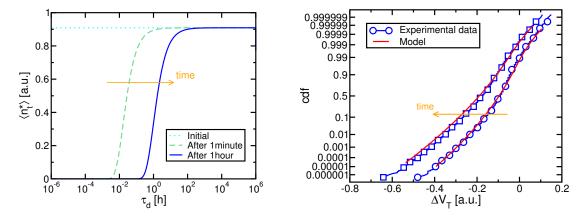

In Equation (15),  $\eta \approx 0.01$  is a fitting parameter, and the expression is modified for small values of  $n_t$  to avoid the divergence in  $\Delta n_t$  (see [224]). Typical results for the  $n_t$  distribution as a function of time (fast cycling conditions, where P/E cycles are conducted before the retention test) are shown

Computers 2017, 6, 16 22 of 55

in Figure 24, left: at a given time t, because of the detrapping term  $1-e^{-t/\tau_d}$  in Equation (14), only electrons having  $\tau_d \ll t$  are detrapped, while those with  $\tau_d \gg t$  are unaffected. Nice agreement with experimental data (Figure 24, right) confirms the validity of this approach.

**Figure 24.** (Left) distribution of  $n_t(\tau_d)$  for different bake times after fast cycling; (Right) comparison between experimental data and model results for  $\Delta V_T$ .

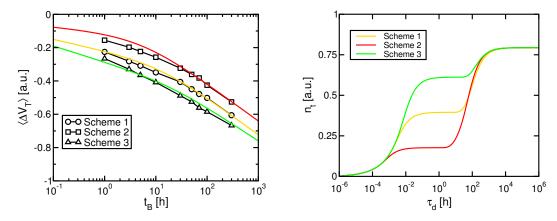

The power of this model can be best appreciated when dealing with so-called *distributed cycling* schemes, where P/E cycles are spread over longer times and separated by bake phases at different temperatures, to emulate the real behavior of a device. Such schemes cannot be managed by the compact expression given by Equation (11), but are easily dealt with by the model synthesized by Equations (12)–(15). As a reference, we take three schemes that are deemed almost equivalent by the model adopted in the JEDEC standard [235] and are depicted in Figure 25: all involve fast-cycling phases at room temperature (marked as blue) separated by high temperature bakes (marked as red). In all cases, the array is subjected to  $N_C = 10k$  cycles, but their distribution over time is different. Results for  $\Delta V_T$  at the end of each process are reported in Figure 26 (left): different  $\Delta V_T$  transients are obtained with the three schemes, featuring nonetheless the same asymptotic slope. The model nicely captures the differences and explains them in terms of the different distributions of  $n_t(\tau_d)$ , as a consequence of the trapping/detrapping phases. Note also that the asymptotic value of  $n_t$  is the same for all schemes, as it is due to the total number of cycles, explaining the uniqueness in the asymptotic slope (see Equation (12)).

**Figure 25.** View of the considered distributed-cycling schemes that are almost equivalent from the viewpoint of the JEDEC standard [236].

Computers 2017, 6, 16 23 of 55

Figure 26. (Left) comparison between experimental data (symbols) and model results (lines) for  $\Delta V_T$  after the distributed cycling schemes in Figure 25 [234], © 2014 IEEE; (**Right**) distribution of  $n_t(\tau_d)$  at the end of the cycling schemes.

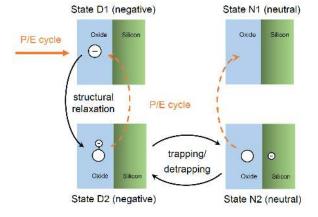

Although the above-mentioned model is successful in describing distributed-cycling procedures and provides a useful support for developing appropriate qualification schemes, it still misses some features, namely the programmed-level dependence of charge detrapping and  $\alpha$ . In particular, it was noted that charge detrapping is enhanced with the oxide electric field and that little or no detrapping takes place during bake phases performed with cells in the erased state [227,237], suggesting that holes may play a non-negligible role in what is usually described as an electron-only detrapping process [238]. These developments led to a recent refinement of the above-mentioned model [225,233] that goes beyond the classical vision of pure charge detrapping, considering multiple-state defects related to structural relaxation of the oxide network. A pictorial view of the proposed defect states can be seen in Figure 27, where the lower states D2 and N2 represent the usual trapping/detrapping phenomena, for which the model discussed so far still holds (besides a minor modification to account for trapping). Now, however, the reservoir for charged defects that can exchange electrons with the substrate (state D2) is dictated by a structural relaxation process from an initial state D1 generated by P/E cycling, allowing a higher degree of flexibility in the description of the  $\Delta V_T$  transients. By assigning a log-time distribution to the structural relaxation time constants while retaining nearly-constant values for the trapping and detrapping time constants (whose ratio is assumed to be affected by the oxide field), a greatly improved fitting was achieved, even over fine details of the experimental data. However, the assumptions of the model still need further investigations to be confirmed, and charge detrapping is likely to remain an active area of research in Flash reliability for quite some time to come.

**Figure 27.** Pictorial view of the multiple-state defects responsible for charge trapping/detrapping according to [225,227,233].

Computers 2017, 6, 16 24 of 55

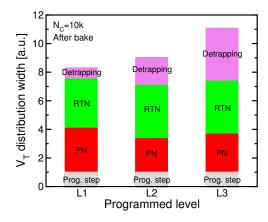

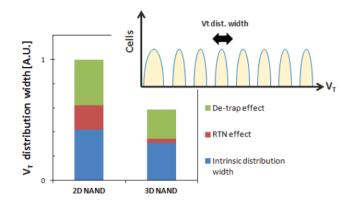

#### 3.4.3. Effect on $V_T$ Distribution after Cycling

From the previous results, it is clear that charge detrapping leads to both an average charge loss and an enlargement of the  $V_T$  distribution, due to the randomness of the detrapping process. A comparative analysis of the impact of charge detrapping on the width of the  $V_T$  distribution after cycling and bake was reported in [239] and shown in Figure 28, normalized to the ISPP step  $V_s$ . The two bottom-most contributions are related to the time-0 placement of the  $V_T$  distribution—namely, the ISPP step  $V_s$  and the fluctuation in the number of injected electrons per step [158,159,240]—and are not discussed here. The remaining part is made up of a native RTN contribution plus the additional terms induced by cycling. Note that RTN is not dependent on the  $V_T$  level while detrapping increases with such level, as previously discussed, becoming a non-negligible error source for the higher  $V_T$  levels. A similar breakdown of the distribution width was presented in [241], without accounting for detrapping. Other studies also identified charge detrapping as the dominant error source in highly-cycled NAND samples [242].

**Figure 28.** Contributions to the width of the  $V_T$  distribution after cycling and bake for different programmed levels [239], © 2015 IEEE.

To overcome this limitation, several solutions have been proposed, including a dummy read [243] or a moving reference [244] scheme and a *self-healing* approach [245], where a built-in heater in the proximity of the tunnel oxide is used to accelerate damage recovery and prolong the endurance. The insertion of specific block healing cycles during run time was shown to increase lifetime and performance of NAND devices [246], suggesting that distributed healing schemes could be devised to maximize their efficacy while reducing the energy dissipation of such cycles [247].

# 3.5. Interface State Recovery

In analogy with oxide defects, interface states are created during P/E cycles and recover in-between. Besides their effect on the endurance figure of NAND devices, discussed in Section 3.1, they also influence the  $V_T$  shift after cycling. In fact, it has been proposed that interface state recovery represents the major source of  $V_T$  instability in 90 nm NAND Flash [63,209,248]. Interface state annealing manifests itself via a reduction of the activation energy, down from the 1.1 eV associated to detrapping to about 0.7 eV [230,231] or even 0.15 eV [249], and are also characterized by a non-uniform distribution over the cell area, usually peaked at the STI edges [74,250]. However, it has been suggested that their effect is dominant for high values of the read current only [230,231], while playing a minor role with respect to charge detrapping as the read current is reduced.

#### 3.6. Disturbs

The arrangements of Flash cells into compact arrays implies that many cells other than the selected ones are biased during read and program operations. Although such biases should not affect the

Computers **2017**, *6*, 16 25 of 55

cell state, degradation in the tunnel oxide characteristics following P/E cycling can reduce the cell immunity to such disturbs. The NAND layout generates three types of disturbs, namely related to the read, program and pass operation, that are discussed hereafter.

#### 3.6.1. Read Disturb

The bias condition of a NAND block during read has been discussed in Section 2.2 and is shown in Figure 29: a suitable read voltage is applied to the selected WLs to sense whether the cells in the page are in the on or off condition, while all other cells in the string are biased to a pass voltage higher than their maximum  $V_T$ . The pass bias is hence analogous to a program operation, albeit performed at a lower gate bias, and as such it can induce a  $V_T$  shift in the cells. This *read disturb* (RD) cumulates with the number of read operations and could eventually lead to a failure. Note that this is a recoverable error, that is nulled after the block is erased and reprogrammed.

Figure 29. NAND array bias condition during read. Cells subjected to RD are circled.

The oxide thickness and bias conditions are designed to assure that no significant  $V_T$  shift is expected after RD. However, this might no longer be the case after heavy P/E cycling, when the gate oxide quality is degraded and SILC and charge detrapping arise, enhancing the conduction at low fields (see the I–V characteristics in Figure 18, left). RD is hence exacerbated in cycled cells [251–253] and in read-intensive applications such as database access, explaining why a lower endurance is sometimes specified in such cases.

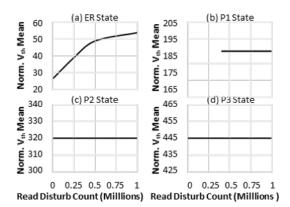

Experimental data for the memory lifetime report a power-law dependence on  $N_C$ , with exponent ranging from -0.3 to -0.4 [251,254]. Data for the  $V_T$  shift as a function of the number of reads feature different dependences [255,256], while raw bit-error rate (RBER) data vs. the number of reads reveal a linear dependence whose slope increases with cycles [60,255,257], with a higher BER observed on SLCs than on MLCs. As with SILC, several process optimization [258,259], voltage tuning [255,260] or system-level correction [261] proposals have been put forward to alleviate the issue.

Typical RD characteristics are reported in Figure 30 [255]: the  $V_T$  shift is larger for the erased state and decreases for higher programmed  $V_T$  levels, in agreement with the reduction on the tunnel oxide field. As a consequence, more errors are expected in the logical pages corresponding to those states. It has also been found [262] that repeated RD on partially-programmed blocks leads to an increased BER when the remaining pages are programmed, suggesting that extensive RD can lead to

Computers **2017**, *6*, 16 26 of 55

a degradation of the program characteristic of the cell. In any case, it has been claimed [61] that RD errors are not the prevalent ones in SSDs used in servers.

**Figure 30.** (**Left**)  $V_T$  distribution for increasing RD time; (**Right**) mean  $V_T$  shift of the different levels as a function of the number of reads [255], © 2015 IEEE.

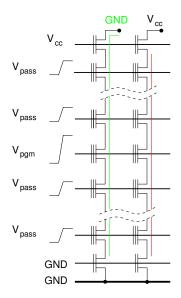

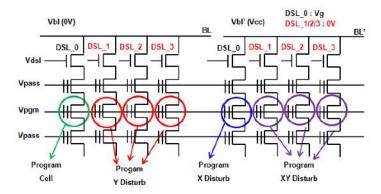

# 3.6.2. Program and Pass Disturbs

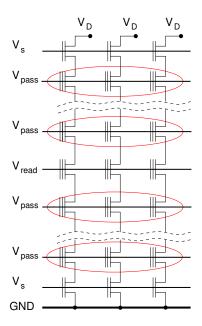

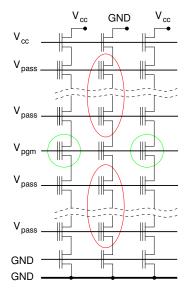

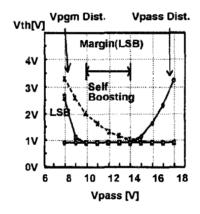

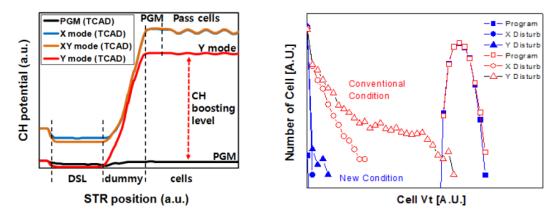

When programming a page, we must ensure that only the desired BLs are actually programmed, while other cells on the same page that must remain in their original state are not affected by such operation. Since electrons are injected into the floating gate via FN tunneling, which is a process strongly dependent on the oxide field, we can inhibit programming by reducing such a field, i.e., the gate-to-channel voltage drop. The simpler solution is to disconnect (i.e., ground) the SSL (see Figure 1) and raise the inhibited BLs to a high voltage [263,264], while biasing the unselected WLs too, to avoid unintentional erase. However, this solution was soon abandoned because of power and time issues related to the charging of highly-capacitive BLs and because of high-voltage limitations in scaled technologies. In replacement, a *self boosting* technique was proposed [265], illustrated in Figure 31: BLs to be programmed are grounded, which turns on their DSL and maintains the string channel to ground (green line). Note that a pass voltage (different from the one used during read) is applied to the unselected WLs. Inhibited BLs, instead, are biased at  $V_{cc}$ , which precharges their channel. When the high passing voltage is applied to the WLs, however, the channel potential (red line) is lifted by capacitive coupling, turning off the DSL and reaching a value high enough to suppress electron injection into the floating gate.

This solution generates two kinds of disturbs, highlighted in Figure 32: a program disturb on the cells on the programmed WL (encircled in green), related to the potential difference between program and boosted bias, and a pass disturb on the cells located on the same (grounded) BL as the programmed ones (red circles), related to the pass voltage. The nature of such disturbs is just the same as the RD, namely a soft-programming at low voltage, with the difference that now the applied field is higher with respect to RD, while the number of cycles is significantly lower. Note also that an increase in the pass voltage will lead to an increase in the channel potential, reducing the program disturb but raising the pass one. This typical behavior is shown in Figure 33 (left). While a logarithmic dependence of  $V_T$  on the number of cycles has been reported [266], the dependence of BER is more complex, as shown on the right of Figure 33 [257]. To limit the pass disturb, improved boosting schemes have been developed, including local boosting [36,267], ramped WL voltage [268], dynamic pass voltage biasing [269] or negative WL pre-biasing [270]. Interestingly, a self-boosting scheme during read was also proposed, to alleviate read-disturb issues [271].

Computers **2017**, *6*, 16 27 of 55

Figure 31. NAND array bias condition during program, highlighting the self-boosting effect.

**Figure 32.** NAND array bias condition during program. Cells subjected to program (green) and pass (red) disturbs are circled.

Computers 2017, 6, 16 28 of 55

**Figure 33.** (Left)  $V_T$  shift due to program and pass disturbs as a function of the pass voltage [36], © 1996 IEEE; (**Right**) BER due to program disturb as a function of the number of P/E cycles [257], © 2009 ACM.

The boosting operation in scaled NAND devices is also responsible for additional reliability concerns. First, the string select transistors must withstand the boosted potential with minimum leakage current, as such current will discharge the channel and increase program disturb (for this reason, such devices are hard to scale). However, under program inhibit conditions, the SSL transistor is subjected to gate-induced drain leakage (GIDL) due to band-to-band tunneling, injecting hot electrons toward the first WL (see Figure 32) and into its floating gate, when erased [266]. This effect leads to an enhanced program disturb at the first WL and is usually curbed by increasing the SSL-to-WL spacing [266] or employing one [272] or two [273] dummy edge WLs. In fact, because of short-channel effects in scaled technologies, the actual electron injection point into the floating gate can move farther into the string, affecting even inner cells [274]. Moreover, such hot carriers may be trapped into the oxide and be subsequently released, giving rise to detrapping-related retention degradation [275]. The full picture is further complicated by electrostatic coupling between adjacent strings, via the STI isolation: when a string is programmed, its channel is kept at zero voltage and it will behave like the gate of a parasitic transistor whose gate oxide is the STI isolation. Adjacent inhibited cells will therefore experience large vertical GIDL current, between the (boosted) surface of the channel and its bulk [276]. Air-gap isolation as well as optimization of channel implant and STI depth uniformity [277] have been suggested as remedies. A related effect has been noted in [278], where a negative  $V_T$  shift contribution was found and explained in terms of hot-hole injection from the STI edge to the control-gate [279,280]. All this suggests that the detailed leakage mechanisms affecting the boosted channel potential must be studied with extreme care [281].

In local self-boosting schemes, where the channel of the programmed WL is isolated from the rest of the string by grounding the neighboring WLs and is boosted by the programmed Wl, other issues arise, such as hot-electron injection via drain-induced barrier lowering (DIBL) [282,283], that paved the way for proposals of hot-carrier based programming of NAND cells [284,285].

In conclusion, this overview demonstrates that many reliability issues have threatened the scaling of the planar NAND technology. In turn, its successful scaling down to the 15 nm node is a tribute to the effectiveness of the many different solutions adopted to keep the failure rate under control. NAND-based SSDs are today the main candidates for mass storage, having reached reliability performance comparable to, or in some aspects even better than, HDDs [62]. In the following, we will extend this discussion to the current leading-edge technology for NAND: 3D.

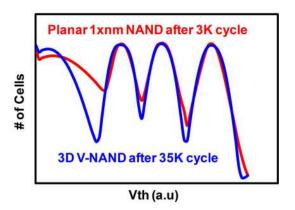

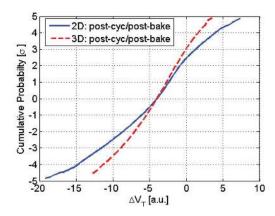

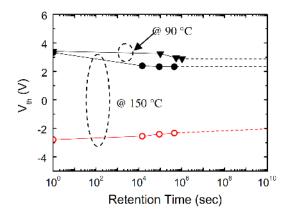

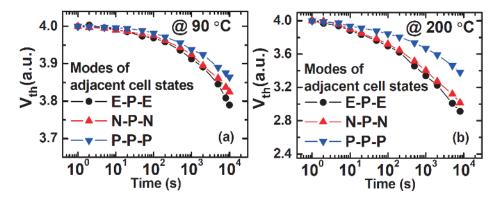

#### 4. 3D NAND Reliability

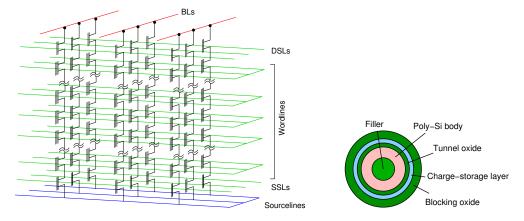

In this Section, we will mainly focus our attention on the most promising 3D NAND architecture, i.e., the one based on vertical strings of cells and parallel planes connecting the control gates [23–25].

Computers **2017**, *6*, 16 29 of 55

A schematic view of the memory array organization is shown in Figure 34 (left), but we will leave the details about the array operation to the specific literature [28]. The individual cell is a vertical-channel transistor with polysilicon body, usually shaped as a hollow cylinder filled with dielectric [286], whose cross-section is depicted on the right of Figure 34. Such a device was shown to exhibit superior performance with respect to a conventional vertical nanowire transistor, because of the high defectivity in the central region that plagued the performance of the latter structure. The gate stack of today's 3D NAND can be based on either a floating gate [23,287–291], similar to planar NAND devices, or a charge-trap stack similar to an oxide/nitride/oxide (ONO) layer, where the charge is stored in traps within the nitride layer [10,11,22,292].