# Research Article Resistance Switching Characteristics in ZnO-Based Nonvolatile Memory Devices

# **Fu-Chien Chiu**

Department of Electronic Engineering, Ming Chuan University, Taoyuan 333, Taiwan

Correspondence should be addressed to Fu-Chien Chiu; fcchiu@mail.mcu.edu.tw

Received 27 September 2013; Accepted 7 November 2013

Academic Editor: Chun-Hsing Shih

Copyright © 2013 Fu-Chien Chiu. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Bipolar resistance switching characteristics are demonstrated in Pt/ZnO/Pt nonvolatile memory devices. A negative differential resistance or snapback characteristic can be observed when the memory device switches from a high resistance state to a low resistance state due to the formation of filamentary conducting path. The dependence of pulse width and temperature on set/reset voltages was examined in this work. The exponentially decreasing trend of set/reset voltage with increasing pulse width is observed except when pulse width is larger than 1 s. Hence, to switch the ZnO memory devices, a minimum set/reset voltage is required. The set voltage decreases linearly with the temperature whereas the reset voltage is nearly temperature-independent. In addition, the ac cycling endurance can be over  $10^6$  switching cycles, whereas, the dependence of HRS/LRS resistance distribution indicates that a significant memory window closure may take place after about  $10^2$  dc switching cycles.

## 1. Introduction

Developments of next generation nonvolatile memory (NVM) devices are required because the physical limitations of traditional Flash memory devices are approaching. In recent years, the resistance random access memory (RRAM) device has attracted a great deal of attention for the next generation NVM applications [1]. Since the RRAM technology is well compatible with the complimentary metal oxide semiconductor (CMOS) process [2], the scaling of RRAM devices may keep on in terms of the low power operation. This benefit will bring a strong cost-competitiveness to RRAM. In addition, the advantages of RRAM include small cell size, simple cell structure, high switching speed, high operation durability, multi state switching, and threedimensional architecture [1-5]. The resistance switching behavior has been reported for a variety of materials such as perovskite-type oxides [1, 3], binary metal oxides [2-4], solid-state electrolytes [4], organic compounds [6], and amorphous Si [7]. In these RRAM materials being studied, binary metal oxides are most potential due to their simple constituents, good compatibility with CMOS processes, and resistive nature to thermal/chemical damages [2, 4, 8].

In this work, Pt/ZnO/Pt capacitors were fabricated and investigated for the NVM applications. The dependence of pulse width and temperature on set/reset voltages was examined. Experimental results show that a minimum set/reset voltage is required to switch the ZnO memory devices. The exponential decreasing trend of set/reset voltage with increasing pulse width is observed except when pulse width is larger than 1 s. The set voltage decreases linearly with the temperature, whereas the reset voltage is almost temperature independent. In addition, the resistance values both at high resistance state (HRS) and low resistance state (LRS) in different Pt/ZnO/Pt memory devices were characterized. The dependence of HRS/LRS resistance distribution on set/reset switching cycles indicates that the memory window begins to close after about 100 voltage sweeping cycles. Although the dc cycling endurance is detrimental, the ac cycling endurance over 10<sup>6</sup> switching cycles can be achieved.

## 2. Experiment

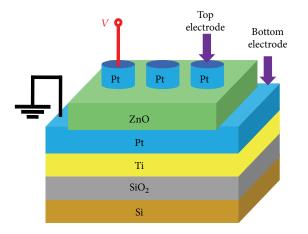

In this work, the sample structure of the resistive switching memory devices is metal insulator metal (MIM) capacitor, as indicated in Figure 1. The ZnO film was deposited on

FIGURE 1: Schematic structure of Pt/ZnO/Pt and configuration of electrical measurement.

Pt/Ti/SiO<sub>2</sub>/Si substrates by *rf* magnetron sputtering at room temperature. The ZnO film thickness is 25 nm. The sputtering power is 40 W. The working pressure is  $5 \times 10^{-3}$  Torr in Ar ambient with a flow rate of 25 sccm. Pt top electrode was then defined by *rf* magnetron sputtering through a metal shadow mask. The electrical properties of the fabricated Pt/ZnO/Pt memory devices were characterized under dark condition by using Agilent 4156C semiconductor parameter analyzer and Agilent 8110A pulse pattern generator, as well as Barth 4002 transmission line pulse generator. During the electrical characterizations, the bias voltage (or current) was applied on the top electrode with the bottom electrode grounded.

### 3. Results and Discussion

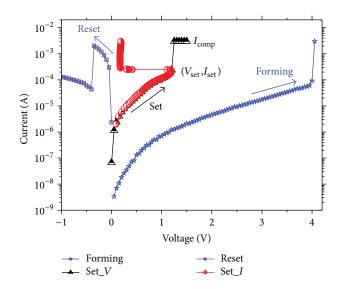

In this work, an initial forming process is required to achieve the bipolar resistance switching behavior on the virgin memory cells. Typical I-V switching characteristics in the Pt/ZnO/Pt memory devices are shown in Figure 2. The forming voltage is about 4 V. After the forming process, the memory device is in low resistance state (LRS). By sweeping the voltage in negative side without a current compliance ( $I_{comp}$ ), the device current decreases suddenly at a reset voltage  $(V_{reset})$  or a reset current  $(I_{reset})$ , and the device is switched from an LRS to an HRS. This event is defined as the reset process. Then applying the voltage in positive side, an abrupt increase of the device current takes place at a set voltage ( $V_{set}$ ) or a set current ( $I_{set}$ ). The  $V_{\rm set}$  triggers the memory cell from an HRS to an LRS, which is defined as the SET process. Obviously, the  $V_{\rm set} \sim$ 1 V should be larger than  $V_{\rm reset} \sim -0.5$  V, and the  $I_{\rm set} \sim 2$  ×  $10^{-4}$  A should be smaller than the  $I_{\rm reset} \sim 2 \times 10^{-3}\,{\rm A}$  . Since the resistance switching depends on the polarity of applied voltage, the resistance switching in Pt/ZnO/Pt structure is bipolar. The bipolar resistance switching is also found in doped ZnO films with sulfur, cobalt, or manganese [9, 10] and in the structure of TiN/ZnO/Pt [11]. In addition, the unipolar resistance switching can be observed in the structures of Al/ZnO/Al [12] and Cu/ZnO/n<sup>+</sup>-Si [13]. Even both unipolar

FIGURE 2: Typical current-voltage switching characteristics in Pt/ZnO/Pt memory cells. The set process can be performed by voltage sweep (Set\_V) or current sweep (Set\_I).

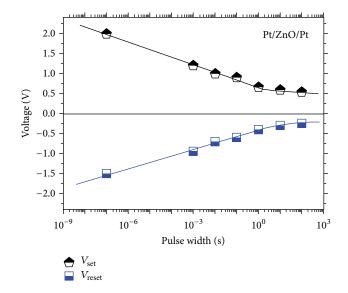

and bipolar resistance switchings may coexist in the structure of Ag/ZnO/Pt [14]. The voltage-biased set process results in a sudden current jump at  $V_{\text{set}}$ , which causes the memory cell to switch from an HRS to an LRS. If, however, the set process is performed by the current sweeping, a negative differential resistance or snapback characteristic may be observed [15]. When the memory cell is switched from an HRS to an LRS at  $V_{\text{set}}$  (or  $I_{\text{set}}$ ), the current transports through quite low resistance immediately due to the conductive filaments formed between two electrodes and then the voltage across the memory cell begins to decrease significantly resulting in the *I-V* snapback characteristic (indicated by Set\_*I*) as shown in Figure 3. Accordingly, the current-biased set I-V curve is much different from the voltage-biased one after the onset of resistance switching from an HRS to an LRS, because the voltage will continue to increase during the voltage sweep mode (indicated by  $Set_V$ ). Note that the I-V snapback phenomena can be often observed in the electrostatic discharge (ESD) protection devices [16] and even in ultrathin SiO<sub>2</sub> films [17]. Since the electric-pulse-induced resistance switching could be significantly affected by the ac voltage pulse width  $(W_{ac})$ , the relationship between set/reset switching voltage and  $W_{\rm ac}$  was examined. In this work, both  $V_{\rm set}$  and  $V_{\rm reset}$  decrease with increasing  $W_{\rm ac}.$  An exponential relationship between  $V_{set}/V_{reset}$  and  $W_{ac}$  can be observed for the condition of low  $W_{ac}$  (10<sup>-7</sup> to 10<sup>0</sup> s), as shown in Figure 3. Meanwhile, a critical threshold voltage is approached for large  $W_{ac}$  (>1 s) [4]. This implies that a minimum set/reset voltage is required to switch the ZnO memory devices. The thresholds  $V_{\text{set}}$  and  $V_{\text{reset}}$  are about 0.55 V and -0.25 V, respectively.

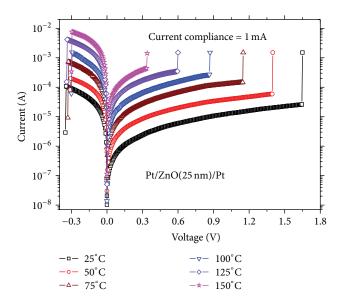

Figure 4 shows the temperature dependence of I-V characteristics both in HRS and LRS. Experimental results show that the device current increases with increasing temperature both in HRS and LRS. According to the temperature dependence of I-V characteristics [18], the conduction

FIGURE 3: Dependence of ac voltage pulse width on set voltage ( $V_{set}$ ) and reset voltage ( $V_{reset}$ ).

FIGURE 4: Temperature dependence of current-voltage characteristics on Pt/ZnO/Pt devices.

mechanism in Pt/ZnO/Pt structure is dominated by the hopping conduction in HRS. The hopping conduction is not the electrode-limited conduction mechanism but the bulklimited conduction mechanism [19]. The electrode-limited conduction mechanism depends on the electrical properties at the electrode-dielectric contact. However, the bulk-limited conduction mechanism depends only on the properties of the dielectric itself. This may imply that the resistance switching mechanism in Pt/ZnO/Pt structure is not the interface type but the filament type. In addition, the device current is enhanced at the elevated temperature in HRS. Consequently, the switching voltage is lowered by the energy requirement of conductive filament formation. Due to the thermally assisted current conduction, the set voltage decreases with

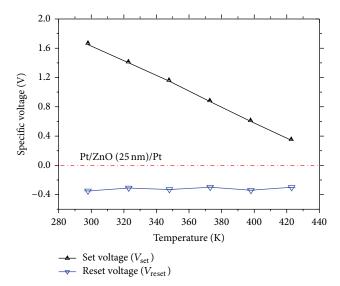

FIGURE 5: Temperature dependence of set voltage  $(V_{\rm set})$  and reset voltage  $(V_{\rm reset})$  on Pt/ZnO/Pt devices.

FIGURE 6: *I*-*V* characteristics before and after the test of dc cycling endurance performed by voltage sweepings at room temperature.

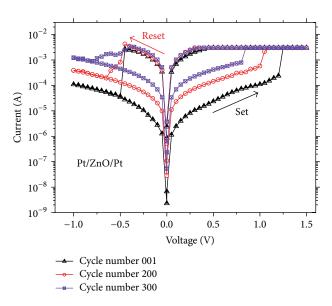

increasing temperature. Figure 5 shows that the set voltage decreases linearly with the temperature, whereas the reset voltage is almost temperature independent. The constant reset voltage is also observed during the dc cycling endurance tests performed by voltage-biased set/reset switching for the Pt/ZnO/Pt memory devices. Figure 6 shows the *I*-V curves before and after the test of dc cycling endurance performed by voltage sweepings at room temperature. The reset voltage during the test of dc cycling endurance keeps approximately constant. The uniform  $V_{\text{reset}}$  value suggests that the dominant reset process may result from the same rupture place in the conducting filamentary paths [3] leading to the dramatic current drop between both electrodes. Note that the  $I_{\text{comp}}$  of 3 mA was set to prevent the permanent breakdown of

FIGURE 7: Weibull plots of HRS/LRS resistances during dc switching endurance for Pt/ZnO/Pt memory devices.

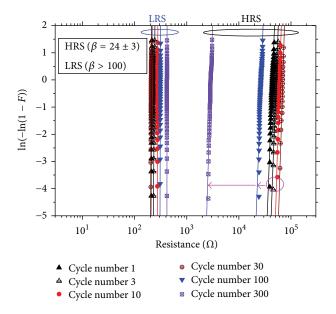

the memory devices during the set processes. On the contrary, no  $I_{\rm comp}$  was set for the reset process. As shown in Figure 6, the HRS/LRS resistance ratio is on the order of  $10^2-10^3$  before the test of dc cycling endurance. Whereas the current in HRS increases after about 100 dc voltage sweeping cycles, which results in the change of HRS/LRS resistance ratio. Figure 7 shows the Weibull cumulative distributions of HRS/LRS resistance (R<sub>HRS</sub> /R<sub>LRS</sub>) values versus the cycle numbers of dc switching endurances for different Pt/ZnO/Pt memory devices. The Weibull distribution function is frequently used in semiconductor failure analysis and can be expressed as [20]

$$F(Q) = 1 - \exp\left[-\left(\frac{Q}{\alpha}\right)^{\beta}\right],$$

$$W(Q) \equiv \ln\left[-\ln\left(1 - F\right)\right] = \beta \ln\left(\frac{Q}{\alpha}\right),$$

(1)

where F(Q) is the cumulative distribution function of failure, Q is the resistance value either in HRS or LRS,  $\alpha$  is the HRS/LRS resistance value at approximately 63rd percentile, and  $\beta$  is the Weibull shape factor, often called Weibull slope. Usually,  $\ln[-\ln(1 - F)]$  is plotted as a function of Q and this will yield a straight line. In this work, the Weibull slope  $(\beta)$  was estimated by the method of maximum likelihood estimation [21]. The  $\beta$  values for memory devices in LRS are very large, which means that the LRS resistance  $(R_{LRS})$  values are extremely centered. As the dc switching cycles increase, the  $R_{LRS}$  nearly keeps constant even though  $R_{LRS}$  increases slightly with the switching cycle. Meanwhile, the  $\beta$  values for memory devices in HRS are much smaller than those in LRS. This means that the HRS resistances  $(R_{HRS})$  have a relatively broad distribution. In addition, the  $R_{\rm HRS}$  values begin to increase significantly after 100 dc switching cycles, as indicated in Figure 7. Therefore, the memory window

FIGURE 8: Memory window between HRS and LRS as a function of the number of dc/ac switching cycles for Pt/ZnO/Pt devices.

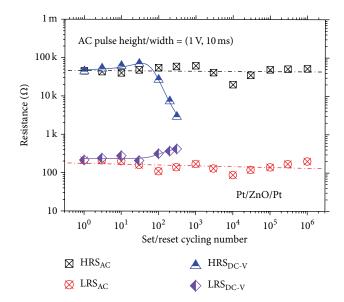

begins to close after about 100 voltage-biased switching cycles. As indicated in Figure 8, the memory window between HRS and LRS is a function of the number of switching cycles. The dc cycling endurance is very detrimental, whereas the ac cycling endurance over  $10^6$  switching cycles can be achieved. In the case of dc cycling endurance, the dc forward sweeping voltage may set the memory device into the soft breakdown mode in which the dielectric is stressed by a large compliance current (3 mA). This high stress may result in the dielectric degradation and therefore memory window closing. As the test of ac cycling endurance, the switching between HRS and LRS is highly controlled, reversible, and reproducible. The memory window shows no degradation after 10<sup>6</sup> ac switching cycles, as shown in Figure 8. In this work, the alternate ac voltage pulses of +1 V and -1 V were applied per 10 ms in the test of ac cycling endurance. The relatively large pulse width (10 ms) was used for worse case. Experimental results showed that ac endurance could be at least higher than 10<sup>6</sup> switching cycles. This implies that the ZnO thin film is very potential in future nanoscale nonvolatile memory applications. Based on the cycling endurance tests, the serious reliability issue in the dc type is highlighted.

#### 4. Conclusions

In summary, bipolar resistance switching characteristic was revealed in Pt/ZnO/Pt memory devices. The dependence of pulse width on set/reset voltages indicates that a minimum set/reset voltage is required to switch the memory cells. The set voltage decreases linearly with the temperature, whereas the reset voltage is nearly temperature independent. The dependence of HRS/LRS resistance distribution shows that the memory window closure may occur after about 100 dc switching cycles. The ac cycling endurance shows that no degradation is observed after 10<sup>6</sup> cycles, which is potential in future nanoscale nonvolatile memory applications.

#### **Conflict of Interests**

The author declares that there is no conflict of interests regarding the publication of this paper.

#### Acknowledgments

The author thanks the National Science Council, Taiwan, for supporting this work under Contract no. NSC 102-2221-E-130-015-MY2. He also thanks Mr. Peng-Wei Li and Dr. Wen-Yuan Chang for the technical assistance.

### References

- W. W. Zhuang, W. Pan, B. D. Ulrich et al., "Novell colossal magnetoresistive thin film nonvolatile resistance random access memory (RRAM)," in *Proceedings of the 48th IEEE International Electron Devices Meeting (IEDM '02)*, pp. 193–196, December 2002.

- [2] H. Akinaga and H. Shima, "Resistive random access memory (ReRAM) based on metal oxides," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2237–2251, 2010.

- [3] A. Sawa, "Resistive switching in transition metal oxides," *Materials Today*, vol. 11, no. 6, pp. 28–36, 2008.

- [4] R. Waser, R. Dittmann, C. Staikov, and K. Szot, "Redoxbased resistive switching memories nanoionic mechanisms, prospects, and challenges," *Advanced Materials*, vol. 21, no. 25-26, pp. 2632–2663, 2009.

- [5] D. L. Lewis and H.-H. S. Lee, "Architectural evaluation of 3D stacked RRAM caches," in *Proceedings of the IEEE International Conference on 3D System Integration (3DIC '09)*, September 2009.

- [6] M. Cölle, M. Büchel, and D. M. de Leeuw, "Switching and filamentary conduction in non-volatile organic memories," *Organic Electronics*, vol. 7, no. 5, pp. 305–312, 2006.

- [7] S. H. Jo, K.-H. Kim, and W. Lu, "Programmable resistance switching in nanoscale two-terminal devices," *Nano Letters*, vol. 9, no. 1, pp. 496–500, 2009.

- [8] I. G. Baek, M. S. Lee, S. Seo et al., "Highly scalable nonvolatile resistive memory using simple binary oxide driven by asymmetric unipolar voltage pulses," in *Proceedings of the 50th IEEE International Electron Devices Meeting (IEDM '04)*, pp. 587–590, December 2004.

- [9] M. Villafuerte, S. P. Heluani, G. Juárez, G. Simonelli, G. Braunstein, and S. Duhalde, "Electric-pulse-induced reversible resistance in doped zinc oxide thin films," *Applied Physics Letters*, vol. 90, no. 5, Article ID 052105, 2007.

- [10] Y. C. Yang, F. Pan, Q. Liu, M. Liu, and F. Zeng, "Fully room-temperature-fabricated nonvolatile resistive memory for ultrafast and high-density memory application," *Nano Letters*, vol. 9, no. 4, pp. 1636–1643, 2009.

- [11] N. Xu, L. Liu, X. Sun et al., "Characteristics and mechanism of conduction/set process in TiN/ZnO/Pt resistance switching random-access memories," *Applied Physics Letters*, vol. 92, no. 23, Article ID 232112, 2008.

- [12] S. Kim, H. Moon, D. Gupta, S. Yoo, and Y.-K. Choi, "Resistive switching characteristics of Sol-Gel Zinc oxide films for flexible

- [13] Z. Ji, Q. Mao, and W. Ke, "Effects of oxygen partial pressure on resistive switching characteristics of ZnO thin films by DC reactive magnetron sputtering," *Solid State Communications*, vol. 150, no. 39-40, pp. 1919–1922, 2010.

- [14] S. Lee, H. Kim, J. Park, and K. Yong, "Coexistence of unipolar and bipolar resistive switching characteristics in ZnO thin films," *Journal of Applied Physics*, vol. 108, no. 7, Article ID 076101, 2010.

- [15] D. C. Kim, S. Seo, S. E. Ahn et al., "Electrical observations of filamentary conductions for the resistive memory switching in NiO films," *Applied Physics Letters*, vol. 88, no. 20, Article ID 202102, 2006.

- [16] A. Amerasekera and C. Duvvury, *ESD in Silicon Integrated Circuits*, John Wiley & Sons, Chichester, UK, 2nd edition, 2002.

- [17] T. P. Chen, M. S. Tse, and X. Zeng, "Snapback behavior of the postbreakdown I-V characteristics in ultrathin SiO<sub>2</sub> films," *Applied Physics Letters*, vol. 78, no. 4, pp. 492–494, 2001.

- [18] F.-C. Chiu, P.-W. Li, and W.-Y. Chang, "Reliability characteristics and conduction mechanisms in resistive switching memory devices using ZnO thin films," *Nanoscale Research Letters*, vol. 7, article 178, 2012.

- [19] F. C. Chiu, "A review on conduction mechanisms in dielectric films," Submitted to Advances in Materials Science and Engineering, Article ID 578168.

- [20] F.-C. Chiu, "Thickness and temperature dependence of dielectric reliability characteristics in cerium dioxide thin film," *IEEE Transactions on Electron Devices*, vol. 57, no. 10, pp. 2719–2725, 2010.

- [21] E. L. Lehmann, *Theory of Point Estimation*, John Wiley & Sons, New York, NY, USA, 1983.

Smart Materials Research

**Research** International

Journal of Nanoscience

Scientifica

Journal of Crystallography

**The Scientific** World Journal

Journal of Ceramics