Open access • Journal Article • DOI:10.1109/EDL.1985.26258

## Resonant tunneling transistors with controllable negative differential resistances — Source link

A. R. Bonnefoi, T. C. McGill, Robert D. Burnham

Institutions: California Institute of Technology

Published on: 01 Dec 1985 - IEEE Electron Device Letters (IEEE)

Topics: Resonant-tunneling diode, Negative resistance, Quantum tunnelling, Schottky barrier and Field-effect transistor

Related papers:

- A New Functional, Resonant-Tunneling Hot Electron Transistor (RHET)

- · Quantum-well resonant tunneling bipolar transistor operating at room temperature

- Resonant tunneling transistor with quantum well base and high-energy injection: A new negative differential resistance device

- Resonant tunneling through quantum wells at frequencies up to 2.5 THz

- · Inverted base-collector tunnel transistors

## Resonant Tunneling Transistors with Controllable Negative Differential Resistances

A. R. BONNEFOI, T. C. MCGILL, AND R. D. BURNHAM

Abstract—Three-terminal devices based on resonant tunneling through two quantum barriers separated by a quantum well are presented and analyzed theoretically. Each proposed device consists of a resonant tunneling double barrier heterostructure integrated with a Schottky barrier field-effect transistor configuration. The essential feature of these devices is the presence, in their output current-voltage  $(I_D - V_D)$  curves, of negative differential resistances controlled by a gate voltage. Because of the high-speed characteristics associated with tunnel structures, these devices could find applications in tunable millimeter-wave oscillators, negative resistance amplifiers, and high-speed digital circuits.

**E**LECTRONIC devices based on tunneling are a source of increasing interest. In particular, resonant tunneling in structures made of two GaAs electrodes separated by two thin  $Al_xGa_{1-x}As$  barriers and a quantum well have been extensively studied [1–6]. Two important properties of these double barrier heterostructures are (i) the presence of negative differential resistances in their current-voltage (*I–V*) characteristics, and (ii) expected operating frequencies in the terahertz range [2]. While it is true that these two-terminal tunnel structures have a number of potential applications, three-terminal devices would be preferable in many cases [7], [8].

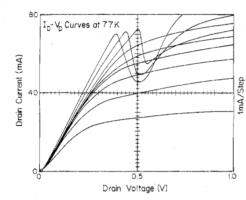

In this letter, we propose and analyze three-terminal devices in which the current through a resonant tunneling double barrier heterostructure is modulated by a Schottky barrier gate placed along the path of the electrons. In fact, these devices can be viewed simply as tunnel structures integrated with Schottky barrier field-effect transistors (MESFET's). For small source-drain bias voltages, a MESFET operates in its linear mode and acts as a variable resistor controlled by the gate voltage. This property may be used to modulate the amplitude and position of the tunnel structure negative differential resistances. We could observe these effects by simply connecting one of our two-terminal tunnel structures [5] in series with a commercial FET. The I-V characteristics obtained in this simple test are shown in Fig. 1 as a direct demonstration of this concept. However, by integrating the FET and double-barrier heterostructure, dimensions can be reduced and parasitic resistances and noise minimized. These are essential requirements for high-frequency performance.

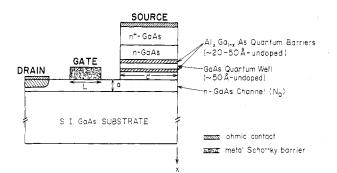

The first proposed device structure is shown schematically

Fig. 1. Experimental *I–V* characteristics at 77K for a two-terminal resonant tunneling structure connected in series with a commercial n-channel enhancement-mode VMOS power FET.

in Fig. 2. It consists of a resonant tunneling heterostructure integrated with a short channel MESFET. After tunneling through the quantum barriers and well, the flow of electrons is controlled by a Schottky barrier gate placed along a thin GaAs channel. The tunnel structure consists of two  $Al_xGa_{1-x}As$  barriers, about 20–50-Å thick, separated by an undoped GaAs well, approximately 50-Å thick. For the top GaAs layer, donor concentrations of  $5 \times 10^{16}-5 \times 10^{17}$  cm<sup>-3</sup> should provide sufficient tunneling currents and, at the same time, allow resonant tunneling effects to be observed at room temperature [6]. Submicron microwave and millimeter-wave FET fabrication techniques can be used to form the gate and the source and drain ohmic contacts [9]-[13].

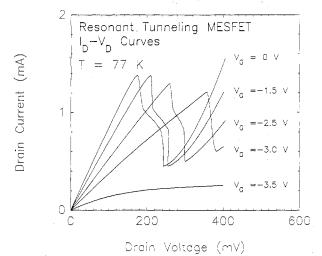

Calculated output current-voltage  $(I_D - V_D)$  characteristics for the schematic of the device in Fig. 2 are shown in Fig. 3 for the first resonance. Because we are mainly interested in the linear regime of the FET, the two-region model of Pucel et al. [14] was used to obtain the velocity-field curve in the channel. For GaAs, this model has been shown to agree perfectly with two-dimensional analysis in the linear region, and to within  $\pm$  15 percent in the saturation region [15]. The characteristics of the tunnel structure constituting the source were obtained by measuring the I-V curves of two-terminal resonant tunneling heterostructures. The growth technique, preparation procedure, and properties of these two-terminal devices were discussed elsewhere [3], [5]. The structure corresponding to Fig. 3 had pure AlAs barriers, approximately 50-A thick, and a nominally undoped GaAs quantum well, about 60-Å thick. The curves in Fig. 3 were calculated using a channel width a, of 0.20  $\mu$ m, a gate length L, of 0.75  $\mu$ m, and a gate width, perpendicular to the plane of Fig. 2, of 20  $\mu$ m. The doping in

Manuscript received August 5, 1985; revised September 20, 1985. This work was supported in part by the Defense Advanced Research Projects Agency under Contract N00014-84-C-0083 and the Office of Naval Research under Contract N00014-82-C-0556.

A. R. Bonnefoi and T. C. McGill are with T. J. Watson, Sr., Laboratory of Applied Physics, California Institute of Technology, Pasadena, CA 91125.

R. D. Burnham is with Xerox Corporation, Palo Alto, CA 94304.

Fig. 2. Schematic diagram (not to scale) of a cross section of the first proposed transistor structure, the "Resonant Tunneling MESFET." The device can be symmetric with respect to the x-axis to minimize channel resistance.

Fig. 3. Calculated current-voltage  $(I_D - V_D)$  characteristics in the voltage range 0-400 mV for the "Resonant Tunneling MESFET" shown schematically in Fig. 2. The channel width *a*, gate length *L*, and gate width perpendicular to the plane of Fig. 2, were taken to be 0.20, 0.75, and 20  $\mu$ m, respectively. The doping in the channel  $N_D$  was  $1 \times 10^{17}$  cm<sup>-3</sup>. The source length *d* and width, were taken to be 3 and 20  $\mu$ m, respectively. The device was assumed to be symmetric with respect to the *x*-axis (Fig. 2).

the channel  $N_D$  was  $1 \times 10^{17}$  cm<sup>-3</sup>. The source length d and width, perpendicular to the plane of Fig. 2, were taken to be 3 and 20  $\mu m,$  respectively. These curves display the substantial variations of the source-drain  $I_D - V_D$  characteristics which may be obtained by modulating the gate voltage. As the latter is decreased, the channel resistance increases, resulting in shifting the positions of the resonances towards larger drain voltages and eventually reducing their peak to valley ratios. For proper operation, the FET must operate in its linear regime. Furthermore, the channel resistance must be smaller than the absolute value of the tunnel structure negative differential resistances over a reasonably wide range of gate bias voltages. Since typical transit times for tunneling through double-barrier heterostructures are on the order of 1 ps or less, the millimeter-wave performance of these devices is limited by the transit time of electrons in the channel. This delay time can be minimized by reducing the gate and channel lengths and by increasing the doping in the channel. Since the minimum gate length in GaAs FET's is about 0.1  $\mu$ m, the expected maximum frequencies of operation should be on the order of 100 GHz [15]. Because they affect the ultimate performance of the device, the source-gate and gate-drain spacings are key parameters. The best values realized so far are 0.1 and 0.2  $\mu$ m, respectively [12]. It should also be mentioned that charging times are important in all tunnel structures. We are currently investigating their influence on the speed performance of the proposed devices.

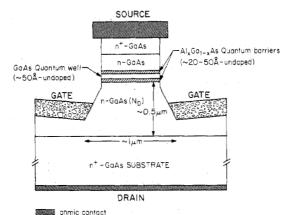

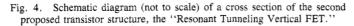

The second proposed device is schematically illustrated in Fig. 4. It consists of a resonant tunneling heterostructure integrated with a vertical MESFET [16]. The source contact is made to the top  $n^+$ -GaAs layer. It is followed first by the tunnel structure, and then by the GaAs active channel. Motion of the electrons in the channel is controlled by a Schottky barrier gate. The n<sup>+</sup>-substrate acts as the drain. It should be noted that the device could also operate in a configuration in which the source and drain electrodes are interchanged. This structure has several advantages over the first proposed device: (i) the geometry is such that the path of the electrons remains perpendicular to the tunnel barriers; (ii) the fabrication procedure is easier; (iii) the length of the active channel can be further reduced; and (iv) more accurate control of the drain to source spacing can be achieved. This should result in maximum frequencies of operation substantially greater than those obtainable with the previous device configuration.

The third proposed structure, schematically illustrated in Fig. 5, is a resonant tunneling heterostructure integrated with a permeable base transistor (PBT) [17], [18]. After tunneling through the double-barrier heterostructure, the flow of electrons is controlled by a thin metal grating which is embedded within the GaAs and forms a Schottky barrier gate. As in the previous device, the roles of the source and drain can be interchanged. It has been claimed that permeable base devices could, in principle, be capable of achieving maximum frequencies of oscillation near 1 THz [17]. This makes them promising for modulating tunnel structure negative differential resistances. Although it has been difficult in the past to achieve high quality epitaxial growth over metal films, improved growth techniques, or different approaches such as replacing the metal grating by p-type semiconductor grid fingers, appear to be promising.

In summary, we have proposed and analyzed three-terminal devices consisting of resonant-tunneling double-barrier heterostructures integrated with microwave field-effect transistor configurations. The three proposed devices, shown in Figs. 2, 4, and 5, could be called a "Resonant Tunneling MESFET," a "Resonant Tunneling Vertical FET," and a "Resonant Tunneling PBT," respectively. Simulations of device characteristics showed that substantial modulation of the tunnel structure negative differential resistances can be obtained by applying a gate voltage. Because they could operate in microwave and millimeter-wave regimes, such three-terminal devices should find applications in high-speed digital circuits, tunable millimeter-wave oscillators, and negative resistance amplifiers. Although these devices were presented in the context of  $GaAs/Al_xGa_{1-x}As$  heterojunction technology, they could be implemented in other materials. It may actually be advantageous to use semiconductors such as InGaAs, which has a higher electron mobility than GaAs. Experimental

metol Schottky barrier

Fig. 5. Schematic diagram (not to scale) of a cross section of the third proposed transistor structure, the "Resonant Tunneling PBT."

investigations are under way to determine the properties of these structures and to explore their possible applications in high-frequency analog and digital circuits.

## ACKNOWLEDGMENT

The authors wish to acknowledge R. S. Bauer, D. H. Chow, M. B. Johnson, W. Williams, and T. K. Woodward for valuable discussions, and are grateful to H. Chung and F. Endicott for technical assistance.

## REFERENCES

- R. Tsu and L. Esaki, *Appl. Phys. Lett.*, vol. 22, p. 562, 1973.

T. C. L. G. Soliner, W. D. Goodhue, P. E. Tannenwald, C. D. Parker,

- T. C. L. G. Soliner, W. D. Goodhue, P. E. Tannenwald, C. D. Parker, and D. D. Peck, *Appl. Phys. Lett.*, vol. 43, p. 588, 1983.

R. T. Collins, A. R. Bonnefoi, J. Lambe, T. C. McGill, and R. D.

- [3] R. T. Collins, A. R. Bonnefoi, J. Lambe, T. C. McGill, and R. D. Burnham, in *Proc. 17th Int. Conf. on the Physics of Semiconductors*, San Francisco, CA. New York: Springer-Verlag, 1984, p. 437.

[4] T. C. L. G. Sollner, P. E. Tannenwald, D. D. Peck, and W. D.

- [4] T. C. L. G. Sollner, P. E. Tannenwald, D. D. Peck, and W. D. Goodhue, *Appl. Phys. Lett.*, vol. 45, p. 1319, 1984.

- [5] A. R. Bonnefoi, R. T. Collins, T. C. McGill, R. D. Burnham, and F. A. Ponce, Appl. Phys. Lett., vol. 46, p. 285, 1985.

- [6] T. J. Shewchuk, P. C. Chapin, P. D. Coleman, W. Kopp, R. Fischer, and H. Morkoç, Appl. Phys. Lett., vol. 46, p. 508, 1985.

- [7] F. Capasso and R. A. Kiehl, J. Appl. Phys., vol. 58, p. 1366, 1985.

[8] A. R. Bonnefoi, D. H. Chow, and T. C. McGill, Appl. Phys. Lett., vol. 47, p. 888, Oct. 1985.

- [9] B. Kim, H. Q. Tserng, and H. D. Shih, *IEEE Electron Device Lett.*, vol. EDL-6, Jan. 1985.

- [10] M. Ogawa, K. Ohata, T. Furutsuka, and N. Kawamura, IEEE Microwave Theory Tech., vol. MTT-24, p. 300, 1976.

- [11] Y. Imai, M. Uchida, K. Yamamoto, and M. Hirayama, IEEE Electron Device Lett., vol. EDL-4, p. 99, 1983.

- [12] S. G. Banby, Y. G. Chai, R. Chow, C. K. Nishimoto, and G. Zdasiuk, *IEEE Electron Device Lett.*, vol. EDL-4, p. 42, 1983.

- [13] P. Baudet, M. Binet, and Boccon-Gibod, *IEEE Microwave Theory Tech.*, vol. MTT-24, p. 372, 1976.

- [14] R. A. Pucel, H. A. Haus, and H. Statz, Advances in Electronics and Electron Physics, L. Martin, Ed. New York: Academic, vol. 38, 1975, p. 195.

- [15] S. M. Sze, *Physics of Semiconductors*, 2nd Ed. New York: Wiley, 1981, p. 340.

- [16] E. Kohn, U. Mishra, and L. F. Eastman, *IEEE Electron Device Lett.*, vol. EDL-4, p. 125, 1983.

- [17] C. O. Bozler and G. D. Alley, *IEEE Electron Devices*, vol. ED-27, p. 1128, 1980.

- [18] G. D. Alley, IEEE Electron Devices, vol. ED-30, p. 52, 1983.