The Pennsylvania State University The Graduate School

### RETHINKING THE MEMORY HIERARCHY DESIGN WITH NONVOLATILE MEMORY TECHNOLOGIES

A Dissertation in Computer Science and Engineering by Jishen Zhao

© 2014 Jishen Zhao

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

May 2014

The dissertation of Jishen Zhao was reviewed and approved<sup>\*</sup> by the following:

Yuan Xie Professor of Computer Science and Engineering Dissertation Advisor, Chair of Committee

Mary Jane Irwin Professor of Computer Science and Engineering

Vijaykrishnan Narayanan Professor of Computer Science and Engineering

Zhiwen Liu Associate Professor of Electrical Engineering

Onur Mutlu Associate Professor of Electrical and Computer Engineering Carnegie Mellon University Special Member

Lee Coraor Associate Professor of Computer Science and Engineering Director of Academic Affairs

\*Signatures are on file in the Graduate School.

### Abstract

The memory hierarchy, including processor caches and the main memory, is an important component of various computer systems. The memory hierarchy is becoming a fundamental performance and energy bottleneck, due to the widening gap between the increasing bandwidth and energy demands of modern applications and the limited performance and energy efficiency provided by traditional memory technologies. As a result, computer architects are facing significant challenges in developing high-performance, energy-efficient, and reliable memory hierarchies. New byte-addressable nonvolatile memories (NVRAMs) are emerging with unique properties that are likely to open doors to novel memory hierarchy designs to tackle the challenges. However, substantial advancements in redesigning the existing memory hierarchy organizations are needed to realize their full potential. This dissertation focuses on re-architecting the current memory hierarchy designs for both CPU and graphics processor (GPU) systems.

The first contribution of this dissertation is to devise a novel bandwidth-aware reconfigurable cache hierarchy with hybrid memory technologies to enhance system performance of chip-multiprocessors (CMPs). In CMP designs, limited memory bandwidth is a potential bottleneck of the system performance. NVRAMs promise high-bandwidth cache solutions for CMPs. We propose a bandwidth-aware reconfigurable cache hierarchy with hybrid memory technologies. With different memory technologies, our hybrid cache hierarchy design optimizes the peak bandwidth at each level of caches. Furthermore, we develop a reconfiguration mechanism to dynamically adapt the cache capacity of each level based on the predicted bandwidth demands of different applications.

This dissertation also explores energy-efficient graphics memory design for GPU systems. We develop a hybrid graphics memory architecture, employing NVRAMs and the traditional memory technology used in graphics memories, to improve

the overall memory bandwidth and reduce the power dissipation of GPU systems. In addition, we design an adaptive data migration mechanism to further reduce graphics memory power dissipation without hurting GPU system performance. The data migration mechanism exploits various memory access patterns of workloads running on GPUs.

Finally, this dissertation discusses how to re-architect the current memory/storage stack with a persistent memory system to achieve efficient and reliable data movements. First, we propose a hardware-based, high-performance persistent memory design. Persistent memory allows in-memory persistent data objects to be updated at much higher throughput than using disks as persistent storage. Most previous persistent memory designs root from software perspective, and unfortunately reduce the system performance to roughly half that of a traditional memory system with no persistence support. One of the great challenges in this application class is therefore how to efficiently enable data persistence in memory. This dissertation proposes a persistent memory design that roots from hardware perspective. offering numerous practical advantages: a simple and intuitive abstract interface, microarchitecture-level optimizations, fast recovery from failures, and eliminating redundant writes to nonvolatile storage media. In addition, this dissertation presents a fair and high-performance memory scheduling for persistent memory systems. This dissertation tackles the problem raised by shared memory interface between memory accesses with and without the persistence requirement. This dissertation proposes a memory scheduling scheme that achieves both fair memory accesses and high system throughput for the co-running applications. Our key observation is that the write operations are also on the critical execution path for persistent applications. This dissertation introduces a new scheduling policy to balance the service of memory requests from various workloads, and a strided logging mechanism to accelerate the writes to persistent memory by augmenting their bank-level parallelism.

# **Table of Contents**

| List of | Figures                                                                                                                                             | ix  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| List of | Tables x                                                                                                                                            | iii |

| Acknow  | vledgments                                                                                                                                          | xv  |

| Chapte  | er 1                                                                                                                                                |     |

| Intr    | oduction                                                                                                                                            | 1   |

| 1.1     | Challenges with Memory Hierarchy Design                                                                                                             | 2   |

|         | <ul><li>1.1.1 Performance Challenges with CPU Memory Hierarchy Design</li><li>1.1.2 Energy Efficiency Challenge with GPU Memory Hierarchy</li></ul> | 2   |

|         | $Design \ldots \ldots$       | 4   |

| 1.2     | Design Opportunities Offered by NVRAMs                                                                                                              | 6   |

|         | 1.2.1 Opportunities in Replacing Traditional Memory Technologies                                                                                    | 6   |

|         | 1.2.2 Opportunities in Re-architecting the Memory/Storage Stack                                                                                     | 7   |

| 1.3     | Solutions                                                                                                                                           | 7   |

| 1.4     | Dissertation Organization                                                                                                                           | 8   |

| Chapte  | er 2                                                                                                                                                |     |

| Bac     | kground and Related Work                                                                                                                            | 10  |

| 2.1     | Background of NVRAM Technologies                                                                                                                    | 10  |

| 2.2     | Background of Persistent Memory                                                                                                                     | 13  |

| 2.3     | Related Research on Replacing Traditional Memory Hierarchies                                                                                        | 14  |

| 2.4     | Related Research on Persistent Memory                                                                                                               | 15  |

|         | 2.4.1 Maintaining Atomicity by Multiversioning                                                                                                      | 15  |

|         | 2.4.2 Preserving Consistency by Ordering                                                                                                            | 16  |

| Chapter | 3 |

|---------|---|

|---------|---|

| BA    |         | Bandwidth-aware Hybrid Cache Hierarchy Design for<br>CMPs 1                                                                                       |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1   |         | ey, Energy, and Bandwidth of Various Memory Technologies . 1                                                                                      |

| 3.2   |         | Cache Hierarchy                                                                                                                                   |

| 3.3   | v       | figuration $\ldots \ldots \ldots$ |

| 3.4   |         | tion Engine $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $2$                                                                    |

| 0.1   | 3.4.1   | Prediction Accuracy                                                                                                                               |

|       | 3.4.2   | Storage Overhead                                                                                                                                  |

|       | 3.4.3   | Computational overhead                                                                                                                            |

| 3.5   |         | $ments \dots \dots$                         |

| 0.0   | 3.5.1   | Experimental Setup                                                                                                                                |

|       | 3.5.2   | Results                                                                                                                                           |

| 3.6   |         | ary                                                                                                                                               |

| 0.0   |         |                                                                                                                                                   |

| Chapt | er 4    |                                                                                                                                                   |

| Ene   | ergy-Ef | ficient Graphics Memory Design 3                                                                                                                  |

| 4.1   | Motiva  | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $3$                                                                                            |

|       | 4.1.1   | Characteristics of Various Memory Technologies 3                                                                                                  |

|       | 4.1.2   | Memory Access Patterns of GPGPU Workloads 3                                                                                                       |

| 4.2   | Hybrid  | l Graphics Memory Architecture                                                                                                                    |

|       | 4.2.1   | Hardware Configuration                                                                                                                            |

|       | 4.2.2   | Data Migration Mechanism                                                                                                                          |

| 4.3   | Experi  | mental Setup                                                                                                                                      |

|       | 4.3.1   | Simulation Framework                                                                                                                              |

|       | 4.3.2   | Workloads                                                                                                                                         |

|       | 4.3.3   | Power Model                                                                                                                                       |

| 4.4   | Result  | s 4                                                                                                                                               |

|       | 4.4.1   | Throughput Improvement                                                                                                                            |

|       | 4.4.2   | Power Savings                                                                                                                                     |

|       | 4.4.3   | Power Breakdown                                                                                                                                   |

|       | 4.4.4   | Energy Efficiency                                                                                                                                 |

| 4.5   | Summ    | ary                                                                                                                                               |

| ~     |         |                                                                                                                                                   |

| Chapt |         |                                                                                                                                                   |

| Kil   |         | ing the Performance Gap Between Systems With and                                                                                                  |

|       |         | Vithout Persistence Support   5                                                                                                                   |

| 5.1   | 0       | Overview                                                                                                                                          |

|       | 5.1.1   | Assumptions and Definitions                                                                                                                       |

|       | 5.1.2   | In-place Updates without Logging or COW                                                                                                           |

|       | 5.1.3  | Ordering Control by Clean-on-commit                                                    |

|-------|--------|----------------------------------------------------------------------------------------|

|       | 5.1.4  | Timeline of a Transaction                                                              |

|       | 5.1.5  | Discussion                                                                             |

| 5.2   | Imple  | mentations $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $6$ |

|       | 5.2.1  | Software Interface and ISA Extension                                                   |

|       | 5.2.2  | Maintaining the State of NV Cache Lines                                                |

|       | 5.2.3  | Cache Extensions                                                                       |

|       | 5.2.4  | NV Cache Overflow and Fall-back Path 6                                                 |

|       | 5.2.5  | Recovery                                                                               |

|       | 5.2.6  | Physical Implementation                                                                |

| 5.3   | Exper  | imental Setup                                                                          |

|       | 5.3.1  | Simulation Framework                                                                   |

|       | 5.3.2  | Benchmarks                                                                             |

| 5.4   | Result | 58                                                                                     |

|       | 5.4.1  | Volatile Vs. Nonvolatile Last-level Cache                                              |

|       | 5.4.2  | Log-based Persistent Memory Performance                                                |

|       | 5.4.3  | Kiln Performance                                                                       |

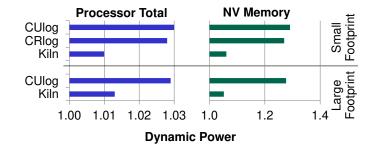

|       | 5.4.4  | Dynamic Power                                                                          |

| 5.5   | Summ   | ary                                                                                    |

|       |        |                                                                                        |

| Chapt |        |                                                                                        |

| FIF   |        | ir and High-Performance Memory Scheduling for                                          |

|       |        | Persistent Memory Systems 7                                                            |

| 6.1   |        | $\mathbf{Problem}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $    |

| 6.2   |        | enges of the Shared Memory Interface                                                   |

|       | 6.2.1  | Persistent Applications                                                                |

|       | 6.2.2  | Memory Organization                                                                    |

|       | 6.2.3  | Conventional Memory Scheduling Mechanisms 8                                            |

|       | 6.2.4  | Memory Access Behaviors of Persistent and                                              |

|       |        | Nonpersistent Applications                                                             |

| 6.3   |        | Observations                                                                           |

|       | 6.3.1  | A Naive Solution                                                                       |

| 6.4   | Mecha  |                                                                                        |

|       | 6.4.1  | Categorizing Sources of Memory Requests                                                |

| 6.5   |        | ry Scheduling                                                                          |

|       | 6.5.1  | Strided Logging                                                                        |

|       | 6.5.2  | Summary of FIRM Mechanism 9                                                            |

| 6.6   | Imple  | mentation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 9             |

|       | 6.6.1  | Software Interface and ISA Extension                                                   |

|       | 6.6.2  | Hardware Counters and Registers                                                        |

|         | 6.6.3   | Implementing Strided Logging                    | 96  |

|---------|---------|-------------------------------------------------|-----|

| 6.7     | Experi  | imental Setup                                   | 96  |

|         | 6.7.1   | Simulation Framework                            | 96  |

|         | 6.7.2   | Workloads                                       | 97  |

|         | 6.7.3   | Metrics                                         | 99  |

| 6.8     | Result  | 8                                               | 99  |

|         | 6.8.1   | Performance and Fairness of the Naive Mechanism | 99  |

|         | 6.8.2   | FIRM Performance and Fairness                   | 101 |

|         | 6.8.3   | Sensitivity to NVRAM Latency                    | 102 |

|         | 6.8.4   | Scalability with Cores                          | 103 |

| 6.9     | Summ    | ary                                             | 104 |

| Chapte  | er 7    |                                                 |     |

| Con     | clusion | n                                               | 105 |

| 7.1     | Summ    | ary of Contributions                            | 105 |

| 7.2     | Future  | Research Directions                             | 107 |

|         | 7.2.1   | Re-architecting the Memory/Storage Stack        | 107 |

|         | 7.2.2   | Hybrid Memory Architectures                     | 108 |

| Bibliog | graphy  |                                                 | 110 |

# **List of Figures**

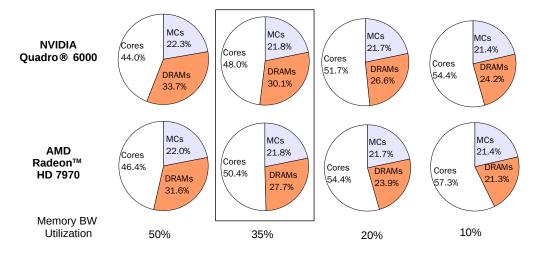

| 1.1          | Power breakdown of both NVIDIA and AMD GPUs. Power con-<br>sumptions of GPU cores and caches, memory controllers, and DRAMs<br>are examined to show that off-chip DRAM accesses consume a sig-<br>nificant portion of the total system power. | 4               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

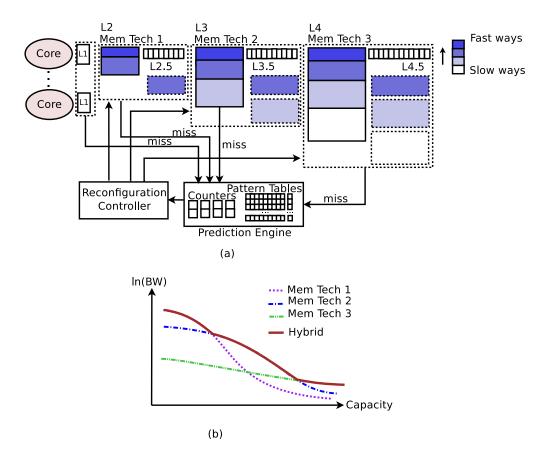

| 3.1          | Overview of the hardware configuration. (a) Configuration of re-<br>configurable hybrid cache hierarchy. (b) The overall bandwidth-<br>capacity curve of the hybrid cache hierarchy (a generic case of Fig-                                   |                 |

| 3.2          | ure 3.3)                                                                                                                                                                                                                                      | 19              |

|              | (c) Dynamic energy with $40\%$ of write intensity                                                                                                                                                                                             | 20              |

| 3.3          | Bandwidth-capacity curves of different memory technologies under dynamic energy constraint (with 40% of write intensity).                                                                                                                     | 22              |

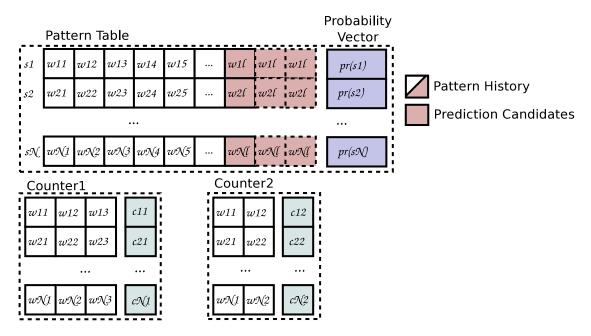

| 3.4          | Components of the prediction engine include the pattern table, the                                                                                                                                                                            |                 |

|              | probability vector, and an array of counters                                                                                                                                                                                                  | 27              |

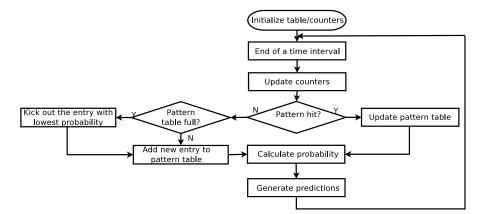

| $3.5 \\ 3.6$ | The control flow of the prediction engine                                                                                                                                                                                                     | 28              |

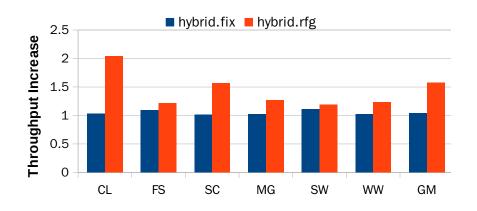

|              | per second.                                                                                                                                                                                                                                   | 32              |

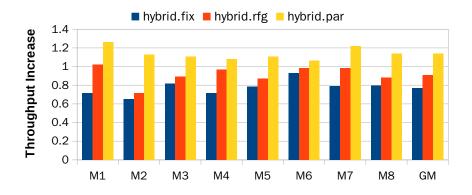

| 3.7          | Performance improvement with multiprogrammed workloads, eval-<br>uated in terms of throughput, i.e., the number of executed instruc-                                                                                                          |                 |

|              | tions per second.                                                                                                                                                                                                                             | 33              |

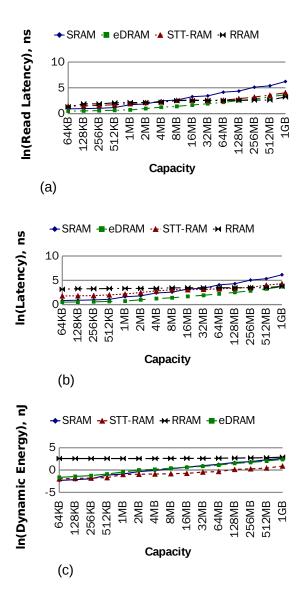

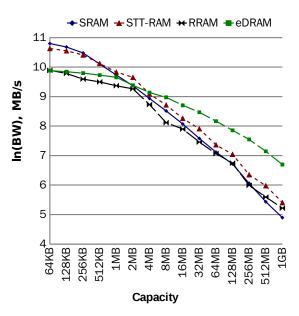

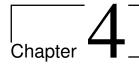

| 4.1          | (a) Latency, (b) provided bandwidth (PBW), and (c) dynamic power of different memory technologies with respect to different                                                                                                                   |                 |

|              | capacities                                                                                                                                                                                                                                    | 37              |

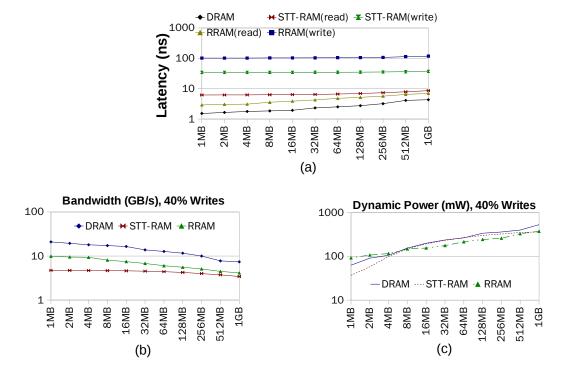

| 4.2          | Leakage power of different memory technologies with respect to                                                                                                                                                                                | 20              |

| 4.3          | various capacities                                                                                                                                                                                                                            | $\frac{38}{39}$ |

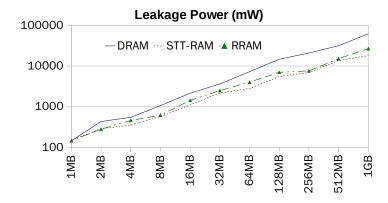

| 4.0          | $\mathbf{H} \mathbf{h} \mathbf{h} \mathbf{h} \mathbf{h} \mathbf{h} \mathbf{h} \mathbf{h} h$                                                                                                                                                   | 09              |

| 4.4        | The pattern of "access then idle". Can also observe the "burst"       |    |

|------------|-----------------------------------------------------------------------|----|

|            | pattern during the access period.                                     | 39 |

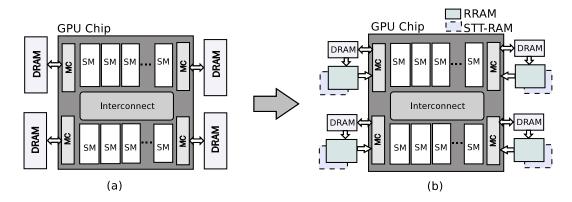

| 4.5        | Overview of GPU system with hybrid memory. (a) Conventional           |    |

|            | GPU system with off-chip GDDRs. (b) GPU system with hybrid            |    |

|            | memory                                                                | 41 |

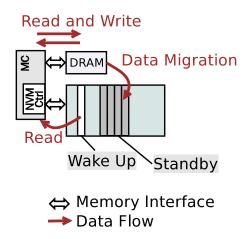

| 4.6        | Memory interface configuration and data flow between memory con-      |    |

|            | troller and hybrid memory                                             | 43 |

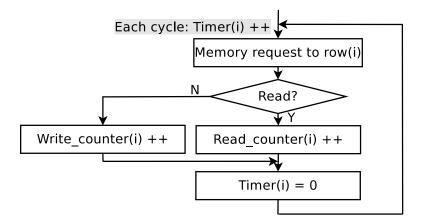

| 4.7        | The loop of DRAM access management.                                   | 43 |

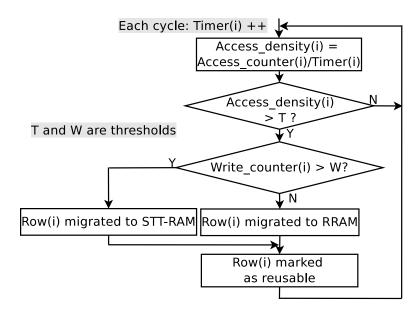

| 4.8        | Control of data migration.                                            | 44 |

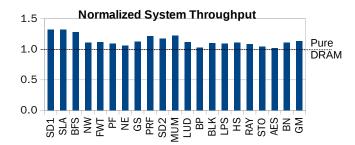

| 4.9        | System throughput with hybrid graphics memory, normalized to          |    |

|            | baseline.                                                             | 48 |

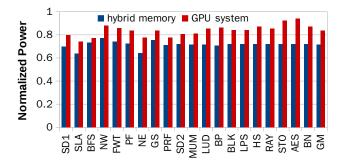

| 4.10       | Memory and system power consumption with hybrid graphics mem-         |    |

|            | ory, normalized to the baseline pure DRAM based graphics memory.      | 49 |

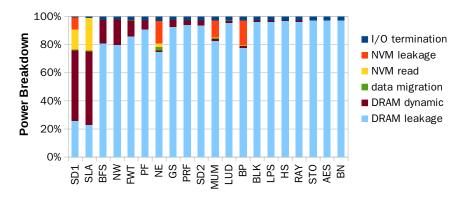

| 4.11       | Power breakdown of hybrid graphics memory.                            | 50 |

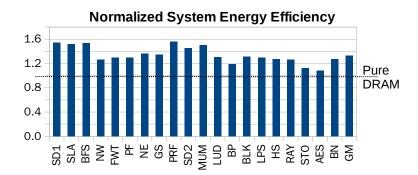

| 4.12       | System energy efficiency with hybrid graphics memory, normalized      |    |

|            | to baseline.                                                          | 50 |

|            |                                                                       |    |

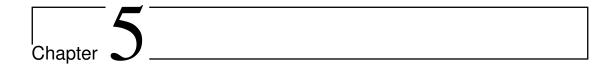

| 5.1        | Comparison between a native system with no persistence support        |    |

|            | (Native) and log-based persistent memory (Persistent Memory).         |    |

|            | Speedups of transaction throughput (higher is better) and memory      |    |

|            | traffic (lower is better), including reads and writes, are averaged   |    |

| ~ ~        | across benchmarks.                                                    | 54 |

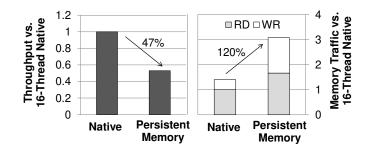

| 5.2        | Overview of Kiln persistent memory design and previous work.          |    |

|            | Most previous studies ((a) and (b)) employ logging or COW to          |    |

|            | maintain multiversioning, explicitly duplicating data in a separate   |    |

|            | journal or temporary buffer data structures. In these studies, order- |    |

|            | ing is enforced by write-through caching, cache flush and memory      |    |

|            | fence instructions, or fsync operations. (c) shows an overview of the |    |

|            | proposed Kiln design. With the multiversioned memory hierarchy        |    |

|            | consisting of the NV cache and the NV memory, Kiln allows in-place    |    |

|            | updates to the real in-memory data structures without logging or      |    |

| <b>F</b> 0 | COW.                                                                  | 55 |

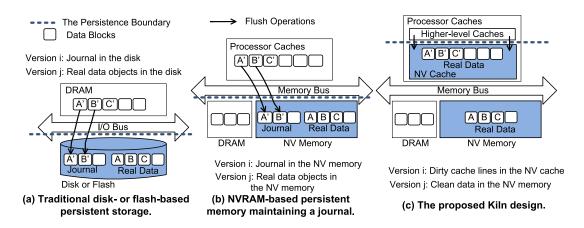

| 5.3        | Comparison of the timeline of Kiln and previous persistent memory     |    |

|            | designs. Block $A$ represents the data block (with a size of multiple |    |

|            | cache lines) of an old valid version. Block $A'$ represents the new   | •  |

|            | version being updated                                                 | 59 |

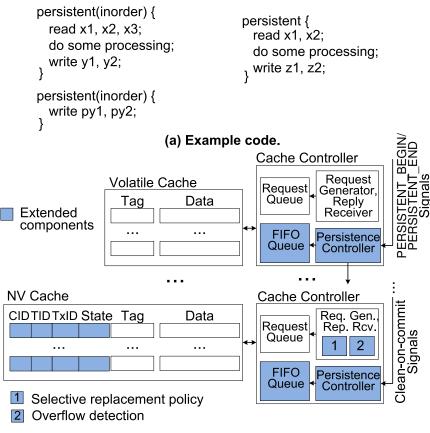

| 5.4          | Software and architecture extensions developed to facilitate Kiln.<br>(a) A code example with Kiln software interface. (b) Cache ar-<br>chitecture extensions. The shaded blocks are the modifications re-<br>quired over conventional architecture. Note that the dirty bit, the<br>invalid bit, and other cache coherence information are included in |   |          |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|

|              | the original tag region.                                                                                                                                                                                                                                                                                                                                |   | 60       |

| 5.5          | The storage overhead of the FIFO queues added to the cache con-<br>trollers. Note that the L1 and L2 caches are private so the total                                                                                                                                                                                                                    |   | 61       |

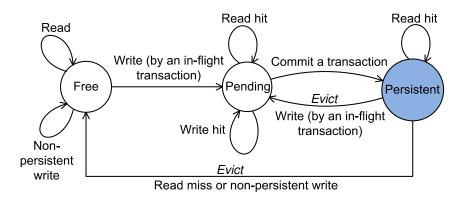

| 5.6          | overheads are calculated as the sum of eight FIFO queues The state transition of NV cache lines                                                                                                                                                                                                                                                         |   | 61<br>64 |

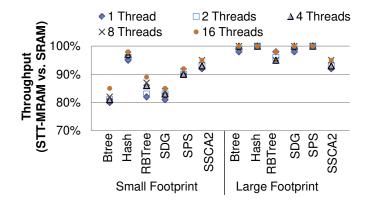

| $5.0 \\ 5.7$ | Performance comparison between two native systems adopting STT-<br>MRAM and SRAM as L3 cache respectively. Results show that the                                                                                                                                                                                                                        | • | 04       |

| 5.8          | two systems have similar performance                                                                                                                                                                                                                                                                                                                    |   | 72       |

|              | results running 16 threads.                                                                                                                                                                                                                                                                                                                             |   | 72       |

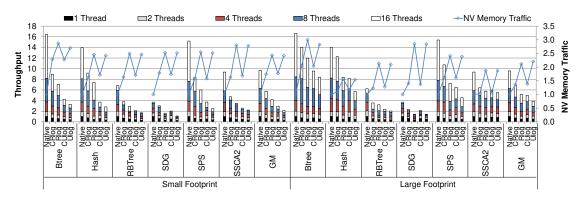

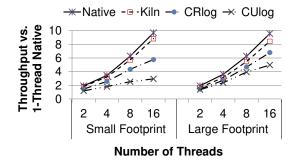

| 5.9          | Performance gap vs. number of threads.                                                                                                                                                                                                                                                                                                                  |   | 73       |

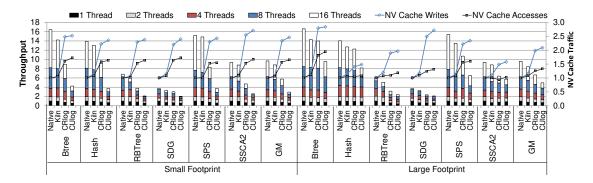

| 5.10         | The throughput (bars) and NV cache traffic (broken lines) of Kiln.<br>All the throughputs are normalized against the native system run-<br>ning 1 thread. For NV cache traffic, we only show the normalized                                                                                                                                             |   |          |

| 5.11         | results running 16 threads                                                                                                                                                                                                                                                                                                                              | • | 74       |

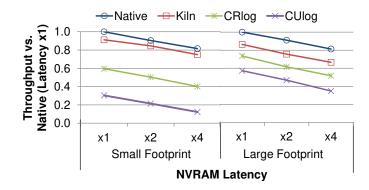

| 5.12         | with ×1 latency and 16 threads                                                                                                                                                                                                                                                                                                                          |   | 75<br>76 |

| 0.1          | - ,                                                                                                                                                                                                                                                                                                                                                     |   |          |

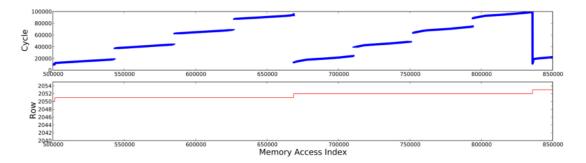

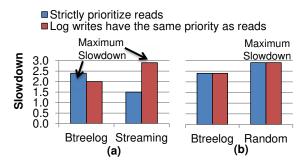

| 6.1          | Effect of simply assigning persistent writes the same priority as reads on different workload combinations. (a) <i>WL1</i> consists of <i>Btreelog</i> and <i>streaming</i> . (b) <i>WL2</i> consists of <i>Btreelog</i> and <i>random</i> .                                                                                                            |   | 86       |

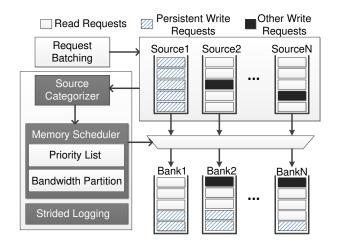

| 6.2          | Overview of FIRM design. Note that we show a logical view of source request queues. The physical locations of memory requests                                                                                                                                                                                                                           | • | 00       |

| 6.3          | are read and write queues in memory controllers Conventional address mapping scheme, address bits of persistent                                                                                                                                                                                                                                         | • | 88       |

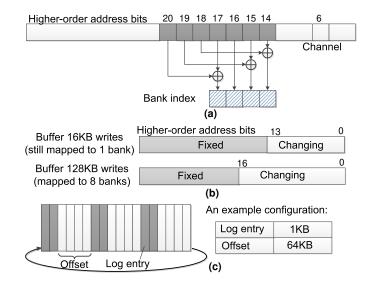

| 0.0          | writes, and proposed bank shuffling                                                                                                                                                                                                                                                                                                                     |   | 93       |

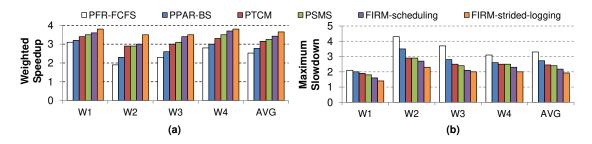

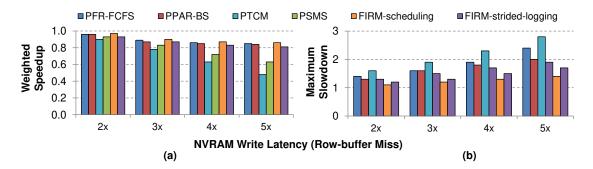

| 6.4 | System throughput and fairness with various memory scheduling                    |

|-----|----------------------------------------------------------------------------------|

|     | schemes. Among listed results, FIRM-scheduling employs the pro-                  |

|     | posed source categorization and memory scheduling mechanisms                     |

|     | but not strided logging. FIRM-strided-logging represents that all                |

|     | FIRM mechanisms, including hardware-based strided logging, are                   |

|     | employed. (a) System throughput evaluated as weighted speedup.                   |

|     | (b) System fairness evaluated as maximum slowdown 101                            |

| 6.5 | Results of average system throughput and fairness, when NVRAM                    |

|     | write latency varies from $2 \times$ to $5 \times$ of the original write latency |

|     | (Table 6.4). Weighted speedup (a) and maximum slowdown (b) are                   |

|     | normalized to the case using the original write latency 103                      |

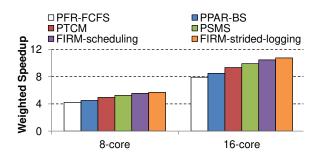

| 6.6 | Average weighted speedup with various memory scheduling schemes                  |

|     | on 8-core and 16-core systems                                                    |

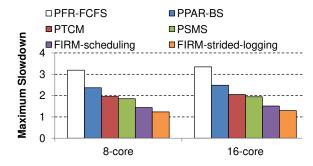

| 6.7 | Average maximum slowdown with various memory scheduling schemes                  |

|     | on a 8-core and 16-core systems                                                  |

|     |                                                                                  |

# **List of Tables**

| 2.1          | Comparison of Kiln with previous work. ( $\star$ means In-place updates<br>are only performed for memory stores to a single variable or at the<br>granularity of the bus width. $\diamond$ means ordering is maintained among<br>the writes to the disk or flash by flush or checkpointing.) | 15 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1          | Prediction accuracy for different widths of the pattern table                                                                                                                                                                                                                                | 28 |

| 3.2          | Storage overhead of the prediction engine.                                                                                                                                                                                                                                                   | 29 |

| 3.3          | Baseline CMP configuration.                                                                                                                                                                                                                                                                  | 30 |

| 3.4          | Characteristics of selected benchmarks. I'06 and F'06 represent the                                                                                                                                                                                                                          |    |

|              | SPEC CPU2006 integer and floating point benchmarks respectively.                                                                                                                                                                                                                             | 31 |

| 3.5          | Multithreaded and multiprogrammed workload sets                                                                                                                                                                                                                                              | 31 |

| 4.1          | Baseline GPU configuration. The parameters of streaming multi-                                                                                                                                                                                                                               |    |

| 1.1          | processors (SMs), caches, and memory controllers                                                                                                                                                                                                                                             | 45 |

| 4.2          | DRAM configurations. Baseline is off-chip GDDR5 memory with                                                                                                                                                                                                                                  |    |

|              | 32-bit bus width per chip. The maximum bus width of 3D die-                                                                                                                                                                                                                                  |    |

|              | stacked DRAM is 256-bit per chip. The maximum clock frequency                                                                                                                                                                                                                                |    |

|              | is 1.5GHz. The peak memory bandwidth of 3D die-stacked DRAM                                                                                                                                                                                                                                  |    |

|              | can be changed by scaling down the bus width and clock frequency.                                                                                                                                                                                                                            | 45 |

| 4.3          | Characteristics of selected GPGPU benchmarks. (IC represents                                                                                                                                                                                                                                 |    |

|              | instruction count. MI represents memory intensity.)                                                                                                                                                                                                                                          | 47 |

| 5.1          | Parameters of the evaluated multi-core system                                                                                                                                                                                                                                                | 67 |

| $5.1 \\ 5.2$ | Benchmarks used in our experiments.                                                                                                                                                                                                                                                          | 70 |

| 0.2          |                                                                                                                                                                                                                                                                                              | 10 |

| Memory intensity, write intensity, bank-level parallelism, and row-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| buffer locality of different applications running individually. Stream-  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ing and random are two nonpersistent applications with streaming         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| and random memory accesses. <i>Btreelog</i> performs inserts and deletes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| to a B+ tree-based key-value store with 25-byte keys and 2K-byte         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| values and employs redo logging to ensure data persistence. In           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| the last row of the table, we show the memory access behavior of         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <i>btreelog</i> when it is performing redo logging                       | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Priority strategy when at least one active persistent source is present  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| in the system.                                                           | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Storage required by hardware counters in each memory controller.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| The values are calculated based on the baseline configuration de-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| scribed in Section 6.7.                                                  | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Parameters of the evaluated multi-core system                            | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Benchmarks used in our experiments                                       | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Workloads mixed with Masstree and various nonpersistent applica-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| tions                                                                    | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Weighted speedup and maximum slowdown of various workloads: a            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| naive memory scheduling mechanism compared with conventional             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| memory scheduling schemes                                                | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                          | buffer locality of different applications running individually. Stream-<br>ing and random are two nonpersistent applications with streaming<br>and random memory accesses. Btreelog performs inserts and deletes<br>to a B+ tree-based key-value store with 25-byte keys and 2K-byte<br>values and employs redo logging to ensure data persistence. In<br>the last row of the table, we show the memory access behavior of<br>btreelog when it is performing redo logging |

## Acknowledgments

First of all, I would like to express my sincere gratitude to my advisor, Professor Yuan Xie, for his guidance throughout my Ph.D. study. His helpful suggestions, important advice, and constant encouragement are of the most important factors that helped me grow as a researcher. I would also like to thank my committee members, Professor Mary Jane Irwin, Professor Vijaykrishnan Narayanan, Professor Onur Mutlu, and Professor Zhiwen Liu for their support, insightful comments, and valuable feedback.

I would like to thank my managers, Dr. Norm P. Jouppi, Dr. Partha Ranganathan, Dr. Jichuan Chang, and Mr. Cullen E. Bash, as well as my mentor, Dr. Sheng Li, for their great support and advice while I was an intern at Hewlett-Packard Labs during the past two years. I would also like to thank my collaborators at AMD and Intel, Dr. Gabrial H. Loh, Dr. Yen-Kuang Chen, Dr. Christopher Hughes, and Dr. Changkyu Kim, for their insightful discussions on various research projects.

Special thanks to my husband, Yu Sheng. His endless love, care, and encouragement have been and will always be my motivation for improvement. Yu has always pushed me to strive for the highest-quality research and papers, the best internships, and the best dissertation. I would like to thank my parents. Their persistent support and belief in me have been invaluable wealth.

I am also greatly indebted to past and present MDL members for providing a supportive and productive environment. Especially, I thank Xiaoxia Wu, Guangyu Sun, Yibo Chen, Xiangyu Dong, Jin Ouyang, Tao Zhang, Dimin Niu, Cong Xu, Jing Xie, Matt Poremba, Qiaosha Zou, Hsiang-Yun Cheng, Jue Wang, Jia Zhan, and Ping Chi for their help. Many thanks are to my friends and colleagues at AMD, Carnegie Mellon University and Hewlett-Packard Labs, including but not limited to Rachata Ausavarungnirun, Kevin Kai-Wei Chang, Samira Khan, Yoongu Kim, Donghyuk Lee, Yixin Luo, Justin Meza, Gennady Pekhimenko, Vivek Seshadri, Lavanya Subramanian, Hongyi Xin, Hans J. Boehm, John Byrne, Dhruva Chakrabarti, Terence Kelly, Kevin Lim, Laura Ramirez, Rob Schreiber, Joseph Tucek, Alistair Veitch, and and Doe Hyun Yoon.

Finally, I would like to thank Penn State, Hewlett-Packard, NSF, DOE, and Semiconductor Research Corporation for their generous funding supports during my Ph.D. study.

## Introduction

The field of computer architecture has seen tremendous achievements. Processor designs have moved from the era of single core to multi-/many-core, preserving continuous system performance growth without significantly increased power budget and design complexity. Special-purpose hardware accelerators, e.g., GPUs and sensor arrays, were developed to support a single or narrow class of applications with much higher energy efficiency than general-purpose computers. However, two major challenges remain: the complexity and richness of application demands continue to overwhelm hardware capabilities; new device and circuit technologies are developed with properties that disrupt previous design assumptions, making current computer architecture designs suboptimal.

Among various components of computer systems, the memory hierarchy – including processor caches and the main memory – is a critical component and fundamental performance/energy bottleneck in addressing these two challenges. The memory hierarchy severs as the bridge between processors and the storage components (disks/flash). It stores applications' data sets being frequently accessed and supplies data to the processors. Modern applications rely on processing data from infinite sea of books, maps, photos, audios, videos, references, facts, and conversations. Consequently, their data sets can be gigabytes, terabytes, or even larger in size. Storing and processing such a large amount of data raises significant challenges in designing high-performance, energy-efficient memory hierarchy. Commodity memory technologies, such as SRAM and DRAM, are facing scalability challenges constrained by their device cell size and power consumption. Recently, various nonvolatile memories (NVRAMs), such as spin-transfer torque memory (STT-MRAM), phase-change memory (PCRAM), and resistive memory (ReRAM), have been studied as the replacement of traditional memory technologies used in the memory hierarchy [1, 2, 3, 4]. NVRAMs and traditional memory technologies trade off density, speed, power, and reliability. Furthermore, NVRAMs promise the game-changing feature – having both traditional memory (fast) and storage (nonvolatile, i.e., retaining data without power supply) properties in one device. Consequently, they yield abundant opportunities and challenges in memory hierarchy design.

This dissertation discusses the challenges and solutions of redesigning the memory hierarchy to achieve efficient and reliable data storage and movement, by leveraging NVRAMs. In particular, this dissertation presents (1) how to use NVRAMs as cache and main memory replacement to accommodate high-performance, energyefficient data access in CPU and GPU systems and (2) how to re-architect the memory/storage stack to fully leverage NVRAMs' game-changing feature to achieve efficient and reliable data movement.

#### 1.1 Challenges with Memory Hierarchy Design

This section describes the challenges in designing high-performance, energy-efficient memory hierarchies in CPU and GPU systems, respectively.

#### 1.1.1 Performance Challenges with CPU Memory Hierarchy Design

One critical bottleneck for CPU performance scaling is the widening gap between the increasing bandwidth demand created by processor cores and the limited bandwidth provided by off-chip memories [5, 6, 7]. Due to such limitation, memorydemanding applications with a large working set spends additional cycles on offchip memory accesses, and thus decreases the parallelism. In addition, even moderately memory-demanding applications will reach the bandwidth limitation as the number of cores scales up [8]. Consequently, memory bandwidth becomes one of the most important factors that influence high performance system design. Various techniques can be found in recent computer systems and research work to address this issue. High performance computing systems such as NVIDIA's Tesla [9] rely on extremely high main memory bandwidth provided by graphics DDR (GDDR) memory to satisfy the demand of large number of processor cores. However, GDDR memory runs at high clock rates and consumes more power than conventional DRAM modules. It is undesirable for either general purpose or highperformance computing systems to improve their computing performance by simply sacrificing power efficiency.

Caching is known to be the most effective approach to reduce memory access latency. Proper cache hierarchy design can also help mitigate the increasing pressure to off-chip memory bandwidth. With an extensive study on limited pin bandwidth in multiprocessor systems, Burger et al. concluded that on-chip cache with more levels would improve the system performance [6]. Rogers et al. explored the requirements of on-chip cache hierarchy and optimization techniques due to scaling of processor core numbers [7]. Both studies show that exploring on-chip memory hierarchy in a manner focusing on bandwidth optimization will benefit future computing systems in terms of performance scaling. Recently, various studies have been performed on addressing the bandwidth problem by optimizing cache hierarchy designs. Yu et al. proposed a last level cache (LLC) partitioning algorithm to minimize bandwidth requirement to off-chip main memory [10]. Cache resources were allocated for the target workload in a way to reduce the overall system bandwidth requirement by considering memory bandwidth demand for each task. One key insight in their work was that cache miss rate information might severely misrepresent the actual bandwidth demand of a workload. Thus the overall system performance and power consumption might be inappropriately estimated. However, they only focused on LLC (L2 cache). In this dissertation, our design target is the overall on-chip memory hierarchy, which provides more design dimensions and flexibility. Furthermore, the cache partition in their study [10] was determined offline, and remained fixed during run-time. This dissertation proposes a reconfiguration mechanism to dynamically adapt the space of each cache level to the demand of different applications.

**Figure 1.1.** Power breakdown of both NVIDIA and AMD GPUs. Power consumptions of GPU cores and caches, memory controllers, and DRAMs are examined to show that off-chip DRAM accesses consume a significant portion of the total system power.

#### 1.1.2 Energy Efficiency Challenge with GPU Memory Hierarchy Design

Modern GPU systems have become an attractive solution for both graphics and general purpose workloads that demand high computational performance. The graphics processing unit (GPU) exploits extreme multithreading to target highthroughput [11, 12]. For example, AMD Radeon<sup>TM</sup>HD 7970 employs 20,480 threads interleaved across 32 compute units [11]. To accommodate such highthroughput demands, the power consumption of GPU systems continues to increase. As existing and future integrated systems become power limited, reducing system power consumption while maintaining high energy efficiency is a critical challenge for GPU system design.

To satisfy the demands of high-throughput computing, the GPUs require substantial amounts of memory (from hundreds of megabytes to gigabytes, which are usually off-chip memory) that can support a very large number of read and write accesses. Consequently, the off-chip memory consumes a significant portion of power in a GPU system. We evaluated the maximum power consumption of two GPU systems, AMD Radeon<sup>TM</sup>HD 7970 [11], and NVIDIA Quadro®6000 [12], with the memory power model described in Section 6.7. Figure 1.1 presents the evaluated power distributions of GPU cores and caches, memory controllers, and off-chip memory. This dissertation consideres the memory bandwidth utilization (the fraction of all cycles when the data-bus is busy transferring data for reads or writes) from 10% to 50%. For both studied GPU systems, the off-chip memory consumes from 20% to over 30% of the total GPU system power. Note that for the workloads evaluated in this dissertation, the highest average bandwidth utilization observed was 35%. At this bandwidth level, the memory power consumption is 30.1% and 27.7% for the two GPU systems, respectively. If we can reduce the memory power by half, 12.5% of system power can be saved; this may seem like a relatively small amount, but it is in fact quite significant. For example, the maximum power consumption of AMD Radeon<sup>TM</sup>HD 7970 [11] is 230W; therefore a 12.5% power reduction saves 29W. Therefore, techniques that reduce the graphics memory power.

Conventional graphics memories (GDDR) have employed several techniques to reduce memory power consumption. Using the pseudo-open drain (POD) signaling scheme [13] with on-die termination (ODT), static power is only consumed when driving a "low" signal and thus reduces the power of the memory interface. GDDR5, the latest generation of commercial graphics memory, provides further power savings compared to its predecessors with lower supply voltages, dynamic voltage and frequency (VF) scaling, and independent ODT strength control of address, command and data [13]. VF scaling techniques employed by conventional GDDRs reduce power by adapting the memory interface to the memory bandwidth requirements of an application. However, the power reduction comes at the expense of memory bandwidth degradation. For example, Elpida's GDDR5 memories are specified to operate over a large contiguous VF range to support data rates starting from as low as 800MB/s per channel to the maximum rate of 20GB/s. While 1.6GB/s per channel may be sufficient for displaying static images, a data rate of 6GB/s is required for playing high-definition (HD) video, and the maximum data rate of 20GB/s may be fully utilized by high-end gaming applications. For future high-performance GPGPU and advanced video processing (e.g., 3D HD multi-screen video games), existing power saving techniques may not suffice.

#### 1.2 Design Opportunities Offered by NVRAMs

NVRAMs have several promising characteristics. They have much higher density than SRAM, as dense as DRAM, and need no refresh (which is required by DRAMs). In addition, they incorporate both memory and storage properties in a single device: can accommodate byte-addressable, fast memory accesses like memories; offer permanent data storage without power supply like disk and flash. These unique properties are likely to create an inflection point, opening doors to novel high-performance, energy-efficient memory hierarchy designs to unlock their full potential.

#### 1.2.1 Opportunities in Replacing Traditional Memory Technologies

NVRAMs promise much lower leakage power than SRAM, which is the traditional memory technology used in the cache hierarchy. Therefore, we can save substantial portion of cache power by adopting NVRAM-based caches in CPUs [2]. Furthermore, we find that NVRAMs can improve cache performance at large capacities. When the cache capacity is small, SRAM has much lower latency, and therefore higher memory bandwidth, than NVRAMs. However, we find that NVRAMs can provide higher memory bandwidth than SRAM at large cache capacities [14]. As a result, using NVRAMs as the memory technology of larger caches can offer much higher system performance than employing pure SRAM-based caches.

NVRAMs also bring in opportunities in designing energy-efficient graphics memories in GPUs. First, NVRAMs do not require refresh operations, which can consume a large portion of memory power [15]. Furthermore, we can shut down NVRAMs, when they are not being accessed. In particular, we can effectively reduce graphics memory power consumption without hurting GPU system performance, by leveraging unique the data access patterns of the workloads running on GPUs [16].

#### 1.2.2 Opportunities in Re-architecting the Memory/Storage Stack

For decades, computer systems adopt a two-level storage model to manipulate data access: a fast, volatile memory updated by loads and stores, with data being lost when system halts or reboots; a slow, nonvolatile storage device managed by databases or file systems, while data can survive across system boots. With the game-changing feature, NVRAMs can enrich such two-level memory/storage stack with the capability of accommodating fast accesses to permanent data storage in a unified nonvolatile memory. This feature brings new opportunities to address the massive online data storage and processing requirements of "big data" applications, allowing them to directly access permanent data storage in memory without the performance and energy overheads of transferring data from/to storage. Unfortunately, current hardware and hardware/software interface are optimized for the two-level memory/storage stack with vastly discrepant speed (fast memory and slow storage), interfaces (memory buses and storage I/Os), and functions (hardware-accelerated memory access and software managed permanent data storage). Consequently, computer architects need to redesign the memory/storage stack to unify the two functions through a memory interface with optimized system performance and reliability.

#### **1.3** Solutions

The goal of this dissertation is to design high-performance, energy-efficient memory hierarchies for CPU and GPU systems, by fully leveraging NVRAM's properties and benefits. This dissertation proposes the following three solutions to achieve this goal.

• The first solution is a novel bandwidth-aware reconfigurable cache hierarchy [14] to enhance system performance of chip-multiprocessors (CMPs) with hybrid memory technologies, by leveraging NVRAM's performance benefits. The hybrid cache hierarchy maximizes the provided bandwidth of processor caches and minimizes the bandwidth demand to the off-chip main memory. We also dynamically reconfigure the hybrid cache hierarchy to accommodate the actively changing bandwidth demands of various applications.

- The second solution is an energy-efficient graphics memory design [16], leveraging NVRAM's energy benefits to replace traditional pure DRAM-based graphics memories. We propose a hybrid graphics memory, mixing DRAM and various types of NVRAMs. The hybrid graphics memory can provide higher memory bandwidth and consumes less power than the traditional graphics memory designs. Although NVRAMs have longer latency than DRAM, our design can hide such longer latency with an adaptive data migration mechanism, by leveraging the memory access patterns of various workloads running on GPUs.

- The third solution of this dissertation leverages the disruptive property of NVRAMs to develop a persistent memory [17], incorporating the functions of memory and storage. Our design allows a persistent memory system to directly update the real in-memory data structures at high throughput.

- The final solution of this dissertation designs a memory scheduling scheme that achieves both fair memory access and high system throughput in persistent memory systems.

#### **1.4** Dissertation Organization

The remainder of the dissertation is organized as follows. Chapter 2 describes the background and the related work in NVRAM technologies, persistent memory, and high-performance, energy-efficient memory hierarchy designs. Chapter 3 presents a CPU cache hierarchy design with optimized memory bandwidth, utilizing hybrid memory technologies. Chapter 4 presents graphics designs with NVRAMs, optimized for system throughput and energy efficiency. Chapter 5 and Chapter 6 present our persistent memory designs, re-architecting the memory/storage stack by incorporating storage functions on maintaining data persistence into the memory system. In particular, Chapter 5 describes our hardware-based persistent memory design, which achieves both persistence and high performance in memory systems. Chapter 6 identifies the performance issue of resource competition

at the shared memory interface of persistent memory, and tackles the problem by redesigning memory scheduling mechanisms. Finally, Chapter 7 concludes the dissertation by summarizing the key results and insights that have been presented, and presenting suggestions on future research directions concerned with NVRAM's implications on novel memory hierarchy design.

# **Background and Related Work**

This chapter first describes the background of emerging technologies, including 3D/2.5D integration and NVRAMs. This is followed by the description of background of the emerging persistent memory technique that leverages the nontraditional property of NVRAMs. Finally, this chapter describes the relevant approaches classified into two categories: replacement of traditional memory hierarchies and the persistent memory by re-architecting the memory/storage stack.

#### 2.1 Background of NVRAM Technologies

This dissertation explores memory hierarchy designs with three types of NVRAMs – STT-MRAM, ReRAM, and PCRAM [18, 19, 20, 21]. Note that some studies refer nonvolatile memories as flash memories [22], which are block addressable. This dissertation investigates the use of byte-addressable nonvolatile memories. Therefore, flash memories are not discussed as NVRAMs in our work.

Various types of NVRAM technologies: STT-MRAM is the latest generation of magnetic RAM (MRAM) [19, 20]. STT-MRAM employs Magnetic Tunnel Junction (MTJ), which contains two ferromagnetic layers and one tunnel barrier layer, as its binary storage. The relative magnetization direction of two ferromagnetic layers determines the resistance of MTJ. If the two ferromagnetic layers appear at the same directions, the resistance of MTJ is low, indicating a "0" state; otherwise, the resistance of MTJ is high, indicating a "1" state. In ReRAM [23, 24, 25], a normally insulating dielectric is conducted through a filament or conduction path generated by applying a sufficiently high voltage. The conduction path can be generated by different mechanisms, including defects, metal migration, etc. The filament may be reset (broken, resulting in high resistance) or set (re-formed, resulting in lower resistance) by applying an appropriate voltage. PCRAM [21, 26] uses chalcogenide-based material to storage information. The chalcogenide-based material can be switched between a crystalline phase (SET or "1" state) and an amorphous phase (RESET or "0" state) with the application of heat.

**Benefits:** NVRAMs promise density, performance, and energy benefits. They have much higher density than SRAM, the memory technology widely used in commodity processor caches. Compared to DRAM, NVRAMs show significant power benefits. Due to the non-volatility, NVMs do not require refresh operations, and have near-zero standby power. In addition, NVRAMs can accommodate both byte-addressable, fast data accesses and nonvolatile data storage. Therefore, they incorporate both memory (fast) and storage (retaining data without power supply) properties in one device. This feature can disrupt current two-level memory/storage stack with the capability of accommodating fast accesses to permanent data storage in a unified nonvolatile memory.

**Drawbacks:** The drawbacks of NVRAMs include long write latency, high write energy, and low write endurance. Write endurance is the number of times that a memory cell can be overwritten before the cell fails. Among the three NVRAMs, only STT-MRAM is free from the low write endurance issue. The endurance of STT-MRAM is larger than  $10^{15}$  [1], which is close to that of SRAM. The endurance of ReRAM is in the range of  $10^5$  to  $10^{11}$  [27, 28, 29]. That of PCRAM is in the range of  $10^5$  to  $10^9$  [30]. Therefore, STT-MRAM is a practical solution for cache design [31, 32, 33], while ReRAM is feasible for last-level cache (LLC) with low write intensity. The low endurance of PCRAM makes it less feasible to be used as processor caches. All the three NVRAMs are feasible for designing the main memory, especially with architecture-level error protection techniques, such as ECP [34], dynamically replicated memory [35], SAFER [36], start-gap [3], security refresh [37], and FREE-p [38]. Furthermore, a projected plan by ITRS [39] highlighted that the endurance of PCRAM and ReRAM will be at the order of  $10^{15}$  or higher by 2024.