# Retrograde p-well for 10kV-class SiC IGBTs

# Amit K. Tiwari, Marina Antoniou, Neophytos Lophitis, Samuel Perkins, Tatjana Trajkovic, and Florin Udrea

Abstract—In this paper, we propose the use of a retrograde doping profile for the p-well for ultra-high voltage (>10kV) SiC IGBTs. We show that the retrograde p-well effectively addresses the punch-through issue, whilst offering a robust control over the gate threshold voltage. Both the punch-through elimination and gate threshold voltage control are crucial to high-voltage vertical IGBT architectures and are determined by the limits on the doping concentration and depth a conventional p-well implant can have. Without any punch-through, a 10kV SiC IGBT consisting of retrograde p-well yields gate threshold voltages in the range 6-7V with a gate-oxide thickness of 100nm. Gate oxide thickness is typically restricted to 50-60nm in SiC IGBTs if a conventional pwell with  $1 \times 10^{17}$  cm<sup>-3</sup> is utilized. We further show that the optimized retrograde p-well offers the most optimum switching performance. We propose that such an effective retrograde p-well, which requires low-energy shallow implants and thus key to minimize processing challenges and device development cost, is highly promising for the ultra-high voltage (>10kV) SiC IGBT technology.

*Index Terms*— SiC IGBTs, Retrograde p-well, Punch-through, Breakdown Voltage, Threshold-voltage control

#### I. INTRODUCTION

ULTRA-high voltage (>10kV) switching devices, most notably SiC IGBTs, have attracted considerable interest for rapidly emerging sector of applications, such as Smart Grids and HVDC [1-3]. The 10kV class SiC IGBT research has gained significant momentum since the inception of the first 10kV p-IGBT on 4H-SiC in 2005 by Zhang et al, particularly, in the aftermath of realization of high-voltage n-channel devices on free-standing 4H-SiC epilayers in 2010 by Wang et al [4, 5]. Extensive efforts have been put lately on realizing SiC IGBTs in the 10kV-30kV voltage range where they can offer a more favorable trade-off between the conduction and switching losses when compared with unipolar counterparts [6-20].

N-channel IGBTs are generally preferred over P-channel IGBTs and evolved at a rapid pace partially because a positive voltage is required to drive their gate and partially because of exhibiting inherently superior channel mobilities and carrier lifetimes. Although, the processing of n-channel IGBTs is particularly challenging, both the breakdown voltage and specific on-resistance have significantly improved due to important breakthroughs in bulk/epilayer growth and controlled post-process substrate grinding [21]. N-epilayers can be grown as thick as 200µm with a good control on the doping concentration in the range  $1 \times 10^{14}$ - $3 \times 10^{14}$ cm<sup>-3</sup> [15-18]. Defect density is acceptable in terms of realizing devices with an active area of 1cm×1cm and the carrier lifetime ( $\tau$ ) is approaching ~12µs [21]. N-channel SiC IGBTs have been successfully demonstrated up to a breakdown voltage of 27kV with continuous improvement in switching characteristics [17-20].

Whilst great emphasis is being placed on the breakdown voltage, a reliable control of the gate threshold voltage ( $V_{th}$ ) has emerged as a critical issue in the development of ultra-high voltage class (>10kV) of SiC IGBTs [6-20]. A robust control over  $V_{th}$  is a prerequisite for a latch-up free and faster IGBT operation.

To have  $V_{th}$  in the range 5-7V, a 10kV SiC IGBT requires substantial reduction in the gate oxide thickness ( $t_{ox}$ ), which in turn leads to long-term reliability issues. Previous studies have shown that the gate oxide thickness is restricted to 50-60nm [4-18]. The doping of conventional p-well can be lowered to further increase the oxide-thickness. However, this makes the IGBT susceptible to issues such as punch-through, latch-up and thus premature electrical breakdown. In the absence of a robust p-well, a high-degree of minority carrier injection, which lowers the junction voltage between the p-well and emitter, can significantly impact the breakdown voltage of IGBTs.

Increasing the depth of p-well is found to be effective for low-voltage devices. However, >10kV devices require the low-doped (~1×10<sup>17</sup>cm-3) conventional p-well to be >2 $\mu$ m deep. Such an implant depth requires implantation energies in excess of 2.0MeV. High-energy implantations are generally very

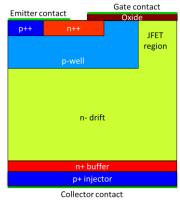

Fig. 1. An n-channel DMOS SiC IGBT

M. Antoniou is with Department of Engineering, University of Warwick, Coventry, CV4 7AL, UK.

S. Perkins and N. Lophitis are with Faculty of Engineering, Environment and Computing, Coventry University, CV1 2JH, Coventry, UK.

A portion of this work is supported by the EPSRC's Centre for Power Electronics under Underpinning Power Electronics (UPE) 2: Switch Optimization Theme (Ref. EP/R00448X/1).

A. Tiwari (<u>akt40@cam.ac.uk</u>), T. Trajkovic and F. Udrea are with Department of Engineering, University of Cambridge, Cambridge, CB2 1PZ, UK.

costly, posing further processing challenges in terms of minimizing the damage to the surface of active area.

Here we present the retrograde approach compatible with ultra-high voltage class of SiC IGBT technology. Retrograde pwell is historically proposed for the high-density Si-based CMOS technology with later studies reporting an improvement in latching performance of scaled devices by the use of specific dopant types, such as Indium, and super-steep doping profile [22-25]. Of late, the retrograde approach is also introduced to SiC devices [3, 5, 8, 26-32]. Most notable efforts include the realization of planar ACCUFET and double-implanted power MOSFETs, being both in 6H-SiC [26, 27].

A few reports are available on the use of retrograde p-well in SiC MOSFETs and IGBTs [3, 5, 8, 28-32]. Nevertheless, little is available in terms of its design requirements and its plausible impact upon the key electrical characteristics of ultra-high voltage SiC IGBTs. The retrograde approach is particularly relevant to >10kV SiC IGBT technology given stringent operational window and considerable processing constraints.

For the first time, retrograde p-well is extensively studied in terms of its impact upon the key electrical characteristics of >10kV class SiC IGBTs. With extensive optimization, we show that it can accommodate blocking voltages as high as 20kV, whilst posing minimal processing challenges. We further show the effectiveness of the optimized retrograde p-well in terms of eliminating punch-through and achieving a robust control on the threshold voltage control by means of depositing thick oxide in ultra-high voltage SiC IGBTs. Thicker gate oxide is crucial to enhance the long-term reliability of power devices, particularly during high-voltage transients or in blocking modes at elevated temperatures. In addition, a thicker gate oxide is also beneficial to reduce the effect of hot carrier degradation and Fowler-Nordheim tunneling, also known as Field Emission. We also show that >10kV SiC IGBT consisting of retrograde p-well offers superior transient performance when compared with counterpart consisting of a conventional p-well.

#### II. DEVICE DESIGN AND METHODOLOGY

A two-dimensional DMOS n-IGBT test-cell (Fig. 1), is simulated at room temperature using Technology-Aided Computer Design (TCAD) tools, as embedded in Synopsys-Sentaurus software package. The IGBT test-cell consists of a p<sup>+</sup> anode/injector, n<sup>+</sup> buffer and n<sup>-</sup> drift epilayer. The drift epilayer is low-doped and sufficiently thick to support >10kV blocking voltages. The thickness of blocking epilayer for 10kV, 15kV and 20kV designs are 100µm, 150µm and 200µm, respectively. The doping concentration of blocking epilayer for investigated blocking voltages is fixed at  $3 \times 10^{14}$  cm<sup>-3</sup>. The doping concentrations for p<sup>+</sup> anode/injector and buffer epilayer are  $1 \times 10^{19}$  and  $1 \times 10^{18}$  cm<sup>-3</sup>, respectively. Under extensive simulations, the optimized width of JFET region is found to be 5µm and the channel length is fixed at 2µm. The lateral dimensions for regions, such as p++ and n++ implants underneath the emitter contact, can be chosen as per processing convenience since these do not readily affect the device characteristics investigated here. Material properties of SiO2 are utilized for the gate oxide.

The lifetimes of carriers are modeled as a product of a doping-dependent, field-dependent and temperature-dependent factors, as embedded in Scharfetter model utilizing Shockley-Read-Hall (SRH) recombination mechanism. Carrier life times of 2.5  $\mu$ s and 0.5  $\mu$ s are used of electrons and holes.

Dependency of impact ionization coefficients upon the electric field is calculated using the Okuto-Crowell model. Breakdown characteristics are obtained using a background carrier concentration of  $1 \times 10^9$  cm<sup>-3</sup>.

Caughey-Thomas model is utilized to model doping and temperature dependency of carrier mobility. The dependency of energy bandgap upon both temperature and doping is considered. Incomplete ionization of dopants in 4H-SiC is also considered, being the donor trap of Nitrogen located at 0.0709 eV with respect to the conduction band and the acceptor trap of Aluminum at 0.265 eV with respect to the valance band. Details regarding the simulation models and material parameters are described in our previous work [33-35].

#### III. RESULTS AND DISCUSSION

We begin our investigation by first highlighting the difference between conventional and retrograde p-wells.

#### A. Retrograde vs. Conventional

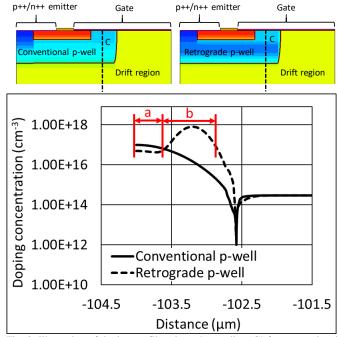

The conventional and retrograde p-wells differ mainly in the manner the doping concentration is varied with the depth. Doping profiles for conventional and retrograde p-wells are illustrated in Fig. 2. In a conventional approach, the peak doping concentration of  $1 \times 10^{17}$  cm<sup>-3</sup> lies mostly at the surface or in the sub-surface region of p-well, which steadily decreases with the depth. In contrast, in the proposed retrograde approach, the doping near the surface or sub-surface region, annotated as region 'a', of the p-well is kept low (< $8 \times 10^{16}$  cm<sup>-3</sup>), which gradually increases up to  $5 \times 10^{17}$ - $5 \times 10^{18}$  cm<sup>-3</sup> in the region

Fig. 2. Illustration of doping profiles along the cut line 'C' for conventional and retrograde p-wells.

annotated as 'b' and then begins to decrease with the depth. The low-doping sub-surface region of retrograde p-well is typically 0.2-0.3µm deep, whilst the remaining depth is dedicated to high-doping concentration, typically higher than  $5 \times 10^{17}$  cm<sup>-3</sup>. In this manuscript, the high-doping region (i.e., region 'b') is referred as the 'bottom' of the retrograde p-well. The retrograde p-well would require two set of implants performed with two separate masks. The region 'b' can be realized using the set of high-energy and high-dose implants, whilst region 'a' will require the set of low energy-low dose implants.

Next, we examine the performance of an ultra-high voltage (>10kV) SiC IGBT comprising of the retrograde p-well and compare it with that of counterpart comprising of a conventional p-well. We begin with the IGBT blocking characteristics.

## B. Blocking characteristics

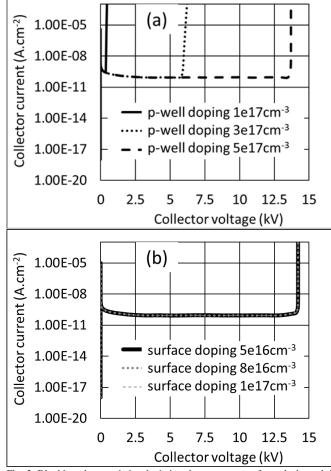

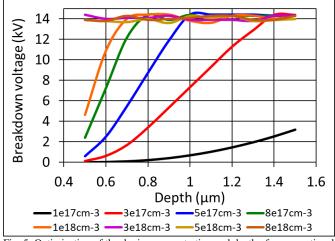

Simulated breakdown characteristics of a 10kV IGBT cell with conventional and retrograde p-wells are shown in Fig 3. When the conventional design is used, as shown in Fig. 3(a), the collector current rises prematurely at voltages as low as ~400V and at ~6kV for uniform doping of  $1 \times 10^{17}$ cm<sup>-3</sup> and  $3 \times 10^{17}$ cm<sup>-3</sup>, respectively. Upon increasing the conventional p-well doping from  $3 \times 10^{17}$ cm<sup>-3</sup> to  $5 \times 10^{17}$ cm<sup>-3</sup>, a desired breakdown occurs, at ~13.5kV, which is very close to the blocking ability of an equivalent 1D open base PNP. It is calculated that same blocking ability can be achieved with doping concentration of  $3 \times 10^{17}$ cm<sup>-3</sup> but a deeper (~1.5µm) conventional p-well will be required.

In the case of retrograde p-well, the doping concentration at the bottom is intentionally kept at very high level  $(>1\times10^{18}$ cm<sup>-3</sup>), which ensures the desired breakdown of ~13.5kV, even if the corresponding highly doped region is relatively thin and shallow. Also, the doping concentration in the sub-surface region, i.e., region 'a', of retrograde p-well becomes less important for blocking, which means it can be designed independently. As shown in Fig. 3(b), the sub-surface region doping is allowed to have a wide range of doping concentration, for example, between  $5\times10^{16}$ cm<sup>-3</sup> and  $1\times10^{17}$ cm<sup>-3</sup>, with no rapid rise in the current observed. Essentially the retrograde p-well achieves to decouple the blocking ability from the doping of the sub-surface region.

For the case of a conventional p-well, the premature rise in current can be attributed to either punch-through or forward biasing of the p-well/emitter junction during both the on-state and turn-off. The punch-through is caused by the lack of strong depletion barrier at the p-well and drift junction, resulting in a direct current conducting path between the emitter and collector. As elaborated in our previous work [34, 35], the forward biasing of the junction between p-well and emitter can originate from electron-hole pair generation in the high-electric field regions surrounding the p-well. In the case of a highdegree of electron-hole pair generation caused by elevated temperatures, IGBT can also conduct the current in a similar manner.

Under blocking conditions, we have examined profiles of different physical properties, such as, absolute current density,

Fig. 3. Blocking characteristics depicting the occurrence of punch-through in a > 10kV IGBT cell with (a) a conventional p-well and (b) a retrograde p-well. The value of t<sub>ox</sub> is 50nm and p-well implants for both conventional and retrograde doping profiles are  $0.7-0.8\mu$ m deep.

impact ionization, in detail and identified punch-through as the main cause behind premature rapid rise of collector current. Impact ionization is found to be very low, lower than

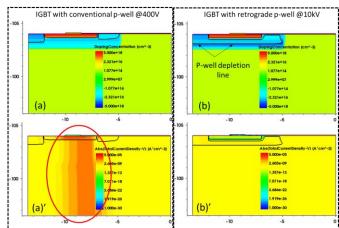

Fig. 4. Depiction of depletion of conventional p-well ((a) and (a')) and retrograde p-well ((b) and (b')) just before the rapid rise of collector current. Doping and current profiles for conventional p-well are taken at 400V, while for retrograde p-well these are taken at 10kV. The value of  $t_{ox}$  is 50nm and p-well implants are 0.8µm deep. Doping concentrations are  $1 \times 10^{17} \text{ cm}^{-3}$  for conventional p-well and  $5 \times 10^{16}$  and  $3 \times 10^{18} \text{ cm}^{-3}$  at the surface and bottom of retrograde p-well, respectively.

$1 \times 10^{11}$  cm<sup>-3</sup>•s<sup>-1</sup> just before the sudden rise of current, i.e., at 400V and 13.5kV for conventional and retrograde p-well IGBT structures.

Absolute current density profiles within IGBTs at different collector voltages are shown in Fig. 4. As shown in Fig. 4 (a), the charge in a 0.8µm deep conventional p-well with doping concentration of  $1 \times 10^{17}$  cm<sup>-3</sup> is not adequate to hold the depletion from reaching the n<sup>++</sup> emitter region at 400V. In other words, even at a low-voltage of 400V, the conventional p-well is fully depleted. This is clearly demonstrated in Fig. 4 (a) and (a'): there exists no depletion barrier (solid black line) around the p-well which in turn lets the current to conduct through (red circled region). In contrast, a retrograde p-well with the same depth is only partially depleted at 10kV, consisting of a clear depletion region (depicted by black line) around the retrograde p-well. Indeed, Fig 4 (b) and (b') validate the effectiveness of the retrograde p-well to withstand voltages even higher than 10kV without exhibiting punch-through. This is corroborated by the blocking characteristics of Fig. 3(b), where the SiC IGBT test cell is approaching the maximum theoretical 2D limit of SiC breakdown of ~14kV for drift region thickness of 100µm and doping concentration of  $3 \times 10^{14}$  cm<sup>-3</sup>.

## C. Further design considerations for 10-20kV range

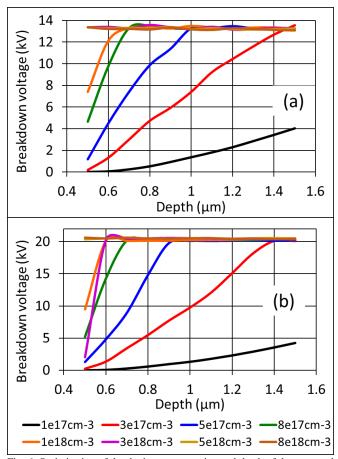

To achieve blocking ability higher than 10kV, as high as 20kV, the total charge in the p-well needs to be increased. As depicted in Fig. 5, to achieve 10kV using a conventionally designed pwell, the doping needs to be higher than  $3 \times 10^{17}$  cm<sup>-3</sup> and p-well depth of  $\sim 1.5 \mu m$ . Alternatively, one can reduce the p-well depth to 0.6-0.8 um but this would require a doping concentration higher than  $8 \times 10^{17}$  cm<sup>-3</sup>. For 20kV blocking ability, even deeper p-wells are needed. In contrast, the retrograde profile can be optimized to block voltages higher than 10kV with a total depth of as thin as 0.6-0.7µm and bottom doping density of  $>1\times10^{18}$  cm<sup>-3</sup>. The same depth is found to be adequate to block 20kV but with slightly higher doping density requirement of  $>3\times10^{18}$  cm<sup>-3</sup>. These results are shown in Fig. 6 (a) and (b). The results for the retrograde case indeed demonstrate a remarkable improvement over the equivalent conventional p-well, which needs to be deeper than 1.5µm for ultra-high voltage IGBTs.

To mitigate from the adverse effect of electric field crowding

Fig. 5. Optimization of the doping concentration and depth of a conventional p-well for 10kV SiC IGBT.

Fig. 6. Optimization of the doping concentration and depth of the retrograde p-well for (a) 10kV and (b) 20kV SiC IGBTs.

at the curvature and the equivalent enhanced impact ionization, the exact profile of the region has been optimised accordingly. This is particularly important for voltages higher than 10kV. Towards this direction the bottom ~0.2µm of the total retrograde p-well depth is designed to be lowly doped. Also, the high-doping region within the p-well is kept away from the corner. The optimized design essentially achieves a softer junction at the bottom and the corner of the p-well and therefore reduces effectively the curvature of the electrostatic distribution and the electric field crowding observed during blocking. It has also been achieved to avoid degradation of the IGBT blocking voltage when the peak doping concentration of the retrograde p-well increases. The latter is key requirement for achieving blocking voltages 10-20kV. For example, as shown in Fig. 6 (a), the blocking voltage remains constant at 13.5kV, even when the doping concentration at the bottom of the p-well is increased to  $8 \times 10^{18}$  cm<sup>-3</sup>. For ultra-high voltage IGBTs these design considerations become necessary when aiming to achieve the maximum possible breakdown voltage without the use of costly deep implantations.

#### D. Threshold voltage control

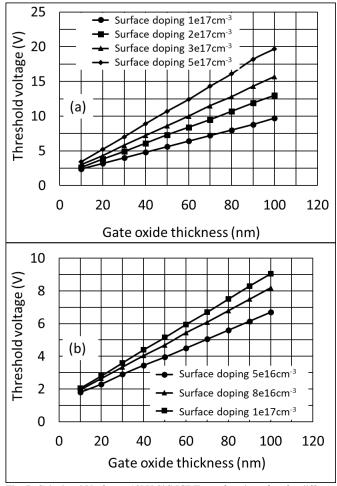

The gate-oxide thickness is an important design parameter which strongly affects  $V_{th}$ . Fig. 7 shows the calculated  $V_{th}$  as a function of  $t_{ox}$  for different values of doping concentrations used in conventional and retrograde p-wells. As can be seen in Fig. 7(a), for a conventional p-well of doping concentration  $1 \times 10^{17} \text{cm}^{-3}$ , 60nm is the maximum allowable  $t_{ox}$  to ensure  $V_{th}$

Fig. 7. Calculated V<sub>th</sub> for a >10kV SiC IGBT as a function of t<sub>ox</sub> for different values of doping (a) in a conventional p-well and (b) at the surface of a retrograde p-well. The bottom of retrograde p-well is fixed at ~1×10<sup>18</sup> cm<sup>-3</sup>. The region of interest for V<sub>th</sub> of a SiC IGBT lies between 5V and 7V.

below 7V. If higher doping concentrations are used, e.g. to enable blocking ability of 10kV, the value of the maximum allowable  $t_{ox}$  is even smaller than 50nm. With the introduction of the retrograde p-well, the allowable gate oxide thickness increases dramatically. A gate threshold voltage of less than 7V can be achieved with oxide layers being as thick as 100nm. Since the sub-surface doping concentration in a retrograde pwell does not affect the blocking ability, there is an extra degree of freedom. As shown in the previous subsection, if required, the doping of the p-well region closer to the surface can be lower than  $5 \times 10^{16}$  cm<sup>-3</sup> in order to allow for a gate oxide thicker than 100nm. For a doping concentration of  $1 \times 10^{16}$  cm<sup>-3</sup>, one can utilize 150nm gate oxide without surpassing V<sub>th</sub> of 7V.

## E. Switching characteristics

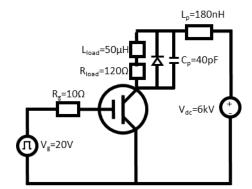

Whilst the advantage of having a retrograde p-well in ultrahigh voltage SiC IGBTs is evident in the static performance, it is instructive to access its impact upon the switching performance and to compare it with that of a conventionally doped. The turn-off waveforms of 10kV rated SiC IGBTs consisting of retrograde and conventional p-well are assessed for their switching performance under inductive load conditions, as illustrated in Fig. 8. The DC link voltage is set to 6kV and load resistance set at  $120\Omega$ , yielding the current

Fig. 8. Circuit schematic used in mixed-mode simulations of inductive load turn-off of 10kV SiC IGBTs.

density of 50A•cm<sup>-2</sup>. The gate voltage applied is set to 20V, which is well above the threshold voltage of all design variations assessed.

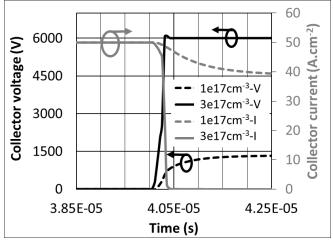

As shown in Fig. 9 (grey lines), an IGBT with conventional p-well doped  $1 \times 10^{17}$  cm<sup>-3</sup> and with depth of  $1.3 - 1.5 \mu$ m is grossly inadequate to achieve good turn-off characteristics. Turn-off behavior is improved with increased in doping concentration of conventional p-well, however, this is coming at the cost of significant increase in the gate threshold voltage.

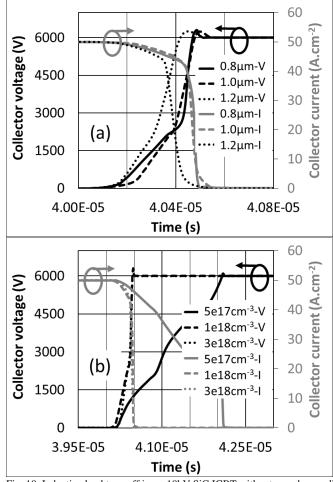

To assess the effect of the retrograde p-well IGBT and to optimize its profile for the most optimum IGBT switching behavior, a large number of design variants are investigated. Even for the retrograde p-well, a higher doping concentration and greater depth is desirable in terms of efficient extraction of holes through the p-well. However, there is limit to what can realized in practice. We have further examined the impact of both the depth and bottom doping of retrograde p-well. As shown in Fig. 10 (a), the turn-off behavior of 10kV SiC IGBT improves with an increasing depth of the retrograde p-well. However, even a shallow retrograde p-well with depth of  $0.8\mu m$  and bottom with doping of  $1 \times 10^{18} cm^{-3}$ , yields excellent turn-off behavior. The turn-off time is low, lying in the range 550-600ns.

As shown in Fig. 6(a), a doping concentration of  $5 \times 10^{17}$  cm<sup>-3</sup> at the bottom of the retrograde p-well is adequate to reach 10kV blocking capability. However, in transient simulations at 6kV (Fig. 9b),  $5 \times 10^{17}$  cm<sup>-3</sup> exhibits a very large turn-off time of

Fig. 9. Inductive load turn-off in a >10kV SiC IGBT with conventional p-well. The p-well depth is fixed at  $1.3-1.5\mu$ m. The gate-oxide thickness is 50nm.

Fig. 10. Inductive load turn-off in a >10kV SiC IGBT with retrograde p-well. (a) Effect of p-well depth and (b) effect of p-well doping. The p-well bottomdoping in (a) is fixed at  $1 \times 10^{18}$  cm<sup>-3</sup> and in (b) depth is fixed at 0.8 µm. The doping concentration at the surface of retrograde p-well is fixed at  $5 \times 10^{16}$  cm<sup>-3</sup> with 50nm gate-oxide lying on top it.

$1.5\mu$ s. Such a large turn-off time is likely to amount to considerable losses and possibly leading to an IGBT failure. This is an important design consideration, while utilizing retrograde p-wells in ultra-high voltage SiC IGBTs. The turn-off time has been considerably reduced with increased doping at the bottom of retrograde p-well. However, for doping concentrations higher than  $1 \times 10^{18}$  cm<sup>-3</sup>, there is not much improvement in switching characteristics.

We have further accessed turn-off losses. We find that >10kV SiC IGBT consisting of the optimized retrograde p-well, i.e., sub-surface doping  $5\times10^{16}$ cm<sup>-3</sup>, bottom doping  $1\times10^{18}$ cm<sup>-3</sup> and depth 0.8 µm, exhibits nearly three order of magnitude lower losses of  $4.83\times10^{-5}$  J•cm<sup>-2</sup> in comparison to  $2.15\times10^{-2}$  J•cm<sup>-2</sup> of the counterpart consisting of a conventional p-well with uniform doping of  $3\times10^{17}$ cm<sup>-3</sup> and depth 1.5 µm.

## IV. CONCLUSION

In conclusion, we have investigated the effect of retrograde pwell doping profile upon the key characteristics of 10kV-class SiC n-IGBTs. Under extensive simulations, we showed that the retrograde p-well eliminates the possibility of a premature breakdown due to punch-through even when a shallow implantation depth of  $<1\mu m$  is adopted. Reduction in implantation energies is crucial to cut the fabrication cost.

We have further showed that the doping concentration of the sub-surface region of the retrograde p-well does not affect the blocking ability, and hence it can be varied over a very large range to achieve a desirable control over V<sub>th</sub> by means of oxide deposition. An appropriately doped sub-surface region of the retrograde p-well, for example,  $<1 \times 10^{16}$ cm<sup>-3</sup>, is allowing the use of gate oxides thicker than 100nm, whilst yielding V<sub>th</sub> in the range of 5-7V. An extended control on V<sub>th</sub> with thicker oxide offers processing convenience and is particularly beneficial to address issues arising 'oxide-reliability' and phenomena such as Fowler-Nordheim tunneling and hot carrier injection.

It is worth mentioning here that a substantial reduction in the sub-surface doping, which has been possible only because of the retrograde approach, can further help with improving the channel mobility of SiC MOS devices. Kimoto et al. have previously reported on increase in the channel mobility with decreasing p-body doping concentration for different crystal faces. Channel mobilities increased from 12 to 26cm<sup>2</sup>•V<sup>-1</sup>•s<sup>-1</sup>, and 61 to 78cm<sup>2</sup>•V<sup>-1</sup>•s<sup>-1</sup> on the Si 0001 and 1121 faces, respectively, when the acceptor doping concentration of p-body decreased from  $2 \times 10^{17}$  to  $1 \times 10^{16}$  cm<sup>-3</sup> [36]. Of particular interest is the channel mobility of  $145 \text{cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  obtained by Ortiz et al. using a very low acceptor concentration of  $1 \times 10^{15}$  cm<sup>-3</sup> on the 0001 Si-face [37]. Previously, Katakami et al. showed an improvement in the channel mobility of pchannel SiC IGBT using the combination of adopting an n-type base layer with a retrograde doping profile and additional wet re-oxidation annealing (wet-ROA) at 1100°C in the gate oxidation process. Considering such a large degree of freedom a designer can have over the selection of doping near the channel region, the retrograde p-well possesses significant importance to the SiC-based MOS technology.

In terms of transient performance, we find that the exact doping profile of retrograde p-well can affect the turn-off speed and losses. We note that the retrograde p-well with depth of  $0.8\mu m$  and a peak concentration of  $1 \times 10^{18} cm^{-3}$  at its bottom gives the most optimum switching performance.

We therefore propose that the retrograde p-well is a highly promising approach for ultra-high voltage (>10 kV) SiC IGBTs. The retrograde p-well concept possesses scope beyond SiC IGBTs, covering a diverse range of MOS-based power devices, such as, MOSFETs and IGCTs on advanced materials, such as, diamond and Ga<sub>2</sub>O<sub>3</sub>, where the implantation process is particularly challenging.

#### REFERENCES

- J. Wang, A. Q. Huang, W. Sung, Y. Liu, and B. J. Baliga, "Smart grid technologies", IEEE Ind. Electron. Mag., vol. 3, no. 2, pp. 16-23, June 2009. DOI: 10.1109/MIE.2009.932583

- [2] J. W. Palmour, J. Q. Zhang, M. K. Das, R. Callanan, A. K. Agarwal, and D. E. Grider, "SiC power devices for smart grid systems", in Proceedings of IEEE International Power Electronics Conference, pp. 1006-1013, June 2010. DOI: 10.1109/IPEC.2010.5542027

- [3] K. Fukuda, D. Okamoto, M. Okamoto, T. Deguchi, T. Mizushima, K. Takenaka, H. Fujisawa, S. Harada, Y. Tanaka, Y. Yonezawa, and T. Kato, "Development of ultrahigh-voltage SiC devices", IEEE Trans. Electron Devices, vol. 62, no. 2, pp. 396-404, Feb. 2015. DOI: 10.1109/TED.2014.2357812

- [4] Q. Zhang, H-R. Chang, M. Gomez, C. Bui, E. Hanna, J. A. Higgins, T. Isaacs-Smith, and J. R. Williams, "10kV trench gate IGBTs on 4H-SiC",

in Proceedings of 17th IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), pp. 303–306, May 2005. DOI: 10.1109/ispsd.2005.1488011

- [5] X. Wang, and James A. Cooper, "High-voltage n-channel IGBTs on freestanding 4H-SiC epilayers", IEEE Trans. on Electron Devices, vol. 57, no. 2, pp. 511-515, Feb. 2005. DOI: 10.1109/TED.2009.2037379

- [6] Q. J. Zhang, J. Charlotte, J. J. Sumakeris, A. K. Agarwal, and J. W. Palmour, "12 kV 4H-SiC P-IGBTs with Record Low Specific Onresistance", Mater. Sci. Forum, vols. 600-603, pp. 1187-1190, Sept. 2008. DOI: 10.4028/www.scientific.net/msf.600-603.1187

- [7] Q. J. Zhang, M. K. Das, J. Sumakeris, R. Callanan, and A. K. Agarwal, "12-kV p-channel IGBTs with low on-resistance in 4H-SiC", IEEE Electron Device Lett., vol. 29, no. 9, pp. 1027-1029, Sept. 2008. DOI: 10.1109/LED.2008.2001739

- [8] M. K. Das, Q. J. Zhang, R. Callanan, C. Capell, J. Clayton, M. Donofrio, S. K. Haney, F. Husna, C. Jonas, J. Richmond, and J. J. Sumakeris, "A 13 kV 4H-SiC N-channel IGBT with low R<sub>diff.on</sub> and fast switching", Mater. Sci. Forum, vols. 600-603, pp. 1183-1186, Sept. 2009. DOI: 10.4028/www.scientific.net/msf.600-603.1183

- [9] S. Ryu, C. Capell, C. Jonas, L. Cheng, M. O'Loughlin, A. Burk, A. K. Agarwal, J. Palmour, and A. Hefner, "Ultra high voltage (> 12 kV), high performance 4H-SiC IGBTs", in Proceedings of 24<sup>th</sup> IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), pp. 257-260, June 2012. DOI: 10.1109/ISPSD.2012.6229072

- [10] S. H. Ryu, L. Cheng, S. Dhar, C. Capell, C. Jonas, J. Clayton, M. Donofrio, M. J. O'Loughlin, A. A. Burk, A. K. Agarwal, J. W. Palmour, "Development of 15 kV 4H-SiC IGBTs", Mater. Sci. Forum, vol. 717–720, pp. 1135-1138, May 2012. DOI: 10.4028/www.scientific.net/msf.717-720.1135

- [11] S. Ryu, C. Capell, C. Jonas, Y. Lemma, M. O'Loughlin, J. Clayton, E. Van Brunt, K. Lam, J. Richmond, A. Burk, and D. Grider, "Ultra high voltage IGBTs in 4H-SiC", in Proceedings of IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), pp. 36-39, Jan. 2013. DOI: 10.1109/WiPDA.2013.6695557

- [12] K. Fukuda, D. Okamoto, S. Harada, Y. Tanaka, Y. Yonezawa, T. Deguchi, S. Katakami, H. Ishimori, S. Takasu, M. Arai, and K. Takenaka, "Ultrahigh voltage SiC bipolar devices", in Proceedings of IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 32-35, Oct. 2013. DOI: 10.1109/WiPDA.2013.6695556

- [13] Y. Yonezawa, T. Mizushima, K. Takenaka, H. Fujisawa, T. Kato, S. Harada, Y. Tanaka, M. Okamoto, M. Sometani, D. Okamoto, and N. Kumagai, "Low V<sub>f</sub> and highly reliable 16 kV ultrahigh voltage SiC flip type n-channel implantation and epitaxial IGBT", in Proceedings of IEEE International Electron Devices Meeting (IEDM), pp. 661–664, Dec. 2013. DOI: 10.1109/IEDM.2013.6724576

- [14] T. Deguchi, T. Mizushima, H. Fujisawa, K. Takenaka, Y. Yonezawa, K. Fukuda, H. Okumura, M. Arai, A. Tanaka, S. Ogata, and T. Hayashi, "Static and dynamic performance evaluation of >13 kV SiC p channel IGBTs at high temperatures", in Proceedings of 26thIEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), pp. 261-264, June 2014. DOI: 10.1109/ISPSD.2014.6856026

- [15] E. Brunt, L. Cheng, M. O'Loughlin, C. Capell, C. Jonas, K. Lam, J. Richmond, V. Pala, S. Ryu, S. T. Allen, and A. Burk, "22kV, 1cm<sup>2</sup>, 4H-SiC n-IGBTs with improved conductivity modulation", in Proceedings of 26thIEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), pp. 358-361, June 2014. DOI: 10.1109/ISPSD.2014.6856050

- [16] S. H. Ryu, C. Capell, C. Jonas, M. O'Loughlin, J. Clayton, K. Lam, E. Brunt, Y. Lemma, J. Richmond, D. Grider, S. Allen, "An analysis of forward conduction characteristics of ultrahigh voltage SiC N-IGBTs", Mat. Sci. Forum, vol. 858, pp. 945-948, May 2016. DOI: 10.4028/www.scientific.net/MSF.858.945

- [17] E. Brunt, L. Cheng, M. J. O'Loughlin, J. Richmond, V. Pala, J. W. Palmour, C. W. Tipton, C. Scozzie, "27 kV, 20 A 4H-SiC n-IGBTs", Mater. Sci. Forum, vols. 821–823, pp. 847-850, June 2015. DOI: 10.4028/www.scientific.net/msf.821-823.847

- [18] X. Yang, Y. Tao, T. Yang, R. Huang and B. Song, "Fabrication of 4H-SiC n-channel IGBTs with ultra-high blocking voltage", Journal of Semiconductors, vol. 39, pp. 034005 1-3, Mar. 2018. DOI: 10.1088/1674-4926/39/3/034005

- [19] A. Kadavelugu, S. Bhattacharya, S. Ryu, E. Brunt, D. Grider, A. K. Agarwal, and S. Leslie, "Characterization of 15 kV SiC n-IGBT and its application considerations for high power converters" in Proceedings of IEEE Energy Conversion Congress and Exposition (ECCE), pp. 2528-2535, Sept. 2013. DOI: 10.1109/ECCE.2013.6647027

- [20] N. Watanabe, H. Yoshimoto, A. Shima, R. Yamada, and Y. Shimamoto, "6.5 kV n-Channel 4H-SiC IGBT with Low Switching Loss Achieved by Extremely Thin Drift Layer", Mater. Sci. Forum, vol. 858, pp. 934- 944, May 2016. DOI: 10.4028/www.scientific.net/msf.858.939

- [21] T. Kimoto, J. A. Cooper, "Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications", John Wiley & Sons, Nov. 2014. DOI: 10.1002/9781118313534

- [22] R. D. Rung, C. J. Dell'oca, L. G. Walker, "A retrograde p-well for higher density CMOS", IEEE Trans. Electron Devices, vol. 28, no. 10, pp. 1115-1119, Oct. 1981. DOI:10.1109/T-ED.1981.20498

- [23] S. R. Combs, "Scaleable retrograde p-well CMOS technology", in Proceedings of IEEE International Electron Devices Meeting (IEDM), pp. 346-349, Dec. 1981. DOI:10.1109/IEDM.1981.190084

- [24] Z. Shen, V. Parthasarathy, and T. P. Chow, "Improvement of IGBT latching performance by indium doping", in Proceedings of 53rd IEEE Annual Device Research Conference Digest, pp. 110-111, June 1995. DOI: 10.1109/drc.1995.496293

- [25] I. De, and C. M. Osburn, "Impact of super-steep-retrograde channel doping profiles on the performance of scaled devices", IEEE Trans. on Electron Devices, vol. 46, no. 8, pp.1711-1717, Aug. 1999. DOI:10.1109/16.777161

- [26] P. M. Shenoy, and B. J. Baliga, "The planar 6H-SiC ACCUFET: A new high-voltage power MOSFET structure", IEEE Electron Device Lett., vol. 18, no. 12, pp. 589-591, Dec. 1997. DOI:10.1109/55.644080

- [27] J. N. Shenoy, J. A. Cooper, and M. R. Melloch, "High-voltage doubleimplanted power MOSFET's in 6H-SiC", IEEE Electron Device Lett., vol. 18, no. 3, pp 93-95, March 1997. DOI:10.1109/55.556091

- [28] G. G. Walden, T. McNutt, M. Sherwin, S. Van Campen, R. Singh, and R. Howell, "Comparison of 10 kV 4H-SiC power MOSFETs and IGBTs for high frequency power conversion", Mater. Sci. Forum, vols. 600-603, pp. 1139-1142, Sept. 2009. DOI: 10.4028/www.scientific.net/MSF.600-603.1139

- [29] T. Tamaki, G. G. Walden, Y. Sui, and J. A. Cooper, "On-State and Switching Performance of High-Voltage 15–20 kV 4H-SiC DMOSFETs and IGBTs", Mater. Sci. Forum, vols. 600-603, pp. 1143-1146, Sept. 2009. DOI: 10.4028/www.scientific.net/MSF.600-603.1143

- [30] S. Katakami, H. Fujisawa, K. Takenaka, H. Ishimori, S. Takasu, M. Okamoto, M. Arai, Y. Yonezawa, and K. Fukuda, "Fabrication of a P-channel SiC-IGBT with high channel mobility", Mater. Sci. Forum, vol. 740-742, pp. 958-961, Jan. 2013. DOI: 10.4028/www.scientific.net/msf.740-742.958

- [31] S. Ryu, S. Krishnaswami, M. O'Loughlin, J. Richmond, A. Agarwal, J. Palmour, and A. Hefner, "10-kV, 123-m cm2 4H-SiC power DMOSFETs", IEEE Electron Device Lett., vol. 25, no. 8, pp. 556-558, Aug. 2004. DOI:10.1109/LED.2004.832122

- [32] C. C. Hung, Y. S. Chen, C. T. Yen, C. Y. Lee, L. S. Lee, and M. J. Tsai, "Simulation and optimization of 4H-SiC DMOSFET power transistors", Mat. Sci. Forum, vol. 740, pp. 711-714, Jan. 2013. DOI: 10.4028/www.scientific.net/MSF.740-742.711

- [33] N. Lophitis, A. Arvanitopoulos, S. Perkins, M. Antoniou, "TCAD device modelling and simulation of wide bandgap power semiconductors", InTech–Open Access Publisher, Sept. 2018. DOI: 10.5772/intechopen.76062

- [34] Amit K. Tiwari, M. Antoniou, N. Lophitis, and F. Udrea, "Operation of Ultra-High Voltage (>10kV) SiC IGBTs at Elevated Temperatures: Benefits & Constraints", in Proceedings of 31<sup>st</sup> IEEE International Symposium on Power Semiconductor Devices & IC's (ISPSD), May 2019 (in press).

- [35] S. Perkins, M. Antoniou, A. K. Tiwari, A. Arvanitopoulos, T. Trajkovic, F. Udrea, N. Lophitis, ">10kV 4H-SiC n-IGBTs for Elevated Temperature Environments", in Proceedings of International Seminar on Power Semiconductors (ISPS), June 2018.

- [36] T. Kimoto, Y. Kanzaki, M. Noborio, H. Kawano, and H. Matsunami, "Interface properties of metal–oxide–semiconductor structures on 4H-SiC {0001} and (1120) formed by N<sub>2</sub>O oxidation" Jpn. J. Appl. Phys., vol. 44, no. 3, pp. 1213, March 2005. DOI: 10.1143/JJAP.44.1213

- [37] G. Ortiz, C. Strenger, V. Uhnevionak, A. Burenkov, A. J. Bauer, P. Pichler, F. Cristiano, E. Bedel-Pereira, and V. Mortet, "Impact of acceptor concentration on electrical properties and density of interface states of 4H-SiC n-metal-oxide-semiconductor field effect transistors studied by Hall effect", Appl. Phys. Letts., vol. 106, no. 6, pp. 062104, Feb. 2015. DOI:10.1063/1.4908123.