### University of Groningen

# Revealing Buried Interfaces to Understand the Origins of Threshold Voltage Shifts in Organic Field-Effect Transistors

Mathijssen, Simon G. J.; Spijkman, Mark-Jan; Andringa, Anne-Marije; van Hal, Paul A.; McCulloch, Iain; Kemerink, Martijn; Janssen, Rene A. J.; de Leeuw, Dago M.

Published in: Advanced materials

DOI: 10.1002/adma.201001865

IMPORTANT NOTE: You are advised to consult the publisher's version (publisher's PDF) if you wish to cite from it. Please check the document version below.

Document Version Publisher's PDF, also known as Version of record

*Publication date:* 2010

Link to publication in University of Groningen/UMCG research database

*Citation for published version (APA):* Mathijssen, S. G. J., Spijkman, M-J., Andringa, A-M., van Hal, P. A., McCulloch, I., Kemerink, M., Janssen, R. A. J., & de Leeuw, D. M. (2010). Revealing Buried Interfaces to Understand the Origins of Threshold Voltage Shifts in Organic Field-Effect Transistors. Advanced materials, 22(45), 5105-+. https://doi.org/10.1002/adma.201001865

#### Copyright

Other than for strictly personal use, it is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license (like Creative Commons).

The publication may also be distributed here under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license. More information can be found on the University of Groningen website: https://www.rug.nl/library/open-access/self-archiving-pure/taverneamendment.

#### Take-down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from the University of Groningen/UMCG research database (Pure): http://www.rug.nl/research/portal. For technical reasons the number of authors shown on this cover page is limited to 10 maximum.

## ADVANCED MATERIALS

### Revealing buried interfaces to understand the origins of threshold voltage shifts in organic field-effect transistors

Simon G. J. Mathijssen, Mark-Jan Spijkman, Anne-Marije Andringa, Paul A. van Hal, Iain McCulloch, Martijn Kemerink, René A. J. Janssen, Dago M. de Leeuw

**Supporting Information**

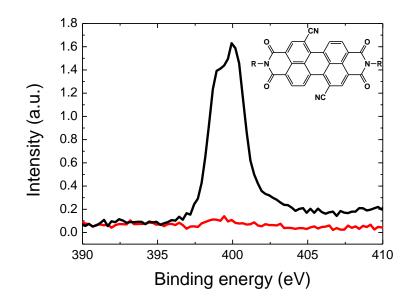

Field-effect transistors were prepared on heavily doped Si wafers, acting as common gate, covered by 200 nm thermally grown SiO<sub>2</sub> acting as the gate dielectric. Gold source and drain contacts were defined by conventional photolithography. The gate dielectric was passivated by vapour deposited hexamethyldisilazane, HMDS. As semiconductor we now use a perylene derivative (ActivInk<sup>TM</sup> N1400, Polyera), an air-stable *n*-type semiconductor. The chemical formula is given as inset in Fig. S1. XPS as presented in Figure S1 shows that the perylene is completely removed upon delamination. The N1s peak before exfoliation has two contributions; the peak at 399 eV is attributed to the nitrile group. The contribution at a binding energy of 400.2 eV occurs due to the presence of the imide group.

**Figure S1:** X-ray photoemission spectroscopy before (black) and after (red) perylene exfoliation. After exfoliation the N1s peak is gone, the perylene is completely removed.

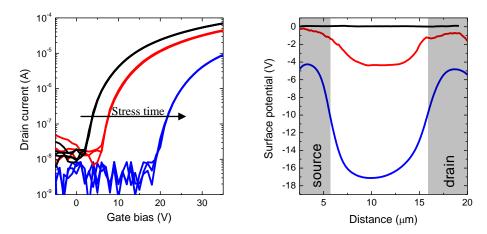

Perylene transistors were subjected to a continuous gate bias of 60 V, source and drain electrodes were grounded. Linear transfer characteristics as a function of stress time are presented in Fig. S2a. The transfer curves shift with stress time in the direction of the applied gate bias; in Fig. S2a to the right.

In order to show that the exfoliation procedure can be extended to examine charge transfer across different weakly bound buried interface, the perylene semiconductor is

## ADVANCED MATERIALS

delaminated at different stages of the stress experiment. Different perylene transistors were stressed for specific periods of time. At the end a transfer curve is measured, the semiconductor is peeled off and the surface potential of the exposed gate dielectric is probed with SKPM with all electrodes grounded. The transfer curves are presented in Fig. S2a with the corresponding surface potentials plotted in Fig. S2b. The non-zero potential originates from the negative interface charges in the gate dielectric. With stress time the surface potential decreases. The magnitude of the surface potential after exfoliation matches to the threshold voltage of the transfer curve before exfoliation, showing that the gate bias stress effect is dominated by charge transfer into the SiO<sub>2</sub> gate dielectric.

**Figure S2.** Charge transfer to the gate dielectric. (a) Transfer curves as a function of stress time measured at a drain bias of 5 V. The gate bias during stress was 60 V. The curves shift to positive voltage. (b) Corresponding surface potential profiles after perylene exfoliation. The net surface potential of the negative charges in the dielectric is revealed.