# Reverse-Conducting Insulated Gate Bipolar Transistor: A Review of Current Technologies

E. M. Findlay, and F. Udrea, Member IEEE

Abstract—The Reverse Conducting IGBT has several benefits over a separate IGBT and diode solution and has the potential to become the dominant device within many power electronic applications; including, but not limited to, motor control, resonant converters, and switch mode power supplies. However, the device inherently suffers from many undesirable design trade-offs which have prevented its widespread use. One of the most critical issues is the snapback seen in the forward conduction characteristic which can prevent full turn-on of the device and result in the device becoming unsuitable for parallel operation (required in many high voltage modules). This phenomenon can be suppressed but at the expense of the reverse conduction performance. This paper provides an overview of the technical design challenges presented by the RC-IGBT structure and reviews alternative device concepts which have been proposed in literature. Analysis shows that these alternate concepts either present a trade-off in performance characteristics, an inability to be manufactured, or a requirement for a custom gate drive.

Index Terms— Insulated Gate Bipolar Transistor (IGBT), Reverse Conducting Insulated Gate Bipolar Transistor (RC-IGBT), Body diode, Anti-parallel diode, Power devices, Power Electronics

#### I. INTRODUCTION

Since the development of the Insulated Gate Bipolar Transistor (IGBT) in 1979 [1], the potential to obtain high on-state current density within a high voltage device has resulted in an exponential growth in the use of IGBTs in a variety of applications in the 600V to 4.5kV range [2]. In recent years, the IGBT has replaced the silicon Power Metal Oxide Semiconductor Field-Effect Transistor (MOSFET) in certain applications since the IGBT has a lower on-state voltage for the same voltage blocking rating due to the bipolar injection mechanism within the device [3], [4].

Compared to MOSFETs, the IGBT can operate at higher power densities due to lower on-state losses [3], but Power MOSFETs have an intrinsic anti-parallel (body) diode providing a reverse conduction path which is not present in the structure of a traditional IGBT [5]. For most power electronic applications, including but not limited to motor control, resonant converters and high switch mode power supplies, the IGBT is utilised in conjunction with a free-wheeling diode (FWD) connected in anti-parallel, typically fabricated in either

separate packages or connected die within a module [5].

The FWD performance is critical during both normal switching and under surge conditions [4]. Separate connections introduces additional cost (bonding, packaging and silicon) [4], [5]. Furthermore, these bond wires can introduce parasitic oscillations under switching conditions, which can lead to additional die losses. By integrating the switch and the antiparallel diode into a single structure, the Reverse-Conducting IGBT (RC-IGBT) enables a higher power per package footprint to be achieved [4]. However the traditional RC-IGBT cannot be used in high power applications as the device is not suitable for parallel operation due to the negative resistance characteristic exhibited in the on-state (forward conduction) [6]. Limitations fabrication technologies have also hampered development of the RC-IGBT concept, however with the emergence of thin-wafer processing (and alternative techniques such as reactive ion etching [7]) more device concepts are being realised and it has become an active area of research [5].

This paper provides a review of the RC-IGBT concepts, highlighting the advantages and disadvantages of each design and discussing the challenges in commercialisation.

# II. TRADITIONAL RC-IGBT STRUCTURE

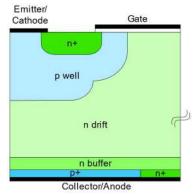

The RC-IGBT structure was first proposed in 1987 with a collector shorted, p-channel IGBT [8] building upon the concept suggested by Ueda et al. [9]. A commercially available SPT n-channel RC-IGBT is given in Fig. 1. To integrate the diode structure within the IGBT n+ regions (anode shorts) are implanted into the p-collector region (p-anode) [10], [11].

Fig. 1. Reverse Conducting (RC) Infineon IHW20N120R3 IGBT [44].

Manuscript submitted 9 August 2018, revised 2 November 2018. This work was supported in part by UK Innovate Project Number 102878. E. M. Findlay was funded by EPSRC Doctoral Training Partnership scheme (grant RG75686).

E. M. Findlay and F. Udrea are with the Electrical Engineering Department, University of Cambridge, Cambridge, CB3 0FA, UK. (e-mail: emf34@cam.ac.uk; fu@eng.cam.ac.uk)

When a reverse voltage is applied to the device, electrons are provided by the n+ anode short and holes are injected from the p-well which is connected to the p+ emitter (p+ cathode), resulting in the device behaving similarly to a PIN diode. It has been reported that the doping profile of the field stop (buffer) layer can be optimised to improve turn-off losses by modifying the injection efficiency of the anode (emitter) [11]. The RC-IGBT presents several advantages;

- 1. An RC-IGBT uses less area than an equivalent IGBT and diode (>30% size reduction)

- 2. Reduction in assembly cost (bonding, packaging and less silicon area)

- 3. Reduction in wafer processing and testing cost

- Lower thermal resistance and reduced temperature ripple as the same silicon volume is used during both diode and IGBT conduction modes

- 5. More degrees of freedom in package layout

- 6. Improves reliability due to fewer bond wires within a module (bond wires induce parasitic (inductive) effects)

- 7. More suitable for high junction temperature operation as the leakage current in IGBT mode is lower due to the presence of the anode shorts (reduced pnp transistor gain).

- 8. Possibility of using a suitable gate signal to allow better trade-off between the on-state voltage drop and the reverse recovery losses of the diode. [5], [12], [13]

However, the RC-IGBT structure within high voltage, hard switching application suffers from several undesirable characteristics;

# A. Snapback in the current-voltage characteristic is present (MOSFET shorting effect)

Anode shorts provide a MOSFET structure within the IGBT such that at initial turn-on of the device, unipolar conduction occurs (current flow through the anode short) until the n buffer/p+ anode region becomes forward biased so that hole injection from the p+ collector begins and conductivity modulation occurs in the drift region. This results in a rapid decrease in the on-state resistance causing the snapback exhibited in the I-V characteristic. This snapback is more prevalent at lower temperatures, as the voltage drop needed to forward bias the p+ collector/n buffer junction increases at lower temperature at a rate of approximately 2mV/°C. As a consequence, at low ambient temperatures the device can fail to fully turn-on. Reduction in the density of n+ shorts within the device area can reduce the snapback voltage but at the expense of the anti-parallel diode performance. [4], [5], [10], [12], [14], [15].

# B. A trade-off between the IGBT on-state losses and the diode reverse recovery losses (plasma shaping effect)

Plasma distribution affects both the on-state and switching losses. Moreover, the collector p-wells in forward conduction (IGBT mode) are also the anode of the device in reverse conduction (diode mode). It is desirable to have a high plasma concentration in the upper part of the drift region (closer to the gate) to reduce the on-state losses in IGBT mode, but in order to minimise the reverse recovery losses of the diode, a low

plasma concentration is desirable. These contradictory aims are difficult to optimise, but typically local lifetime control helps to achieve selective plasma reduction [16], [17].

# C. Reduction in SOA (the charge uniformity effect)

Non-uniform current distribution occurs in RC-IGBTs due to the relatively large p+ collector (anode) implant, compared to the n+ anode short. Current crowding can occur at the p+ collector/n+ anode short boundary when the RC-IGBT conducts in diode mode. This can result in the device overheating and the local hotspot formation can ultimately lead to the destructive failure of the device. [18].

# D. A trade-off between the IGBT and diode softness (drift layer effect)

It is desirable for the RC-IGBT to have a thin n-drift layer to minimise on-state losses in IGBT mode. However, this low resistance induces a high di/dt during the reverse recovery of the diode which causes it to exhibit snappy behaviour. The diode is therefore prone to hard reverse recovery which increases electromagnetic interference [12], [19].

There have been many reported optimisations of the traditional RC-IGBT structure to overcome these trade-offs. Several papers have investigated the use of a dedicated gate drive scheme in order to reduce losses by varying the p-emitter (p-anode of diode) efficiency [20], [21]. Although the devices with this additional gate control enable the user to vary the onstate voltage for the diode, the complicated nature of the gate control (the requirement for a dedicated current direction detection during inverter operation) makes it unsuitable for the majority of applications [20], [21]. An alternate variation is the introduction of an oxide trench between the anode short and the p+ anode which increases the resistance of the short such that the snapback characteristic is suppressed but the device suffers from non-uniform current flow and poor switching performance [22]. In addition, the processing of the oxide trench on the back of the wafer is challenging and the effect of phenomena such as hot carrier injection still needs to be examined.

Research has also been conducted into improving the junction terminations to improve the safe operating area of the RC-IGBT [23] as well as optimising the dimensions and structure of the FWD within the RC-IGBT to minimise losses without lifetime control in order to minimise process steps [24].

# III. ALTERNATE RC-IGBT STRUCTURES

Several approaches have been proposed to improve the electrical performance of the RC-IGBT. The concepts can be grouped into four classifications, which are explored in more detail in the following sections;

- 1. Thyristor based structures

- 2. Complex backside processing

- 3. Pilot structures

- 4. Other concepts

A summary of these structures' advantages and disadvantages can be found in Table I. 2D simulations of some

of these concepts have been modelled using a comparable cell to enable a direct performance comparison. Results are given in Section VIII.

#### IV. THYRISTOR BASED STRUCTURES

# A. RC-IGBT with Anti-parallel thyristor

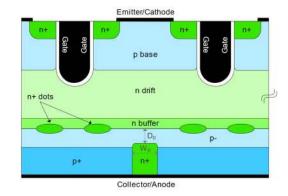

A proposed RC-IGBT which utilises a thyristor to enable conduction in the reverse direction is shown in Fig. 2 (without n+ dots). The NPT variation of this concept has also been reported as RC-TCIGBT [25]. Within the p+ anode region, an n+ column is present leaving a narrow p- layer before the n+ buffer region; the p base, n- drift/n buffer, p- layer, n+ column form the thyristor structure. It is reported that the thyristor has a comparable on-state voltage to an anti-parallel PIN diode, but the thyristor structure is not immediately triggered when a 0.7V forward bias is applied, instead occurring when the current gain of the NPN and PNP transistors equal 1 or when either the NPN or PNP is operating in punch through mode (either the n- drift/n buffer or the p- layer is depleted) [14].

The narrow p- layer present in this design forms a barrier to electrons when conducting in IGBT mode, thus avoiding the snapback phenomenon, assuming that  $D_P$  (Fig. 2) is of sufficient size. As  $D_P$  is reduced, the gain of the NPN transistor increases such that electrons are no longer confined to the n buffer layer and the snapback characteristic in the I-V characteristic re-emerges [14]. In the extreme (when  $D_P = 0$ ) this results in the traditional RC-IGBT structure (Fig. 1). To minimise the snapback phenomenon in the forward conduction direction it is important that the PNP transistor is turned on quickly which can be achieved by: increasing the channel density, increasing  $R_{n \text{ buffer}}$ , or reducing current gain of the NPN transistor to facilitate turn-on of the PNP [14].

2D simulations showed that by increasing the channel density, a snapback characteristic in the reverse conduction state emerges (the  $\alpha_{pnp}$  is reduced to such an extent that it is difficult to turn on the thyristor) [14]. A similar snapback occurs in the reverse conducting characteristic when the carrier lifetime is decreased, despite the overall improvement to the switching performance [14]. To eliminate this snapback in the reverse conduction characteristic, the addition of floating n+ dots (Fig. 2) to restrict hole injection was proposed such that carrier lifetime could remain high without affecting switching performance [14]. A number of dots were removed above the n+ column to reduce the turn-over voltage in the forward conduction without affecting the turn-off time [14]. Simulation results have indicated several trade-offs with this proposed solution. Firstly, the snapback in the forward conduction mode was not eliminated, but the effect was less pronounced with the removal of more n+ dots above the n+ column and the turn-off time for the IGBT increased as more n+ dots were removed.

A variation on the design includes the addition of dielectric (oxide) trenches either side of the n+ column, instead of the use of n+ dots [26]. Simulation results have reported that these techniques also suppress the snapback phenomenon. By increasing the number of parallel thyristor structures within a single device (by reducing the n+ column and p+ anode widths),

Fig. 2. Device structure of the RC-IGBT with anti-parallel thyristor and n+ dots [14].

Fig. 3. Device structure for SH-RC-IGBT [27].

a more uniform current density distribution can be achieved in both the forward and reverse conduction direction for a given chip area, but this in turn results in increased on-state losses in both modes. [26]

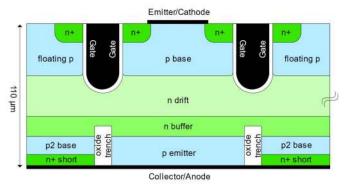

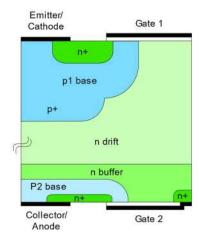

A similar oxide trench thyristor structure has also been reported as RC-IGBT with anti-parallel Shockley diode (SH-RC-IGBT) (Fig. 3) [27]. Simulated results for the SH-RC-IGBT show an improved on-state voltage compared to the conventional RC-IGBT of 25% in the forward mode and 50% in the reverse mode. To eliminate the snapback characteristic, the SH-RC-IGBT requires a carrier lifetime less than 0.5 µs and a 10µm wide drift region (300µm for conventional RC-IGBT). As a result of the former, the Shockley diode requires a much higher current to be triggered, although the impact of this can be reduced by reducing the doping concentration of the p2-base. The device also has an improved current distribution which increases the SOA of the SH-RC-IGBT, but suffers from a higher reverse-recovery charge (Q<sub>rr</sub>) and longer delay in turnoff due to the higher injection efficiency, making it unsuitable for higher frequency applications. [27]

Experimental data to support the simulation results has yet to be reported for RC-IGBT with anti-parallel thyristor structures. All of these studies indicate that the trade-off between forward and reverse conduction capabilities is difficult to optimise for this structure [10].

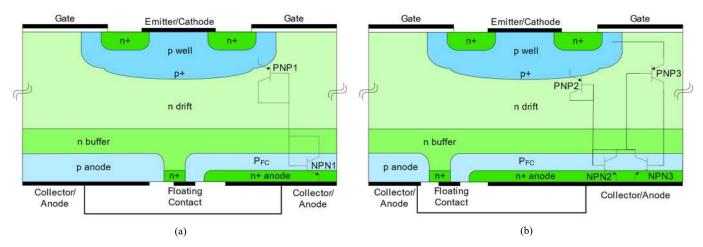

# B. Pseudo-double anode RC-IGBT

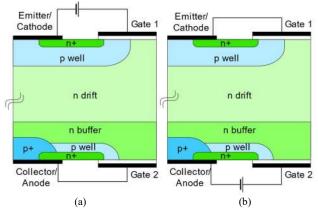

A variation upon the RC-IGBT with anti-parallel thyristor, the Pseudo-double anode (PDA-RC-IGBT) structure is shown

Fig. 4. PDA-RC-IGBT structure (a) diode version (b) thyristor version [28].

in Fig. 4, with two variations to provide diode and thyristor conduction. The P<sub>FC</sub> region is short-connected with the n-buffer through a floating contact. Snapback is suppressed, as under forward conduction, the n+ anode and PFC region are reverse biased and therefore make no contribution to current flow. When the structure is reverse biased (V<sub>CE</sub><0) the floating contact ensures that both bipolar transistors (PNP1 and NPN1) are in a collector-base short-circuited configuration, such that electrically the device behaves as two series connected diodes under this condition. This does however result in a higher reverse voltage drop compared to a traditional RC-IGBT. For larger current density applications, the device can be modified to trigger the parasitic thyristor formed by PNP3 and NPN3. Compared to the diode version, the thyristor has lower on-state voltage drop but has a negative resistance characteristic. The PDA-RC-IGBT has a recombination current in the forward conduction state which reduces the overall injection efficiency of the device, but has a significantly more uniform current distribution for both diode and thyristor versions which increases the SOA of the device. [28]

#### V. COMPLEX BACKSIDE PROCESSING

## A. RC-IGBT with Floating P-Region

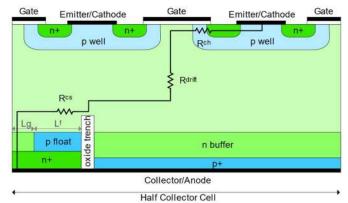

Fig. 5 shows a schematic cross-section of the RC-IGBT with floating p-region structure. An oxide trench is present at the collector/anode of the device, with a floating p doped region, p-float, located between the n-collector and the n-drift. The p-float region begins at a distance  $L_{\rm g}$  from the edge of the device. The FWD structure is achieved via p-well, n-drift, n-buffer and n-collector on the extreme left of the schematic. At large currents, the NPN transistor, formed by n-collector, p-float, n-drift, can become activated to provide a low-impedance current path (the emitter for the forward and reverse conduction is the n-drift and n-collector respectively). For small currents, the p-float acts as a barrier to electrons, which together with the oxide trench, forms a high-resistance collector short path suppressing the snapback characteristic. [22]

Simulation results have shown that by increasing L<sub>F</sub> the snapback can be reduced and ultimately eliminated under certain conditions even at -40°C. In practice, however, L<sub>F</sub> is

reduced to achieve a better trade off in performance; smaller  $L_F$  has lower turn-off losses but increased forward voltage drop. With this optimisation, it is reported that the proposed RC-IGBT turn-off time is reduced by 21% compared to a conventional RC-IGBT or 27% compared to a Soft Punch Through or Field Stop IGBT (SPT-IGBT/FS-IGBT), attributed to the small collector cell length and the action of the NPN transistor. [22]

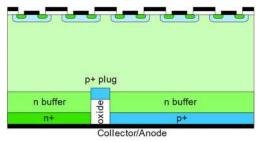

A similar structure utilising the p-plug concept has been proposed in Fig. 6. This device has an improved current distribution but suffers from the snapback effect. By reducing the non-uniform current distribution typically found in RC-IGBTs, the likelihood of local hotspot formation (and ultimately the destructive failure of the device) is lowered. The introduction of the p-plug in the n-buffer layer above the oxide trench, means that the electron path in the n-buffer is blocked

Fig. 5. RC-IGBT with floating p-region device structure [22]

Fig. 6. RC-IGBT with floating p-plug situated on top of an oxide trench in the n-buffer layer [18].

(in the x direction, Fig. 6), such that the device can be split into two discrete parts (IGBT and diode) unlike a conventional RC-IGBT. The device can be optimised to maximise the conduction volume in each mode, with simulations reporting 90% utilisation in IGBT mode (75% for a standard RC-IGBT and 35% for BIGT) and 60% in diode mode (30% for a standard RC-IGBT and 27% for BIGT). This increased the reliability of the proposed device, but, did induce a larger snapback characteristic [18].

Fig. 7 shows the Carrier Stored Floating P-region Reverse Conducting IGBT (CSFP-RC-IGBT). The device contains an n doped charge stored (CS) layer between the p-well and the ndrift region, which is comparatively more doped than the drift region. The addition of this layer reduces the on-state voltage drop in IGBT mode and, with increased doping density, reduces the on-state resistance compared to a RC-IGBT with floating pregion but increases the turn-off losses slightly. The concept of CS was also described in the HiGT structure from Hitachi [29] and the SPT+ structure from ABB [30]. For increasing carrier concentration in the CS layer, the I-V characteristic tends towards a PIN diode, however, the breakdown voltage of the device is reduced. There were no reported results regarding the performance of the reverse conducting diode, however, given the increase in carriers at the cathode, the performance is expected to worsen. [31].

Fabrication of these structures are complex and costly due to the requirement for backside photolithography and the non-uniform current distribution in both conduction states, so these results are limited to simulation only [19].

# B. RC-IGBT with Alternating N/P Buffers (AB RC-IGBT)

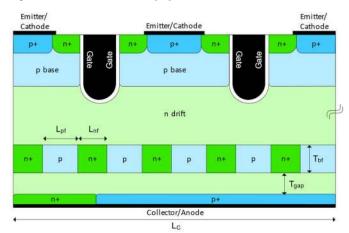

The Alternating Buffer Reverse Conducting IGBT (AB RC-IGBT), shown in Fig. 8, has a similar structure to a conventional RC-IGBT with the addition of a buffer layer with alternating n and p implants. In this device, the p buffer acts as an electron barrier, forcing the electrons to flow through the high resistance n-drift region between the buffer and collector. Fig. 9 compares the on-state performance of the AB RC-IGBT to the RC-IGBT with floating p-region (Fig. 5) and a conventional RC-IGBT. For a collector length ( $L_{\rm C}$ ) 30µm, the AB RC-IGBT can eliminate snapback entirely, whereas a collector length of 80µm is required for RC-IGBT with floating p-region to eliminate snapback: shorter devices are more desirable to reduce the current crowding at the anode short during reverse conduction. [32].

This snapback suppression is achieved by increasing the relative implant width of the p buffer region (L<sub>pf</sub>) compared to the n+ buffer (L<sub>nf</sub>) to increase the barrier to electron flow. However, the AB RC-IGBT structure has a parasitic PNP transistor, formed between the p+ collector/n-drift/p buffer. Base punch through of this parasitic transistor compromises the blocking capabilities of the device which becomes increasingly significant for wider p buffer implants. Wider p buffer regions also result in larger switching losses as the p buffers obstruct extraction of excess carriers in the drift region during turn-off. However, the AB RC-IGBT is still a 20% improvement on a conventional RC-IGBT for a device with the same IGBT on-

Fig. 7. CSFP-RC-IGBT structure [31].

Fig. 8. Alternating Buffer (AB) RC-IGBT [32].

Fig. 9. I-V characteristic of AB RC-IGBT ( $L_{\rm C}$  (collector length)=30 $\mu$ m,  $L_{\rm P}$  (p+length)=25 $\mu$ m), RC-IGBT with floating p-region ( $L_{\rm C}$ =30 $\mu$ m,  $L_{\rm P}$ =25 $\mu$ m) and a conventional RC-IGBT ( $L_{\rm C}$ =300 $\mu$ m,  $L_{\rm P}$ =295 $\mu$ m) [32].

state voltage. Increasing the thickness of the buffer layer (T<sub>bf</sub>) also helps supress snapback by shielding electrons in unipolar mode, but this in turn reduces injection efficiency and increases the on-state losses during IGBT conduction. [32]

# C. RC-IGBT with double gate structure

The Dual-Gate Bidirectional IGBT (BD-IGBT or DGIGBT) was first proposed in 1988 by Nakagawa [33]. Fabrication techniques to realise this structure have since been developed and in 2014 a 1200V 25A single-chip dual-gate BD-IGBT was manufactured with a fusion wafer bonding process [34] but fabrication of IGBTs with lower breakdown voltages using this method have resulted non-ideal electrical performance [34].

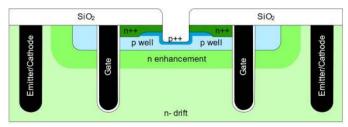

The structure of the BD-IGBT is shown in Fig. 10. The structure inherently has a reverse conducting diode: in the forward conduction mode, with gate 2 shorted and gate 1

positively biased, normal IGBT conduction occurs, whereas with gate 2 forward biased and gate 1 shorted a forward voltage blocking state is provided alongside a reverse conduction path, thus serving the same function as a FWD [33]. Turn-off losses are smaller than a standard FS-IGBT as an anode short is effectively realised when an n-channel is formed underneath a positively biased gate, resulting in a shorter turn-off irrespective of carrier lifetime within the device [33], [35]. Due to the structural symmetry, the forward and reverse conduction behaviour is the same, with the I-V characteristic 180° symmetric about the origin [35].

Operation of this device is, however, complicated. A quasi-IGBT mode can be achieved when both gates are positive, as the hole injection efficiency of the backside p-well (in either conduction direction) is reduced by the presence of the parallel MOS channel [35]. It is also possible to exhibit MOSFET behaviour when the current is lower than a threshold value I<sub>H</sub> (typically ~4A/cm²) such that the backside p-well is biased by <0.7V so hole injection does not occur. It is this transition from MOSFET mode to quasi-IGBT mode which exhibits the snapback characteristic in the I-V curve, however, in this operation mode much higher switching speeds can be achieved than in the IGBT mode [35] and higher back-gate voltage reduces the susceptibility of the breakdown voltage and leakage currents with temperature [34]. It has been reported that multifaceted gate drive schemes can be implemented to

Fig. 10. BD-IGBT device structure, (a) forward conduction mode, (b): reverse conduction mode [33].

Fig. 11. AG-RC-IGBT structure [10].

optimise the switching and on-state losses of the device for various applications [35]. However, this makes the device undesirable for use within the majority of commercial circuits due to the increased cost and complexity of driving two gates for a single switch.

To be more favourable to a larger range of applications, the Automatically Controlled Gate RC-IGBT (AG-RC-IGBT, Fig. 11) has been proposed [10]. The structure is similar to that given in Fig. 10 except that the anode gate (gate 2) is connected to the n+ region within the n-buffer through an ohmic contact. In this device, the voltage of gate 2 is lower than that of the anode in forward conduction mode and therefore snapback does not occur [10]. In reverse conduction mode, when a voltage is applied to the anode, the capacitance of gate 2 is charged through the floating n+ region (that the gate has an ohmic contact with) until the threshold voltage is achieved and a reverse conduction path is provided. The device suffers from a higher on-state resistance compared to a conventional RC-IGBT [10]. The doping of the p2 base is reduced for faster charging of the gate and to enable the device to operate at higher switching speeds and lower anode voltages, however, this in turn reduces the injection efficiency of the anode in the forward conduction state [10]. With some optimisation, it is possible to trigger the thyristor structure (p+ region (top), n-drift/n-buffer, p2-base, n+-region) to form a MOS-controlled thyristor (MCT) in the reverse direction. This structure has a lower on-state resistance making it more suitable for higher current densities, but the snapback phenomenon re-emerges in both conduction directions, presenting an issue if the device is paralleled [10]. In both variations of the AG-RC-IGBT, the non-uniformity of current distribution in the volume of silicon can lead to localised hot-spots, limiting both the current capability and reliability of the device [26]. There has been no reported experimental data for AG-RC-IGBT.

## D. Tunnelling Injection IGBT (TIGBT)

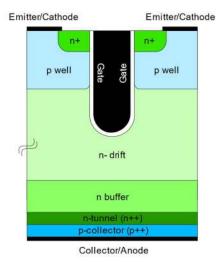

The tunnelling Injection IGBT (TIGBT) (Fig. 12) uses band-to-band tunnelling to overcome the known issues with the traditional RC-IGBT. A highly doped (10<sup>19</sup>cm<sup>-3</sup>) n-tunnel layer is sandwiched between the p++ collector and the n-buffer. For forward conduction, the collector (anode) and the gate are positively biased, and there exist a common band of energies such that electrons can tunnel from the n-tunnel into the p++ collector. The device exhibits a snapback characteristic since for increasing collector voltage the tunnelling current decreases after reaching a peak value. This peak current exponentially increases with the decrease in the barrier width which is dependent upon the doping concentrations [19]. It is possible to remove this snapback by increasing the doping concentration of the n-tunnel and p++ collector but at the expense of the diode mode conduction losses. [19].

In the reverse direction, the device is equivalent to a PIN diode in series with a backward tunnel injection; with the collector negatively biased and the gate zero biased, electrons can inject via band-to-band tunnelling from the p-collector into the n-tunnel layer. In diode mode, the TIGBT exhibits a soft recovery as electrons extracted through tunnelling across the n-

Fig. 12. TIGBT structure [19].

tunnel/p++ collector junction induces hole injection into the ndrift which results in a small reverse recovery and minimal voltage overshoot. However, these injected holes attract electrons to maintain charge neutrally in the drift region which need to be extracted from the p-well to the emitter. This induces a relatively long current tail in the turn-off which is undesirable in high frequency applications. The TIGBT conducts uniformly across the device region (unlike a standard RC-IGBT) and therefore the device has a smaller turn-on voltage at low currents and the reverse recovery peak currents are reduced. The device also has the advantage over the other concepts that the fabrication method does not need to allow for non-uniform current distribution nor require backside photolithography, which is a complex and expensive fabrication process, however it is very difficult to produce a very thin n-tunnel layer with such high doping. [19].

#### VI. PILOT STRUCTURES

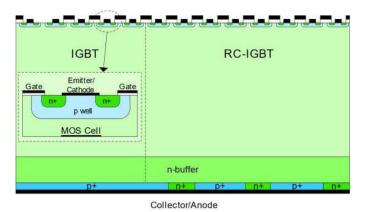

## A. BIGT (Bi-mode Integrated Gate Transistor)

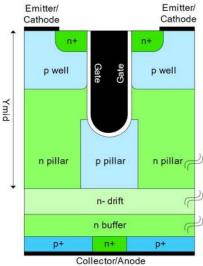

The BIGT was first proposed in 2009 by ABB Semiconductors, and consists of a hybrid structure of an IGBT (referred to as a pilot-IGBT) and RC-IGBT integrated into a single device (Fig. 13) [16]. The initial prototype device was a 3300V module, but in 2013 a 6500V HiPak module was produced [6]. The overall module performance (output current) of the BIGT compared to a separate IGBT/diode solution is up to 15% higher [36].

The pilot-IGBT is sized to reduce the snapback in the forward conduction mode at low temperatures [16]. The device has, however, suffered from secondary snapbacks due to plasma formation primarily limited to the IGBT region with only a small section of the RC-IGBT area being conductivity modulated [37]. In order to utilise the full device area through the lateral expansion of the plasma area towards the RC-IGBT area, a radial layout of the anode shorts is used. This achieves the optimum trade-off in diode and IGBT conduction losses while eliminating this secondary snapback [37]. It also results in the on-state characteristics being less sensitive to the n buffer doping, therefore providing another degree of freedom to

optimise the device for high temperature operation [37].

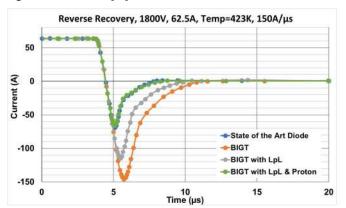

Reduction in the reverse recovery losses in the diode while minimising the impact on the on-state performance in the forward direction was achieved by finite control of the doping profile of the cathode (emitter) p-well and the anode (collector) p+/n+ regions using Local p-well Lifetime (LpL) control through particle implantation and uniform local lifetime control through proton irradiation [16]. The impact of these three steps is highlighted in Fig. 14. The finite control of the p-well results in a worsening of performance of the individual device under surge, however in typical applications where multiple devices are paralleled into a single BIGT module, this is compensated by the increased silicon area such that the overall surge capability remains constant [6]. It was reported that as a result of performing the uniform local lifetime control, the forward conduction mode on-state voltage increased by 300mV to 3.3V at 125°C [16]. However, a 10% reduction in the diode mode reverse recovery and IGBT mode turn on losses are obtained when MOS Control Diode function is utilised [16], [17]. This increase in the conduction losses limited the output current capability of the device at low frequencies [6], and the on-state voltage drop in diode mode (reverse conduction) is relatively high at 3.0V at 125°C [16].

The gate voltage has a strong influence on the reverse conduction losses during diode mode, as it affects the plasma shape near the emitter, by causing the shorting of the RC-IGBT/BIGT MOS cells' p-well which are functioning as the anode regions of the diode [6], [38]. As a result, the gate voltage is required to be below the MOS channel threshold so that pwell injection remains high [6], [38]. The optimum control has the channel off during diode conduction mode, with it turned on towards the end of the diode conduction time, before being turned-off again prior to diode reverse recovery to prevent a short circuit [36]. As a consequence of this complex gate drive scheme to prevent unnecessarily high conduction losses and to optimise switching performance, operation of the device is more difficult, making it less attractive to application circuit designers [6]. It has been acknowledged that it is this requirement for a custom gate drive scheme, which is one of main obstacles preventing the BIGT from being adopted in mainstream applications [38].

The device exhibits a strong positive temperature coefficient in both modes thus making it suitable for paralleling in modules to achieve higher operating powers [16]. The SOA of the BIGT is not compromised but the temperature ripple is reduced as the same volume of silicon is heated during both IGBT and diode mode, therefore increasing the reliability of the device [6], [16]. Switching losses are comparable to SPT-IGBT/diode modules but BIGT does not show oscillations or voltage overshoot caused by current tail snap-off [6], [16]. The BIGT has softer turn-off behaviour in both conduction modes compared to state of the art IGBT and diode modules due to the presence of injected holes and charge extraction [16].

The Enhanced Trench Bi-mode Insulated Gate Transistor (ET-BIGT) is a further development of the BIGT concept. The enhanced trench (ET) structure (Fig. 15) reduces conduction losses in the IGBT mode by enhancing the excess carrier

Fig. 13. BIGT structure [16].

Fig. 14. Nominal reverse recovery currents for 3.3kV/62.5A BIGT operating in diode mode at 125°C [16].

Fig. 15. Enhanced Trench MOS cell structure [39].

concentration at the MOS cell structure [39]. It also provides improved controllability while extending the maximum junction temperature rating [39]. The ET-BIGT addresses the requirement on the BIGT that the gate voltage should be less than a threshold during diode conduction to reduce on-state losses [6]; the ET design was optimised for reverse mode conduction losses under positive gate biasing conditions for ease of control and to maintain good surge capability [39]. Initial results have shown that without MOS gate control the ET-BIGT can achieve lower switching losses compared to the Enhanced Planar BIGT, but the trench cell does suffer from a higher diode on-state forward voltage when a positive gate emitter bias is applied [39]. The addition of a pilot diode perpendicular to the gate/emitter trenches is required for low diode conduction losses under positive gate bias; the pilot diode makes the ET-BIGT diode mode performance comparable with the EP-BIGT [39]. Results have indicated that the pilot diode region does not affect the performance of the ET cell if the dimensions between the repetitive pilot diode regions are large,

however it does give a higher forward voltage drop in diode mode [39]. Recent research has focussed on optimising the ET-IGBT with pilot diode to eliminate the need for complex gate drive schemes [38]. The study reported a reduction in the forward voltage drop of the diode by 1.2V compared to the reference BIGT under +15V gate bias condition, but the new BIGT suffers from a 21% increase in diode recovery losses and 11% increase in IGBT mode turn-on losses at 150°C [38]. This indicates that this optimised version of the device is only suitable at low switching frequencies (<500Hz) and that different design trade-offs should be chosen for applications where the BIGT is required to switch faster [38].

#### VII. OTHER CONCEPTS

# A. RC-IGBT with Superjunction Structure

The majority of RC-IGBT development has focussed on the anode structure, however, the Trench Field Stop Superjunction RC-IGBT (TFS SJ RC-IGBT) (Fig. 16) instead employs a superjunction structure at the cathode and utilises traditional anode shorts to provide the reverse conduction path [5], [40]. It should be noted that the p-pillars in the superjunction structure do not extend all the way through the drift region; the p-pillar length  $(Y_{mid})$  is considerably smaller than the total length of the drift region, resulting in the device being often referred to as a semi-superjunction structure [40].

In the conventional RC-IGBT structure (and ordinary IGBT), the resistance of the n-drift region is determined by the region's thickness and doping, which is limited by the breakdown rating of the device. Employing the superjunction structure within the RC-IGBT allows the n-drift doping to be increased by several orders to magnitude without impacting the breakdown voltage, and thus reducing the drift region resistance significantly. In fact, in the SJ structure the drift resistance is dependent on the length of the pillar Y<sub>mid</sub> as it is the sum of the n-pillar resistance and the remaining drift region. By increasing Y<sub>mid</sub>, the snapback voltage is reduced and is eliminated at 360µm for a 3.3kV device of thickness 370µm, even at low temperatures [5], [40]. For a TFS SJ RC-IGBT comparable with a CoolMOS structure (3 x 10<sup>15</sup> cm<sup>3</sup> p-pillar doping and Y<sub>mid</sub>=70μm), the switching losses of the proposed device are lower than a standard RC-IGBT, however, a snapback is present in the I-V characteristic. Increasing Y<sub>mid</sub> to achieve a deep superjunction results in an initial increased gate capacitance which decreases rapidly, and therefore enhanced ringing is present in the switching waveforms, which can result in worse switch-off losses compared to a NPT-IGBT [40], [41]. Increasing the doping concentration of the pillars is also detrimental to turn-off of the device as the depletion region expansion is slower [42]. The diode reverse recovery characteristic was, however, unaffected by the SJ structure [42].

The majority of investigations for the SJ RC-IGBT structure have been simulation based due to the nature of manufacturing IGBTs using Field Zone (FZ) wafers and the concern regarding the creation of voids within the structure [41]. Experimental results for the SJ SPT-IGBT and SJ NPT-IGBT were reported validating the simulations, showing that the switching losses of

Fig. 16. TFS SJ RC-IGBT [5], [40].

Fig. 17. Schottky Controlled RC-IGBT structure [43].

the SJ NPT-IGBT were lower than the SJ SPT-IGBT. The SJ-NPT had better short circuit ruggedness, but both exhibited superior on-state and switching performance compared to a traditional SPT-IGBT [41]. The results highlight that the trade-off between the forward and reverse conduction capabilities in the superjunction design is difficult to optimise [10].

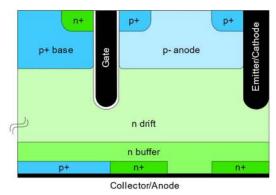

## B. Schottky Controlled Diode within RC-IGBT

The introduction of the Schottky controlled (SC) injection concept to the diode within the RC-IGBT was reported in 2016. The device structure is given in Fig. 17, where the p+ base and p- anode are formed separately to reduce reverse recovery loss by suppressing carrier injection from the surface while the patterned cathode suppresses carrier injection from the backside. The partially formed p+ ohmic areas on the anode are based upon the SC concept and high dynamic ruggedness is achieved by connecting the internal electrode of the trench at the diode area to the emitter electrode. The peak reverse recovery current was reduced by 49% due to the introduction of the anode structure compared to a conventional RC-IGBT, and the cathode structure reduced the tail current, but there was increased ringing in the reverse recovery waveforms. The study focuses on the diode performance and does not comment on the overall performance of the device, particularly in reference to behaviour in IGBT mode. [43].

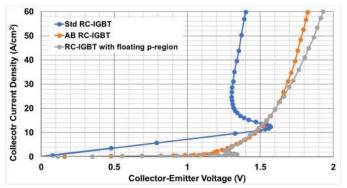

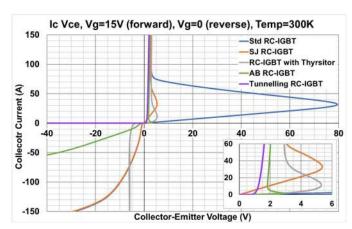

#### VIII. RC-IGBT CONCEPT COMPARISON

2D simulations were undertaken in order to directly compare some of the RC-IGBT concepts. A 1.7kV 150A trench SPT IGBT structure was used for this analysis with an n+ anode short implant covering 10% of the total collector area. This RC-IGBT structure has not been optimised for a particular application, but provides a platform for comparison. It has a snapback voltage of 79.5V and a reverse conduction voltage drop of 3.66V at 50A.

Given the BIGT and RC-IGBT with double gate structure have been manufactured and experimental results have been published, they were not included in this simulation analysis. For this investigation the basic geometry of the IGBT cell and n+ implant were not modified, and the concepts were implemented in line with the original studies. The RC-IGBT concepts which were considered are;

- 1. RC-IGBT with thyristor structure (thyristor based structure)

- 2. AB RC-IGBT (complex backside processing)

- 3. Tunnelling IGBT (complex backside processing)

- 4. TFS SJ RC-IGBT (other concepts)

Fig. 18 compares all concepts to the reference RC-IGBT. All concepts show considerable improvement to the snapback characteristic, but with varying impact on the reverse conduction performance. The thyristor structure could have been optimised further to eliminate the snapback by reducing the depth of the p+ collector implants (4 $\mu$ m in Fig. 18, with Dp=7 $\mu$ m), however this resulted in the device being unable to conduct in the reverse direction. In fact, the reverse conduction was very difficult to design and optimise, either introducing a secondary snapback as reported in the original study, or even a negative resistance characteristic shown in Fig. 18.

For the Tunnelling RC-IGBT, the n++ region was doped in line with [19] to  $7e19cm^{-3}$ . For tunnelling to occur, n++ depth could not exceed  $0.28\mu m$  (Fig. 18), which is unrealistic to manufacture given current fabrication techniques. For this IGBT cell geometry, the device showed minimal conduction in the reverse direction. Optimisation of this device is exceedingly difficult and, if it could be produced, would require fabrication processes with very small tolerances.

The Alternating Buffer in Fig. 18 was designed with  $L_{pf}=2\mu m$ ,  $L_{nf}=1\mu m$ ,  $T_{gap}=8\mu m$ ,  $T_{bf}=4\mu m$ . This geometry provided a minimal snapback in the forward conduction, but in the reverse direction the on-state losses increased by 91%. The behaviour of the AB RC-IGBT with different features was investigated, where the ratio of Lpf/Lnf was fixed at 2 in accordance with the study in [32]. Doubling the number of buffer implants across the width of the device (Lpf/Lnf=2) reduced the snapback by 17% but increased the on-resistance in the reverse conduction by over 6 times. Reducing the gap between the buffer layer and the p+ collector implant (T<sub>gap</sub>) to 2µm eliminated the snapback in the forward direction but induced a large snapback in the reverse characteristic. The placement of the anode shorts is also critical to the success of this design; by moving the anode short from the centre of the cell to the edge, the snapback is almost entirely removed as the

TABLE I SUMMARY OF RC-IGBT CONCEPTS

| Concept                                                                     | Advantages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Disadvantages                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RC-IGBT with<br>anti-parallel<br>thyristor<br>[14], [26], [27]              | Narrow p-layer (depth Dp) acts as a barrier to electrons to minimise snapback effect. Introduction of floating n-dots in the n-buffer improved switching characteristics and snapback became less pronounced as more n-dots are removed. Addition of a dielectric trench either side of n+ column suppressed snapback and resulted in a more uniform current distribution by paralleling multiple thyristor structures in the device.                                                                                                   | Minimising snapback in the forward conduction (triggering PNP faster) induces snapback in the reverse characteristic. Trade-off between snapback and switching characteristics. Removal of n-dots increased turn-off time. Addition of a dielectric trench either side of n+ column worsened on-state characteristics. Device has not been manufactured.                                                                       |

| Pseudo-double<br>anode RC-IGBT<br>(PDS-RC-IGBT)<br>[28]                     | Snapback can be supressed as diode/thyristor structure makes no contribute to current flow. Reverse conduction is achieved by the floating contact ensuring the bipolar structure is in a collector-base short-circuited configuration. Device has uniform current distribution compared to a conventional RC-IGBT and has an increased SOA. Structures can be modified for larger current density applications by triggering parasitic thyristor structure which presents lower on-state losses in the forward conduction mode.        | Higher on-state losses in reverse conduction due to two series connected diode structures. In forward conduction the device has reduced injection efficiency compared to a conventional RC-IGBT structure. Under high current applications when parasitic thyristor structure is used, in reverse conduction device exhibits a negative resistance characteristic. Device has not been manufactured.                           |

| RC-IGBT with floating p-region [18], [22], [31]                             | For large currents, the NPN transistor (n-collector, p-float, n-drift) can provide a low-impedance current path. For small currents, the p-float acts as a barrier to electrons with the oxide trench, and forms a high-resistance collector short path, suppressing snapback. As the length of the p-float is increased, on-state voltage drop is reduced, and snapback is reduced (can be removed). Structure of p-plug on top of oxide trench improves current distribution increasing reliability (reduced likelihood of hotspots). | Increasing the length of p-float increases turn-off losses. Structure of p-plug on top of oxide trench suffers from snapback characteristics. Fabrication of structures are complex and costly due to the requirement for backside photolithography, and nonuniform current distribution in both conduction modes. Device has not been manufactured.                                                                           |

| Alternating<br>Buffer (AB) RC-<br>IGBT [32]                                 | The floating p buffer implants act as an electron barrier which, with certain geometry, eliminates snapback. Increasing both the width and length of the p buffer implant suppresses snapback. Snapback is suppressed for a much narrower device width compared to both the conventional RC-IGBT and the RC-IGBT with floating p-region. 20% reduction in switching losses compared to a conventional RC-IGBT.                                                                                                                          | Base punch through of the parasitic pnp transistor (p+ collector/n-drift/p buffer) reduces blocking capacity of the device. Increasing the width of the p buffer implant increases switching losses. Increasing the length of the p buffer reduces injection efficiency and increases IGBT on-state losses. Device has not been manufactured.                                                                                  |

| RC-IGBT with double gate structure [10], [33]                               | Device has structural symmetry in the forward and reverse direction and inherently has a reverse conduction path to serve as a FWD. Turn-off loss minimised when operating in quasi-IGBT and MOSFET mode. Automatically-Controlled Gate RC-IGBT (AC-RC-IGBT) shorts the second gate to the n-buffer region such that only single gate control is required. No snapback occurs and structure can be modified to trigger MCT for higher currents. Device has been manufactured.                                                           | Complicated gate drive requirements as device has 2 gates and 4 modes of operation. [IGBT (single gate positive), Quasi-IGBT (both gates positive), MOSFET (current lower than a threshold), Blocking mode]. Transition from quasi-IGBT to MOSFET exhibits snapback. AC-RC-IGBT has higher on-state resistance compared to RC-IGBT, suffers from localised hotspots and in MCT mode snapback occurs in reverse characteristic. |

| Tunnelling<br>IGBT<br>[19]                                                  | Reverse conduction achieved by electrons tunnelling from p-collector to n-tunnel. Snapback can be suppressed by increasing the doping of p-collector and n-tunnel. Exhibits soft turn-off characteristics with small reverse recovery and minimal voltage overshoot. Fabrication does not require backside photolithography or need to account for nonuniform current distribution.                                                                                                                                                     | Trade-off between snapback characteristics and diode mode conduction losses. Relatively long current tail in the turn-off making it unsuitable for high frequency applications. Difficult to manufacture a very thin tunnel layer with such high doping. Device has not been manufactured.                                                                                                                                     |

| BIGT (Bi-mode<br>Integrated Gate<br>Transistor)<br>[6], [16], [38],<br>[39] | Pilot IGBT sized to reduce snapback, with radial layout of anode shorts removing secondary snapback in the on-state. Turn-off losses minimised when operating in quasi-IGBT and MOSFET mode. Suitable for paralleling multiple devices as there is a strong positive temperature coefficient. Soft turn-off behaviour in both conduction modes. Reduced temperature ripple for same area of silicon compared to a separate IGBT/diode. Device has been manufactured.                                                                    | Radial layout of anode shorts presents a trade-off between conduction losses in the IGBT and diode mode. Optimising trade-off in reverse recovery losses and on-state in IGBT mode worsens the performance of the device under surge and increases conduction losses which limits device capability at low frequencies. Complex gate drive schemes are required to optimise switching and on-state performance.                |

| RC-IGBT with<br>superjunction<br>structure<br>[40]                          | Trench Field Stop (TFS) Superjunction (SJ) RC IGBT removes snapback using superjunction structure at cathode. Anode short provides reverse conduction path. Increasing doping concentration of pillars reduces on-state losses for a given breakdown voltage. Increasing length of p-pillar (Ymid) reduces snapback (can be eliminated). Diode characteristic unaffected by superjunction structure.                                                                                                                                    | For a structure comparable with commercially available COOLMOS, snapback is present in the waveform. Increasing length of p-pillar (Ymid) can increase switching losses due to an oscillatory gate voltage. Increasing doping concentration of pillars increases turn-off time. Device has not been manufactured, but an SJ SPT IGBT has been reported [41].                                                                   |

| Schottky<br>Controlled<br>Diode within<br>RC-IGBT [43]                      | Peak diode reverse recovery current was reduced by 49% compared to a conventional RC-IGBT. Reduced tail current in transient waveforms.                                                                                                                                                                                                                                                                                                                                                                                                 | Increased ringing in the diode reverse recovery waveforms. The study did not comment on the overall performance of the RC-IGBT, particularly in reference to the behaviour in IGBT mode. Device has not been manufactured.                                                                                                                                                                                                     |

Fig. 18. Simulated on-state forward and reverse conducting characteristics for RC-IGBT concepts

lateral resistance along the p+ collector is increased, but this further increases reverse conduction losses, rendering the diode portion of the device unsuitable for use within typical application circuits. The AB structure replaces the traditional SPT buffer layer, and the design of this AB layer also needs to be optimised for the breakdown capability of the device. The complex requirements of this device make the design and fabrication challenging.

For SJ RC-IGBT, p-pillars were implanted under the gate trenches to emulate a more realistic fabrication. For increasing pillar depth, a reduction in the snapback occurs, with no effect on the reverse conduction performance as reported in [5], [40]. For the 1.7kV IGBT cell, the snapback could not be removed in its entirety due to the buffer design which limited the maximum pillar length to 87.5% of the total device thickness. The original study in [5] reported elimination of the snapback but, to achieve this, had a buffer design which enabled the superjunction pillars to extend to 97.3% of the total device thickness. The buffer design is therefore critical to the performance of the SJ RC-IGBT, however the length of the required SJ pillars means that at present, this device would be difficult to fabricate.

#### IX. CONCLUSION

This paper presents a review of the recent advancements of the RC-IGBT structure, outlining new concepts developed to overcome some of the technical design challenges of the traditional device. The RC-IGBT features an anti-parallel diode integrated within the same chip area which, at a module level, reduces the bill of materials, is a more compact design and ultimately has a lower cost. The first RC-IGBT structure introduced collector shorts, but optimisation of this implantation to give a good trade-off between the forward snapback and the reverse conducting characteristics is extremely challenging. The introduction of a pilot IGBT has been one of the most pragmatic solutions to solve the snapback issue, whist still offering good reverse characteristics. Double gate structures have been hampered by the complicated gate drive requirements which have prevented their widespread use. Other solutions such as the trench oxide barriers, tunnelling devices, and complex buffer structures have also been proposed but at present have only been validated through simulations.

Such structures may be too complex to be practical as they require advanced back-side processing of the silicon wafers. The SJ RC-IGBT concept also suffers with processing issues as the superjunction structure needs to extend deep into the drift region to give favourable trade-off characteristics. Nevertheless, it is one of the most promising solutions as it alleviates the snap-back issue whilst also offering low switching losses both during forward and reverse recovery. Another promising concept to alleviate the snapback is to use a thyristor with very low breakover voltage instead of an antiparallel diode. Whilst this eliminates the snapback in the forward mode it introduces a snapback in the reverse conduction mode which is difficult to control.

Despite these advancements, the RC-IGBT still has dynamic limitations particularly for high power applications, as there are conflicting requirements for the diode and IGBT in terms of their plasma distribution at the collector: high plasma concentration at the top of the drift region (p-well) reduces the on-state losses in IGBT mode, but to minimise the reverse recovery losses and prevent EMC issues, a low plasma concentration is required during diode mode. The snappy behaviour of the diode can be controlled by a low circuit stray inductance or by reducing the IGBT turn on di/dt, but this increases the IGBT turn on losses. Local lifetime killing in the diode regions can improve performance, but for electron irradiation it is difficult to mask and therefore degrades the performance of adjacent IGBT cells. Separate diode and IGBT chips allow optimisation of each device independently, but the RC-IGBT offers improved utilisation of silicon area. The RC-IGBT may also have an advantage in terms of the IGBT leakage current; the leakage current amplification due to the pnp transistor gain is smaller as a result of the presence of anode shorts. This can result in lower off-state losses especially at high junction temperatures. No single solution to optimise all the static and dynamic trade-offs has emerged for the RC-IGBT but it is an active area of current research.

#### REFERENCES

- B. J. Baliga, "Enhancement and depletion-mode vertical-channel M.O.S. gated thyristors," *Electron. Lett.*, vol. 15, no. 20, pp. 645–647, 1979.

- [2] B. J. Baliga, "The IGBT Compendium: Applications and Social Impact."

- [3] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics: Convertors, Applications and Design*, Third Edit. USA: John Wiley & Sons, Inc., 2003.

- [4] M. Rahimo, "Future trends in high-power bipolar metal-oxide semi-conductor controlled power semi-conductors," *IET Circuits, Devices Syst.*, vol. 8, no. 3, pp. 155–167, 2014.

- [5] M. Antoniou, F. Udrea, F. Bauer, and I. Nistor, "A new way to alleviate the RC IGBT snapback phenomenon: The Super Junction Solution," in 22nd International Symposium on Power Semiconductor Devices & ICs (ISPSD), 2010, pp. 153–156.

- [6] L. Storasta, A. Kopta, M. Rahimo, C. Papadopoulos, S. Geissmann, and R. Schnell, "The next generation 6500V BIGT HiPak modules," in PCIM Europe, 2013, pp. 337–344.

- [7] J. Won, J. G. Koo, T. Rhee, H.-S. Oh, and J. H. Lee, "Reverse-conducting IGBT using MEMS technology on the wafer back side," *Electron. Telecommun. Res. Inst. J.*, vol. 35, no. 4, pp. 603–609, 2013.

- [8] T. P. Chow, B. J. Baliga, H. R. Chang, P. V. Gray, W. Hennessy, and C. E. Logan, "P-channel, vertical insulated gate bipolar transistors with collector short," in 1987 International Electron Devices Meeting (IEDM), 1987, pp. 670–673.

- [9] D. Ueda, K. Kitamura, H. Takagi, and G. Kano, "A New Injection

Supression Structure for Conductivity Modulated Power MOSFETs," in 18th International Conference on Solid State Devices and Materials, 1986, pp. 97–100.

- [10] L. Zhu and X. Chen, "An investigation of a novel snapback-free reverse-conducting IGBT and with dual gates," *IEEE Trans. Electron Devices*, vol. 59, no. 11, pp. 3048–3053, 2012.

- [11] S. Voss, F. J. Niedernostheide, and H. J. Schulze, "Anode design variation in 1200-V trench field-stop reverse-conducting IGBTs," in 20th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2008, pp. 169–172.

- [12] M. Rahimo and L. Storasta, "Optimization and advantages of the Bimode insulated gate transistor," *Facta Univ. Ser. Electron. Energ.*, vol. 28, no. 3, pp. 383–391, 2015.

- [13] A. P. S. Hsieh et al., "Field-stop layer optimization for 1200V FS IGBT operating at 200°C," Proc. Int. Symp. Power Semicond. Devices ICs, pp. 115–118, 2014.

- [14] W. C. Hsu, F. Udrea, H. Hsu, and W. Lin, "Reverse-conducting Insulated Gate Bipolar Transistor with an Anti-parallel Thyristor," in 22nd International Symposium on Power Semiconductor Devices & ICs (ISPSD), 2010, pp. 149–152.

- [15] U. Vemulapati, N. Kaminski, D. Silber, L. Storasta, and M. Rahimo, "Reverse conducting-IGBTs initial snapback phenomenon and its analytical modelling," *IET Circuits, Devices Syst.*, vol. 8, no. 3, pp. 168– 175, 2014.

- [16] M. Rahimo, A. Kopta, U. Schlapbach, J. Vobecky, R. Schnell, and S. Klaka, "The Bi-mode Insulated Gate Transistor (BIGT) a potential technology for higher power applications," in 21st International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2009, pp. 283–286.

- [17] M. Rahimo, U. Schlapbach, A. Kopta, J. Vobecky, D. Schneider, and A. Baschnagel, "A high current 3300V module employing reverse conducting IGBTs setting a new benchmark in output power capability," 20th International Symposium on Power Semiconductor Devices and ICs (ISPSD). Orlando, FL, pp. 68–71, 2008.

- [18] W. Chen et al., "A high reliable reverse-conducting IGBT with a floating P-plug," in 25th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2013, pp. 265–268.

- [19] H. Jiang, J. Wei, B. Zhang, W. Chen, M. Qiao, and Z. Li, "Band-to-band tunneling injection insulated-gate bipolar transistor with a soft reverserecovery built-in diode," *IEEE Electron Device Lett.*, vol. 33, no. 12, pp. 1684–1686, 2012.

- [20] D. Werber et al., "A 1000A 6.5kV Power Module Enabled by Reverse Conducting Trench-IGBT-Technology," in PCIM Asia, 2016, pp. 269– 276

- [21] D. Domes, "Control Method for a Reverse Conducting IGBT," in PCIM Europe, 2015, no. May, pp. 147–154.

- [22] H. Jiang, B. Zhang, W. Chen, C. Liu, Z. Rao, and B. Dong, "A snapback suppressed reverse conducting IGBT with oxide with a floating p-region in trench collector," *IEEE Electron Device Lett.*, vol. 33, no. 3, pp. 417– 419, 2012.

- [23] W. Zhang, Y. Zhu, S. Lu, X. Tian, and Y. Teng, "Increase of the reliability of the junction terminations of reverse-conducting insulated gate bipolar transistor by appropriate backside layout design," *IEEE Electron Device Lett.*, vol. 35, no. 12, pp. 1281–1283, 2014.

- [24] T. Yoshida, T. Takahashi, K. Suzuki, and M. Tarutani, "The second-generation 600V RC-IGBT with optimized FWD," in 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 159–162.

- [25] D. Kumar, M. Sweet, K. Vershinin, L. Ngwendson, and E. M. . Narayanan, "RC-TCIGBT: A Reverse Conducting Trench Clustered IGBT," in 19th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2007, pp. 161–164.

- [26] A. Lale, A. Bourennane, and F. Richardeau, "RC-IGBT-thyristor structure having trenches filled with dielectric on the backside: Physical analysis and application to the integration of a multiphase generic power converter using the 'two-chip' approach," in 17th European Conference on Power Electronics and Applications (EPE'15 ECCE Europe), 2015.

- [27] L. Zhu and X. Chen, "A novel snapback-free reverse conducting IGBT with anti-parallel Shockley diode," in 25th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2013, pp. 261–264.

- [28] Z. Lin, X. Chen, and B. Yi, "Snapback-free reverse-conducting IGBT with low turnoff loss," *Electron. Lett.*, vol. 50, no. 9, pp. 703–705, 2014.

- [29] M. Mori, Y. Uchino, J. Sakano, and H. Kobayashi, "A novel high-conductivity IGBT (HiGT) with a short circuit capability," in 10th International Symposium on Power Semiconductor Devices and ICs

(ISPSD), 1998, pp. 429-432.

- [30] M. Rahimo, U. Schlapbach, A. Kopta, R. Schnell, and S. Linder, "SPT+, the Next Generation of Low-Loss HV-IGBTs," in *PCIM Europe*, 2005, pp. 1–6.

- [31] B. Jiang, F. X. C. Jiang, Z. Li, and X. Lin, "A reverse conducting IGBT with low on-state voltage and turnoff loss," in 11th International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2012.

- [32] G. Deng et al., "A Snapback-free RC-IGBT with Alternating N/P Buffers," in 29th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2017, pp. 127–130.

- [33] A. Nakagawa, "Numerical experiment for 2500V double gate bipolar-mode MOSFETs (DGIGBT) and analysis for large safe operating area (SOA)," in 19th Annual IEEE Power Electronics Specialists Conference (PESC), 1988, pp. 84–90.

- [34] J. W. Wu *et al.*, "1200V, 25A bi-directional Si DMOS IGBT fabricated with fusion wafer bonding," in *26th International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, 2014, pp. 95–98.

- [35] D. Wang et al., "Applicability of Single-Chip Dual-Gate Bidirectional IGBTs in Matrix Converters," in 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), 2016.

- [36] A. Kopta et al., "Next Generation IGBT and Package Technologies for High Voltage Applications," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 753–759, 2017.

- [37] L. Storasta, M. Rahimo, M. Bellini, A. Kopta, U. R. Vemulapati, and N. Kaminski, "The radial layout design concept for the Bi-mode insulated gate transistor," in 23rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2011, pp. 56–59.

- [38] M. Rahimo, C. Papadopoulos, C. Corvasce, and A. Kopta, "An Advanced Bimode Insulated Gate Transistor BIGT with Low Diode Conduction Losses under a Positive Gate Bias," in 29th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2017, pp. 483–486.

- [39] M. Rahimo, M. Andenna, L. Storasta, C. Corvasce, and A. Kopta, "Demonstration of an Enhanced Trench Bimode Insulated Gate Transistor ET-BIGT," in 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 151–154.

- [40] M. Antoniou, F. Udrea, F. Bauer, and I. Nistor, "The Soft Punchthrough+ Superjunction Insulated Gate Bipolar Transistor: A High Speed Structure With Enhanced Electron Injection," *IEEE Trans. Electron Devices*, vol. 58, no. 3, pp. 769–775, 2011.

- [41] K. H. Oh et al., "Experimental investigation of 650V superjunction IGBTs," in 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 299–302.

- [42] M. Antoniou, F. Udrea, and F. Bauer, "The superjunction insulated gate bipolar transistor optimization and modeling," *IEEE Trans. Electron Devices*, vol. 57, no. 3, pp. 594–600, 2010.

- [43] R. Gejo et al., "High switching speed trench diode for 1200V RC-IGBT based on the concept of Schottky Controlled injection (SC)," in 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 155–158.

- [44] Infineon Technologies, "Reverse Conducting IGBT for Induction Cooking and Resonant Applications," 2014.

Emma M. Findlay received the B.A. and M.Eng. degrees in Electrical and Electronic Engineering in 2015 and the M.A. degree in 2018, all from the University of Cambridge. She is currently pursuing the Ph.D. degree at the University of Cambridge investigating silicon IGBT structure and design.

Florin Udrea (M'91) received the Ph.D. degree in power devices from the University of Cambridge in 1995. He is a Professor in semiconductor engineering and Head of the High Voltage Microelectronics and Sensors Laboratory with the University of Cambridge. He has authored over 400 papers in journals

and international conferences.