University of Warwick institutional repository: http://go.warwick.ac.uk/wrap This paper is made available online in accordance with publisher policies. Please scroll down to view the document itself. Please refer to the repository record for this item and our policy information available from the repository home page for further information.

To see the final version of this paper please visit the publisher's website. Access to the published version may require a subscription.

Author(s): V. A. Shah, A. Dobbie, M. Myronov, D. J. F. Fulgoni, L. J.

Nash, and D. R. Leadley

Article Title: Reverse graded relaxed buffers for high Ge content SiGe

virtual substrates

Year of publication: 2008 Link to published version:

http://dx.doi.org/ 10.1063/1.3023068

Publisher statement: None

## Reverse graded relaxed buffers for high Ge content SiGe virtual substrates

V. A. Shah, <sup>1,a)</sup> A. Dobbie, <sup>1</sup> M. Myronov, <sup>1</sup> D. J. F. Fulgoni, <sup>2</sup> L. J. Nash, <sup>2</sup> and D. R. Leadley <sup>1</sup> Department of Physics, The University of Warwick, Coventry CV4 7AL, United Kingdom <sup>2</sup> AdvanceSis Ltd., Sir William Lyons Road, Coventry CV4 7EZ, United Kingdom

(Received 12 August 2008; accepted 19 October 2008; published online 10 November 2008)

An innovative approach is proposed for epitaxial growth of high Ge content, relaxed  $Si_{1-x}Ge_x$  buffer layers on a Si(001) substrate. The advantages of the technique are demonstrated by growing such structures via chemical vapor deposition and their characterization. Relaxed Ge is first grown on the substrate followed by the reverse grading approach to reach a final buffer composition of 0.78. The optimized buffer structure is only 2.8  $\mu$ m thick and demonstrates a low surface threading dislocation density of  $4 \times 10^6$  cm<sup>-2</sup>, with a surface roughness of 2.6 nm. The buffers demonstrate a relaxation of up to 107%. © 2008 American Institute of Physics. [DOI: 10.1063/1.3023068]

Strained Ge has been shown to offer increased hole mobility and can be realized by epitaxial growth of Ge on a relaxed Si<sub>1-x</sub>Ge<sub>x</sub>/Si(001) substrate with a different lattice constant.<sup>2</sup> These lattice-parameter controlled substrates, known as "virtual substrates" (VSs), are required to provide an interface to the ubiquitous Si wafer and must accommodate the change in lattice parameter without compromising the final layer quality by introducing excessive threading dislocations or surface roughening. Commonly, they consist of relaxed Si<sub>1-x</sub>Ge<sub>x</sub> buffers grown on Si(001) substrate. A high Ge fraction in the range of  $0.6 \le x \le 0.9$  is required to allow a reasonable thickness of compressive strained Ge to be grown without exceeding the critical thickness. These latticeparameter tunable substrates are also of great interest for optoelectronic applications, as they provide a route to integrating existing III-V technologies with Si.

Using reduced pressure chemical vapor deposition (RP-CVD), Si and SiGe epitaxial films can be grown of very high structural quality, often exceeding that obtained using molecular beam epitaxy (MBE). As these buffer structures are relatively thick, growth by solid-source MBE with growth rates of about 0.1 nm/s would be extremely slow whereas rates of 5 nm/s are easily achievable by RP-CVD. An added bonus with RP-CVD is that the residual H<sub>2</sub> gas acts as a surfactant and suppresses surface roughness during growth.

The high quality high Ge content buffers are typically grown by two major techniques by CVD. The first is through a two temperature growth method directly on the Si(001) substrate.<sup>3,4</sup> The second is by a slow grading of a buffer structure, <sup>5,6</sup> which, for such high-composition layers leads to a relatively thick structure, typically  $8-12~\mu m$ , since a Ge grading rate of  $10\%/\mu m$  and a  $1-2~\mu m$  Si<sub>1-x</sub>Ge<sub>x</sub> cap layer have to be grown to obtain a root mean square (rms) surface roughness of 8-15 nm (Refs. 6-8) and threading dislocations density (TDD) in the range  $10^6$  cm<sup>-2</sup> or below. In this work, we introduce an innovative approach to producing high Ge composition Si<sub>1-x</sub>Ge<sub>x</sub> relaxed buffer of relatively small thickness and high quality.

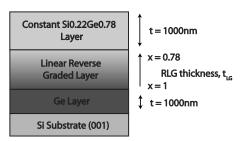

The  $Si_{0.22}Ge_{0.78}/RLG/Ge/Si(001)$  VS design is shown in Fig. 1. The structures were grown by RP-CVD in an ASM Epsilon 2000 reactor with GeH<sub>4</sub> and SiH<sub>2</sub>Cl<sub>2</sub> as gaseous precursors. Initially, a relatively high quality 1  $\mu$ m Ge layer was grown directly on the Si(001) substrate using the two tem-

The unique feature of the proposed VSs is that the alloy content is graded *down* from a relatively high quality, relaxed pure Ge interlayer to the required final composition instead of grading *up* from the Si wafer. As well as producing thinner VSs, the main advantage from having the buffer relax under biaxial tensile strain rather than the compressive strain is that the buffer layers will remain smoother during growth.

To view threading dislocation formation and establish the actual layer thicknesses, cross-sectional transmission electron microscopy (TEM) investigations were performed along the {110} plane using a JEOL 2000FX TEM at 200 kV.

FIG. 1. Schematic design of the reverse linear graded  $\mathrm{Si}_{0.22}Ge_{0.78}/RLG/Ge/Si(001)$  VS.

perature growth method.<sup>3,4</sup> This allows dislocations to nucleate while keeping the roughness to a minimum at the initial lower temperature and then allows the dislocations to glide during the higher temperature phase, the temperatures used were 400 °C for the initial seed layer then 670 °C for the high temperature layer. After this, the reverse linear graded (RLG) layer was deposited at a high growth temperature of 850 °C, with the Ge content reducing linearly from x=1 to x=0.78 over a thickness  $t_{LG}$ , which was varied from 50 to 5000 nm corresponding to a range of effective grading rates between 440%/ $\mu$ m and 4.4%/ $\mu$ m. Finally, a 1.1  $\mu$ m constant composition Si<sub>0.22</sub>Ge<sub>0.78</sub> layer was grown. The grading was achieved by keeping the GeH4 flow constant and reducing the SiH<sub>2</sub>Cl<sub>2</sub> flow. The grading was calibrated in 5% composition steps to account for the increase in growth rate from 1.26 nm/s at pure Ge to 4.74 nm/s at Si<sub>0.2</sub>Ge<sub>0.8</sub>. The linear grading profile was confirmed through high energy secondary ion mass spectroscopy. Alongside these wafers, a pure Ge layer and another without a graded layer were also fabricated as controls. In this letter, we will demonstrate and discuss the results of characterization for the optimum structure with  $t_{LG}$  of 800 nm corresponding to an effective grading rate of  $27.5\% / \mu m$ .

a) Electronic mail: vishal.shah@warwick.ac.uk.

FIG. 2. A cross-sectional TEM image in the (220) diffraction condition. Shown are dislocations confined to the RLG region but not penetrating upwards.

Figure 2 shows how the initial 100 nm Ge seed is riddled with defects, while no defects can be observed in the high temperature Ge layer indicating a TDD below  $10^8 \, \mathrm{cm}^{-2}$ . From a sample of ten such images, the TDD reaching the surface of the Ge layer was estimated to be  $<5 \times 10^7 \, \mathrm{cm}^{-2}$ . Within the reverse graded layer misfit dislocations, needed to relax the top composition layer, are generated. These can be seen to be confined to this graded layer, as with linear "forward graded" structures. Due to the tensile strain imposed on the graded region by the Ge layer, microtwins are initially formed in the graded layer and extend down into the Ge layer. Finally, the constant composition  $\mathrm{Si}_{0.22}\mathrm{Ge}_{0.78}$  layer is seen to be  $1.1 \, \mu\mathrm{m}$  thick, again with very few defects.

The TDD reaching the top surface was measured through selective etching and viewing any etch pits formed with a differential interference contrast microscope. To reveal threading dislocations in the Si<sub>0.22</sub>Ge<sub>0.78</sub> top layer alloy, a dilute Schimmel etchant was used, fo with a bulk etching rate of 2.1 nm/s determined for 78% Ge. The TDD was obtained from the average of 30 images each with an area of  $8.2 \times 10^3 \ \mu \text{m}^2$ . After a 5 min Schimmel etch, a defect level of  $(4.2 \pm 0.1) \times 10^6$  cm<sup>-2</sup> was measured. No dislocation pileup or stacking fault formation was seen, although a cross-hatch pattern is observed on the surface of the sample both before and after etching. This cross-hatch pattern is typical of graded structures due to the strain field generated by misfit dislocation running in orthogonal directions during growth of the graded layer. <sup>11</sup> A separate wafer was grown to evaluate the density of defects within the Ge base layer. Since the reactivity of Schimmel etchant decreases as the Ge fraction increases and it has virtually no effect on pure Ge, a dilute iodine etchant<sup>12</sup> was used. After a 15 s iodine etch, a TDD of  $\sim 2 \times 10^7$  cm<sup>-2</sup> was found, consistent with the defect level found from TEM.

Having confirmed these low defect levels, the surface rms roughness was assessed from an average of eight 10  $\times$  10  $\mu m^2$  scans measured by a Veeco Nanoscope contact mode atomic force microscope (AFM). An average rms value of 2.6  $\pm$  0.3 nm was found, with a maximum height range of 16.3  $\pm$  2.2 nm. The cross-hatch pattern can now be resolved in more detail and was determined to have an average wavelength of 1.5  $\pm$  0.2  $\mu$ m. This is seen to be the main mechanism for roughening of the layers.

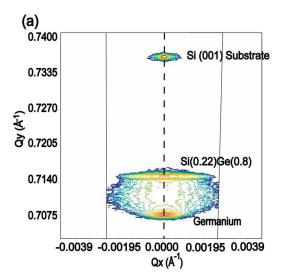

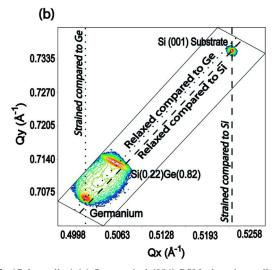

FIG. 3. (Color online) (a) Symmetrical (004) RSM, there is no tilt of the layers. (b) Asymmetrical (224) RSM, full relaxation of layers.

The relaxation and composition of the layers was determined by x-ray diffraction using a Philips X'pert MRD Pro single crystal high resolution x-ray diffractometer. Reciprocal space maps (RSMs) were performed along the symmetrical (004) and asymmetrical (224) orientations, which allowed the in-plane and out-of-plane lattice parameters to be calculated. The alignment of the peaks in the (004) scan [Fig. 3(a) shows that there is minimal tilt to the epitaxial layers. As there are two different constant composition layers, the underlying relaxation of the Ge layer will influence the relaxation of the top alloy layer. The Ge layer is measured to be 104.2% relaxed compared to the Si(001) substrate. The slight tensile strain incurred in the layer has been calculated to result from the difference in thermal contraction of both materials as they cool from the growth temperature. This is represented in Fig. 3 by a deviation from the diagonal dashed line that represents the full relaxation of a layer compared to the Si substrate, whereas a fully pseudomorphic, and hence compressively strained, layer is represented by the vertical dashed line. The relaxation of the Si<sub>0.22</sub>Ge<sub>0.78</sub> layer was measured to be  $107.3\% \pm 0.2\%$  relative to the Si substrate. The relaxation of the Si<sub>0.22</sub>Ge<sub>0.78</sub> layer can also be compared to the underlying Ge layer. Within Fig. 3, the diagonal dotted line shows complete relaxation compared to the Ge layer and the vertical dotted line shows 100% strain. A relaxation of  $85.8\% \pm 0.2\%$  was calculated for the Si<sub>0.22</sub>Ge<sub>0.78</sub> layer compared to the Ge layer. After annealing for 10 h at 750 °C, the relaxation increases slightly to  $88.7\% \pm 0.1\%$  and  $106.1\% \pm 0.1\%$ , relative to Ge and Si, respectively. Again differential thermal contraction is responsible for a small compressive strain, which partially explains why the layer is not fully relaxed. As can be seen in both the (004) and the (224), a spreading of the peaks from the epitaxial layers is observed. This is due to the periodic strain field, which arises from small monocrystalline blocks formed from the crossing of misfit dislocations, termed "mosaicity." During growth, this mosaicity forms the undulations which are more commonly know as crosshatch.

These RLG buffers can be compared to conventional CVD grown linear graded buffers with no intermediate steps where a TDD is reported in the range  $10^6-10^7$  cm<sup>-2</sup> for structures having an overall buffer thickness of over  $8 \mu \text{m.}^{6,13}$  When chemical mechanical polishing (CMP) is employed within a forward graded structure TDD values of 10<sup>5</sup> cm<sup>-2</sup> are reported. If a thick constant composition layer is deposited instead of grading of any kind, a TDD of 10<sup>8</sup> cm<sup>-2</sup> will arise.<sup>5</sup> We have found that a grading rate of  $31\%/\mu m$  can be used to obtain well relaxed, low TDD, and smooth buffers. The optimum structures, with a total thickness of just 2.8 µm above the Si wafer, have a high degree of relaxation and a relatively low TDD of  $(4.2 \pm 0.1)$  $\times 10^6$  cm<sup>-2</sup>. Buffers grown by forward grading from Si have been shown to use an optimal grading rate, which is slower, typically  $10\% / \mu m$ , and make a much greater change in lattice parameter, hence they are much thicker, relieve more strain energy, and have a comparable TDD of around 10<sup>6</sup> cm<sup>-2</sup>. The low grading rate is required to limit nucleation of dislocations and ensure that relaxation occurs through the glide of dislocations. Isaacson et al. 14 suggest the dislocation nucleation regime is partly temperature limited; however, in our RLG buffers, there is already a reasonably high dislocation content at the top of the Ge layer and, as the energy for dislocation glide is lower than the energy of dislocation nucleation, we suggest that dislocation glide is the main mechanism for strain relief in the reverse graded layer. As glide dominates, rather than nucleation, we speculate the higher growth temperatures can be used that suppress further dislocation nucleation, which reduces the strain field associated with dislocations, resulting in reduced surface roughening. Further evidence for the importance of dislocation glide in the graded region is that the TDD reaching the top Si<sub>0.22</sub>Ge<sub>0.78</sub> surface is much lower than that at the Ge surface; however, further reduction of the final TDD is still limited by the number of threading dislocations in the underlying Ge layer. The higher growth temperature along with the fact that under tensile strain a smoother surface is achieved avoids the vicious cycle<sup>6</sup> of surface morphology affecting dislocation glide, producing pileup, which in turn reduces the local growth rate around arrested dislocations and creates a rougher surface. Most importantly, the rms surface roughness in the RLG buffers, of  $2.6 \pm 0.3$  nm is at least a factor of 6 lower than in previous works. <sup>6,7</sup> In an attempt to produce smoother layers, Bogumilowicz et al.<sup>8</sup> employed a midgrowth CMP step after linearly grading to 50% Ge. After CMP, the rms roughness was 0.4 nm, but continued growth to 75% Ge again increased the roughness to 15 nm. Thus the RLG buffers are shown to be comparable in terms of full relaxation of the layer and relatively low TDD, but considerably thinner and much better in terms of surface morphology compared to conventional forward graded substrates.  $^{5,6,13}$

Reverse grading has previously been exploited on low composition structures to produce thin buffers with low TDD. 15,16 In that case, there was no relaxed underlayer and the abrupt step to higher Ge content was used to nucleate misfit dislocations at the interface to the Si substrate. Residual strain in the reverse grading region was thought to act as threading dislocation filters. 16 By contrast, the technique outlined here uniquely incorporates a high-quality fully relaxed Ge layer underneath the RLG region and enables high Ge composition buffers to be developed.

In summary, an innovative approach to grading for highcomposition  $Si_{1-x}Ge_x/Si(001)$  VSs has been proposed. The structures were grown using RP-CVD and a range of characterization techniques have been applied. A high degree of relaxation was obtained with a comparatively low TDD of  $4.2 \times 10^6$  cm<sup>-2</sup>, compared to forward graded structures typically with TDDs of  $10^6-10^8$  cm<sup>-2</sup>. The higher grading rate of 27.5%/µm resulted in a much thinner structure of 2.8  $\mu$ m when compared to similar structures of over 8  $\mu$ m. Finally a surface rms roughness of 2.6 nm has been achieved, six times lower than traditional forward grading. These encouraging results show the potential of using reverse grading as part of the platform for strained Ge layers. The technique could similarly be applied to produce VSs for highly strained silicon, or SiGe, by varying the initial seed layer.

<sup>&</sup>lt;sup>1</sup>M. Myronov, K. Sawano, Y. Shiraki, T. Mouri, and K. M. Itoh, Appl. Phys. Lett. 91, 082108 (2007).

<sup>&</sup>lt;sup>2</sup>D. J. Paul, Semicond. Sci. Technol. **19**, R75 (2004).

<sup>&</sup>lt;sup>3</sup>S. Akira, S. Ken, Y. Takeo, O. Masahisa, I. Hiroya, Y. Yukio, and Z. Shigeaki, Appl. Phys. Lett. 79, 3398 (2001).

<sup>&</sup>lt;sup>4</sup>J. M. Hartmann, A. Abbadie, A. M. Papon, P. Holliger, G. Rolland, T. Billon, J. M. Fedeli, M. Rouviere, L. Vivien, and S. Laval, J. Appl. Phys. **95**, 5905 (2004).

<sup>&</sup>lt;sup>5</sup>E. A. Fitzgerald, Y. H. Xie, D. Monroe, P. J. Silverman, J. M. Kuo, A. R. Kortan, F. A. Thiel, and B. E. Weir, J. Vac. Sci. Technol. B 10, 1807 (1992).

<sup>&</sup>lt;sup>6</sup>S. B. Samavedam and E. A. Fitzgerald, J. Appl. Phys. **81**, 3108 (1997). <sup>7</sup>K. Hans von, K. Matthias, I. Giovanni, M. Elisabeth, and H. Thomas, Appl. Phys. Lett. 80, 2922 (2002).

<sup>&</sup>lt;sup>8</sup>Y. Bogumilowicz, J. M. Hartmann, C. Di Nardo, P. Holliger, A. M. Papon, G. Rolland, and T. Billon, J. Cryst. Growth 290, 523 (2006).

<sup>&</sup>lt;sup>9</sup>Y. H. Xie, G. H. Gilmer, C. Roland, P. J. Silverman, S. K. Buratto, J. Y. Cheng, E. A. Fitzgerald, A. R. Kortan, S. Schuppler, M. A. Marcus, and P. H. Citrin, Phys. Rev. Lett. 73, 3006 (1994).

<sup>&</sup>lt;sup>10</sup>J. L. Liu, C. D. Moore, G. D. U'Ren, Y. H. Luo, Y. Lu, G. Jin, S. G. Thomas, M. S. Goorsky, and K. L. Wang, Appl. Phys. Lett. 75, 1586 (1999)

<sup>&</sup>lt;sup>11</sup>J. W. P. Hsu, E. A. Fitzgerald, Y. H. Xie, P. J. Silverman, and M. J. Cardillo, Appl. Phys. Lett. 61, 1293 (1992).

<sup>&</sup>lt;sup>12</sup>D. P. Malta, J. B. Posthill, R. J. Markunas, and T. P. Humphreys, Appl. Phys. Lett. 60, 844 (1992).

<sup>&</sup>lt;sup>13</sup>M. T. Currie, S. B. Samavedam, T. A. Langdo, C. W. Leitz, and E. A. Fitzgerald, Appl. Phys. Lett. 72, 1718 (1998).

<sup>&</sup>lt;sup>14</sup>D. M. Isaacson, C. L. Dohrman, and E. A. Fitzgerald, J. Vac. Sci. Technol. **B** 24, 2741 (2006).

<sup>&</sup>lt;sup>15</sup>L. H. Wong, J. P. Liu, F. Romanato, C. C. Wong, and Y. L. Foo, Appl. Phys. Lett. 90, 061913 (2007).

<sup>&</sup>lt;sup>16</sup>J. P. Liu, L. H. Wong, D. K. Sohn, L. C. Hsia, L. Chan, C. C. Wong, and H. J. Osten, Electrochem. Solid-State Lett. 8, G60 (2005).