# Review Article Review of Ni-Cu Based Front Side Metallization for c-Si Solar Cells

# Mehul C. Raval and Chetan S. Solanki

Solar Lab, Department of Energy Science and Engineering, National Center for Photovoltaic Research and Education (NCPRE), Indian Institute of Technology Bombay, Powai, Mumbai 400076, India

Correspondence should be addressed to Mehul C. Raval; mehul.c.raval@iitb.ac.in

Received 10 April 2013; Revised 12 September 2013; Accepted 24 September 2013

Academic Editor: Haricharan S. Reehal

Copyright © 2013 M. C. Raval and C. S. Solanki. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Given the high percentage of metal cost in cell processing and concerns due to increasing Ag prices, alternative metallization schemes are being considered. Ni-Cu based front side metallization offers potential advantages of finer grid lines, lower series resistance, and reduced costs. A brief overview of various front side patterning techniques is presented. Subsequently, working principle of various plating techniques is discussed. For electroless plated Ni seed layer, fill factor values nearing 80% and efficiencies close to 17.5% have been demonstrated, while for Light Induced Plating deposited layers, an efficiency of 19.2% has been reported. Various methods for qualifying adhesion and long term stability of metal stack are discussed. Adhesion strengths in the range of 1–2.7 N/mm have been obtained for Ni-Cu contacts tabbed with conventional soldering process. Given the significance of metallization along with the various methods for characterization are outlined. The problem of background plating for Ni-Cu based metallization indicates process cost saving of more than 50% with Ni-Cu-Sn based layers. Recent successful commercialization and demonstration of Ni-Cu based metallization on industrial scale indicate a potential major role of Ni-Cu based contacts in near future.

### 1. Introduction

The present solar PV market is growing at a rate of 35-40% per year and is one of the important renewable energy sources for non-CO<sub>2</sub> energy in the future [1]. The rapid decline in the cost per watt has promoted increased deployment, hence nearing the tipping point of grid parity. Given the improving efficiencies of leading technologies, the focus should be to reduce the cost of various system components from wafer to balance of system components [1]. The cell processing typically contributes around 16-17% of the total system cost [2], while the contribution of metallization to the cell processing is around 40% due to the expensive Ag paste [3]. As shown in (1a), the mass of Ag required in the front grid is inversely proportional to the acceptable fractional resistive losses due to front side metallization, irrespective of the finger design [4]. Equation (1a) is obtained from (1b), where  $J_{\rm mp}$  is substituted in terms of  $p_{\rm rf}$  from (1c) [4]. Hence the amount of Ag required will double for decrease in acceptable resistive

losses by 50%. In addition, due to presence of voids and additional constituents in screen-printed Ag contacts, typical  $d_{\rm rel}\rho_{\rm rel}$  product value is around 1.875, which further increases the amount of Ag required by more than 80% as compared to pure Ag to meet the resistive loss criteria [4]. A report in 2011 [5] indicates that the prices of Ag may rise further, thus putting more pressure on the manufacturers to reduce paste consumption or pursue alternative routes to reduce the costs:

$$\frac{m_{\rm Ag}}{W} = 20.7 \frac{d_{\rm rel} \rho_{\rm rel} B^2}{p_{\rm rf}} \,\mu g/W, \tag{1a}$$

where,  $m_{Ag}$  is the mass of Ag paste deposited on front side of solar cell in  $\mu g$ , W= per watt of power generated from solar cell,  $d_{rel}$  and  $\rho_{rel}$  are the relative density and resistivity of fired Ag pastes compared to bulk Ag, *B* is the length of finger per unit cell, and  $p_{rf}$  is the Fractional resistive loss due to front side metallization. One has

$$\frac{m_{\rm Ag}}{W} = \frac{d_{\rm Ag}t_F W_F}{SJ_{\rm mp}V_{\rm mp}},\tag{1b}$$

where  $d_{Ag}$  is mass density of Ag (10.5 gm/cc for pure Ag),  $t_F$  is the thickness of finger,  $W_F$  is the width of finger, S is the finger spacing,  $J_{mp}$  and  $V_{mp}$  is the maximum power point current density and voltage.

One has

$$p_{\rm rf} = \frac{\rho_{\rm Ag} B^2 S J_{\rm mp}}{3 t_F W_F V_{\rm mp}},\tag{1c}$$

where  $\rho_{Ag}$  is resistivity of Ag (1.6  $\mu\Omega$ -cm for pure Ag),

Screen printed contacts have been the standard technology for metallization in solar cell manufacturing. The process simplicity and cofiring of the front and back contacts reduces the number of processing steps and hence leads to high throughput production of cells with efficiencies nearing 19% for mono- c-Si solar cells. The smallest finger width that has been achieved is around  $80 \,\mu\text{m}$ , which is limited by the type of mesh, emulsion layer, and the wire diameter of the screen [6]. For good screen-printed contacts, the fill factor (FF) is in the range of 76-78%. FF of 81-82% can be obtained with metallization based on photolithography [2] and hence there is considerable scope of improvement for the screen-printed contacts. Similarly, best values of other vital parameters, that is, aspect ratio, contact resistivity,  $(\rho_c)$ and line resistivity that have been obtained are around 0.22, 1.45 m $\Omega$ -cm<sup>2</sup>, and 2.55  $\mu\Omega$ -cm, respectively [7]. The line resistivity is much higher than the value of bulk resistivity, of Ag which is 1.63  $\mu\Omega$ -cm. The presence of glass frit in the Ag paste to penetrate the ARC during firing process results in an additional glass phase to be introduced between Ag and Si interface which increases the  $\rho_c$  [8]. Voids present in the grid lines also increase the line resistance and hence the series resistance  $(R_s)$  [8]. For finger widths of 80  $\mu$ m, the shading losses can be as high as 6.92% [6].

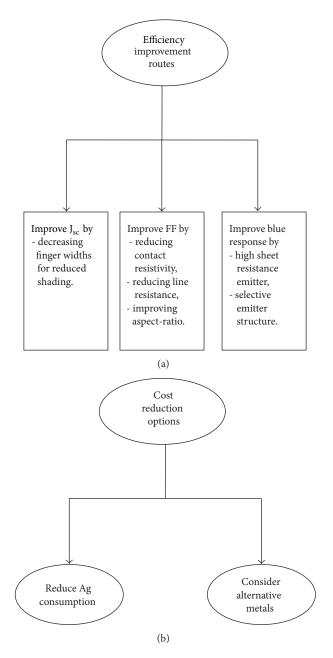

Efficiency and cost improvements based on metallization are possible by various routes as shown in Figure 1. Improvement in current density and FF can be achieved by reducing the shading losses and line resistance of screen printed contacts by double printing of finer lines down to  $30 \,\mu\text{m}$  [6]. Aspect ratio of as high as 0.44 has been achieved with double printed contacts [7] and these improvements can push the efficiency towards 19%. Given the improvements offered by double printing, the requirement of maintaining alignment accuracy for high throughput production is a critical factor. Improvement in economic aspect is feasible by reducing the metal paste consumption to reduce the cost per watt. Another possibility is to consider alternative material with reduced cost and equivalent or better achievable metallization properties. Also since the screen-printing process exerts certain pressure on the wafer during printing, the factor becomes more important as the technology moves to thinner substrates.

Given the limitations of screen-printed contacts and possibility of considering alternative metal for front side

FIGURE 1: Possible methods for efficiency and cost improvement by altering metallization properties.

metallization, many groups have demonstrated cells based on Ni-Cu front side metallization with improved FF's and efficiencies compared to conventional cells [9, 10]. Table 1 shows the comparison of cost and conductivity for Ag, Cu, and Ni. It can be seen that though the reduction in conductivity of Cu is only 3.7%, the cost reduction is nearly hundred times [11]. This can prove to be an important factor for cost reduction compared to the current technology. Also Cu is widely used in Si ULSI due to its low resistivity and good resistance to electromigration [12] and hence has a proven track record in the microelectronics industry. Since Cu can easily move through Si and can act as deep level impurity, it

TABLE 1: Comparison of metal properties and costs.

| Parameters                         | Ag    | Cu    | Ni   |

|------------------------------------|-------|-------|------|

| Conductivity (10 <sup>6</sup> S/m) | 61.39 | 59.1  | 13.9 |

| Density (gm/cm <sup>3</sup> )      | 10.49 | 8.92  | 8.9  |

| Cost (\$/troy oz) in April, 2013   | 27.26 | 0.231 | 0.50 |

can form traps which reduce the carrier life time. Also if it diffuses near the junction, it can increase the leakage current [12]. To prevent the diffusion of Cu in Si, Ni can be used as an effective barrier layer.

Also formation of Ni silicide at the interface reduces the contact resistance which will ensure minimum power loss due to  $R_{s}$ .

Earliest use of Ni plating for metallization can be traced back to 1959 when M. Wolf first proposed use of electroless plated Ni grid lines to reduce  $R_s$  of early c-Si solar cells [13]. All plated contacts with a stack of Pd-Ni-Cu and electroless Ni/solder contacts with good adhesion and reliability were demonstrated in 1980 [14, 15]. An alternative electroless Ni bath with low bath temperatures and without phosphorus incorporation in deposited Ni was reported to form ohmic contacts for solar cells [16]. Later during early 1980s, work on screen-printable Ni or Ni-Cu contacts with low sintering temperatures, low contact resistance, and good adhesion properties was reported [17, 18], though concerns related to metal diffusion in Si and requirement of additional layer for providing solderability persisted [19]. Interdigitated back contact solar cells commercialized by SunPower Corporation incorporated metallization scheme of patterned Al followed by plated Ni-Cu-Ag which was then annealed to complete contact formation [2]. Currently SunPower cells hold the world record of efficiencies up to 24% [20]. Ni-Cu based laser grooved buried contacts (LGBC) technology was licensed by BP Solar from University of New South Wales in 1985, followed by pilot line development and demonstration of 17.5% average production efficiencies in 1991 [21, 22]. Later efforts to improve the LGBC cells were to replace the thin Al film with laser fired contacts on the rear side [2].

# 2. Promise and Commercial Aspects of Ni-Cu Based Metallization

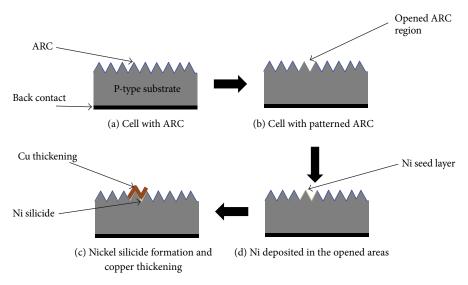

Various reported works show a lot of promise for Ni-Cu based metallization, but at the same time there are challenges to optimize and simplify the process flow so that it can compete with the current screen-printing technology in terms of reliability, cost competitiveness, and high throughput production. A generic flow for Ni-Cu based metallization is shown in Figure 2. As can be observed one of the important steps involved in Ni-Cu based metallization is the need for selectively opening the front ARC to make contact with the underlying emitter. The variety of methods available for patterning the ARC along with different techniques for metal deposition presents a unique challenge to come up with a standardized method that can be commercialized with minimum additional processing steps. In addition, To analyze the commercial potential of Ni-Cu based metallization for solar cells, it is vital to obtain detailed technical insights into the various process steps. Given the simplicity of the plating process, various factors from patterning the front ARC to optimizing the bath and contact formation need to be well analyzed and evaluated. In the current work, a brief overview of the different methods for patterning the ARC is presented. Working principle of the different metal deposition techniques which have been reported till date is also discussed. Influence of deposited metal thickness, process conditions, temperature treatment, and associated characterization techniques to analyze their impacts on solar cell performance is also presented.

#### 3. Methods for Patterning the ARC

The patterning of front ARC for screen-printed metallization is aided by the inclusion of glass frit in the metal paste, which etches the  $SiN_x$  during the firing process [8]. For the case of Ni-Cu based metallization, a separate step for opening the grid pattern is required, which is then subsequently filled by a metal deposition process like electroplating. A brief overview and process description of the various methods are presented ahead.

3.1. Etch Resist and Wet Etching Based Methods. In this method, an etch resist is deposited on the front side such that only the grid pattern area is exposed for the etching step. Photolithography is a classic example of this method, but its high cost and more number of processing steps have limited its use to lab-level high efficiency cells. Alternatively an etch resist can also be deposited by ink-jet or screen-printing method and then the ARC is etched by a wet chemical treatment step. As reported by Nguyen et al. [31] a UV curing resist can also be used as a mask. The line resolution would be limited by the specific method used for pattern deposition. Line widths of 30  $\mu$ m can be achieved with photolithography, while widths down to  $20\,\mu m$  can be obtained by ink-jet method [32]. All methods require an additional cleaning step to remove the resist once the patterning is done and hence would limit the throughput rate.

3.2. Direct Etching Based Methods. As the name suggests, no etching mask is applied and the ARC is directly etched by application of a suitable etchant onto the front side of solar cell. Application of phosphoric acid based etch paste and curing in temperature range of  $300^{\circ}$ C- $390^{\circ}$ C etches the underlying SiN<sub>x</sub> [33, 34]. Etched line widths of 85  $\mu$ m have been achieved by screen printing of solar etch paste [33]. Another technique which avoids the high temperature treatment is based on application of a water soluble acidic polymer which reacts with a locally deposited fluoride based solution to form HF-based species which will etch SiO<sub>2</sub> or SiN<sub>x</sub> underneath [35]. Etched line widths of 25  $\mu$ m have been achieved in a 75 nm SiN<sub>x</sub> deposited on textured Si surface by

FIGURE 2: Process flow for Ni-Cu based front side metallization.

such a method. Though fluoride containing  $NH_4F$  solution is used in this method; it is safer to handle than HF-based etching solutions. Since the method produces low amount of waste, it is easy to handle and dispose and keep the fluoride concentration well below the regulatory limits.

3.3. Laser-Assisted Methods. One of the earliest application of laser was for the fabrication of LGBC cells [21] which was successfully commercialized by BP Solar. Infrared range laser of wavelength 1,064 nm was used to create grooves of depth 40  $\mu$ m and width of 20  $\mu$ m [36]. Creating such deep contacts and fine width grids reduced the shading losses and facilitates collection of carriers generated by longer wavelength. Also the high aspect ratio of contacts with a heavy doping beneath the contacts reduced the *R*<sub>s</sub> losses in cell.

Dube and Gonsiorawski demonstrated YAG laser based patterning and subsequent plating based contacts for EFG polycrystalline solar cells in 1990 [37]. A reduction in the metal-semiconductor interface decreased the emitter saturation ( $J_{oe}$ ) current density and shading losses for the solar cells. A significant gain of 8 mV in the  $V_{oc}$  was also obtained as compared to the standard photolithography based patterned cells.

Laser Chemical Processing (LCP) based patterning offers addition of selective emitter (SE) formation along with the patterning step, circumventing elaborate processing as needed in LGBC cells. By combining a dopant-containing carrier which guides a Nd:YAG green laser beam, pseudo FF's as high as 80% have been achieved. This indicates minimum defects were introduced in the emitter and no shunting was introduced during the laser processing step [38]. With reduced line width and higher sheet resistance emitter, improvement in  $V_{oc}$  and blue region quantum efficiency can be achieved. Also the SE formation is much simpler compared to other possible methods [39].

3.4. Mechnical Methods for Patterning. Mechnical grooving for contact deposition can be applied for single side buried contact solar cells [40], while application of back contact scribing has also been reported [41, 42]. The scribing tip typically made of artificial diamond with width of as low as 10  $\mu$ m was used for patterning of SiO<sub>2</sub> layer, while patterning of Si-rich SiN<sub>x</sub> with mechanical scribing was found to be more effective compared to wet-etching techniques [41]. Diamond blade based sawing has been successfully applied for deep groove formation on the front side of solar cells by Solarex Corporation, USA [43]. Grooves with width and depth of 25  $\mu$ m and 45  $\mu$ m, respectively, were obtained with this technique and successfully applied for c-Si solar cells under 14-20 suns concentration to obtain efficiencies greater than 18.5% [43]. Dicing based grooving to form buried contacts on mc-Si cells with mechanical V-texturing process achieved efficiencies in the range of 16.5-17.5% [44]. The metal shading due to narrow grooves was only 4% in the later work. Given the advantages of process simplicity and high throughput potential, mechanical methods for patterning can play an important role in Ni-Cu based metallization in the future.

#### 4. Ni and Cu Deposition Process Parameters

As compared to the screen printed Ag contacts, Ni and Cu are deposited by plating process which is a noncontact process. To improve the metallization properties, reduction in shading losses and  $R_s$  along with increasing the aspect ratio is vital. The finger width for Ni-Cu based metallization is determined by the patterning process and, as indicated

above, can go down to 20  $\mu$ m. The line resistivity and  $\rho_c$  will depend on the plating and temperature treatment steps. The various methods which can be used to deposit the metals are presented ahead.

4.1. Methods for Ni and Cu Deposition. As discussed above, the metallization scheme requires deposition of Ni as the seed layer over which Cu is deposited to thicken the contacts and reduce the  $R_s$ . Various physical vapor deposition (PVD) methods like sputtering and evaporation can be used for the Ni seed layer. But such methods involve photolithography or masking of the front surface for selective area deposition. Also the deposition rates are slow which makes them unsuitable for high throughput production. Chemical bath based methods offer a cost effective option with control of the deposition process based on parameters like bath composition, pH, and temperature. Light Induced Plating (LIP) is another method that utilizes the photovoltaic effect of a solar cell for plating the front side. The generated photovoltage will supply the necessary electrons for reduction of metal cations. The various deposition techniques with their respective applications are elaborated in the following sections.

4.2. Electroless Plating. Electroless plating is an autocatalytic process in which plating can take place on an activated substrate without the need of electrodes or current flow as in a conventional electroplating system. Electroless Ni plating is a well-established process [45] and is ideally suited to deposit the Ni seed layer, as electroplating process would require a conducting substrate to deposit the metal. Masking to prevent deposition on unpatterned regions would be provided by ARC during the process. Electroless Cu processes [45] can also be used for the subsequent thickening of contacts, but the deposition rates are low and hence time consuming.

4.2.1. Mechanism of Electroless Plating. Electroless deposition involves reduction of metal cations by electrons obtained from a reducing agent. The process is autocatalytic and continues till the reducing source or metal source is exhausted in the bath, unlike displacement plating in which the plating stops once the entire surface is covered with the deposited metal. The oxidation and reduction reactions involved in the deposition are

$$\mathbf{R}^{n+} \longrightarrow \mathbf{R}^{n+z} + z \mathbf{e}^{-} \tag{2a}$$

$$M^{z+} + ze^- \longrightarrow M$$

(2b)

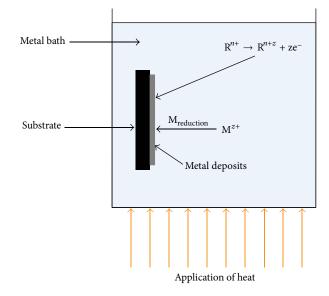

where R and M are the reducing and metal ions, respectively. A schematic with typical reactions involved is shown in

Figure 3.

For electroless Ni plating, nickel sulfate  $(NiSO_4[H_2O]_6)$ and nickel chloride  $(NiCl_2)$  are the most commonly used source of Ni cations. A variety of reducing agents can be used based on the desired properties and constituents. Sodium hypophosphite  $(NaH_2PO_2)$  which is inexpensive and nonpoisonous is commonly used as the reducing agent. One of the earliest works to deposit Ni on Si was reported by

FIGURE 3: Schematic of electroless plating setup.

Sullivan and Eigler [46] which was based on reduction of NiCl<sub>2</sub> by NaH<sub>2</sub>PO<sub>2</sub> with a bath temperature of  $95^{\circ}$ C.

For a  $NaH_2PO_2$  based solution, the anodic reactions involve dehydrogenation of the hypophosphite anion which results in release of hydrogen ion. In addition, phosphate anion is also generated with release of electron [47]. Respective reactions for the same are shown below [47]:

$$H_2 PO_2^- \longrightarrow H\dot{P}O_2^- + \dot{H}$$

(3a)

$$H\dot{P}O_{2}^{-} + OH^{-} \longrightarrow H_{2}PO_{3}^{-} + e$$

(3b)

The associated recombination and oxidation reactions for hydrogen ions are

$$\dot{H} + \dot{H} \longrightarrow H_2$$

(4a)

$$\dot{H} + OH^- \longrightarrow H_2O + e$$

(4b)

Prominence of either reaction determines the reducing efficiency of the process and depends on the properties of the surface, pH, and mixed potential [47]. For Pd, dehydrogenation takes place via equation 4b and hence the reducing efficiency is 100% [47]. This explains why Pd is a very good catalyst and hence commonly used for activation when plating on nonmetallic surface. The reducing efficiency for Ni-P deposition is in the range of 6 to 45%, as deposition involves (4a) for hydrogen evolution.

The cathodic processes involving deposition of Ni-P are

$$Ni^{2+} + 2e^{-} \longrightarrow Ni$$

$2H_2O + 2e \longrightarrow H_2 + 2OH^{-}$  (5)

$H_2PO_2^{-} + e \longrightarrow P + 2OH^{-}$

It can be observed that there is hydrogen evolution due to reduction of water molecule as well.

4.2.2. Photoassisted Electroless Ni Plating. As outlined in the previous section, the simultaneous anodic and cathodic reactions on the surface are responsible for metal deposition in electroless plating. The electrons supplied from the anodic reaction reduce the metal cations which are deposited on the substrate. The electron migration at the surface is determined by photovoltage for p-n junctions and electronegativity of the substrate [48]. Significant variation in the plating rates for n-type substrates under illumination has been observed [48, 49]. The photogenerated electrons which diffuse to the surface can contribute to reduction of Ni<sup>2+</sup> and hence increase the plating rate [48].

Application of photoassisted electroless Ni deposition for solar cell metallization has been reported in [31, 50, 51]. Application of light reduces the activation energy for deposition and hence facilitates deposition at lower bath temperatures. Though increased deposition was observed at the tips of the pyramids, an optimal combination of light and temperature can lead to uniform Ni deposition [50]. A variety of light sources like incandescent lamps, LED lights, halogen lamps, and lasers can be used for illuminating the cell with light intensity varying from 8,000 to 20,000 lux [51]. The light intensity can be kept constant throughout the plating duration or can be reduced after a fixed time interval to achieve best results for Ni deposition [51].

4.2.3. Laser-Assisted Electroless Plating. In addition to patterning and doping, laser application has also been reported for Ni deposition. In a laser induced Ni deposition technique [52], the solar cell is immersed in a Ni bath and then a suitable laser is shone through the electrolyte on the solar cell. The heat generated due to laser exposure causes localized reduction of the bath and also leads to electronhole pair generation in the cell. At the same time ARC is simultaneously patterned for localized deposition. Selection of the laser wavelength will depend on the absorption spectra of the bath. The metal salt and the reducing agent also play an important role in determining the deposit quality as was observed in [52]. Excessive laser exposure interval can lead to Si melting and bath evaporation in the plating regions. Metal diffusion in the space-charge region due to higher laser duration led to low FF values of 47.7% and 67.7% for two different bath compositions [52].

Another laser based technique known as Laser Transfer Contacts (LTC) heats a thin metal layer through an optically transparent window to make a direct contact with the emitter [24]. Seed layer line widths of 7  $\mu$ m were achieved which were further thickened by Ni and Cu plating to a final line width of less than 30  $\mu$ m. The Ni coverage over the grid pattern depends on the number of irradiation cycles and a higher number of laser cycles improved the coverage [24].

4.2.4. Importance of Ni and Silicide Thickness. Thickness of the plated Ni layer and the resulting silicide after annealing are critical for solar cell performance. If the deposited metal has higher thickness such that only part of it diffuses in Si, the grid resistance contribution from the unreacted film will be much higher than the silicide layer underneath [53]. Hence the total sheet resistance of the deposited film will be determined by the amount of silicide formed and the decreased resistance of the unreacted film due to defect annealing. In addition, film of higher thickness with more inhomogeneities increases the probability of shunt formation and high recombination areas near the junction as was determined using DLIT technique [23]. For a  $40-45 \Omega/\Box$ emitter, the junction depth is  $0.2-0.3 \mu m$ , while for lightly doped emitters ( $110-170 \Omega/\Box$ ) it can be as low as  $0.1-0.15 \mu m$ . Hence the Ni silicide formed after the annealing step should be less than  $0.1 \mu m$  to avoid shunt formation. As was observed in [31], a uniform seed layer does not necessarily lead to uniform silicide thickness. The interface between the Ni layer and Si plays an important role in silicide formation.

4.2.5. Electroless Ni Plating for Solar Cell Metallization. FF of 80.7% has been demonstrated with a uniform Ni seed layer of thickness in the range of 30–50 nm [23]. The plating duration was less than a minute for the light-assisted  $NiSO_4[H_2O]_6$ based alkaline bath. For higher Ni thickness in the range of 80-150 nm, localized shunts were detected which led to variations in FF from 64.2% to 76% [23]. In another study [54], a  $3 \mu m$  Ni layer deposited from a NiCl<sub>2</sub> based bath was found to be a good barrier to Cu diffusion with an extrapolated solar cell life time of more than 50 years at 45°C.  $\rho_c$  as low as  $3.5 \times 10^{-5} \,\Omega \text{cm}^2$  has been obtained for Ni seed layer, which was less than what was achieved for Ag/Pd/Ti/Si based contacts [10]. Because of the low  $\rho_c$ , high FF of 79.81% was achieved for the fabricated cells. For LTC with good coverage of the Ni seed layer,  $\rho_c$  of less than 1 m $\Omega$ - $\rm cm^2$  was possible. Also efficiency of 17.4% and FF of 77.7% were achieved with this method [24]. Electroless Ni can also be deposited as a barrier layer on fine line printed contacts which can subsequently be thickened by Cu plating. For aerosol printed contacts which were thickened by Ni-Cu-Sn layers demonstrated 20.3% efficiency on  $2 \times 2 \text{ cm}^2$  FZ cells, while 16.8% efficiency was achieved on  $5 \times 5 \text{ cm}^2 \text{ CZ}$  solar cells [25]. Ni being deposited by LIP instead of electroless plating did not affect the cell performance in former study. The important results for cells with front contacts based on electroless Ni seed layer are summarized in Table 2.

4.2.6. Electroless Ag Plating for Solar Cell Metallization. In addition to application of electroless plating for deposition of seed Ni layer, photoassisted electroless Ag plating over screen-printed Ag seed layer has been demonstrated to decrease the  $R_s$  and  $\rho_c$  leading to absolute improvement in FF by 2 to 8% [55, 56]. The improvement in FF is due to filling up of micropores and voids in the screen-printed contacts with plated Ag [55]. Commercially manufactured cells with noncontinuous contact grids or high  $R_s$  were also found to improve after electroless Ag plating with absolute efficiency gain of 0.2% to 1.8% [56, 57]. For B class production cells, reduction of more than 40% in  $R_s$  was possible which led to absolute 8% improvement in FF with a tighter distribution of  $R_s$  variation [56].

Also the peel strength of the Cu ribbon soldered over Ag plated contacts was stable after 200 temperature cycles from

| Result<br>type | Substrate<br>type | Cell Area<br>(cm <sup>2</sup> ) | Ni thickness<br>(µm) | V <sub>oc</sub><br>(mV) | $J_{\rm sc}$<br>(mA/cm <sup>2</sup> ) | FF<br>(%) | η<br>(%) | Reference |

|----------------|-------------------|---------------------------------|----------------------|-------------------------|---------------------------------------|-----------|----------|-----------|

| Average        | CZ                | 25                              | 0.03-0.04            | 617.4                   | 36.38                                 | 77.9      | 17.5     |           |

| Best           | FZ                | 4                               | 0.03-0.04            | 650.6                   | 39.36                                 | 80.7      | 20.7     | [23]      |

| Min            | FZ                | 44.89                           | _                    | 685.9                   | 37.9                                  | 79        | 20.5     | [10]      |

| Best           | FZ                | 44.89                           | _                    | 692.4                   | 37.8                                  | 81.95     | 21.4     | [10]      |

| Best           | CZ                | 4                               | 3                    | 612                     | 36.5                                  | 77.7      | 17.4     | [24]      |

| Best           | FZ                | 4                               | —                    | 646.4                   | 38.86                                 | 80.8      | 20.3     |           |

| Average        | CZ                | 25                              | —                    | 613.8                   | 35.74                                 | 74.9      | 16.4     | [25]      |

| Best           | CZ                | 25                              | —                    | 616.8                   | 35.69                                 | 76.2      | 16.8     |           |

TABLE 2: Solar cell performance data for front contacts with electroless Ni as the seed or barrier layer.

$-40^{\circ}$ C to 85°C due to more dense and continuous plated Ag surface [56]. For minimodules fabricated from such cells, the degradation in module performance was less than 5% after 200 temperature and 1000 hour damp heat test as required by IEC 61215 standard.

4.3. Electroplating. Subsequent to deposition and temperature treatment of the Ni seed layer, the line resistance of the front contact is to be reduced by thickening using a suitable metal. Though Ag can be plated using standard recipes, since the aim is to consider a low cost alternative, Cu can be plated over the seed layer. Copper sulphate (CuSO<sub>4</sub>[H<sub>2</sub>O]<sub>5</sub>) along with a Cu anode is commonly used in electroplating of Cu. The CuSO<sub>4</sub>[H<sub>2</sub>O]<sub>5</sub> solution will dissociate into positively charged Cu ions and negatively charged SO<sub>4</sub> ions. Due to the applied electric field, the positively charged ions will migrate towards cathode, while the negatively charged ions will move to anode. Reduction of the Cu ions takes place as shown below and Cu will be deposited on the cathode [58]:

$$Cu^{2+} + 2e \longrightarrow Cu$$

(6)

The Cu deposition will continue to build until the Cu ions and electrons are available at the cathode for reduction. The anode Cu dissolves in the bath and enters into equilibrium with the  $SO_4$  ions that have migrated towards anode. Deposition and dissolution of specific electrode can be controlled by the applied potential and accordingly oxidation and reduction of Cu will occur on the respective electrodes:

$$Cu \frac{\leftarrow Reduction}{Oxidation} Cu^{2+} + 2e \tag{7}$$

The deposition rate on cathode can be calculated from Faraday's first law [26], which is given by

$$m = c \cdot I \cdot t \cdot a, \tag{8}$$

where m is the mass of the deposited metal, c is the electrochemical equivalent in g/Ah, I is the current in amperes, t is the plating duration in hours, and a is the current efficiency of the process in %.

The electrochemical equivalent values for various metals are shown in Table 3 [26].

TABLE 3: Electrochemical equivalent of different metals relevant to solar cell metallization [26].

| Metal | Valency | Electrochemical equivalent (g/Ah) |

|-------|---------|-----------------------------------|

| Ag    | 1       | 4.0245                            |

| Cu    | 1       | 2.3715                            |

| Cu    | 2       | 1.1858                            |

| Ni    | 2       | 1.0947                            |

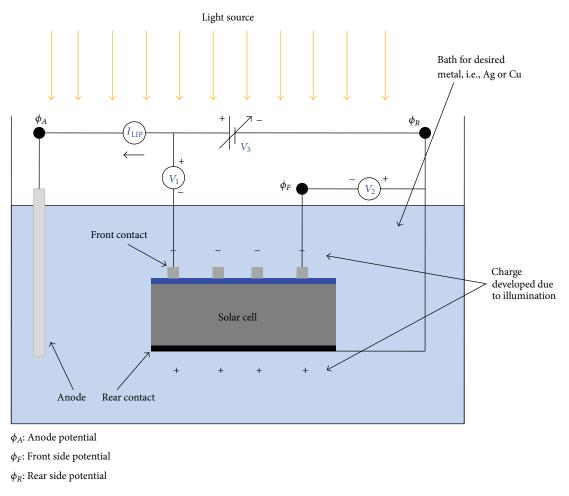

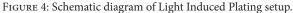

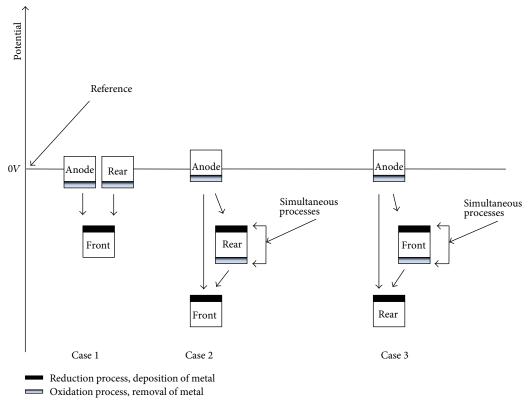

4.3.1. Light Induced Plating (LIP). LIP derives its working principle from conventional electroplating but utilizes the photovoltaic property of a solar cell for plating the desired metal. Early work on application of illumination for plating on a p-n junction was done by Durkee [59] and Grenon [60]. A typical setup of LIP with the associated voltages and current is shown in Figure 4. By application of external voltage between an auxiliary electrode and the rear side, deposition on the front and rear side can be controlled simultaneously [60]. The advantages offered by LIP as compared to electroplating and electroless plating are as follows.

- (i) No requirement to contact the front surface of solar cell as in an electroplating system: this is a critical advantage when plating of fine lines is being considered for front side metallization.

- (ii) Uniform voltage distribution across the grid pattern due to photovoltaic effect will ensure uniform current density across the plating area. In the conventional electroplating system, varying distance of the cathode regions from the cathode probe leads to nonuniform voltage distribution and hence nonuniform thickness across the sample.

- (iii) No requirement of a reducing agent as in electroless plating process: this increases the bath stability and reduces maintenance overheads.

- (iv) For laser based processing such as laser doping or ablation, LIP can avoid deposition in regions where microcracks are generated since the photovoltage is low [61]. This is unlike electroless plating in which plating takes place on the exposed Si and hence increases the formation of shunts in laser damaged areas.

Given the possible advantages of LIP, there are associated difficulties with respect to anodic process and front surface related parameter measurement. The rear surface needs to be protected against dissolution as the entire cell will be immersed in the electrolyte. This can be achieved by introduction of an additional auxiliary electrode in the bath and application of a potential as indicated in Figure 4. The anodic process will in turn be transferred to the auxiliary electrode and prevent dissolution of the rear side. For the plating process, the two important parameters that determine the deposition rate and deposit quality are the working electrode potential and current density. Both the parameters can be easily monitored in a conventional setup. For LIP, since the front surface is not contacted and also the measured current is not the direct current flowing through the front side, measurement of the parameters becomes difficult. Reported work [27, 62, 63] to analyze the relation between various bath parameters and their impact on deposition will be discussed ahead.

Simplified Understanding of LIP Process. The two processes that are of central importance in a plating process are

reduction and oxidation which occur at the cathode and the anode, respectively. The impact of illumination can be understood by analyzing its effect under different plating conditions. When the rear side of the cell is covered with a protective resist, oxidation of the rear side will not take place and hence the plating process cannot be completed. When the rear side is introduced in the bath, anodic oxidation takes place and metal deposition on the front grid will occur. There will also be an associated dissolution of the back side Al due to oxidation process. When an additional auxiliary electrode is introduced in the setup which is connected to the rear side, the plating process will depend on the illumination and applied voltage. The impact of varying voltage applied between the auxiliary electrode and rear side can be understood by considering Figure 5 [62]. The different cases as indicated are explained as follows.

*Case 1* ( $\Phi_A = \Phi_R > \Phi_F$ ). In this condition, the auxiliary electrode and rear side are short circuited and hence are at a higher potential compared to the front side. Under such a scenario, metal from auxiliary and rear will get oxidized and will be deposited on the front side.

FIGURE 5: Scenarios for LIP based on the applied potentials [62].

*Case 2* ( $\Phi_A > \Phi_R = \Phi_F/2$ ). Since the anode is at the highest potential, deposition will occur on the front and rear side. But since the front side is at the lower potential compared to rear side, the deposition rate will be higher for the former electrode. Similarly, since the rear is at the higher potential than the front side, it will also get oxidized. In an ideal scenario, the oxidization and reduction rate of the rear side will be equal and deposition will only occur on the front side. This is the optimum scenario for LIP given the operating current is also optimized.

*Case 3* ( $\Phi_A > \Phi_F = \Phi_R/2$ ). This scenario is similar to the previous case, except that the front and rear sides have been interchanged. Under such a condition, deposition will take place on the rear side and no deposition will result on the front side.

Illumination intensity also plays an important role in defining the optimum operating conditions. For obtaining high deposition rates, the current should be close to the maximum operating current of the bath. So if the illumination is too low, the optimum condition defined under Case 2 will be achieved at low current densities [62]. Similarly, operating at a very high value of illumination, the current for achieving Case 2 can be beyond the maximum current limit of the bath. Hence an optimum irradiation value will be one in which the current is fairly high along with operation under Case 2 [62].

A simplified equivalent circuit for LIP process along with different current paths is illustrated in Figure 6 and Table 4 respectively [27]. It can be observed that the rear side has a cathodic function in the first path, while on the other hand it serves as the anode for the third path. As can be noted, presence of additional current paths through the electrolyte has a shunting effect on the  $I_{\text{LIP}}$  v/s  $V_3$  plot, though the current values can be high for increased values of V <sub>RS-AUX</sub> [27].

Measurement of Current Density during Plating. Calculation of the current density on the front side has to be done through an indirect method since direct contact is not possible. By measuring the mass of the deposited metal in a known time interval, the current density can then calculated from Faraday's law as shown in (8). As has been demonstrated in [27], introduction of two solar cells with front and rear side covered with a resist in respective cells facilitates calculation of deposition mass after plating. The setup closely mimics the working of an actual solar cell and hence is a reliable method for calculating the weight gain and hence the current density on the front side. Another reported method which does not require selective application of a resist on each side is based on Inductively Coupled Plasma Optical Emission Spectroscopy (ICP-OES) and Inductively Coupled Plasma Mass Spectrometry (ICP-MS) [63]. In this method, the plated metal was dissolved in a known volume of 35% nitric acid in deionised water and then the metal concentration was

FIGURE 6: Electrical equivalent of LIP setup with different current paths [27].

TABLE 4: Different current paths in a LIP setup [27].

| Path | Description                   | Functional<br>anode | Functional cathode |

|------|-------------------------------|---------------------|--------------------|

| 1    | Protective potential          | Auxiliary<br>anode  | Rear side          |

| 2    | Direct deposition             | Auxiliary<br>anode  | Front side         |

| 3    | Solar cell short circuit path | Rear side           | Front side         |

determined by either of the above mentioned methods. For low level metal concentrations, ICP-MS was used due to its higher sensitivity.

*Impact of Rear Side Potential on the Plating Process.* As would be expected, an increasingly negative rear side potential will prevent dissolution of the Al back contact. As was observed in [63], the amount of Al dissolved reduced for decreasing rear side potential, while the mass of deposited Cu increased. At a lower potential than the point of minimum Al dissolution, there was a sudden increase in the amount of dissolved Al, which was attributed to induced galvanic corrosion of Al due to high amount of deposited Cu [63]. Also deposition of Cu on the rear side is undesirable, as it may interact with the back side encapsulant [63].

Another important impact of the rear side potential is on the morphology of the deposited metal. A more granular and inhomogeneous deposition was observed for more negative rear side potential [63]. This in turn led to a lower value of weight normalized conductivity with respect to deposition at lower negative potentials or with a cyanide containing electrolyte. Hence it can be inferred that apart from prevention of Al dissolution, the rear potential also strongly influences the morphology of front side deposition. More negative rear side potential tends to be more detrimental for the deposition process on either sides of the solar cell.

4.3.2. Electroplating for Solar Cell Metallization. Thickening of stencil printed 80 µm grid lines by electroplating of Ni-Cu-Sn stack based on a commercial plating tool was shown to improve efficiency of mc-Si and mono-Si solar cells by absolute 0.4% [64]. The platform had single side wafer processing and hence no chemical attack on the back side Al. Complete solar cell metallization based on electrochemical deposition of Ni and Cu has also been demonstrated [65]. Pulsed plating was used as compared to direct plating in the work to ensure homogeneous and well adhered contacts. LIP based thickening of screen-printed contacts was first reported by Mette et al. [28]. An absolute efficiency gain of 0.4% was obtained for large area cells based on standard production process, while an improvement of more than 1% absolute was possible for fine line 70  $\mu$ m printed contacts. For an optimized grid design, efficiency gain of 0.7% was achieved for large area cells as shown in Table 5. With an optimized  $SiN_x$ , efficiency of 19.2% has been demonstrated on industrial grade Si with Ni and Cu layers deposited by LIP on LDSE cells [29]. Psuedo fill factors (pFF) nearing 80% were possible with Ni-Cu-Sn based contacts deposited by LIP, with no observable degradation in the pFF after a stress test at 200°C for 1000 hours [25].

LIP of Ag for short durations over the screen printed contacts results in improvement of the FF which was attributed to reduction in contact resistance alone [66]. For increased time duration, the reduction is due to decrease in line resistance as well. The LIP solution etches the glass layer on the finger edges and hence the reduction in  $\rho_c$  [66]. Similar effect was also observed when the cells were subjected to FGA anneal or a short HF dip [66].

After plating the conducting Cu layer, an Ag or Sn capping layer is deposited to protect the Cu conducting lines from oxidation and facilitate soldering of the interconnection tabs. Journal of Solar Energy

|                |                                  |                   | -                               |                         |                                       | -          | -                |                  |           |

|----------------|----------------------------------|-------------------|---------------------------------|-------------------------|---------------------------------------|------------|------------------|------------------|-----------|

| Result<br>type | Process<br>difference            | Substrate<br>type | Cell area<br>(cm <sup>2</sup> ) | V <sub>oc</sub><br>(mV) | $J_{\rm sc}$<br>(mA/cm <sup>2</sup> ) | pFF<br>(%) | FF<br>(%)        | η<br>(%)         | Reference |

| Best           | Before LIP                       | mc-Si             | 243.36                          | 612.1                   | 34.6                                  | _          | 74.9             | 15.9             |           |

| Best           | After LIP                        | mc-Si             | 243.36                          | 613.4                   | 34.1                                  | _          | 79.2             | 16.6             |           |

| Average        | Before LIP                       | mc-Si             | 243.36                          | $610 \pm 2$             | $34.5\pm0.1$                          | _          | $74.3\pm0.6$     | $15.6\pm0.2$     | [28]      |

| Average        | After LIP                        | mc-Si             | 243.36                          | $611 \pm 2$             | $34.1\pm0.1$                          | _          | $77.9\pm0.9$     | $16.3\pm0.2$     |           |

| Best           | Ni-Ni-Cu-<br>Sn                  | CZ                | 25                              | 619                     | 35.7                                  | 79.4       | 72.7             | 16.4             |           |

| Best           | Ni-Cu-Sn                         | CZ                | 25                              | 624                     | 35.4                                  | 79.7       | 69.5             | 15.4             | [25]      |

| Best           | Ni-Cu-Sn                         | CZ                | 20.5                            | 623                     | 37.3                                  | 79.7       | 74.2             | 17.2             |           |

| Best           | Background<br>plating<br>present | CZ                | —                               | 639                     | 38.7                                  | _          | 74.2             | 18.3             | [29]      |

| Best           | No<br>background<br>plating      | CZ                | —                               | 634.3                   | 38.7                                  | _          | 78.3             | 19.2             | [27]      |

| Best           | _                                | CZ                | 156.9                           | 638.3 ± 1.9             | $38.43 \pm 0.73$                      | _          | $78.82 \pm 0.51$ | $19.33 \pm 0.39$ | [30]      |

TABLE 5: Solar cell performance data for front contacts with electroplated metal layer (s).

Another important function of the capping layer is to prevent interaction of Cu with the EVA encapsulant. An impulse voltage test failure indicated by development of discharge sites was observed due to presence of Cu particles at the Al/EVA interface on the back side [67].

4.4. Factors Determining Adhesion of Plated Contacts. Adhesion and long term stability are vital factors for commercial success of Ni-Cu based contacts. It appears that mechanical adhesion of plated contacts is more critical than the problem of Cu diffusion in Si [68]. Since the plated contacts have 2 to 5 times smaller widths compared to printed contacts, the electrical and mechanical properties have to be relatively better to achieve the same performance [68].

Since electroless plating is normally done at a higher temperature, stress will be induced in the films due to the temperature gradient, which can adversely affect the film adhesion [69]. It has been reported that chemical roughening of Si improves the adhesion of plated Ni [70]. The roughened sites provide mechanical anchors for the film and hence improve its stability. Hence in that respect, the texturing on front side of solar cells would tend to improve the adhesion of plated Ni.

For electroplating of Cu over Ni, bath ageing plays an important role in the amount of stress present in the films which impacts the adhesion as well [71]. It has also been observed that adhesion of films was inversely proportional to the acidity of bath, while residual film formation can occur which can easily peel off from the underlying film [71]. Cleanliness of the substrate also plays an important role in adhesion of the deposited metal. In a study of Cu-Ni adhesion, it was found that the adhesion coefficient was adversely affected by unclean surfaces [72]. Unclean surfaces prevent surface diffusion of the metal and hence the area of contact is less compared to a cleaned surface [72]. Even when

the adhesion of Cu over Ni is good, the stress within the Cu layer can result in peeling of the Cu-Ni stack from the Si substrate [73]. As the thickness of deposited Cu increases, the internal stress generated is more than the strength of Ni-Si interface and leads to peeling of the metal stack. It was observed that uniform silicide formation anchors the Ni layer and improves the adhesion of contacts [73].

4.5. Contacting p-Type Layer with Ni-Cu Stack. In the previous sections, application of Ni-Cu metallization was discussed to contact n-type emitter on p-type cells. Given the potential benefits of n-type solar cells and their projected share of more than 30% by 2023 in c-Si solar cells [74], it becomes important to consider their application for p-type emitters and heavily diffused boron regions. As was studied by Hitto Iwasa et al. [48], photovoltage and electronegativity of the substrate play a significant role in the process of electroless Ni deposition. A decrease in plating rate was observed on p-type Si as compared to n-type Si, which was attributed to increased electronegativity of p-type substrate [48]. Addition of EDTA to the Ni bath increases the redox potential of the process to a level that the impact of electronegativity and photovoltage was suppressed, leading to similar deposition rates on both types of materials [48]. Adhesion of electroless Ni has been observed to be weak on Pd activated p-type substrates, which was attributed to weaker Ni-Pd silicide bonds due to lack of electrons in the p-type substrate, in spite of good bonding of Pd silicide and Si [75].

An exhaustive study of application of electroless Ni for contacting both n-type and p-type regions has been conducted by Kate Fischer for interdigitated backside buried contact (IBBC) solar cells [73]. An alkaline Ni bath operated at 80°C with Pd activation was found suitable to contact both regions with uniform silicide formation for good adhesion of Ni-Cu layers. Ni deposition from alkaline bath maintained at 93°C without activation led to nonuniform silicide formation on p-type grooves which was attributed to nonuniform nucleation of Ni particles causing extreme migration at Ni/Si interface during silicidation [73]. Electroless Ni-Cu based metallization has been successfully demonstrated to contact n- and p-type regions for Emitter Wrap Through, Metal Wrap Through, and Metal Wrap Around solar cell structures [76–78].  $\rho_c$  of less than  $3 \text{ m}\Omega$ -cm<sup>2</sup> has been reported on boron diffused emitter of 50–140  $\Omega/\Box$  with a two-step electroless Ni plating process [79]. Since complete coverage was not obtained in first plating step, Ni was deposited and annealed again subsequent to sintering of first layer.

### 5. Characterization of Ni-Cu Based Metallization

For Ni-Cu based metallization, it is important to characterize the various properties of contacts at different stages of fabrication. Apart from  $R_s$  and  $\rho_c$ , factors like shunt formation, metal layer thickness, uniformity, and adhesion are vital from characterization perspective.

5.1. Surface Morphology and Deposit Composition. Obtaining dense and uniform metal deposition is one of the critical factors to ensure good contact formation and reduced  $R_{\rm s}$ . Based on the bath conditions, the deposited metal coverage can be nonuniform due to unequal catalytic activity across the substrate. Surface morphology analysis based on scanning electron microscopy (SEM) can be performed to observe the variation in the thickness across the deposited areas. Crosssectional SEM can yield the thickness of deposited layer, which is otherwise difficult to determine for textured solar cell surface. Methods like energy dispersive X-ray analysis (EDAX) can indicate the percentage constituents present in the plated metals. Determination of phosphorus content in the deposited Ni is important, since the amount of stress induced in the films is inversely proportional to the amount of phosphorus incorporated in the films [45]. Also EDAX helps to determine if any impurities are deposited during the metallization process which can possibly be detrimental to the solar cell performance.

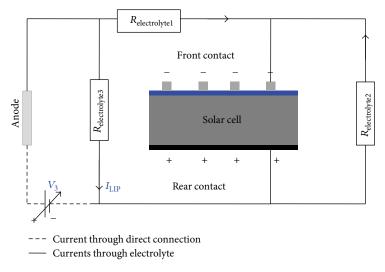

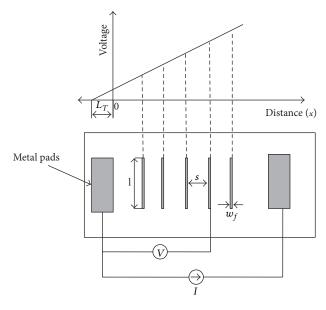

5.2. Contact Resistivity ( $\rho_c$ ) of the Interface. The metal-Si interface plays an important role in determining the  $R_s$  of a solar cell. For the power loss due to  $R_s$  to be less than 5%,  $\rho_c$  should be less than  $2 \text{ m}\Omega \text{-cm}^2$  [80].  $\rho_c$  defines the ease with which the current flows from the substrate to the metal grid lines and is quantified by the transfer length ( $L_T$ ) under the contacts. Figure 7 illustrates the concept of  $L_T$  for a metal-semiconductor interface [80]. When the current flows from the semiconductor side, it will enter the metal contacts and travel more under the contacts if the interface resistance is higher and vice versa.

Figure 8 illustrates the widely used setup for measurement of  $\rho_c$ . The method is based on having contacts of a predefined width placed between larger outer contacts through which a constant current is driven. As can be

FIGURE 7: Concept of transfer length under the contact.

FIGURE 8: Setup for measurement of contact resistivity [81].

observed, since the current will flow through the emitter, metal-Si interface, and then the metal contacts, the potential developed at the contacts will be dependent on the contact resistance ( $R_c$ ) of the interface. By extrapolating the resistance versus distance plot,  $L_T$  and  $R_c$  can be determined from the *x*- and *y*-axis intercepts, respectively. The  $\rho_c$  can then be calculated from the equations below [81]:

$$\rho_c = R_c * w_f * l, \quad \text{for } w_f < L_t, \tag{9a}$$

$$\rho_c = R_c * L_t * l, \quad \text{for } w_f > L_t. \tag{9b}$$

Another principle that measures  $\rho_c$  is as implemented in commercial equipment such as Corescan [82]. A light beam that illuminates the solar cell locally under short circuit condition is scanned in a direction perpendicular to the grid lines and the potential drop at each point is monitored. Based on the variation in the potential, changes in  $\rho_c$  along the grid lines can be observed.

5.3. Determination of Series Resistance  $(R_s)$ . Losses due to  $R_s$  in a solar cell can be significant given the cell size and magnitude of current flowing through it. Hence it is important to measure the  $R_s$  due to a particular metallization scheme. Broadly three methods can be employed for a reliable measurement of  $R_s$  [83]. First method is based on varying the illumination on the solar cell and then deriving the  $R_s$  based on the difference in generated voltage for the corresponding change in short-circuit current.

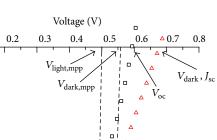

Another reliable and simple technique which does not require variation in illumination is the comparison of Suns- $V_{oc}$  curve [84] with the *I*-V curve taken under the solar simulator. Since the Suns- $V_{oc}$  measurement is made under open-circuit condition, the measurement will not be affected by  $R_s$  and hence comparison with the actual *I*-V curve will reveal information corresponding to  $R_s$  losses. By comparing the voltages at maximum power point (mpp) of the two *I*-V curves, the  $R_s$  can be obtained by the formula [83]:

$$R_s = \frac{\Delta V}{J_{\rm mpp}},\tag{10}$$

where  $\Delta V$  is the voltage difference between Suns- $V_{oc}$  and illuminated *I*-*V* curve at mpp and  $J_{mpp}$  is the current density at the mpp of illuminated *I*-*V* curve.

The final method is based on the comparison of the illuminated *I*-*V* curve with the dark *I*-*V* curve shifted by  $J_{sc}$ . As suggested by Aberle et al. [85],  $R_s$  can then be calculated as follows:

$$R_{\rm s,light\_dark} = \frac{V_{\rm dark_{mpp}} - V_{\rm light_{mpp}}}{\left| J_{\rm mpp} \right|}.$$

(11)

The parameters in the equation are as explained in Figure 9. Since the method does not consider the dark  $R_s$  contribution, errors of more than 5% can be present in the calculations [86]. Correction for the formula can be applied to obtain the modified equation:

$$R_{s,\text{light.dark,corr}} = \frac{V_{\text{dark}_{\text{mpp}}} - V_{\text{light}_{\text{mpp}}} - (|J_{sc}| - |J_{\text{mpp}}|) * R_{s,\text{dark}}}{|J_{\text{mpp}}|}, \qquad (12)$$

where  $R_{s,\text{dark}} = (V_{\text{dark},J_{\text{sc}}} - V_{\text{oc}})/|J_{\text{sc}}|$ .

5.4. Determination of Optimum Annealing Condition for Ni Silicide Formation. Optimization of annealing conditions for silicide formation is critical for obtaining reduced  $\rho_c$ and also ensuring that there are no adverse effects due to Ni diffusion into the solar cell. For annealing in the range of 200°C–350°C, Ni<sub>2</sub>Si is obtained, while annealing in the range of 350°C–750°C results in the formation of NiSi. For higher temperatures, the most stable phase NiSi<sub>2</sub> is formed [87]. NiSi is known to give the lowest resistivity [88] and hence is desirable from metallization point of view. For given deposition process and film thickness it is important to determine the temperature window for silicide

FIGURE 9: Parameters for calculation of series resistance by comparing Illuminated *I-V* and shifted dark *I-V* curves.

0.0

0

10

-20

-30

-40

Current density (mA/sq·cm)

0.1

light

Illuminated I-V curve

△ Dark *I*-V curve shifted by J<sub>sc</sub>

formation along with the percentage contribution of different phases present. Differential Scanning Calorimetry (DSC) measurements can be performed to determine the transition temperatures based on the heat flow peaks from the samples for a given temperature range [89]. Application of such a technique for silicide formation for solar cell metallization is reported in [81]. Additional techniques like XPS, XRD, and TEM measurements can be performed to confirm the presence of various phases.

5.5. Determination of Shunt Formation during Metallization. Metal diffusion into Si is known to create intermediate defects states and the front side metallization process of a solar cell can lead to metal diffusion across the p-n junction which may result in shunt formation. Since this degradation is process dependent and not a material related property, analysis of the solar cell to determine the impact of possible shunts is important.

Dark-*IV* measurement reveals many important properties of a solar cell [23]. By observing the reverse saturation current ( $I_o$ ) and variations in the local ideality factor in the low voltage regime, shunts across the device can be quantified. A pronounced hump in the ideality factor indicates presence of shunts, while the variation in higher voltage range can be used to determine  $R_s$  of a solar cell.

Another attractive method to determine the impact of shunt resistance  $(R_{\rm sh})$  on the solar cell *I*-*V* curve without the influence of  $R_s$  is the Suns- $V_{\rm oc}$  technique [84]. Since the measurements are done in open-circuit condition, impact of  $R_s$  and material quality on the device performance can be obtained. Comparison of the *I*-*V* curve for samples without front side metallization and after metallization from Suns- $V_{\rm oc}$  measurement can give a qualitative indication of the impact of the metallization process.

Core-Scan is another instrument which in the shunt scan mode operates the solar cell in dark condition and maps the local potential [83]. Due to presence of shunts, there will be spikes in the potential map across the cell. By operating at different bias levels, nonlinearity of the shunts can also be determined.

Shunts are sites of increased current in solar cells and hence they produce more heat which can be detected thermographically. For solar cells operating under forward bias, the shunts exhibit temperature difference of only few m°K as compared to the remaining area [90]. Also due to lateral diffusion of heat, thermal profiling and hence the resolution of steady-state thermography technique is poor. To overcome the drawbacks and take advantage of the thermography method, lock-in thermography (LIT) based systems can be used. Dark LIT, in which a current flows through the cell in dark condition, can give a map of the localized shunts present in the solar cell. By combining measurements under forward-bias and reverse bias, linear and nonlinear shunts can be quantified [90].

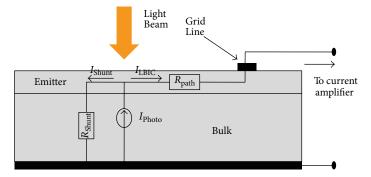

Light Beam Induced Current (LBIC) and Electron Beam Induced Current (EBIC) are complementary methods that operate a solar cell locally in short-circuit mode to obtain a map of current density variation. The current density variation would result mainly due to recombination defects within the material but can also be due to presence of shunts introduced during cell or material processing [91]. A typical LBIC setup will consist of a pulsed laser beam with a spot size of around  $20\,\mu m$  focused on a sample which is moved using an X-Y stage [91]. In EBIC, an accelerated electron beam is used instead of laser and hence can give a resolution of less than  $1 \,\mu m$  as compared to  $10-20 \,\mu m$  for LBIC [92]. In spite of a lower spatial resolution, LBIC allows imaging of large area solar cells with light beam which has a higher depth of penetration [91]. Since LBIC and EBIC are operated under short-circuit condition, the measurement is not affected by the dark I-V diode characteristics as is the case with LIT [91]. Contrast in LBIC/EBIC imaging can be attributed to three main factors: (i) recombination centers like grains of mc-Si material or areas with differing diffusion lengths, (ii) metallization lines, which will reflect the light and hence appear dark, and (iii) presence of shunts with the impact based on its location relative to the grid lines [91]. As illustrated in Figure 10, the detection current  $I_{\rm LBIC}$  flowing into the amplifier will depends on the parallel combination of shunt resistance  $(R_{sh})$  and the path resistance  $(R_{path})$  which includes contribution from emitter, bulk, grid lines, and wire connections. Hence the effective  $I_{\rm LBIC}$  value can be given by [91]

$$I_{\rm LBIC} = I_{\rm Photo} \frac{R_{\rm Shunt}}{(R_{\rm Shunt} + R_{\rm Path})},$$

(13)

where  $I_{\text{Photo}}$  is the locally generated photocurrent,  $I_{\text{LBIC}}$  is the detected LBIC current,  $R_{\text{Shunt}}$  is the localized shunt value, and  $R_{\text{Path}}$  is the resistance for current flow from detection point to collection,

For a reduced shunt value, if the value of  $R_{\text{Path}}$  is significant,  $I_{\text{LBIC}}$  will be reduced as indicated in the above equation.

Though LBIC/EBIC and LIT are imaging techniques for shunt mapping, difference in operating principle leads to difference in the data obtained in either cases. As was observed in [92], an ohmic shunt due to crack near a grid line was prominently displayed in LIT, while with LBIC it was observed like a grain boundary and not a strong shunt. Likewise a shunt observed via LBIC or EBIC which appeared between the grid lines, seemed to be located under the grid line as was observed by LIT [92]. For LBIC measurements, if the shunted region is away from the grid lines the value of  $R_{\text{Path}}$  will be significant and hence a decrease in  $I_{\text{LBIC}}$  will be observed, while the shunt located below the grid lines will not have a prominent impact due to negligible resistance to collection point [92]. Since in LIT the solar cell is operated in forward or reverse bias condition, the opposite condition for current flow will be applicable and hence the observed difference.

5.6. Characterization of Adhesion and Long Term Stability of Ni-Cu Contacts. Adhesion of the plated metal and long term stability are important aspects of the contacts for performance quantification. For electroless plated Ni and electroplated Cu, heat-quench test and peel test can be employed for qualitative indication of the adhesion [93]. Methods like exposure to salt spray test and atmospheric conditions can also indicate various defects like metal corrosion, blisters, pits, and cracks that are present in the metallic coating subsequent to exposure [94-97]. Pull test method has been used for quantifying adhesion of plated Ni films on Si substrates [69, 75] and adhesion strengths in the range of 5-10 MPa indicate strong adhesion of deposited Ni over Si. For examining the long term stability of Ni-Cu contacts, stress test at 200°C can indicate degradation in the solar cell performance due to diffusion of Cu in the cell [25]. The test is an accelerated way to determine the degradation of cells in actual module operating conditions close to 80°C for 20 years [96].

For solar cells tabbed on the front busbars with conventional soldering process in module-level interconnection, good adhesion for screen-printed contacts is in the range of 2–2.5 N/mm for a 45° pull strength test [97]. Adhesion strength in the range of 1–2.7 N/mm has been obtained for Ni-Cu based front contacts [68, 97, 98] with the best results obtained for thinner ribbons. Low peel strengths were obtained for standard soldering process with a failure in the metallization stack [99]. Alternative adhesive ribbon technology and lower temperature bonding processes were shown to achieve good adhesion for module integration [99]. Hence it can be inferred that improvements in the Ni-Cu metal stack along with adaptation of module-level tabbing process are needed to achieve good adhesion for Ni-Cu front contacts.

# 6. Background Plating for Ni-Cu Based Metallization

During the Ni-Cu metallization process, the ARC acts as a barrier mask and plating takes place on the exposed grid pattern area. However, there may be pin holes present in the ARC, which may expose the underlying Si during the plating

FIGURE 10: Current distribution during LBIC measurement based on localized shunt and path resistance [91].

| No. | Characterization method                        | Characterization technique that can be used                        | Information obtained                                                                                                                       |

|-----|------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Surface morphology Studies                     | SEM and optical microscopy                                         | Size of the deposits and density quantification possible                                                                                   |

| 2   | Optical measurements                           | UV/V is spectroscopy setup with an<br>integrating sphere           | Shading losses can be estimated                                                                                                            |

| 3   | Elemental analysis                             | Energy dispersive analysis, total reflection<br>X-ray fluorescence | Constituents of the deposits can be known and density can be quantified                                                                    |

| 4   | Luminescence imaging                           | Lock-in thermography, photoluminescence, electroLuminescence       | Localized shunt formation can be detected                                                                                                  |

| 5   | Quasi-steady state<br>Photoconductance studies | Life time and Suns- $V_{\rm oc}$ studies                           | Variation in life time due to defect<br>introduction and impact on passivation<br>properties possible. Shunt creation can be<br>determined |

TABLE 6: Methods for characterizing background plating.

process. The unwanted plating that might occur on the unpatterned areas during the metallization process is known as background plating. Since it is an undesirable phenomenon it is also commonly referred as overplating or ghost plating. Various groups have reported background plating during the metallization process [29, 100–102]. Background plating may lead to the following undesirable effects on a solar cell:

- (i) aesthetical degradation of cells,

- (ii) shading of the front side and hence a reduction in  $J_{sc}$ ,

- (iii) possibility of shunt formation across the junction due to metal diffusion,

- (iv) increase in the effective surface recombination velocity due to localized metal-Si contact,

- (v) adverse impact on solar cell life time due to creation of defect states by metal diffusion.

Given the possible impacts of background plating, it is important to optimize the deposition process and also characterize its possible impacts on solar cell performance. Table 6 gives an overview of the possible methods that can be employed for characterizing background plating.

As has been reported in [103], a qualitative and quantitative analysis of background plating is possible by electrical and surface morphology studies. Due to presence of pin hole deposited areas on the dielectric film, the resistivity will decrease and hence a qualitative quantification is possible by monitoring the change in current for an applied potential. By performing electroless Ni plating on the unpatterned  $SiN_x$ on the front side and observing them by optical or scanning electron microscopy, it is possible to estimate the pin-hole density. Subsequent Ag plating step can be done to enhance the visibility of dots than are too small to be observed. In spite of such methods, a thorough characterization of background plating is difficult due to the randomness associated with its manifestation.

In contrast to plating in pinholes on the ARC, Braun et al. [102] observed overplating in the trenches between the pyramids. Presence of discontinuous  $SiN_x$  and cracks due to insufficient texturing time were responsible for the deposition. In addition to metal deposition over the pinholes, deposition on the ARC has also been observed for electroless Ni and electroplating Cu baths [104-106]. These deposits need not constituent metal ions to be plated but miscellaneous ions from the bath may also be deposited [45]. As was observed in [104], if Na ions are deposited on the Si surface, they may diffuse during the silicide formation step and adversely impact the solar cell life time. For electroless Ni plating with Pd activation step, background plating becomes more severe with increased bath temperature [105]. In addition to reflectance studies, variation in minority carrier lifetime and implied  $V_{\rm oc}$  can also be used to quantify background plating [105].

FIGURE 11: Cross-section of a seed layer plated to thicken the contact [62].

6.1. Minimizing Impact of Background Plating. Optimization of  $SiN_x$  deposition process to obtain more conformal coating and varying the plating conditions have been shown to reduce the extent of background plating [29]. A thermally grown oxide before the ARC also solves the background plating problem [29] but would be undesirable due to the additional high temperature step in fabrication process. A double layer ARC stack of carbon-doped  $SiO_x/SiN_x$  in addition to reducing the front side reflectance also acts as a protective layer and eliminates background plating [107].

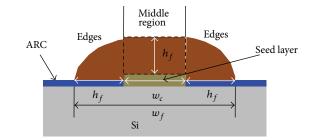

6.2. Lateral Overplating of Plated Contacts. In addition to the undesired plating in pin holes or over ARC, undesired lateral growth of fingers will occur due to the isotropic nature of the plating process. As illustrated in Figure 11, when a seed layer with width of  $w_c$  is plated to a height of  $h_f$ , the final finger width will be  $(2h_f + w_c)$  [62]. If the middle region is the desired geometry, the final finger width and crosssectional area will increase by  $2h_f/w_c$  and  $\Pi \cdot h_f/2w_c$  times, respectively. This implies an undesired increase in shading due to grid lines and metal cost by the respective factors. For an aerosol printed 40  $\mu$ m wide seed layer thickened to 20  $\mu$ m by LIP of Ag, the final finger width increased to 80  $\mu$ m [108]. However, when such type of cell was incorporated in a module structure, the effective optical width of contacts was found to be in the range of one-third to half of the geometrical width [109].

# 7. Commercialization of Ni-Cu Based Metallization

Though the Ni-Cu contacts based LGBC cells were commercialized, low throughput rates and increased processing costs led to screen printed contacts becoming the standard for solar cell metallization [110]. Another major concern is regarding the chemical waste due to the metal baths which can lead to serious environment contamination issues [111]. Steady research and advances in plating techniques have enabled transition of solar cell with Ni-Cu based metallizaton from labs to commercial scale production. Economic factors play vital role when considering an alternative technology with introduction of new equipments in the fabrication line. Given a new scheme of metallization, its long term stability and influence of module integration needs to be studied and optimized thoroughly.

A minimum efficiency gain of 0.4% absolute can be expected for fine line printed contacts which are subsequently thickened by LIP [28]. For an optimized bus bar design a gain of more than 1% absolute is possible [28]. Based on the efficiency gain and the amount of metal deposited, net cost savings can be estimated. Finally a process level comparison will yield the break-even point for the metallization process if the costs are more than the reference case of screen printed contacts [3]. As was indicated, an optimized ink-jet deposited seed layer with LIP of Ag can yield absolute efficiency gain of 1% at nearly the same cost for the screen printed contacts. The process cost savings become nearly 50% if the plated Ag layer is replaced by Ni-Cu-Sn layers [3]. Though an Ag seed layer is deposited in the above scenario, the cost savings will be more if its entire metallization scheme consists only of Ni-Cu-Sn lavers.

The Pluto series from Suntech Power is based on Ni-Cu based metallization with stabilized efficiencies of 19.0% on large area monocrystalline cells [112]. There was an improvement of over 6% as compared to the screen printed contacts due to reduced shading and improvement in  $V_{oc}$ . A related report indicated an improvement in efficiency to 20.3% for the same series, which was expected to rise to 21% [113]. Using a PERC structure, Schott Solar along with Schmid Group demonstrated 20.9% efficient 6" cells [114]. IMEC has also recently demonstrated conversion efficiencies of 20.3% on large area cells with plated contacts [115].

#### 8. Conclusions

Encouraging results in the last few years have pushed Ni-Cu based metallization on the verge of commercialization with companies having demonstrated commercial scale front side metallization based on plated contacts with an absolute efficiency enhancement of more than or equal to 1% compared to screen printed contacts. For Ni seed layer deposited by electroless plating, FF's nearing 80% can be achieved and subsequently efficiencies more than 17.5% are possible. LIP is an attractive variant of the electroplating method which can be used to deposit all metal layers in the front side metallization stack. Absolute gain of 1% is possible for fine line printed contacts, while complete metallization based on plated contacts can achieve efficiencies beyond 19%. Exhaustive characterization of the plated contacts would be necessary to optimize the process flow and achieve best performance from the cells.

Economic and efficiency advantages of fine line printed contacts thickened by plating demonstrate the benefits and viability of integrating plating with existing process. Since a commercial scale plating system involves continuous variations in chemical concentration and bath parameters, more detailed study would be required on its control and impact on contact properties. Though initial studies for thermal stress conditions for cells have been conducted, interaction of various metals with the module components under different environmental conditions will be critical for long term reliability assurance.

#### Acknowledgments

The work is supported by National Centre for Photovoltaic Research and Education (NCPRE), funded by Ministry of New and Renewable Energy (MNRE), Government of India.

#### References