# Review of Packaging Schemes for Power Module

Hou, Fengze; Wang, Wenbo; Cao, Liqiang; Li, Jun; Su, Meiying; Lin, Tingyu; Zhang, Guoqi; Ferreira, Braham

DOI

10.1109/JESTPE.2019.2947645

**Publication date** 2020

**Document Version**

Accepted author manuscript

Published in

IEEE Journal of Emerging and Selected Topics in Power Electronics

Citation (APA)

Hou, F., Wang, W., Cao, L., Li, J., Su, M., Lin, T., Zhang, G., & Ferreira, B. (2020). Review of Packaging Schemes for Power Module. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 8(1), 223-238. [8869891]. https://doi.org/10.1109/JESTPE.2019.2947645

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Review of Packaging Schemes for Power Module

Fengze Hou<sup>10</sup>, Wenbo Wang, Liqiang Cao, Jun Li, Meiying Su, Tingyu Lin, Guoqi Zhang, Fellow, IEEE, and Braham Ferreira, Fellow, IEEE

Abstract—SiC devices are promising for outperforming Si counterparts in high-frequency applications due to its superior material properties. Conventional wirebonded packaging scheme has been one of the most preferred package structures for power modules. However, the technique limits the performance of a SiC power module due to parasitic inductance and heat dissipation issues that are inherent with aluminum wires. In this article, low parasitic inductance and high-efficient cooling interconnection techniques for Si power modules, which are the foundation of packaging methods of SiC ones, are reviewed first. Then, attempts on developing packaging techniques for SiC power modules are thoroughly overviewed. Finally, scientific challenges in the packaging of SiC power module are summarized.

*Index Terms*—High-efficient cooling, low parasitic inductance, packaging schemes, scientific challenges, SiC power module.

#### I. INTRODUCTION

SILICON carbide (SiC) is a promising semiconductor material in high operating temperature, high blocking voltage, and high switching frequency applications due to its excellent electrical and thermal properties [1]–[4]. Compared with Si counterparts, SiC devices are cable of switching at higher speed and thus enable increased operation frequency of SiC power modules [5]. However, these features pose substantial challenges to packaging of a SiC power module.

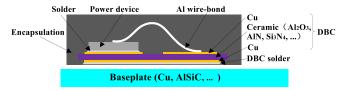

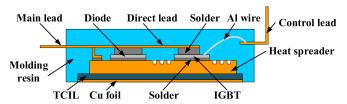

Aluminum (Al) wirebonded packaging scheme has been the most preferred package structure for power module up to now. Fig. 1 shows a power module with a conventional packaging

Manuscript received May 31, 2019; revised September 15, 2019; accepted September 24, 2019. Date of publication October 15, 2019; date of current version February 3, 2020. This work was supported by the National Natural Science Foundation of China under Grant U1537208. Recommended for publication by Associate Editor Jason Neely. (Corresponding authors: Liqiang Cao; Guoqi Zhang; Braham Ferreira.)

F. Hou is with the Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China, with the Department of Microelectronics, Delft University of Technology, 2628 CT Delft, The Netherlands, and also with the National Center for Advanced Packaging, Wuxi 214135, China (e-mail: houfengze@ime.ac.cn).

W. Wang is with the Shenzhen Institute for Wide Bandgap Semiconductors (WinS), Shenzhen 518055, China (e-mail: wenbo.wang@iwins.org).

L. Cao, J. Li, and M. Su are with the Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China, and also with the National Center for Advanced Packaging, Wuxi 214135, China (e-mail: caoliqiang@ime.ac.cn; lijun@ime.ac.cn; sumeiying@ime.ac.cn).

T. Lin is with the National Center for Advanced Packaging, Wuxi 214135, China (e-mail: tingyulin@ncap-cn.com).

G. Zhang is with the Department of Microelectronics, Delft University of Technology, 2628 CT Delft, The Netherlands (e-mail: g.q.zhang@tudelft.nl).

B. Ferreira was with the Department of Electrical Sustainable Energy, Delft University of Technology, 2628 CT Delft, The Netherlands. He is now with the Department of Telecommunication Engineering, University of Twente, 7522 NB Enschede, The Netherlands (e-mail: j.a.ferreira@utwente.nl).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JESTPE.2019.2947645

Fig. 1. Conventional packaging scheme for a power module.

scheme. The bottom side of a power semiconductor device is attached to a ceramic substrate [direct-bonded copper (DBC)], usually using solder, while the top side is connected using wirebonds. DBC is basically a ceramic tile with two layers of copper (Cu), with one of them patterned to form an electrical circuit [6]. The conventional package provides electrical interconnects (via Al wirebonds and upper Cu tracks of DBC ceramic substrate), electrical insulation (using the DBC ceramic substrate), device protection (by encapsulation material), and thermal management (through bottom side). This typical package structure is used in the vast majority of the power modules that are currently manufactured [7].

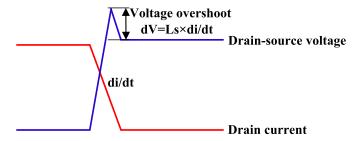

The conventional wirebonded interconnection solution, however, limits the performance of a SiC power module. Wirebonds have inherent parasitic inductance that could exceed 10 nH. High di/dt at turn-off transient would easily lead to voltage overshoot, increasing switching loss of power devices, causing electromagnetic interferences (EMIs), limiting switching frequency, and affecting switching waveforms [7]–[9]. From a heat dissipation point of view, heat generated by power devices is dissipated through its bottom side only, which affects the thermal performance of the power module. Moreover, as power loss increases with switching frequency, a cooling system that could remove heat through both sides of the die in a power module would be much more efficient for high-frequency operation of a power module [7]. Therefore, new low parasitic inductance and high-efficiency cooling interconnection solutions need to be developed to push the development of a power module.

In Section II, SiC material properties and SiC device potentials are introduced. In Section III, a comprehensive review of packaging schemes for Si power module is performed. In Section IV, packaging techniques for SiC power module are thoroughly overviewed. In Section V, scientific challenges in the packaging of SiC power module are summarized.

# II. SiC Material Properties and Device Potentials

Fundamental properties of several different semiconductor materials are listed in Table I [3]. Compared with Si

2168-6777 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

| TABLE I FUNDAMENTAL PROPERTIES OF VARIOUS |

|-------------------------------------------|

| SEMICONDUCTOR MATERIALS                   |

| Property                                            | 4H-SiC               | GaN                   | GaAs                 | Si                   |

|-----------------------------------------------------|----------------------|-----------------------|----------------------|----------------------|

| Bandgap (eV)                                        | 3.25                 | 3.44                  | 1.43                 | 1.12                 |

| Intrinsic carrier concentration (cm <sup>-3</sup> ) | 8.2×10 <sup>-9</sup> | $1.9 \times 10^{-10}$ | 1.8×10 <sup>-6</sup> | $1.5 \times 10^{10}$ |

| Breakdown electric field (MV/cm)                    | 2.2                  | 3.0                   | 0.3                  | 0.25                 |

| Thermal conductivity (W/mK)                         | 370                  | 130                   | 55                   | 150                  |

| Saturation drift velocity (10 <sup>7</sup> cm/s)    | 2.0                  | 3.0                   | 1.0                  | 1.0                  |

| Dielectric constant                                 | 9.7                  | 9.0                   | 12.8                 | 11.8                 |

| CTE (ppm/°C)                                        | 5.1                  | 4                     | 5.73                 | 2.6                  |

| Young's modulus (GPa)                               | 400                  | 181                   | 70                   | 131                  |

| Density (g/cm <sup>3</sup> )                        | 3.21                 | 6.15                  | 5.3                  | 2.3                  |

material, the bandgap of 4H-SiC is about three times higher and the intrinsic carrier concentration of 4H-SiC is much smaller. The wide bandgap energy and low intrinsic carrier concentration allow SiC devices to operate at much higher temperature (approximately five times higher than Si devices). The breakdown electric field of 4H-SiC is an order magnitude higher than Si, making SiC devices capable of sustaining higher voltage. Moreover, a SiC device can switch at higher speed because saturation drift velocity of such device is twice of Si and thus enable at least 5-10 times higher switching frequency [3], [10], [11].

Up until now, SiC devices, such as SiC MOSFET, Schottky diode, junction gate field-effect transistor (JFET), and insulated-gate bipolar transistor (IGBT), have been produced or demonstrated. Among these devices, SiC MOSFET has received most of the attention due to its promising capabilities of replacing Si IGBT in power electronics systems [11], [12].

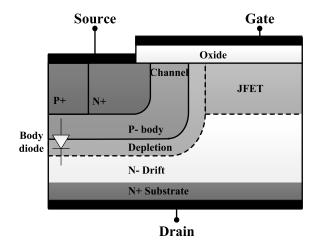

A SiC MOSFET is comprised of more than 10000 small parallel-connected n-channel enhancement mode MOSFET cells. A cross section of a SiC DMOSFET half-unit cell is shown in Fig. 2 [13]. A SiC MOSFET is fabricated by beginning with an n-drift layer grown on a heavy-doped n+ substrate. In order to attain high breakdown voltage, the drift layer is lightly doped. The breakdown voltage  $V_{\rm BR}$  of SiC MOSFET is influenced by the doping concentration of n-drift layer  $N_D$  and the thickness of n-drift layer  $w_B$ . The relationships can be expressed as follows, respectively [14]-[16]:

$$N_D = \left(\frac{4.45 \times 10^{13}}{1.25 V_{\text{BR}}}\right)^{4/3}$$

$$w_B = \sqrt{\frac{2\varepsilon_{\text{sic}} V_{\text{BR}}}{q N_D}}$$

$$(1)$$

$$w_B = \sqrt{\frac{2\varepsilon_{\rm sic}V_{\rm BR}}{qN_D}} \tag{2}$$

where  $\varepsilon_{SiC}$  is the buck electron mobility of SiC and q is the electron charge. The drift layer resistance  $R_{\text{drift}}$  is given in [16], which is expressed as

$$R_{\text{drift}} = \frac{w}{\varepsilon_{\text{SiC}} \cdot q \cdot A_{\text{GD}} \cdot N_D}$$

$$w = w_B - w_{\text{DSJ}}$$

(4)

$$w = w_B - w_{\text{DSJ}} \tag{4}$$

where  $A_{\rm GD}$  is the gate-drain overlap area, w is the drainsource undepleted drift width, and  $w_{DSI}$  is the drain-source

Typical structure of a SiC DMOSFET half-unit cell.

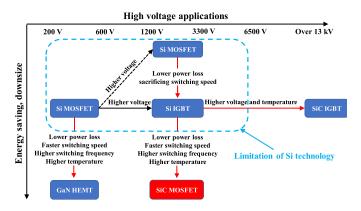

Fig. 3. Application range of Si, GaN, and SiC power devices.

depletion width. According to (1) and (2), the thicker the drift layer and the lower its doping level, the higher the breakdown voltage. On the contrary, in accordance with (3) and (4), the thinner the layer and the higher the doping level, the lower the drift layer resistance. Thus, a tradeoff exists between breakdown voltage and drift layer resistance. Moreover, the high breakdown electric field of SiC allows SiC power MOSFET with thinner and more highly doped drift layer. The more highly doped drift layer (more than ten times higher) provides lower drift layer resistance for SiC MOSFET. The thinner drift layer of SiC devices (1/10 that of Si devices) also contributes to the lowering of the drift layer resistance by a factor of 10. The combination of 1/10 the drift layer thickness with ten times the doping concentration can yield a SiC device with a factor of 100 advantages in resistance compared to that of a Si device [13], [14].

Fig. 3 shows the application range of Si, GaN, and SiC devices [17]-[20]. Switching loss of a unipolar device, such as SiC MOSFET, is relatively low as its switching speed is faster, so it can be used in high-frequency conditions. In comparison, switching loss of IGBT is higher due to its inherent slower switching speed attributed to its bipolar nature [17]. Compared with Si IGBT, the conduction loss of SiC MOSFET is lower because of its higher doping concentration in the drift region. The smaller depletion width reduces the ON-state resistance

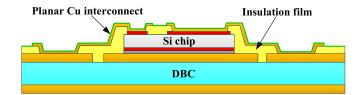

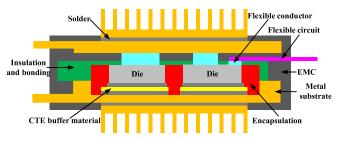

Fig. 4. Cross section of power module with planar interconnects.

of SiC MOSFET, resulting in less conduction loss. Besides, SiC MOSFET has much lower output capacitances and gate charge, and they can switch at much higher *dv/dt* and *di/dt*. High switching speed enables low switching loss and high switching frequency, which can improve the power density and efficiency of power module [18]. Moreover, switching loss of Si IGBT will increase significantly in higher operational temperature, while switching loss of SiC MOSFET has little variation over temperature [19]. Therefore, SiC MOSFET possesses definite advantages in middle-high voltage applications over competing Si counterparts.

#### III. PACKAGING SCHEMES FOR Si POWER MODULE

Packaging techniques of Si power modules, which are the foundation of packaging methods of SiC ones, are reviewed first. Various packaging schemes for Si power module have been developed, such as planar interconnection, press pack, chip embedded package, 3-D interconnection, and hybrid package.

#### A. Planar Interconnect Scheme

- 1) Siemens Planar Interconnect Technology: Siemens introduced a novel packaging technique for power modules based on a planar interconnect technology (SiPLIT), as shown in Fig. 4. The SiPLIT featured thick Cu interconnects on a high-reliable insulating film for top contacts of power chip. Due to the conductor structure and contact technology, ON-resistance and parasitic inductances of the power module were very low in comparison to state-of-the-art Al wirebonded interconnection. In addition, the large area contacting improved power cycling capability and surge current robustness significantly. Through electrical and thermal characterization, it was found that up to 50% reduction in parasitic inductances of the interconnects and a remarkable 20% decrease in thermal resistance were achieved [21].

- 2) Transfer-Molded Power Module Package: Mitsubishi reported a simple, compact, robust, and high-performance transfer-molded power module (T-PM) with direct lead bonding (DLB) technology, as shown in Fig. 5. Cu lead was directly bonded on the emitter and cathode electrodes by a Pb-free solder, and Al conventional wire was bonded on the gate electrode. In order to improve the thermal performance of the T-PM, a high thermally conductive electrically insulated layer (TCIL) was applied to the module. Compared with conventional wirebonded power module, the TPM showed 43% and 50% reduction in parasitic inductance and parasitic resistance, respectively [22].

Fig. 5. Structure diagram of DLB package.

Fig. 6. Multilayer planar interconnection package structure.

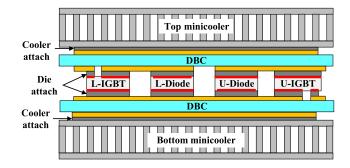

- 3) Multilayer Planar Interconnection Package: Liang et al. [23] proposed a multilayer planar interconnection package structure for a 200-A/1200-V IGBT phase-leg power module, as shown in Fig. 6. The switching dies were sandwiched between two symmetric substrates, providing planar electrical interconnections and insulation. Two minicoolers were directly bonded to outside of these substrates, allowing double-side integrated cooling. The upper switch pair and lower switch pair in the phase-leg were oriented in a face-up/face-down configuration. The bonding areas between the dies and the substrates, as well as the substrates and coolers, were designed to use identical materials and were formed in one heating process. Compared with wirebonded power module, total inductance and resistance of the planar bonded power module decreased by 62% and 90.6%, respectively. Besides, voltage overshoot reduced by 54%, and the total loss of the planar bond package was less than 10% of that of the wirebonded package. The double-sided cooling of the planar module reduced the specified thermal resistance to 0.33 cm<sup>2</sup> °C/W, which was 38% lower than that of the wirebonded power module.

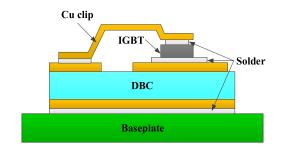

- 4) Cu Clip Bonding Technology: The concept of Cu clip bonding technology is shown in Fig. 7. Conventional Al wirebonds were replaced with a flat Cu clip. Due to the high electrical conductivity and high thermal conductivity of Cu, the clip could not only improve the switching characteristics of the power module through reduction of parasitic inductance but also provide an additional heat conduction path from the top surface of the die [24], [25]. Compared with conventional wirebonded counterpart, up to 23% reduction in junction to case thermal resistance for one individual die and around 18% decrease for the parallel operation of two dies were observed in the single-sided cooling tests, while in the double-sided cooling experiments, an additional average of 18% thermal improvement was achieved due to the addition of a top fancooled heatsink mounted onto the Cu clip [25].

Fig. 7. Structure diagram of Cu clip bonding package.

Fig. 8. Schematic of spacer-based sandwich structure.

5) Spacer-Based Sandwich Structure: Fig. 8 shows a schematic of spacer-based sandwich structure for power module. Cu spacers with different thicknesses were used to accommodate height differences between IGBT and diode in a power module [26], [27]. SAC305 solder sheet was selected as a dieattach material. To build solder bump on the IGBT and diode, an additional metallization layer was needed to be sputtered on the front-side source and gate pads to increase the wettability of solder. For this purpose, the original Al metallization of emitter, anode, and gate contact was modified by sputtering of Ti/Ni/Ag (60/500/800 nm) layers [26]. Compared with conventional IGBT module, 55.1% and 13.2% reduction in parasitic inductance and resistance and a 47.5% decrease in thermal resistance were achieved.

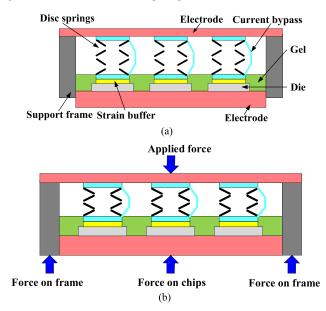

# B. Press-Pack Packaging Scheme

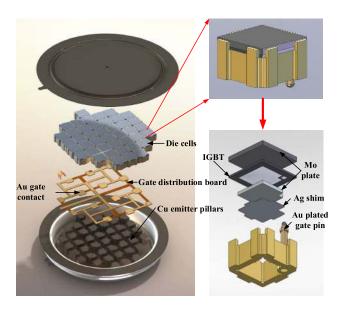

Press pack is a packaging approach that uses pressure contact instead of wire bonding and soldering in conventional power modules. Press-pack packaging has been developed for high-voltage and high-current applications. Fig. 9 shows the internal construction of a rigid press pack IGBT from Westcode [28], [29]. This package employs a hermetically sealed ceramic housing, with connections to the chips made by physical contact pressure via external clamping between rigid electrodes and strain buffers. In order to ease the stress of the package induced in the operating condition, molybdenum (Mo) plates are usually used.

Fig. 10 shows a construction of a compliant press-pack power module. Compliant press-pack devices are currently available, such as those manufactured by ABB, which employ a nonhermetic plastic housing, and the actual contact pressure made to the individual chip surfaces is controlled locally by disk spring assemblies inside the package [30].

#### C. Chip Embedded Packaging Scheme

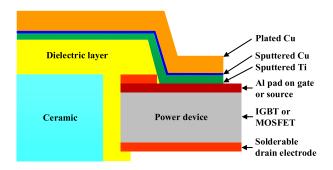

1) Ceramic Embedded Power Module: Fig. 11 shows a structure schematic of a ceramic embedded power module [31]. Multiple power chips, such as IGBT, MOSFET,

Fig. 9. Internal construction of a press pack IGBT from Westcode.

Fig. 10. Construction of a compliant press-pack IGBT. (a) Before compression. (b) After compression.

and diode, were embedded in a ceramic frame and covered by a dielectric layer with via holes on the Al pads of the chips. Then, metallization multilayers were deposited on the whole surface which formed contacts with the Al pads on the chips through via holes in the interlayer. Conventional sputtering was employed to deposit thin-film Ti and Cu layers. Electroplating was used to form thicker Cu deposition. Finally, the metallization layer was patterned to form both power and control circuits as well as their I/O terminals. Compared with conventional wirebonded package, a 75% reduction in parasitic inductance and a 44% improvement thermal dissipation performance were achieved.

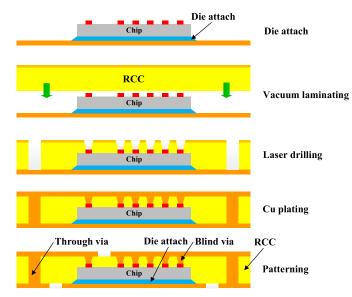

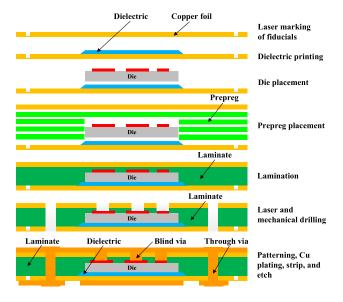

2) PCB Embedded Power Module: Printed circuit board (PCB) embedded package, also called "chip in polymer" technology, was first introduced by Fraunhofer IZM and TU Berlin. The ultrathin semiconductor chips were

Fig. 11. Structure schematic of a ceramic embedded power module.

Fig. 12. Process flow of PCB embedded package developed by Fraunhofer IZM and TU Berlin.

embedded into the build-up layers of PCB together with integrated passive components. Electrical interconnection between chip and outer layer footprints were realized by laser-drilled and metallized microvias [32]–[34]. The detailed packaging process is shown in Fig. 12 [33].

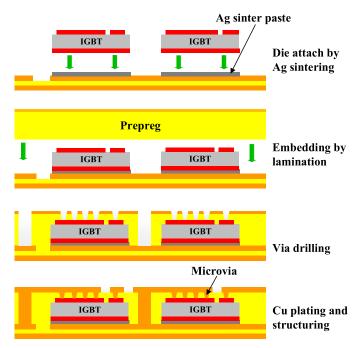

In 2013, Fraunhofer IZM and TU Berlin developed a PCB embedded packaging scheme for IGBT power module. In order to be compatible with laser drilling and Cu plating, a thin electroless Ni/Pd layer was added on IGBT and diodes [34]. The process flow is shown in Fig. 13. At first, a base substrate was manufactured by lamination of thick Cu and a thermally conductive prepreg layer. The top Cu layer was structured and selectively metalized by immersion Ag. Then, Ag sinter paste was printed to Ag areas and IGBTs and diodes were placed and sintered into the substrate at 200 °C with a relatively low pressure of 2 MPa. Third, IGBTs and diodes were embedded into a prepreg layer with  $105-\mu m$  Cu foil through vacuum lamination. Vias to chip pads and thick Cu were drilled by laser. Finally, the vias were filled with Cu by electroplating and the Cu was structured by etching [35].

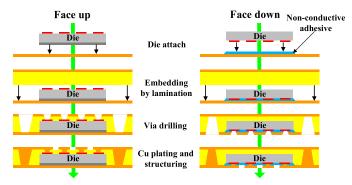

PCB embedded packaging technologies for power modules mainly include two process flows: face-up and face-down, as shown in Fig. 14 [36]. Die-attach material used in the face-down process is nonconductive adhesive, while for face-

Fig. 13. Process flow of PCB embedded IGBT module developed by Fraunhofer IZM and TU Berlin.

Fig. 14. PCB embedding process flows: face-up (left) and face-down (right).

up technology, die-attach material can be nonconductive adhesive, solder, sintered Cu/Ag, and so on. The face-up technology is more suitable for high power-density vertical dies, such as MOSFET, IGBT, and diode.

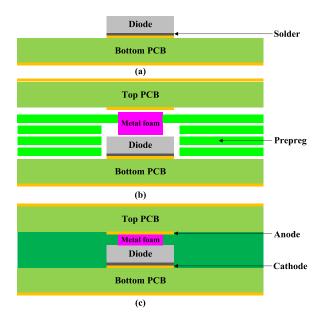

Pascal *et al.* [37] proposed an innovative PCB embedded manufacturing process, as shown in Fig. 15. They used a piece of nickel foam to create a pressed contact between the top side of a PCB embedded power die and the rest of the circuit. The average pore diameter of the nickel foam was about 350  $\mu$ m, and there were 57–63 pores/in. The detailed packaging process flow is as follows. First, as shown in Fig. 15(a), the bottom side of the diode is soldered onto a bottom PCB. Then, a piece of nickel foam, four layers of prepregs, and a top PCB are positioned above the bottom PCB, as shown in Fig. 15(b). Third, as shown in Fig. 15(c), the stack is laminated through high-temperature and high-pressure process, and the epoxy resin polymerizes and floods the foam. Compared with other PCB integration techniques, the proposed process is simple and cost-effective.

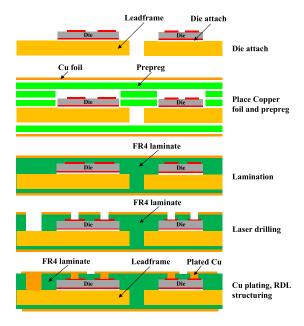

Munding et al. [38] reported a new lead frame-based laminate chip embedding technology. The packaging process

Fig. 15. Steps of packaging process using metal foam.

Fig. 16. Process flow of lead frame-based laminate chip technology.

flow is shown in Fig. 16 in detail. For power dies with vertical current flow, diffusion solder was adopted as die-attach layer, while for gate driver, insulating glue was also used. They presented a study on the laminate material choice and found that prepreg material with highly filled glass fibers and high Tg (glass transition temperature) was more robust than resin-coated copper (RCC) material. Then, they proposed a novel approach to avoid lamination voids, validated lamination process simulation based on the Monte Carlo method, and could predict process stability for a specific set of parameters and parameter variations. Third, they systematically analyzed the physics mechanism of laser-induced chip metallization damages and define countermeasures to avoid such damages.

Kearney et al. [39] developed a 1200-V PCB embedded three-phase IGBT inverter module, as shown in Fig. 17.

Fig. 17. PCB embedded three-phase inverter module.

The PCB embedded technology requires Cu metallization of the chips. The original Al metallization of emitter, gate, and anode contact was modified by sputtering Cr/Cu (5 nm/8  $\mu$ m) layers, while a portion of the individual chip was protected with a shadow mask. Then, six pairs of IGBT and diodes were sintered into a Cu lead frame with premachined cavities. Cu vias from outer Cu traces to chip pads were formed by laser drilling, electroplating, and so on. Comparing the switching performance, thermal resistance, breakdown insulation, partial discharge, and long-term aging with Semikron MiniSKiiP 23AC126V1 that used a traditional DBC sandwich structure, the PCB embedded module improved thermal management, reliability, and insulation.

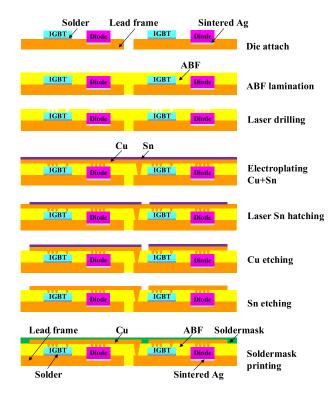

Chang et al. [40] presented an IGBT power module package by a chip embedding technology. The package process flow is shown in Fig. 18. Because the size and thickness of IGBT and diode adopted in the module are different from each other, a half-etched Cu lead frame was designed and fabricated. The IGBTs were attached to the lead frame by SAC305 solder paste, whereas the thicker diodes were sintered onto the halfetched Cu lead frame. Then, an ABF lamination process was conducted to form a built-up dielectric layer on the Cu lead frame. Next, the blind vias and circuits were formed on the built-up dielectric layer by a UV laser and were metalized with sputtered seed layer and electroplating. To form a circuit pattern, an additional 1- $\mu$ m-thick Sn layer was subsequently plated as a patterning mask, and a laser skiving process was conducted to remove Sn above the Cu layer. Thereafter, the etching of Cu, Sn, and Ti processes was performed to remove the metal on the dielectric layer, thus forming the required circuit pattern. Finally, a layer of solder mask was printed to prevent electric shock on the surface layer.

AT&S developed a panel-level PCB embedded lateral device package technology, known as embedded component packaging (ECP). The packaging process flow is shown in Fig. 19 [41]. The micro-vias were used as electrical interconnections and thermal conduction between the chip and Cu layers on the top and bottom surfaces [42], [43].

#### D. 3-D Interconnect Scheme

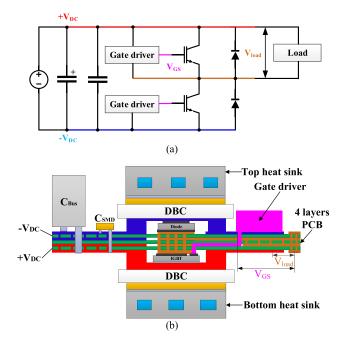

1) Power Chip-on-Chip Package: In order to reduce parasitic inductances, Marchesini et al. [44] presented a power chip-on-chip (PCoC) packaging technology for IGBT power module, as shown in Fig. 20. Electrical interconnection of the switching cell was realized through two DBC substrates and a four-layer PCB. DC link and decoupling capacitors were integrated directly on the PCB. The experimental results

Fig. 18. Process flow of IGBT power module by chip embedding technology.

Fig. 19. AT&S ECP process flow.

showed that the parasitic inductance of the PCoC module was drastically reduced compared with planar ones, especially when internal decoupling capacitors were integrated in the assembly.

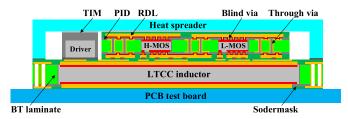

2) Power Chip-on-Inductor Package: In [45], a power chip-on-inductor (PCoI) packaging technique with double-sided cooling was presented. The structure diagram of PCoI package is shown in Fig. 21. A fan-out panel-level PCB embedded packaging technique for power MOSFETs and low-temperature co-fired ceramic (LTCC) inductor in a synchronous converter was proposed. The power MOSFETs and LTCC inductor were embedded in the top and the bottom PCB, respectively. A stacking of the top PCB and the bottom

Fig. 20. PCoC package. (a) Electric circuit. (b) Structure diagram.

PCB was implemented to form a 3-D integrated power supply module. The MOSFETs, gate driver, and passive components were interconnected by the redistribution layer (RDL) and PCB vias. According to thermal simulation results, PCB vias could improve the thermal performance of the 3-D module with cap heat spreader, which could effectively dissipate heat of the PCB embedded 3-D power supply module.

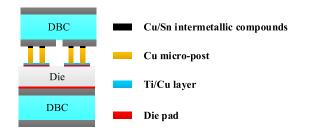

3) Micro-Post-Based Sandwich Structure: Micro-post-based sandwich structure is one of the 3-D interconnection configurations with double-sided cooling capability. Fig. 22 shows the schematic of Cu micro-post interconnection for power module. The Cu micro-posts were electroplated on topside of the die. The die with its micro-posts was then attached to a top DBC substrate using a Cu/Sn transient liquid phase (TLP) technique. An assembly of backside of the die to a bottom DBC substrate was processed concurrently using the same TLP technique [47]. In this bonding technique, a layer of Sn  $(0.5~\mu\text{m})$  was deposited on top of the posts, which was used as a solder between the posts and the Cu of the DBC substrate. Another bonding solution, Cu–Cu bonding, does not need any additional materials between micro-posts and the Cu of the DBC substrate [7].

The micro-post-based sandwich structure allows for cooling from two sides. The Cu posts provide spacing between the die and the top substrate. They are also useful to accommodate height differences between the dies in a multichip power module. Different types of dies (such as IGBT and diode), which are commonly used in a single module, do not always have the same thickness. The Cu micro-posts can compensate for thickness differences between the dies [6].

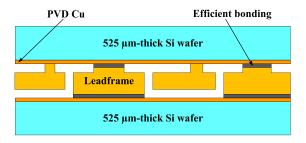

4) Solderless Lead Frame-Assisted Wafer-Level Packaging: In [46], a wafer-level packaging technique for power module was presented. Fig. 23 shows the schematic of the assembly with two Si wafers covered with Cu layer and the patterned and perforated Cu lead frame. A metallic lead frame was bonded between two wafers of semiconductor devices.

Fig. 21. Structure diagram of PCoI package.

Fig. 22. Schematic of Cu micro-post interconnection for power module.

Fig. 23. Schematic of the assembly with two Si wafers covered with Cu layer and the patterned and perforated Cu lead frame.

The 3-D assembly of the power devices and the metallic lead frame was realized by a solderless, thermocompression bonding.

5) Hybrid Packaging Scheme: Since high-power devices are usually metallized by Al on the top pads to be suitable for Al bonding wires, almost all wirebondless package structures require that the top electrode pads of power devices are remetallized, while in some hybrid packages, remetallization process is not needed and wire bonding techniques are still suitable.

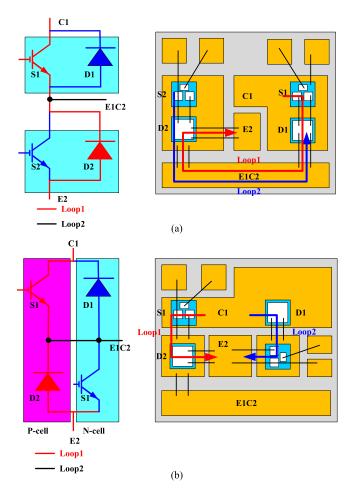

Switching Cell-Based Package: In [48], a switching cell-based IGBT phase-leg module was proposed. Fig. 24(a) and (b) shows the conventional module and p-cell and n-cell-based module, respectively. Compared with the conventional module, two devices in the commutation loop of the p-cell and n-cell module were placed at the same side, and thus, the physical length of the commutation loop was reduced. The parasitic inductance reduction of the layout design was in the range of 5–10 nH.

Table II presents a summary of different packaging schemes for Si power module.

# IV. PACKAGING TECHNIQUES FOR SiC POWER MODULE

Up to now, attempts for packaging SiC power module, e.g., planar packaging, press pack, 3-D packaging, and hybrid packaging techniques, have been performed.

Fig. 24. Phage-leg package layout. (a) Conventional module. (b) p-cell and n-cell-based module.

# A. Planar Packaging Technique

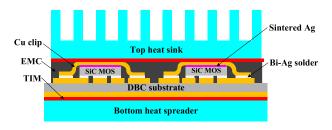

1) Miniaturized Double-Side Cooling: Rhee et al. [49] developed a miniaturized double-sided cooling packaging for SiC high-power inverter module using new materials to withstand high temperature over 220 °C, as shown in Fig. 25. The flip-chip bonding for source and gate interconnections was developed, and Bi-Ag solder paste was adopted. Its solidus temperature is around 260 °C and liquidus temperature is around 360 °C, which has much high thermal stability than conventional lead-free solder. In order to increase the wettability of solder paste, an electroless nickel immersion gold process on the Al bonding pads on the DMOSFET surface was performed. For drain interconnection, Cu clips were attached using Ag sintering materials. Through thermal modeling and characterization, thermal dissipation performance of power module was found to be enhanced by twice compared with the conventional single-side cooling-type power module.

2) Power Overlay Interconnect Packaging: General Electric developed a power overlay (POL) interconnect technology for SiC MOSFET packaging. The sources and gates of MOSFETs were interconnected by a flexible substrate, as shown in Fig. 26. Because the parasitic inductances of the package were greatly decreased, the POL showed low-voltage overshoot, which is the product of parasitic inductance and di/dt. When the drain–source voltage was 540 V and drain current

TABLE II

COMPARISON AMONG DIFFERENT PACKAGING SCHEMES FOR

SI POWER MODULE

| Packaging scheme                       | Features                                                                                                                                                                                                                                                                                |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 dekaging seneme                      | • Thick Cu interconnects on a high-reliable                                                                                                                                                                                                                                             |

| SiPLIT [21]                            | <ul> <li>insulating film.</li> <li>50% reduction in parasitic inductances of the interconnects and a remarkable 20% decrease in thermal resistance are achieved.</li> </ul>                                                                                                             |

| T-PM [22]                              | Cu lead is directly bonded on the emitter and cathode electrodes by Pb-free solder;     TCIL is applied to the module.                                                                                                                                                                  |

| Multilayer planar interconnection [23] | <ul> <li>Double-sided cooling;</li> <li>Structure symmetry;</li> <li>Switch pairs in phase-leg are oriented in face-up/face-down configuration;</li> <li>Total inductance is 12.08 nH;</li> <li>The specified thermal resistance is 0.33 cm²-°C/W.</li> </ul>                           |

| Cu clip [24]-[25]                      | Wire-bonds are replaced with a flat Cu clip;     up to 23% reduction in junction to case thermal resistance for one individual die.                                                                                                                                                     |

| Spacer-based sandwich [26]-[27]        | <ul> <li>Double-sided cooling;</li> <li>Cu spacers with different thickness are used to accommodate height differences of IGBT and diode;</li> <li>55.1% and 13.2% reduction in parasitic inductance and resistance and a 47.5% decrease in thermal resistance are achieved.</li> </ul> |

| Press-pack [28]-[30]                   | High-voltage and high-current application.                                                                                                                                                                                                                                              |

| Ceramic embedded package [31]          | <ul> <li>Integrate all switches into a single embedded power module;</li> <li>A 75% reduction in parasitic inductance and a 44% improvement thermal dissipation performance was achieved.</li> </ul>                                                                                    |

| PCB embedded package [32]-[43]         | <ul><li>Small form factor;</li><li>Light weight;</li><li>Simple packaging process.</li></ul>                                                                                                                                                                                            |

| PCoC package [44] PCoI package [45]    | <ul> <li>3D integration through DBC substrate and PCB.</li> <li>Low parasitic inductance;</li> <li>Structure symmetry;</li> <li>Double-sided cooling.</li> </ul>                                                                                                                        |

| Wafer-level package [46]               | Power devices and metallic lead frame are bonded by a solderless, thermocompression process.                                                                                                                                                                                            |

| Micro-post-based<br>sandwich [47]      | <ul> <li>Double-sided cooling;</li> <li>Micro-posts on the top of power dies can be performed at wafer level;</li> <li>Micro-posts can compensate for thickness differences between the dies.</li> </ul>                                                                                |

| Switching cells-based package [48]     | Reduction in the physical length of commutation<br>loop. The parasitic inductance reduction of the<br>layout design was in the range of 5-10 nH.                                                                                                                                        |

was 300 A, the voltage rise time was 11.2 ns, and voltage overshoot was below 28% [50].

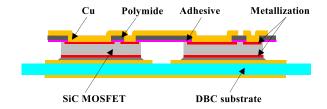

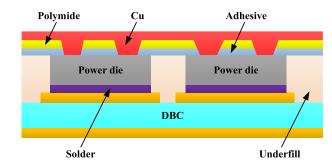

In 2018, they presented a power overlay kiloWatt (PO-kW) for SiC power module. The schematic of a typical POL-kW module structure is shown in Fig. 27. Cu vias were used as interconnects between dies (Al pads) and routings on the polyimide film surface. The adhesive layer was used to attach dies to the polyimide film. Cu vias were formed by laser drilling and subsequently filled by electroplating. DBC substrate (Ni/Au finish) was soldered to the die backside metallization (Ag finish). An underfill was applied for electrical isolation and mechanical strengthening. Compared with conventional wirebonded package, the utilization of polyimide-based Cu via interconnections resulted in much

Fig. 25. Double-side cooling packaging for SiC high-power inverter module.

Fig. 26. Schematic of POL interconnect package for SiC MOSFETs.

Fig. 27. Schematic of a typical POL-kW module structure.

reduced parasitic inductance, contributing to significantly lower switching loss and less voltage overshoot [51].

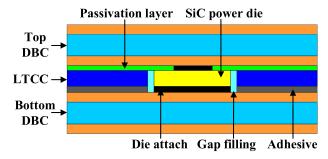

3) LTCC-Based Double-Sided Cooling Module: Zhang et al. [52] proposed a wirebondless SiC power module with a double-sided cooling capability. In this module, an LTCC substrate was used as a dielectric and chip carrier. Nano Ag paste was used to attach power devices to top and bottom DBC substrates as well as to pattern the gate connection. The top and bottom sides of DBC were plated with Ag on top of the 8-mil-thick Cu, and the subsequent layers of Cr/Ni/Ag were deposited on top of the anode of the diode, the source, and gate of the MOSFET through a liftoff process. To protect the power devices from electrical breakdown during operation, a high-temperature dielectric material was used to fill the gaps between the LTCC substrate carrier and the power devices. The cross section of the power module with double-sided cooling is shown in Fig. 28. Simulation results showed that the LTCCbased double-sided cooling module had the lowest junction to ambient thermal resistance compared to the embedded power and PBGA modules under similar operating conditions.

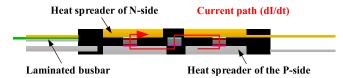

4) 6-in-1 Power Module: In order to reduce the inductance of wiring, magnetic cancellation effect was used. Fig. 29 shows the cross section of a 6-in-1 SiC power module with double-sided cooling. Heat spreader was utilized as magnetic cancellation. Laminated busbar had an insulation film between positive and negative terminals, in which current paths were in the opposite directions. Current paths between

Fig. 28. Cross section of LTCC-based double-sided cooling for SiC module.

Fig. 29. Current path and structure view of 6-in-1 power module.

Fig. 30. Structural view of PCoB power module.

the chips were also configured to be in opposite directions. A parasitic inductance of 7.5 nH was obtained [53].

5) Power Chip-on-Bus Structure: In [54], a double-sided air-cooled power chip-on-bus (PCoB) power module was proposed. Fig. 30 shows the structural view of PCoB power module. Thick finned Cu acted as both heatsink and busbar. Power dies were electrically attached to two busbarlike power substrates directly. Mo spacers were used as CTE buffer between the die and bottom substrate for reducing thermomechanical stress caused by CTE mismatch. Through extensive multiphysics simulation and verification, 0.5 °C/W thermal resistance and 8-nH power loop parasitic inductance were achieved.

### B. Press-Pack Packaging Technique

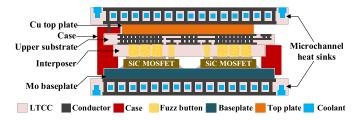

1) Press-Pack Packaging Solution Based on LTCC Interposer: Zhu et al. [55] proposed a press-pack packaging solution for SiC MOSFETs, as shown in Fig. 31. A pressure contact solution for SiC MOSFET die was developed using miniature and flexible press pins called "fuzz buttons" in a low-profile LTCC interposer. To minimize the loop parasitic inductance, ultrathin microchannel heatsinks were designed based on the LTCC technology. A phase-leg stack prototype with two press packs and three heatsinks was developed. According to the simulation results, the internal parasitic inductances of the press pack were less than 550 pH, and the parasitic inductance of a phase-leg stack formed by two press packs and three microchannel heatsinks was 4.3 nH at a frequency of 100 kHz.

Fig. 31. Press-pack packaging solution for SiC MOSFETs.

Fig. 32. Diagram of 3-D wirebondless switching cells.

### C. 3-D Packaging Technique

1) Chip Scale, Flip-Chip Capable Package: Seal et al. [56], [57] and Mantooth and Ang [58] developed a chip-scale wirebondless packaging technology for a SiC Schottky diode that led to lower parasitics, higher reliability, lower costs, and lower losses. The approach used a flip-chip solder ball array to make connections to the anode. A Cu connector was used to make contact with the bottom cathode, thus reconfiguring the bare die into a chip-scale, flip-chip capable device. Compared with conventional wirebonded package, a 24% reduction in ON-state resistance was observed in the wirebondless package. In 2018, they presented a 3-D wirebondless switching cell using SiC power devices, as shown in Fig. 32. In order to obtain a solderable finish, a very thin zinc seed layer was deposited on the top Al pads, followed by the electroless plating of a thick nickel layer. Double-pulse tests showed that over three times reduction in the parasitic inductance of the 3-D cell compared with a conventional wirebonded module [59].

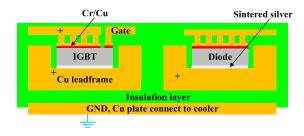

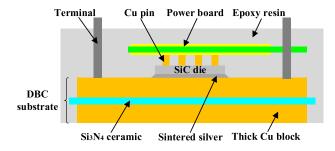

2) Cu Pin Connection Technology: Fuji Electric developed a Cu pin interconnection structure for SiC power module, as shown in Fig. 33. Conventional Al wirebonds, solder joints, and silicone gel encapsulating structures were replaced with Cu pin connections, Ag sintering joints, and epoxy resin molding structures, respectively. In order to further reduce thermal resistance, a much thicker Cu block was bonded to the silicon nitride (Si<sub>3</sub>N<sub>4</sub>) ceramic substrate. Compared with conventional alumina ceramic structure, the Cu pin structure enabled a 50% reduction in the thermal resistance of the overall structure. Compared with the conventional Si-based wirebonded package, the loss reduction with SiC devices was 57%–87% using the Cu pin structure [60], [61].

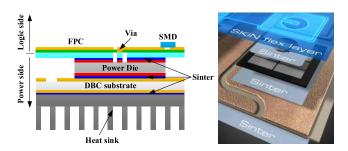

3) SKiN Interconnect Technology: SKiN technology comprises sintering of power chips to a DBC substrate, a top side sintering of the power chips to a flexible printed circuit (FPC), and sintering of the substrate to a pin-fin heat

Fig. 33. Package structure schematic of SiC power module with Cu pin.

Fig. 34. SKiN double-side sintering package.

sink, as shown in Fig. 34. This technology was first introduced in 2011 in [62]. Now, it has been used in a 1200-V, 400-A phase-leg SiC power module. The phase-leg power module with  $8 \times 50$  A SiC MOSFET chips in parallel had a total commutation parasitic inductance of less than 1.4 nH [63].

# D. Hybrid Packaging Technique

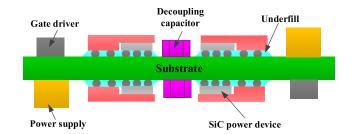

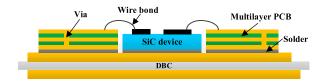

1) DBC and PCB Hybrid Structure: In [64], a DBC and PCB hybrid structure for SiC power module was developed, as shown in Fig. 35. A multilayer PCB with grooves was attached on the DBC substrate. SiC devices were fit in the grooves and attached on the DBC substrate. Bonding wires were then used to connect the top electrodes of the device to top Cu trace on the PCB.

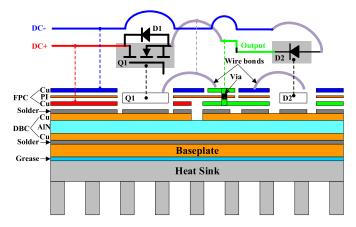

2) DBC and FPC Hybrid Structure: In [65], a 1200-V, 120-A SiC phase-leg power module based on DBC and FPC hybrid structure was proposed. Fig. 36 shows the DBC and FPC hybrid structure and the commutation loop associated with MOSFET (Q1) and diode (D2). Since the opposite currents flowed through the thin FPC board, the cancellation of the magnetic coupling effect was strong. The parasitic inductance of the power module could be significantly minimized to only 0.79 nH by using the thin FPC and proper layout design. Compared with the commercial module, voltage overshoot of the hybrid structure module was decreased by about 50%, and switching energies were only one-third of the commercial module under the same decoupling capacitors and driving conditions.

Up to date, several packaging technologies for SiC power module have been developed. Although some similar packaging schemes for Si-based power module has also been explored, requirements on parasitic inductance and heat dissipation for SiC power module package are more stringent. There exist challenges in the packaging of SiC power modules

Fig. 35. Cross-sectional view of DBC and PCB hybrid structure.

Fig. 36. DBC and FPC hybrid structure.

due to unique features of the newly developed modules, e.g., high-speed and high-frequency switching. Comparison among these packaging schemes for SiC power module is listed in Table III.

# V. CHALLENGES OF PACKAGING TECHNIQUES FOR SIC POWER MODULE

Compared with Si counterparts, SiC MOSFETs have faster switching speed, smaller form factor, and lower switching loss and can realize higher switching frequency and efficiency. In the same power module package, however, superior properties of a SiC MOSFET cannot be exploited if it is used simply as a direct replacement of Si device [64]–[66]. These features of SiC MOSFETs pose substantial challenges to packaging of SiC power module, e.g., fast switching speed and heat dissipation. Developing novel packaging technique needs to face several challenges, e.g., material selection and packaging process. Once a new package is developed, module characterization is also a challenge. These issues must be handled more carefully in the SiC MOSFET power module packaging design.

# A. Fast Switching Speed

A comprehensive comparison between Si IGBT and SiC MOSFET with the same power rating was performed in [67]. The selective devices are from Infineon's third-generation Si IGBT IKW15N120H3 and Cree's SiC MOSFET C2M0080120D. The quantitative *dv/dt* and *di/dt* values of the two devices are shown in Table IV. As seen in Table IV, SiC MOSFET switches much faster than Si IGBT. Due to fast switching speed capability, switching characteristics of SiC MOSFET are more susceptible to parasitic elements,

TABLE III

COMPARISON AMONG THE EXISTING PACKAGING SCHEMES FOR SiC

POWER MODULE

| Packaging scheme                        | Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5 5                                     | Double-sided cooling with flip-chip and clip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Miniaturized double                     | bonding;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| side cooling [49]                       | Withstand high temperature over 220 °C;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| side cooming [49]                       | • 2 times enhancement in thermal dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                         | performance is achieved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| POL [50]-[51]                           | • Wire-bonds are replaced with flexible substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| LTCC based                              | <ul> <li>Double-sided cooling;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| double-sided cooling                    | • LTCC interposer is used as dielectric and chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| [52]                                    | carrier;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                         | Parasitic inductance of 3.3 nH is achieved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 6: 1.5523                               | Double-sided cooling;     Magnetic annual trian offset is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 6-in-1 [53]                             | Magnetic cancellation effect is used;      Pagnetic industry as a 6.7.5 p.H. is abtoined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |