# Review of Power Module Automatic Layout Optimization Methods in Electric Vehicle Applications\*

Puqi Ning<sup>1, 2</sup>, Huakang Li<sup>1, 2</sup>, Yunhao Huang<sup>1, 2</sup> and Yuhui Kang<sup>1\*</sup>

(1. Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing 100190, China;

2. School of Electronic, Electrical and Communication Engineering, University of Chinese Academy of Sciences,

Beijing 100049, China)

Abstract: The layout of power modules is a crucial design consideration, especially for silicon carbide devices. For electrical layout, optimizing the parasitic parameters can improving switching loss and dynamic behavior. For thermal layout, reducing the thermal resistance and controlling thermal capacitance can reduce the local hot point. Conventional layout design iterations are based on human knowledge and experience. But the major drawback of manual design methods is a limited choice of candidates, large time consumption and also the lack of consistency. With the introduce of automatic layout design, these challenges can be overcome which in the meanwhile alleviates current and temperature imbalance. By reviewing element representation, placement, routing, fitness evaluation, and the optimization algorithm approaches, a state-of-the-art power module layout design method for electric vehicle applications is introduced.

Keywords: Automatic layout design, power modules, optimization method

#### 1 Introduction

In an electric vehicle (EV), the motor drive is a core power conversion component, which requires high speed switching and low on-resistance power devices. The performance requirements and cost constraints promote the development of Si and SiC devices, as well as module packaging layout and design methods [1-2].

Momentous power module layouts for different power ratings have been proposed [3]. Several of these power module layouts exhibit appropriate electrical, thermal, and mechanical performance and are sufficiently compact to fit in the limited space in motor drives. Hence, research focus is not only on inventing new layouts and structures, but also on developing novel layout optimization methods. With the super calculation abilities of computers, layout optimization can be faster, more reasonable, and meet all types of

requirements.

From the electrical layout standpoint, parasitic parameters in a power module adversely affect switching loss and dynamic behavior <sup>[4]</sup>. Smaller parasitics can mitigate voltage overshoot, lower device voltage rating, and reduce device switching losses. In the compact power module for EV applications, high integration reduces space and distance, which may increase coupling between different current paths. To ensure high efficiency and high performance, effort is required to reduce parasitics and maintain balance between paralleled devices <sup>[5-6]</sup>.

From the thermal layout standpoint, the switching frequency enlarges the distribution unbalance of the junction temperature <sup>[7]</sup>. By reducing the thermal resistance and controlling thermal capacitance, the magnitude of the local hot point can be reduced. Furthermore, the thermal resistance between paralleled devices needs to be balanced as it contributes to both equal current distribution and temperature uniformity, enhancing the performance of the entire module.

Recently, to further reduce parasitic parameters and enhance thermal management, numerous advanced packaging structures have been designed and developed

Digital Object Identifier: 10.23919/CJEE.2020.000015

Manuscript received July 16, 2020; revised August 5, 2020; accepted September 1, 2020. Date of publication September 30, 2020; date of current version September 7, 2020.

<sup>\*</sup> Corresponding Author, E-mail: kangyuhui@mail.iee.ac.cn

<sup>\*</sup> Supported by the National Key Research and Development Program of China (2016YFB0100600) and the Key Program of Bureau of Frontier Sciences and Education, Chinese Academy of Sciences (OYZDBSSW-JSC044).

for products. Most of these packaging use planar structures, in which the device topside is interconnected directly to copper traces, a copper strip, or flexible conductors. Simultaneously, layout optimization methods for these planar packages have been invented and reported <sup>[5]</sup>.

Over the last two decades, SiC devices have emerged as an attractive alternative to Si devices, possessing various electrical and thermal advantages <sup>[8]</sup>. For EV applications, 900-1 700 V SiC MOSFET chips and SiC SBD chips have been successfully developed, and they demonstrate high switching frequencies and high-temperature capabilities <sup>[9-10]</sup>.

However, the current rating for a 1 200 V SiC die is usually limited to 100 A at 150 °C, considering the current manufacturing capability and cost <sup>[11]</sup>. A regular 1 200 V/600 A hybrid pack drive module requires a minimum of 36 SiC MOSFETs. For enhanced performance, an additional 36 SiC diodes would be added to the module. Careful layout design and optimization are required to balance current sharing and junction temperature <sup>[4]</sup>.

Conventional layout design iterations are based on human knowledge and experience. In most of these designs, the devices, power terminals, copper traces, and wire bonds are set as the basic elements. Elements are purposely placed, following all constraints, using a trial-and-error procedure. In some cases, the routing processes are also implemented via the placement processes. In other cases, routing and placement are two distinct processes, with only dies and terminals placed initially, followed by interconnecting with copper traces or wire bonds. Subsequently, using finite element analysis (FEA) or other calculation methods, the electrical parasitic parameters and thermal performance of the designed candidate is evaluated [12-13]. With similar steps and iterations, after comparing several candidates, the best candidate in the group is selected for further study.

In most of the relevant studies in the literature, manual designs are based on an enumeration algorithm, and the number of design candidates is seldom over 30. There is still no figure of merit that can determine the best layout design with a limited trial number. Therefore, the major drawback of manual design methods is a limited choice of candidates and large time consumption. Furthermore, human-experience-based design lacks consistency [3,11].

To overcome these challenges, over the past two decades, automatic layout design methods have been proffered and studied. These can be classified as semi-automatic or fully automatic methods. For semi-automatic methods, either the element positions are fixed and the routing is designed by a computer, or each element has a one-dimensional variable and can move only horizontally or vertically. In these designs, layout variations are less flexible, and the layout optimization space cannot be thoroughly searched.

In a fully automatic layout design, all element positions are unfixed, and they do not need to follow any predefined path. In some methods, human experience can be incorporated in the design as a constraint. The design space can be further reduced by following manufacturability rules and cost limits.

Several automatic layout design methods became mature in the last five years and have already achieved crucial cost savings in power module design. They can automatically perform advanced model abstraction, electrical parasitic extraction, and thermal analysis and automatically generate design candidates using geometry-dependent optimization models. Several concepts have been proposed to provide solutions to automatic design challenges, such as symbolic systems, layout languages and virtual grids. With degradations and simplifications, it becomes a problem of minimizing or maximizing the fitness of a complicated arrangement of several objects in constrained and aligned planes [14].

This review introduces the main procedures and concepts in automatic layout design. In section 2, the core optimization aspects are reviewed. Element representation is reviewed in section 3, element placement in section 4, and routing in section 5. Fitness evaluation and optimization algorithms are reviewed in sections 6 and 7, respectively, and future perspectives are discussed in section 8.

# 2 Core optimization aspects

An optimization problem involves three primary aspects: important design variables, fitness evaluation and constraints. The important design variables (also called decision variables) can be selected by a human or a computer for each design candidate and can be chosen arbitrarily under certain constraints. In the layout design of a power module, the

three-dimensional (3D) physical variables are usually simplified and mapped onto a two-dimensional (2D) model to reduce complexity.

Conversely, constraints are restrictive conditions that must be satisfied to accomplish an acceptable design. The constraints may be geometrical, electrical, thermal, manufacturability related, or cost related. In power module design, e.g., very large scale integration (VLSI) design, the procedures of placement and routing are also required, with special evaluation steps<sup>[15]</sup>. The requirements for each aspect of optimization are listed in Tab. 1.

Tab. 1 Requirements for optimization aspects

| Aspect                         | Requirement                                                                                            |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Component                      | Easy coding and decoding, unique representation, and group of components simplified as one             |  |  |  |  |  |

| representation                 | element.                                                                                               |  |  |  |  |  |

| Constraints                    | Easily implemented in the design                                                                       |  |  |  |  |  |

| Placement method               | Fast and reasonable                                                                                    |  |  |  |  |  |

| Routing method                 | Fast and reasonable                                                                                    |  |  |  |  |  |

| Evaluation method Optimization | Fast evaluation speed with specific levels of accuracy.  Thoroughly search the design space in a short |  |  |  |  |  |

| method                         | time.                                                                                                  |  |  |  |  |  |

Building a layout design with 3D components while limiting geometric configurations is time consuming. To address these issues, element representation is required to handle 3D geometrical complexity using a regular 2D plane optimization approach. In the element representation step, a special DNA string can be formed and coded under the guidance of representation rules. These DNA strings should be easily usable in the placement, routing, and optimization steps.

All common technology constraints should be determined at the very beginning, e.g., minimum width, minimum spacing, minimum enclosure, and minimum extension. There may be many user-defined reliability constraints, such as terminal position, voltage dependent spacing, and current dependent trace width. These should be easy to implement in the design model.

The placement usually includes a coding and decoding procedure for interpreting the DNA string into a physical layout. Before element placement, layer information, namely layout area, element dimensions, material properties, ambient temperature, and switching frequency, should be used as input to facilitate coding and decoding [15].

However, element placement does not consider

the connection possibility for each electrical net. Therefore, an iterative checking process must be passed in the routing step. In some complicated layout cases, more than 85% of the placement solutions are immediately eliminated by routing failures <sup>[16]</sup>. Both placement and routing steps need to find reasonable solutions in a short time.

A fitness evaluation can be functions or simulations that provide the criterion for further optimization. For power module design, fitness is typically related to electrical performance, thermal performance, weight, cost, volume, efficiency, or a combination of two or more desirable attributes. In the fitness evaluation step, accuracy can be sacrificed slightly in some circumstances to expedite the process.

The optimization method is the algorithm that finds the conditions providing the maximum or minimum value for a special objective [17]. Furthermore, the optimization can be based on a single objective or multiple objectives. The basic requirement for an optimization algorithm is to thoroughly examine the design space in a short time, without sinking into the local optimum early in the process.

# 3 Element modeling

#### 3.1 Element representation

In the literature, the optimization procedure predominantly involves only the main elements of the power module, and the important design variables regularly employ a simplified encoded mapping (Tab. 2). For EV applications, partial discharge is not considered in most designs.

Tab. 2 The simplification of elements

| Item                  | Simplification method in element representation                                                       |  |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                       | process                                                                                               |  |  |  |  |  |  |

| Power switch          | Rectangle or point, in placement step                                                                 |  |  |  |  |  |  |

| Diode                 | Rectangle or point, in placement step                                                                 |  |  |  |  |  |  |

| Terminal              | Rectangle or point, in placement step                                                                 |  |  |  |  |  |  |

| Wire bond/metal strap | Line/area, or as part of the power device and transfer area, in placement step and/or in routing step |  |  |  |  |  |  |

| Direct bonding        | Line/area, in placement step and/or in routing                                                        |  |  |  |  |  |  |

| copper                | step                                                                                                  |  |  |  |  |  |  |

| Baseplate             | Omitted in the design                                                                                 |  |  |  |  |  |  |

| Encapsulant           | Omitted in the design                                                                                 |  |  |  |  |  |  |

| Housing               | Omitted in the design                                                                                 |  |  |  |  |  |  |

| Decoupling capacitor  | Rectangle or point, in placement step                                                                 |  |  |  |  |  |  |

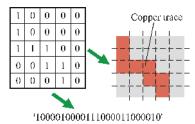

Because the shapes of devices and terminals are square or rectangular, the positions of devices can be interpreted via a matrix representing a grid layout region. The positions can then be transformed into single-dimensional vectors and expressed as integers.

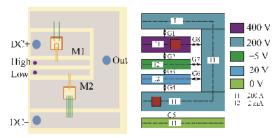

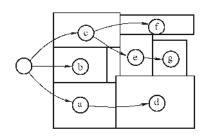

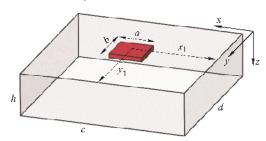

A study by Mouawad et al. <sup>[10]</sup> presents a physical-design-based simplification that retains flexibility and generates relatively detailed routing, as shown in Fig. 1. In the simplification, each component is represented as a single-type rectangle. It can represent all heterogeneous elements, with no limitation to the number of elements. Sherwani <sup>[18]</sup> and Nakaya et al. <sup>[19]</sup> employ a similar idea.

Fig. 1 Physical-design-based simplification

However, the DNA interpretations in these studies become very complicated when the number of dies in the power module is large (n>25). To expedite the placement and routing procedures, several studies use only three types of element: switches, diodes and power terminals [20].

In a wire bond package, wire bonds contribute to the largest impedance. They connect the top pads to the nearest copper traces. Therefore, the shortest and most feasible wire bonds are commonly used. Detailed wire bond connections do not require a special description in the DNA string. Instead, these details are considered in the subsequent evaluation step.

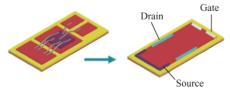

In a study by Ning et al. <sup>[3]</sup>, a combination of die, wire bond, and adjacently connected copper trace region was degraded and treated as one element, as shown in Fig. 2. In this simplification, pads of the device are extended as fringe terminals of the 2D element. This degradation significantly reduces placement and routing times <sup>[21]</sup>.

Fig. 2 Combined element

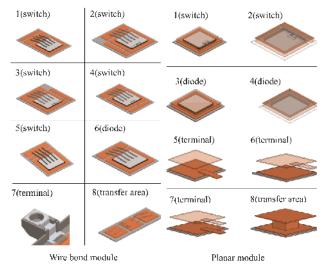

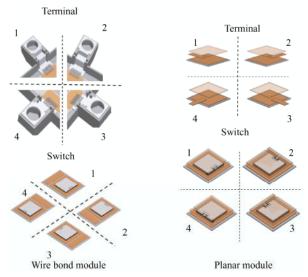

In a study by Hingora et al. [22], typical devices were

degraded and depicted for both wire bond package and planar package, as shown in Fig. 3. Subsequently, the positioning procedure speed was increased.

Fig. 3 Typical element representation

Shook et al. <sup>[5]</sup> provided a symbolic layout model (Fig. 4), which has three basic elements: lines, points and rectangles. Lines represent bond wires and copper traces. Points represent power devices, leads and terminals. Rectangles represent traces that span multiple traces vertically or horizontally, with topological definition. However, this model requires an additional complex coding procedure to generate DNA strings for further optimization.

Fig. 4 Symbolic layout model

### 3.2 Orientation

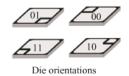

As shown in Fig. 5, pads on the die may not be in the center but may be on the edge or corner. Asymmetrically distributed pads restrict the direction of an interconnection, which is limited by the wire bond or copper trace fabrication process. In most cases, the orientation of interconnections is critical to parasitic reduction and parameter balancing. Therefore, the orientation

needs to be included to the DNA strings. In the study by Ning et al. <sup>[3]</sup>, the orientation of a die was represented by binary strings (00, 01, 10, 11), as depicted in Fig. 5.

Fig. 5 Orientation definition

To expedite placement and routing, combined element orientations for a wire bond package and a planar package were depicted in a study by Hingora et al. <sup>[22]</sup>, as shown in Fig. 6. In a planar package module, elements can be described using z axis orientation to indicate the upward and downward facing directions.

When considering the product style of a power module in EV applications, the orientation of the power terminal always faces outward from the edge. Thus, the terminal orientations in a 2D layout plane can be reduced from four to one. The transfer area can be formed in the subsequent routing step, if required. With these simplifications, the orientation string of a planar module is reduced to i+3j+k, for i power terminals, j switches and k diodes.

Fig. 6 Combined element orientation

# 4 Element placement

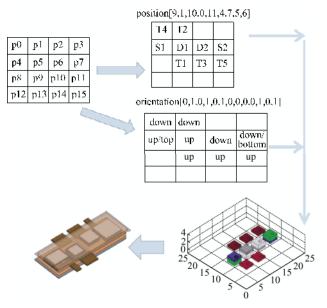

The element placement step generates an abstract layout representation (symbolic layout). This symbolic layout usually consists of points, lines, or blocks, representing chips, terminals and traces. Typically, the layout coordinates are normalized. Subsequently, each

component is stamped into a vector sequence or DNA string, with the representation rules introduced in section 3, which effectively update the trace dimensions and component locations in the optimization process. A placement example is presented in Fig. 7.

Fig. 7 Example of placement

The placement step in power module layout design is resembles the floor plan step in VLSI layout design. To expedite the design procedure and reduce the datum size, a placement is a data structure capturing relative positions rather than fixed coordinates. A placement can be interpreted as a non-overlapping arrangement in the plane, by deciding the position of each component relative to the position of others <sup>[15]</sup>. It is thus desirable to develop an efficient, effective, and flexible coding and decoding method to describe the geometric relationship between elements in placement designs.

There are basically two categories in placement: slicing-based and packing-based [19]. The slicing-based floor plan repetitively subdivides rectangles vertically or horizontally into smaller rectangles, thereby representing each rectangle as an element in the power module. The packing-based methods use compacted structures to emulate the packing procedure in a fabric [23]. In a packing-based placement, first, one element is fixed to a corner of a layout region, e.g., the bottom-left corner, and other modules can be shifted further to the top or right. These methods can model only partial topological information. Module dimensions, orientation, and distance need to be added to the DNA strings to construct an exact placement.

Compared with packing-based methods, the size of each rectangle in the slicing-based methods cannot be controlled easily. In power modules, the numbers and types of elements are much smaller than in VLSI designs. Because the dimension of each type of element is determined at the beginning, slicing-based methods are rarely used in power module layout design [15, 18-19].

## 4.1 Relative position

In the layout optimization iterations for power modules, the representations of elements are the most critical key to effectively solving a problem. In a regular data structure for packing-based placement, let  $B=[b_1, b_2, \dots, b_m]$  be a set of m rectangles, with width, height, and orientation denoted by  $w_i$ ,  $h_i$  and  $r_i$  respectively;  $1 \le I \le m$ . Let  $(x_i, y_i)$  denote the coordinates of the bottom-left corner of rectangle  $b_i$ ;  $1 \le i \le m$ . A placement representation P is an assignment of  $(x_i, y_i)$  for each  $b_i$ , such that no two modules overlap.

The most commonly used compacted placement representations in power module layouts are O-tree, B-tree, sequence pair (SP), and adjacent constraint graph (ACG) <sup>[5]</sup>. Other methods, such as corner sequence (CS), bounded slice line grid (BSG), transitive closure graph (TCG), and transitive closure graph with a sequence (TCG-S), have their unique benefits and are awaiting further research <sup>[24-25]</sup>.

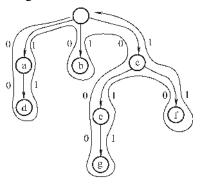

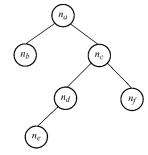

An O-tree is a root ordered tree structure, and each node has several branches. An O-tree can be horizontal or vertical, and they use similar definition. In a horizontal O-tree, the root represents the left boundary of the placement. The children are placed adjacent to their parent on the right, with their y coordinate equal to that of the parent. The children are placed adjacent to their siblings at the top, with their x coordinate equal to that of the siblings. In the branching structure, 0 represents a traversal that descends an edge, and 1 means the traverse subsequently ascends that edge in the tree. An example is depicted in Fig. 8, with the branching (00110100011011, adbcegf) presented in Fig. 8a and the decoded placement in Fig. 8b.

B-trees were proposed by Zhu et al. [16] and are based on ordered binary trees and admissible placements. The root in a B-tree corresponds to the elements at the bottom-left corner. The left child is placed adjacent to the parent on the right, with its y coordinate equal to that of

the parent. The right child represents the lowest element, which is located above, and its x coordinate is equal to that of the parent. An example is depicted in Fig. 9, with the branching presented in Fig. 9a and the decoded placement in Fig. 9b.

(a) O-tree branching

(b) Decoded placement from O-tree Fig. 8 Example of O-tree

(a) B-tree branching

(b) Decoded placement from B-tree Fig. 9 Example of a B-tree

Hatta et al. [23] proposed the SP method, which is particularly suitable for stochastic algorithms, e.g., genetic

algorithms (GAs). The SP is a pair of sequences comprising n component names used to indicate the relative positions of n components (Fig. 10). For each pair of components, an SP imposes a horizontal/vertical (H/V) constraint. If two components have the same sequence in the horizontal and vertical sequences, the first component is to the left of the second component. If the horizontal and vertical sequences of the two components are different, the first component of the horizontal sequence is above the second component. An example is depicted in Fig. 10.

$$(<...a...b...>, <...a...b...>) \Rightarrow a$$

is to the left of  $b$  Horizontal  $(<...a...b...>, <...b...a...>) \Rightarrow \sigma$  is above  $b$  Vertical  $(123, 231) \longrightarrow 13$ ,  $31 \longrightarrow 1$  is above  $3$  23,  $23 \longrightarrow 2$  is on the left of  $3$  Example for  $3$  components

Fig. 10 Example of a sequence pair

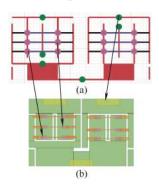

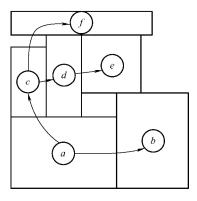

For power module layouts, Al et al. <sup>[26]</sup> expanded the data structure of corner stitching using the ACG. The corner stitching structure has solid and vacant elements, which is obtained by partitioning the layout area into horizontally maximal rectangular tiles. Each tile contains four pointers to preserve neighboring information, with two top-right and two bottom-left corner position pointers <sup>[27]</sup>.

In a constraint graph, the nodes represent elements, the edges of the horizontal graph represent the relation "left of", and the edges of the vertical graph represent the relation "below". The adjacent graph is an undirected graph and has one edge between each pair of adjacent elements. An ACG is a combination of a constraint graph and an adjacent graph, as shown in Fig. 11.

Fig. 11 Example of corner stitching and an ACG

With an ACG, the placement area and element positions can simply be found using longest path computations. Furthermore, it is unnecessary to add extra data in the DNA string for white space.

# 4.2 White space considerations

Minimizing area is a conventional key objective of power module layout design. However, it is insufficient for the fitness evaluation step. In a power module, the placement must contain some white space (empty room) to mitigate impossible routing issues <sup>[28]</sup>. If there is plenty of white space within the layout area, a reasonable and high-quality routing solution can be expected.

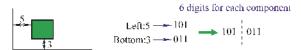

In most packing-based placement, gaps are added between elements to retain sufficient white space. Wu et al. <sup>[2]</sup> define the gap as the distance from the bottom-left corner of a component to the left or bottom boundary. To reduce infinite layout candidates, a minimum distance between elements must be set, e.g., 1 mm, 0.5 mm, or 0.1 mm. The gaps between elements are usually represented by decimal strings and binary strings (Fig. 12). In the example in Fig. 12, the horizontal gap is five, and the vertical gap is three, all represented by 3-bit binaries.

Fig. 12 Gap representation example

# 5 Routing method

The routing step connects elements using wire bonds, copper traces, and copper straps under certain constraints. Typical constraints include: following the electrical topology connection of the power module, avoiding meandering paths, and minimizing the lengths of critical nets.

Power module routing methods usually operate in a two-phase mode <sup>[3]</sup>. At the beginning, a coarse routing is performed to match the electrical topology. A punishment is directly assigned to the fitness if a placement data set cannot be routed at all. In the second phase, based on the coarse rouging result and enlargement methods, a detailed routing is performed in which the final interconnection is formed among the elements.

Two routing phases can use the same grain grid

structure. This grain grid can borrow from placement and can be further used in electrical evaluation and thermal evaluation. Interconnection in routing is assumed to have widths that meet the design rules and are adequately separated from adjacent connections and elements.

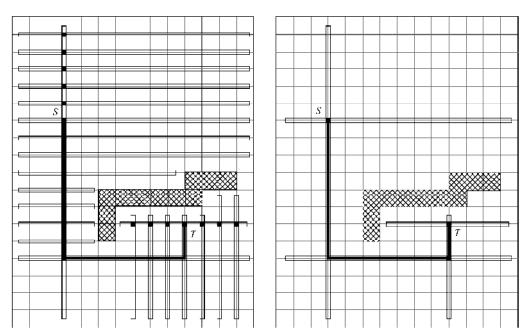

An example is presented in Fig. 13. After element representation, the routing problem is reduced to a two-dimensional copper wire connection problem. A 1×1 mm grid was used in this example to substitute the routing area. 1 represents a local copper trace and 0 represents the absence of a copper trace. A one-dimensional binary string was used to expedite subsequent crossover and mutation operations in a subsequent GA.

Fig. 13 Routing plane example

## 5.1 Single net routing

The most widely used routing methods in single

net circuits are the mazing and line search methods. They are introduced first for two-terminal routing and then used for coarse routing. Recently, they have been developed for multiple terminal connections and detailed routing.

For automatic wire routing, the mazing algorithm proposed by Lee is one of the earliest routing algorithms. The basic algorithm uses a uniform grid to operate on a single terminal network. In the grid, there are some device cells indicated as blockages.

An example is presented in Fig. 14. First, a wavefront is expanded from one of the elements, and neighboring cells of the element are labeled as 1. Then, at each step, the unlabeled neighbors of the cells labeled L are labeled as L+1. This process continues until the wavefront reaches the target element. Once the target is found, the shortest path is constructed using a backtracking method.

As an enhancement, the wavefront from both elements can be simultaneously expanded until two wavefronts meet, reducing routing time by approximately 30%-45%.

| 9  | 8  | 7  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |    |    | 9  | 8  | 7  | 6  | 7   | 8              | 9           | 10               | 11   | 12                | 13 | 14 |    |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----------------|-------------|------------------|------|-------------------|----|----|----|----|

| 8  | 7  | 6  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |    | 8  | 7  | 6  | 5  | 6   | 7              | 8           | 9                | 10   | 11                | 12 | 13 | 14 |    |

| 7  | 6  | 5  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 7  | 6  | 5  | 4  | 5   | 6              | 7           | 8                | 9    | 10                | 11 | 12 | 13 | 14 |

| 6  | 5  | 4  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 6  | 5  | 4  | 3  | 4   | 5              | 6           | 7                | 8    | 9                 | 10 | 11 | 12 | 13 |

| 5  | 4  | 3  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 5  | 4  | 3  | 2  | 3   | 4              | 5           | 6                | 7    | 8                 | 9  | 10 | 11 | 12 |

| 4  | 3  | 2  | l  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 4  | 3  | 2  | 1  | 2   | 3              | 4           | 5                | 6    | 7                 | 8  | 9  | 10 | 11 |

| 3  | 2  | 1  | S  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 3  | 2  | 1  | S  | l   | 2              | 3           | 4                | 5    | 6                 | 7  | 8  | 9  | 10 |

| 4  | 3  | 2  | _  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | Ш  | 4  | 3  | 2  | 1  | 2   | 3              | 4           | 5                | 6    | 7                 | 8  | 9  | 10 | 11 |

| 5  | 4  | 3  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 5  | 4  | 3  | 2  | 3   | 4              | 5           | 6                | 7    | 8                 | 9  | 10 | 11 | 12 |

| 6  | 5  | 4  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |    |    |    | 13 | 6  | 5  | 4  | 3  | 4   | 5              | 6           | 7                | 8    | 9                 |    |    |    | 13 |

| 7  | 6  | 5  | 4  | 5  |    |    |    |    |    |    |    | 15 | 14 | 7  | 6  | 5  | 4  | 5   |                |             |                  |      |                   |    |    | 15 | 14 |

| 8  | 7  | 6  | 5  | 6  |    | 12 | 13 | 14 | 15 | T  |    |    | 15 | 8  | 7  | 6  | 3  | 6   |                | 1 2-        | -l <del>-}</del> | -14- | -I <del>ş</del> - | T  |    |    | 15 |

| 9  | 8  | 7  | 6  | 7  |    | 11 | 12 | 13 | 14 | 15 |    |    |    | 9  | 8  | 7  | 6  | 7   |                | Įį.         | 12               | 13   | 14                | 15 |    |    |    |

| 10 | 9  | 8  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |    |    | 10 | 9  | 8  | 7- | -8- | <del>-9-</del> | <b>-1</b> 0 | 11               | 12   | 13                | 14 | 15 |    |    |

| 11 | 10 | 9  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |    |    |    | 11 | 10 | 9  | 8  | 9   | 10             | 11          | 12               | 13   | 14                | 15 |    |    |    |

| 12 | 11 | 10 | 9  | 10 | 11 | 12 | 13 | 14 | 15 |    |    |    |    | 12 | 11 | 10 | 9  | 10  | 11             | 12          | 13               | 14   | 15                |    |    |    |    |

| 13 | 12 | 11 | 10 | 11 | 12 | 13 | 14 | 15 |    |    |    |    |    | 13 | 12 | 11 | 10 | 11  | 12             | 13          | 14               | 15   |                   |    |    |    |    |

| 14 | 13 | 12 | 11 | 12 | 13 | 14 | 15 |    |    |    |    |    |    | 14 | 13 | 12 | 11 | 12  | 13             | 14          | 15               |      |                   |    |    |    |    |

Fig. 14 Mazing routing algorithm example

The first line search algorithms were proposed by Ulutal and Isliev <sup>[29]</sup>. As shown in Fig. 15, initially, the algorithm expands one horizontal and one vertical line segment for every source and target point. Then the process continues iteratively

until one source point line segment intersects with one target point line segment. Once they meet, the path is constructed by backtracking from the intersection point to the source and target points [29].

Fig. 15 Line searching routing algorithm example

Multiple terminal routing is an upgraded version of two-terminal routing. A practical approach is to apply the routing algorithm iteratively. Typically, wave expansion starts from a source terminal until a target terminal is reached. Subsequently, the route between these two terminals is regarded as a new source of the wave expansion. When all terminals in the net are routed, this process ends.

After a coarse routing, a detailed routing can be conducted by filling the empty grid. The filling procedure can be a random generation with further checking [30], or growing from coarse routing with certain rules and limits [31]. In a study by Wong et al. [32], nearly 10% of the nets were routed using pure coarse routing, and the rest were executed with detailed routing. However, approximately 73% of the routing time was spent on coarse routing.

# 5.2 Multiple net routing

Phase-leg modules and multi-phase modules require routing multiple nets concurrently, and the routing solution for one net may potentially impact other nets. The routing methods for multiple nets can be divided into two categories: sequential routing and concurrent routing.

Sequential routing is a straightforward approach, but nets routed in the later iterations may be forced to form relatively low-quality connections. With this approach, selection of the routing order is very sensitive. To solve this problem, the order selection is built into DNA strings in some optimizations.

Concurrent routing can be formulated as a multi-commodity flow problem. A flow network can be modeled based on the layout condition, with each edge in this network having a specific flow capacity and cost. A commodity transports over this network corresponding to each net. The multi-commodity flow problem can be solved as finding a flow for each commodity, while satisfying all flow capacity constraints from the edges in the network.

#### 6 Fitness evaluation method

All fitness evaluation methods must provide a high prediction accuracy with an acceptable computational speed. For power modules in EV applications, most evaluations in layout design are focused on electrical and thermal performance. Mechanical evaluations are typically from a package material and module structure standpoint.

## 6.1 Electrical evaluation

In the early layout design method, design candidates are evaluated using finite element method (FEM) software, such as Ansys. It can achieve high accuracy, but needs to update the geometry for each candidate [33]. Another drawback is the simulation speed; it will take approximately three years for one million candidates in a regular layout optimization [34].

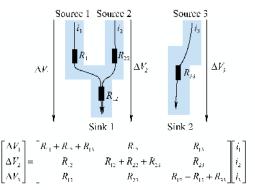

Another commonly used method is the partial element equivalent circuit, which has slightly more simulation error, but can reduce the simulation time considerably. Xia et al. <sup>[1]</sup> introduced a method for calculating the parasitic resistance matrix based on the voltages and currents. An example is presented in Fig. 16 <sup>[28]</sup>.

Fig. 16 Method for calculating the parasitic resistance matrix

where  $R_{11}$ ,  $R_{22}$  and  $R_{33}$  are the self-resistance of each current path,  $R_{12}$ ,  $R_{13}$  and  $R_{23}$  are the mutual resistance. In the next step, the magnetic vector potential is calculated based on the current of each element, which is given by

$$A = \frac{\mu_0}{4\pi} \sum_{V} \frac{J}{r} \tag{1}$$

where A is the magnetic vector potential; J is the current density, i.e., the current value in the element area;  $\mu_0$  is the vacuum permeability. The inductance matrix can be calculated as

$$\boldsymbol{L}_{ij} = \sum_{V_i} \boldsymbol{A} \cdot \boldsymbol{J}_j \tag{2}$$

where i and j are current paths. Thus, the primary parasitic resistance and inductance are calculated.

To increase the simulation speed, layouts can be divided into lumped elements. Each element is then approximated by micro-strip transmission line equations. Fig. 17 presents an example of element division in which the network was evaluated by traversing each trace segment.

Fig. 17 Micro-strip transmission line approximation

The length of each graph edge is measured and the segment trace width is used as the input of the transmission line equations <sup>[5]</sup>.

In the study by Zhang et al. [35], the evaluation is focused primarily on the commutation path. A straight line connecting the terminals facilitates the commutation path forming a closed loop. In the design, mutual inductance is neglected, considering only self-inductance. The primary optimization objective is to control the commutation loop size, and its inductance is expressed as

$$\lambda = C \cdot \ln(S) - l \cdot \left[ \ln(2l) - 1 \right] \tag{3}$$

where l (mm) is the length of the conductor, C is the perimeter of the loop, and S (mm<sup>2</sup>) is the area of the loop.

To further increase the optimization speed, the surrounding areas can be used to represent the inductance of the commutation path. Zhang et al. [35] introduced a planar module case. The 3D commutation area was first divided into n triangles. The inductance is the addition of individual areas. If the corner point of a 3D triangle is  $A(x_1, y_1, z_1)$ ,  $B(x_2, y_2, z_2)$  and  $C(x_3, y_3, z_3)$ , the area of the triangles is then computed as

$$S = \frac{1}{2} \sqrt{\begin{vmatrix} y_2 - y_1 & z_2 - z_1 \\ y_3 - y_1 & z_3 - z_1 \end{vmatrix}^2 + \begin{vmatrix} z_2 - z_1 & x_2 - x_1 \\ z_2 - z_1 & x_3 - x_1 \end{vmatrix}^2 + \begin{vmatrix} x_2 - x_1 & y_2 - y_1 \\ x_2 - x_1 & y_3 - y_1 \end{vmatrix}^2}$$

(4)

#### 6.2 Thermal evaluation

The conventional method for evaluating the thermal performance of a layout candidate is the finite volume method (FVM) using computation fluid dynamics (CFD) software. Resembling FEM in electrical simulations, FVM takes a long time to evaluate candidates. Particularly, when considering convection performance, the Stokes' theorem equation needs to be solved.

In a study by Zhong et al. <sup>[8]</sup>, a modified partial differential equation was introduced to solve thermal equations for a power module with a pin-fin or plate-fin heat sink in less time. Eqs. (5) and (6) present the discretization formulas.

$$C_{v}\Delta x \Delta y \Delta z \frac{T}{t} - k \frac{T_{i+1,j,k} - 2T_{i,j,k} + T_{i-1,j,k}}{\Delta x^{2}} - k \frac{T_{i,j+1,k} - 2T_{i,j,k} + T_{i,j,k-1}}{\Delta x^{2}} = \stackrel{\bullet}{q} \Delta x \Delta y \Delta z$$

(6)

$$C_{y}\Delta x \Delta y \Delta z \frac{T}{t} - k_{xx} \frac{T_{i+1,j,k} - 2T_{i,j,k} + T_{i-1,j,k}}{\Delta x^{2}} - k_{yy} \frac{T_{i,j+1,k} - 2T_{i,j,k} + T_{i,j-1,k}}{\Delta y^{2}} - k_{zz} \frac{T_{i,j,k+1} - 2T_{i,j,k} + T_{i,j,k-1}}{\Delta z^{2}} + C_{y}u_{y}\Delta A_{y}(T_{S2} - T_{S1}) = \dot{q}\Delta x \Delta y \Delta z$$

where T is the temperature of the control volume; k is the thermal conductivity of the material;  $\dot{q}$  is the volumetric heat generation rate inside the volume;  $C_v$  is the volumetric specific heat of the material; (i, j, k) is the location of the node in the thermal grid;  $k_{xx}$ ,  $k_{yy}$ , and  $k_{zz}$  are the conductivity of the fluid;  $u_y$  is the average velocity of the fluid flowing through the cell in the y direction;  $\Delta A_y$  is area of the fluid cell in y direction;  $T_{S2}$  and  $T_{S1}$  are the surface temperatures of the back and front faces, respectively. With further simplification and calculation, a 3D thermal impedance network is obtained, which can be used to evaluate multi-chip modules [36].

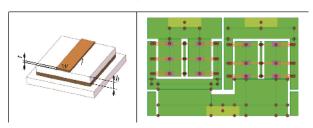

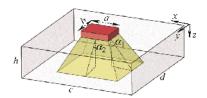

To increase the simulation speed, Zhu et al. [37] used stacked thermal block simplification. As shown in Fig. 18, the block emulates a die and is set as the heat source. a and b are the length and width, respectively, of the heat source, c is the length, d is the width of the block, and h is the thickness of the block.

Fig. 18 Stacked thermal block

The calculation equation is presented as Eq. (7)

$$\begin{cases} T(x,y,z) = A_0 + B_0 z + \sum_{m=1}^{\infty} \cos(\lambda_m x) [A_1 \cosh(\lambda_m z) + B_1 \sinh(\lambda_m z)] + \\ \sum_{n=1}^{\infty} \cos(\delta_n y) [A_2 \cosh(\delta_n z) + B_2 \sinh(\delta_n z)] + \\ \sum_{m=1}^{\infty} \sum_{n=1}^{\infty} \cos(\lambda_m x) \cos(\delta_n y) [A_3 \cosh(\beta_{mn} z) + B_3 \sinh(\beta_{mn} z)] \\ m, n = 1, 2, 3, \cdots \\ \lambda_m = \frac{m\pi}{d} \quad \delta_n = \frac{n\pi}{c} \quad \beta_{mn} = \sqrt{\lambda_m^2 + \delta_n^2} \end{cases}$$

$$(7)$$

where  $A_j$  and  $B_j$  are coefficients determined by the material and layers. When there are multiple heat sources, the temperature can be calculated as

$$T(x, y, z) = \sum_{i=1}^{n} T_i(x, y, z)$$

(8)

To expedite these equations for power modules with numerous dies, a further simplified thermal evaluation method was proposed by Zhu et al. [37] (Fig. 19).

Fig. 19 Cone model for thermal evaluation

$$R_{th} = \frac{1}{h_{t}} \int_{0}^{h} \frac{dz}{(a + 2z \tan \alpha_{1})(b + 2z \tan \alpha_{2})}$$

(9)

$$C_{th} = \rho c_v \int_0^h (a + 2z \tan \alpha_1)(b + 2z \tan \alpha_2) dz \qquad (10)$$

$$\alpha = \begin{cases} 5.86 \ln(\lambda) + 40.4 & \lambda \le 1\\ 46.45 - 6.048 \lambda^{-0.969} & \lambda > 1 \end{cases}$$

(11)

$$\lambda = \frac{h}{a} \tag{12}$$

where  $R_{th}$  is the thermal resistance,  $C_{th}$  is the thermal capacitance, a and b are the length and width, respectively, of the heat source, d is the width of the block,  $h_k$  is the thermal conductivity of the baseplate,  $\alpha_1$  and  $\alpha_2$  are the angles in the lengthwise direction and the widthwise direction, respectively,  $\rho$  is the density of the baseplate,  $c_v$  is the specific capacitance of the baseplate, and h is the thickness of baseplate.

# 7 Optimization algorithm

In the layout literature, several optimization methods are proposed. Some of these methods are based on classical methods, such as the sequential unconstrained minimization method, the augmented Lagrangian method, the Newton-Raphson method, and the successive quadratic programming algorithm method.

However, these methods do not appropriately solve complex layout optimization problems. As the complexity of the problem increases (especially when position and connection are not fixed), more complicated optimization techniques are required [38]. Metaheuristic methods emerged and have been developed to solve these issues.

There are two categories of metaheuristic optimization methods: trajectory-based and population-based. The main difference is the number of tentative solutions used in each step of the iteration. A

trajectory-based method majorly consists of hill climbing, tabu search, simulated annealing, and other explorative local search methods. They usually start with an initial solution, and the solution of each step is replaced by the best solution found around it. Trajectory-based methods take a longer time to find the global optimum but are not easily trapped in local optimal solutions. Due to the speed consideration, only a few power module layout optimizations use these methods.

Population-based metaheuristic algorithms (PMA) primarily include evolutionary algorithms, swarm intelligence, and neural networks. They use a set of solutions in each iteration step. The initial population is randomly generated and then enhanced through subsequent iterations. For each step, some members in the population are replaced by newly created individuals. Most of the time, the characteristics of new individuals have a relationship with old ones and have better fitness. Population-based methods show better performance than global optimization and have attracted significant attention in recent years. Tab. 3 outlines the studies that have used these classical methods and metaheuristic algorithms.

Tab. 3 Metaheuristic optimization methods

| Method              |                      | Option                 |                            | Literature<br>References |

|---------------------|----------------------|------------------------|----------------------------|--------------------------|

| Classical<br>method |                      | _                      |                            | [39-42]                  |

|                     | Trajectory-based     | _                      | _                          | [37, 43-44]              |

|                     |                      |                        | Genetic<br>algorithm       | [45-46]                  |

|                     |                      | Evolutionary algorithm | Immune<br>algorithm        | [47]                     |

| Metaheuristic       |                      |                        | Clonal selection           | [48]                     |

| algorithm           | Population-<br>based |                        | Particle swarm             | [49-52]                  |

|                     |                      | Swarm intelligence     | Ant colony                 | [53-54]                  |

|                     |                      | genee                  | Bacterial foraging         | [55-56]                  |

|                     |                      | Hybrid<br>algorithm    | Social spider optimization | [57-58]                  |

# 7.1 Genetic algorithm

GAs are based on natural genetics and are a special evolutionary algorithm that utilizes techniques inspired by evolutionary biological mechanisms, such as inheritance, mutation, selection, and crossover. The GA is a stochastic search method that deals with population solutions, and each individual is generally

encoded in a problem-independent representation.

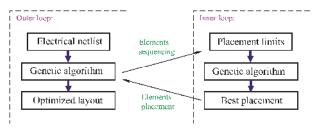

As shown in Fig. 20, Ning et al. [3] proposed a two-loops-based GA method. The outer loop is the element placement loop, and the inner loop is the routing loop. The element sequences of the first generation are randomly generated without overlap. Further, the DNA strings evolve to form a new generation [11] through crossover and mutation operations. When the optimization criteria are met, the algorithm terminates.

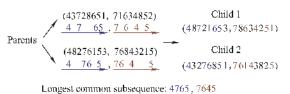

Fig. 20 Two-loop genetic algorithm

Crossover and mutation are the most important operations in the GA process. Conventional crossover and conventional mutation can be used in most cases. If the SP method is used in the element placement, a special operation is required, i.e., a common topology preserving crossover (CTPX). In a CTPX, the longest common subsequences (LCSs) of the parent SP are first determined. Then, elements in the LCSs are preserved in the same sequence, while other elements are exchanged, such that sequences of children are the same as parents. An example is presented in Fig. 21.

Fig. 21 Example of common topology preserving crossover

In the study by Ning et al. <sup>[3]</sup>, the optimized layout is obtained after 50 outer-loop iterations and a total of 3 982 inner-loop iterations, and the electrical performance is at least 30% better than that of other design candidates in the design procedure. In a study by Shen et al. <sup>[59]</sup>, a 15% thermal performance improvement was obtained after 100 generations of GA optimization.

## 7.2 Particle swarm optimization

Particle swarm optimization (PSO) is a

population stochastic optimization algorithm first developed by Eberhart and Kennedy [60], which is inspired by the behavior of birds. It has been used to solve numerous optimization problems for electrical engineering, e.g., parameter identification, maximum power point tracking of photovoltaic systems, and parameter optimization of hybrid electric vehicles. Some researchers have begun to use them in layout design [61].

In PSO, all particles follow the optimal particle to fly through the problem space. In each iteration, each particle accelerates toward its own best solution that it has found so far, and simultaneously, it accelerates toward the global best solution found so far by any particle in the group. When a particle discovers a promising new solution, all the other particles move closer to it, exploring the region more thoroughly. Through these steps, the global optimum can be determined, and local optimization traps are avoided.

During each iteration, each particle in the swarm is updated using a velocity update formula and a position update formula. Therefore, almost all the placement and routing methods can fit this algorithm without any special modification. In a study by Maharana and Mohanty [52], a PSO method was compared with a simulated annealing technique for layout area efficiency, area size and layout speed. The PSO shows absolute advantages in five group competitions [52].

#### 7.3 Hybrid algorithm

In a PMA, each individual has to decide whether to explore unknown positions or to exploit and improve tested positions. Pure exploration increases the capacity to find new potential solutions. However, pure exploitation may drive to local optimal solutions because it allows for refining existent solutions. Therefore, the capacity of a PMA to maintain a suitable balance between exploitation and exploration determines its ultimate performance. To meet this requirement, some hybrid algorithms have been introduced and used in electronic design. They possess the operations and benefits of both an evolutionary algorithm and a swarm-based algorithm [62].

Among these hybrid algorithms, the social spider optimization (SSO) algorithm is a typical algorithm.

Its members are divided in two categories: males and females. Individuals with different genders are conducted by a set of different evolutionary operators, which mimic the different cooperative behaviors. In the colony, each member does cooperative activities, e.g., maintain the communal web, prey capture, mating, and social contact. Mating is modified from GAs, and similarly, an SSO algorithm has crossover and mutation operations. Based on the division of the entire population into different categories and the selective use of specialized operators, it is possible to improve the balance between exploitation and exploration. The main differences between a genetic algorithm and a spider colony are listed in Tab. 4.

Tab. 4 Comparison of genetic algorithm and spider colony

| Features                | GAs               | SSO                                  |  |  |  |  |  |

|-------------------------|-------------------|--------------------------------------|--|--|--|--|--|

| Individual modification | Non               | Selectively changing                 |  |  |  |  |  |

| Individual vanish       | In crossover step | Anytime                              |  |  |  |  |  |

| Population size         | Fixed or increase | Fixed/increase/decrease              |  |  |  |  |  |

| Mating selection        | Stochastically    | Emulate the colony selection process |  |  |  |  |  |

| Gender                  | Unisex            | Can be male/female                   |  |  |  |  |  |

The SSO algorithm was applied to 19 functions and compared with PSO by Hu et al. <sup>[54]</sup> and Debnath et al. <sup>[45]</sup>. SSO delivered better results than PSO for all functions.

## 8 Future perspectives

The trend of using automatic optimization methods in power module layout design is related to the progress of the metaheuristic algorithm theory, progress in power device development, and EV application requirements. With the developments in optimization theory and computer technology, automatic optimization methods have come to florescence in electrical specializations such as VLSI design, circuit components selection, and control variable determination. They have been proved and have demonstrated fruitful results in power electronics. However, the power module layout design research domain is still relatively young and is a fast-growing area of research.

Multi-objective optimization (MOO) is a pivotal approach to fully exploiting the potential of automatic layout design. A power module layout needs to be

evaluated for electrical performance, thermal performance, weight, and volume. Most studies use cost functions, including electrical and thermal metrics, to generate a Pareto front for further selection. However, some studies experimentally demonstrate that the use of simple fitness aggregation methods with fixed weights does not yield satisfactory results <sup>[26]</sup>. In the near future, dynamic weight-based fitness aggregation methods will be required for MOO.

Another pivotal approach is the thermo-mechanical reliability analysis, which is a fast evaluation method that has been adopted in automatic design. In the early days of reliability optimization, it was majorly a purely statistical approach, like other component evaluations in the automotive industry <sup>[63]</sup>. However, it has shifted to a more physical-based approach that involves physical modeling and predicting failures. Cataliotti et al. <sup>[64]</sup> and Lu et al. <sup>[65]</sup> provide analytical methods for evaluating simple rectangle direct bonded copper (DBC). In the near future, mechanical formulas will be fully extended and applied in complex module design <sup>[64-65]</sup>.

Another important issue is heterogeneous components such as the capacitor, bus-bar, gate drivers, and EMI filters. Automatic layout design in power modules can be extended to explore a converter system solution space with enhanced searching ability flexibility. The representation heterogeneous components should consider 3D models, flexible rotation, and convex joints. The converter system or power assembly should be optimized with power modules simultaneously, thereby mitigating individual optimization weaknesses such determining the positions of terminals, plugs, and sockets [66].

## 9 Conclusions

To better utilize advanced power devices in EV applications, this study reviews the layout methods for power modules. With thorough optimization, packages can have lower parasitic parameters and lower thermal resistance, and both allow a comprehensive exploration of the actual capacity of a power module.

The core layout optimization aspects, element representation, placement, routing, evaluation, and optimization algorithm are introduced and discussed. Some practical considerations for different optimization aspects are also presented. The promising optimization results predict the prevalence of these layout methods and related software in the near future. The proven high performance of layout design will ensure the speedy development of power modules in EV applications.

#### References

- [1] X Xia, X Zhang, H Zeng, et al. A novel design of hybrid energy storage system for electric vehicles. *Chinese Journal of Electrical Engineering*, 2018, 4(1): 45-51.

- [2] X Wu, S Cheng, Q Xia, et al. A 3 600 V/80 A series parallel connected silicon carbide MOSFETs module with a single external gate driver. *IEEE Transactions on Power Electronics*, 2014, 29(5): 2296-2306.

- [3] P Ning, F Wang. Automatic layout design for power module. *IEEE Transactions on Power Electronics*, 2013, 28(1): 481-487.

- [4] Q Chen, X Yang, J Liu, et al. Practical design considerations for IPEM-based PFC converter employing CoolMOS and SiC diode. Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, 2006, Dallas, TX. APEC'06, 2006: 6.

- [5] B W Shook, A Nizam, Z Gong, et al. Multi-objective layout optimization for multi-chip power modules considering electrical parasitics and thermal performance. 2013 IEEE 14th Workshop on Control and Modeling for Power Electronics (COMPEL), 2013, Salt Lake City, UT. COMPEL, 2013: 1-4.

- [6] Q Tian, K Bai. Widen the zero-voltage-switching range and secure grid power quality for an ev charger using variable-switching-frequency single-dual-phase-shift control. *Chinese Journal of Electrical Engineering*, 2018, 4(1): 11-19.

- [7] Y Iwata, S Hayashi, R Satoh, et al. An efficient thermal design method based on boundary condition modeling. IEEE Transactions on Components Packaging Technologies, 2006, 29(3): 594-603.

- [8] X Zhong, X Wu, W Zhou, et al. An all-SiC high-frequency boost DC-DC converter operating at 320 °C junction temperature. *IEEE Transactions on Power Electronics*, 2014, 29(10): 5091-5096.

- [9] B Lu, W Dong, Q Zhao, et al. Performance evaluation of CoolMOS™ and SiC diode for single-phase power factor correction applications. *Eighteenth Annual IEEE Applied Power Electronics Conference and Exposition*, 2003, Miami Beach, FL, USA. APEC'03, 2003, 2: 651-657.

- [10] B Mouawad, A Hussein, A Castellazzi, et al. A 3.3 kV SiC MOSFET half-bridge power module. 10th International Conference on Integrated Power Electronics Systems, 2018, Stuttgart, Germany. CIPS, 2018: 1-6.

- [11] P Ning, X Weng, Y Li, et al. An improved automatic layout method for planar power module. *IEEE Applied Power Electronics Conference & Exposition*, 2016, Long Beach, CA, USA. APEC, 2016: 3080-3085.

- [12] J D V Wyk, F C Lee, Z Liang, et al. Integrating active, passive and EMI-filter functions in power electronics systems: A case study of some technologies. *IEEE Transactions on Power Electronics*, 2005, 20(3): 523-536.

- [13] Z Liang, B Lu, J D V Wyk, et al. Integrated CoolMOS FET/SiC-Diode module for high performance power switching. *IEEE Transactions on Power Electronics*, 2005, 20(3): 679-686.

- [14] C Alberto, F Asad, R Gianpaolo, et al. SiC power MOSFETs performance, robustness and technology maturity. *Microelectronics reliability*, 2016, 58(3): 164-176.

- [15] M Sarrafzadeh, C K Wong. An introduction to vlsi physical design. New York: McGraw Hill, 1996.

- [16] N Zhu, M Chen, D Xu. A simple method to evaluate substrate layout for power modules. 8th International Conference on Integrated Power Electronics Systems, 2014, Nuremberg, Germany. CIPS, 2014: 1-6.

- [17] E I Amoiralis, M A Tsili, D G Paparigas, et al. Global transformer design optimization using deterministic and nondeterministic algorithms. *IEEE Transactions on Industry Applications*, 2014, 50(1): 383-394.

- [18] N A Sherwani. Algorithms for VLSI physical design automation. Boston: Springer, 1993.

- [19] S Nakaya, T Koide, S Wakabayashi. An adaptive genetic algorithm for VLSI floorplanning based on sequence-pair. 2000 IEEE International Symposium on Circuits and Systems (ISCAS), 2000, Geneva, Switzerland. ISCAS, 3: 65-68.

- [20] S Nakatake, K Fujiyoshi, H Murata, et al. Module placement on BSG-structure and IC layout applications. Proceedings of International Conference on Computer Aided Design, 1996, San Jose, CA, USA. ICCAD, 1996: 484-491.

- [21] B Mirman, S Knecht. Creep strains in an elongated bond layer. *IEEE Transactions on Components Hybrids Manufacturing Technology*, 2002, 13(4): 914-928.

- [22] N Hingora, X Liu, B McPherson, et al. Concerning layout synthesis for power electronic multi-chip modules. 2010 IEEE 12th Workshop on Control and Modeling for Power Electronics (COMPEL), 2010, Boulder, CO. 2010,

- COMPEL, 2010: 1-5.

- [23] K Hatta, S Wakabayashi, T Koide. Solving the rectangular packing problem by an adaptive GA based on sequence-pair. Proceedings of the ASP-DAC '99 Asia and South Pacific Design Automation Conference 1999 (Cat. No.99EX198), 1999, Wanchai, Hong Kong. ASP-DAC'99, 1999, 1: 181-184.

- [24] P Guo, C Cheng, T Yoshimura. An O-tree representation of non-slicing floorplan and its applications. *Proceedings* 1999 Design Automation Conference (Cat. No. 99CH36361), 1999, New Orleans, LA, USA. DAC, 1999: 268-273.

- [25] T Lengauer. Combinatorial algorithms for integrated circuit layout. Wiesbaden: Springer, 1992.

- [26] R Al, Q Le, H A Mantooth. Constraint-aware algorithms for heterogeneous power module layout synthesis and reliability optimization. 2018 IEEE 6th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 05.17.2018, Xi'an Shaanxi, China. WiPDA, 2018: 323-330.

- [27] N Hingora, X Liu, Y Feng, et al. Mantooth power-CAD: A novel methodology for design, analysis and optimization of power electronic module layouts. 2010 IEEE Energy Conversion Congress and Exposition, 2010, Atlanta, GA. ECCE, 2010: 2692-2699.

- [28] P Zhang, X Wen, Y Zhong. Parasitics consideration of layout design within IGBT module. *2011 International Conference on Electrical Machines and Systems*, 2011, Beijing, China. ICEMS, 2011: 1-4.

- [29] B H Ulutal, A A Isliev. A clonal selection algorithm for dynamic facility layout problems. *Journal of Manufacturing Systems*, 2009, 28(4): 123-131.

- [30] M Nagode. Continuous damage parameter calculation under thermo-mechanical random loading. *MethodsX*, 2014, 1: 81-89.

- [31] E H Wong, K Lim, Y Mai. Analytical solutions for PCB assembly subjected to mismatched thermal expansion. *IEEE Transactions on Advanced Packaging*, 2009, 32(3): 602-611.

- [32] H Wong, T B Lim. A more comprehensive solution for tri-material layers subjected to thermal stress. *IEEE Transactions on Components Packaging Technologies*, 2008, 31(1): 54-64.

- [33] J Fu, O Ojo. Steady-state thermal analysis and layout optimization of DC-DC converter. 2011 IEEE International Symposium on Industrial Electronics, 2011, Gdansk. ISIE, 2011: 419-424.

- [34] C Martin, J Guichon, J Schanen, et al. Gate circuit layout optimization of power module regarding transient current

- imbalance. *IEEE Transactions on Power Electronics*, 2006, 21(5): 1176-1184.

- [35] H Zhang, J Zhou, S S Ang, et al. Reliability assessment for a double-sided cooling power electronics module. Proceedings of the IEEE 2012 Prognostics and System Health Management Conference (PHM-2012 Beijing), 2012, Beijing. PHM, 2012: 1-6.

- [36] D Seruga, M Fajdiga, M Nagode. Creep damage calculation for thermo mechanical fatigue. *Strojniški vestnik-Journal of Mechanical Engineering*, 2011, 57(5): 371-378

- [37] N Zhu, M Chen, X Zhang, et al. Substrate layout evaluation for T-type three-level IGBT modules. 2014 IEEE Energy Conversion Congress and Exposition (ECCE), 2014, Pittsburgh, PAECCE, 2014: 4677-4684.

- [38] S E D Leon-Aldaco, H Calleja, J A Alquicira. Metaheuristic optimization methods applied to power converters: A review. *IEEE Transactions on Power Electronics*, 2015, 30(12): 6791-6803.

- [39] Y Soufi, S Ghoudelbourk, T Bahi, et al. Harmonics minimization of multilevel inverter connecting source renewable energy to power system. *International Journal* of Renewable Energy Research-IJRER, 2011, 1: 265-270.

- [40] C Liu, J Wang, D Luo, et al. Elimination of harmonics in multilevel converters using stochastic Newton method. 2010 Asia-Pacific Power and Energy Engineering Conference, 2010, Chengdu. APPEEC 2010, 2010: 1-4.

- [41] A Al-Judi, H Bierk, E Nowicki. Selective harmonic power optimization in multilevel inverter output. 2011 IEEE Vehicle Power and Propulsion Conference, 2011, Chicago, IL. VPPC, 2011: 1-5.

- [42] R Yu, G K Y Ho, B M H Pong. Optimization methodology for efficient LLC resonant converter with power factor correction circuit. 6th IET International Conference on Power Electronics, Machines and Drives (PEMD 2012), 2012, Bristol. PEMD, 2012: 1-6.

- [43] M J Scott. Applications, benefits, and challenges of wide bandgap based power inversion. *Dissertations & Theses-Gradworks*, 2015: 901-922.

- [44] A Bindra, A Mantooth. Modern tool limitations in design automation: Advancing automation in design tools is Gathering momentum. *IEEE Power Electronics Magazine*, 2019, 6(1): 28-33.

- [45] S Debnath, N Rup, R Ray. THD optimization in 13 level photovoltaic inverter using genetic algorithm. *International Journal of Engineering Research and Applications*, 2012, 2: 385-389.

- [46] D Suman, R Narayan, R Rupnarayan. Elimination of low order harmonics in multilevel inverters using genetic

- algorithm. *Journal of Power Electronics*, 2011, 11(2): 132-139.

- [47] X Zheng, C Chao, G Cheng. Inverter control research based on immune algorithms. 2007 IEEE International Conference on Control and Automation, 2007, Guangzhou. ICCA, 2007: 2031-2034.

- [48] H Lou, C Mao, D Wang, et al. PWM optimisation for three-level voltage inverter based on clonal selection algorithm. *IET Electric Power Applications*, 2007, 1(6): 870-878.

- [49] R Maldonado, C Gómez, M J C Sitiriche. Simulation, design, hardware implementation, and control of a 9-level flying capacitor multilevel inverter with particle swarm optimization algorithm. 2012 IEEE 13th Workshop on Control and Modeling for Power Electronics (COMPEL), 2012, Kyoto. COMPEL, 2012: 1-6.

- [50] R Taleb, A Meroufel, A Massoum. Control of a uniform step asymmetrical 13-Level inverter using particle swarm optimization. *Automatika*, 2017, 55(1): 79-89.

- [51] W Al-Saedi, S W Lachowicz, D Habibi. An optimal current control strategy for a three-phase grid-connected photovoltaic system using particle swarm optimization. 2011 IEEE Power Engineering and Automation Conference, 2011, Wuhan. PEAM, 2011: 286-290.

- [52] M K Maharana, R Mohanty. PSO based harmonic reduction technique for wind generated power system. *Interscience*, 2012.

- [53] K Sundareswaran, K Jayant, T N Shanavas. Inverter harmonic elimination through a colony of continuously exploring ants. *IEEE Transactions on Industrial Electronics*, 2007, 54(5): 2558-2565.

- [54] C Hu, Q Wang, W Jiang, et al. Optimization method for generating SHEPWM switching patterns using chaotic ant colony algorithm applied to three-level NPC inverter. 2007 International Conference on Electrical Machines and Systems (ICEMS), 2007, Seoul. ICEMS, 2007: 149-153.

- [55] S Mishra, C N Bhende. Bacterial foraging technique-based optimized active power filter for load compensation. *IEEE Transactions on Power Delivery*, 2006, 22(1): 457-465.

- [56] B Vahidi, R Salehi, N Farokhnia, et al. Harmonic elimination and optimization of stepped voltage of multilevel inverter by bacterial foraging algorithm. *Journal of Electrical Engineering and Technology*, 2010, 5(4): 545-551.

- [57] I A Razi, Q Le, H A Mantooth, et al. Constraint-aware algorithms for heterogeneous power module layout synthesis and reliability optimization. *IEEE Workshop on*

- Wide Bandgap Power Devices & Applications, 2018, Xi'an, China, WiPDA, 2018; 323-330.

- [58] K Hermanns, Y Peng, A Mantooth. The increasing role of design automation in power electronics: Gathering what is needed. *IEEE Power Electronics Magazine*, 2020, 7(1): 46-50.

- [59] G Shen, M Qin, Q Huang. SPICE model with lumped circuits for a thermal flow sensor. SENSORS, 2006 IEEE, 2006, Daegu. ICSENS, 2006: 1444-1447.

- [60] R Eberhart, J Kennedy. A new optimizer using particle swarm theory. *MHS'95. Proceedings of the Sixth International Symposium on Micro Machine and Human Science*, 1995, Nagoya, Japan. MHS, 1995: 39-43.

- [61] Y Wang, Y Shen, X Yuan, el at. Operating point optimization of auxiliary power unit based on dynamic combined cost map and particle swarm optimization. *IEEE Transactions on Power Electronics*, 2015, 30(12): 7038-7050.

- [62] C Carlos, T E Ghazali, A Enrique. Parallel hybrid metaheuristics. New Jersey: John Wiley&Sons, 2005.

- [63] M A Tawhid, A F Ali. A hybrid social spider optimization and genetic algorithm for minimizing molecular potential energy function. *Soft Computing*, 2017, 21(21): 6499-6514.

- [64] A Cataliotti, D D Cara, G Marsala, el at. Measurements methodology for the reliability evaluation of intelligent power modules. 2014 IEEE International Instrumentation and Measurement Technology Conference (I2MTC) Proceedings, 2014, Montevideo. I2MTC, 2014: 665-669.

- [65] H Lu, C Bailey, C Y Yin. Design for reliability of power electronics modules. *Microelectronics Reliability*, 2009, 49(9-11): 1250-1255.

- [66] Q Chen, X Yang, Z Wang. Practical thermal design considerations for IPEM-based converter. 2006 CES/IEEE 5th International Power Electronics and Motion Control Conference, Shanghai, China. IPEMC, 2006: 1-5.

**Puqi Ning** has received B.S. and M.S. degrees in electrical engineering from Tsinghua University, Beijing, China, in 2004, and 2006, respectively, and earned his Ph.D. in electrical engineering at Virginia Tech, Blacksburg, USA, in 2010. From 2010 to 2013, he was with Oak National

Laboratory, Knoxville, TN, USA, and since 2013, he has been a full professor at the Institute of Electrical Engineering, Chinese Academy of Sciences. Dr. Ning has been involved in high-temperature packaging and high-density converter design for more than 10 years.

Huakang Li received his B.S. degree in electrical engineering from Wuhan University, Wuhan, China, in 2019. He is now working toward his master's degree at the Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing, China. His current research interests include power device packaging and power

device modeling.

Yunhao Huang received his B.S. degree in the automatization specialty from Tianjin University of Technology and Education, Tianjin, China, in 2019. He is now working toward his master's degree at the Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing, China. His current research interests include power device packaging

and power device modeling.

Shijiazhuang Tiedao University, Hebei, China, in 2015, and an M.S. degree from the Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing, China in 2019. Her research interests are in the packaging technology of power

Yuhui Kang received her B.S. degree in electrical

engineering and the automatization specialty from

electronic devices