# RF Capacitance-Voltage Characterization of MOSFETs with high leakage dielectrics

J. Schmitz, Member, IEEE, F. N. Cubaynes, R. J. Havens, R. de Kort, A. J. Scholten, and L. F. Tiemeijer

Abstract— We present a MOS Capacitance-Voltage measurement methodology that, contrary to present methods, is highly robust against gate leakage current densities up to 1000 A/cm². The methodology features specially designed RF test structures and RF measurement frequencies. It allows MOS parameter extraction in the full range of accumulation, depletion and inversion.

Index Terms—MOSFETs, MOS capacitors, capacitance, capacitance measurement, RF, leakage currents, tunneling

### I. INTRODUCTION

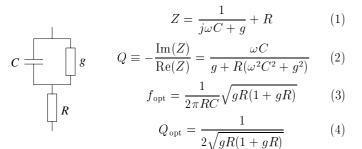

S CMOS device dimensions are scaled below 100 nm, the concurrent gate dielectric thinning leads to progressively higher gate leakage currents. Tunnel current densities around 100 A/cm² are foreseen for the near future in some CMOS logic applications [1]. Although this may be acceptable from a functional point of view, such leakage currents complicate fundamental MOS characterization techniques like charge pumping [2], time-dependent dielectric breakdown tests [3] and capacitance-voltage (C-V) measurements [4-8]. Gate leakage affects the measurement of the capacitance-voltage characteristic as well as its interpretation. This can be understood conceptually by considering a simple three-element equivalent circuit for the leaky MOS capacitor as sketched in Fig. 1. The capacitance C is connected in parallel to a (strongly bias-

Fig. 1. Three-element equivalent circuit approximation of a leaky MOS capacitor, with equations for its impedance Z, the related quality factor  $Q(\omega)$ , and the maximum achievable quality factor  $Q_{\mathrm{opt}}$ , found at frequency  $f_{\mathrm{opt}}$ .

dependent) differential conductance  $g \equiv dI/dV$  arising from gate current. An external resistance R, originating e.g. from gate resistance, is also inevitable. The equations (1)–(4) in Fig. 1 give the analytic expressions for the impedance Z, the

J. Schmitz (email: Jurriaan.Schmitz@philips.com) was with Philips Research Leuven, Belgium at the time of writing. He is presently with the University of Twente, The Netherlands. F. N. Cubaynes is with Philips Research Leuven, Belgium. R. J. Havens, R. de Kort, A. J. Scholten and L. F. Tiemeijer are with Philips Research Laboratories, Eindhoven, The Netherlands. This work was partly supported by the EC within the framework of the Artemis project.

quality factor Q, and the optimum measurement frequency  $f_{\rm opt}$  at which the quality factor reaches its maximum value  $Q_{\rm opt}$ . Measurement at  $f_{\rm opt}$  will lead to the most accurate value for C. A capacitance measurement is only straightforward when the capacitance is large enough (typically at least 1 pF), and when the quality factor is larger than 10. In case of a quality factor below unity, it is hardly possible to obtain a good estimate of the capacitance.

To obtain  $Q_{\rm opt} \gg 1$ , it follows from (4) that R should satisfy

$$gR \ll \frac{\sqrt{2} - 1}{2} \approx 0.2 \tag{5}$$

This equation shows that the higher the gate leakage (and hence g), the lower the external resistance R must be. This can be achieved by a careful design of the test structure: abundant, nearby well contacts and a small gate area. (For a sufficiently high total capacitance, several devices with separate well contacts can be connected in parallel, as in [9].) The minimum frequency for  $Q \geq 1$  can then be expressed as

$$f_{\min} = \frac{1 - \sqrt{1 - 4gR(1 + gR)}}{4\pi RC} \approx \frac{g}{2\pi C} \tag{6}$$

For a  $10\times10~\mu\mathrm{m}^2$  MOS capacitor with  $10~\mathrm{A/cm}^2$  gate leakage, typical values are C=2 pF,  $g\approx50\times10^{-6}~\Omega^{-1}$ , and  $R=10-100~\Omega$  leading to  $f_{\mathrm{min}}=4~\mathrm{MHz}$ .

Note that  $f_{\min}$  is independent of gate area and external resistance. Therefore it cannot be reduced by design improvements. As a direct consequence, high leakage dielectrics demand high measurement frequencies, driving us into the gigahertz range.

### II. DEVICE FABRICATION AND CHARACTERIZATION

The experimental study of *C-V* measurements at gigahertz frequencies (RF-CV measurements) is carried out using transistors designed for two-port RF measurements in ground-signal-ground configuration. They consist of many gates connected in parallel, with a layout resulting in very low gate resistance and low well resistance (see e.g. [9]). Sub-micron channel lengths are used to achieve a low channel resistance.

Devices were fabricated in a standard 6-metal 0.12  $\mu m$  CMOS flow, and in a single-metal 0.18  $\mu m$  CMOS research process. S-parameter measurements in the range 0.1–48 GHz were carried out on-wafer using a HP 8510C network analyzer. The gate was connected to Port 1, drain connected to Port 2. The gate was biased, the other terminals grounded. The measurements were accompanied by SOLT calibration and open-short de-embedding [10].

## III. VALIDATION OF RF-CV MEASUREMENTS

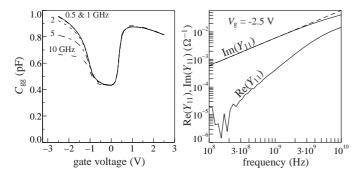

Capacitance-voltage measurements between 0.5 and 10 GHz are shown in Fig. 2 (left). Here,  $C_{gg} \equiv \text{Im}(Y_{11})/\omega$ , which is only a good approximation of the MOS capacitance C when the external resistance R is negligible. At the lowest frequencies, the

Fig. 2. Left: capacitance-voltage curve of a W/L = 384  $\mu$ m/0.18  $\mu$ m NMOS RF transistor as measured at various frequencies, after de-embedding. Right: real and imaginary parts of  $Y_{11}$  as a function of frequency at  $V_{\rm g}$  = -2.5 V. The dashed line shows the trend of a capacitor without series resistance.

shape of the curve is as expected, with the accumulation behavior of an ultra-thin dielectric and inversion capacitance decreasing due to gate depletion. The depletion region around  $V_{\rm g}=0~{\rm V}$  shows only a moderate decrease in capacitance because this is a sub-micron channel device with significant gate-drain overlap capacitance.

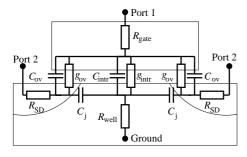

At frequencies above 1 GHz, we observe a drop in the capacitance at accumulation bias. It is accompanied by a downward bend of the real part of  $Y_{11}$ : see Fig. 2 (right). This is not due to a drop in the MOS capacitance, but rather the signature of a significant external series resistance. The origin is the well resistance  $R_{\rm well}$ , which results in a limited response time of bulk holes; see Fig. 3. In this figure, we have explicitly separated

Fig. 3. Cross section of a capacitor (or transistor), with an approximated equivalent circuit in accumulation. All components in this diagram are bias dependent except  $R_{\rm gate}$ ,  $R_{\rm SD}$  and  $R_{\rm well}$ .

the overlap regions, with capacitance  $C_{\rm ov}$  and conductance  $g_{\rm ov}$ , from the intrinsic or "channel" region with capacitance  $C_{\rm intr}$  and conductance  $g_{\rm intr}$ . In accumulation and depletion, charging and discharging of  $C_{\rm intr}$  requires holes to move from the "channel" region to the ground connection through  $R_{\rm well}$ . This transport is limited by the characteristic delay time  $\tau = R_{\rm well}C_{\rm intr}$ , which implies that the measurement frequency f is restricted to

$$f \ll \frac{1}{2\pi R_{\text{well}} C_{\text{intr}}} \tag{7}$$

For the transistor under study,  $\tau \approx 20$  ps. As a result the depletion and accumulation capacitances of  $C_{\rm intr}$  are attenuated at frequencies above 1 GHz. Therefore, in this paper we present further analysis of data obtained at 1 GHz.

2

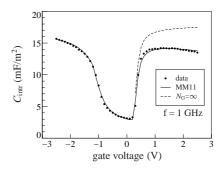

To find the intrinsic capacitance  $C_{\rm intr}$  we measured the Y-parameters of two devices with equal design except for the gate lengths, being 130 and 180 nm. From the difference of the obtained  $C_{\rm gg}$  curves, we can establish the  $C_{\rm intr}$  of a 50 nm channel segment. The capacitance of this segment is shown in Fig. 4. A C-V model can now be fitted to these data to ob-

Fig. 4. Area-normalized capacitance of a 50 nm wide channel segment as computed from the difference of a 130 nm and a 180 nm gate length RF transistor. A fit of MOS Model 11 (MM11) to the data is also shown (see text). The dashed line symbolizes the (modeled) inversion capacitance in case of infinitely high gate doping.

tain the required MOS parameters. As an example we fitted MOS Model 11 [11] over the full curve, also shown in the figure. Fit values were: -1.07 V flatband voltage, 1.9 nm oxide thickness,  $2.6\times10^{20}$  cm<sup>-3</sup> gate doping, and  $1.7\times10^{18}$  cm<sup>-3</sup> substrate doping (using no other fit parameters). These values are as expected for this  $0.12~\mu m$  CMOS process.

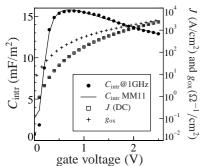

### IV. RF-CV AND GATE LEAKAGE

The RF-CV measurement method can cope with a large gate leakage current. We fabricated RF transistors with highleakage dielectrics in a research process flow (based on 0.18  $\mu$ m CMOS) using a different design of RF structures. These devices have a considerably higher  $\tau$ , preventing the correct measurement of accumulation and depletion capacitance in the channel. In inversion however,  $\tau$  does not play a role while the gate leakage current is at its highest. The external resistance in inversion (being the sum of gate and source/drain resistance) is just below 1  $\Omega$ , which adequately solves the measurement problems discussed in e.g. [12]. Fig. 5 shows the measured inversion capacitance.  $C_{\rm intr}$  was obtained from the capacitance difference between a 1  $\mu$ m and a 0.2  $\mu$ m gate length device. (For this approach to be valid, the threshold voltage difference between these devices must be limited.) The MOS Model 11 fit yields an oxide thickness and gate doping level independent of frequency in the range 0.2–2 GHz (see the table in Fig. 5) and fits poorly outside that region (due to a low quality factor).

Given the fact that power and functionality requirements restrict the gate leakage in CMOS circuits to typically  $< 1000 \text{ A/cm}^2$ , the successful extraction of  $C_{\text{intr}}$  at gate currents exceeding this value shows that the presented methodology is well suited for the characterization of any dielectric that satisfies reasonable leakage specifications.

| f              | $t_{\rm ox}$     | $N_{ m G}$           |

|----------------|------------------|----------------------|

| $\mathrm{GHz}$ | $_{\mathrm{nm}}$ | $10^{20}/{\rm cm}^3$ |

| 0.10           | (1.24)           | (0.80)               |

| 0.21           | 1.33             | 0.90                 |

| 0.48           | 1.35             | 0.94                 |

| 1.0            | 1.35             | 0.95                 |

| 2.1            | 1.33             | 0.94                 |

| 4.8            | (1.42)           | (1.15)               |

Fig. 5. Inversion capacitance and gate leakage current density of a high-leakage dielectric. The inversion capacitance is correctly measured even when the gate current density exceeds 1 kA/cm², as confirmed by the excellent fit with MOS Model 11. The fit values are listed in the table for various frequencies

### V. CONCLUSIONS

This paper presents the RF-CV methodology, which allows the measurement and analysis of capacitance-voltage curves even in the presence of gate leakage exceeding 1000 A/cm². On the basis of theoretical and experimental findings, design guidelines are formulated for RF capacitors. When these guidelines are followed, the appropriate Capacitance-Voltage characteristics are obtained around 1 GHz. These can be used for the extraction of MOS parameters such as (equivalent) oxide thickness, substrate doping concentration, and gate depletion. Since power and functionality requirements restrict the gate leakage in CMOS circuits to typically < 1000 A/cm², the presented methodology is well suited for the characterization of *any* dielectric foreseen in future CMOS technologies.

# ACKNOWLEDGMENTS

We would like to thank D. B. M. Klaassen, Ronald van Langevelde, Johan Klootwijk, and W. Kirklen Henson for fruitful discussions, and the IMEC P-line for manufacturing the devices discussed in Section IV.

### REFERENCES

- T. Ghani, K. Mistry, P. Packan, S. Thompson, M. Stettler, S. Tyagi, and M. Bohr, "Scaling challenges and device design requirements for high performance sub-50 nm gate length planar CMOS transistors", VLSI Symp. Tech. Dig., pp. 174-175, 2000.

- [2] P. Masson, J.-L. Autran, and J. Brini, "On the tunneling component of charge pumping current in ultrathin gate oxide MOSFET's", *IEEE Elec*tron Device Lett., Vol. 20, no. 2, pp. 92-94, 1999.

- [3] J. Schmitz, H. P. Tuinhout, H. J. Kretschmann, and P. H. Woerlee, "Comparison of Soft-Breakdown Triggers for Large Area Capacitors", *Transactions on Device and Materials Reliability*, Vol. 1 no. 3, pp. 150-157, 2001.

- [4] W. K. Henson, K. Z. Ahmed, E. M. Vogel, J. R. Hauser, J. J. Wortman, R. D. Venables, M. Xu, and D. Venables, "Estimating Oxide Thickness of Tunnel Oxides Down to 1.4 nm Using Conventional Capacitance-Voltage Measurements on MOS Capacitors", *IEEE Electron Device Lett.*, Vol. 20, no. 4 pp. 179-181, 1999.

- [5] J. Schmitz, "Capacitance-voltage measurements and gate leakage", Tutorial presented at the 2002 ICMTS Conference, Cork, Ireland.

- [6] C.-H. Choi, J.-S. Goo, T.-Y. Oh, Z. Yu, R. W. Dutton, A. Bayoumi, M. Cao, P. Vande Voorde, D. Vook, and C. H. Diaz, "MOS C-V Characterization of Ultrathin Gate Oxide Thickness (1.3-1.8 nm)", *IEEE Electron Device Lett.*, Vol. 20, no. 6 pp. 292-294, 1999.

- [7] K. J. Yang and C. Hu, "MOS Capacitance Measurements for High-Leakage Thin Dielectrics", *IEEE Trans. Electron Devices*, Vol. 46, no. 7 pp. 1500-1501, 1999.

- [8] D. W. Barlage, J. T. O'Keeffe, J. T. Kavalieros, M. M. Nguyen, and R. S. Chau, "Inversion MOS capacitance extraction for high-leakage dielectrics using a transmission line equivalent circuit", *IEEE Electron De*vice Lett., Vol. 21, No. 9, pp. 454-456, 2000.

- [9] L. F. Tiemeijer, H. M. J. Boots, R. J. Havens, A. J. Scholten, P. W. H. de Vreede, P. H. Woerlee, A. Heringa, and D. B. M. Klaassen, "A record high 150 GHz f<sub>max</sub> realized at 0.18 μm gate length in an industrial RF-CMOS technology", *IEDM Tech. Dig.*, 2001, pp. 223-226.

[10] M. C. A. M. Koolen, J. A. M. Geelen, and M. P. J. G. Versleijen, "An

- [10] M. C. A. M. Koolen, J. A. M. Geelen, and M. P. J. G. Versleijen, "An improved de-embedding technique for on-wafer high frequency characterization", *Proceedings BCTM*, 1991, pp. 188-191.

- [11] Available: http://www.semiconductors.philips.com/Philips\_models

- [12] D. W. Barlage, R. Arghavani, G. Dewey, M. Doczy, B. Doyle, J. T. Kavalieros, A. Murthy, B. Roberds, P. Stokley and R. S. Chau, "High-frequency response of 100nm integrated CMOS transistors with high-K gate dielectrics", *IEDM Tech. Dig.*, 2001, pp. 231-234.