Received 24 January 2019; revised 22 March 2019 and 13 May 2019; accepted 18 May 2019. Date of publication 12 July 2019; date of current version 9 August 2019. The review of this paper was arranged by Editor A. Nathan.

Digital Object Identifier 10.1109/JEDS.2019.2919677

# Robust Gate Driver on Array Based on Amorphous IGZO Thin-Film Transistor for Large Size High-Resolution Liquid Crystal Displays

QUNGANG MA<sup>1,2</sup>, HAIHONG WANG<sup>3</sup>, LIUFEI ZHOU<sup>3</sup>, JIALI FAN<sup>®</sup><sup>4</sup>, CONGWEI LIAO<sup>1</sup>,

## XIAOJUN GUO<sup>® 4</sup> (Member, IEEE), AND SHENGDONG ZHANG<sup>® 1,2</sup> (Member, IEEE)

1 School of Electronic and Computer Engineering, Peking University Shenzhen Graduate School, Shenzhen 518055, China

2 School of Electronics Engineering and Computer Science, Peking University, Beijing 10087, China

3 Research and Development Center, Nanjing CEC Panda LCD Technology Company Ltd., Nanjing 210033, China

4 Department of Electronic Engineering, School of Electronic Information and Electrical Engineering, Shanghai Jiao Tong University, Shanghai 200240, China

CORRESPONDING AUTHORS: X. GUO AND S. ZHANG (e-mail: x.guo@sjtu.edu.cn; zhangsd@pku.edu.cn)

This work was supported in part by NSFC under Project 61574003 and Project 61774010, and in part by the Shenzhen Municipal Scientific Program under Grant GGFW20170728163447038 and Grant JCYJ20180504165449640.

**ABSTRACT** Amorphous IGZO thin-film transistors (TFTs) in an etch stop layer (ESL) structure was processed on 2500 mm  $\times$  2200 mm size substrate. The fabricated devices exhibit enhancement mode characteristics, and excellent uniformity over large area. The presented good operational stabilities under both positive gate bias temperature stress (PBTS) and negative gate bias temperature stress (NBTS) tests can well meet the requirements for pixel switching. However, considering even threshold voltage shift under long term positive bias stress might affect proper operation of the gate driver on array (GOA), a design with a pulse gating scheme is proposed, consisting of 13 TFTs and 1 capacitor, to avoid long term continuous bias stressing of the TFT. With the proposed GOA design, a 32-inch QUHD (7680 $\times$ 4320) high-resolution liquid crystal display (LCD) panel with a 7 mm wide bezel is achieved. The reliability of the GOA circuit is well proved through standard aging tests.

**INDEX TERMS** Thin-film transistor, IGZO, gate driver, stability.

#### I. INTRODUCTION

The amorphous indium gallium zinc oxide (a-IGZO) TFT has been regarded as a promising backplane technology for developing large size high resolution displays, including liquid crystal displays (LCDs) and organic light emitting diode (OLED) displays [1], [2]. Compared to amorphous silicon TFTs, the a-IGZO TFT owns much improved mobility and operational stability, while maintaining similar processing complexity and device uniformity suitable for large area and low-cost manufacturing [3], [4]. Such amorphous metal oxide semiconductor TFTs may also exhibit attractive features of ultra-low off-state leakage and steep subthreshold swing for developing low power displays with lower frame rate and reduced scanning voltage [5], [6].

To achieve high resolution displays with narrow bezel, the gate driver circuits need to be integrated on the panel with the pixel array based on the TFT technology, so called gate driver on array (GOA) [7]. With the a-IGZO TFT, the GOA circuits become much easier to be implemented compared to that with a-Si TFTs. However, the non-ideal characteristics of a-IGZO TFTs still bring design challenges. Firstly, the depletion mode characteristics of a-IGZO TFTs with large leakage current at zero gate to source bias  $(V_{GS})$  cause large power consumption and even malfunction with the conventional GOA circuit design. Many designs have thus been proposed to address this issue [8]-[10]. Secondly, the operation of GOA circuits needs more stable and uniform TFTs compared to that of pixel switches, especially for large size TV applications [11]. Small threshold voltage variation of a-IGZO TFTs induced by processes or long-term operation might result in deterioration of the circuits [12], [13]. To address these issues, many circuit designs have been proposed in the past, which, however, increase the circuit complexity and thus the layout area [14]-[17]. Moreover, very few of

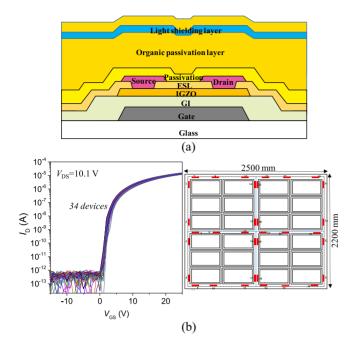

**FIGURE 1.** (a) Schematic of the cross-sectional structure of the fabricated a-IGZO TFTs in an inverted stagger structure with an etching stop layer (ESL), and (b) the measured transfer characteristics  $(I_D - V_{CS})$  of 34 devices with the channel width of 25  $\mu$ m and the channel length of 8  $\mu$ m at V<sub>DS</sub> = 10.1 V over a 2500 × 2200 nm size substrate.

these designs were realized with large area manufacturing processes, and their functionalities were not verified through standard reliability tests.

In this work, the etch stop layer (ESL) structure was adopted for processing a-IGZO TFTs because of its robustness to variations of process conditions and capability of achieving higher device performance than the back-channel etch (BCE) structure. The fabricated devices exhibit enhancement mode characteristics, and excellent uniformity over a 2500 mm×2200 mm size Gen 8 large area substrate. The presented good operational stabilities under both positive gate bias temperatures stress (PBTS) and negative gate bias temperature stress (NBTS) can well meet the requirements for pixel switching. However, considering even slight  $V_{\rm th}$ shift under long term bias stress might still affect proper operation of the GOA circuits, a GOA design with a pulse gating scheme is proposed, consisting of 13 TFTs and 1 capacitor, to avoid long term continuous bias stress of the TFT. With the proposed GOA design, a 32-inch QUHD (7680×4320) high resolution liquid crystal display (LCD) panel with a 7 mm wide bezel is achieved. The reliability of the GOA circuit is well proved through standard aging tests.

#### **II. DEVICE STRUCTURE AND PERFORMANCE**

Fig. 1(a) shows the cross-sectional structure of the fabricated a-IGZO TFTs in an inverted stagger structure with an ESL to protect the channel in the processes. The source, drain and gate electrodes are formed with copper. A light shielding structure is adopted to reduce the effects of light illumination. The measured transfer characteristics (I<sub>D</sub>-VGS)

**FIGURE 2.** The measured transfer characteristics (I<sub>D</sub>-V<sub>GS</sub>) at V<sub>DS</sub> = 10.1 V under (a) positive bias temperature stress (PBTS) and (b) negative bias temperature stress (NBTS) at 60 °C for 3600s. (c) The extracted V<sub>th</sub> shifts over the stress time under PBTS and NBTS.

of 34 devices over a 2500 mm×2200 mm size substrate as given in Fig. 1(b), showing excellent uniformity. The channel width and length are 25  $\mu$ m and 8  $\mu$ m, respectively. The average mobility is 9 cm<sup>2</sup>/V·s. Fig. 2(a) and (b) present the measured ID-VGS at VDS=10.1 V under positive bias temperature stress (PBTS) and negative bias temperature stress (NBTS) at 60 °C for 3600s. The PBTS was carried out at V<sub>GS</sub> = 30 V and V<sub>DS</sub> = 0, and the NBTS was with V<sub>GS</sub> = -30 V and V<sub>DS</sub> = 0. The extracted Vth shifts over the stress time under PBTS and NBTS are given in Fig. 2(c). It can be seen that, after 1 hour continuous stress, there was a V<sub>th</sub> shift of about 1.5 V with PBTS and about 0.4 V with NBTS. The stability of devices is good enough for pixel switches. However, the operation of GOA circuits is more sensitive to the V<sub>th</sub> variation.

#### **III. GOA CIRCUIT DESIGN**

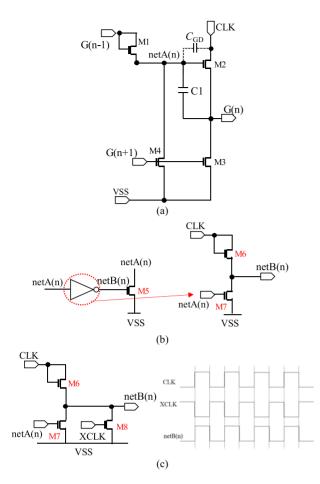

In a basic GOA circuit design, as illustrated in Fig. 3(a), the pull-up TFT M2 needs to be of a relatively large channel width-to-length ratio to provide enough current driving capability for charging the gate line (G(n)), resulting in large gate to drain parasitic capacitor of M2 ( $C_{GD}$ ). During the OFF state of M2, transition of the clock signal (CLK) will cause a voltage coupling to the gate of M2 (netA(n)) with clock feedthrough via  $C_{GD}$  of TFT1. If the induced voltage change is larger than  $V_{th}$  of M2, abnormal outputs to the gate line will occur. By using a larger boot-trap capacitor ( $C_b$ ), clock feedthrough can be reduced, but the charging/discharge speed will be affected. An effective approach is to add a circuit

**FIGURE 3.** (a) Schematic of the basic GOA circuit design. (b) Schematic of a circuit unit being added in the GOA circuit in (a) to stabilize the voltage at netA(n). (c) Schematic of the circuit design to replace the inverter in (b) for pulse gating of M5.

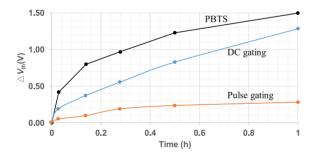

**FIGURE 4.** Comparison of the measured V<sub>th</sub> shifts under the DC and pulse gating methods with the PBTS test results for the fabricated IGZO TFT.

unit to stabilize the voltage at netA(n), as shown in Fig. 3(b). The circuit consists of an inverter and a pull-down TFT M5. Once netA (n) is high, netB (n) will go low, thus turning M5 off to maintain the voltage level at netA(n). NetA (n) and G (n) are discharged to VSS, when netA (n) is low and netB (n) is high. However, because during most time of each frame, netA(n) is low and netB(n) is high, the holding TFT M5 will be under nearly continuous positive bias stress (DC gating) over long operation time. As a result, a certain positive shift will occur. With a too positive  $V_{th}$ , M5 will

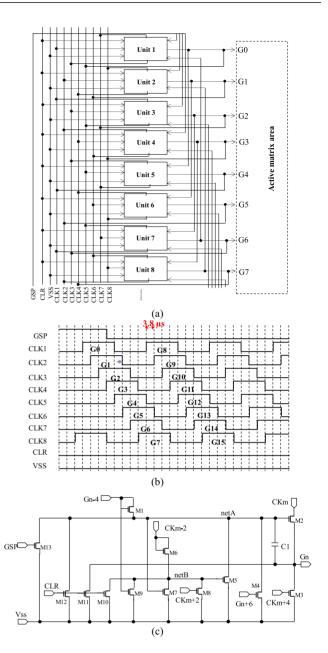

FIGURE 5. (a) Illustrate of the implemented 8 clock GOA architecture. (b) Timing of all the input control signals. (c) Diagram of the unit GOA circuit composed of 13 TFTs.

not be able to sufficiently discharge netA(n), causing noise at G(n) and risk of failure for the circuits.

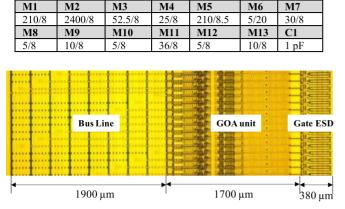

To address this issue, a pulse gating method is used as shown in Fig. 3(c). An additional TFT M8 is added in the circuit, and controlled by the clock signal XCLK, which is complementary to CLK. Since M6 and M8 are alternately turned on under control of CLK and XCLK, respectively, the voltage level at netB(n) becomes periodically high, effectively reducing the bias stress time at M5. Fig. 4 compares the measured  $V_{\text{th}}$  shifts under the two different methods with that obtained under PBTS. It can be seen with M8 and its control clock XCLK, the pulse gating method can help to effectively decrease  $V_{\text{th}}$  shift of M5 over long time operation. TABLE 1. Values of the design parameters of the TFTs (M1-M13) and the capacitor (C1) in the circuit (Fig. 5c) (for TFTs, the given value is channel width/channel length in  $\mu$ m).

FIGURE 6. Photo image of the overall GOA including the bus line and ESD protection parts.

### **IV. IMPLEMENTATION OF THE GOA**

Based on this design, an 8 CLK GOA architecture, as depicted in Fig. 5 (a), is implemented in a 32 inch OUHD LCD panel. The operation timing of all the input control signals is given in Fig. 5(b). The pulse width of the gate output waveform is designed to be 15.2  $\mu$ s. More clock signals can help to reduce the parasitic capacitance on each CLK line, and thus decrease RC delay. For the 32 inch QUHD display, the row selection time is quite short, and thus such an 8 CLK design is needed. For lower resolution displays, design with less CLK signals can be used. The multi-clock design is also able to reduce the power consumption. The unit circuit, as shown in Fig. 5(c), adopts the pulse gating method, consisting 13 TFTs and 1 capacitor. In the circuit, additional TFTs M9/M10/M11/M12/M13 are added to clear the critical node charges before the circuit starts to operate. The design parameters of the TFTs and the capacitor are listed in Table 1. The photo image of the overall GOA including the bus line and ESD protection parts is given in Fig. 6 with the total width less than 4 mm.

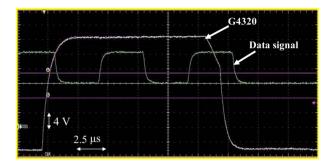

With this GOA, a 32 inch OUHD (7680 RGB  $\times$ 4320) high resolution LCD panel with a 7 mm wide bezel was achieved. The measured power consumption of the GOA is about 360.3 mW. To verify the reliability of the GOA, the whole panel was placed under standard aging tests, including storage at high temperature (70°C) and low temperature (-20°C) for 240 hours, operation at high temperature (60°C) and low temperature ( $-20^{\circ}$ C) for 240 hours, storage and operation at high temperature (60°C) and high humidity (RH of 90%) for 24 hours, being turned ON/OFF for 30000 cycles, and ESD test at 15 kV. After all the aging tests, the display can work normally without any defects as shown in Fig. 7. The measured output voltage waveform of the 4320<sup>th</sup> gate line (G4320) is given in Fig. 8, indicating proper operation of the GOA. The results can well prove that designed GOA has good enough reliability for large area high resolution LCDs.

**FIGURE 7.** Photo image of the 32 inch QUHD LCD panel using the designed GOA after aging tests and the specifications of the panel.

**FIGURE 8.** The measured output voltage waveform of the 4320th gate line (G4320) of the fabricated 32 inch QUHD LCD panel.

#### **V. CONCLUSION**

In summary, GOA was designed and implemented based on the a-IGZO TFT processed on Gen 8 substrate. The TFT devices exhibited excellent uniformity over large area. To improve the robustness of the GOA to long term operation, a pulse gating scheme is adopted to avoid the TFTs to be operated with long term bias stress. The GOA was integrated to achieve a 32 inch QUHD (7680 RGB  $\times$  4320) high resolution LCD panel with a narrow bezel. Good reliability was well proved through standard aging tests.

#### REFERENCES

- J. Y. Noh, D. M. Han, W. C. Jeong, J. W. Kim, and S. Y. Cha, "21-1: Development of 55" 4K UHD OLED TV employing the internal gate IC with high reliability and short channel IGZO TFTs," in *SID Tech. Dig.*, vol. 48, no. 1, May 2017, pp. 288–290. doi: 10.1002/sdtp.11605.

- [2] S. Yamada, F. Shimoshikiryoh, Y. Itoh, and A. Ban, "37-4L: Latenews paper: Development of a 27-in. 8K x 4K liquid-crystal display utilizing an InGaZnO TFT backplane," in *SID Tech. Dig.*, vol. 47, no. 1, May 2016, pp. 480–483. doi: 10.1002/sdtp.10713.

- [3] D. Geng, H. M. Kim, M. Mativenga, Y. Chen, and J. Jang, "29.3: High resolution flexible AMOLED with integrated gate-driver using bulk-accumulation a-IGZO TFTs," in *SID Tech. Dig.*, Jun. 2015, pp. 423–426. doi: 10.1002/sdtp.10393.

- [4] Y. G. Mo *et al.*, "69.3: Amorphous oxide TFT backplane for large size AMOLED TVs," in *SID Tech. Dig.*, vol. 41, no. 1, May 2010, pp. 1037–1040. doi: 10.1889/1.3499826.

- [5] P. Ma *et al.*, "Low voltage operation of IGZO thin film transistors enabled by ultrathin Al<sub>2</sub>O<sub>3</sub> gate dielectric," *Appl. Phys. Lett.*, vol. 112, no. 2, Jan. 2018, Art. no. 023501. doi: 10.1063/1.5003662.

- [6] N.-C. Su *et al.*, "Low-voltage-driven flexible InGaZnO thin-film transistor with small subthreshold swing," *IEEE Electron Device Lett.*, vol. 31, no. 7, pp. 680–682, Jul. 2010. doi: 10.1109/LED.2010.2047232.

- [7] Z. Hu, C. Liao, W. Li, L. Zeng, C.-Y. Lee, and S. Zhang, "Integrated a-Si:H gate driver with low-level holding TFTs biased under bipolar pulses," *IEEE Trans. Electron Devices*, vol. 62, no. 12, pp. 4044–4050, Dec. 2015. doi: 10.1109/TED.2015.2487836.

- [8] L.-Q. Shi *et al.*, "7-2: Design of highly reliable depletion-mode a-IGZO TFT gate driving circuit for 31-in. 8K4K 287-ppi TFT-LCD," in *SID Tech. Dig.*, vol. 48, no. 1, May 2017, pp. 68–71. doi: 10.1002/sdtp.11561.

- [9] J.-H. Kim, J. Oh, K. Park, and Y.-S. Kim, "IGZO TFT gate driver circuit with large threshold voltage margin," *Displays*, vol. 53, pp. 1–7, Jul. 2018. doi: 10.1016/j.displa.2018.03.003.

- [10] S.-J. Ahn, S.-K. Hong, and O.-K. Kwon, "P-18: A low-power scan driver using depletion-mode a-IGZO TFTs for high-resolution displays," in *SID Tech. Dig.*, vol. 45, no. 1, Jun. 2014, pp. 1009–1012. doi: 10.1002/j.2168–0159.2014.tb00262.x.

- [11] H.-J. Shin *et al.*, "4.4L: LateNews paper: A novel high reliable integrated gate driver with bi-scanning structure using a-Si TFT for large size FHD TFT-LCD TVs," in *SID Tech. Dig.*, vol. 41, no. 1, May 2010, pp. 35–38. doi: 10.1889/1.3500457.

- [12] X. Liu et al., "Gate bias stress-induced threshold voltage shift effect of a-IGZO TFTs with Cu gate," *IEEE Trans. Electron Devices*, vol. 61, no. 12, pp. 4299–4302, Dec. 2014. doi: 10.1109/TED.2014.2362850.

- [13] J. I. Kim *et al.*, "Local-degradation-induced threshold voltage shift in turned-off amorphous InGaZnO thin film transistors under AC drain bias stress," *IEEE Electron Device Lett.*, vol. 36, no. 6, pp. 579–581, Jun. 2015. doi: 10.1109/LED.2015.2424966.

- [14] C.-L. Lin, M.-H. Cheng, C.-D. Tu, C.-E. Wu, and F.-H. Chen, "Low-power a-Si:H gate driver circuit with threshold-voltage-shift recovery and synchronously controlled pull-down scheme," *IEEE Trans. Electron Devices*, vol. 62, no. 1, pp. 136–142, Jan. 2015. doi: 10.1109/TED.2014.2372820.

- [15] C.-L. Lin, C.-E. Wu, and C.-E. Lee, "P-41: New a-IGZO TFT gate driver circuit with threshold voltage shift recovery driving scheme," in *SID Tech. Dig.*, vol. 46, no. 1, pp. 1293–1296, Jun. 2015. doi: 10.1002/sdtp.10099.

- [16] B.-H. You *et al.*, "Real-time external compensation of threshold voltage shift using double-gate oxide TFTs in a gate driving system," *J. Display Technol.*, vol. 12, no. 9, pp. 892–897, Sep. 2016. doi: 10.1109/JDT.2016.2550665.

- [17] K. Cao et al., "Integrated gate drive circuit employing IGZO TFTs for AMOLED compensative pixel driving," in *SID Tech. Dig.*, vol. 46, no. 1, Jun. 2015, pp. 1324–1325. doi: 10.1002/sdtp.10110.