## Runtime Verification of Analog and Mixed Signal Designs

Zhiwei Wang

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science (Electrical & Computer Engineering)

at

Concordia University Montréal, Québec, Canada

June 2009

© Zhiwei Wang, 2009

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-63186-7 Our file Notre référence ISBN: 978-0-494-63186-7

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## CONCORDIA UNIVERSITY

#### School of Graduate Studies

This is to certify that the thesis prepared

| By:           | Zhiwei Wang                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------|

| Entitled:     | Runtime Verification of Analog and Mixed Signal Designs                                         |

| and submitted | d in partial fulfilment of the requirements for the degree of                                   |

|               | Master of Applied Science (Electrical & Computer Engi-                                          |

| neering)      |                                                                                                 |

| _             | the regulations of this University and meets the accepted standards to originality and quality. |

| Signed by the | final examining committee:                                                                      |

|               | Dr. Amir G. Aghdam                                                                              |

| <del> </del>  | Dr. Hon Fung Li                                                                                 |

|               | Dr. Rabin Raut                                                                                  |

|               | Dr. Sofiène Tahar                                                                               |

| Approved by . |                                                                                                 |

|               | Chair of the ECE Department                                                                     |

| 20            | 009                                                                                             |

|               | Dean of Engineering                                                                             |

#### ABSTRACT

#### Runtime Verification of Analog and Mixed Signal Designs

#### Zhiwei Wang

Analog and mixed signal (AMS) circuits play an important role in system on chip designs. They pose, however, many challenges in the verification of the overall system due to their complex behaviors and expensive consumption of simulation resources. Besides functionality, AMS systems also suffer from stochastic processes such as random noise which exhibits statistical properties. Among many developed verification techniques, runtime verification has been shown to be effective by experimenting finite executions instead of going through the whole state space. In this thesis, we propose a methodology for the verification of AMS designs using functional and statistical runtime verification. Functional runtime verification is used to check the functional behavior of the AMS design. A system of recurrence equation (SRE) is used to model the AMS design and construct a functional property monitor. This functional runtime verification is carried out in an *online* fashion. Statistical runtime verification is used to verify the statistical properties of the AMS design. Hypothesis test, which is a method to make statistical decisions about rejecting or accepting some statement about the information of a sample, is used to verify the statistical properties. We use Monte Carlo simulation for the hypothesis test and for evaluating its performance. The proposed methodology is applied to a phase lock loop based frequency synthesizer where several functional properties and stochastic noise properties are verified.

#### ACKNOWLEDGEMENTS

It has been an amazing experience to accomplish my Master's thesis in the Hardware Verification Group (HVG) at Concordia. It certainly would not have happened without the support and guidance of several people to whom I owe a great deal.

First of all, I would like to thank my supervisor, Dr. Sofiène Tahar. It is he who offered me the opportunity to join the group. He was fully supportive, understanding, involved and present during all the phases of my research. I have learned many things from him in regard to research, academia, and life in general.

Secondly, I would like to thank Dr. Mohamed Zaki. He introduced me to the topic of this thesis and guided me in the right direction. His wisdom, elegance of thought and extreme kindness were always very inspiring to me.

Next, let me thank all the members of HVG for their help and encouragement. Their friendship brought me a warm environment in the lab. I especially appreciate the collaboration with Naeem Abbasi, Rajeev Narayanan and William Denman. My work, from the first conference paper to my Master's thesis, has benefited a lot from their valuable advice and technical support.

Last but not least, this thesis could not have been done without the unconditional love from my parents who always give me their full support. In addition, I would like to give many thanks to Amy for her full understanding and spirit support during my research.

| $To\ my$ $mother$ | grand father, | Lindai, | and | the | memory | of | my | grand |

|-------------------|---------------|---------|-----|-----|--------|----|----|-------|

|                   |               |         |     |     |        |    |    |       |

|                   |               |         |     |     |        |    |    |       |

v

## TABLE OF CONTENTS

| LI  | ST O | F FIGURES                                        | viii |

|-----|------|--------------------------------------------------|------|

| LI  | ST O | F TABLES                                         | ix   |

| LIS | ST O | F ACRONYMS                                       | X    |

| 1   | Intr | oduction                                         | 1    |

|     | 1.1  | Motivation                                       | 1    |

|     | 1.2  | Runtime Verification                             | 5    |

|     | 1.3  | Related Work                                     | 8    |

|     |      | 1.3.1 Functional Runtime Verification            | 8    |

|     |      | 1.3.2 Statistical Runtime Verification           | 10   |

|     | 1.4  | Proposed Methodology                             | 11   |

|     | 1.5  | Phase Locked Loop                                |      |

|     | 1.6  | Thesis Contributions                             | 14   |

|     | 1.7  | Thesis Outline                                   | 14   |

| 2   | Pre  | liminaries                                       | 16   |

|     | 2.1  | The System of Recurrence Equations (SRE)         | 16   |

|     | 2.2  | Property Specification Language: PSL             | 17   |

|     | 2.3  | C-SRE Simulator                                  | 19   |

|     | 2.4  | Basic Concepts in Probability and Random Process | 21   |

|     |      | 2.4.1 Random Variables                           | 21   |

|     |      | 2.4.2 Distribution Functions                     | 22   |

|     |      |                                                  | 23   |

|     | 2.5  | Monte Carlo Simulation                           | 24   |

| 3   | Rur  | ntime Verification Methodology                   | 25   |

|     | 3 1  | Overall Methodology                              | 25   |

|                  | 3.2    | SRE Modeling of AMS Design                      | <br>    | <br> |   | 26         |

|------------------|--------|-------------------------------------------------|---------|------|---|------------|

|                  | 3.3    | Runtime Verification with Online Monitoring     | <br>    | <br> |   | 27         |

|                  |        | 3.3.1 Writing PSL using SREs                    | <br>    | <br> |   | 28         |

|                  |        | 3.3.2 Online Monitoring                         | <br>    | <br> | • | 30         |

|                  | 3.4    | Statistical Runtime Verification                | <br>    | <br> |   | 34         |

|                  |        | 3.4.1 Hypothesis Testing                        | <br>. ; | <br> |   | 35         |

|                  |        | 3.4.2 Monte Carlo Methods for Hypothesis Test . | <br>    | <br> |   | 42         |

|                  |        | 3.4.3 Hypothesis Test Performance Assessment    | <br>    | <br> |   | 43         |

|                  |        | 3.4.4 Hypothesis Test Summary                   | <br>    | <br> | • | 46         |

|                  |        | 3.4.5 Statistical Runtime Verification          | <br>    | <br> |   | 47         |

|                  | 3.5    | Summary                                         | <br>    | <br> |   | 49         |

| 4                | Cas    | se Study: PLL Based Frequency Synthesizer       |         |      |   | 50         |

|                  | 4.1    | SRE Modeling                                    | <br>    | <br> | • | 50         |

|                  | 4.2    | Online Monitoring of Functional Properties      | <br>    | <br> |   | 56         |

|                  | 4.3    | Offline Monitoring of Statistical Properties    | <br>    | <br> |   | 61         |

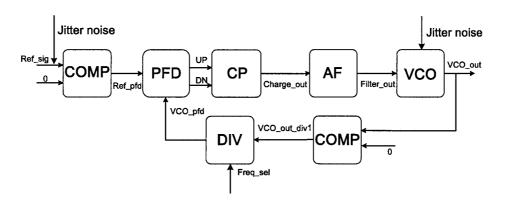

|                  |        | 4.3.1 Jitter Noise in Frequency Synthesizer     | <br>    | <br> |   | 62         |

|                  |        | 4.3.2 Jitter Metrics                            | <br>    | <br> |   | 63         |

|                  |        | 4.3.3 Jitter in VCO                             | <br>    | <br> |   | 65         |

|                  |        | 4.3.4 Statistical Runtime Verification          | <br>    | <br> |   | 67         |

|                  | 4.4    | Discussion                                      | <br>    | <br> |   | 73         |

| 5                | Cor    | nclusion and Future Work                        |         |      |   | <b>7</b> 4 |

|                  | 5.1    | Conclusion                                      | <br>    | <br> |   | 74         |

|                  | 5.2    | Future Work                                     | <br>    | <br> |   | 76         |

| $\mathbf{R}^{i}$ | ibling | graphy                                          |         |      |   | 77         |

## LIST OF FIGURES

| 1.1  | Design Productivity Gap [49]                       |

|------|----------------------------------------------------|

| 1.2  | The Rate of First Silicon Success [49]             |

| 1.3  | Runtime Verification Methodology                   |

| 1.4  | General PLL Architecture                           |

| 2.1  | C-SRE Simulator Framework                          |

| 2.2  | Timing Diagram                                     |

| 3.1  | Overall Methodology                                |

| 3.2  | Online Runtime Verification                        |

| 3.3  | Online Runtime Verification                        |

| 3.4  | Rejection Region for a Lower Tail Test             |

| 3.5  | Monte Carlo Based Statistical Runtime Verification |

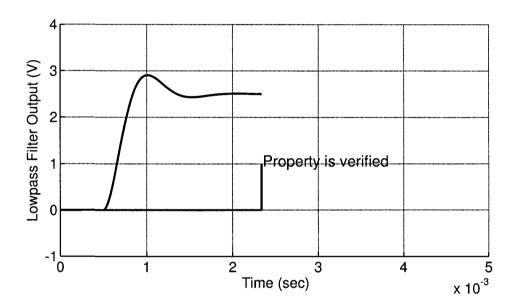

| 4.1  | PLL Frequency Synthesizer Architecture             |

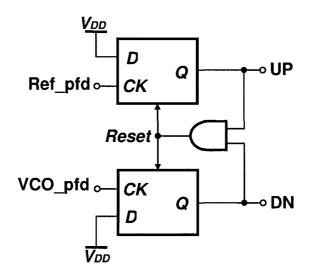

| 4.2  | Phase and Frequency Detector                       |

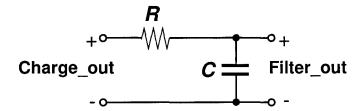

| 4.3  | First Order Lowpass Filter                         |

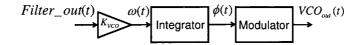

| 4.4  | Voltage Controlled Oscillator                      |

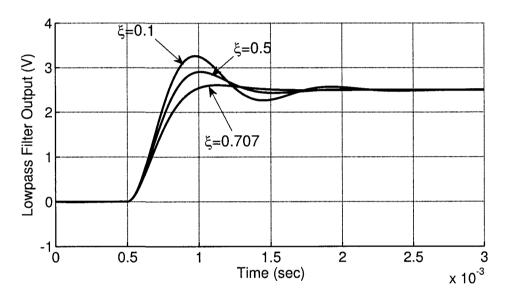

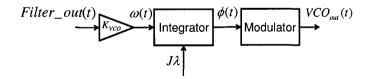

| 4.5  | Lowpass Filter Output Voltage with Different $\xi$ |

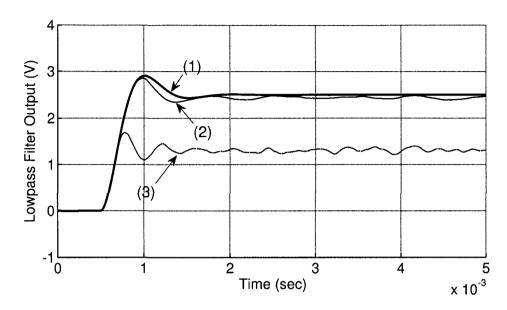

| 4.6  | Locktime Property                                  |

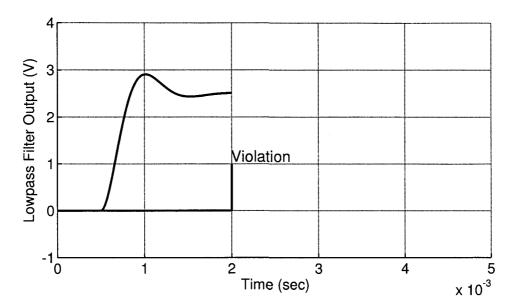

| 4.7  | Verification Results of Property 2                 |

| 4.8  | PLL Frequency Synthesizer with Jitter Sources      |

| 4.9  | Jitter Metrics                                     |

| 4.10 | VCO Model with Jitter Noise                        |

| 4.11 | Filter Output with Jitter Noise in VCO             |

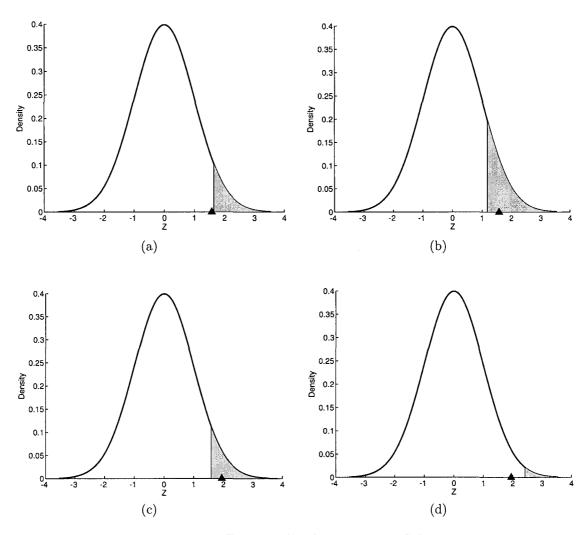

| 4.12 | Effects of Confidence Level Selection              |

## LIST OF TABLES

| 3.1 | Basic Comparison of Online Method and Offline Method             | 34 |

|-----|------------------------------------------------------------------|----|

| 3.2 | Summary of Hypothesis Test Concepts                              | 46 |

| 4.1 | Frequency Synthesizer Parameters                                 | 58 |

| 4.2 | Simulation Results                                               | 61 |

| 4.3 | Statistical Runtime Verification with Different $J$              | 69 |

| 4.4 | Statistical Runtime Verification with Different $J$ and $\alpha$ | 70 |

| 4.5 | Performance of Monte Carlo Monitoring with Different Trials $M$  | 72 |

#### LIST OF ACRONYMS

A/D Analog to Digital Converter

AF Analog Filter

AMS Analog and Mixed Signal

AMT Analog Monitoring Tool

ASIC Application Specific Integrated Circuits

CDF Cumulative Distribution Function

COMP Comparator

CP Charge Pump

CPU central Processing Unit

CSL Continuous Stochastic Logic

CT Continuous Time

CTL Computational Tree Logic

D/A Digital to Analog Converter

DAE Differential Algebraic Equations

DC Direct Current

DE Discrete Event

DIV Divider

DJ Deterministic Jitter

DSP Digital Signal Processor

DT Discrete Time

EDA Electronic Design Automation

FL Foundation Language

FPGA Field-Programmable Gate Array

GPS Global Positioning System

FSM Finite State Machine

HDL Hardware Description Language

HOL Higher Order Logic

IP Intellectual Property

LHA Linear Hybrid Automata

LTL Linear Temporal Logic

MaC Monitoring and Checking

MEDL Meta Event Definition Logic

MITL Metric Interval Temporal Logic

MSA Mixed Signal Assertions

OBE Optional Branching Extension

PDF Probability Density Function

PFD Phase and Frequency Detector

PLL Phase Locked Loop

PMF Probability Mass Function

PSL Property Specification Language

PVS Prototype Verification System

RF Radio Frequency

RJ Random Jitter

SERE Sequential Extension Regular Expressions

SoC System on Chip

SRE System of Recurrence Equation

STL Signal Temporal Logic

VCO Voltage Controlled Oscillator

VHDL Very (High Speed Integrated Circuits) Hardware Descrip-

tion Language

## Chapter 1

## Introduction

#### 1.1 Motivation

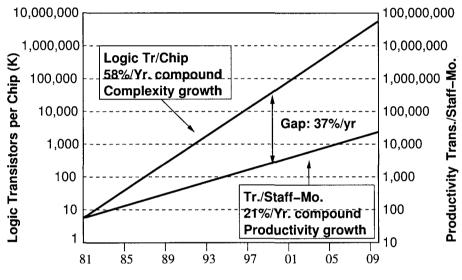

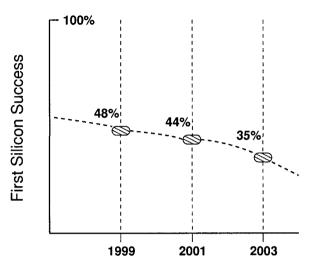

With the constant growth in integrated circuit technology, the number of transistors per chip has been doubling almost every two years according to Moore's Law [10] and that figure passed two billion by the end of 2008 [43]. As a consequence of high level integration, more complex functionalities can be realized in compact systems such as smart cell phones and portable game consoles. In modern design methodologies, instead of putting every transistor separately on the multi-million-transistor chip, functional components are integrated as building blocks in one chip. Because of this, System on Chip (SoC) architecture has prevailed for the last decade. It may contain digital, analog, mixed signal and radio frequency functional units in one chip. Although SoC designs have been driving the semiconductor industry, as shown in Figure 1.1, the growth of design productivity has been lagging behind the improvement in the number of transistors per chip by as much as 37% [49]. The rate of the first silicon success is one of the main reasons for this gap. Figure 1.2 shows that this rate dropped to 35% in 2003. As the performance of SoC continues to improve, AMS components are considered a bottleneck in improving the overall performance of the system and the factor for enhancement of the first silicon success rate. 70% of re-spun designs contain functional bugs [9]. To overcome these obstacles, 70% of the total design effort in the semiconductor industry is now spent on verification. The failure of analog and mixed signal (AMS) components has been one of the major causes for the high design re-spun rate [9]. The design and verification of AMS systems became very important in recent years.

Figure 1.1: Design Productivity Gap [49]

We live in an analog world. The SoC system of the design operates in the real analog environment as well. The data is processed by the digital components inside the system. The class of components which connect the analog world to digital domain processors is called Analog and Mixed Signal (AMS). Examples of AMS designs include analog filters, frequency synthesizer, digital to analog converters (D/A), and analog to digital converters (A/D). They can be Intellectual Property (IP) cores or the interface between them.

Simulation is traditionally used to check whether a design exhibits the proper behavior as elicited by a series of tests. However, pure simulation approach is feasible only when the expected results can be done manually and the state space is not complete [50]. For more complex systems, especially AMS designs, pure simulation

#### North American Re-spin Statistics

Figure 1.2: The Rate of First Silicon Success [49]

finds itself not competent for functional verification due to the coverage issue and long simulation time. With the evolution of hardware description languages (HDL) extensions tailored for AMS designs, such as VHDL-AMS [46], Verilog-AMS [45] and SystemC-AMS [44], the complex behaviors of an AMS system can be described at different abstraction levels. Recently, many Electronic Design Automation (EDA) companies have dedicated to the development of efficient AMS simulators. All these efforts have allowed the AMS modeling and specification to reach a new level together with the accuracy and efficiency. However, the development of verification of AMS systems has been lagging behind the design due to the limitations in platforms and different levels of the abstraction. A complete verification methodology integrating modeling and verification is desired.

In order to solve the coverage issue, formal verification has been advanced in recent years. Formal verification is a mathematical reasoning procedure to prove that an implementation satisfies its specification. The implementation can be a description of the design at any abstraction level, such as behavior level or Register Transfer Level (RTL). The specification refers to a correct description, or a

desired property, of the system to be checked. There are three main techniques of formal verification method [25]: theorem proving, equivalence checking, and model checking.

In theorem proving, the relationship between specification and implementation is defined as a theorem to be proven through a deductive procedure with a set of axioms and inference rules. Theorem proving, a proof based method, is able to perform various verification tasks at different abstraction levels. Although it is a powerful verification technique, the entire proof procedure requires considerable amount of manual effort. The two most common higher order logic provers are HOL [18] and PVS [39].

In industry, equivalence checking is widely used to compare two models of a system to check whether they are functionally equivalent. In digital domain, equivalence checking exhibits its efficiency for systems of moderate size. In an AMS system, the continuous signal representation makes the alternative real value model difficult to find. Hence, equivalence checking is not suitable for AMS designs.

Model checking, known as a state exploration method, is used to find out whether the model of the design satisfies a given temporal specification. The model refers to a space which contains all the possible states of the system. A state exploration algorithm is then applied to determine whether the model satisfies the property. If the property does not hold, a counterexample is reported at the state where the violation occurs. Model checking is an automatic technique. However, when scaling up to large circuits, it suffers inevitable problems such as state explosion which limits the computational resources in terms of memory and time. In the case of AMS designs, the situation is even worse because the analog signal in continuous domain can only be expressed using infinite states. Bounded model checking [8] technique has been adapted to cope with the state explosion issue. However, the price paid is the incomplete coverage issue due to the bounded approximation.

Runtime verification combining simulation and formal specification, which is

considered a semi-formal verification approach, has been adopted to complement formal methods. By evaluating finite execution traces instead of exploring them all, runtime verification avoids the state space explosion. The formal specification ensures the coverage of the verification. A survey on the formal verification of AMS designs using the above mentioned techniques can be found in [50].

The general motivation of this thesis is to present a complete methodology for the runtime verification of ASM designs. This methodology contains a new modeling technique, a functional runtime verification and a statistical runtime verification method. The modeling technique unifies the expression of analog and digital signal representation in order to simulate them in the same environment. The runtime online verification method constructs the monitor based on the formal specification of the system property using the same modeling technique. The statistical runtime verification method is capable of analyzing stochastic processes occurring in AMS designs. In following we will introduce the notions of runtime verification and its application in AMS designs followed by discussions of related works.

#### 1.2 Runtime Verification

In recent years, runtime verification has been developed to bridge the gap between formal verification and traditional simulation methods. Initially serving in software verification, runtime verification can also be applied to hardware verification especially when formal methods and conventional simulation encounter practical obstacles. The most distinguishing feature of runtime verification is that the verification procedure is accomplished at runtime based on the simulation traces. The feature that no computational model is needed prior to the verification avoids the state space explosion problem [50]. Runtime verification deals with the detection of violation, as well as satisfaction, of the property. A monitor is used to detect the violation. The monitoring technique can be performed in two ways, namely,

online and offline monitoring. Online monitoring, which is used to check a current execution of a system when the simulation is running, is able to detect a property violation as soon as it occurs. On the other hand, offline monitoring operates on a set of recorded executions after the simulation is done.

Runtime verification can be grouped into functional runtime verification and statistical runtime verification in terms of different kinds of properties to be verified. In the following, we will introduce the functional and statistical runtime verification, respectively.

#### **Functional Runtime Verification**

Functional runtime verification is used to determine if the design satisfies a specified functional property [34]. The functional property refers to a specification that indicates the correct operation or how the system will function. For AMS designs, examples of functional properties include whether an oscillator oscillates or if a phase lock loop locks at the desired frequency.

Compared with model checking, functional runtime verification deals with finite executions instead of walking through large state space. This allows runtime verification to be applied to the AMS system whose entire system model is available at higher level of abstraction. In addition, the verification points are easy to be set up according to the finite traces. In model checking, the state exploration algorithm usually requires a complete generation of the state space before executing. This prevents online monitoring applicable for model checking. Runtime verification does not have this problem except that the requirement is needed. The advantage of functional runtime verification over conventional simulation approach is that runtime verification uses a formal specification for the property, which can be a trace or several individual observation points, instead of evaluating the inputs and output pairs in simulation. In addition, *online* monitoring technique allows the verification to terminate as soon as the violation is detected. This is important especially for

such AMS designs requiring long time in simulation. The formal specification also introduces more confidence in runtime verification than with simulation.

In functional runtime verification, the monitor is generated from a high level system specification, for which a high level modeling is needed. In this thesis, a high level modeling approach is introduced, and is then used to generate the monitor. Because of the consistency between the modeling and monitoring techniques, the *online* runtime verification of AMS design becomes feasible.

#### Statistical Runtime Verification

In this thesis, we propose a statistical runtime verification approach to investigate statistical properties of AMS systems. A statistical property refers to the property which deals with the stochastic behavior of the system and is analyzed using statistical methods. Examples of the statistical properties are mean, variance, and standard deviation. In AMS designs, the system suffers from different kinds of random noise such as thermal noise and jitter noise. We propose an approach for the verification of statistical properties using Monte Carlo simulation [33] and statistical hypothesis testing [28]. In statistical hypothesis testing, two hypotheses are made based on the property to be verified. The two hypotheses are exclusive to each other. The rejection of one leads to the acceptance of the other. In order to perform a hypothesis test, the distribution of the parameter of interest, or statistic, is expected to be known. Sometimes the distribution of the sample data is not known in advance. In such case, Monte Carlo simulation is applied to estimate the statistic model to perform the hypothesis test. Each decision made by hypothesis test has an associated confidence level. A 100% in confidence level is usually not realistic in random process. It is unlikely that the statistics estimated from a random sample is exactly equal the true value of the population parameter. The confidence interval is used to enclose the estimated value. The confidence level indicates the probability that the estimated value presents itself in such interval. The difference between the

bounds of the interval and the estimated value is called error margin. The assumed statistic model could result in some errors. The Monte Carlo method is then used to assess the performance of the hypothesis test conducted. For many properties of a stochastic process, it is usually acceptable to receive either a violation or satisfaction of the property with a bounded confidence level and error margin.

In next section, we will introduce the works related to functional runtime verification and statistical runtime verification, respectively.

#### 1.3 Related Work

#### 1.3.1 Functional Runtime Verification

Runtime verification originated in software verification initially. Recently, several notable efforts have been made to verify AMS designs using runtime verification. In one of the most prominent works [30], the authors present an offline methodology for monitoring the simulation of continuous signals. The monitoring technique was based on Signal Temporal Logic (STL) [30] which is an analog extension of Metric Interval Temporal Logic (MITL) [4]. The simulation and monitoring was conducted using Matlab/Simulink [32]. In [37], the authors synthesized the Property Specification Language (PSL) analog extension (STL/PSL) into an Analog Monitoring Tool (AMT). The tool is capable of both offline and incremental monitoring. In a recent case study [22], the authors investigated the verification of a DDR2 SDRAM memory using AMT in an offline mode. The approach mentioned synthesizes the property in terms of lower abstraction levels such as a finite state machine (FSM). The work we propose in this thesis applies to online monitoring, and presents a unified framework for both modeling and verification at a higher level of abstraction.

In [17], the authors propose an online monitoring technique. They used the linear hybrid automata (LHA) as a monitor to analyze the reachability of time domain features. A hybrid system analysis tool named HPAVer [16] was used to

verify the signal amplitude and jitter properties of an oscillator circuit. In order to avoid infinite memory required, necessary approximations were employed and the assumption of the existence of templates to build the monitor was also done. The computational expense of this technique is high because the work is based on formal verification and state space analysis rather than linear temporal logic (LTL) [14]. In general, it does not provide a generic way to obtain the monitors from the specification. In contrast, the approach we advance is capable of modeling and monitoring the AMS design and supports PSL as the specification language. An FPGA implementation of assertion based monitor is presented in [36]. The authors used PSL to generate an asynchronous monitor which is robust to process, temperature and voltage variations and suitable for ASIC designs. Nevertheless, the work in [36] is unable to support both analog and mixed circuits or sequential extended regular expression (SERE) [2] in PSL.

A more recent work [21] introduces a methodology to define mixed signal assertions (MSA) for verification by combining PSL and STL. In this work the specifications for digital and analog parts are translated into PSL and STL, respectively, as either precondition or postcondition. An MSA is then constructed by combining the precondition and postcondition with an implication. Assertion based verification or formal verification could then be carried out given the formalized properties. The authors applied the MSA to a first order delta-sigma converter and checked several properties. The work was validated within the MLDesigner [35] tool with an enhanced assertion monitoring library. In the research reported in this thesis, we use one single formalism, namely SRE (System of Recurrence Equation) [3], to express PSL properties for both analog and digital parts. Additionally, we offer a complete methodology including a simulator and an online monitor. In [3], an offline assertion based verification is introduced, where SREs are used to model the AMS design. Our work is different from [3] in two aspects. First, we use online monitoring to achieve verification. Secondly, we present a tool, named C-SRE [1], which

simulates AMS designs modeled with SREs, reads PSL properties in SRE notations and performs the online monitoring.

#### 1.3.2 Statistical Runtime Verification

Statistical verification can be divided into three main categories: statistical theorem proving, statistical model checking and statistical runtime verification. Although several interesting advances have been made in statistical theorem proving, this technique is still in its infancy. The theorem for continuous random variables and random processes is needed to handle the analysis and verification of AMS and hybrid system [19]. The model checking method has been advanced first to complement general model checking. In [47], the authors present an independent model checking approach for verifying probabilistic properties of discrete event systems. The probabilistic properties were expressed using continuous stochastic logic (CSL) [5] formulas. These formulas were then verified through Monte Carlo simulations and statistical hypothesis testing. The verification procedure provides two parameters,  $\alpha$  and  $\beta$ , which represent the probability of making a wrong decision in checking whether a formula is true or false. In a related work [48], the author presents a probabilistic model checking method to bound the probability of error, mentioned in |47|, for the indifferent region (i.e., the region where both acceptance and rejection decisions can not be made). A symmetric polling system was studied to demonstrate the performance of the method. Following the statistical model checking approach in [47, 48], the authors in [7] applied this technique to a class of AMS circuits for the first time. The saturation property of a third order delta-sigma converter was verified both in time and frequency domains. However, the issues of state explosion and excessive computation time still prevail in statistical model checking.

Statistical runtime verification has also been investigated in the past. One of the most important works is [42] where the authors introduce a methodology

to verify quantitative and probabilistic properties in a real-time system at runtime. The quantitative specification was realized using Meta Event Definition Logic (MEDL) [23] which is based on LTL. The probabilistic properties are specified using time-bounded temporal operators and probabilistic operators. Statistical hypothesis testing technique was employed to evaluate the probabilistic properties and to make decisions about acceptance and rejection. Whenever the decision is made, a confidence level and error margin is provided. The monitor was implemented in a runtime verification tool termed MaC (Monitoring and Checking) [24] and performed in an online fashion. In this thesis, we present a methodology for statistical runtime verification for AMS designs.

## 1.4 Proposed Methodology

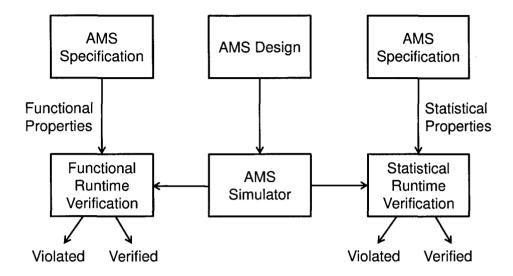

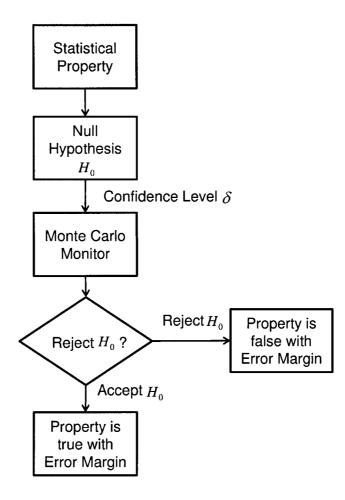

The general methodology for runtime verification of AMS designs is shown in Figure 1.3. The AMS design is modeled and then simulated using an AMS simulator. The properties of the AMS design are derived from the system specification. The satisfaction of the properties is checked based on the output of the simulator and the parameters of the design environment at runtime.

In this thesis, we employ the System of Recurrence Equation (SRE) [3] to model the AMS design. The simulation is done using an SRE based simulator. The properties are categorized into two classes: functional properties and statistical properties. A functional property describes the functional behavior of an AMS design. A statistical property on the other hand is used to describe stochastic or random behavior of the system. These properties are determined using statistical methods. During the runtime verification process, two different monitors are used for each kind of property. For functional property, an *online* monitor is constructed using SRE notation. For statistical property, a statistical monitor is designed to perform statistical runtime verification. The *online* monitor reports the violation or

Figure 1.3: Runtime Verification Methodology

satisfaction and terminates the simulation as soon as it detects a violation. By doing this, the simulation resources are saved as the simulation for AMS design is usually very time consuming. The statistical monitor is capable of making the decision of the property satisfaction decision with the confidence level and error margin.

### 1.5 Phase Locked Loop

In this thesis, we will apply the proposed methodology on a phase locked loop (PLL) based frequency synthesizer as case study. A PLL is considered as a classical AMS system. Its theory was first developed by H. De Bellescize in 1932 [11]. The applications of a PLL can be found in many areas: in wireless communication, a PLL can act as a frequency synthesizer in radio frequency (RF) receivers to provide a desired frequency; for serial link and optical communications, it is used in data and signal recovery circuits; in microprocessors, it works as a clock multiplier unit. In general, PLL deals with clock or frequency for the system.

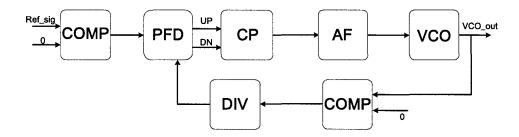

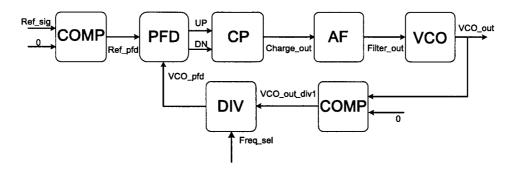

Frequency synthesizer is a basic building block in modern communication devices such as cellular phones and GPS systems. It is capable of generating a certain range of frequency. The PLL based frequency synthesizer shown in Figure 1.4 is the most widely used architecture. It is composed of a comparator (COMP), a phase and frequency detector (PFD), a charge pump (CP), an analog filter (AF), a voltage controlled oscillator (VCO) and a frequency divider (DIV). It consists of pure analog components (i.e., analog filter and VCO), pure digital components (i.e., PFD and divider) and mixed signal components (i.e., comparator and charge pump).

Figure 1.4: General PLL Architecture

The PLL operates on the principle of negative feedback control. The PFD detects the frequency and phase difference between the reference signal and VCO output. This difference produces appropriate voltage through the charge pump. The analog filter removes any high frequency noise of the voltage signal. The filtered voltage signal drives the VCO. The frequency of the VCO output signal is proportional to its input voltage. The VCO output is fed back to the PFD block through a frequency divider. The two comparator blocks convert sinusoid input to a square wave output of the same frequency and phase. Comparing the frequency and phase of the reference signal and VCO output feedback signal, PFD produces a new difference value and affect VCO output accordingly. This process continues until the phase and frequency of the VCO output coincide with the reference signal.

#### 1.6 Thesis Contributions

In this thesis, a comprehensive runtime verification methodology for the Analog and Mixed Signal design is presented. The contributions of the thesis can be summarized as follows:

- We used the System of Recurrence Equations (SRE) to model the AMS design and to express PSL properties.

- We developed a runtime functional verification methodology for AMS designs.

The proposed verification technique works in an *online* fashion and has the potential to save computational resources.

- We developed a statistical runtime verification methodology for AMS designs.

The statistical properties are verified in an *offline* fashion, where the monitor reports the verification result along with a confidence level and error margin.

- We applied the whole runtime verification methodology to a Phase Locked Loop based frequency synthesizer as case study. The frequency synthesizer was simulated in a SRE based simulator. The functional properties were checked using online monitoring at runtime. The jitter noise properties were analyzed using the proposed statistical runtime verification.

#### 1.7 Thesis Outline

The rest of the thesis is organized as follows: Preliminaries on SRE, PSL, and basic concepts on probability and statistics are described in Chapter 2. The SRE based simulator is also introduced in this chapter. Chapter 3 presents details of the runtime verification methodology for AMS designs including both functional and statistical runtime verification approaches. In Chapter 4, we describe the modeling and verification of the PLL based frequency synthesizer. Several interesting properties of

the PLL are checked and experimental results are described . Finally, Chapter 5 concludes the thesis and suggests avenues for future work.

## Chapter 2

## **Preliminaries**

In this chapter, we introduce the preliminary components that the runtime verification methodology is built on. They are SRE, PSL, SRE based simulator, and some basic concepts in probability and statistics as well as an introduction to Monte Carlo simulation.

## 2.1 The System of Recurrence Equations (SRE)

A recurrence equation or a difference equation is the discrete version of an analog differential equation [3]. A recurrence equation defines a relation between consecutive elements of a sequence. The notion of recurrence equation is extended to describe digital circuits using the normal form: generalized If-formula [3].

**Definition 1** Generalized If-formula The generalized If-formula is a class of symbolic expressions that extend recurrence equations to describe digital systems. Let i and n be natural numbers. Let  $\mathbb{K}$  be a numerical domain in  $(\mathbb{N}, \mathbb{Z}, \mathbb{Q}, \mathbb{R} \text{ or } \mathbb{B})$ , a generalized If-formula is one of the following:

• A variable  $X_i(n)$  or a constant C that take value in  $\mathbb{K}$

- Any arithmetic operation  $\diamond \in \{+, -, \times, \div\}$  between variables  $X_i(n)$  that take values in  $\mathbb{K}$

- A logical formula: any expression constructed using a set of variables  $X_i(n) \in \mathbb{K}$  and logical operators: not, and, or, xor, nor, . . . etc.

- A comparison formula: any expression constructed using a set of variables  $X_i(n) \in \mathbb{K}$  and comparison operators  $\alpha \in \{=, \neq, <, \leq, >, \geq\}$

- An expression IF(X, Y, Z), where X is a logical formula or a comparison formula and Y, Z are any generalized If-formula. Here,  $IF(X, Y, Z) : B \times \mathbb{K} \times \mathbb{K} \longrightarrow \mathbb{K}$  satisfies the axioms:

- 1. IF(True, X, Y) = X

- 2. IF(False, X, Y) = Y

The System of Recurrence Equations is defined as follows [3]:

#### Definition 2 The System of Recurrence Equations (SRE)

Consider a set of variables  $X_i(n) \in \mathbb{K}, i \in V = \{1, ..., k\}, n \in \mathbb{Z}, \text{ an } SRE \text{ is a } system \text{ of the form:}$

$$X_i(n) = f_i(X_j(n-\gamma)), (j,\gamma) \in \epsilon_i, \forall n \in \mathbb{Z}$$

(2.1)

where  $f_i(X_j(n-\gamma))$  is a generalized If-formula. The set  $\epsilon_i$  is a finite non empty subset of  $1, \ldots, k \times \mathbb{N}$ . The integer  $\gamma$  is called the delay.

## 2.2 Property Specification Language: PSL

The Property Specification Language (PSL) is a language for the formal specification of hardware [2]. It is used to describe properties that are required to hold in the design under verification. PSL provides a means to write specifications that are

both easy to read and mathematically precise. It is intended to be used to define a functional specification on one hand and as input to functional verification tools on the other hand. Thus a PSL specification is an executable documentation of a hardware design. PSL is also an extension of the standard temporal logics LTL and CTL [2].

PSL consists of four layers: Boolean, temporal, verification and modeling layer [13]. The Boolean layer provides the Boolean expression to temporal layer. The temporal layer is the heart of PSL where complex temporal relations between signals can be expressed. The verification layer is used to tell the verification tools what to do with the behavior of the design inputs and to model auxiliary hardware that is not part of the design, but is needed for verification [2]. The modeling layer provides a means to model behavior of design inputs and to declare and give behavior to auxiliary signals and variables. Only the Boolean and temporal layers are used in our methodology for AMS runtime verification.

The temporal layer enhances LTL with regular expressions [12] and is used to describe the relationships between Boolean expressions of the Boolean layer over time. Instead of using Boolean expressions, the basic properties are employed in our methodology. The temporal layer is composed of the Foundation Language (FL) [13] and the Optional Branching Extension (OBE) [13]. The FL is used to describe properties of single traces, while OBE is used to express properties according to multiple traces. The Foundation Language is composed of two styles: LTL (Linear Temporal Logic) and SERE (Sequential Extended Regular Expression) [2]. In this thesis, we concentrate on the FL properties. Definition 1 shows the syntax of an SERE expression.

## Definition 3 Syntax of Sequential Extended Regular Expressions (SEREs) [3]

• if b is a Boolean expression, then b is a SERE

- if r is a SERE, then r[\*] is a SERE (finite consecutive repetitions)

- if  $r_1$  and  $r_2$  are SEREs, then the following are SEREs:

- the consecutive concatenation of two sequences,  $r_1; r_2$

- one-state overlapping concatenation  $r_1:r_2$

- disjunction of sequence  $r_1|r_2$

- overlapping sequences  $r_1 \& r_2$

- length-matching sequence  $r_1 \&\& r_2$

#### 2.3 C-SRE Simulator

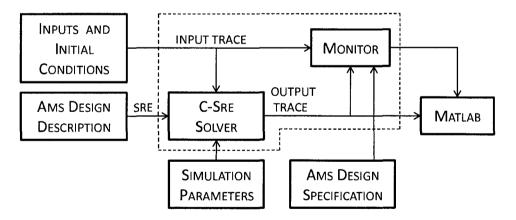

The proposed modeling technique and *online* monitoring are implemented in a tool named C-SRE. Figure 2.1 shows the C-SRE simulator framework.

Figure 2.1: C-SRE Simulator Framework

The C-SRE tool solves a system of recurrence equations describing the behavior of an analog and mixed signal system. There are four main inputs to the tool. They are: (1) The AMS design behavior described using continuous-time (CT), discrete-time (DT) and discrete-events (DE) SRE notations; (2) PSL property monitors expressed in C language; (3) Various inputs and initial conditions to

the design; and (4) Simulation parameters such as minimum and maximum time step sizes, and simulation duration etc. The tool output contains the results of executing the monitor in an online fashion, along with various supporting signal traces for easy visualization of the results.

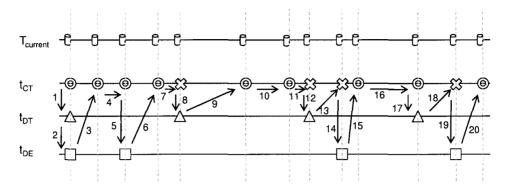

The C-SRE solver is the core of the simulator. It guarantees that the CT, DT or DE SREs are executed at an appropriate instant of time to simulate the correct transient behavior of the circuit. The scheduling algorithm is explained below: Let  $T_{CT}$ ,  $T_{DT}$  and  $T_{DE}$  be the continuous time, discrete time, and discrete event time steps, respectively. If we assume that  $T_{CT}$  is always the smallest time step taken during the simulation, we can achieve both a desired time resolution and accuracy.  $T_{DT}$  is uniformly spaced in time and is known in advance. The size of  $T_{CT}$  and  $T_{DE}$  is determined dynamically during the simulation. In an AMS design, the continuous-time, discrete-time and discrete-event processes may interact with each other. The discrete-time part of the design only interacts at intervals of  $T_{DT}$  with the other parts. The simulation time advances by following four rules given below:

- If  $T_{CT} = T_{DT}$  and  $T_{CT} = T_{DE}$  then update the DE and DT SREs

- If  $T_{CT} = T_{DT}$  and  $T_{CT} < T_{DE}$  then update the DT SREs

- If  $T_{CT} < T_{DT}$  and  $T_{CT} = T_{DE}$  then update the DE SREs

- If  $T_{CT} < T_{DT}$  and  $T_{CT} < T_{DE}$  then update the CT SREs

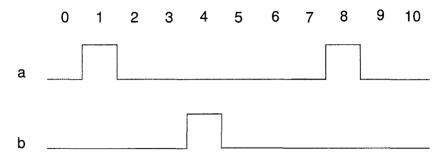

where  $t_{CT} = t_{CT} + T_{CT}, t_{DT} = t_{DT} + T_{DT}, t_{DE} = t_{DE} + T_{DE}$  and  $T_{current} = MIN(t_{DT}, t_{CT}, t_{DE})$ . Figure 2.2 illustrates sample time points at which continuous-time (circle), discrete-time (triangle), and discrete-event (square) SREs have to be executed so as to simulate the correct behavior of the system. The numbers in the figure show the sequence of operations. The discrete time steps (triangle) are equally spaced where as the continuous time (circle) and discrete event (square) time steps are determined dynamically during the simulation. The simulation starts with

Figure 2.2: Timing Diagram

initialization and then proceeds guided by the scheduling algorithm. It terminates when the current simulation time ( $T_{current}$ ) either exceeds or becomes equal to the maximum simulation time. The algorithm described above guarantees that SREs execute in proper sequence in order to simulate the correct behavior of the circuit. For a detailed description of the C-SRE simulator, please refer to [1].

# 2.4 Basic Concepts in Probability and Random Process

The basic definitions and concepts in probability and random process are briefly reviewed in this section. These concepts are essential for the understanding of statistical hypothesis testing method.

#### 2.4.1 Random Variables

A random variable is a variable such that we do not know what specific value it will take on. We do know, however, the possible values it can assume and the probabilities of those values. There are two kinds of random variables: discrete random variables and continuous random variables. A discrete random variable can take on values from a finite or countably infinite set of numbers. Discrete

random variable arises in many applications involving counting. Most commonly used discrete random variable is the bernoulli random variable which is used to model the coin toss experiment. A *continuous random variable* can take on values from an interval of real numbers such as voltage, current or noise. Normal or gaussian random variable is the most commonly encountered continuous random variable in both manmade and natural phenomena.

#### 2.4.2 Distribution Functions

#### Distribution Functions for Discrete Random Variables

Let X be a discrete random variable and suppose that the possible value it can assume are  $x_1, x_2, x_3, \dots$  Suppose that these values have probabilities given by

$$f(x_i) = P(X = x_i)$$

$i = 1, 2, 3, ...$  (2.2)

$f(x_i)$  is called the probability mass function (PMF). The cumulative distribution function, or CDF, for a discrete random variable X is defined as given by

$$F(x) = P(X \le x) \tag{2.3}$$

where x is any real number, i.e.  $-\infty < x < \infty$ . The CDF for a given value a can be obtained from the PMF by

$$F(a) = P(X \le a) = \sum_{x_i \le a} f(x_i) \qquad i = 1, 2, 3, \dots$$

(2.4)

#### Distribution Functions for Continuous Random Variables

The cumulative distribution function (CDF) for a continuous random variable X is defined by

$$F(x) = P(X \le x) = P(-\infty < X \le x) = \int_{-\infty}^{x} f(t)dt$$

(2.5)

It is a positive and monotonically increasing bounded function. The probability that a random variable X lies between the interval (a, b) is given by

$$P(a < X < b) = \int_{a}^{b} f(t)dt \tag{2.6}$$

The probability density function (PDF) for a continuous random variable is given by

$$f(x) = \frac{dF(x)}{dx} \tag{2.7}$$

and

$$f(x) \ge 0 \tag{2.8}$$

$$\int_{-\infty}^{\infty} f(x)dx = 1 \tag{2.9}$$

F(x) is a positive bounded function.

#### 2.4.3 Statistics

In statistics, we are interested in observing the behavior of a large group of objects and drawing conclusions based on our observation. The entire group is usually called a population. It can be finite, such as the final exam score of 500 students, or infinite, for example a study of the fairness of a particular coin, the population of all possible sequences of tosses of the coin is infinite. In practice, instead of investigating the entire group, which is difficult or impossible to do, we examine a small part of the population, which is usually called a sample.

#### 2.5 Monte Carlo Simulation

Monte Carlo method originated in the 1940's [33]. It refers to a method of solving problems using random variables. It is widely used in the estimation of phenomena involving stochastic processes. One of the most important components of Monte Carlo simulation is the random number generator which generates random numbers without bias. The random numbers generated by computer softwares function are not truly random. They are generated based on a deterministic algorithm [27] and are sometimes called pseudo random numbers. The basic idea behind the Monte Carlo method is to sample the model of the true population of interest. This is followed by calculating the statistics of interest. The sampling and calculation procedure is repeated for M trials. The investigation of the distribution characteristics of the statistics is carried out based on those M experiments. When the Monte Carlo method is applied in hypothesis testing, we sample from a distribution which is known or assumed. The Monte Carlo hypothesis testing algorithm used for statistical runtime verification is described in detail in Chapter 3.

# Chapter 3

# Runtime Verification Methodology

In this chapter, we present the proposed runtime verification methodology for AMS designs. It consists of SRE modeling, functional runtime verification methodology and statistical runtime verification.

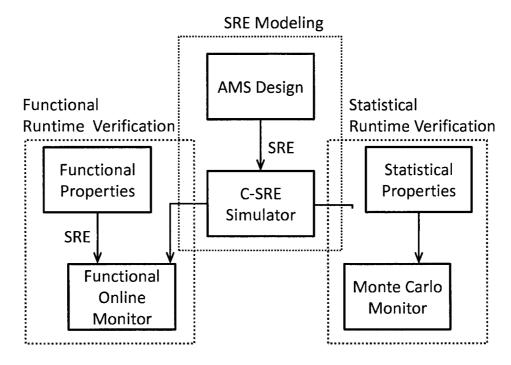

## 3.1 Overall Methodology

The proposed methodology contains three stages: the modeling stage, the functional runtime verification stage, and the statistical runtime verification stage. As shown in Figure 3.1, in the modeling stage the AMS design is modeled using SRE notations and delivered to the C-SRE simulator. In the functional verification stage, the functional properties derived from the AMS system specifications are verified using online runtime verification. The statistical properties which summarize the stochastic behavior of the AMS design is performed in statistical verification stage. The AMS system with stochastic process is modeled using SRE and simulated in C-SRE simulator as well. The functional runtime verification is performed using online monitoring technique and the monitor is implemented in C programming language incorporated with the C-SRE simulator. The statistical runtime verification is carried out in an offline fashion as all the information from the simulation

trace is needed. The statistical monitor is implemented in Matlab [32] environment.

Figure 3.1: Overall Methodology

In the following sections, we describe the SRE modeling, the online runtime verification and the statistical verification, respectively.

# 3.2 SRE Modeling of AMS Design

The modeling stage is the first step of the proposed runtime verification methodology. The AMS system is modeled using a system of recurrence equations (SRE). In this section, we describe how AMS systems can be modeled using SRE.

SRE is used to model the system at a high level abstraction. The SRE modeling procedure of AMS designs usually begins with the mathematical model of the system. An AMS design is usually a complex mixture of pure analog, pure digital or mixed signal components. For digital blocks, the SRE can be generated based

on their logic function. The logic function can be expressed as difference equations which are already SRE (Definition 2). For analog components, we have two potential options to generate SRE. First, we can write the recurrence equation based on time domain differential algebraic equations (DAEs) through a discretization (i.e., in discrete form). However, most analog components are expressed using transfer function in frequency domain. The second option allows the use of the transfer function. We use Impulse-Invariant z transformation [6], which is a frequency transformation of discrete-time signal, to find z domain [38] approximation of the s domain transfer function of an analog component. Then, we apply the inverse of s transform to the s domain transfer function to generate time domain difference equation and convert it into equivalent SRE model. For mixed signal components, the input and output relation can be expressed using SRE notations. At the end of modeling we are left with a system of recurrence equations (SREs) which accurately describe the behavior of the system.

The SREs are then the input to the C-SRE simulator introduced. The sequence of the SREs has to be exactly the same as that of the original system. The outputs of each component of the AMS design can be conveniently plotted using a graphic interface such as Matlab [32]. The detailed examples of modeling the AMS design are illustrated in the case study of Chapter 4.

## 3.3 Runtime Verification with Online Monitoring

In functional runtime verification stage, the functional properties of AMS system are verified in an *online* fashion. We first use PSL to formulate the property of the AMS system. The PSL expression is then translated into SRE notation to construct a monitor. The consistency of the monitor and the modeling allows us to achieve *online* monitoring. In this section, we first describe how to convert PSL properties into SRE notations, followed by the functional runtime verification methodology.

### 3.3.1 Writing PSL using SREs

As an assertion language, PSL contains four layers [12]: Boolean, temporal, verification and modeling layer. The verification layer provides the communication and interaction between the property and the verification tool. The modeling layer is used to define the verification environment for the tool. The Boolean layer constructs the basic expressions for the property. The temporal layer, where the temporal relations between the signals are expressed, is the heart of the PSL. In this thesis, we consider the Boolean layer and the temporal layer only. In following, we will describe how to write PSL properties using SRE in terms of the Boolean layer and the temporal layer, respectively.

#### **Boolean Layer**

The Boolean layer specifies expressions of the design and associated signals which evaluate in a single cycle. The evaluation result is either true or false. In PSL the analog description to a Boolean variable is an inequation which is built using signals and registers of the AMS design [3]. This expression is defined as the *Basic Property* [3]:

#### Definition 4 Basic Property

Let x be the name of an AMS signal (or register), a basic property p is a logical formula defined as follows:  $p = x \diamond y$ , where  $\diamond \in \{<, \leq, >, \geq, =, \neq\}$  and y is a value, a name of a signal (or a register) in the design or an arithmetic function built using the design signals.

The Boolean expression can be written in SRE according to the logic it involves. Suppose that a and b are both basic properties, the expressions a -> b and a <-> b produce Boolean results, true or false. The expression a -> b can be expressed in SRE as

and the SRE expression of a <-> b is given by

The two SREs employ the nested form of the generalized If-formula.

#### Temporal Layer

The Temporal Layer is used to specify temporal chains of events of Boolean expressions. In AMS design, these Boolean expressions are replaced with basic properties. The temporal layer consists of the Foundation Language (FL) and the Optional Branching Extension (OBE). FL is a linear temporal logic which embeds a customized version of Regular Expression, called the Sequential Extended Regular Expression (SERE). OBE is a class of the computational tree logic (CTL) [15] language. FL and OBE cannot be mixed in PSL property. In this thesis, we focus on SERE and FL expressions only.

For example, the PSL property shown below is in the temporal layer. It contains SERE and Boolean expression as well as LTL style property. In order to translate such complex PSL into SRE, we have to translate each sub-properties and join them together based on the temporal operator.

$$\underbrace{\text{always}\{\text{req;ack;!cancel}\}}_{SERE}\underbrace{\text{next[2]}\underbrace{(\text{ena}\,|\,\text{lenb})}_{LTL}}_{Emporal\ Layer}$$

The SERE concatenation operator (;) constructs an SERE that is the concatenation of two other SEREs. The property req; ack holds tightly on a path if and only if there is a future cycle n, such that req holds tightly on the path up to and including the  $n^{th}$  cycle and ack holds tightly on the path starting at the  $n+1^{th}$  cycle. In order to write SERE expression in SRE, cycle should be the whole time

cycle space (i.e., for all n). The SRE notation for the property req; ack can be given by

$$IF\{\prod_{i=0}^{n} req(n), IF\{ack(n+1), true, false\}, false\}$$

FL properties describe single or multi-cycle behavior built from Boolean expressions, sequential expressions, and subordinate properties. The most basic FL Property is a Boolean expression. An FL Property enclosed in parentheses (), as opposite to SERE that is identified using curly braces  $\{\}$ . The compound FL properties can be converted into SRE notation by nesting the operands of the FL property according to the temporal logic operator. In the example above, next[2](ena||enb) is an FL property. The *next* operator is in weak semantics which means that the Boolean expression is not required to happen at the next second cycle on the path. The property holds in two cases: (1) the path ends before the second cycle; (2) the operand (ena||enb), which is a basic FL property, holds at the next second cycle. Suppose that the path length is denoted by N and the current cycle is denoted by n. The SRE of this FL property can be described as

IF

$$\{n+2>N$$

, true, IF $\{ena(n+2)=1 \lor enb(n+2)=1$ , true, false $\}\}$

The SRE notation can be implemented using if-else statement in any programming language such C/C++, Matlab or VHDL. The transformation from PSL to SRE allows us to achieve the *online* runtime verification for AMS designs.

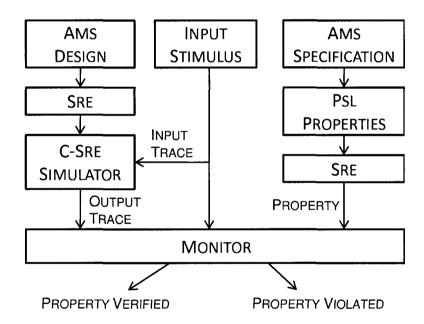

## 3.3.2 Online Monitoring

The verification flow of the *online* monitoring of an AMS design is shown in Figure 3.2. The AMS design is modeled using SRE based on the circuit description and simulated using the C-SRE simulator. Design properties are formally expressed in PSL. The PSL expression is then converted to the SRE notation. Finally, the input

stimulus and output traces are delivered to the monitor. The monitor evaluates the inputs and outputs of the simulator and checks whether the behavior satisfies the design specification. The monitoring is performed in an *online* fashion which means if the property is satisfied, the monitor reports the satisfaction; otherwise, the monitor terminates the simulation at the cycle when the violation occurs.

The input stimulus includes the input signal and environment such as control signals. The output trace of the simulator can be either from any observation point or from any component within the system. The AMS specifications we focus on are written in temporal logic. The evaluation of the relation between input and output with the design specification is carried out within the monitor.

Figure 3.2: Online Runtime Verification

The monitor is used to check whether the current simulation behavior satisfies a given property of correctness. With the help of Basic Property (Definition 3), the properties of AMS design can be expressed properly in PSL. The properties are then translated into recurrence sequence notations. In our methodology, the input and output traces are available to the monitor at each simulation time instant.

Incorporated with the property checker (monitor) described above, at each time instant of the simulation, the violation of the property is also checked. The process is carried out as long as no violation is detected within simulation trace. Moreover, by taking advantage of the C-SRE simulator, which records all the transient data of all circuit blocks at runtime, the monitor is able to observe the property of individual block. This is useful when we want to verify the functionality of single component in a complex design. This allows us to check the interface between two components and the complex effects of one component brought by others. These two advantages enable us to verify large system with many blocks in a realistic environment.

There are two categories for PSL properties: safety property and liveness property. A safety property claims that something bad will never happen. For example, the property "after the frequency select signal Freq\_sel is activated, the PLL will lock at the desired frequency within the lock time 1.5ms" is a safety property. This property verifies that the PLL will lock within 1.5ms after the activation of Freq\_sel. If the PLL cannot lock within this period or it locks at a different frequency, the property fails. This safety property guarantees that the PLL system functions correctly. A liveness property claims that something good will eventually happen. For example, the property "after the frequency select signal Freq\_sel is activated, the PLL will lock sometime in the future" is a liveness property. It is expected that the PLL will lock eventually after the activation of Freq\_sel.

The temporal operator in PSL can be either strong or weak. A strong temporal operator is denoted by concatenating an exclamation point (!) to the ordinary operator. Examples of strong temporal operator are eventually! and next!. The operator without an exclamation point such as next is weak. Both strong and weak operators have the terminating condition. The terminating condition is a Boolean expression and the occurrence of it causes the property to complete. For example, the terminating condition of the property always(a -> next[3] b) is that signal b holds. There is no requirement about the terminating condition for

the weak operator, while the strong operator requires that the terminating condition eventually happen. The PSL property using a weak temporal operator will hold as long as nothing else has gone wrong. For example, in the case that the simulation path ends before three cycles after signal a holds, the property a -> next[3] b will holds because if we keep run the simulation for a few more cycles, the terminating condition might happen. On the other hand, in the case that the simulation path is not long enough, the property using a strong temporal operator will not hold, even if nothing else has gone wrong. Two properties always(a -> next[3] b) and always(a -> next![3] b) have different results when they are applied to the same simulation path shown in Figure 3.3. The terminating condition happens once at cycle 4 and the simulation path ends at 10. The property using weak operator holds because there is no requirement for the termination condition to happen again at cycle 11. However, the property using strong operator fails to hold. The reason is that the property requires that the terminating condition occur based on the simulation path shown in Figure 3.3 and does not consider what will happen after the cycle 10. The difference between weak and strong operators is important when the simulation path is "too short". For offline monitoring, the strong operator is difficult to achieve because we have to manually change the simulation path to make sure that it is long enough for the occurrence of the terminating condition. On the other hand, online monitoring is able to fully support the strong operator because the simulation keeps running until the violation is detected or the terminating condition of the property occurs.

Table 3.1 compares online and offline monitoring methods in terms of their support to safety and liveness properties and strong and weak semantics. In summary, the online monitoring is not only a good complement to offline as shown in Table 3.1, but also it can save the computational resource in terms of simulation time compared to offline. We will see more examples of online monitoring in the following chapter and the comparison with offline method in terms of simulation

Figure 3.3: Online Runtime Verification

time and memory usage.

Table 3.1: Basic Comparison of Online Method and Offline Method

|                   | Online monitoring | Offline monitoring |

|-------------------|-------------------|--------------------|

| Safety property   | Yes               | Yes                |

| Liveness property | Yes               | Yes                |

| Strong semantics  | Yes               | No                 |

| Weak semantics    | Yes               | Yes                |

## 3.4 Statistical Runtime Verification

In this section, we will present the statistical runtime verification methodology using Monte Carlo monitoring. The monitor is constructed to perform statistical hypothesis testing using Monte Carlo simulation. We first introduce statistical hypothesis test and the theory behind it. Then we describe how Monte Carlo method is applied to the statistical hypothesis test and to the evaluation of the hypothesis test performance. Finally we present the runtime verification methodology for the verification of statistical properties of AMS designs.

### 3.4.1 Hypothesis Testing

#### Statistical Hypothesis Testing

Statistical hypothesis testing is a technique which provides a decision making procedure about logic statements based on statistical information. The conclusion is drawn with a confidence level and an error estimate. Hypothesis testing is generally formulated in two parts. They are null hypothesis, denoted by  $H_0$ , which is what we want to test and alternative hypothesis, denoted by  $H_1$ , which is what we want to test against the null hypothesis. If we reject  $H_0$  based on our statistical investigation, then the decision to accept  $H_1$  is made. For example, we want to determine whether there is a difference in quality between two products A and B. The null hypothesis might be that there is no difference between the A and B. Then the alternative hypothesis might be that there is a difference (i.e., that one is better in quality than the other). The steps in statistical hypothesis testing are listed below

- 1. Determine the null and the alternative hypotheses.

- 2. Take a random sample from the population of interest.

- 3. Calculate a statistic from the sample that provides information about the null hypothesis.

- 4. If the value of the statistic is consistent with  $H_0$ , then accept  $H_0$ .

- 5. If the value of the statistic is inconsistent with  $H_0$ , then reject  $H_0$  and accept  $H_1$ .

#### **Error Bounds**

There are two kinds of error bounds that apply when we are making a decision in statistical hypothesis testing. They are known as Type I error and Type II error [31]. A Type I error, or false positive, occurs when we reject  $H_0$  which is actually true. A

Type II error, or false negative, arises when we accept  $H_0$  which is actually false.  $\alpha$  and  $\beta$  denote the probability of Type I error and Type II error respectively. Formally,

$$\alpha = Pr\{\text{reject } H_0 | H_0 \text{ is true }\}$$

$$\beta = Pr\{\text{accept } H_0 | H_0 \text{ is false}\}$$

Typically,  $\alpha$  is the maximum probability of Type I error tolerated. In hypothesis testing, we are looking for significant evidence that the null hypothesis  $H_0$  is false, namely that  $H_1$  is valid. In order to avoid changing decision status unless there exists sufficient evidence guiding us, the probability of incorrectly rejecting  $H_0$ , namely Type I error  $\alpha$ , is expected to be controlled.

#### Confidence Level

As defined, the Type I error is the probability of rejecting null hypothesis  $H_0$  while it is true. In other words, it means the likeliness that we accept alternative hypothesis  $H_1$  when  $H_0$  is true. The confidence is drawn according to the compliment of the Type I error  $\alpha$ .  $\alpha$  is also called *significance level*. Formally, the confidence level  $\delta$  is give by:

$$\delta = 1 - \alpha \tag{3.1}$$

For instance,  $\alpha = 0.05$  refers to the confidence level of 95% and  $\alpha = 0.01$  refers to the confidence level of 99%. Before performing the hypothesis testing, the Type I error (i.e., the confidence level) should be established. The reason is that in a hypothesis test we are looking for the significant evidence to reject null hypothesis  $H_0$  (i.e.,  $H_0$  is false) and the probability that  $H_0$  is true needs to be controlled.

#### Tail Test

In order to determine whether or not the observed statistic is consistent with  $H_0$ , we should know the distribution of the statistic under the condition that  $H_0$  is true.

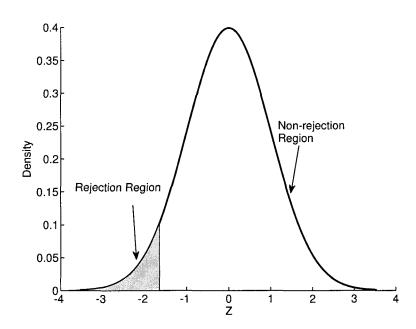

A rejection region is needed to perform the statistical hypothesis test. A rejection region, over which we would reject  $H_0$ , is the area covered by the PDF. The critical value is used to divide the domain of the test statistic into a rejection region and a non-rejection region. The rejection region depends on the distribution of the statistic under  $H_0$ ,  $H_1$  and the Type I error we are willing to tolerate. Generally, the rejection region is located at the tails of the distribution of the test statistic when  $H_0$  is true. The test can take place either in the lower tail or the upper tail which depends on the alternative hypothesis  $H_1$ .

- (a) Upper tail test: If a large value of the test statistic would provide evidence for rejecting  $H_0$ , then the rejection region is in the upper tail of the distribution of the test statistic.

- (b) **Lower tail test**: If a small value of the test statistic would provide evidence for rejecting  $H_0$ , then the rejection region is in the lower tail of the distribution of the test statistic.

#### Hypothesis Testing Algorithm

There are several approaches for hypothesis testing. In this thesis, we address only the critical value approach. It is also important to note that in order to perform the hypothesis test, the distribution of the test statistic under the null hypothesis  $H_0$  is assumed to be known. Before we describe the critical value approach, we first introduce an important concept, namely quantile function.

#### Quantile Function

Quantile function plays an important role in statistics [31]. The quantile  $q_p$  of a random variable X is defined as the smallest number q such that the cumulative distribution function (CDF) P(X) is greater than or equal to some p, where 0 . This can be calculated for a continuous random variable with probability

density function f(x) by solving

$$p = \int_{-\infty}^{q_p} f(x)dx \tag{3.2}$$

for  $q_p$ . The quantile function is the inverse of the cumulative distribution function (CDF) and is given by

$$q_p = quantile(p) = F^{-1}(p) \tag{3.3}$$

The p-th quantile of a random variable X is the value  $q_p$  such that

$$F(q_p) = P(X < q_p) = p \tag{3.4}$$

In general, the quantile function is the inverse of cumulative distribution function (CDF). In hypothesis test, we will see that quantile function is used to determine the decision about rejection of a hypothesis.

#### Critical Value Approach

In hypothesis testing, if the observed statistic is within some region, we reject the null hypothesis. The interval where the null hypothesis is rejected is called *critical* region, or rejection region. The critical value is used to divide the domain of the test statistic into rejection region and non-rejection region. The critical value approach is used to check whether the observed value falls into the rejection region. The procedure of this approach is outlined in Algorithm 1. The critical value approach requires  $\alpha$  and  $T_{obs}$  to perform.  $\alpha$  is the significant level, or Type I error, and  $T_{obs}$  is the observed value calculated by

$$T_{obs} = \frac{\bar{x} - \mu_0}{\bar{\sigma}} \tag{3.5}$$

where  $\bar{x}$  is the sample mean of the random variable,  $\mu_0$  is the mean value under the null hypothesis and  $\bar{\sigma} = \sigma_x/\sqrt{n}$  is the standard error of the sample. The algorithm is performed in two cases: upper tail test and lower tail test. In the case of upper tail

test (from line 1 to line 8), we first calculate the critical value using quantile function and the significance level  $1 - \alpha$  (line 2). The hypothesis test is performed from line 3 to line 7. For upper tail test, we are looking for large significant evidence to reject the null hypothesis  $H_0$ . If the observed value  $T_{obs}$  is greater than the critical value, then we reject  $H_0$ ; otherwise, the decision of accepting  $H_0$  is made. The procedure of lower tail test (from line 9 to line 16) is similar except that the critical value, i.e,. the rejection region, is different. The critical value is calculated based on the significance level  $\alpha$ . In this case, if  $T_{obs}$  is smaller than the critical value, then we reject  $H_0$ ; otherwise, we accept  $H_0$ .

#### Algorithm 1 Hypothesis Testing- Critical Value Approach

```

Require: \alpha, T_{obs}

1: while Upper Tail Test do

critical\_value = quantile(1 - \alpha)

2:

if T_{obs} > critical\_value then

3:

4:

Reject H_0

else if T_{obs} < critical\_value then

5:

Accept H_0

6:

7:

end if

8: end while