# Runtime verification of embedded real-time systems

Thomas Reinbacher · Matthias Függer · Jörg Brauer

Published online: 7 November 2013 © The Author(s) 2013. This article is published with open access at Springerlink.com

**Abstract** We present a runtime verification framework that allows on-line monitoring of past-time Metric Temporal Logic (ptMTL) specifications in a discrete time setting. We design observer algorithms for the time-bounded modalities of ptMTL, which take advantage of the highly parallel nature of hardware designs. The algorithms can be translated into efficient hardware blocks, which are designed for reconfigurability, thus, facilitate applications of the framework in both a prototyping and a post-deployment phase of embedded real-time systems. We provide formal correctness proofs for all presented observer algorithms and analyze their time and space complexity. For example, for the most general operator considered, the time-bounded Since operator, we obtain a time complexity that is doubly logarithmic both in the point in time the operator is executed and the operator's time bounds. This result is promising with respect to a self-contained, non-interfering monitoring approach that evaluates real-time specifications in parallel to the system-under-test. We implement our framework on a Field Programmable Gate Array platform and use extensive simulation and logic synthesis runs to assess the benefits of the approach in terms of resource usage and operating frequency.

**Keywords** Runtime verification · Embedded real-time systems · Past-time logics · Online monitoring

e-mail: fuegger@ecs.tuwien.ac.at

J. Brauer

T. Reinbacher  $\cdot$  M. Függer ( $\boxtimes$ )

Embedded Computing Systems Group, Vienna University of Technology, Treitlstrasse 3, 1040 Vienna, Austria

T. Reinbacher e-mail: reinbacher@ecs.tuwien.ac.at

Embedded Software Laboratory, RWTH Aachen University and Verified Systems International GmbH, Am Fallturm 1, 28359 Bremen, Germany e-mail: brauer@verified.de

### 1 Introduction

Rigorous verification strategies are especially vital for the domain of safety-critical embedded real-time systems [48] where systems often do not only need to comply with a set of functional requirements but also—equally important—with tight timing constraints. Correct behavior of these systems is defined by the sequence of data they produce—either internally or at their physical outputs—complemented with their temporal behavior. The key idea behind formal verification techniques such as model checking [6, 22] is to exhaustively *check all executions* of a structure that is related to an implementation and its environment against given requirements, the latter of which are often formalized in terms of a temporal logic. Exhaustive analysis of programs, however, often suffers from practical infeasibility (due to state space explosion [21]) and/or theoretical impossibility (due to undecidability results).

In runtime verification [9], observers are synthesized to automatically evaluate the *cur*rent execution of a system-under-test (SUT), typically from a formal specification in a logic that is suitable to cover certain forms of real-world specifications. The on-the-fly nature of runtime verification can be coupled with costly overhead [10, 56, 71]. Some mitigated overhead by reducing instrumentation points [34]; others ported the system and/or the observers to a more powerful architecture, such as database systems [8]. These artifacts of runtime verification are not compatible with embedded real-time systems running on ultra-portable hardware with power and performance limitations [65].

To evaluate specifications, runtime verification depends on observations of the state of the SUT. These observations are referred to as events and are input to the observer. However, the SUT's state typically is not directly observable.

An approach classically taken in runtime verification to obtain observations is to instrument the code base, a technique that has proven feasible for a number of high-level implementation languages such as C, C++, and Java [9, 39, 40, 64] as well as for hardware description languages such as VHDL and Verilog [4, 77]. Instrumentation can be done manually, or automatically by scanning programs for assignments and function calls at the level of the implementation language and then inserting hook-up functions that emit relevant events to an observer. However, for the domain of (safety-critical) embedded real-time systems, existing approaches, despite the considerable progress in the past, are not directly applicable; mainly due to the following limitations:

- Source code instrumentation of high-level languages can only capture events that are accessible from within the instrumented software system. Embedded systems [59] often include both hardware and mechanical parts; events from those might go unnoticed for an instrumenting runtime verification approach.

- The timing behavior of the SUT is altered by instrumentation [23, 34]. The additional runtime overhead may drastically impact the correctness of a heavy-loaded real-time application with tight deadlines. The same applies to memory consumption of resource constrained systems. The relevance of this argument is supported by the fact that restricted architectures are often used in critical environments[12, 33, 66], such as in nuclear power plants [28] and spacecrafts [30, Chap. 3].

- Instrumentation may make re-certification of the system onerous (e.g., systems certified for civil aviation after DO-178B [73]).

- In its present shape, runtime verification often analyzes the correctness of high-level code. However, to show that a high-level specification is correctly reproduced by the target system, it is further necessary to show the correctness of the translation of the high-level code into executable code, i.e., the compiler. Despite recent breakthroughs [52, 53], only

few verified compilers are used in practice and flaws introduced by compilers [31, 55, 81] may remain undetected by existing approaches.

- Instrumentation at binary code level may circumvent the process of establishing correctness of the compiler. However, binary instrumentation is incomplete as long as a sound reconstruction of the control flow graph is not obtained from the binary. Despite being an active area of research [7, 35, 46, 67], generating sound yet precise results remains a challenge.

There exist, however, systems and applications [80], where the relevant events can be observed without the need to infuse additional functions into the high-level code. Consider, for example, an implementation of a network protocol, where the task is to check the correctness of data flow between two network nodes. It appears natural to place an additional (passive) node in the network that collects events sent over the network, rather than instrumenting the high-level code of the network nodes. The strength of an approach like this is that collecting of events is non-intrusive, at least, as long as the additional node is passive and does not actively participate in the communication. It is important to observe that information exchange among systems is often performed by standardized interfaces. This is especially the case for embedded real-time systems, at various levels of detail [59, Chap. 3]. For certain systems, wiretapping is the only option left to gain information of the state of the system, for example, if the design includes proprietary hardware or software components.

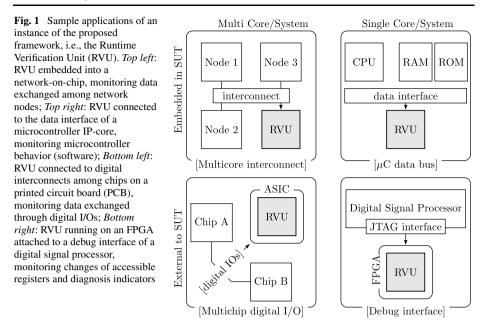

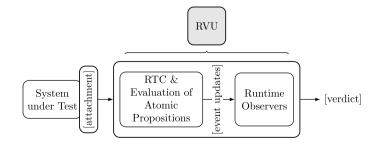

In the light of the discussion above, we proceed by defining requirements of a runtime verification framework targeting embedded real-time systems. We aim at a framework that is transparent to a hardware implementation, so as to be attached to or embedded into various SUTs. Examples of applications are outlined in Fig. 1. We summarize these special requirements as:

**Stand-alone** The runtime verification framework should not only be deployed during the testing phase of the product but also after the product is shipped. Therefore, it should

operate in a self-contained way and not depend on a powerful host computer that executes the observer.

- **Non-intrusive** The resulting observers should be efficient enough to not alter the timing requirements of the SUT. From an algorithmic viewpoint, observers with an a-priory known execution time are of utmost importance so as to statically determine upper bounds of the execution time of the observer. From an implementation point of view, we need to provide measures to passively observe events from the SUT.

- **Timed** To support correctness claims that involve timed properties, the framework should support expressive logics to formalize not only functional but also real-time requirements.

- **Reconfigurable** For the testing phase, the framework should be reconfigurable without requiring to re-synthesize the whole hardware design, which may take dozens of minutes to complete, for example when targeting an Field Programmable Gate Array (FPGA) platform.

## 2 Contributions and roadmap

Our work can be seen as a response to overcome the above limitations that hinder the broad application of runtime verification to embedded real-time systems. This article provides the following contributions toward a *stand alone*, *non-intrusive*, *timed*, and *reconfigurable* hardware runtime verification approach:

- (a) We present on-line observer algorithms that allow one to verify whether a past-time metric temporal logic (ptMTL) formula holds at (discrete) times  $n \in \mathbb{N}_0$ . The algorithms make use of basic operations only and are stated in a way that allows for a direct implementation in hardware, that can run without a host computer. By that our observers fulfill the timed and stand alone requirements.

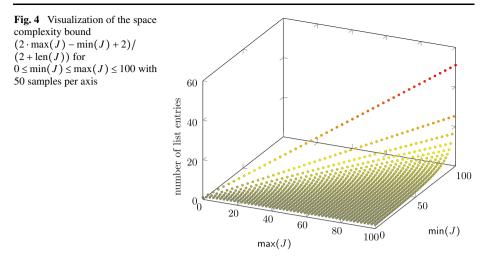

- (b) We formally prove the observers' correctness and derive bounds on their time complexity in terms of gate delays and their space complexity in terms of required memory bits. With *n* being the time an observer algorithm is executed and *J* a non-empty interval we obtain, for the most general of the presented observer algorithms, the ptMTL Since operator  $\varphi_1 S_J \varphi_2$ , a time complexity of  $\mathcal{O}(\log_2 \log_2 \max(J \cup \{n\}))$ , only. The observer's space complexity is dominated by the size of a list it needs to maintain. We show that the list's space complexity is at most  $2\lceil \log_2(n) \rceil \cdot (2\max(J) \min(J) + 2)/(2 + \operatorname{len}(J))$ , where  $\operatorname{len}(J) = \max(J) \min(J)$ . Both complexity results, as well as the fact that our algorithms refrain from loops and recursions and build on simple operations only, enable applications of our runtime verification framework on resource limited platforms that require predictable timing and memory consumption.

- (c) We explain how to derive non-instrumenting efficient realizations of the proposed observer algorithms in hardware. The resulting hardware profits from the simplicity and low complexity of our highly-parallel observer algorithms. In contrast to instrumentation-based runtime verification techniques for software systems our observers are well suited to supervise hardware components. By that, in combination with (b), our observers fulfill the non-intrusive requirement. Although our algorithms are tailored for a hardware implementation, the observers can simply be adopted to run in software too. Reconfigurability of our observers is achieved by, instead of hardwiring the observers inputs and outputs according to their parse tree, letting a programmable, specifically tailored microprocessor control a pool of observers.

With regard to the contributions above, (a) and (b) are an extension of our work we presented at the International Conference on Runtime Verification [71], including detailed correctness proofs for our algorithms and (c) and (d) are unique contributions of this article. Contribution (c) builds on our previous work [69], where we presented a microprocessor designed to evaluate ptLTL specifications in a software-oriented fashion. Using this approach to check ptMTL specifications, however, requires a costly (cf. Sect. 3.3) rewriting to an equivalent ptLTL specifications. Instead, we show how to map the building blocks of our ptMTL observer algorithms into efficient hardware units. This enables our microprocessor to natively evaluate ptMTL specifications in real-time. Both (c) and (d) help us to put the presented real-time observer algorithms into industrial practice.

The contributions of this article are presented as follows. First, Sect. 3 is a primer on temporal logics, which sets the scene for the monitoring algorithms stated in Sect. 4. Section 5 details the key structures of the hardware design and Sect. 6 reports on experimental evidence. We continue with a survey of related work in Sect. 7 and conclude in Sect. 8.

#### 3 Logics for runtime verification

We briefly summarize the temporal logics past-time linear temporal logic (ptLTL) and pasttime metric temporal logic (ptMTL) which are used to specify properties in our framework. Both allow one to specify safety, past-time properties over executions. For further details, we refer the reader to more elaborate sources such as [2, 13, 32, 42, 51, 57].

#### 3.1 Past-time linear temporal logic

A popular logic in runtime verification is the past-time fragment of LTL (ptLTL), mainly due to: (i) observer generation for ptLTL is straightforward [39, Sect. 5], and (ii) ptLTL can easily express typical specifications [54]. Even though past-time operators do not yield the expressive power of full LTL [32, Sect. 2.6], past-time operators often express desired properties from specifications [50, 54]. With • in { $\land, \lor, \rightarrow$ } and  $\sigma$  in the set  $\Sigma$  of atomic propositions, a formula  $\varphi$  is defined as:

$$\varphi ::= true \mid false \mid \sigma \mid \neg \varphi \mid \varphi \bullet \varphi \mid \odot \varphi \mid \Diamond \varphi \mid \Box \varphi \mid \varphi S_s \varphi \mid \varphi S_w \varphi$$

Hereby,  $\odot \varphi$  is the past-time analogue of next and referred to as *previously*  $\varphi$ . Likewise,  $\Diamond \varphi$  is referred to as *eventually in the past*  $\varphi$  and  $\Box \varphi$  as *always in the past*  $\varphi$ . The duals of the until and the weak-until operators are  $S_s$  and  $S_w$ , i.e., *strong since* and *weak since*, respectively. Similar as in LTL [41, Theorem 1], ptLTL can be reduced to the propositional operators plus two past-time operators [58], e.g., to  $\odot$  and  $S_s$ . The satisfaction relation of a ptLTL specification can be defined as follows: Let  $e = (s_t)_{t\geq 0}$  be an execution where  $s_t$  is a state of the system. Denote by  $e^n$ , for  $n \in \mathbb{N}_0$ , the *execution prefix*  $(s_t)_{0\leq t\leq n}$ . For a ptLTL formula  $\varphi$ , time  $n \in \mathbb{N}_0$  and execution e, we define  $\varphi$  holds at time n of execution e, denoted

$e^n \vDash \varphi$ , inductively as follows:

| $e^n \vDash true$ ,                             |                                                                                                                |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| $e^n \not\models false$ ,                       |                                                                                                                |

| $e^n \vDash \sigma$ , where $\sigma \in \Sigma$ | iff $\sigma$ holds on $s_n$ ,                                                                                  |

| $e^n \vDash \neg \varphi$                       | iff $e^n \neq \varphi$ ,                                                                                       |

| $e^n \vDash \varphi_1 \land \varphi_2$          | iff $e^n \vDash \varphi_1$ and $e^n \vDash \varphi_2$ ,                                                        |

| $e^n \vDash \varphi_1 \lor \varphi_2$           | iff $e^n \vDash \varphi_1$ or $e^n \vDash \varphi_2$ ,                                                         |

| $e^n \vDash \varphi_1 \rightarrow \varphi_2$    | iff $e^n \vDash \varphi_1$ implies $e^n \vDash \varphi_2$ ,                                                    |

| $e^n \vDash \odot \varphi$                      | iff $e^{n-1} \vDash \varphi$ if $n > 0$ , and $e^0 \vDash \varphi$ otherwise,                                  |

| $e^n \vDash \varphi_1 S_s \varphi_2$            | iff $\exists j (0 \le j \le n) : (e^j \vDash \varphi_2 \land \forall k (j < k \le n) : e^k \vDash \varphi_1).$ |

The above syntax can be augmented with a set of additional operators [42, 51] to provide a succinct representation of common properties that appear in practice:

$$\varphi ::= \uparrow \varphi \mid \downarrow \varphi \mid [\varphi, \varphi)_s \mid [\varphi, \varphi)_w$$

↑ *φ* and ↓ *φ* are trigger conditions where ↑ *φ* stands for *start φ* (i.e., *φ* was false in the previous state and is true in the current state, equivalent to  $φ \land \neg \odot φ$ ), ↓ *φ* for *end φ* (*φ* was true in the previous state and is false in the current state, equivalent to  $\neg φ \land \odot φ$ ). The interval operators are strong *interval*  $[φ_1, φ_2)_s$  ( $φ_2$  was never true since the last time  $φ_1$  was true, including the state when  $φ_1$  was true, equivalent to  $\neg φ_2 \land ((\odot \neg φ_2) S_s φ_1))$  and weak *interval* (equivalent to  $\Box \neg φ_2 \lor [φ_1, φ_2)_s$ ). In the following we will only refer to the strong since and shortly write *S* instead of *S*<sub>s</sub>. Checking whether a ptLTL formula holds at time  $n \in \mathbb{N}_0$  in some execution  $e = (s_t)_{t \ge 0}$  can be determined by evaluating only the current state  $s_n$  and the results from the predecessor state  $s_{n-1}$  [42]. For example, evaluating the invariant  $φ = \Box σ$  on execution  $e = (s_t)_{t \ge 0}$  can be done by:

$$e^{n} \vDash \boxdot \sigma \Leftrightarrow \bigwedge_{t=0}^{n} (\sigma \text{ holds on } s_{t})$$

$$\Leftrightarrow (e^{n-1} \vDash \boxdot \sigma) \land (\sigma \text{ holds on } s_{n})$$

### 3.2 Past-time metric temporal logic

MTL [2] extends LTL by replacing the qualitative temporal operators of LTL by quantitative operators that respect time bounds. Since we are interested in on-chip observer algorithms, progress of time is provided by the (possibly divided) chip's clock signal, resulting in a discrete time base  $\mathbb{N}_0$ .<sup>1</sup> Time bounds of quantitative operators are given in form of intervals: For *t* in  $\mathbb{N}_0$  and *t'* in  $\mathbb{N}_0 \cup \{\infty\}$ , we write [t, t') for the set  $\{i \in \mathbb{N}_0 | t \le i < t'\}$  and, if *t'* in  $\mathbb{N}_0$ , [t, t'] for the set  $\{i \in \mathbb{N}_0 | t \le i \le t'\}$ . Similar to ptLTL, a restriction of MTL to its past time fragment (ptMTL) is of interest. Formally, a ptMTL formula  $\varphi$  is defined by:

$$\varphi ::= true \mid false \mid \sigma \mid \neg \varphi \mid \varphi \bullet \varphi \mid \varphi S_J \varphi$$

where  $\sigma \in \Sigma$ ,  $\bullet \in \{\land, \lor, \rightarrow\}$ , and J = [t, t'] for some  $t, t' \in \mathbb{N}_0$ . The semantics of *true*, *false*,  $\sigma$ ,  $\neg \varphi$ , and  $\varphi \bullet \varphi$  are as before. Recall that in ptLTL  $\varphi_1 S \varphi_2$  expresses  $\varphi_2$  was true in the past and since then  $\varphi_1$  was true. By way of contrast, satisfaction of  $e^n \models \varphi_1 S_J \varphi_2$  in ptMTL, does not only depend on the observation that  $\varphi_1 S \varphi_2$  holds in the current state, but also on (i) the

<sup>&</sup>lt;sup>1</sup>In our framework, we thus assume time points to be from  $\mathbb{N}_0$ .

time *n* of the current state and (ii) the times  $i \in \mathbb{N}_0$  since when  $\varphi_1 S \varphi_2$  was observed to be true: for at least one such *i*,  $e^i \models \varphi_2$ , and  $n - i \in J$  have to hold. Formally, we define:

$$e^n \models \varphi_1 \ S_J \ \varphi_2 \ \text{iff} \ \exists i \ (0 \le i \le n) : (n - i \in J \land e^i \models \varphi_2 \land \forall j \ (i < j \le n) : e^j \models \varphi_1)$$

Example Many real-time properties, such as

"If the system leaves the idle mode, it has received an according signal in the past 50 clock-cycles."

can be expressed in ptMTL. The above property, e.g., can be formalized by:

$(\downarrow (in idle mode)) \rightarrow (true S_{[0,50]} (received message))$

Not surprisingly, determining satisfaction of an MTL (or ptMTL) formula is computationally more expensive than checking satisfaction of an LTL (or ptLTL) formula [78, Theorem 3.4].

3.3 Rewriting past-time metric temporal logic to past-time linear temporal logic

In a discrete time setting, there is an equivalent ptLTL formula for every ptMTL formula [57], directly leading to an observer algorithm for  $\varphi_1 S_{[a,b]} \varphi_2$ . With  $\odot^i \varphi$  being  $\odot$  applied *i* times to  $\varphi$ , a straightforward generic translation is given by the equivalence:

$$e^{n} \vDash \varphi_{1} S_{[a,b]} \varphi_{2} \iff \exists i (a \le i \le b) : ((\odot^{i}\varphi_{2}) \land (\odot^{i-1}\varphi_{1}) \land (\odot^{i-2}\varphi_{1}) \land \dots \land \varphi_{1}) \\ \Leftrightarrow \bigvee_{i=a}^{b} ((\odot^{i}\varphi_{2}) \land \bigwedge_{j=0}^{i-1} (\odot^{j}\varphi_{1}))$$

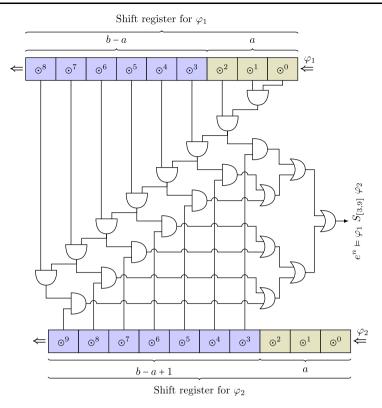

In a hardware implementation, one can make use of shift-registers to store the relevant part of the execution path with regard to the truth values of  $\varphi_1$  and  $\varphi_2$ . We will proceed by a sample implementation making use of the equivalence above.

*Example* Consider the ptMTL formula  $\varphi_1 S_{[3,9]} \varphi_2$ . Rewriting the formula into a hardware implementation, requires two shift registers of length 9 and 8, respectively. With the equivalences from above,  $e^n \models \varphi_1 S_{[3,9]} \varphi_2$  can be rewritten into  $\bigvee_{i=3}^{9} ((\odot^i \varphi_2) \land \bigwedge_{j=0}^{i-1} (\odot^j \varphi_1))$ , which can be realized by the optimized, hand-crafted circuit shown in Fig. 2. Observe that we do not need to store  $\odot^0 \varphi_1$  and  $\odot^0 \varphi_2$  explicitly, as they are immediately available. The circuit accounts for 15 two-input AND gates and six two-input OR gates. In a generalized setting, the proposed circuit requires the following resources:

| – Shift registers (memory):              | $2 \times b - 1$ |

|------------------------------------------|------------------|

| <ul> <li>Two-input AND gates:</li> </ul> | $2 \times b - a$ |

| – Two-input OR gates:                    | b-a              |

With parameters a = 5 and b = 1500, the circuit will occupy  $3 \times b - 2 \times a = 3 \times 1500 - 2 \times 5 = 4490$  two-input gates, and  $2 \times b - 1 = 2 \times 1500 - 1 = 2999$  flip-flops to implement the shift registers, resulting in a huge circuit.

It is important to observe that the chain of AND gates starting at  $\odot^0 \varphi_1$  introduces a gate propagation delay [44, Chap. 9]  $\Delta$  on the signal that is proportional to *b* and delays the output of the verdict  $e^n \models \varphi_1 S_{[a,b]} \varphi_2$ . With a propagation delay  $\delta_{AND}$  of a single AND gate of and an AND chain of length b-1, the total propagation delay equals to  $\Delta = (b-1) \times \delta_{AND}$ . The chain becomes the *critical path* of the circuit and lowers the achievable operational frequency of the observer design. This effect can be alleviated by introducing a pipeline, however, not without the cost of additional memory and control logic.

**Fig. 2** Hardware realization of a rewriting from  $\varphi_1 S_{[3,9]} \varphi_2$  to  $\bigvee_{i=a}^{b} ((\odot^i \psi) \wedge \bigwedge_{j=0}^{i-1} (\odot^j \varphi))$ . The parameters *a* and *b* are set according to the interval in  $\varphi_1 S_{[3,9]} \varphi_2$ , i.e., a = 3 and b = 9, yielding  $\bigvee_{i=3}^{9} ((\odot^i \psi) \wedge \bigwedge_{i=0}^{i-1} (\odot^j \varphi))$

This supports that rewriting ptMTL to ptLTL, albeit theoretically possible, is costly and thus infeasible in practice with an application in mind where the satisfaction relation is checked on-the-fly, i.e., in parallel to the SUT. Rewriting, however, may prove feasible when the observer is executed on a powerful host computer with a capable term rewriting engine at hand, as studied in [72].

#### 4 Observer design for real-time properties

In the following, we discuss the formal design of on-line observer algorithms for specifications in ptMTL in a discrete time model. The design is inspired by the observers described in [11] and extends work on observers for ptLTL [42] which have been built in hardware [63, 68]. We first give a high-level definition of the algorithms and turn to a hardware implementation in Sect. 5.

#### 4.1 Decomposing a specification

In the following let  $e = (s_t)_{t\geq 0}$  be an execution and  $\varphi$  a ptMTL formula. Further, let J = [t, t'], with  $t, t' \in \mathbb{N}_0$ , be a non-empty interval. An observer is an algorithm that, given input  $\varphi$  and

**Fig. 3** Validity of  $e^n \models \varphi_1$  and  $e^n \models \varphi_2$  for prefix of execution e

execution *e*, at each time  $n \in \mathbb{N}_0$ , returns true if  $e^n \models \varphi$ , and false otherwise. We define the return value of our observer algorithm with input  $\varphi$  at time *n* by structural induction on ptMTL formula  $\varphi$ :

- (i)  $\varphi = true$  returns true.

- (ii)  $\varphi = false$  returns false.

- (iii)  $\varphi = \sigma$ , where  $\sigma \in \Sigma$  returns true if  $\sigma$  holds on  $s_n$ , and false otherwise.

- (iv)  $\varphi = \varphi_1 \bullet \varphi_2$  is true if  $e^n \models \varphi_1 \bullet e^n \models \varphi_2$ , where  $\bullet \in \{\land, \lor, \rightarrow\}$ , and false otherwise.

- (v) If  $\varphi$  is a ptLTL formula, we apply the algorithms proposed in [41, 42].

- (vi) For  $\varphi = \varphi_1 S_J \varphi_2$ , we collect all times where  $\varphi_2$  was true in the past and since then  $\varphi_1$  remained true and store them in a list. At time *n* we check if there exists a time  $\tau$  in the list such that  $n \tau \in J$ . If such a  $\tau$  exists we return true, and false otherwise.

Algorithms for cases (i)–(iv) are straightforward. For case (v), we use the algorithm of Havelund and Roşu [41, 42], for which a translation into hardware building blocks (specified in terms of VHDL) is known [68]. Finding an efficient algorithm to detect satisfaction of  $e^n \models \varphi_1 S_J \varphi_2$  requires more sophisticated reasoning, and is the topic of the next sections. We start with efficient observer algorithms for the time-bounded variants of the ptLTL modalities  $\Box \varphi$  and later extend them to an efficient observer algorithm for  $\varphi_1 S_J \varphi_2$ .

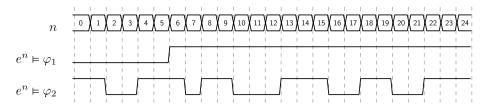

*Running example* In the following, we frequently refer to the execution given in Fig. 3, which describes satisfaction of the two formulas  $\varphi_1$  and  $\varphi_2$  over times  $n \in [0, 24]$ . We say *transition*  $\square$  (*resp.*  $\square$ ) of  $\varphi$  occurs at time n iff  $e^n \models \uparrow \varphi$  in case n > 0 and  $e^0 \models \varphi$  otherwise (resp.  $e^n \models \downarrow \varphi$  in case n > 0 and  $e^0 \models \neg \varphi$  otherwise). In the running example, transition  $\square$  of  $\varphi_1$  occurs at time 6.

4.2 The invariant and exists previously operators

We first discuss specializations of the common operators  $\otimes_J$  (exists within interval J) and  $\Box_J$  (invariant within interval J). In accordance with [6] we define both operators in terms of the Since operator by:

$$\diamondsuit_J \varphi \equiv \operatorname{true} S_J \varphi \qquad \boxdot_J \varphi \equiv \neg \diamondsuit_J \neg \varphi$$

(1)

From a practical point of view, two instances of the *exists within interval* and the *invariant within interval* operators, namely *invariant previously*  $(\square_{\tau})$  and *exists previously*  $(\bigotimes_{\tau})$ , where  $\tau \in \mathbb{N}_0$ , are valuable. They have the intended meaning at least once in the past  $\tau$  time units  $(\bigotimes_{\tau})$  respectively *invariant for the past*  $\tau$  time units  $(\square_{\tau})$ , and are defined by  $\bigotimes_{\tau} \equiv \bigotimes_{[0,\tau]}$  respectively  $\square_{\tau} \equiv \square_{[0,\tau]}$ .

For example,  $(\uparrow \sigma_1) \rightarrow (\square_{10} \sigma_2)$  expresses that whenever  $\sigma_1$  becomes true,  $\sigma_2$  holds at all 10 previous time units. For both  $\otimes_{\tau}$  and  $\square_{\tau}$  we present simplifications that yield space- and time-efficient observers.

# **Algorithm 1** Observer for $\Box_{\tau}\varphi$ . Initially, $m_{\Box_{\tau}\varphi} = \infty$ .

1: At each time  $n \in \mathbb{N}_0$ : 2: **if**  $\_$  transition of  $\varphi$  occurs at time *n* **then** 3:  $m_{\square_T \varphi} \leftarrow n$ 4: **end if** 5: **if**  $\_$  transition of  $\varphi$  occurs at time *n* **then** 6:  $m_{\square_T \varphi} \leftarrow \infty$ 7: **end if** 8: return valid<sup>[I]</sup>  $(m_{\square_T \varphi}, \tau, n)$

Invariant previously  $(\Box_{\tau} \varphi)$  is transformed into  $\neg$ (true  $S_{[0,\tau]} \neg \varphi$ ) by (1). An observer for  $\Box_{\tau} \varphi$  requires a single register  $m_{\Box_{\tau}\varphi}$  with domain  $\mathbb{N}_0 \cup \{\infty\}$ . Initially  $m_{\Box_{\tau}\varphi} = \infty$ . Note that an actual implementation of this observer algorithm clearly must restrict itself to a bounded domain  $\{0, 1, \dots, N\} \cup \{\infty\}$ , where N is chosen sufficiently large to cover the expected mission time of the system being analyzed. We will discuss implementation considerations of our observers in Sect. 5 and meanwhile assume unbounded domain registers.

For the observer in Algorithm 1, we define predicate valid<sup> $\square$ </sup>  $(m, \tau, n)$  as:

valid<sup>$$\square$$</sup> $(m, \tau, n) \equiv (\max(n - \tau, 0) \ge m)$

Intuitively, the predicate valid<sup>(m)</sup>  $(m, \tau, n)$  holds, and thus the algorithm returns true at time *n*, iff the latest  $\neg$  transition of  $\varphi$  occurred before  $n - \tau$  and no  $\neg$  transition of  $\varphi$  occurred since then until time *n*.

**Theorem 1** For all  $n \in \mathbb{N}_0$ , the observer stated in Algorithm 1 implements  $e^n \models \square_\tau \varphi$ .

*Proof* We first observe the equivalences

$$e^{n} \models \Box_{\tau} \varphi$$

$$\Leftrightarrow e^{n} \models \neg (\text{true } S_{[0,\tau]} \neg \varphi)$$

$$\Leftrightarrow \forall i (0 \le i \le n) : (n - i \in [0,\tau] \rightarrow e^{i} \models \varphi)$$

$$\Leftrightarrow \forall i (0 \le i \le n) : (i \in n - [0,\tau] \rightarrow e^{i} \models \varphi)$$

$$\Leftrightarrow \forall i : i \in [0,n] \cap [n - \tau,n] \rightarrow e^{i} \models \varphi$$

$$\Leftrightarrow \forall i : i \in [\max(0,n-\tau),n] \rightarrow e^{i} \models \varphi.$$

(2)

Note that interval  $[\max(0, n - \tau), n]$  is never empty. Thus equation (2) holds iff a  $\Box$  transition of  $\varphi$  occurred at a time at most  $\max(0, n - \tau)$  and no  $\Box$  transition of  $\varphi$  occurred since then until time *n*. The theorem follows.

*Running example* Consider  $\psi \equiv (\uparrow \varphi_1) \rightarrow (\Box_2 \varphi_2)$  on the execution in Fig. 3. Initially,  $m_{\Box_2 \varphi_2} = \infty$ . At time 0,  $\varphi_2$  holds and thus  $m_{\Box_2 \varphi_2} = 0$ . The predicate valid<sup> $\Box$ </sup> ( $m_{\Box_2 \varphi_2}, 2, 0$ ) holds, the algorithm returns true and we have that  $e^0 \models \Box_2 \varphi_2$ . For similar arguments, at time 1,  $e^1 \models \Box_2 \varphi_2$ . At time 2, a  $\Box$  transition of  $\varphi_2$  occurs and we have  $m_{\Box_2 \varphi_2} = \infty$ . Since predicate valid<sup> $\Box$ </sup> ( $m_{\Box_2 \varphi_2}, 2, 2$ ) does not hold, we have that  $e^2 \not\models \Box_2 \varphi_2$ . For similar arguments, at time 3,  $e^3 \not\models \Box_2 \varphi_2$ . Since a  $\Box$  transition of  $\varphi_2$  occurs at time 4,  $m_{\Box_2 \varphi_2} = 4$ . Again, valid<sup>©</sup>  $(m_{\boxtimes_2 \varphi_2}, 2, 4)$  does not hold, thus,  $e^4 \neq \boxtimes_2 \varphi_2$ . The same is true for time 5, thus,  $e^5 \neq \boxtimes_2 \varphi_2$ . At time 6,  $\uparrow \varphi_1$  becomes true and since valid<sup>®</sup>  $(m_{\boxtimes_2 \varphi_2}, 2, 6)$  is true, we deduce  $e^6 \models \psi$ . For times n' prior to 6, (i.e.,  $0 \le n' < 6$ ), the left-hand side of the implication of  $\psi$  does not hold. We immediately have that  $e^{n'} \models \psi$ .

*Exists previously* ( $\otimes_{\tau} \varphi$ ) From the equivalence  $\otimes_{\tau} \varphi \equiv \neg \boxtimes_{\tau} \neg \varphi$ , we can immediately derive an observer for  $\otimes_{\tau} \varphi$  from the observer for  $\boxtimes_{\tau} \varphi$ . The resulting algorithm can straightforwardly be implemented by checking for a  $\frown$  (resp.  $\frown$ ) transition of  $\varphi$  instead of a  $\bigcirc$  (resp.  $\frown$ ) transition of  $\neg \varphi$  in line 2 (resp. line 5) and negating the output in line 8.

4.3 The invariant and exists within interval operators

We now present observers for the more general operators *invariant within interval*  $J (\Box_J)$ and *exists within interval*  $J (\diamondsuit_J)$ . Instead of a register (such as  $m_{\Box_T \varphi}$  in case of the observer for  $\Box_T \varphi$ ), both observers require a list of time point pairs. Clearly, an efficient implementation of this list is vital for an efficient observer. In the following, we present several techniques so as to keep the list succinct, whilst preserving validity of the observer. For a list *l*, we denote by |l| its length, and by l[k], where  $k \in \mathbb{N}$ , its *k*th element. We assume that elements are always appended to the tail of a list.

Invariant within interval  $(\Box_J \varphi)$  is transformed into  $\neg (\text{true } S_J \neg \varphi)$  by (1). An observer for  $\Box_J \varphi$  requires a list  $l_{\Box_J \varphi}$  of elements from  $(\mathbb{N}_0 \cup \{\infty\})^2$ . For a pair of time points  $T \in (\mathbb{N}_0 \cup \{\infty\})^2$ , we shortly write  $T.\tau_s$  for its first component and  $T.\tau_e$  for its second component. Initially,  $l_{\Box_J \varphi}$  is empty. For the observer in Algorithm 2, we define predicate valid<sup> $\Box$ </sup>(T, n, J), with  $T \in (\mathbb{N}_0 \cup \{\infty\})^2$ , by:

$$\mathsf{valid}^{\square}(T, n, J) \equiv (T.\tau_s \le \max(0, n - \max(J))) \land (T.\tau_e \ge n - \min(J)),$$

and predicate feasible(T, n, J) as:

$$\mathsf{feasible}(T, n, J) \equiv (T.\tau_e - T.\tau_s \ge \mathsf{len}(J)) \lor (T.\tau_s = 0 \land T.\tau_e \ge n - \mathsf{min}(J)).$$

Intuitively, Algorithm 2 keeps track of all maximal intervals where  $\varphi$  holds whose length is large enough to potentially lead to the satisfaction of  $\Box_J \varphi$ . Whether this is the case is determined by the fact whether a tuple representation of an interval satisfies the feasible predicate. For large *n*, this means that an interval has to have length at least len(*J*).

We will deduce the correctness of the observer stated in Algorithm 2 from the correctness of a generalized algorithm, presented in Sect. 4.4, obtaining:

**Theorem 2** For all  $n \in \mathbb{N}_0$ , the observer stated in Algorithm 2 implements  $e^n \models \boxdot_J \varphi$ .

*Running example* Consider  $\psi \equiv (\uparrow \varphi_1) \rightarrow (\Box_{[3,4]}\varphi_2)$  and execution *e* of Fig. 3. At time 0, the element  $(0, \infty)$  is inserted into  $l_{\Box_{[3,4]}\varphi_2}$ . The transition of  $\varphi_2$  at time 2 then leads to  $l_{\Box_{[3,4]}\varphi_2} = ((0,1))$ , since feasible((0,1), 2, [3,4]) holds. At time 4, another pair is added, resulting in  $l_{\Box_{[3,4]}\varphi_2} = ((0,1), (4,\infty))$ . Since at time 6:

$$\begin{aligned} \text{valid}^{\square} \left( l_{\square_{[3,4]}\varphi_2}[1], 6, [3,4] \right) \Leftrightarrow \left( 0 \le 6-4 \right) \land \left( 1 \ge 6-3 \right) & \Leftrightarrow \text{ false} \\ \text{valid}^{\square} \left( l_{\square_{[3,4]}\varphi_2}[2], 6, [3,4] \right) \Leftrightarrow \left( 4 \le 6-4 \right) \land \left( \infty \ge 6-3 \right) \Leftrightarrow \text{ false} \end{aligned}$$

we obtain  $e^6 \neq \psi$ .

# **Algorithm 2** Observer for $\Box_J \varphi$ . Initially, $l_{\Box_J \varphi} = ()$ .

1: At each time  $n \in \mathbb{N}_0$ : 2: if  $\Box$  transition of  $\varphi$  occurs at time *n* then add  $(n, \infty)$  to  $l_{\Box_{I}}$ 3: 4: end if 5: if  $\Box$  transition of  $\varphi$  occurs at time *n* and  $l_{\Box, \varphi}$  is non-empty then remove tail element  $(\tau_s, \infty)$  from  $l_{\Box_I \varphi}$ 6: 7: if feasible( $(\tau_s, n-1), n, J$ ) then add  $(\tau_s, n-1)$  to  $l_{\Box_I \varphi}$ 8: end if 9: 10: end if 11: return  $\bigvee_{k=1}^{|l_{\Box_J}\varphi|}$  valid<sup>1</sup>  $(l_{\Box_J}\varphi[k], n, J)$  in case  $n \ge \min(J)$  and true otherwise

*Exists within interval*  $(\diamond_J \varphi)$  From the equivalence  $\diamond_J \varphi \equiv \neg \boxdot_J \neg \varphi$ , we can easily derive an observer for  $\diamond_J \varphi$  from the observer for  $\boxdot_J \varphi$ . As before, we obtain the observer by swapping  $\neg \_$  and  $\_ \urcorner$  transitions and negating the output.

# 4.4 The since within interval operator

An observer for  $\varphi_1 S_J \varphi_2$  is obtained from a  $\otimes_J$  observer and additional logic to reset the observer's list. Let  $l_S$  be an initially empty list. The  $\varphi_1 S_J \varphi_2$  observer is stated in Algorithm 3. In case  $\varphi_1$  holds at time *n*, the observer executes the same code as a  $\otimes_J \varphi_2$  observer. In case  $\varphi_1$  does not hold at time *n*, the list  $l_{\varphi_1 S_J \varphi_2}$  is reset to contain only a single entry whose content depends on the validity of  $\varphi_2$ . Intuitively, for the maximum suffix where  $\varphi_1$  holds Algorithm 3 keeps track of all maximal intervals where  $\varphi_2$  holds whose length is large enough to potentially lead to the satisfaction of  $\varphi_1 S_J \varphi_2$ .

**Theorem 3** For all  $n \in \mathbb{N}_0$ , the observer in Algorithm 3 implements  $e^n \models \varphi_1 S_J \varphi_2$ .

For the proof we introduce additional notation. For list *l* denote with  $l \cdot T$ , the list resulting from adding element *T* to the tail of list *l*. Further denote with  $l^n$ , where  $n \in \mathbb{N}_0$ , the state of Algorithm 3's list  $l_s$  in line 19 executed at time *n*. By  $\overline{l}^n$  we denote the set  $[0, n] \setminus \bigcup_{1 \le k \le |l|} [l[k].\tau_s, l[k].\tau_e + 1)$ . For example, if  $l^{10} = ((0, 3), (5, 8))$ , then  $\overline{l}^{10} = \{4, 9, 10\}$ . We first show that the following proposition holds:

**Proposition 1** Consider Algorithm 3 without the feasibility check in line 8, i.e., replace this line with "if true then". For the modified algorithm the following is correct: For all  $n \in \mathbb{N}_0$  and  $i \leq n, i \in \overline{l}^n$  holds iff both  $e^i \models \varphi_2$  and for all  $k, i < k \leq n, e^k \models \varphi_1$ .

*Proof* The proof is by induction on  $n \in \mathbb{N}_0$ .

**Begin** (*n* = 0): Consider the four cases for  $\varphi_1$  and  $\varphi_2$ :

*Case (i):* Assume  $e^n \models \varphi_1$  and  $e^n \notin \varphi_2$ . Then  $l^n = ((0, \infty))$  and thus  $\overline{l}^n = \emptyset$ . Since  $e^n \notin \varphi_2$ , the induction basis follows in this case.

*Case (ii):* Assume  $e^n \vDash \varphi_1$  and  $e^n \vDash \varphi_2$ . Then  $l^n = ()$  and thus  $\overline{l}^n = \{0\}$ . Since  $e^n \vDash \varphi_2$ , the induction basis follows in this case.

**Algorithm 3** Observer for  $\varphi_1 S_J \varphi_2$ . Initially,  $l_{\varphi_1 S_J \varphi_2} = ()$ .

1: At each time  $n \in \mathbb{N}_0$ : 2: if  $\varphi_1$  holds at time *n* then if  $\neg$  transition of  $\varphi_2$  occurs at time *n* then 3: add  $(n, \infty)$  to  $l_{\varphi_1 S_I \varphi_2}$ 4: end if 5: if  $\Box$  transition of  $\varphi_2$  occurs at time *n* and  $l_{\varphi_1 S_1 \varphi_2}$  is non-empty then 6: remove tail element  $(\tau_s, \infty)$  from  $l_{\varphi_1 S_1 \varphi_2}$ 7: if feasible( $(\tau_s, n-1), n, J$ ) then 8: add  $(\tau_s, n-1)$  to  $l_{\omega_1 S_1 \omega_2}$ 9: end if 10: end if 11: 12: else 13: if  $\varphi_2$  holds at time *n* then set  $l_S = ((0, n - 1))$  in case  $n \neq 0$  and  $l_S = ()$  otherwise 14: 15: else set  $l_S = ((0, \infty))$ 16: 17: end if 18: end if 19: return  $\neg(\bigvee_{k=1}^{|l_{\varphi_1}S_J\varphi_2|} \text{valid}^{\square}(l_{\varphi_1}S_J\varphi_2[k], n, J))$  in case  $n \ge \min(J)$  and false otherwise

*Case (iii):* Assume  $e^n \neq \varphi_1$  and  $e^n \neq \varphi_2$ . The arguments are analogous to the arguments of case (i).

*Case (iv):* Assume  $e^n \notin \varphi_1$  and  $e^n \models \varphi_2$ . The arguments are analogous to the arguments of case (ii).

**Step**  $(n - 1 \rightarrow n)$ : Assume that the statement holds for  $n - 1 \ge 0$ . We will show that it holds for *n*, too. Thereby we consider the same cases (i) to (iv) as in the induction basis.

*Case (i):* We distinguish two cases for  $\varphi_2$ : a  $\neg$  transition of  $\varphi_2$  (i.a) did, or (i.b) did not occur at time *n*.

In case of (i.a),  $l^n = l^{n-1} \cdot (n, \infty)$ . Thus  $\overline{l}^n = \overline{l}^{n-1}$ . Since  $e^n \models \varphi_1$  but  $e^n \not\models \varphi_2$ , the induction step follows in this case.

In case of (i.b),  $l^n = l^{n-1}$ . By the algorithm, the last element in  $l^n$  must be of the form  $(n', \infty)$  with n' < n. Thus  $\overline{l}^n = \overline{l}^{n-1}$ . Again, the induction step follows in this case.

*Case (ii):* We distinguish two cases for  $\varphi_2$ : a  $\neg$  transition of  $\varphi_2$  (ii.a) did, or (ii.b) did not occur at time *n*.

Now consider case (ii.a): If  $l^{n-1} = ()$ ,  $l^n = l^{n-1}$  holds, and thus  $\overline{l}^n = \overline{l}^{n-1} \cup \{n\}$ . Otherwise, the last element in  $l^{n-1}$ , say  $(n', \infty)$ , with  $n' \le n$ , is replaced with (n', n) in  $l^n$ . Again,  $\overline{l}^n = \overline{l}^{n-1} \cup \{n\}$ . In both cases, the induction step follows, as  $e^n \models \varphi_1$  and  $e^n \models \varphi_2$ .

In case of (ii.b),  $l^n = l^{n-1}$ . By the algorithm, the last element in  $l^n$ , if it exists, must be of the form (n', n'') with  $n' \le n'' < n$ . Thus  $\overline{l}^n = \overline{l}^{n-1} \cup \{n\}$ . Again, the induction step follows in this case.

*Case (iii):* By the algorithm,  $l^n = ((0, \infty))$ . Thus  $\overline{l}^n = \emptyset$ . Since  $e^n \notin \varphi_2$ , the induction step follows in this case.

*Case (iv):* By the algorithm, and since n > 0,  $l^n = ((0, n - 1))$ . Thus  $\overline{l}^n = \{n\}$ . Since  $e^n \models \varphi_1$ , the induction step follows in this case.

We are now in the position to prove Theorem 3.

*Proof of Theorem 3* Consider the modified Algorithm 3 without feasibility check. By analogous arguments as in the proof of Theorem 1, we obtain

$$e^{n} \vDash \varphi_{1} S_{J} \varphi_{2}$$

$$\Leftrightarrow \forall i : i \in [0, n] \cap [n - \max(J), n - \min(J)] \wedge (e^{i} \vDash \varphi_{2}) \wedge \forall k(i < k \le n) : e^{k} \vDash \varphi_{1}$$

$$\Leftrightarrow \forall i : i \in [\max(0, n - \max(J)), n - \min(J)] \wedge (e^{i} \vDash \varphi_{2}) \wedge \forall k(i < k \le n) : e^{k} \vDash \varphi_{1}.$$

We distinguish two cases for *n*, namely (i)  $n < \min(J)$ , and (ii)  $n \ge \min(J)$ .

(i) In case  $n < \min(J)$ , interval  $[\max(0, n - \max(J)), n - \min(J)]$  is empty, and  $e^n \models \varphi_1 S_J \varphi_2$  is trivially false. Since the algorithm returns false in this case, the theorem follows for Algorithm 3 without the feasibility check for case (i).

(ii) In case  $n \ge \min(J)$ , interval  $I = [\max(0, n - \max(J)), n - \min(J)]$  is non-empty. Thus  $e^n \models \varphi_1 S_J \varphi_2$  holds iff there exists an  $i \in I$  for which  $e^i \models \varphi_2$  and for all  $k, i < k \le n$ ,  $e^k \models \varphi_1$ . From Proposition 1 we know that this is the case iff there exists an  $i \in I$  with  $i \in \overline{l}^n$ . The latter is the case iff there exists no tuple  $(\tau_s, \tau_e)$  in  $l^n$  with valid<sup> $\Box$ </sup>  $((\tau_s, \tau_e), n, J)$ . Since, for  $n \ge \min(J)$ , the algorithm returns true iff this is the case, the theorem follows for Algorithm 3 without the feasibility check for case (ii).

It remains to show that the theorem holds for Algorithm 3 with original line 8. If we can show that from  $\neg$ feasible( $(\tau_s, \tau_e), n, J$ ) follows  $\neg$ valid<sup> $\Box$ </sup>( $(\tau_s, \tau_e), n', J$ ), for all times  $n' \ge n$ , we may safely remove tuple  $(\tau_s, \tau_e)$  from the algorithm's list without changing the algorithm's return value.

Assume that valid<sup> $\square$ </sup>(( $\tau_s, \tau_e$ ), n', J) holds, with  $n' \ge n$ . We distinguish two cases for n': (a)  $n' < \max(J)$  and (b)  $n' \ge \max(J)$ :

(a) In case  $n' < \max(J)$ , it follows from valid<sup> $\square$ </sup> (( $\tau_s, \tau_e$ ), n', J) that  $T.\tau_s = 0$  and  $T.\tau_e \ge n' - \min(J) \ge n - \min(J)$ . Thus feasible(( $\tau_s, \tau_e$ ), n, J) holds.

(b) Otherwise  $n' \ge \max(J)$ , and it follows from valid<sup> $\Box$ </sup> (( $\tau_s, \tau_e$ ), n', J) that  $T.\tau_s \le n' - \max(J)$  and  $T.\tau_e \ge n' - \min(J)$ . Thus  $T.\tau_e - T.\tau_s \le \operatorname{len}(J)$  and thereby feasible(( $\tau_s, \tau_e$ ), n, J).

The theorem follows.

With the two definitions in (1), an observer algorithm implementing  $e^n \models \Box_J \varphi$  can be deduced from Algorithm 3 by negating its input, its output, and replacing the if condition in line 2 by true. Since the obtained algorithm is equivalent to Algorithm 2, Theorem 2 immediately follows.

### 4.5 Garbage collection

Thus far, we did not consider housekeeping of either list so as to control the growth of the lists. It is important to appreciate that each timed operator has a bounded time-horizon on which it depends. This horizon can be exploited to eliminate pairs T from Algorithm 2 or Algorithm 3's lists that can neither validate nor invalidate the specification. Our garbage

collector works as follows: at any time  $n \in \mathbb{N}_0$ , we remove a tuple T from the list if the proposition

garbage

$$(T, n, J) \equiv T \cdot \tau_e < n - \min(J)$$

holds. The main purpose of the garbage collector is to reduce the algorithms' space and time complexity: We will show that, by removing tuples, garbage collection considerably reduces the algorithms' space complexity. Further, observe that direct implementations of line 11 of Algorithm 2 and line 19 of Algorithm 3 require searches through a list. We will show that, with our garbage collector running in parallel to the observer algorithms, these lines reduce to checking the list's first element only. Thus we may replace the list in both algorithms by a simple queue, where elements are added only to its tail and read and removed only at its head.

In the following, we show the correctness of our garbage collection strategy for any of the proposed algorithms: We first show that if a tuple T is allowed to be removed by the garbage collector at time n, it cannot satisfy valid<sup><sup>□</sup></sup> at that time or at any later time. It is thus safe to remove it from the list.

**Lemma 1** If garbage (T, n, J), then  $\neg$ valid  $\Box(T, n', J)$  for all  $n \ge n'$ .

*Proof* Assume that garbage(T, n, J) holds. Then  $T.\tau_e < n - \min(J) \le n' - \min(J)$ . Since  $T.\tau_e \ge n' - \min(J)$  is necessary for valid<sup>[]</sup>(T, n', J) to hold, the lemma follows.

We next show that always a prefix of a list is removed. This allows the garbage collector to evaluate garbage iteratively, starting from the head of the list.

For that purpose we introduce additional notation. We write "..." for a potentially empty sequence of tuples. For example, (..., T, T', ...) denotes a list of length at least two, where T and T' are any two successive elements in this list.

**Lemma 2** Let l = (..., T, T', ...) be the list of any of the proposed observer algorithms at time  $n \in \mathbb{N}_0$ . If garbage(T', n, J), then garbage(T, n, J).

*Proof* Assume that garbage(T', n, J) holds. Then  $T'.\tau_e < n - \min(J)$ . By observing that all of the proposed algorithms ensure that  $T.\tau_e \le T'.\tau_e$  for successive list elements T and T', we obtain  $T.\tau_e < n - \min(J)$ , i.e., garbage(T, n, J) holds. The lemma follows.  $\Box$

We next prove an upper bound on the length of Algorithm 2 or Algorithm 3's lists. We start by showing that there is a minimum distance between successive elements in the algorithms' lists.

**Lemma 3** Let l = (..., T, T', ...) be the list of any of the proposed observer algorithms at time  $n \in \mathbb{N}_0$ . Then  $T.\tau_e + 2 \le T'.\tau_s$ .

*Proof* Consider Algorithm 2. By the algorithm, tuple *T* must have been added by line 8. For line 8 to add  $T = (T.\tau_s, n-1)$ , transition  $\neg \Box$  of  $\varphi$  must have occurred at time *n*. Thus the next tuple added to the list at a time n' > n must have been of the form  $(n', \infty)$ . Since, by the algorithm, then  $T'.\tau_s \ge n'$  must hold, we further obtain  $T'.\tau_s \ge (n-1) + 2 = T.\tau_e + 2$ . The lemma follows for Algorithm 2.

For Algorithm 3 the lemma follows by analogous arguments.

Further the first element in the list that was not removed by the garbage collector cannot be of arbitrary age:

**Lemma 4** Consider a time-bounded formula  $\boxdot_J \varphi$ ,  $\diamondsuit_J \varphi$ , or  $\varphi_1 S_J \varphi_2$ . Let l = (T, ...) be the list of the proposed respective observer algorithm at time  $n \in \mathbb{N}_0$ , after garbage collection has run at time n. Then  $T.\tau_e \ge n - \min(J)$ .

*Proof* It must hold that garbage(T, n, J) is false, since otherwise T would have been removed by the garbage collector. Thus  $T \cdot \tau_e \ge n - \min(J)$ .

**Lemma 5** Let l be the list of any of the proposed observer algorithms at time  $n \in \mathbb{N}_0$ , after garbage collection has run at time n, and assume that l is non-empty. Let  $T^k = \ell[k]$ , for  $1 \le k \le |\ell|$ . Then  $T^k \cdot \tau_e \ge n - \min(J) + (k - 1)(2 + \operatorname{len}(J))$ .

*Proof* The proof is by induction on the number  $k \ge 1$  of the element in the list.

**Begin** (k = 1): Immediately follows from Lemma 4.

**Step**  $(k - 1 \rightarrow k)$ : Assume that the statement holds for  $k - 1 \ge 1$ . We will show that it holds for *k*, too. By Lemma 3,

$$T^k.\tau_s \ge T^{k-1}.\tau_e + 2.$$

Because k > 1, it must hold that  $T^k \cdot \tau_s \neq 0$ . Thus, by the algorithms, either feasible  $(T^k, n', J)$  must have held at time  $n' \le n$ , when  $T^k$  was added to the list, or  $T^k = (n', \infty)$ . In both cases,

$$T^k.\tau_e \geq T^k.\tau_s + \operatorname{len}(J).$$

It follows that,

$$T^{k}.\tau_{e} \ge T^{k-1}.\tau_{e} + 2 + \operatorname{len}(J).$$

(3)

Combining (3) and the induction hypothesis

$$T^{k-1}$$

. $\tau_e \ge n - \min(J) + (k-2)(2 + \operatorname{len}(J))$

thus yields,

$$T^{k} \cdot \tau_{e} \ge n - \min(J) + (k - 1)(2 + \operatorname{len}(J)).$$

The lemma follows.

We may now derive an upper bound on the number of list elements for all our observer algorithms:

**Theorem 4** Consider a time-bounded formula  $\Box_J \varphi$ ,  $\bigotimes_J \varphi$ , or  $\varphi_1 S_J \varphi_2$ . Let l be the list of the proposed respective observer algorithm at time  $n \in \mathbb{N}_0$ , after garbage collection has run at time n. Then l is of length at most

$$\frac{2\max(J) - \min(J) + 2}{2 + \operatorname{len}(J)}.$$

*Proof* In case *l* is empty the lemma follows trivially. Assume  $l = (T^1, ..., T^k)$  is non-empty. We distinguish two cases for  $T^k$ :

(i) In case  $T^k . \tau_e \neq \infty$ , we obtain from Lemma 5,

$$T^{k}.\tau_{e} \ge n - \min(J) + (k - 1)(2 + \operatorname{len}(J)).$$

(4)

Further, by the algorithms, a finite  $T^k cdot au_e$  implies that

$$T^k.\tau_e \le n-1. \tag{5}$$

Combination of (4) and (5) yields

$$n-1 \ge n-\min(J) + (k-1)(2+\operatorname{len}(J)) \Leftrightarrow$$

$$k \le \frac{\max(J)+1}{2+\operatorname{len}(J)} \le \frac{2\max(J)-\min(J)+2}{2+\operatorname{len}(J)}.$$

The theorem follows for this case.

(ii) Otherwise, i.e., in case  $T^k \cdot \tau_e = \infty$ , by the algorithms,

$$T^k.\tau_s \le n \tag{6}$$

must hold. We obtain from Lemma 5,

$$T^{k-1}.\tau_e \ge n - \min(J) + (k-2)(2 + \operatorname{len}(J)),$$

and by Lemma 3,

$$T^{k}.\tau_{s} \ge n - \min(J) + 2 + (k - 2)(2 + \operatorname{len}(J)).$$

(7)

Combination of (6) and (7) yields

$$n \ge n - \min(J) + 2 + (k - 2)(2 + \operatorname{len}(J)) \Leftrightarrow$$

$$k \le \frac{2\max(J) - \min(J) + 2}{2 + \operatorname{len}(J)}.$$

The theorem also follows for this case.

4.6 Discussion of space and time complexity

We first give a bound on space complexity in terms of single-bit registers that are required by a hardware implementation of our observer algorithms. Clearly, the space complexity for an observer of ptMTL formula  $\varphi$  is the sum of the space complexity of its observers for all subformulas of  $\varphi$ , and its time complexity scales with the depth of the parse tree of  $\varphi$ . It is thus sufficient to state bounds for  $\Box_J \varphi$ ,  $\otimes_J \varphi$ , and  $\varphi_1 S_J \varphi_2$ . In all these cases the respective observer algorithm's space complexity is dominated by the space complexity of the algorithm's list. Clearly the bit complexity of the  $\tau_s$  or  $\tau_e$  component of a tuple added by one of the proposed algorithms to its list before time  $n \in \mathbb{N}_0$  is bounded by  $\lceil \log_2(n) \rceil$ . We thus obtain from Theorem 4 that for any of the time-bounded formulas  $\Box_J \varphi$ ,  $\otimes_J \varphi$ , or

$\varphi_1 S_J \varphi_2$ , our proposed observer algorithms, if executed at time  $n \in \mathbb{N}_0$ , have to maintain a list of space complexity at most:

$$2\left[\log_2(n)\right] \cdot \frac{2\max(J) - \min(J) + 2}{2 + \operatorname{len}(J)}.$$

(8)

Figure 4 visualizes this bound, revealing that memory consumption is moderate for almost all cases, except for configurations where  $\min(J) = \max(J)$ , where space complexity grows linear in  $\max(J)$ . Note that  $\log_2(n)$  is small for realistic experimental setups. For example, allowing to store 52 bit per tuple component is sufficient to check executions that are sampled with a 1 MHz clock during a period of over 140 years.

An alternative to storing absolute times in the observer's list, is to adapt the observer algorithms in a way such that only relative times are stored. While this potentially reduces the bound of Eq. (8) by substituting  $\log_2(n)$  with  $\log_2(\max(J))$ , it requires updating of the list elements (as these then contain relative times) at every time  $n \in \mathbb{N}_0$ . Since this would require more complex hardware mechanism and result in a slower on-line algorithm, we decided not to follow this path in our hardware implementation.

We next show that garbage collection allows one to reduce time complexity of the proposed observers. The time-determining part of Algorithms 2 and 3 is the evaluation of the predicate valid<sup>©</sup> for all list elements in line 11 and line 19 respectively. However, garbage collection makes it possible to only evaluate the predicate for the first element in the list, thus greatly improving time complexity of the proposed algorithms:

**Lemma 6** Let l = (T, ..., T', ...) be the list of any of the observer algorithms at time  $n \in \mathbb{N}_0$ , after garbage collection has run at time n. Then  $\neg$ valid<sup> $\square$ </sup>(T', n, J).

*Proof* Assume by means of contradiction that  $\text{valid}^{\square}(T', n, J)$  holds. Then  $T'.\tau_s \leq \max(0, n - \max(J)) \leq \max(0, n - \min(J))$ . For both Algorithms 2 and 3 we observe that  $T.\tau_e < T'.\tau_s$  has to hold. Thus  $T.\tau_e < \max(0, n - \min(J))$ . Since neither Algorithms 2 nor 3 add tuples with a negative  $\tau_s$  or  $\tau_e$  component, we obtain that  $T.\tau_e < n - \min(J)$  has to hold and by that garbage(T, n, J) holds. A contradiction to the fact that garbage collection has been run at time n: it would have removed tuple T in that case. The lemma follows.

Since further there exist circuits that perform an addition of two integers of bit complexity  $w \in \mathbb{N}$  within time  $\mathcal{O}(\log_2(w))$  [47], and since evaluating the valid<sup> $\square$ </sup>(T, n, J) and garbage(T, n, J) predicates at time  $n \in \mathbb{N}_0$  requires addition of integers of bit complexity at most max $(\log_2(n), \log_2(J))$ , we arrive at an asymptotic time complexity of

$$\mathcal{O}(\log_2 \log_2 \max(J \cup \{n\})),$$

for any of the observers  $\Box_J \varphi$ ,  $\diamond_J \varphi$ , and  $\varphi_1 S_J \varphi_2$  executed at time *n*.

### 5 Mapping the framework into hardware structures

In what follows, we elaborate design considerations to map the proposed runtime verification framework into hardware. Figure 5 shows the main modules of a hardware instance of the framework, i.e., the runtime verification unit (RVU). The design of the RVU is generic and can be attached to various SUTs, as shown in Fig. 1. We start with a discussion of how our RVU connects to existing systems and how we map registers and lists into primitive hardware structures. We then show how we derive the current time from a Real-Time Clock (RTC) and how we evaluate atomic propositions, before we show how to adapt an existing low-footprint, programmable ptLTL verification microprocessor to also evaluate ptMTL specifications using the observer algorithms described in Sect. 4.

5.1 Interfacing the system under test

Our runtime verification unit (see Fig. 5) connects to various systems through wiretapping of the SUT's communication interfaces, as outlined in Fig. 1. The attachment to these communication interfaces is application specific. In its current shape, we implemented bus interfaces for systems operating with: RS-232 (serial port), CAN (vehicle bus), Wishbone (System-on-Chip interconnect),  $I^2C$  (multimaster serial bus), and JTAG (boundary scan) variants.

# 5.2 Registers and lists of pairs of time points

Registers are implemented by, for example, linking multiple flip-flops. The width of such a register equals to the width of the (upper bounded) time points issued by the RTC plus two additional bits. These additional bits enable indication of overflows when performing arithmetics on time points and indication of the special value  $\infty$ . For lists of pairs of time points, we turn to block RAMs, which we organize as ring buffers. Each ring buffer is managed by a unit that controls its read pointer (RP) and its write pointer (WP).

Fig. 5 The runtime verification unit (RVU) and its architecture

### 5.3 Real-time clock

The progression of time is measured by a digital clock, i.e., the real-time-clock (RTC), which contains a counter and an oscillation mechanism that periodically increments the counter [48, Chap. 3]. For an on-chip RVU solution, the oscillation mechanism can also be bounded to the global system clock of the SUT. Note that the design also allows for an instantiation of a fully external clock which is decoupled from the SUT, such as a GPS receiver. Time points are internally stored in registers of width  $w = \lceil \log_2(N) \rceil + 2$ , where N is the maximum time (in terms of ticks of the RTC) expected to occur during a run of the SUT. The two additional bits enable indication of overflows when performing arithmetical operations on time points and indication of  $\infty$ .

Note that our proposed algorithms (cf. Sect. 4) make use of absolute time points, i.e., we store time points for both  $\$  and  $\$  transitions of an event *e*. In contrary, we could also use a mixed representation of absolute and relative time points, i.e., store the absolute time points of the  $\$  transition of event *e* and then count the duration of *e* (the number of clock ticks until the  $\$  transition occurs). While the latter would help to improve the average-case memory requirements in a software-oriented implementation, the former is superior in terms of a hardware implementation: In a hardware design, memory needs to be statically assigned at design time; thus registers have to be of width *w* rendering the benefits of relative time points. Further storing relative time points would require an additional counter of width *w* for all atomic propositions and subformulas that use time points.

#### 5.4 Evaluation of atomic propositions

Ideally, with respect to expressiveness of the supported specifications, atomic propositions include arbitrary equalities, inequalities, and disequalities over variables in the state of the SUT. To arrive at a responsive framework, however, an observer needs to guarantee that it finishes evaluation of atomic propositions within a tight time bound. It is therefore necessary to establish a balance between (hardware) complexity of the resulting observer and expressiveness. To achieve this balance, we restrict the class of atomic propositions supported by our framework in a way inspired by the so-called logahedron abstract domain [45], frequently used in the field of abstract interpretation [24].

Specifically, the class of supported atomic propositions consist of conjunctions of linear constraints, where each constraint ranges over two variables. In addition, each variable can be negated and multiplied by a power of two. In our implementation, we support atomic propositions that are restricted linear constraints ranging over values transferred through an interface of the SUT. Specifically, atomic propositions are of the form  $(\pm 2^n \cdot v_1 \pm 2^m \cdot v_2) \bowtie c$ , where  $v_1$  and  $v_2$  are application specific symbols,  $c, n, m \in \mathbb{Z}$  and  $\bowtie \in \{=, \pm, \le, >, <\}$ . For example, when the RVU is connected to a microcontroller data bus (cf. Fig. 1),  $v_1$  (and  $v_2$ ) can be interpreted as the value stored in a memory location, which in turn, maps to a program variable.

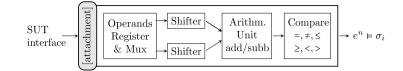

In [68, Sect. 3] we showed how to build circuits (see Fig. 6) that evaluate such linear constraints, with a minimum time penalty. We will use the term AtChecker to refer to such a circuit. It comprises an operands register to fetch new data from the SUT interface, two shifter units to implement multiplication and division by a power of two, an arithmetic unit (i.e., an adder) and a comparator stage. For every atomic proposition of the ptMTL formula, one such unit is instantiated. To evaluate the hardware requirements of AtChecker units, we synthesized the respective circuits with the industrial logic synthesis tool ALTERA QUARTUS II for an Altera Cyclone IV EP4CE115 FPGA device. A single AtChecker unit consumes 290 logic elements (0.25 % of the available logic elements) and can run with a clock frequency of up to  $f_{max} = 128$  MHz.

Fig. 6 An AtChecker unit to evaluate an atomic proposition  $\sigma_i$  in hardware

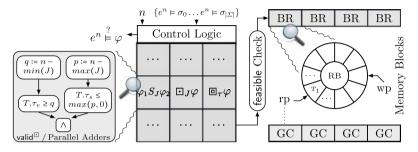

**Fig. 7** Hardware runtime observers for ptMTL specifications; abbreviations: garbage collector (GC), block ram (BR), ring buffer (RB), read pointer (rp), and write pointer (wp)

*Example* Consider the ptMTL formula  $\varphi = (\uparrow (2 \cdot v_1 + v_2 \le 68)) \rightarrow (\Box_{[5,10]}(4 \cdot v_3 = 20 \lor v_4 = 40))$ . Assume that the runtime verification framework is instantiated as shown in the top-right part of Fig. 1, i.e., it monitors a microcontroller core. The atomic propositions  $\{\sigma_1, \sigma_2, \sigma_3\}$  of  $\varphi$  are:  $\sigma_1 \equiv (2 \cdot v_1 + v_2 \le 68), \sigma_2 \equiv (4 \cdot v_3 = 20), \text{ and } \sigma_3 \equiv (v_4 = 40)$ . The symbols  $v_1, \ldots, v_4$  relate to memory locations stored in the microcontroller RAM. Together with debug information from the compiler they can be linked to high-level language symbols, e.g., C code variables. Evaluating  $\{\sigma_1, \sigma_2, \sigma_2\}$  requires three AtChecker blocks. For example, to evaluate  $\sigma_1$ , an AtChecker is configured to load new data from the SUT interface as soon as new values for either  $v_1$  or  $v_2$  are transferred. Its shifter is programmed to shift  $v_1$  one position to the left and the arithmetic unit so as to calculate the sum of  $2 \cdot v_1$  and  $v_2$ . The comparator then compares this result with the constant 68 and finally outputs the truth value of  $\sigma_1$  at the current time point *n*.

#### 5.5 Runtime observers

Figure 7 shows the hardware architecture to evaluate ptMTL operators. A pool of statically synthesized hardware observers is interconnected by a control logic to resemble the parse tree of the specification  $\varphi$ . For each operator we use Theorem 4 to statically assign sufficient memory to it.

*Evaluating the observer algorithms' predicates* Subtraction and relational operators as required by the predicates feasible, garbage, and valid can be built around adders. Observe that, when Add( $\langle a \rangle$ ,  $\langle b \rangle$ , c) is a ripple carry adder for arbitrary length unsigned vectors  $\langle a \rangle$  and  $\langle b \rangle$  and c the carry in, then a subtraction of  $\langle a \rangle - \langle b \rangle$  is equivalent to Add( $\langle a \rangle$ ,  $\langle \overline{b} \rangle$ , 1). Relational operators can be built around adders in a similar way [49, Chap. 6]. For example (left part of Fig. 7), valid<sup> $\Box$ </sup>(( $\tau_e$ ,  $\tau_s$ ), n, J) is implemented using five w-bit adders: one for  $q := n - \min(J)$ , one for r := T.  $\tau_e \ge q$ , one to calculate  $p := n - \max(J)$  and two to calculate t := T.  $\tau_s \le \max(p, 0)$ . Finally, the unit outputs the verdict  $t \land r$ , where t and r

are calculated in parallel. To evaluate valid<sup>(III)</sup>  $(m, \tau, n)$  the unit uses three *w*-bit adders, one to determine  $q := n - \tau$ , one for p := q > 0, and a third to either calculate  $r := q \ge m_{\square_{\tau}\varphi}$  or  $r := 0 \ge m_{\square_{\tau}\varphi}$ , depending on the truth value of *p*. Finally, the validity checker outputs the verdict *r* to the ptLTL evaluation unit. Note that, for the actual implementation, we do not explicitly calculate  $q := n - \min(J)$  through an adder. Instead, the design is configured with an absolute time point that signalizes the end of the *startup phase*, which equals to  $\max(J) + 1$ . A dedicated signal is cleared at reset and asserted once  $n = \max(J) + 1$ , therefore, replacing an adder by a more resource friendly comparator circuit in the implementation for the valid<sup>(III)</sup>  $(\tau_e, \tau_s), n, J)$  predicate.

Lists and garbage collection For a list  $l_{\Box_J\varphi}$  we turn to block RAMs (abundant on contemporary FPGAs) which are organized as ring buffers (right in Fig. 7). Each ring buffer has a read (rp) and a write pointer (wp). To insert a time point pair that satisfies feasible $((\tau_s, n-1), n, J)$ ), wp is incremented to point to the next free element in the ring buffer. The GC then adjusts rp to indicate the latest element with regard to n and J that is *recent enough*. In a fresh cycle (indicated by a changed time point n), the GC loads  $(\tau_s, \tau_e)$  using rp, which is incremented iff garbage $((\tau_s, \tau_e), n, J)$  holds.

*Control logic and modularity* The control logic as shown in Fig. 7 allows one to easily reconnect hardware observers according to the specification's parse tree, which entails that the specification can be modified (within resource limitations) without re-synthesizing the whole design, which could take tens of minutes for FPGA designs.

5.6 A microcomputer to evaluate ptMTL and ptLTL specifications

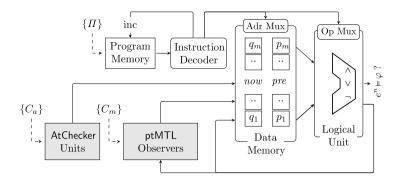

In the following, we discuss a low footprint, reconfigurable microcomputer design that uses AtChecker blocks and the hardware observer blocks to evaluate arbitrary ptLTL and ptMTL formulas. The microcomputer, called  $\mu$ Spy, is configured with a binary program that controls and configures the building blocks depending on the formula to be evaluated. This configuration-based design of the  $\mu$ Spy proves elegant in a dynamic setting, such as product testing in early development phases, where the specification is subject to frequent changes [70]. Modifying the specification then only requires to download a new program to the  $\mu$ Spy. The hardware design of the  $\mu$ Spy is shown in Fig. 8 and builds on our previous work [68, 70] where we showed how to evaluate ptLTL formulas on such an architecture. An additional component (ptMTL observers) implements the control logic needed to instantiate ptMTL hardware observers to cover the time-bounded operators of the specification.

*Workflow* A (GUI-based) observer-generation application on a host computer compiles a ptMTL specification  $\varphi$  into a triple  $\langle \Pi, C_a, C_m \rangle$ , where  $C_a$  is a configuration for the AtChecker,  $C_m$  is a configuration for the pool of time bounded MTL operators and  $\Pi$  is a native program for the  $\mu$ Spy.

The synthesis of a configuration for the  $\mu$ Spy, denoted by  $\langle \Pi, C_a, C_m \rangle$ , from  $\varphi$  requires the following steps:

- (1) We use the ANTLR parser generator [61] to parse  $\varphi$ . This step yields an abstract syntax tree (AST) that represents the specification.

- (2) After some pre-processing of the AST, we determine the *m* subformulas φ<sub>1</sub>,..., φ<sub>m</sub> of φ by using a post-order traversal.

- (3) For each subformula  $\varphi_i$ ,  $1 \le i \le m$ :

Fig. 8 The  $\mu$ Spy architecture. AtChecker units as in Fig. 6 and ptMTL observers as in Fig. 7

- If  $\varphi_i$  is an atomic proposition, instantiate an AtChecker block and add its configuration to  $C_a$ .

- If  $\varphi_i$  is a ptLTL formula, we use the approach shown in [68, 70] to generate a native instruction for the  $\mu$ Spy and add the instruction to  $\Pi$ .

- If  $\varphi_i$  is a ptMTL formula, we instantiate the corresponding observer hardware block, generate the hardware block's configuration and a native instruction for the  $\mu$ Spy. We add the configuration to  $C_m$  and the instruction to  $\Pi$ .

After running steps (1–3) of the synthesis procedure, the resulting configuration  $\langle \Pi, C_a, C_m \rangle$  is then transferred from the host computer to the hardware platform where the  $\mu$ Spy is instantiated on, e.g., from the host computer through an Universal Serial Bus (USB) to an FPGA. We note that the host computer is only required to generate such a configuration for the current specification, but is not required during monitoring.

Instruction set architecture The  $\mu$ Spy is a pipelined microcomputer organized as a classical Harvard architecture. Its Instruction Set Architecture (ISA) supports 22 opcodes to handle ptLTL and ptMTL operators, where each instruction word is 40 bits long. It contains the opcode, addresses of two operands, an interval address, and a further address to select a private memory space for ptMTL operators. The first two bits from the operands address denote the source of the operands data which can be a memory location, i.e., the location in the data memory where the result of the respective subformula is held, an atomic proposition or an immediate value, which can be *true* or *false*. The additional fields *Interval Address* and *List Address* are necessary for the ptMTL operators only. A single instruction word for the  $\mu$ Spy is 40 bit long and is structured as follows:

| OpCode | Addr. Operand 1 | Addr. Operand 2 | Interval Addr. | List Addr. |

|--------|-----------------|-----------------|----------------|------------|

| 5 bit  | 2+8 bit         | 2+8 bit         | 8 bit          | 7 bit      |

Architectural features The  $\mu$ Spy manages two memories p[0, ..., m-1] and q[0, ..., m-1], one containing the evaluations of all *m* subformulas of  $\varphi$  (generated in a post-order traversal of the parse tree of  $\varphi$ ; in step (1) of the synthesis procedure) in the current and in the previous execution cycle (i.e., time points *n* and *n*-1). This allows for space and time efficient evaluation of formulas whose parse tree is a directed acyclic graph, and not

| <b>Table 1</b> $\mu$ Spy clock-cycles for<br>Boolean, ptLTL, and ptMTL<br>operators | Logic   | Operator                                                   | $\mu$ Spy clock cycles |

|-------------------------------------------------------------------------------------|---------|------------------------------------------------------------|------------------------|

| operators                                                                           | Boolean | $\neg \varphi$                                             | 1                      |

|                                                                                     |         | $\varphi_0 \bullet \varphi_1, \bullet \in \{\land, \lor\}$ | 1                      |

|                                                                                     | ptLTL   | $\odot \varphi$                                            | 1                      |

|                                                                                     |         | $\varphi_1 S \varphi_2$                                    | 1                      |

|                                                                                     | ptMTL   | $\Box_{\tau} \varphi \mid \otimes_{\tau} \varphi$          | 2                      |

|                                                                                     |         | $\boxdot_J \varphi \   \ \diamondsuit_J \varphi$           | 4                      |

|                                                                                     |         | $\varphi_1 S_J \varphi_2$                                  | 4                      |

necessarily a tree. For example, to evaluate the formula  $\varphi \equiv (\uparrow \sigma_1) \equiv \sigma_1 \land \neg \odot \sigma_1$ , one is not required to evaluate both  $\sigma_1$  and  $\odot \sigma_1$  independently, and thus  $\sigma_1$  twice. Rather, we will have two registers of length 1, i.e., p[0] holds the result of  $\sigma_1$  from the previous round and q[0] from the current round. The  $\mu$ Spy then fetches both p[0] and q[0] and executes the instruction that represents the operator  $\uparrow$ , which maps to the Boolean operation ( $q[0] \oplus$  $p[0]) \land q[0]$ , namely,  $\sigma_1$  did toggle its truth value ( $q[0] \oplus p[0]$  holds) and  $\sigma_1$  is true in the current state (q[0] holds). Each instruction is processed through a four-stage pipeline (*fetch, load, calc,* and *write back*). All stages except the calc stage require one clock cycle per instruction, the execution time of the calc stage depends on the operator and requires from one to four clock cycles.

*Execution time per operator* Due to the pipelined design of the  $\mu$ Spy any ptLTL operator is executed within a single clock cycle in the pipeline stage. The additional overhead for list management and garbage collection required for the ptMTL operators require an additional one to three clock cycles. Due to a data forwarding strategy from the execution to the load stage in the pipeline, no further pipeline stalls are necessary and the pipeline is guaranteed to be optimally filled. Table 1 summarizes the execution times for various Boolean, ptLTL, and ptMTL operators.

*Example* Consider the ptMTL property  $\varphi \equiv (\uparrow (2 \cdot v_1 + v_2 \le 68)) \rightarrow (\Box_{[5,10]}(4 \cdot v_3 = 20 \lor v_4 = 40))$ . As in the example of Sect. 5.4, the atomic propositions  $\{\sigma_1, \sigma_2, \sigma_3\}$  of  $\varphi$  are evaluated by three AtChecker units. The subformulas  $\uparrow (2 \cdot v_1 + v_2 \le 68)$  and  $(4 \cdot v_3 = 20 \lor v_4 = 40)$  are checked by the  $\mu$ Spy. For example, the value of  $\sigma_1$  and the result of  $\sigma_1$  from time n - 1 is used by the calc stage, which decides if  $\uparrow \sigma_1$  holds at the current time. The process is similar to determine the truth value of  $\sigma_2 \lor \sigma_3$ , the result of which is used as input to calculate  $\Box_{[5,10]} (\sigma_2 \lor \sigma_3)$ . The observer block is configured through the interval memory so as to represent J = [5, 10]. The output of the  $\Box_{[5,10]} (\sigma_2 \lor \sigma_3)$  calculation is then the input to the final ptLTL computation, i.e.,  $\varphi \equiv (\uparrow \sigma_1) \rightarrow (\Box_{[5,10]} (\sigma_2 \lor \sigma_3))$ .

# 6 Evaluation

To demonstrate the feasibility of our approach, we implemented the presented algorithms for ptMTL monitoring by means of the  $\mu$ Spy on an FPGA platform. In the current implementation, subformulas are evaluated sequentially as they appear in the specification's parse tree. Since the observer blocks are executed in sequence, their logic elements can be reused and it

suffices to equip the  $\mu$ Spy with only one  $\Box_T \varphi$ , one  $\Box_J \varphi$ , and one  $\varphi_1 S_J \varphi_2$  hardware observer block and assign memory according to the number of subformulas.<sup>2</sup> The implementation is a synchronous register-transfer-level VHDL design, which we both simulated in MEN-TOR GRAPHICS MODELSIM and synthesized for various FPGAs using the industrial logic synthesis tool ALTERA QUARTUS II.<sup>3</sup>

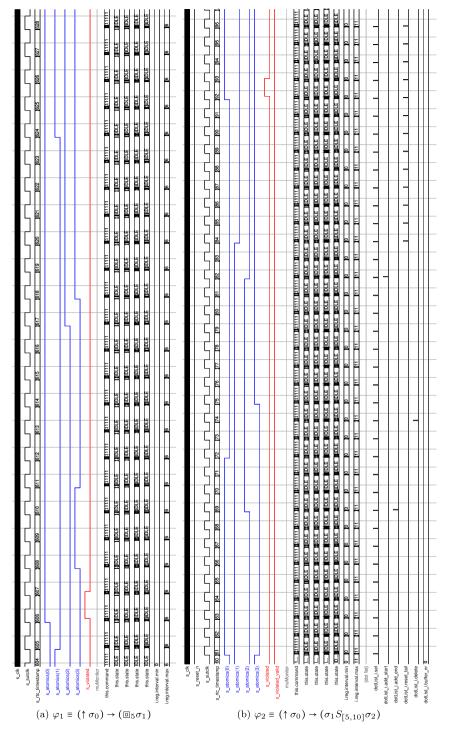

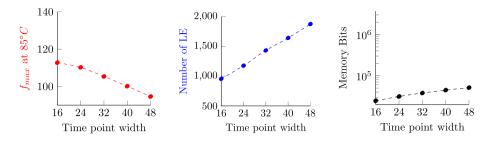

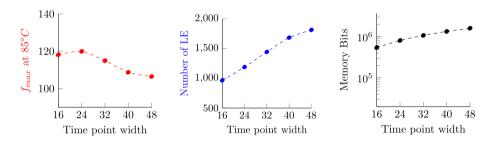

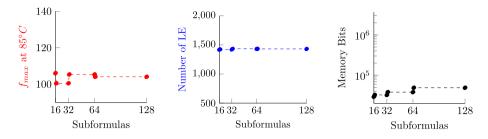

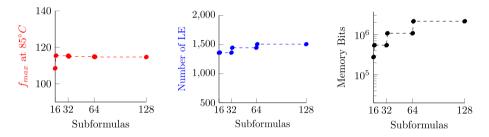

# 6.1 Simulation results