Received: 28 November 2017 Accepted: 28 March 2018 Published online: 16 April 2018

# **OPEN** Scalability assessment of Group-IV mono-chalcogenide based tunnel FET

Madhuchhanda Brahma<sup>1,2</sup>, Arnab Kabiraj<sup>2</sup>, Dipankar Saha<sup>2</sup> & Santanu Mahapatra 10<sup>2</sup>

Selection of appropriate channel material is the key to design high performance tunnel field effect transistor (TFET), which promises to outperform the conventional metal oxide semiconductor field effect transistor (MOSFET) in ultra-low energy switching applications. Recently discovered atomically thin GeSe, a group IV mono-chalcogenide, can be a potential candidate owing to its direct electronic band gap and low carrier effective mass. In this work we employ ballistic quantum transport model to assess the intrinsic performance limit of monolayer GeSe-TFET. We first study the electronic band structure by regular and hybrid density functional theory and develop two band  $k \cdot p$  hamiltonian for the material. We find that the complex band wraps itself within the conduction band and valence band edges and thus signifies efficient band to band tunneling mechanism. We then use the  $k \cdot p$  hamiltonian to calculate self-consistent solution of the transport equations within the non-equilibrium Green's function formalism and the Poisson's equation based electrostatic potential. Keeping the OFF-current fixed at 10 pA/µm we investigate different static and dynamic performance metrics (ON current, energy and delay) under three different constant-field scaling rules: 40, 30 and 20 nm/V. Our study shows that monolayer GeSe-TFET is scalable till 8 nm while preserving ON/OFF current ratio higher than 104.

Dennard's scaling theory<sup>1,2</sup> has acted as a guideline for the semiconductor industry to miniaturize the metal oxide semiconductor (MOS) technology in order to comply with the Moore's law3. According to this theory, the power density remains constant over technology nodes if both the dimension and supply voltage  $(V_D)$  are scaled by the same factor (known as constant-field scaling). A  $V_{\rm D}$  scaling also calls for an equal scaling of the threshold voltage  $(V_T)$  to preserve the ON-current  $(I_{ON})$ . Since the subthreshold slope (SS) of a MOSFET does not scale with feature size (rather degrades due to drain-induced-barrier-lowering (DIBL) effect) and limited to minimum value of 60 mV/decade, the OFF-current ( $I_{OFF}$ ) increases exponentially with  $V_T$  reduction. It is worth noting that the limited value of SS arises from the thermionic emission of the carriers from the source to the channel in a conventional MOSFET. This OFF-state current leads to significant static power dissipation, which is very crucial for battery operated modern hand-held electronic gadgets (cell phone, tablet etc). As a result, the semiconductor industry has been forced to adopt the energy-inept constant-voltage scaling practice for a decade with a value

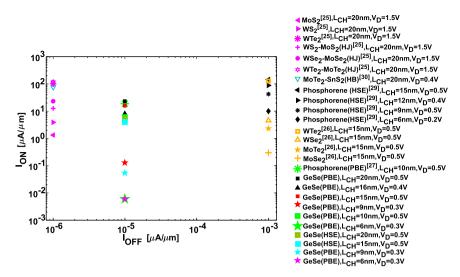

Thus next generation transistor which can offer sub-60 mV/decade subthreshold slope is in high demand as it may restore the energy efficient constant-field scaling by enabling the supply voltage reduction below 0.6 V. In this view, some interesting devices like negative-capacitance FETs<sup>4,5</sup>, imapact-ionization FETs<sup>6-8</sup> and tunnel FETs (TFET)<sup>9-12</sup> are being explored. Present work is focused on TFET, which is basically a gated p-i-n diode where the carriers are injected from the source to the channel by band-to-band tunneling (BTBT) mechanism<sup>13</sup> and hence promises to offer very low I<sub>OFF</sub> with steep subthreshold swing. However, poor SS and low ON-current have been observed in Silicon based TFETs<sup>14</sup> due to large indirect energy band gap (1.12 eV), which imposes inefficient phonon assisted tunneling (PAT)<sup>15</sup>. Recent time has seen an extensive investigation of alternative materials for designing high performance TFET<sup>16-21</sup>. Atomically thin layered materials, also known as 2D materials, have found great significance as TFET channel material due to their planar structure, excellent electrostatic integrity, mechanical flexibility and possibility of having direct band gap with low effective mass. Theoretical analysis has been conducted to estimate the performance of TFET based on different such 2D materials: Graphene nanoribbon<sup>22–24</sup>, transition metal di-chalcogenides (MoS<sub>2</sub>, WS<sub>2</sub>, MoSe<sub>2</sub>, WSe<sub>2</sub>, MoTe<sub>2</sub> etc)<sup>25,26</sup>, Phosphorene<sup>27–29</sup> etc. Such

<sup>1</sup>Centre for Nano Science and Engineering, Indian Institute of Science, Bangalore, 560012, India. <sup>2</sup>Nano-Scale Device Research Laboratory, Department of Electronic Systems Engineering, Indian Institute of Science, Bangalore, 560012, India. Correspondence and requests for materials should be addressed to M.B. (email: madhu.brahma@gmail.com)

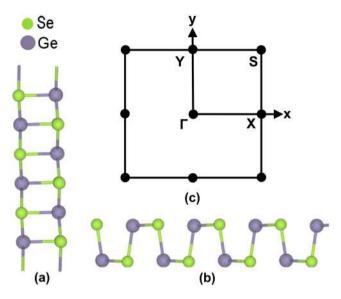

Figure 1. (a) Top view and (b) Side view of monolayer GeSe (c) High-symmetry points in the Brillouin zone.

| Method   |     | a(Å) | b(Å) | $E_{\rm G}({ m eV})$ | $m_{ex}^*(m_0)$ | $m_{ey}^*(m_0)$ | $m_{hx}^{*}\left(m_{0}\right)$ | $m_{hy}^* (m_0)$ |

|----------|-----|------|------|----------------------|-----------------|-----------------|--------------------------------|------------------|

| DFT-PAW  | HSE | 4.28 | 3.97 | 1.6                  | 0.14            | 0.22            | 0.15                           | 0.23             |

|          | PBE | 4.28 | 3.97 | 1.15                 | 0.13            | 0.44            | 0.14                           | 0.44             |

| DFT-LCAO |     | 4.24 | 3.99 | 1.17                 | 0.13            | 0.57            | 0.14                           | 0.31             |

**Table 1.** Lattice parameters considered for DFT calculation and resulting electronic properties.

study has also been extended to hetero-bilayer<sup>30-32</sup> and hetero-junction devices<sup>25</sup>. At the same time, experimental devices built upon such 2D materials<sup>33-35</sup> are also reported.

Lately, a new group of 2D materials, namely group IV mono-chalcogenides (GeSe, GeS, SnSe, SnS etc.), has attracted much attention due to their structural similarities with Phosphorene. Among all of them only GeSe has been reported to have direct band gap and low effective mass<sup>36–42</sup>. Moreover, there are reports of experimental fabrication of GeSe nanostructures and nanodevices<sup>43–49</sup> and their excellent stability in air<sup>50,51</sup>. GeSe is also available with commercial vendors<sup>52</sup> for experimental research. However, to our best knowledge there is no study on the assessment of GeSe channel based TFET performance. It motivates us to assess the intrinsic performance limit of GeSe-TFET and compare with other 2D material based TFETs.

In this work, we first conduct density functional theory (DFT) calculation to extract effective mass, band gap and the complex band structure (CBS) of monolayer GeSe. Next we perform transport calculations on GeSe-TFET using self-consistent NEGF-Poisson simulation, the details of which are given in the Methods section. We estimate the figure of merit for static performance namely ON-curent ( $I_{\rm ON}$ ) and compare the values with other state of the art 2D materials based TFETs. This is followed by the assessment of dynamic figures of merit namely intrinsic switching delay ( $\tau$ ) and the power-delay product (PDP). Our study can be useful to assess the potential of GeSe-TFET at the early stage of technology development.

### Results

In this section we first discuss about the atomic structure of monolayer GeSe that we use for DFT calculations. Then we present the calibration of E-K dispersion generated from our adopted two band  $k \cdot p$  hamiltonian model with the DFT results. This is followed by transport calculations for a double gate TFET.

Figure 1 shows the top and side views of the relaxed atomic configuration of monolayer GeSe including the Brillouin zone. It inherits orthorhombic crystal structure from its bulk counterpart which is a van der Waals layered material. Moreover, monolayer GeSe looks quite similar to the puckered structure of Phosphorene with a slight distortion. It exhibits direct band gap along  $\Gamma$ -X and  $\Gamma$ -Y directions, with a lesser gap along  $\Gamma$ -X direction (See Supplementay Information). The lattice parameters used for electronic structure calculations as well as the values of energy band gap and effective masses obtained from DFT are listed in Table 1. All these values are in agreement with other reported results<sup>40,41</sup>.

First principles calculations based on two different DFT functionals: Perdew-Burke-Ernzenhof (PBE) exchange-correlation functional<sup>53</sup> and Heyd-Scuseria-Ernzerhof (HSE) hybrid functional<sup>54</sup>, generate similar band-dispersion with different band gap values. Moreover, the optical band gap value of monolayer GeSe as claimed by commercial vendor<sup>52</sup> turns out to be 1.6 eV, which has not yet been validated by any scholarly report. Such DFT functional dependent band gap difference is also observed in case of Phosphorene<sup>55–57</sup>. Therefore in our study, we consider it suitable to include DFT calculations based on both methods. Considering both HSE and

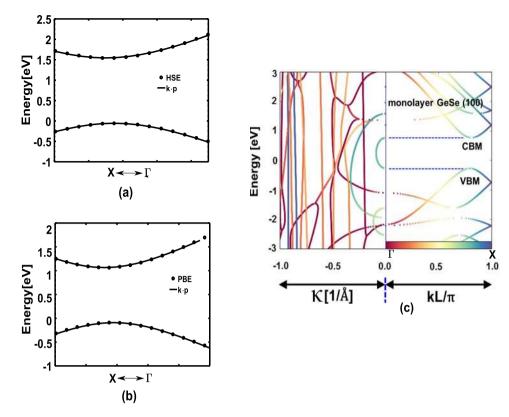

Figure 2. (a) DFT-PAW HSE band structure and (b) DFT-PAW PBE band structure calibrated with  $k \cdot p$  model around the band gap regime (see Supplementary Information) (c) 2D plot of complex bandstructure of monolayer GeSe (surface cleaved in (100) direction) as obtained from DFT-LCAO. The right-hand panel illustrates the real bands, where the solution  $\mathbf k$  are normalized by the perpendicular layer separation  $\mathbf L$ . The left-hand panel portrays the complex bands against reciprocal Cartesian coordinates on the x-axis, shows complete wrapping of imaginary branches within CBM and VBM.

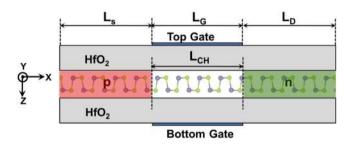

**Figure 3.** Schematic of the cross-section of the considered GeSe based monolayer TFET.  $L_{\rm CH}$  denotes the channel length, which equals the gate length  $L_{\rm G}$ . The shaded regions on the left and right represent source (p-doped) and drain (n-doped) respectively.

PBE methods also enable us to study the effect of different band gaps on the scaling behavior of TFETs based on materials with near identical effective mass in the transport direction. We also perform DFT calculations using linear combination of atomic orbitals (DFT-LCAO) in order to compute the complex band structure, which acts as a guideline for material selection.

In Fig. 2(a) and (b) we show the agreement between the energy dispersion obtained from our calibrated  $k \cdot p$  model and DFT using projector-augmented-wave (DFT-PAW) method, along the  $\Gamma$ -X direction. From the figure we find that the  $k \cdot p$  band dispersion matches very well over a range of  $\approx$ 0.5 eV near conduction band (CB) and valence band (VB) edges, which is sufficient for the tunneling window considered in our transport simulations. We also see in Fig. 2(c) that the imaginary branches of CB and VB completely wrap with each other within the CB mimima (CBM) and VB maxima (VBM), thereby projecting to a very high tunneling probability and insignificant PAT<sup>15</sup>. This allows us to calculate quantum transport under ballistic approximation without considering phonon scattering.

In our simulation, we have considered a double gate tunnel FET structure as shown in Fig. 3, with effective oxide thickness, EOT = 0.5 nm. The source and drain are uniformly doped p and n regions, while the channel is

|            |                         | Scaling | Scaling rule (nm/V) |      |       |        |        |  |  |

|------------|-------------------------|---------|---------------------|------|-------|--------|--------|--|--|

|            |                         | 40      |                     | 30   | 30    |        | 20     |  |  |

| $V_{ m D}$ |                         | HSE     | PBE                 | HSE  | PBE   | HSE    | PBE    |  |  |

| 0.5 V      | L <sub>CH</sub> (nm)    | 20      | 20                  |      | 15    |        | 10     |  |  |

|            | I <sub>ON</sub> (μΑ/μm) | 5.05    | 23.29               | 1.74 | 16.30 | 1.07   | 6.09   |  |  |

| 0.4 V      | L <sub>CH</sub> (nm)    | 16      | 16                  |      | 12    |        | 8      |  |  |

|            | I <sub>ON</sub> (μΑ/μm) | 0.75    | 8.17                | 0.62 | 5.32  | 0.13   | 0.22   |  |  |

| 0.3 V      | L <sub>CH</sub> (nm)    | 12      | 12                  |      | 9     |        | 6      |  |  |

|            | I <sub>ON</sub> (μΑ/μm) | 0.09    | 1.37                | 0.05 | 0.13  | 0.0062 | 0.0061 |  |  |

**Table 2.** Values of ON-current for devices considered under different scaling rules.

undoped. The channel length  $L_{\rm CH}$  is same as the gate length  $L_{\rm G}$ . The source extension  $L_{\rm S}$  is taken as 16 nm in all the devices under study. The thickness of the GeSe monolayer extracted from the DFT simulations is found to be 0.586 nm. The in-plane and out-of-plane dielectric constants are taken as  $13.8^{40}$  and 1 (ideal 2D case) respectively. The gate work-function is adjusted so that the OFF-state current ( $I_{\rm OFF}$ ) at zero gate voltage ( $V_{\rm G}$ ) is set at  $10\,{\rm pA/\mu m}$  for all the devices under study as specified in International Technology Roadmap for Semiconductors (ITRS) for low power nodes<sup>58</sup>. From hereon, all the results obtained from HSE and PBE parameters are marked as HSE and PBE on the plots and in the text.

As pointed out earlier, our main objective is to predict the scaling behavior of GeSe based tunnel FET under the constant-field scaling methodology. Therefore, we have considered three different scaling rules and varied the channel length and  $V_{\rm D}$  accordingly as shown in Table 2. In doing so, we have to vary the doping concentration as well as the drain length extensions, in order to achieve  $I_{\rm ON}-I_{\rm OFF}$  ratio of  $10^4$  and charge neutrality at the contacts respectively (see Supplementary Information).

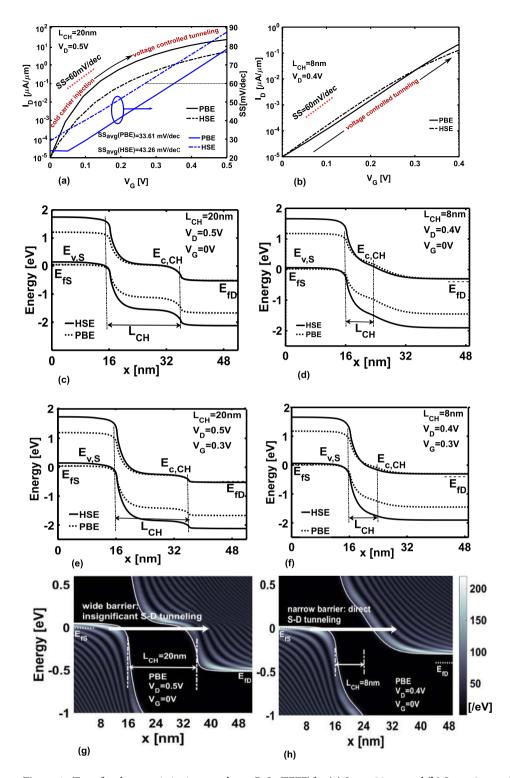

The ON-current,  $I_{\rm ON}$  obtained from self-consistent calculations are listed in Table 2, for all the devices. Careful examination of the vaues in the Table reveal that the difference in magnitude of ON-current between HSE and PBE diminishes as the channel length is scaled down. In order to explain this phenomenon we consider two cases,  $L_{\rm CH}=20\,{\rm nm}$  at  $V_{\rm D}=0.5\,{\rm V}$  and  $L_{\rm CH}=8\,{\rm nm}$  at  $V_{\rm D}=0.4\,{\rm V}$ , for which we plot the transfer characteristics in Fig. 4. The reason for such difference in transfer characteristics lies in the fact that, in longer channel length devices ( $L_{\rm CH}\geq 10\,{\rm nm}$ ) the transport is dominated by "cold carrier injection" whereas in shorter length devices, it is controlled by "voltage controlled tunneling" 59. As pointed out in 59 and also what we find in Fig. 4(a), (b) is that, "voltage controlled tunneling" does not have significant effect on the lowering of SS below the Boltzmann limit and does not vary considerably with gate voltage.

To elaborate this further, we refer to Fig. 4(c)–(f) where we plot the energy-band diagrams for  $L_{CH}$  = 20 nm at  $V_D = 0.5 \text{ V}$  and  $L_{CH} = 8 \text{ nm}$  at  $V_D = 0.4 \text{ V}$  for both OFF ( $V_G = 0 \text{ V}$ ) and ON-states ( $V_G = 0.3 \text{ V}$ ). We also show the local density of states (LDOS) plots for the above-mentioned cases at  $V_G = 0$  V with respect to PBE. It is worth mentioning that similar behavior of LDOS is also observed in HSE (see Supplementary Information). If we examine the LDOS plot in Fig. 4(g) for longer channel TFET at OFF-state, we find that the electrons adjacent to source Fermi level, i.e. the region where the current spectrum peaks (see Supplementary Information) see a higher barrier while crossing over to the channel-drain junction in order to fill the empty states. But as V<sub>G</sub> increases there is a significant opening up of the tunneling window. This can be seen from the potential energy diagram in Fig. 4(c), (e) showing a well defined crossing over of  $E_{v,S}$  and  $E_{c,CH}$  from OFF to ON-state. As a result electrons from the source see a thinner tunneling barrier and higher availability of empty states in the channel. The crossing over of the band edges is resposible for the "low-pass filtering" of the high energy tails of the Fermi distribution function<sup>60</sup> of the source side. As a result, in the low  $V_G$  regime, transport in long channel TFET is determined by the "cold carrier injection"<sup>59</sup> which entails the SS  $\approx ln(10)\frac{\Delta\phi}{\sigma}$ , where  $\Delta\phi = E_{\rm v,S} - E_{\rm c,CH}$ . From our calculations it is found that,  $\Delta\phi \approx 0.01\,\mathrm{eV}$  in HSE TFET and 0.001 eV in PBE TFET. Due to the linear dependence of SS on  $\Delta \phi^{60}$ , the PBE TFET shows a larger regime of SS  $\leq$  60 mV/dec with respect to gate bias (see Fig. 4(a)) and therefore higher drain current compared to HSE TFET in this low  $V_{\rm G}$  regime. As  $V_{\rm G}$  increases i.e. in the postsubthreshold regime, value of  $\Delta\phi$  increases and the transport mechanism shifts to "voltage controlled tunneling"59. The SS in both HSE and PBE does not change significantly with gate voltage in this high  $V_{\rm G}$  regime (see Fig. 4(a)). However, since the BTBT current is proportional to tunneling probability under Wentzel-Kramers-Brillouin approximation ( $T_{\text{WKB}}$ ), where  $T_{\text{WKB}} = \exp \xi_I / F^{59}$ , with F corresponding to the electric field at the source-channel junction and  $\xi_I = 4\sqrt{2m_r^*} E_G^{3/2}/3(q\hbar)$ , where q is the electronic charge,  $m_r^*$  is the reduced tunneling mass and  $\hbar = h/(2\pi)$ , h being the Planck's constant, therefore PBE TFET due to higher electric field F resulting from its low band gap value, gives rise to significantly higher ON-state current.

In case of shorter channel TFETs ( $L_{\rm CH} \leq 10$  nm), the electrons in the source see a smaller and thinner tunneling barrier in the OFF-state and are able to directly tunnel through to the channel-drain junction to fill up the empty states (see LDOS plot in Fig. 4(h)). The higher probabilty of direct source to drain tunneling in shorter channel TFET in low  $V_{\rm G}$  regime, ultimately renders the minor (with respect to long channel TFET) crossing over of  $E_{\rm c,CH}$  and  $E_{\rm v,S}$  (see Fig. 4(d),(f)) from OFF to ON-state, ineffective. This eventually results in over-passing the "filtering effect of the source Fermi function" and forces the device to be in the "voltage controlled tunneling" regime. Mathematically, the SS is now determined as  $\frac{1}{q^2} \Lambda \xi_1$ , where  $\Lambda = W_D + \lambda$ , with  $W_D$  and  $\lambda$  corresponding to the depletion width at the source-channel junction and geometric screening length respectively.

**Figure 4.** Transfer characteristics in monolayer GeSe-TFET for (a)  $L_{\rm CH}=20\,{\rm nm}$  and (b)  $L_{\rm CH}=8\,{\rm nm}$  with respect to both HSE and PBE methods. Energy band profile at  $V_{\rm G}=0\,{\rm V}$  for (c)  $L_{\rm CH}=20\,{\rm nm}$  and (d)  $L_{\rm CH}=8\,{\rm nm}$  and at  $V_{\rm G}=0.3\,{\rm V}$  for (e)  $L_{\rm CH}=20\,{\rm nm}$  and (f)  $L_{\rm CH}=8\,{\rm nm}$ . LDOS plots at OFF-state for (g)  $L_{\rm CH}=20\,{\rm nm}$  and (h)  $L_{\rm CH}=8\,{\rm nm}$  where S and D stand for source and drain respectively. In (a) the point SS is plotted on the right y-axis. Average SS is calculated by considering the threshold voltage at  $V_{\rm D}/2^{11}$ .

In the best case, the value of SS is very close to the thermal limit<sup>59</sup>. In our case, SS turns out to be >60 mV/dec (95.2 mV/dec for PBE and 83.6 mV/dec for HSE). For the chosen gate voltage regime, the values of SS show insignificant difference between HSE and PBE TFETs, and remain almost constant over the range of  $V_{\rm G}$  (see Fig. 4(b)). This eventually results in minimal change of  $I_{\rm D}$  between HSE and PBE TFETs.

**Figure 5.** Comparison of  $I_{\rm ON}$  with other 2D material based TFETs. HJ and HB correspond to hetero-junction and hetero-bilayer respectively whereas PBE and HSE correspond to the functional of the DFT-PAW method used to calculate the electronic structure of the material.

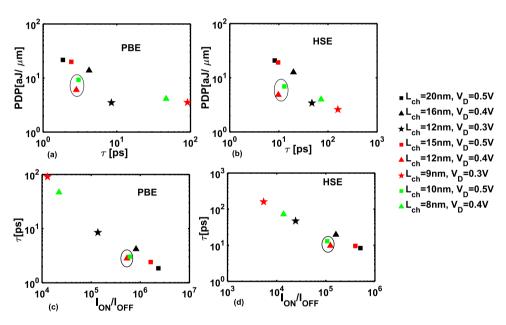

**Figure 6.** PDP versus intrinsic switching delay graph for (a) PBE and (b) HSE. Intrinsic switching delay versus  $I_{\text{ON}}/I_{\text{OFF}}$  for (a) PBE and (b) HSE. The circled nodes are the most optimized in performance.

#### Discussion

First we present a comparison of the ON-current obtained in our device with respect to other reported 2D material based TFETs. It is worth noting that achieving hetero-bilayer materials with direct band gap is difficult  $^{61,62}$ . However, theoretical calculations  $^{30}$  are conducted under ballistic assumption. From Fig. 5, we find that irrespective of the scaling rule, GeSe-TFETs with  $L_{\rm CH} \ge 10$  nm show comparable  $I_{\rm ON}$  as other reported TMD and Phosphorene TFETs.

Next we discuss about the dynamic performance metrics, expressed in terms of intrinsic switching delay  $(\tau)$ , and power delay product (PDP). The intrinsic switching delay is computed following the method explained in  $^{63}$  as  $\tau = (Q_{\rm ON} - Q_{\rm OFF})/I_{\rm ON}$ , where  $Q_{\rm ON}$  and  $Q_{\rm OFF}$  are the overall charges in the device at ON and OFF-state, respectively. The PDP is calculated as  $V_{\rm D}(Q_{\rm ON} - Q_{\rm OFF})^{64}$ .

From the PDP-delay curve in Fig. 6(a) and (b) it can be seen that for a particular scaling rule the PDP decreases with the scaling of  $L_{\rm CH}$  and  $V_{\rm D}$  (go vertically down in Table 2). This is due to the decrease in values of  $Q_{\rm ON}$  and  $Q_{\rm OFF}$  as  $L_{\rm CH}$  and  $V_{\rm D}$  are reduced. However,  $\tau$  increases due to the degradation of ON-current. If we go horizontally in Table 2, *i.e.*  $L_{\rm CH}$  is scaled keeping  $V_{\rm D}$  constant, the PDP decreases due to decrease in the charge content in smaller devices, but  $\tau$  fluctuates between nodes depending on the value of  $I_{\rm ON}$  and the ratio  $(Q_{\rm ON} - Q_{\rm OFF})/I_{\rm ON}$ . The best performant devices should lie in lower left corner of the graph. We find two devices in that region,

|             | Fitting Parameters for $k \cdot p$ hamiltonian |                                      |                                  |                                      |         |  |  |

|-------------|------------------------------------------------|--------------------------------------|----------------------------------|--------------------------------------|---------|--|--|

| Method      | $a_c(eVÅ^2)$                                   | $a_{\nu}(\text{eV } \mathring{A}^2)$ | $b_c(\text{eV } \mathring{A}^2)$ | $b_{\nu}(\text{eV } \mathring{A}^2)$ | γ(eV Å) |  |  |

| DFT-PAW PBE | 4.581                                          | 3.19                                 | 9.453                            | 8.594                                | 5.28    |  |  |

| DFT-PAW HSE | 5.105                                          | 4.211                                | 17.188                           | 16.441                               | 5.92    |  |  |

**Table 3.** Fitting parameters of  $k \cdot p$  hamiltonian obtained by calibrating against DFT results.

namely  $L_{\rm CH}=10$  nm at  $V_{\rm D}=0.5$  V, *i.e.* the first node in the column of scaling rule =20 nm/V and  $L_{\rm CH}=12$  nm at  $V_{\rm D}=0.4$  V *i.e.* the second node in the column of scaling rule =30 nm/V. Interestingly, these two nodes represent the optimally designed GeSe-TFETs with respect to PDP-delay for both PBE and HSE calculations.

Next we analyze the  $\tau-I_{\rm ON}/I_{\rm OFF}$  graph in Fig. 6(c) and (d). Here the best performant devices should lie in the lower right corner. For a particular scaling rule  $I_{\rm ON}/I_{\rm OFF}$  ratio decreases as a function of  $L_{\rm CH}$  and  $V_{\rm D}$  and  $\tau$  increases. The degradation in values of  $\tau$  becomes prominent as devices are scaled below  $L_{\rm CH}=12$  nm due to the rapid decrease of  $I_{\rm ON}$  compared to  $(Q_{\rm ON}-Q_{\rm OFF})$ . Even so, we still find the two nodes pointed out previously, lying in the lower right corner of the graph demonstrating  $I_{\rm ON}/I_{\rm OFF}>10^4$  and  $\tau=3$  ps. Moreover, in all of the plots we find that the devices considered under scaling rule 30 nm/V perform better in terms of switching speed and energy consumption.

In conclusion, monolayer GeSe-TFETs show appreciable performance with respect to  $I_{\rm ON}-I_{\rm OFF}$  ratio while scaling down to 0.3 V supply voltage with 9 nm channel and to 8 nm channel with a supply voltage of 0.4 V. It is also worth noting that, PBE TFETs always outperform HSE TFETs in case of  $I_{\rm ON}$  requirements due to its higher tunneling probability arising from lower band gap value. However, with respect to the dynamic metrics both HSE and PBE TFETs exhibit a common trend in terms of PDP-delay and delay- $I_{\rm ON}/I_{\rm OFB}$  with certain nodes dominating in switching speed and dynamic power dissipation. Apart from these, all the devices show comparable ON-current values with other 2D material based homojunction-TFETs. Therefore from our studies it can be predicted that monolayer GeSe can be seen as a potential candidate for 2D material based TFET in the future due to its interesting electronic properties and better air stability.

### Methods

DFT calculations are carried out using generalized gradient approximation (GGA) as implemented in the code VASP<sup>65-67</sup> with PAW<sup>68</sup> method using the PBE exchange-correlation functional. Also, the HSE hybrid functional is used to determine electronic properties. A plane wave cutoff energy of 545 eV is used and a  $\Gamma$ -centered  $8 \times 8 \times 1$  (in X, Y and Z directions) k-mesh is found to be suitable to sample the Brillouin zone. Electronic convergence is achieved when the difference in energy of successive electronic steps becomes less than  $10^{-4}$  eV, whereas the structural geometry is optimized until the maximum force on every atom falls below 0.01 eV/Å. A large vacuum space of more than 20 Å in the direction of Z is applied to avoid any interaction between successive layers.

For generating CBS, we perform DFT calculations using Atomistix Tool Kit (ATK)<sup>69</sup>, where the accuracy of the calculations largely depends on the selection of norm-conserving pseudopotentials and numerical LCAO basis sets. We employ the GGA as the exchange correlation in conjunction with the PBE functional. We use "SG15" norm-conserving pseudopotentials with "Medium" basis sets. The optimized "SG15" provide smooth pseudopotentials with multiple projectors and non-linear core corrections<sup>70,71</sup>. For the purpose of obtaining the electronic structure of monolayer GeSe using "SG15" pseudopotentials, we set the k-points in the Monkhorst-Pack grid as  $9 \times 9 \times 1$  (in X, Y and Z directions). The density mesh cutoff, in the numerical accuracy settings, is taken as 150 Hartree

For simulating transport we conceive a two-band  $k \cdot p$  hamiltonian<sup>72,73</sup> which is given as

$$H(\mathbf{k}) \equiv \begin{bmatrix} a_c k_x^2 + b_c k_y^2 & \gamma k_x \\ \gamma k_x & a_v k_x^2 + b_v k_y^2 \end{bmatrix},\tag{1}$$

where  $\mathbf{k} = (k_x, k_y)$  is the in-plane wave vector. It is worth noting that since no other bands are present near the CBM and VBM in the energy window (-1 to 2 eV), therefore the two-band model is sufficient to capture transport in our device. The off-diagonal first order  $k_x$  terms in the hamiltonian are responsible for opening a band gap<sup>72</sup>. The fitting parameters used in calibration of the  $k \cdot p$  model are listed in Table 3.

The electron and hole effective masses along the transport direction as calculated from the  $k \cdot p$  model for PBE are  $0.1317 \, m_0$  and  $0.1384 \, m_0$  respectively whereas for HSE are  $0.1401 \, m_0$  and  $0.1449 \, m_0$  respectively. Next we model the transport by self-consistently solving the transport equations based on NEGF formalism with the Poisson's equation. We assume the device to be invariant along the transverse direction y and impose Born-von Karman periodic boundary conditions. This enables us to parameterise the hamiltonian and the Green's functions in terms of the transversal wave vector  $k_y$ . The retarded Green's function<sup>74,75</sup> for each wave vector  $k_y$ , is calculated as

$$G'(k_y, E) = [EI - H(k_y) - \Sigma_S - \Sigma_D]^{-1}$$

(2)

where E is the energy,  $H(k_y)$  is the hamiltonian matrix discretized along the transport direction x, I is the identity matrix and  $\Sigma_{S}/\Sigma_{D}$  are self-energy matrices associated to the source/drain contacts. From the retarded Green's function  $G^r(k_y, E)$ , we eventually calculate the electron and hole Green's functions:  $G^n(k_y, E)$  and  $G^p(k_y, E)$  and the current density from position i to i+1 along the x direction as follows:

$$G^{n}(k_{y}, E) = G^{r}(k_{y}, E) \Sigma_{n} G^{r\dagger}(k_{y}, E)$$

$$G^{p}(k_{y}, E) = G^{r}(k_{y}, E) \Sigma_{p} G^{r\dagger}(k_{y}, E)$$

$$J^{n(p)}{}_{i,i+1} = \sum_{k_{y}} \frac{2q}{\hbar S} \int_{-\infty}^{+\infty} \frac{dE}{2\pi} [H_{i,i+1} G^{n(p)}{}_{i+1,i}(k_{y}, E) - H_{i+1,i} G^{n(p)}{}_{i,i+1}(k_{y}, E)]$$

(3)

where

$$\Sigma_{n} \equiv (\Sigma_{S/D} - \Sigma_{S/D}^{\dagger}) \cdot f_{S/D}$$

$$\Sigma_{p} \equiv (\Sigma_{S/D} - \Sigma_{S/D}^{\dagger}) \cdot (1 - f_{S/D})$$

(4)

with  $\dagger$  denoting the transpose conjugate and  $f_{S/D}$  denoting the Fermi-Dirac distribution function at source/drain. The 2D Poisson's equation is solved in a cross-section in the x-z plane. The discretization is based on the finite difference method, enforcing Dirichlet boundary conditions at the metal gate electrodes and Neumann boundary conditions on the rest of the edges.

#### References

- 1. Dennard, R. H., Gaensslen, F. H., Rideout, V. L., Bassous, E. & LeBlanc, A. R. Design of ion-implanted MOSFET's with very small physical dimensions. *IEEE Journal of Solid-State Circuits* 9, 256–268 (1974).

- 2. Johnsson, L. & Netzer, G. The impact of Moore's Law and loss of Dennard scaling: Are DSP SoCs an energy efficient alternative to x86 SoCs? *Journal of Physics: Conference Series* 762, 012022 (2016).

- 3. Moore, G. E. Cramming more components onto integrated circuits. Proceedings of the IEEE 86, 82-85 (1998).

- 4. Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. *Nano letters* **8**, 405–410 (2008).

- 5. Zhirnov, V. V. & Cavin, R. K. Nanoelectronics: Negative capacitance to the rescue? Nature Nanotechnology 3, 77–78 (2008).

- 6. Gopalakrishnan, K., Griffin, P. B. & Plummer, J. D. I-MOS: A novel semiconductor device with a subthreshold slope lower than kT/q. In *Electron Devices Meeting*, 2002. *IEDM'02*. *International*, 289–292 (IEEE, 2002).

- 7. Choi, W. Y., Song, J. Y., Lee, J. D., Park, Y. J. & Park, B. G. 70-nm impact-ionization metal-oxide-semiconductor (I-MOS) devices integrated with tunneling field-effect transistors (TFETs). In *Electron Devices Meeting*, 2005. IEDM Technical Digest. IEEE International, 955–958 (IEEE, 2005).

- 8. Björk, M. T., Hayden, O., Schmid, H., Riel, H. & Riess, W. Vertical surround-gated silicon nanowire impact ionization field-effect transistors. *Applied Physics Letters* **90**, 142110 (2007).

- Mayer, F. et al. Impact of SOI, Si<sub>1-x</sub>Ge<sub>x</sub> OI and GeOI substrates on CMOS compatible tunnel FET performance. In Electron Devices Meeting, 2008. IEDM 2008. IEEE International, 1–5 (IEEE, 2008).

- 10. Verhulst, A. S., Vandenberghe, W. G., Maex, K. & Groeseneken, G. Boosting the on-current of a *n*-channel nanowire tunnel field-effect transistor by source material optimization. *Journal of Applied Physics* **104**, 064514 (2008).

- 11. Seabaugh, A. C. & Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. *Proceedings of the IEEE* **98**, 2095–2110 (2010).

- 12. Avci, U. E., Morris, D. H. & Young, I. A. Tunnel field-effect transistors: Prospects and challenges. *IEEE Journal of the Electron Devices Society* 3, 88–95 (2015).

- 13. Gandhi, R., Chen, Z., Singh, N., Banerjee, K. & Lee, S. Vertical Si-Nanowire *n*-Type Tunneling FETs With Low Subthreshold Swing (≤50 mV/decade)at Room Temperature. *IEEE Electron Device Letters* **32**, 437–439 (2011).

- $14. \ Lu, H. \& Seabaugh, A. Tunnel field-effect transistors: State-of-the-art. {\it IEEE Journal of the Electron Devices Society 2}, 44-49 (2014).$

- 15. Luisier, M. & Klimeck, G. Simulation of nanowire tunneling transistors: From the Wentzel-Kramers-Brillouin approximation to full-band phonon-assisted tunneling. *Journal of Applied Physics* **107**, 084507 (2010).

- 16. Knoch, J. & Appenzeller, J. Modeling of high-performance p-type III-V heterojunction tunnel FETs. *IEEE Electron Device Letters* 31, 305–307 (2010).

- Zhou, G. et al. Novel gate-recessed vertical InAs/GaSb TFETs with record high I <sub>ON</sub> of 180 μ A/μm at VDS = 0.5 V. In Electron Devices Meeting (IEDM), 2012 IEEE International, 32–6 (IEEE, 2012).

- 18. Li, R. et al. AlGaSb/InAs Tunnel Field-Effect Transistor With On-Current of 78 μA/μm at 0.5 V. IEEE electron device letters 33, 363–365 (2012)

- Kim, S. H., Kam, H., Hu, C. & Liu, T. J. K. Germanium-source tunnel field effect transistors with record high I ON/I OFF. In VLSI Technology, 2009 Symposium on, 178–179 (IEEE, 2009).

- Lee, M. H., Chang, S. T., Wu, T. H. & Tseng, W. N. Driving current enhancement of strained Ge (110) p-type tunnel FETs and anisotropic effect. IEEE Electron Device Letters 32, 1355–1357 (2011).

- 21. Damrongplasit, N., Shin, C., Kim, S. H., Vega, R. A. & Liu, T. J. K. Study of random dopant fluctuation effects in germanium-source tunnel FETs. *IEEE Transactions on Electron Devices* **58**, 3541–3548 (2011).

- 22. Zhang, Q., Fang, T., Xing, H., Seabaugh, A. & Jena, D. Graphene nanoribbon tunnel transistors. *IEEE Electron Device Letters* 29, 1344–1346 (2008)

- 23. Zhao, P., Chauhan, J. & Guo, J. Computational study of tunneling transistor based on graphene nanoribbon. *Nano letters* **9**, 684–688 (2009).

- 24. Chin, S. K., Seah, D., Lam, K. T., Samudra, G. S. & Liang, G. Device physics and characteristics of graphene nanoribbon tunneling FETs. *IEEE Transactions on Electron Devices* **57**, 3144–3152 (2010).

- 25. Lam, K. T., Cao, X. & Guo, J. Device performance of heterojunction tunneling field-effect transistors based on transition metal dichalcogenide monolayer. *IEEE Electron Device Letters* 34, 1331–1333 (2013).

- Ilatikhameneh, H. et al. Tunnel field-effect transistors in 2-D transition metal dichalcogenide materials. IEEE Journal on Exploratory Solid-State Computational Devices and Circuits 1, 12–18 (2015).

- 27. Seo, J., Jung, S. & Shin, M. The Performance of Uniaxially Strained Phosphorene Tunneling Field-Effect Transistors. *IEEE Electron Device Letters* 38, 1150–1152 (2017).

- 28. Chen, F. W., Ilatikhameneh, H., Ameen, T. A., Klimeck, G. & Rahman, R. Thickness engineered tunnel field-effect transistors based on phosphorene. *IEEE Electron Device Letters* 38, 130–133 (2017).

- 29. Ameen, T. A., Ilatikhameneh, H., Klimeck, G. & Rahman, R. Few-layer phosphorene: An ideal 2D material for tunnel transistors. *Scientific reports* 6, 28515 (2016).

- 30. Szabó, Á., Koester, S. J. & Luisier, M. Ab-initio simulation of van der waals MoTe 2-SnS 2 heterotunneling fets for low-power electronics. *IEEE Electron Device Letters* **36**, 514–516 (2015).

- 31. Cao, J. et al. Operation and Design of van der Waals Tunnel Transistors: A 3-D Quantum Transport Study. IEEE Transactions on Electron Devices 63, 4388–4394 (2016).

- 32. Chen, F. et al. Transport in vertically stacked hetero-structures from 2D materials. In *Journal of Physics: Conference Series*, vol. 864, 012053 (IOP Publishing, 2017).

- 33. Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91-95 (2015).

- 34. Roy, T. et al. Dual-gated MoS<sub>2</sub>/WSe<sub>2</sub> van der Waals tunnel diodes and transistors. Acs Nano 9, 2071–2079 (2015).

- 35. Aretouli, K. E. et al. Epitaxial 2D SnSe<sub>2</sub>/2D WSe<sub>2</sub> van der Waals Heterostructures. ACS applied materials & interfaces 8, 23222–23229 (2016).

- Singh, A. K. & Hennig, R. G. Computational prediction of two-dimensional group-IV mono-chalcogenides. Applied Physics Letters 105, 042103 (2014).

- 37. Hu, Y. et al. GeSe monolayer semiconductor with tunable direct band gap and small carrier effective mass. Applied Physics Letters 107, 122107 (2015).

- 38. Shi, G. & Kioupakis, E. Anisotropic spin transport and strong visible-light absorbance in few-layer SnSe and GeSe. *Nano letters* 15, 6926–6931 (2015).

- Zhang, S. et al. Structural and electronic properties of atomically thin germanium selenide polymorphs. Science China Materials 58, 929–935 (2015).

- 40. Gomes, L. C. & Carvalho, A. Phosphorene analogues: Isoelectronic two-dimensional group-IV monochalcogenides with orthorhombic structure. *Physical Review B* **92**, 085406 (2015).

- 41. Xu, L., Yang, M., Wang, S. J. & Feng, Y. P. Electronic and optical properties of the monolayer group-IV monochalcogenides MX (M = Ge, Sn; X = S, Se, Te). *Physical Review B* **95**, 235434 (2017).

- 42. Cheng, K. et al. Lateral heterostructures of monolayer group-IV monochalcogenides: band alignment and electronic properties. *Journal of Materials Chemistry C* 5, 3788–3795 (2017).

- 43. Yoon, S. M., Song, H. J. & Choi, H. C. p-Type Semiconducting GeSe Combs by a Vaporization–Condensation–Recrystallization (VCR) Process. *Advanced Materials* 22, 2164–2167 (2010).

- 44. Vaughn, D. D. II, Patel, R. J., Hickner, M. A. & Schaak, R. E. Single-crystal colloidal nanosheets of GeS and GeSe. *Journal of the American Chemical Society* 132, 15170–15172 (2010).

- 45. Xue, D. J. et al. Anisotropic Photoresponse Properties of Single Micrometer-Sized GeSe Nanosheet. Advanced Materials 24, 4528–4533 (2012).

- 46. Vaughn, D. D. et al. Colloidal Synthesis and Electrical Properties of GeSe Nanobelts. Chemistry of Materials 24, 3643-3649 (2012).

- Mukherjee, B. et al. NIR Schottky photodetectors based on individual single-crystalline GeSe nanosheet. ACS applied materials & interfaces 5, 9594–9604 (2013).

- 48. Ramasamy, P., Kwak, D., Lim, D. H., Ra, H. S. & Lee, J. S. Solution synthesis of GeS and GeSe nanosheets for high-sensitivity photodetectors. *Journal of Materials Chemistry C* 4, 479–485 (2016).

- 49. Xue, D. J. et al. GeSe Thin-Film Solar Cells Fabricated by Self-Regulated Rapid Thermal Sublimation. J. Am. Chem. Soc 139, 958–965 (2017).

- 50. Gomes, L. C., Carvalho, A. & Castro Neto, A. H. Vacancies and oxidation of two-dimensional group-IV monochalcogenides. *Physical Review B* **94**, 054103 (2016).

- 51. Guo, Y., Zhou, S., Bai, Y. & Zhao, J. Oxidation resistance of monolayer group-IV monochalcogenides. ACS Applied Materials & Interfaces 9, 12013–12020 (2017).

- 52. 2dsemiconductors. http://www.2dsemiconductors.com/germanium-selenide-gese/. Last accessed: 2017-11-26.

- 53. Perdew, J. P., Burke, K. & Ernzerhof, M. Generalized gradient approximation made simple. Physical review letters 77, 3865 (1996).

- 54. Heyd, J., Scuseria, G. E. & Ernzerhof, M. Hybrid functionals based on a screened Coulomb potential. *The Journal of Chemical Physics* 118, 8207–8215 (2003).

- 55. Peng, X., Wei, Q. & Copple, A. Strain-engineered direct-indirect band gap transition and its mechanism in two-dimensional phosphorene. *Physical Review B* **90**, 085402 (2014).

- 56. Ziletti, A. et al. Phosphorene oxides: Bandgap engineering of phosphorene by oxidation. Physical Review B 91, 085407 (2015).

- 57. Wang, L., Kutana, A., Zou, X. & Yakobson, B. I. Electro-mechanical anisotropy of phosphorene. Nanoscale 7, 9746–9751 (2015).

- 58. International Technology Roadmap for Semiconductors. http://www.itrs2.net/2013-itrs.html. Last accessed: 2017-11-26.

- 59. Sylvia, S. S., Khayer, M. A., Alam, K. & Lake, R. K. Doping, tunnel barriers, and cold carriers in InAs and InSb nanowire tunnel transistors. *IEEE transactions on electron devices* **59**, 2996–3001 (2012).

- 60. Knoch, J., Mantl, S. & Appenzeller, J. Impact of the dimensionality on the performance of tunneling FETs: Bulk versus one-dimensional devices. *Solid-State Electronics* **51**, 572–578 (2007).

- 61. Terrones, H., López-Uras, F. & Terrones, M. Novel hetero-layered materials with tunable direct band gaps by sandwiching different metal disulfides and diselenides. *Scientific reports* 3, 1549 (2013).

- 62. Paul, A. K. et al. Photo-tunable transfer characteristics in MoTe<sub>2</sub>-MoS<sub>2</sub> vertical heterostructure. npj 2D Materials and Applications 1, 17 (2017).

- 63. Koswatta, S. O., Lundstrom, M. S. & Nikonov, D. E. Performance comparison between pin tunneling transistors and conventional MOSFETs. *IEEE Transactions on Electron Devices* **56**, 456–465 (2009).

- 64. Logoteta, D., Fiori, G. & Iannaccone, G. Graphene-based lateral heterostructure transistors exhibit better intrinsic performance than graphene-based vertical transistors as post-CMOS devices. *Scientific reports* 4 (2014).

- 65. Kresse, G. & Furhmuller, J. Software VASP, Vienna (1999); Kresse G. and Hafner J. Phys. Rev. B 47, R558 (1993).

- Kresse, G. & Furthmüller, J. Efficient iterative schemes for ab initio total-energy calculations using a plane-wave basis set. *Physical review B* 54, 11169 (1996).

- 67. Kresse, G. & Furthmüller, J. Efficiency of ab-initio total energy calculations for metals and semiconductors using a plane-wave basis set. *Computational materials science* **6**, 15–50 (1996).

- 68. Kresse, G. & Joubert, D. From ultrasoft pseudopotentials to the projector augmented-wave method. *Physical Review B* **59**, 1758 (1999).

- 69. QuantumWise Atomistix ToolKit (ATK) with Virtual NanoLab. http://quantumwise.com/. Last accessed: 2017-11-26.

- 70. Hamann, D. R. Optimized norm-conserving Vanderbilt pseudopotentials. *Physical Review B* **88**, 085117 (2013).

- 71. Schlipf, M. & Gygi, F. Optimization algorithm for the generation of ONCV pseudopotentials. *Computer Physics Communications* **196**, 36–44 (2015).

- 72. Appelbaum, I. & Li, P. Electrons, holes, and spin in the IV-VI monolayer four-six-enes. Physical Review B 94, 155124 (2016).

- 73. Rodin, A. S., Gomes, L. C., Carvalho, A. & Castro Neto, A. H. Valley physics in tin (II) sulfide. Physical Review B 93, 045431 (2016).

- 74. Datta, S. Quantum Transport: Atom to Transistor (2005).

- 75. Guo, J. Carbon nanotube electronics: modeling, physics, and applications. Purdue University (2004).

# **Acknowledgements**

This work was supported by Science and Engineering Research Board (SERB), Department of Science and Technology (DST), Government of India, under Grant SB/S3/EECE/0209/2015, Robert Bosch Cyber Physical System, Indian Institute of Science (IISc) Bangalore, under grant no:RBC00011.

# **Author Contributions**

A.K. performed the DFT-PAW calculations. D.S. conducted DFT-LCAO calculations. M.B. conducted NEGF calculations, generated and analyzed final results. S.M. conceived the problem statement and overall supervised the work. All authors contributed in the writing.

# Additional Information

**Supplementary information** accompanies this paper at https://doi.org/10.1038/s41598-018-24209-1.

**Competing Interests:** The authors declare no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2018