Portland State University PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

Summer 8-5-2015

# Scalable Equivalence Checking for Behavioral Synthesis

Zhenkun Yang Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Programming Languages and Compilers Commons Let us know how access to this document benefits you.

# **Recommended Citation**

Yang, Zhenkun, "Scalable Equivalence Checking for Behavioral Synthesis" (2015). *Dissertations and Theses.* Paper 2461. https://doi.org/10.15760/etd.2459

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

Scalable Equivalence Checking for Behavioral Synthesis

by

Zhenkun Yang

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

Dissertation Committee: Fei Xie, Chair Suresh Singh Feng Liu Sandip Ray Fu Li

Portland State University 2015

# ABSTRACT

Behavioral synthesis is the process of compiling an Electronic System Level (ESL) design to a register-transfer level (RTL) implementation. ESL specifications define the design functionality at a high level of abstraction (e.g., with C/C++ or SystemC), and thus provide a promising approach to address the exacting demands to develop feature-rich, optimized, and complex hardware systems within aggressive time-to-market schedules. Behavioral synthesis entails application of complex and error-prone transformations during the compilation process. Therefore, the adoption of behavioral synthesis highly depends on our ability to ensure that the synthesized RTL conforms to the ESL description.

This dissertation provides an end-to-end scalable equivalence checking support for behavioral synthesis. The major challenge of this research is to bridge the huge semantic gap between the ESL and RTL descriptions, which makes the direct comparison of designs in ESL and RTL difficult. Moreover, a large number and a wide variety of aggressive transformations from front-end to back-end require an end-to-end scalable checking framework.

A behavioral synthesis flow can be divided into three major phases, including 1) *front-end*: compiler transformations, 2) *scheduling*: assigning each operation a clock cycle and satisfying the user-specified constraints, and 3) *back-end*: local optimizations and RTL generation. In our end-to-end and incremental equivalence checking framework, we check each of the three phases one by one. Firstly, we check the front-end that consists of a sequence of compiler transformations by decomposing it into a series of checks, one for each transformation applied. We symbolically explore paths in the input and output programs of each transformation, and check whether the input and output programs have the same observable behavior under the same path condition. Secondly, we validate the scheduling transformation by checking the preservation of control and data dependencies, and the preservation of I/O timing in the user-specified scheduling mode. Thirdly, we symbolically simulate the scheduled design and the generated RTL cycle by cycle, and check the equivalence of each mapped variables. We also develop several key optimizations to make our back-end checker scale to real industrial-strength designs. In addition to the equivalence checking framework, we also present an approach to detecting deadlocks introduced by parallelization of RTL blocks that are connected by synthesized interfaces with handshaking protocols.

To demonstrate the efficiency and scalability of our framework, we evaluated it on transformations applied by a behavioral synthesis tool to designs from the C-based CHStone and SystemC-based S2CBench benchmarks. Based on the evaluation results, our front-end checker can efficiently validate more than 75 percent of the total of 1008 compiler transformations applied to designs from the CHStone benchmark, taking an average time of 1.5 seconds per transformation. Our scheduling checker can validate control-data dependencies and I/O timing of all designs from S2CBench benchmark. Our back-end checker can handle designs with more than 32K lines of synthesized RTL from the CHStone benchmark, which demonstrates the scalability of the checker. Furthermore, our checker found several bugs in a commercial tool, underlining both the importance of formal equivalence checking and the effectiveness of our approach.

# DEDICATION

To my wife Jialu.

To my parents Xiuzeng and Yunpeng.

In memory of my grandmother Xiuli Zhang (1920-2004)

# ACKNOWLEDGMENTS

This dissertation could not have been accomplished without generous support from many talented people. I am grateful to all of them from the bottom of my heart.

First and foremost, I would like to express my great appreciation to my advisor, Prof. Fei Xie, for his enlightening guidance and generous support during my Ph.D study. Prof. Xie is an excellent advisor. He taught me how to identify research problems and become an independent researcher. Without his support and encouragement, this dissertation would not have been accomplished. His deep theoretical knowledge and passion about developing practical tools have great influence on my Ph.D research and future career.

I would like to thank Prof. Suresh Singh, Prof. Feng Liu, Dr. Sandip Ray, and Prof. Fu Li for serving on my dissertation committee. Thanks for their advice and sacrifice of valuable summer time for coming to my dissertation defense.

I would like to thank Dr. Kecheng Hao and Dr. Sandip Ray. I benefit a lot from the great infrastructure they built before I joined the group. Many research ideas of this dissertation come from fruitful discussions with them. I sincerely thank them for being excellent collaborators. I am grateful that I have this great opportunity to work with talented group members: Kai Cong, Li Lei, Bin Lin, Disha Puri, Bo Chen, and Christopher Havlicek.

Finally, I would like to thank my parents for their continuous support and endless love. Special thanks to my wife Jialu for her sound and complete love.

# **Table of Contents**

| Abstract           |                                            | i    |  |

|--------------------|--------------------------------------------|------|--|

| Dedication ii      |                                            |      |  |

| Acknowledgments in |                                            |      |  |

| List of Table      | es                                         | vii  |  |

| List of Figur      | res                                        | viii |  |

| List of Abbr       | reviations                                 | xi   |  |

| Chapter 1          | Introduction                               | 1    |  |

| 1.1                | Motivation                                 | 1    |  |

| 1.2                | Problem Statement                          | 3    |  |

| 1.3                | Proposed Equivalence Checking Framework    | 4    |  |

| 1.4                | Dissertation Outline                       | 7    |  |

| Chapter 2          | Background                                 | 8    |  |

| 2.1                | Behavioral Synthesis                       | 8    |  |

| 2.2                | Symbolic Simulation                        | 9    |  |

| 2.3                | Formal Equivalence Checking                | 10   |  |

| Chapter 3          | Front-end Compiler Transformation Checking | 12   |  |

| 3.1                | Notations and Definitions                  | 12   |  |

| 3.2                | Equivalence Checking Framework             | 15   |  |

| 3.3                | Modular Reasoning across Functions         | 18   |  |

| 3.4                | Handling Loops                             | 21   |  |

| 3.5                | Experimental Results                       | 24   |  |

| 3.6        | Related Work                                                                                                                                      | 27 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7        | Summary                                                                                                                                           | 29 |

| Chapter 4  | Validating Scheduling Transformation                                                                                                              | 32 |

| 4.1        | Scheduling Transformation                                                                                                                         | 32 |

| 4.2        | Formalization                                                                                                                                     | 35 |

| 4.3        | Validation Approach                                                                                                                               | 40 |

| 4.3.1      | Validating Trace Compatibility                                                                                                                    | 40 |

| 4.3.2      | Validating I/O Timing                                                                                                                             | 40 |

| 4.4        | Experimental Results                                                                                                                              | 44 |

| 4.5        | Related Work                                                                                                                                      | 47 |

| 4.6        | Summary                                                                                                                                           | 48 |

| Chapter 5  | Scaling Back-end RTL Generation Checking                                                                                                          | 49 |

| 5.1        | Equivalence Checking Framework                                                                                                                    | 49 |

| 5.2        | Handling Operation Gating Optimization                                                                                                            | 51 |

| 5.3        | Handling Global Variables                                                                                                                         | 56 |

| 5.4        | Experimental Results                                                                                                                              | 58 |

| 5.4.1      | Performance Evaluation                                                                                                                            | 58 |

| 5.4.2      | A Behavioral Synthesis Bug                                                                                                                        | 60 |

| 5.5        | Related Work $\ldots$                                            | 61 |

| 5.6        | Summary                                                                                                                                           | 63 |

| Chapter 6  | Interface Synthesis Checking                                                                                                                      | 64 |

| 6.1        | Interface Synthesis                                                                                                                               | 65 |

| 6.2        | Deadlock Detection                                                                                                                                | 68 |

| 6.2.1      | Deadlock Example                                                                                                                                  | 68 |

| 6.2.2      | Deadlock Detection Algorithm                                                                                                                      | 71 |

| 6.3        | Experimental Results                                                                                                                              | 75 |

| 6.4        | Related Work $\ldots$                                            | 77 |

| 6.5        | Summary                                                                                                                                           | 78 |

| Chapter 7  | Conclusion and Future Work                                                                                                                        | 79 |

| 7.1        | $Conclusion \ldots \ldots$ | 79 |

| 7.2        | Future Work                                                                                                                                       | 80 |

| References |                                                                                                                                                   | 82 |

# List of Tables

| Table 3.1       | Summary of CHStone Benchmark for Equivalence Checking  |    |

|-----------------|--------------------------------------------------------|----|

|                 | of Front-end Compiler Transformations                  | 24 |

| Table 3.2       | Summary of Evaluation on CHStone Benchmark for Equiva- |    |

|                 | lence Checking of Front-end Compiler Transformations   | 25 |

| <b>T</b> 11 4 1 |                                                        |    |

| Table 4.1       | Summary of Evaluation on S2CBench Benchmark            | 44 |

| Table 5.1       | Summary of CHStone Benchmark for Equivalence Checking  |    |

|                 | of Back-end RTL Generation                             | 58 |

| Table 5.2       | Summary of Evaluation on CHStone Benchmark for Equiva- |    |

|                 | lence Checking of Back-end RTL Generation              | 59 |

|                 |                                                        |    |

# List of Figures

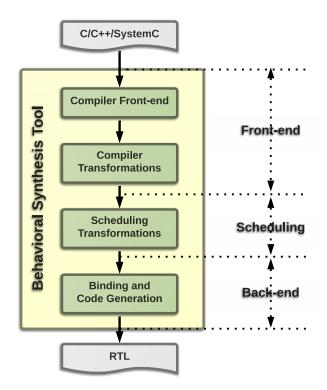

| Figure 1.1 | Behavioral synthesis flow                                                                                                                                                                                                                                                                                                            | 2  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

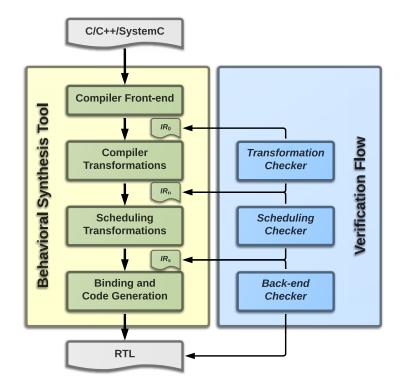

| Figure 1.2 | Behavioral synthesis and verification flow                                                                                                                                                                                                                                                                                           | 5  |

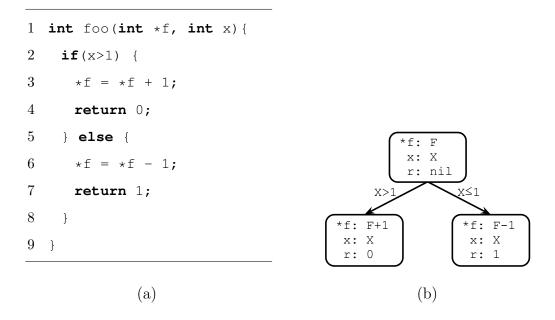

| Figure 2.1 | A simple function foo in C with its symbolic execution tree.<br>(a) Function foo in C. (b) Symbolic execution tree of foo,<br>where F and X are symbolic values for $*f$ and x, r denotes<br>the return value, and nil denotes that the value is not yet<br>available.                                                               | 10 |

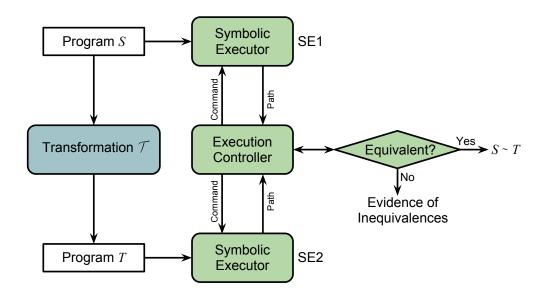

| Figure 3.1 | 1 Framework of checking equivalence between program $S$ and $T$ , which are the input and output of transformation $\mathcal{T}$ respectively.                                                                                                                                                                                       |    |

| Figure 3.2 | A simple function bar in C with its symbolic execution tree.<br>(a) Function bar in C. (b) Symbolic execution tree of bar,<br>where F and X are symbolic values for *f and x, r denotes the                                                                                                                                          |    |

|            | return value, and nil denotes that the value is not yet available.                                                                                                                                                                                                                                                                   | 17 |

| Figure 3.3 | Symbolic execution tree of function foo and bar, where bar<br>is executed after foo, and based on the execution condition                                                                                                                                                                                                            |    |

|            | of foo.                                                                                                                                                                                                                                                                                                                              | 18 |

| -          | Global variable usage with sub-function call example A simple function with a loop in C and its IR. (a) Function <b>f</b> has an unbounded <b>for</b> loop. (b) The IR of <b>f</b> , with boxes representing basic blocks, and arrows representing control flow. Control flow merge is implemented via $\phi$ -instructions in basic | 20 |

|            | block $B_2$ .                                                                                                                                                                                                                                                                                                                        | 21 |

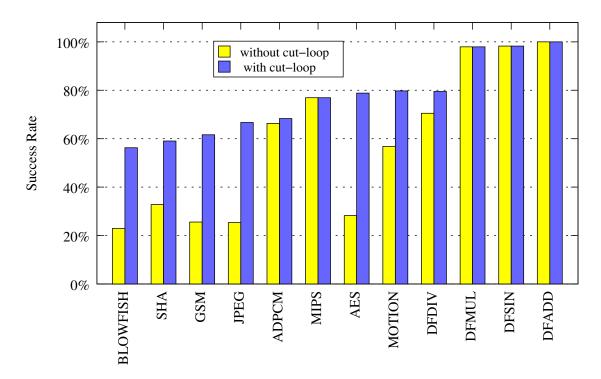

| Figure 3.6 | Comparison of success rate on designs of CHStone benchmark                                                                                                                                                                                                                                                                           |    |

|            | without and with cut-loop optimization. The $x$ axis is ordered<br>by the success rate with cut-loop                                                                                                                                                                                                                                 | 26 |

|            |                                                                                                                                                                                                                                                                                                                                      | 40 |

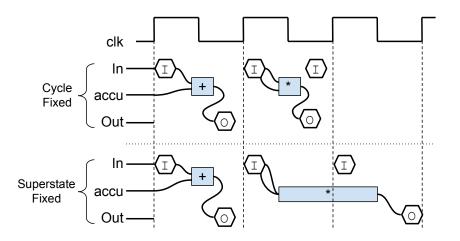

| Figure 4.1   | An example of a SystemC thread, which has two superstates                           |    |

|--------------|-------------------------------------------------------------------------------------|----|

|              | in the while loop.                                                                  | 33 |

| Figure 4.2   | Cycle-fixed and superstate-fixed scheduling mode for the while                      |    |

|              | loop in thread in Fig. 4.1.                                                         | 34 |

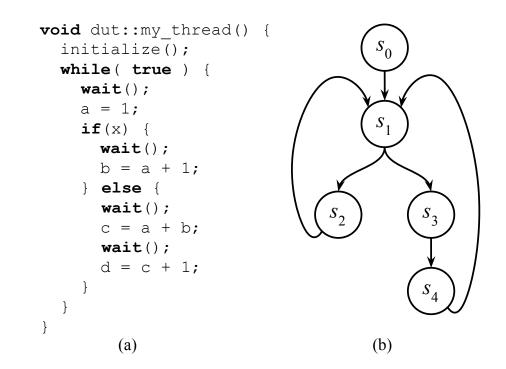

| Figure 4.3   | Extract <i>superstates</i> of a thread in SystemC. (a) my_thread is                 |    |

|              | a thread of module dut, wait statements are the boundary of                         |    |

|              | superstates in SystemC. (b) Superstates and their transitions                       |    |

|              | of $my\_thread$                                                                     | 41 |

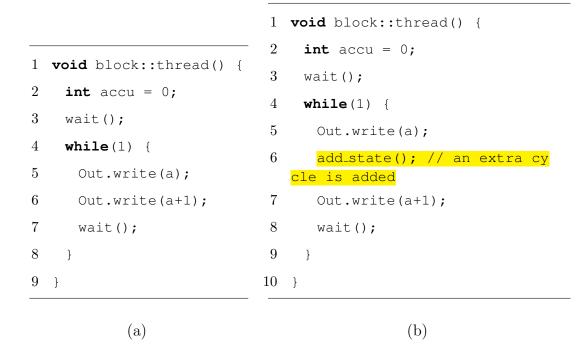

| Figure 4.4   | An example of incorrect scheduling of signal I/O. (a). Design                       |    |

|              | before scheduling, where a signal output Out is written twice                       |    |

|              | with different values, however, only the last write is visible                      |    |

|              | and valid. (b). The design after scheduling, where two writes                       |    |

|              | of Out are scheduled to two different cycles. For simplicity, we                    |    |

|              | use function add_state() to represent the scheduling trans-                         |    |

|              | formation will add a new state on that line                                         | 45 |

| Figure 4.5   | An example of incorrect scheduling of signal I/O. (a). Design                       |    |

|              | before scheduling, where a local signal <b>sig</b> is written and then              |    |

|              | read at the same cycle. The read statement takes the old                            |    |

|              | value. (b). The design after scheduling, where the write and                        |    |

|              | read statements are scheduled to two different cycles, then                         |    |

|              | the read takes the new value. For simplicity, we use function                       |    |

|              | add_state() to represent the scheduling transformation will                         |    |

|              | add a new state on that line. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 46 |

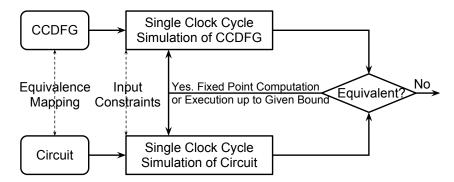

| Figure 5.1   | Dual-rail cycle-based symbolic simulation of a CCDFG and                            |    |

| i iguite 0.1 | RTL circuit.                                                                        | 49 |

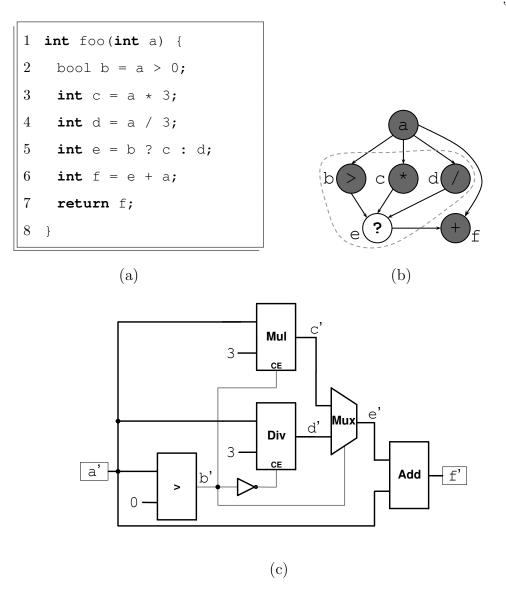

| Figure 5.2   | Operation gating example. (a) C code. (b) Data flow graph.                          | 10 |

| 1 iguite 0.2 | (c) Schematic of generated RTL                                                      | 52 |

| Figure 5.3   | Simplified C source code of the MOTION example.                                     | 61 |

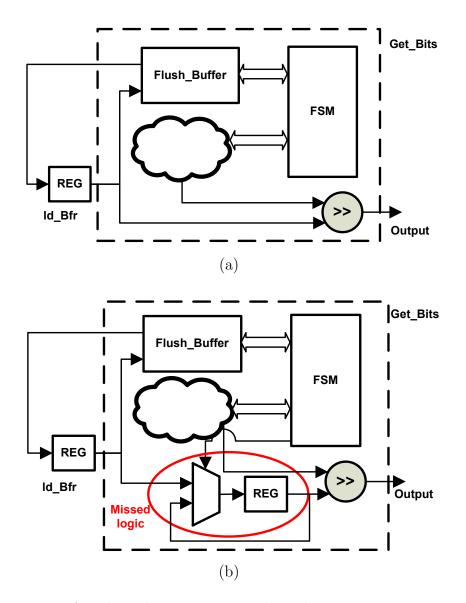

| -            | Bug found in the MOTION example, where an important regis-                          | 01 |

| 1 15010 0.4  | ter is eliminated. (a). Wrong RTL (b). Correct RTL                                  | 62 |

|              | to be character (a). Wrong fill (b). Confect fill                                   | 04 |

ix

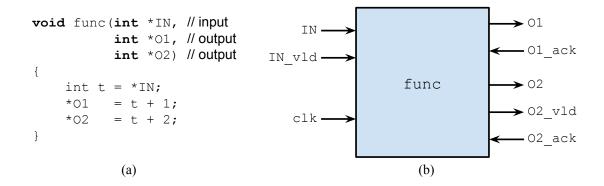

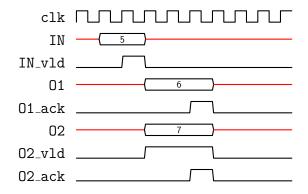

| Figure 6.1                                                           | gure 6.1 Example of interface synthesis. (a). A simple C function with                                |    |  |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----|--|--|

|                                                                      | one input and two outputs. (b). Synthesized block diagram of                                          |    |  |  |

|                                                                      | the C function. Input IN has an associated valid signal $IN_vld$                                      |    |  |  |

|                                                                      | to indicate when IN is ready to be read. Output O1 has an as-                                         |    |  |  |

|                                                                      | sociated acknowledge signal O1_ack to allow the downstream                                            |    |  |  |

|                                                                      | block to acknowledge block 'func' that the output data <b>01</b> has                                  |    |  |  |

|                                                                      | been read. Output 0_2 has both valid and acknowledge signals.                                         |    |  |  |

| Figure 6.2                                                           | Timing diagram of the synthesized block 'func'                                                        | 66 |  |  |

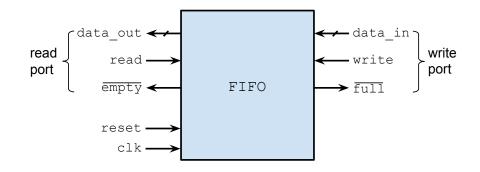

| Figure 6.3                                                           | Figure 6.3 Block diagram of a FIFO with read and write ports. Signals                                 |    |  |  |

|                                                                      | $\overline{\texttt{empty}}$ and $\overline{\texttt{full}}$ indicate the emptiness and fullness of the |    |  |  |

|                                                                      | FIFO                                                                                                  | 67 |  |  |

| Figure 6.4                                                           | Timing diagram of a FIFO with depth of 2                                                              | 67 |  |  |

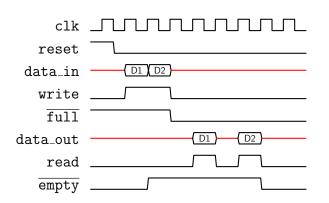

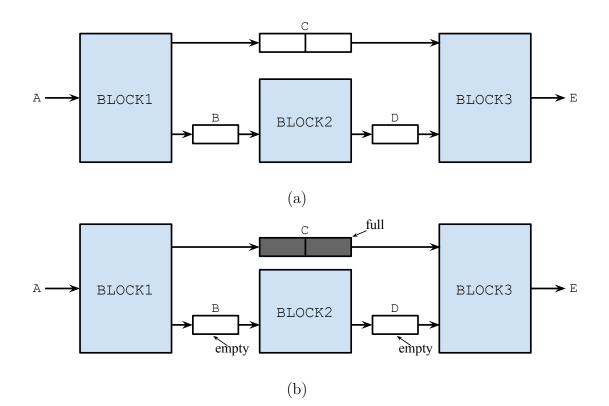

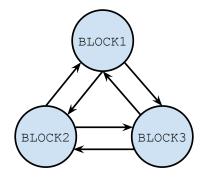

| Figure 6.5                                                           | A design in C with three blocks.                                                                      | 69 |  |  |

| Figure 6.6 Deadlock example: a synthesized design with three blocks. |                                                                                                       |    |  |  |

|                                                                      | Interface $\tt C$ is a FIFO of depth of 2. Interfaces $\tt B$ and $\tt D$ are                         |    |  |  |

|                                                                      | FIFOs of depth of 1. (a). FIFOs are initialize to be empty.                                           |    |  |  |

|                                                                      | (b). Status of FIFOs when the design deadlocks                                                        | 70 |  |  |

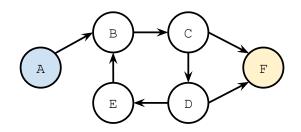

| Figure 6.7                                                           | Dependency graph of Fig. 6.6                                                                          | 72 |  |  |

| Figure 6.8                                                           | Dependency graph example                                                                              | 73 |  |  |

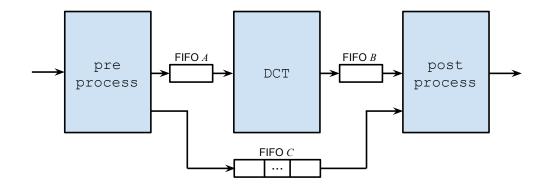

| Figure 6.9                                                           | Block diagram of DCT example                                                                          | 76 |  |  |

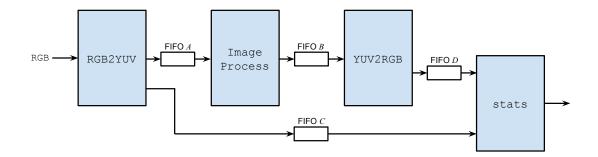

| Figure 6.10                                                          | Block diagram of YUV Filter example.                                                                  | 76 |  |  |

х

# LIST OF ABBREVIATIONS

| BDD   | Binary Decision Diagram            |

|-------|------------------------------------|

| CCDFG | Clocked Control/Data Flow Graph    |

| CDFG  | Control/Data Flow Graph            |

| DFG   | Data Flow Graph                    |

| EDA   | Electronic Design Automation       |

| ESL   | Electronic System Level            |

| FIFO  | First In, First Out                |

| FSMD  | Finite State Machine with Datapath |

| HLS   | High-Level Synthesis               |

| IP    | Intellectual Property              |

| IR    | Intermediate Representation        |

| PSL   | Property Specification Language    |

| RTL   | Register Transfer Level            |

| SAT   | Boolean satisfiability problem     |

| SEC   | Sequential Equivalence Checking    |

| SMT   | Satisfiability Modulo Theories     |

| SSA   | Single Static Assignment           |

| STP   | State Transition Partition         |

| SVA   | SystemVerilog Assertions           |

|       |                                    |

## Chapter 1

### INTRODUCTION

#### 1.1 MOTIVATION

With the ever-growing complexity in modern VLSI systems, designing high-quality hardware at Register-Transfer Level (RTL) under high time-to-market pressure is challenging. Behavioral synthesis, also called high-level synthesis (HLS), is the process of compiling an Electronic System Level (ESL) design to an RTL implementation. ESL specifications define the design functionality at a high level of abstraction (*e.g.*, with C/C++ or SystemC), and thus provide a promising approach to address the exacting demands to develop feature-rich, optimized, and complex hardware systems within aggressive time-to-market schedules. Recent years have seen the adoption of behavioral synthesis in industry. A typical example is how Google uses a behavioral synthesis tool to design the G2 VP9 hardware decoder [72] to implement the VP9 video compression standard.

As shown in Fig. 1.1, a behavioral synthesis takes a design specified in highlevel languages, applies a sequence of transformations, and generates targeted RTL netlist. A typical behavioral synthesis flow can be roughly divided into three phases: *front-end*, *scheduling* and *back-end*. The front-end primarily entails compiler transformations; the goal is to reduce code complexity of the generated design, maximize data locality, *etc.* [19], and transform the design into a form more suitable for resource allocation and control synthesis. The scheduling transformation

Figure 1.1: Behavioral synthesis flow

schedules each operation a clock cycle to execute. The scheduled design needs to satisfy user-specified timing and resource constraints at the same time. The back-end entails local, sometimes manual, optimizations for a number of metrics, e.g., performance and power consumption, and generates RTL at the end.

Behavioral synthesis provides two major advantages over traditional design methodology: accelerated development and fast verification. Firstly, development of the functionality at a higher abstraction level is much more efficient than development at RTL. Secondly, functional verification can be done at high-level, which is usually hundreds of times faster than verification at RTL in terms of runtime. However, the expensive verification efforts of generated RTL can be saved only if we guarantee that behavioral synthesis tool generates correct RTL from the ESL specification. Therefore despite that there are several commercial behavioral synthesis tools available, the adoption of behavioral synthesis critically depends on our ability to ensure that the synthesized designs indeed correctly implement the ESL specifications. The goal of this research is to provide a formal equivalence checking support for behavioral synthesis, with the emphasis on scalability and end-to-end checking ability.

## 1.2 PROBLEM STATEMENT

Real industrial designs are typically thousands or even tens of thousands of lines of C/C++ code. The performance (runtime and memory usage) of the equivalence checker should scale to large industrial designs. To provide a scalable end-to-end formal equivalence checking support for behavioral synthesis, we need to decompose the verification flow into phases that are defined in the behavioral synthesis flow, and address the following challenges for different phases.

- How to check front-end compiler transformations? Front-end transformations constitute the majority of synthesis transformations. It is typical that more than a hundred transformations are applied to a design. Furthermore, they are applied aggressively under delicate and implicit invariants, and tend to be complex and error-prone.

- How to validate scheduling transformation? Scheduling transformation is usually a very aggressive, complicated, thus error-prone transformation to meet the timing and resource constraints. It entails sophisticated heuristics to minimize register usage, improve timing and possibilities for sharing. The scheduling transformation not only needs to preserve control and data dependencies of the original design, but also needs to accommodate user specified timing constraints: either compiler directives or wait statements explicitly specified in the design. In this dissertation, we don't consider pipelining in the scheduling transformation.

- How to make the back-end checking framework scale to industrial-strength designs? Previous work [36, 64] proposed a dual-rail symbolic simulation framework to check the equivalence between the design after scheduling transformation and the synthesized RTL. However, the framework is inadequate to handle design and implementation optimizations, therefore it is not scalable to real industrial-strength designs. In order to improve the scalability of the framework, we need a robust approach to handling the design and implementations.

- How to detect deadlocks introduced by parallelization of RTL blocks that are connected by synthesized interfaces with handshaking protocols? Behavioral synthesis tools allow designers to synthesize concurrent RTL blocks from a sequential high-level specification, and to synthesize interfaces between blocks into pre-defined interface components with handshaking protocols. Allowing blocks to run concurrently may introduce deadlocks. Therefore, we need scalable approach to detecting deadlocks in the synthesized RTL implementations.

# 1.3 PROPOSED EQUIVALENCE CHECKING FRAMEWORK

Because of the huge semantic gap between the ESL specification and the generated RTL implementation, and the fact that a large number of transformations will be applied to the ESL design, it is extremely hard to check equivalence of the ESL design and the RTL implementation directly. This research focuses on the ability of checking the entire behavioral synthesis flow and the scalability to industrialstrength designs. Instead of checking the ESL and RTL directly, we employ an incremental checking approach, taking advantage of the similarity of the design representations before and after each transformation. We establish intermediate equivalence points in the checking flow by decomposing the checking into a sequence of checks, one for each transformation applied by the behavioral synthesis tool. This incremental approach is essential to the scalability of our framework.

Figure 1.2: Behavioral synthesis and verification flow

As discussed in Section 1.1, a behavioral synthesis tool mainly has three phases: front-end, scheduling and back-end. To build a scalable end-to-end formal equivalence checking framework, we also partition our verification flow shown in Fig. 1.2 into the following three parts.

1. Front-end transformation checker checks the equivalence of the input and output programs of each transformation applied. We use symbolic execution techniques to explore paths of the input and output programs of each transformation. We then check that under the same path condition, whether they have the same observable behavior. Our incremental approach checks the front-end transformations by decomposing them into a sequence of checks, one for each transformation applied. We identify two major sources to path explosion problem in symbolic execution: *subroutine calls* and *loops*. We propose a compositional checking approach to checking a design that consists of a number of functions on a function-by-function basis, which greatly reduces the checking complexity. We use *cut-loop* optimization to handle path explosions introduced by loops.

- 2. Scheduling checker validates that 1) every operation in the design must be scheduled to be executed, 2) control and data dependencies of the design are preserved after scheduling, and 3) user specified timing constraints are satisfied. We identify the properties need to be checked for different I/O scheduling modes. and propose different algorithms to check the properties.

- 3. Back-end checker checks the equivalence of the scheduled design and the generated RTL. We symbolically simulate them cycle by cycle, and compare the mapped variables (including inputs and outputs) at the end of each cycle. Design and implementation optimizations employed either by the designers or by the behavioral synthesis tool complicate the equivalence checking problem. In particular, interface synthesis of global variables of a design and operation gating are hurdles to the scalability of our checker. We use a compositional equivalence checking approach together with automatic inference of the extended signature of each module to handle global variables. We propose a relaxed equivalence checking algorithm to tolerate local and irrelevant in-equivalences introduced by operation gating. These two optimizations are essential to make our checker scale to industrial-strength applications.

In addition to the three-phase equivalence checking framework, our deadlock detection approach takes the design representation after scheduling transformation and the result of interface synthesis, automatically generates assertions to capture deadlock conditions. The generated assertions can be used in assertion-based verification (simulation or formal verification tools) to detect deadlocks.

# 1.4 DISSERTATION OUTLINE

The rest of this dissertation is organized as follows: Chapter 2 provides background on *behavioral synthesis*, *symbolic simulation* and *equivalence checking* techniques employed in hardware verification. In Chapter 3, we present our equivalence checking framework for front-end compiler transformations in behavioral synthesis. We also present several optimizations to handle the path explosion problem. In Chapter 4, we present our validation approach to scheduling transformation, including validation of control and data dependencies and I/O interface timing under different scheduling modes. In Chapter 5, we present several optimizations to make our back-end equivalence checker scale to industrial applications. We present an assertion based verification approach to detecting deadlocks introduced by parallelization of RTL blocks that are connected by synthesized interfaces with handshaking protocols in Chapter 6. We conclude this dissertation research and discuss some future research directions in Chapter 7.

#### Chapter 2

### BACKGROUND

#### 2.1 BEHAVIORAL SYNTHESIS

Behavioral synthesis [26] provides a promising approach to dealing with the evergrowing complexity in modern hardware design by generating high-quality RTL implementations from high-level specifications. An early effort was made by researchers at Carnegie Mellon University [51,58] in the 1970s, which used *instruction set processor specification* as input language. There are open-source behavioral synthesis tools from academia, *e.g.*, SPARK [33], LegUp [17], and Bambu [1]. Commercially available tools from major EDA (Electronic Design Automation) vendors include Cadence's C-to-Silicon Compiler [3], and Cynthesizer [5], Calypto's Catapult HLS [4], NEC's Cyber Workbench [71], Synopsys's Synphony C Compiler [67], and Xilinx's Vivado high-level synthesis [73]. Beside the above C based behavioral synthesis tool, there are also tools use domain-specific input languages, *e.g.*, HDL Coder [52] from MathWorks generates portable, RTL code from MATLAB functions or Simulink models. Bluespec [57] uses Bluespec SystemVerilog as input language.

A behavioral synthesis tool takes an ESL behavioral description of a design (in SystemC or C/C++), together with a library of hardware resources, and generates an RTL implementation [20]. Similar to a compiler, a behavioral synthesis tool first performs lexical, syntax and semantic analysis, and builds an intermediate representation (IR) of the ESL description. A series of transformations is then applied to the IR, which can be categorized into three phases.

- *Compiler transformations* form the first phase. This includes transformations such as dead code elimination, constant propagation, loop unrolling, *etc.*

- Scheduling transformations entail computing for each operation the clock cycle for its execution. The clock cycle must account for constraints in hardware resources as well as control and data flow. These transformations include pipelining loops, grouping independent operations for concurrent execution, etc.

- *Resource binding and control synthesis* map each operation to a hardware functional unit, allocates registers for variables used across clock cycles, and generates a finite state machine to implement the schedule.

After these transformations, the design can be represented in RTL. The RTL may be subjected to further manual tweaks.

# 2.2 SYMBOLIC SIMULATION

Symbolic execution [43] is a technique that executes a program with symbolic inputs instead of concrete ones. A symbolic program state includes a statement counter, values of variables and a path condition. Since the inputs are symbolic, the values of variables are expressions over symbolic inputs, and the path condition is a Boolean expression over symbolic inputs. During the execution, a symbolic execution tree is built, with each node representing a program state and each edge representing a state transition condition.

Fig. 2.1 illustrates an example of symbolic execution of a simple program. Fig. 2.1(a) shows a function foo written in C, and Fig. 2.1(b) shows its symbolic execution tree. For simplicity, we only show the values of variables (in the box) and path conditions (on the edge). At the beginning of the execution, variable  $\mathbf{x}$  and  $\mathbf{*f}$  take symbolic value  $\mathbf{X}$  and  $\mathbf{F}$ , respectively. Function foo has two paths:

Figure 2.1: A simple function foo in C with its symbolic execution tree. (a) Function foo in C. (b) Symbolic execution tree of foo, where F and X are symbolic values for \*f and x, r denotes the return value, and nil denotes that the value is not yet available.

one path increments f, and returns 0 with path condition X > 1; the other path decrements f, and returns 1 with path condition  $X \le 1$ .

# 2.3 FORMAL EQUIVALENCE CHECKING

Formal equivalence checking techniques play an important role in EDA. After synthesize an RTL design to a gate-level implementation, logic equivalence checking tools are used to to prove that the gate-level implementation is functionally equivalent to the RTL design. With decades of research and development, logic equivalence checking has become a mature field. Binary decision diagrams (BDDs) [14] provide canonical representations for Boolean functions, early verification efforts [50] use BDDs for formal logic verification. The idea is to convert two Boolean functions into two BDDs, two functions are equivalent if they have the same BDD representation. Boolean satisfiability problem (SAT) is to check whether a given propositional formula is satisfiable. There have been research on using SAT for equivalence checking [32]. The basic idea is to convert the equivalence of two circuits problem into satisfiability of a propositional formula, and leverage the state-of-the-art SAT solver to solver the formula.

Our research leverages the success of logic equivalence checking. We borrow the idea of logic equivalence checking of RTL designs and their gate-level implementations to check the equivalence of the high-level (C/C++) designs and the generated RTL implementations in behavioral synthesis.

#### Chapter 3

# FRONT-END COMPILER TRANSFORMATION CHECKING

Behavioral synthesis tools apply a sequence of transformations to the input design before scheduling. We check front-end by decomposing it into a sequence of checks, one for each transformation applied. The key observation is that even if the transformation implementations may be closed-source, it is still possible to obtain from most tools the IRs after application of each front-end transformation. Thus, an sequential equivalence checking (SEC) methodology was developed to compare each pair of consecutive IRs.

# 3.1 NOTATIONS AND DEFINITIONS

Let P be a program, V be the set of variables of P, and  $V_{\mathcal{O}} \subseteq V$  be the set of *observable variables*. Intuitively, variables that we can observe during the execution of P are called observable variables; we assume that the  $V_{\mathcal{O}}$  includes the input, output, and global variables.

**Definition 3.1** (State). A state  $s \triangleq \{\langle v, u \rangle \mid v \in V, u \text{ is the value of } v\}$  of a program P is the set of variables in P with their values.

**Definition 3.2** (Observable State). An observable state  $s_{\mathcal{O}}$  at state s of a program P, denoted by  $s_{\mathcal{O}}(s)$ , is a projection of s, where variables in  $s_{\mathcal{O}}$  are restricted to observable variables in program P.

**Remark 3.1.** We leave the domains for the values of variables undefined for this presentation, but assume that they can be determined from the context. Also, we

assume that the domain can be both concrete or symbolic; this permits us to use the same notation for both concrete and symbolic states. For simplicity, we use s[v] to denote the value, either concrete or symbolic, of variable v in state s.

**Definition 3.3** (Path). A path  $\pi \triangleq s_0, c_1, s_1, c_2, s_2, \ldots, c_n, s_n$  of a program is an alternating sequence of states and state transition conditions, starting from an *initial state*  $s_0$  and ending with a *terminal state*  $s_n$ , where  $c_i$  is the state transition condition (Boolean expression over program variables) from  $s_{i-1}$  to  $s_i$  for all  $1 \leq i \leq n$ .

**Definition 3.4** (Path Condition). Let  $\pi \triangleq s_0, c_1, s_1, c_2, s_2, \ldots, s_{n-1}, c_n, s_n$  be a path of a program *P*. The path condition  $pc \triangleq \bigwedge_{i=1}^n c_i$  of path  $\pi$  is a conjunction of all transition conditions on  $\pi$ . We use  $\pi[pc]$  to denote the path condition of  $\pi$ .

**Definition 3.5** (Path Compatibility). Given two programs S and T with the same set of observable variables  $V_{\mathcal{O}}$ , let  $\pi$  be a path of S with initial state  $s_0$  and path condition pc, and  $\pi'$  be a path with initial state  $s'_0$  and path condition pc' of T. We say  $\pi$  and  $\pi'$  are compatible if  $s_{\mathcal{O}}(s_0) = s_{\mathcal{O}}(s'_0)$  and  $pc \wedge pc'$  is satisfiable. Paths  $\pi$  and  $\pi'$  are called a *compatible path pair* of S and T.

**Definition 3.6** (Path Equivalence). Let  $\pi$  be a path of program S with terminal state  $s_n$ , and  $\pi'$  be a path of program T with terminal state  $s'_m$ , and suppose that programs S and T have the same set of observable variables  $V_{\mathcal{O}}$ . We say path  $\pi$  and  $\pi'$  are *equivalent*, denoted by  $\pi \sim \pi'$ , if  $\pi$  and  $\pi'$  are compatible, and for each variable  $v \in V_{\mathcal{O}}$ ,  $s_n[v] = s'_m[v]$ .

Informally, two paths are equivalent if they are compatible, and they have the same observable state at their terminal states.

**Definition 3.7** (Program Equivalence). Let S and T be two programs, we say that program S and T are *equivalent*, denoted by  $S \sim T$ , if every compatible path pair of S and T has the same observable state at their terminal states. Formally let

Figure 3.1: Framework of checking equivalence between program S and T, which are the input and output of transformation  $\mathcal{T}$  respectively.

Paths(S) and Paths(T) be all paths of program S and T respectively, program Sand T are equivalent if for each path  $\pi \in Paths(S)$  and every path  $\pi' \in Paths(T)$ that is compatible with  $\pi$ ,  $\pi$  is equivalent to  $\pi'$ .

We define the correctness of a transformation by the equivalence of the observable behavior of the source program S and the target program T. Informally Sand T are equivalent if fed the same inputs to both programs, they produce the same output, and have the same effect on the environment (modification to global variables) when terminating.

**Definition 3.8** (Transformation Correctness). Let  $\mathcal{T}$  be a transformation which takes a source program S as input and produces a target program T as the output. We say  $\mathcal{T}$  is a *correct* transformation on program S if  $S \sim T$ .

# 3.2 EQUIVALENCE CHECKING FRAMEWORK

As shown in Fig. 3.1, suppose a transformation  $\mathcal{T}$  takes a program S as input and generates a program T as output. We validate the correctness of transformation  $\mathcal{T}$  when applied to S by checking whether T is equivalent to S. According to Definition 3.7, we need to prove that S and T have the same observable state at their terminal states for all compatible path pairs.

As a pedagogical simplification, assume that all the paths in S and T are enumerable. Also assume that S and T have the same function signature and global variables; this assumption does not limit our approach because compiler transformations usually do not change function signature unless there are parameters that are irrelevant or unused in the function body, which can be easily detected. Finally, assume that for each observable variable of S we can find the corresponding variable for T and vice versa. We then proceed as follows. We assign the same symbols to the input and non-constant global variables of S and T, then symbolically execute them. After enumerating all paths of S and T, for each compatible path pair  $\pi$  in S and  $\pi'$  in T, we check whether  $\pi$  and  $\pi'$  have the same observable behavior; this check is done by an SMT (satisfiability modulo theories) solver by checking the equality between the symbolic expressions of the (symbolic) values of the observable variables.

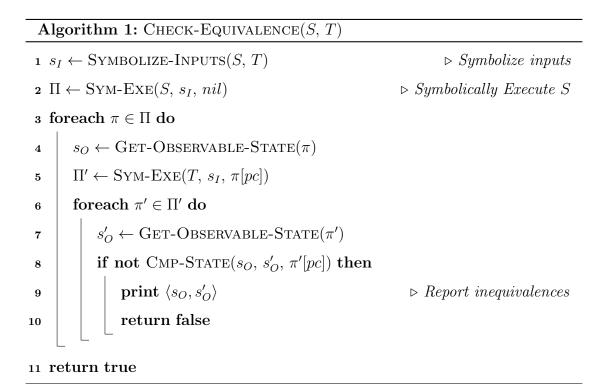

Algorithm 1 provides a high-level description of our approach. Function <u>CHECK-EQUIVALENCE</u> takes two programs S and T as arguments. Subroutine <u>SYMBOL-IZE-INPUTS</u> creates symbols for inputs of S and T. Subroutine <u>SYM-EXE</u> symbolically executes S with symbolic inputs, and collects all paths of S. For each path  $\pi$  with path condition  $\pi[pc]$  of S, subroutine <u>GET-OBSERVABLE-STATE</u> collects the observable state  $s_O$  corresponding to the terminal state in path  $\pi$ . Subroutine <u>SYM-EXE</u> symbolically executes T with the same symbolic inputs under condition  $\pi[pc]$ , and collects all paths of T. Since all paths found in T are under the condition

$\pi[pc]$ , therefore they are all compatible path with  $\pi$ . For each path  $\pi'$  of T found under the condition of  $\pi[pc]$ , subroutine <u>CMP-STATE</u> checks if  $\pi$  and  $\pi'$  have the same observable state at termination. If the observable states are not equal, the algorithm reports the inequivalences, otherwise it proceeds until all paths of S and T are checked.

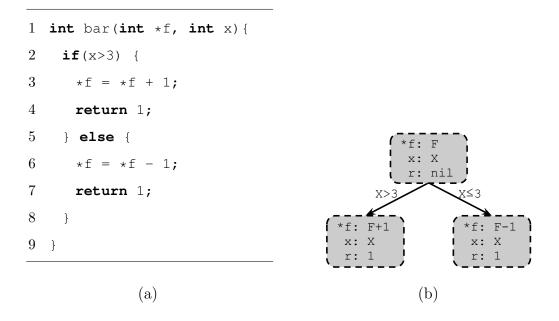

Fig. 2.1 and Fig.3.2 show two programs foo and bar which are defined in C and their independent symbolic execution trees. Before execution, foo and bar have the same symbolic input {  $\langle *f, F \rangle$ ,  $\langle x, X \rangle$  }, where F and X are symbolic values of variables \*f and x, respectively. Function foo has two paths, the final observable states are {  $\langle *f, F + 1 \rangle$ ,  $\langle x, X \rangle$ ,  $\langle r, 0 \rangle$  } and {  $\langle *f, F - 1 \rangle$ ,  $\langle x, X \rangle$ ,  $\langle r, 1 \rangle$  }, with conditions X > 1 and X  $\leq$  1, respectively. Similarly, the two final observable states of function bar are {  $\langle *f, F + 1 \rangle$ ,  $\langle x, X \rangle$ ,  $\langle r, 1 \rangle$  } and {  $\langle *f, F - 1 \rangle$ ,  $\langle x, X \rangle$ ,  $\langle r, 1 \rangle$  }, with conditions X > 3 and X  $\leq$  3, respectively.

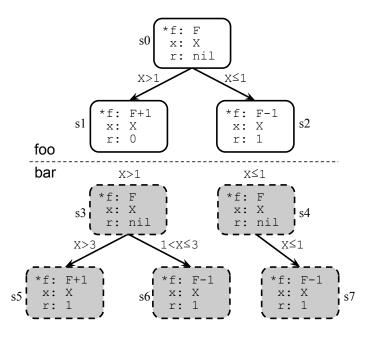

Fig. 3.3 shows the symbolic execution tree when function bar is executed under

Figure 3.2: A simple function **bar** in C with its symbolic execution tree. (a) Function **bar** in C. (b) Symbolic execution tree of **bar**, where **F** and **X** are symbolic values for **\*f** and **x**, **r** denotes the return value, and **nil** denotes that the value is not yet available.

the path condition of function foo. In Fig. 3.3, state s0 is the initial state of function foo, states s3 and s4 are the initial states of function bar, states s1 and s2 are terminal states of foo, and states s5, s6 and s7 are terminal states of bar. We need to conduct three equivalence checks:

- s1 vs. s5, where the return values are not equivalent;

- s1 vs. s6, where the values of \*f are not equivalent, and return values are also not equivalent;

- s2 vs. s7, the states are equivalent.

Therefore, our checking algorithm returns that **foo** and **bar** are not equivalent, and reports the inequivalences.

Figure 3.3: Symbolic execution tree of function foo and bar, where bar is executed after foo, and based on the execution condition of foo.

In summary, the above approach symbolically execute the two IRs (referred to as S and T) and check that each pair of corresponding program paths is equivalent. A program path is uniquely specified by the sequence of branch conditions that must hold for the control flow to execute the instructions in the path. The approach was used on some cryptographic applications. Unfortunately, it does not scale to other practical programs. In particular, it requires effective enumeration of all paths in S and T; in practice, this can lead to *path explosion*. Two key sources of path explosion in practice are subroutine calls and loops. In the next two sections we discuss optimizations to address these problems.

# 3.3 MODULAR REASONING ACROSS FUNCTIONS

Why do subroutine calls contribute to path explosion? The naïve approach of symbolically executing the program treats each function as if it were inlined: the function body is symbolically executed at each call site. When a function f having a number of branches in its body (and hence program paths) is invoked many times, each invocation contributes a multiplicative factor to the number of paths explored.

Our approach to address this problem is to develop a compositional approach to symbolic execution [31], which permits equivalence checking on a per-function basis. Suppose functions f and f' invoke functions g and g' respectively. Then (1) we separately check the equivalence of g and g'; and (2) when checking the equivalence of f and f', we replace g and g' with the same uninterpreted function symbols.

Of course the above naïve scheme only works for *side effect* free functions. If g and g' update some global variables or pass-by-reference arguments, then replacing g and g' with the same uninterpreted function on the explicit arguments will be unsound since the effect on the global variable or pass-by-reference arguments is not accounted for. To address this, we use a notion of "extended signature". The idea is to extend the type signature of a function explicitly accounting for the side effects. Let g be a sub-function; we use  $\tau = g(\vec{\alpha_v}, \vec{\alpha_r})$  to represent the signature of g, where  $\tau$  denotes the return value,  $\vec{\alpha_v}$  denotes pass-by-value arguments, and  $\vec{\alpha_r}$  denotes pass-by-reference arguments. Then, in addition to the function arguments, suppose function g reads globals  $\vec{\beta_r}$  and updates globals  $\vec{\beta_w}$ . The extended type signature of g is:

$$\langle \tau, \vec{\alpha'_r}, \vec{\beta'_w} \rangle = g(\vec{\alpha_v}, \vec{\alpha_r}, \vec{\beta_r}),$$

where  $\vec{\alpha'_r}$  and  $\vec{\beta'_w}$  are updated versions of  $\vec{\alpha_r}$  and  $\vec{\beta_w}$  respectively, mimicking the notion that they may be arbitrarily changed by function g.<sup>1</sup>

Fig. 3.4 shows an example of a sub-function with side effects. Function f invokes

<sup>&</sup>lt;sup>1</sup>Pass-by-reference arguments are pointers, and most behavioral synthesis tools restrict the usage of pointers to compile-time determinable ones, which makes this approach works in finding which variable a pointer points to.

```

1 char A;

// global variable

2

int B;

// global variable

int C[2];

// global variable

3

void f(int d[4]) {

4

5

int i = 8;

6

g(i, d);

7

}

void g(int x, int y[4]) {

8

9

B = A + x;

// side effect on global B

10

C[1] = C[0] + x;

// side effect on global C

11

y[1] = y[0] + x;

// side effect on arguments

12 \}

```

Figure 3.4: Global variable usage with sub-function call example.

function g which updates the globals B and C, and pass-by-reference argument y.

Extended signatures are exploited to replace function calls with uninterpreted functions symbols. Suppose that function g has been certified; when certifying function f, we replace g with an *uninterpreted function* (say  $\mathcal{G}$ ) of four arguments, and the effect of the invocation of g on the globals (B and C) and argument y is given by:

$$\langle d, B, C \rangle = \mathcal{G}(i, d, A, C).$$

Since each invocation of sub-functions is replaced by an uninterpreted function symbol, we alleviate path-explosion problem introduced by subroutine calls. It is worth noting that this can generate false alarms, and we need to take special care to handle common false negatives. We discuss this issue when describing our experiments.

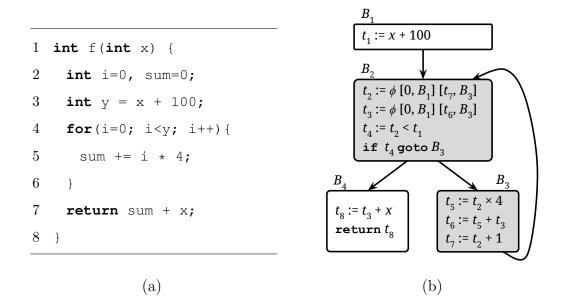

Figure 3.5: A simple function with a loop in C and its IR. (a) Function f has an unbounded for loop. (b) The IR of f, with boxes representing basic blocks, and arrows representing control flow. Control flow merge is implemented via  $\phi$ instructions in basic block  $B_2$ .

# 3.4 HANDLING LOOPS

Loops are the second major contributors to path explosion (and, in case of unbounded ones, non-termination) in symbolic simulation of software programs. The reason is that symbolic simulation of a loop induces (at least) two branches for each loop iteration simulated: (1) the branch where the loop test holds (and hence the body is executed) and (2) the branch where the test is false.<sup>2</sup>

We handle equivalence of loops by an approach called *cut-loop optimization*. Our approach borrows ideas from a corresponding one for back-end SEC between high-level IR and RTL [36], and is an adaptation of classic inductive assertions

<sup>&</sup>lt;sup>2</sup>The branching may be limited if the value of the loop test can be computed concretely during symbolic execution of the loop. However, this is not possible for most non-trivial loops in practice.

approach [29, 38] to program equivalences. The idea is to "cut" the loop, which reduces equivalence of loop execution to equivalence checks at entry, body, and exit. To illustrate the idea, consider the example in Fig. 3.5. Fig. 3.5 (a) shows a simple unbounded loop in C. Fig. 3.5 (b) shows the IR of function  $\mathbf{f}$ .<sup>3</sup> If the input  $\mathbf{x}$  is symbolic, then the symbolic expansion of the loop (and hence the symbolic execution of  $\mathbf{f}$ ) will not terminate.<sup>4</sup> We assume loops are in *natural loop* form in the IRs. A *natural loop* must have a single entry point (header) and at least one *back edge* leading the control flow from the loop body back to the loop header. Fig. 3.5 (b) is an example of a natural loop, where  $B_2$  is the loop header, and edge  $(B_3, B_2)$  is the back edge.

Back-end SEC [36] exploits mappings of variables provided by behavioral synthesis tool. For simplicity, suppose each basic block is a scheduling step in Fig. 3.5 (b). At the end of execution of each scheduling step, we check the equivalence of all mapped variables. If they are equivalent, we replace every pair of mapped variables with the same symbolic symbol (with *cut-point* optimization). Suppose the loop is entered from  $B_1$ , after executing of  $B_3$ , variables  $t_5$ ,  $t_6$  and  $t_7$  are checked equivalence with their mapped variables in RTL, and then will be replaced with symbolic variables. Till this point, we checked the first iteration of the loop. The subsequent iterations of the loop are all led by the back edge. Since we made  $t_5$ ,  $t_6$  and  $t_7$  symbolic, executing the subsequent iterations once will cover all possible cases. All we need to do is to avoid multiple entrance of a loop through the same back edge.

<sup>&</sup>lt;sup>3</sup>Control flow merge is implemented via  $\phi$ -instructions in basic block  $B_2$ . A  $\phi$ -instruction  $\mathbf{v} = \phi [\alpha, B_i] [\beta, B_j]$  in basic block B means that  $\mathbf{v}$  has the value  $\alpha$  if B is reached from  $B_i$ , and  $\beta$  if reached from  $B_j$ .

<sup>&</sup>lt;sup>4</sup>Technically, symbolic simulation can terminate when a fixpoint is reached, *i.e.*, when all reachable states have been explored. But achieving such fixpoint requires the restriction that all the variable types are finite, as well as an expensive fixpoint computation through symbolic simulation.

However, variables mappings between two IRs are not available during frontend transformations. Suppose a loop consists of a list of basic blocks; then we must identify a minimum set of variables that need to be mapped between the two IRs. In particular, we need to identify mappings for loop-carried variables. The reason is that we want to make them symbolic, so that we only need to execute the loop once through each back edge (see below).

We achieve the above through *use-definition chains* analysis [10]. In the example shown in Fig. 3.5 (b), loop L consists of basic blocks  $B_2$  and  $B_3$ , variable  $t_6$  and  $t_7$  are loop-carried variables. For example, execution of loop L is done as follows:

- 1. Loop L is entered from  $B_1$ :

- path 1:  $B_1 \to B_2 \to B_4$ : we check the equivalence of return variable  $t_8$ ;

- path 2:  $B_1 \rightarrow B_2 \rightarrow B_3$ : we check the equivalence of loop-carried variables  $t_6$  and  $t_7$ , and make them symbolic afterwards.

- 2. Loop L is entered from  $B_3$  through the back edge:

- path 1:  $B_3 \to B_2 \to B_4$ : we check the equivalence of return variable  $t_8$ ;

- path 2:  $B_3 \to B_2 \to B_3$ : we check the equivalence of loop-carried variables  $t_6$  and  $t_7$ , and terminate L.

The above approach requires detecting the loop structure (*e.g.*, loop header, exit, back edge, etc.) in the IRs. Once the loop-carried variables are identified, equivalence of loop computation can be verified by checking the first iteration (entered from entry) and one subsequent symbolic iteration (entered through back edge) for each back edge; since we made loop-carried variables symbolic after first iteration, this covers all possible cases for the subsequent iterations. The sufficiency of these checks was mechanically proven in previous work using the ACL2 theorem prover [63]. Finally, cut-loop requires that when the corresponding loops in the two IRs being compared have the same structure, and perform equivalent computation at each iteration, *e.g.*, it is inapplicable if the transformation entails partial loop unrolling. However, as our experiments indicate, most behavioral synthesis transformations are structure-preserving, making the optimization widely applicable.

# 3.5 EXPERIMENTAL RESULTS

Table 3.1: Summary of CHStone Benchmark for Equivalence Checking of Front

end Compiler Transformations

| App. Domain      | Design   | Lines of C Code | Lines of RTL | # of Functions |

|------------------|----------|-----------------|--------------|----------------|

| Arithmetic       | DFADD    | 542             | 12933        | 17             |

|                  | DFDIV    | 452             | 10948        | 19             |

|                  | DFMUL    | 392             | 7100         | 16             |

|                  | DFSIN    | 772             | 22949        | 31             |

| Microprocessor   | MIPS     | 256             | 7237         | 1              |

| Media Processing | ADPCM    | 521             | 33706        | 15             |

|                  | GSM      | 388             | 22816        | 12             |

|                  | JPEG     | 1031            | 53584        | 30             |

|                  | MOTION   | 414             | 13770        | 13             |

| Security         | AES      | 699             | 40014        | 11             |

|                  | BLOWFISH | 1241            | 23490        | 6              |

|                  | SHA      | 1284            | 12491        | 8              |

We applied our framework to CHStone [37], a publicly available behavioral synthesis benchmark suite containing 12 ESL designs (in C). We used LegUp [17] to synthesize these designs. We conducted our experiments on a workstation with Debian 7.1 running on a 2.93 GHz Intel Xeon X3470 processor with 8 GB of

| Design   | # of Checked    | # of Successful | Success     | Avg.     | Memory |

|----------|-----------------|-----------------|-------------|----------|--------|

|          | Transformations | Checks          | Rate $(\%)$ | Time (s) | (MB)   |

| DFADD    | 62              | 62              | 100.00      | 0.78     | 159.86 |

| DFDIV    | 62              | 78              | 79.49       | 0.95     | 161.22 |

| DFMUL    | 47              | 48              | 97.92       | 0.93     | 155.93 |

| DFSIN    | 113             | 115             | 98.26       | 0.88     | 187.70 |

| MIPS     | 10              | 13              | 76.92       | 2.32     | 15.01  |

| ADPCM    | 69              | 101             | 68.32       | 3.33     | 123.85 |

| GSM      | 53              | 86              | 61.63       | 0.26     | 122.94 |

| JPEG     | 158             | 237             | 66.67       | 1.55     | 694.76 |

| MOTION   | 59              | 74              | 79.73       | 0.49     | 52.50  |

| AES      | 67              | 85              | 78.82       | 4.22     | 120.56 |

| BLOWFISH | 27              | 48              | 56.25       | 3.28     | 93.58  |

| SHA      | 36              | 61              | 59.02       | 0.05     | 106.14 |

Table 3.2: Summary of Evaluation on CHStone Benchmark for Equivalence Checking of Front-end Compiler Transformations

memory. We focused on intra-procedural transformations. The experiments were run with a cutoff time of 90 seconds: certifications taking longer than this time are classified as failures. The reason for this cutoff is that in our experience, most successful transformation certifications that complete in any reasonable time finish within a few seconds of this size; if symbolic execution takes more than 90 seconds, it is unlikely to finish. Thus we believe that the impact of making the cutoff longer on the number of successful transformations will be insignificant. Our tool supports a number of SMT solvers. The results on this benchmark use Z3 [24] since it outperforms others.

Table 3.1 and 3.2 show the statistics of the experiments, e.g., the number

Figure 3.6: Comparison of success rate on designs of CHStone benchmark without and with cut-loop optimization. The x axis is ordered by the success rate with cut-loop.

of transformations applied by the synthesis tool,<sup>5</sup> the number of transformations checked successfully, as well as time and memory usages. In all successful cases, time and memory usages are modest. With compositional execution and cut-loop optimization, we successfully validated 75.69 percent of transformations (763 out of 1008).

Fig. 3.6 compares the success without and with cut-loop optimization. Without cut-loop, we can validate only 52.88 percent of transformations (533 out of 1008). Cut-loop optimization provides an improvement of 22 percent. The improvement is most significant for AES, JPEG, GSM, and BLOWFISH since they have more loops. The transformations that fail certification (about 25 percent) typically do so for

<sup>&</sup>lt;sup>5</sup>Some transformations are applied more than once.

two reasons: (1) the transformation changes loop structure thus makes cut-loop inapplicable; or (2) symbolic expressions of corresponding variables in source and target programs become too complex, causing blow-up of the SMT solver.

Since we focus on intra-procedural transformations, we check the designs compositionally; this may sometimes introduce subtle false alarms. False alarms can arise in surprising ways, *e.g.*, the extended signature of a sub-function is different in the source and target programs. As an example <sup>6</sup>, suppose that a function foo has a sub-function legup\_memcpy that is invoked as follows.

```

r = legup_memcpy(a, b, c)

```

This sub-function has a return value, but the value is never used subsequently. Similarly, suppose that a function **bar** invokes the same sub-function **legup\_memcpy** as follows:

```

legup_memcpy(a, b, c)

```

This invocation treats  $legup_memcpy$  as if it returns void. The problem is when we compositionally check foo and bar, we abstract sub-function  $legup_memcpy$  with uninterpreted function. Since the extended signatures are different for two invocations of the sub-function, (one with a return value and the other one without), a naïve approach will report an inequivalence due to type mismatch. Since the result of return value **r** in foo is not used, this inequivalence is a false alarm. However, it can be easily eliminated, by excluding from the extended signature the types of return values that are not subsequently used.

#### 3.6 RELATED WORK

Formal verification of compilers: There has been research on formally proving compiler transformations correct by theorem prover. CompCert [49] is the

<sup>&</sup>lt;sup>6</sup>This is a real example in function Fill\_Buffer in MOTION design. The transformation is called "Combine Redundant Instructions"

first formally verified compiler. Similar to CompCert, Vellvm [76] project formalizes LLVM's intermediate representation, and develops a framework for reasoning about programs. Ray *et al.* proposed an certification framework for transformations in behavioral synthesis [64]. This framework uses theorem proving to certify high-level transformations. However, using theorem proving to prove all transformations requires enormous manual effort; it also requires knowledge about internal algorithms of each transformation, which is often not available because most behavioral synthesis tools are closed source.

Translation validation: Pnueli et al. proposed the notion of translation validation [59] for validating the transformations during compilation. Instead of verifying a transformation once and for all, they showed how to generate a proof of correspondence between the source and target programs for each individual transformation. However, it is problematic for the approach to handle programs with more than one loop. Zuck *et al.* extended this approach to support structure-modifying transformations [77]. Necula used symbolic evaluation techniques from proof-carrying code to tackle translation validation [56]. However, this approach only handled transformations where source and target programs have the same branch conditions. Zaks and Pnueli proposed a framework to construct the cross product of the source and target programs [75]. This reduces the problem of checking the equivalence of two programs to verification of a single program. Peggy [69] performed translation validation for the LLVM compiler using equality saturation. It built Program Expression Graphs for the source and target programs of a transformation and then reasons about equalities among graph nodes. If output nodes of two programs are shown equal, the two programs are equivalent. To our knowledge, these approaches do not scale to programs of the size we consider in this research. Note that a key reason for the differences in scalability is that the aim of the above line of research is to check the correctness of generic compiler transformations while we focus on the transformations in behavioral synthesis. In particular, the programs being synthesized can be represented as finite state machines and many language features such as dynamic memory allocation are prohibited.

Symbolic execution based techniques: There has also been recent research on applying symbolic techniques to checking the equivalence of two arbitrary programs. UC-KLEE [62] proposes a smart stub function that invokes two routines that need to be verified for equivalence, and leverages KLEE [15] to symbolically execute the stub function. Upon finding a path, UC-KLEE checks if the two routines behave the same. UC-KLEE enumerates path with best efforts; thus it suffers from path explosion and does not terminate when executing unbounded loops. SYM-DIFF [48] is a symbolic differentiation tool, which symbolically executes two programs with same symbolic inputs, and checks if the two programs have identical outputs. SYM-DIFF handles loops by unrolling them to a user-specified depth; consequently it cannot certify equivalence between programs whose loops iterations are long or controlled by input variables; we can handle such programs with cut-loop optimization.

# 3.7 SUMMARY

In this Chapter, we have presented a scalable SEC framework to validate the correctness of front-end compiler transformations in behavioral synthesis. We use symbolic execution technique to explore (possibly all) paths of the source and target programs of each transformation. We showed how to ameliorate path explosion and non-termination in symbolic simulation through compositionality and cut-loop optimization. Our framework can fully automatically certify results of more than 75 percent of 1008 transformations employed by a synthesis tool on designs from the CHStone benchmark. We are not aware of any SEC framework that can handle compiler transformations at such diversity and scale.

Our results underline the importance of aligning verification methodology with

the design flow in the development of a scalable verification framework. SEC for behavioral synthesis transformations at the scale achieved here has not been done before because extant tools focused on input/output equivalence between the highlevel ESL description and synthesized RTL; such efforts are ineffective because of the high abstraction gap. On the other hand, pre-certified compiler transformation via theorem proving as proposed in previous work [64] was not successful both because of the number and complexity of such transformations and the reluctance of synthesis tool vendors to expose transformation implementation for formal analysis. Our key insights are that (1) design IRs before and after each transformation application can be made available from a commercial synthesis flow even if the transformations themselves are proprietary, and (2) restrictions in program features enforced by behavioral synthesis from the need to eventually generate hardware circuit from the design description make it possible to use "black-box" SEC techniques effectively to certify these IRs. The key take-away from our paper is that once the right verification methodology has been identified, it is possible with insight of the source of verification complexity of the domain to adapt wellknown analysis ingredients into an end-to-end certification solution in a complex domain.

One possible argument against our framework is the requirement that IRs after each transformation application be available to the tool. In particular, if the validation is performed by a third party, this requirement may provide exposure to confidential design intellectual property (IP). In practice, we have not seen that to be a problem for two reasons. First, in many industrial contexts, the validation is performed by personnel who have access to the original ESL and RTL designs anyhow (*e.g.*, by a validation group in the same organization that designed the ESL). Second, most extant commercial behavioral synthesis tools already provide the information on IRs; we do not require any additional information to perform our analysis. Nevertheless, the potential of IP leakage is an important one, and we plan to look at the constraints and data available to third-party evaluators during design certification in future work to determine how our framework can be made usable in that context.

#### Chapter 4

# VALIDATING SCHEDULING TRANSFORMATION

#### 4.1 SCHEDULING TRANSFORMATION

Scheduling is a critical synthesis phase that directly affect the quality of synthesized design in terms of timing, performance, and thermal characteristics [22]. Scheduling transformation involves complex heuristics to ensure that the design being synthesized can meet the timing and resource constraints while preserving control and data dependencies.

To understand the source of resource constraints consider scheduling the following operations:

S1: x = y \* z;S2: p = x + y;S3: w = a \* b;S4: q = a + z;

Assume that the design is not being pipelined, the system has a single multiplier that requires 3 cycles for completion, and two adders. Suppose the scheduling transformation schedules **S1** to start at clock cycle t. Then, since there is data dependency between **S1** and **S2**, the operation **S2** cannot be scheduled before t. Furthermore, since multiplier takes 3 clock cycles, **S2** cannot be scheduled to start before cycle t+3. Finally, since there is only one multiplier, **S3** cannot be scheduled to start before cycle t+3 either, although there is no data dependency between **S1**

```

1

void block::thread() {

\mathbf{2}

int accu = 0;

3

wait();

4

while(1) {

int a = In.read();

5

6

Out.write(a + accu);

7

wait();

8

int b = In.read();

9

Out.write(b * b);

10

accu = In.read();

11

wait();

12

}

}

13

```

Figure 4.1: An example of a SystemC thread, which has two superstates in the while loop.

and S3 (or S3 is scheduled at clock cycle t, then S1 can not be scheduled before cycle t + 3). On the other hand, since there are two adders, S2 and S4 can be scheduled concurrently.