#### Louisiana State University LSU Digital Commons

LSU Historical Dissertations and Theses

Graduate School

1999

#### Scaling Simulations of Reconfigurable Meshes.

Jose Alberto Fernandez zepeda Louisiana State University and Agricultural & Mechanical College

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_disstheses

#### **Recommended Citation**

Fernandez zepeda, Jose Alberto, "Scaling Simulations of Reconfigurable Meshes." (1999). LSU Historical Dissertations and Theses. 7081.

https://digitalcommons.lsu.edu/gradschool\_disstheses/7081

This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Historical Dissertations and Theses by an authorized administrator of LSU Digital Commons. For more information, please contact gradetd@lsu.edu.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# UMI®

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

.

## SCALING SIMULATIONS OF RECONFIGURABLE MESHES

A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

The Department of Electrical and Computer Engineering

by José Alberto Fernández Zepeda B.S., Universidad Nacional Autonóma de México, 1991 M.S., Universidad Nacional Autonóma de México, 1994 December 1999

-

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

UMI Number: 9960052

## UMI®

#### UMI Microform 9960052

Copyright 2000 by Bell & Howell Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

## Acknowledgments

I sincerely thank my advisors Dr. Jerry L. Trahan and Dr. Ramachandran Vaidyanathan for their supervision, guidance, patient, and for all the time that they dedicated to me during my studies at Louisiana State University.

I am grateful for the financial support provided by Consejo Nacional de Ciencia y Tecnología (CONACYT), the program Fulbright-IEE, the National Science Foundation, and the Department of Electrical and Computer Engineering at LSU.

I dedicate this dissertation to my mother Ana María Zepeda for her love and encouragement throughout my life.

Finally, I would like to thank all my friends for a memorable time at LSU, especially to Anu Bourgeois for her sincere friendship.

## **Table of Contents**

| A  | CKNO  | WLEDG  | GMENTS                            | . ii   |

|----|-------|--------|-----------------------------------|--------|

| Lı | ST O  | f Figu | IRES                              | . v    |

| A  | BSTR. | ACT .  |                                   | . viii |

| Cı | HAPT  | ER     |                                   |        |

| 1  | INT   | RODUC  | TION                              | . 1    |

| -  | 1.1   |        | figuration                        |        |

|    | 1.2   |        | g Simulations and Previous Work   | -      |

|    | 1.3   |        | of the Dissertation               |        |

|    | 1.4   | -      | ibutions of This Work             |        |

|    | 1.5   |        | nization of the Dissertation      | -      |

| 2  | Def   | INITIO | NS AND TERMINOLOGY                | . 17   |

| _  | 2.1   |        | R-Mesh                            |        |

|    | 2.2   |        | <b>FR-Mesh</b>                    |        |

|    | 2.3   |        | JR-Mesh                           |        |

|    | 2.4   |        | rrent Writes                      |        |

|    | 2.5   |        | action and Windows Mappings       |        |

| 3  | FR-   | MESH   | Scaling Simulation                | . 23   |

|    | 3.1   | Scalin | g Simulation Terminology          | . 24   |

|    | 3.2   |        | ing for FR-Mesh                   |        |

|    | 3.3   | Gener  | al Description of the Simulation  | . 27   |

|    | 3.4   |        | oonent Determination              |        |

|    |       | 3.4.1  | Horizontal Prefix Assimilation    | . 29   |

|    |       | 3.4.2  | Vertical Prefix Assimilation      | . 34   |

|    |       | 3.4.3  | Component Numbering               | . 36   |

|    |       | 3.4.4  | Second Vertical Component Sweep   |        |

|    |       | 3.4.5  | Second Horizontal Component Sweep |        |

|    | 3.5   | Data I | Delivery                          | . 40   |

|    |       | 3.5.1  | Window Homogenization             | . 41   |

|    |       | 3.5.2  | Second Vertical Data Sweep        |        |

|    |       | 3.5.3  | Slice Homogenization              | . 44   |

|    |       | 3.5.4  | Second Horizontal Data Sweep      | . 47   |

|    | 3.6  | Other Write Rules                                        |

|----|------|----------------------------------------------------------|

|    |      | 3.6.1 Simulation 1                                       |

|    |      | 3.6.2 Simulation 2 51                                    |

|    |      | 3.6.3 Simulation 3 54                                    |

|    |      | 3.6.4 Simulation 4                                       |

|    | 3.7  | Improved Scaling Simulation of the R-Mesh 57             |

|    |      | 3.7.1 Existing R-Mesh Scalability Simulation             |

|    |      | 3.7.2 The New Simulation                                 |

| 4  | Bus  | <b>5</b> LINEARIZATION                                   |

|    | 4.1  | Definitions                                              |

|    |      | 4.1.1 Graph of an R-Mesh 67                              |

|    |      | 4.1.2 Mapping R-Mesh Processors to LR-Mesh Processors 67 |

|    |      | 4.1.3 Leader Election                                    |

|    | 4.2  | Bus Linearization                                        |

|    |      | 4.2.1 Simulation of R-Mesh by LRN-Mesh                   |

|    |      | 4.2.2 Simulation Running Time                            |

|    |      | 4.2.3 Allowing Other Write Rules in $Q$                  |

|    |      | 4.2.4 Reducing the Size of $\mathcal{Z}$                 |

|    |      | 4.2.5 Exclusive Write for $\mathcal{Z}$                  |

|    | 4.3  | Scaling Simulations                                      |

|    |      | 4.3.1 R-Mesh Scaling Simulation                          |

|    |      | 4.3.2 FR-Mesh Scaling Simulation                         |

|    | 4.4  | Simulation of R-Mesh by PR-Mesh 87                       |

| 5  | SIM  | ULATION OF DR-MESH BY LR-MESH                            |

|    | 5.1  | The DR-Mesh                                              |

|    | 5.2  | DR-Mesh Simulation Terminology                           |

|    | 5.3  | DR-Mesh Simulation Description                           |

|    | 5.4  | Algorithm Going_Out                                      |

|    |      | 5.4.1 Procedure Find_A*                                  |

|    |      | 5.4.2 Procedure Find_Dout                                |

|    |      | 5.4.3 Procedure Find $A^+$                               |

|    | 5.5  | Algorithm Going_In                                       |

|    | 5.6  | Algorithm Correctness                                    |

|    | 5.7  | Simulation Improvements                                  |

| 0  |      | -                                                        |

| 6  | SUM  | IMARY AND FUTURE WORK 112                                |

| Bı | BLIO | GRAPHY                                                   |

| Vı | TA.  |                                                          |

## List of Figures

| 1.1  | A reconfigurable linear array computing the OR function                                            | 3  |

|------|----------------------------------------------------------------------------------------------------|----|

| 1.2  | Summation of eight binary bits on an R-Mesh                                                        | 5  |

| 1.3  | Example of a graph algorithm                                                                       | 6  |

| 1.4  | Simulating an R-Mesh using an smaller R-Mesh                                                       | 9  |

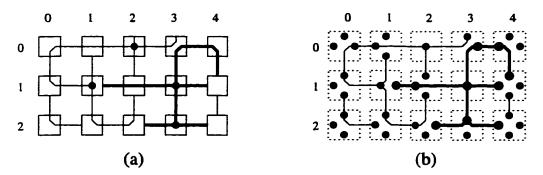

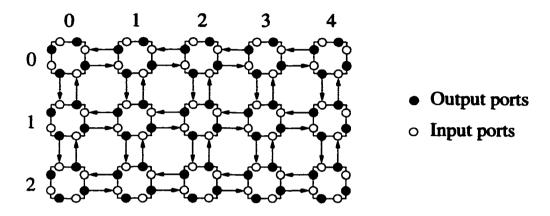

| 2.1  | Internal connections of a 3 $\times$ 5 R-Mesh                                                      | 18 |

| 2.2  | $3 \times 5$ FR-Mesh                                                                               | 19 |

| 2.3  | $3 \times 5$ LR-Mesh                                                                               | 20 |

| 2.4  | Mappings of $6 \times 9$ R-Mesh to $3 \times 3$ R-Mesh $\ldots \ldots \ldots \ldots \ldots \ldots$ | 21 |

| 3.1  | Slices and windows of the simulated $N \times N$ FR-Mesh                                           | 24 |

| 3.2  | Contraction mapping for an FR-Mesh                                                                 | 26 |

| 3.3  | Pseudo-code for component determination                                                            | 30 |

| 3.4  | An illustration of horizontal prefix assimilation                                                  | 31 |

| 3.5  | Example of vertical component sweep                                                                | 38 |

| 3.6  | Pseudo-code for data delivery                                                                      | 41 |

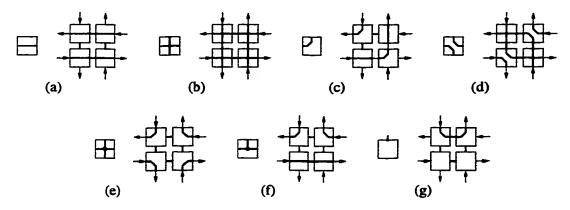

| 3.7  | Configurations for window homogenization                                                           | 43 |

| 3.8  | Example showing need for slice homogenization                                                      | 45 |

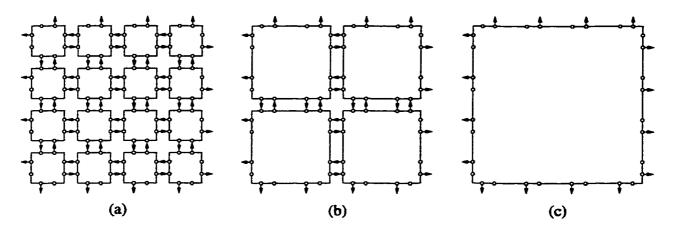

| 3.9  | Ben-Asher et al. procedure to calculate connected components                                       | 58 |

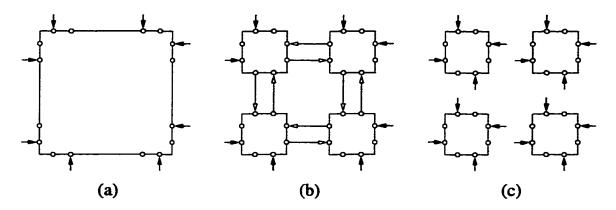

| 3.10 | Decomposition of R-Mesh $S$ into $S_1$ , $S_2$ , $S_3$ , and $S_4$                                 | 59 |

| 3.11 | Embedding the incidence matrix in an FR-Mesh                       | 61          |

|------|--------------------------------------------------------------------|-------------|

| 4.1  | Type of buses                                                      | 64          |

| 4.2  | Port partitions of an R-Mesh                                       | 66          |

| 4.3  | Graph of the R-Mesh                                                | 67          |

| 4.4  | Equivalent group configurations for R-Mesh processors              | 68          |

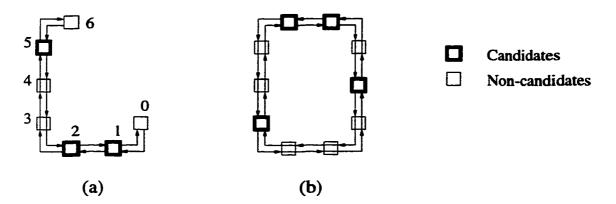

| 4.5  | Leader election examples                                           | 69          |

| 4.6  | Linearization procedure                                            | 72          |

| 4.7  | LR-Mesh simulating an R-Mesh (first part)                          | 74          |

| 4.8  | Raking chains of linear nodes in Step 3                            | 74          |

| 4.9  | LR-Mesh simulating an R-Mesh (second part)                         | 77          |

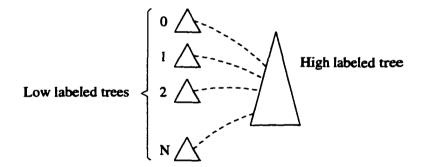

| 4.10 | Grafting operation                                                 | 79          |

| 4.11 | The worst case scenario for grafting trees                         | 79          |

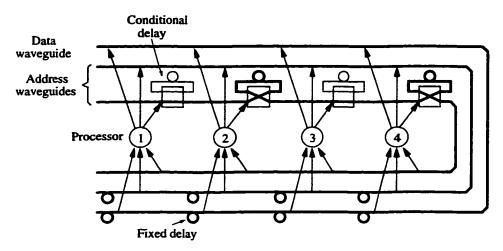

| 4.12 | $1 \times 4$ PR-Mesh                                               | 88          |

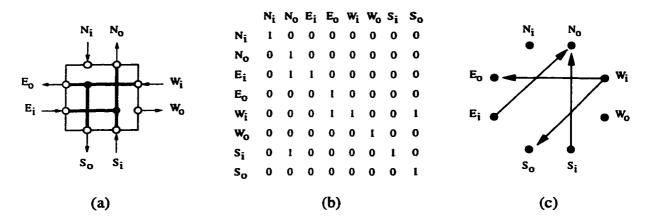

| 5.1  | $3 \times 5$ DR-Mesh                                               | 93          |

| 5.2  | Representation of connections of a DR-Mesh processor               | 94          |

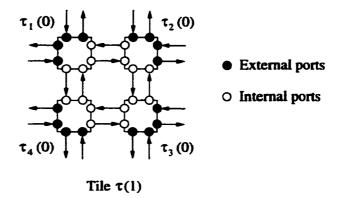

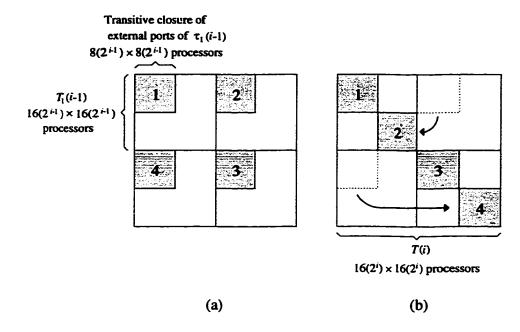

| 5.3  | Tile $\tau(1)$ , its four sub-tiles $\tau_1(0), \ldots, \tau_4(0)$ | 95          |

| 5.4  | Pseudo-code for algorithm Going_Out                                | 98          |

| 5.5  | Moving matrices $A_2^+(i-1)$ and $A_4^+(i-1)$                      | 99          |

| 5.6  | Algorithm Going_Out propagates bus data $Dout(i)$                  | 101         |

| 5.7  | Pseudo-code for algorithm Going In                                 | 1 <b>03</b> |

| 5.8  | Procedure Find_Din                                                 | 105         |

| 5.9  | Algorithm Going_Out | 106 |

|------|---------------------|-----|

| 5.10 | Algorithm Going_In  | 108 |

Fernández Zepeda, José Alberto, B.S., Universidad Nacional Autonóma de México, 1991

M.S., Universidad Nacional Autonóma de México, 1994

Doctor of Philosophy, Fall Commencement, 1999

Major: Electrical Engineering; Minor: Mathematics

<u>Scaling Simulations of Reconfigurable Meshes</u>

Thesis directed by Associate Professor Jerry L. Trahan and Associate Professor Ramachandran Vaidyanathan

Pages in thesis, 128. Words in abstract, 312.

#### ABSTRACT

This dissertation deals with reconfigurable bus-based models, a new type of parallel machine that uses dynamically alterable connections between processors to allow efficient communication and to perform fast computations. We focus this work on the Reconfigurable Mesh (R-Mesh), one of the most widely studied reconfigurable models.

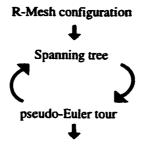

We study the ability of the R-Mesh to adapt an algorithm instance of an arbitrary size to run on a given smaller model size without significant loss of efficiency. A *scaling simulation* achieves this adaptation, and the *simulation overhead* expresses the efficiency of the simulation. We construct a scaling simulation for the Fusing-Restricted Reconfigurable Mesh (FR-Mesh), an important restriction of the R-Mesh. The overhead of this simulation depends only on the simulating machine size and not on the simulated machine size. The results of this scaling simulation extend to a variety of concurrent write rules and also translate to an improved scaling simulation of the R-Mesh itself.

We present a *bus linearization* procedure that transforms an arbitrary non-linear bus configuration of an R-Mesh into an equivalent acyclic linear bus configuration implementable on an Linear Reconfigurable Mesh (LR-Mesh), a weaker version of the R-Mesh. This procedure gives the algorithm designer the liberty of using buses of arbitrary shape, while automatically translating the algorithm to run on a simpler platform. We illustrate our bus linearization method through two important applications. The first leads to a faster scaling simulation of the R-Mesh. The second application adapts algorithms designed for R-Meshes to run on models with pipelined optical buses.

We also present a simulation of a Directional Reconfigurable Mesh (DR-Mesh) on an LR-Mesh. This simulation has a much better efficiency compared to previous work. In addition to the LR-Mesh, this simulation also runs on models that use pipelined optical buses.

٠

## Chapter 1

## Introduction

In recent years, reconfigurable models have drawn considerable interest and numerous fast algorithms have been proposed for them. These models use dynamically alterable connections between processors not only to allow efficient communication, but also to perform computation faster than on conventional "non-reconfigurable" models. Researchers have proposed a number of reconfigurable models including the Reconfigurable Mesh (R-Mesh) [20, 26, 33], Reconfigurable Network (RN) [6], Polymorphic Processor Array (PPA) [30], Processor Array with Reconfigurable Bus System (PARBS) [54], Reconfigurable Multiple Bus Machine (RMBM) [50], Reconfigurable Buses with Shift Switching (REBSIS) [28], and Distributed Memory Bus Computer (DMBC) [42]. Nakano [37] presented a bibliography of published research on reconfigurable models.

This dissertation deals with the ability of a reconfigurable model to adapt an algorithm instance of an arbitrary size to run on a given smaller model size without significant loss of efficiency. A *scaling simulation* achieves this adaptation, and the *simulation overhead* expresses the efficiency of the simulation. For most conventional models, such a scaling simulation is trivial. For reconfigurable models, however, the problem presents several challenges as explained later.

In this dissertation, we focus our attention on the R-Mesh (one of the most widely studied reconfigurable models) and some of its variants. We present new and faster scaling simulations for these models using various write rules. We also demonstrate how some of these models can simulate each other, and describe some important applications of these results.

We organize the remainder of this chapter as follows. Section 1.1 illustrates the main features of reconfigurable models through some examples. Section 1.2 defines the concept of scaling simulations for models of parallel computation and describes previous work on this aspect of reconfigurable models. Section 1.3 describes the scope of the dissertation and Section 1.4 details the main contributions of this work. Finally, Section 1.5 outlines the organization of the dissertation.

#### 1.1 Reconfiguration

A reconfigurable (bus-based) model operates by creating elaborate patterns of "buses" between processors. Some of the most important features of such a model are the following.

1. It uses an internal port connection mechanism to segment or fuse buses.

2. Each processor can independently change its internal port connections at each step.

3. It assumes a constant propagation delay on buses.

4. It uses its buses as a computational resource.

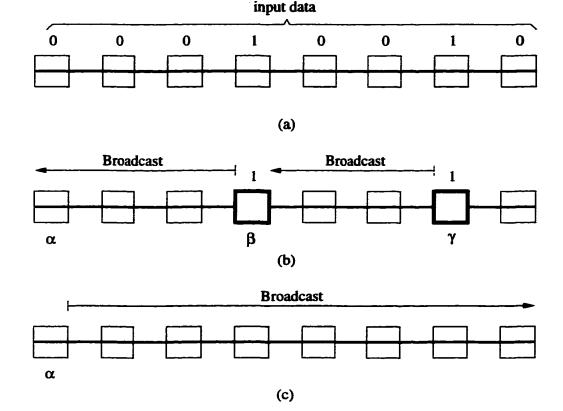

We now present an example that illustrates these features and their use in constructing a very fast algorithm. Figure 1.1 shows an eight-processor reconfigurable linear array (RLA). Each processor connects directly to its neighboring processors through two ports (left and right). Each processor is permitted to internally connect or disconnect its ports.

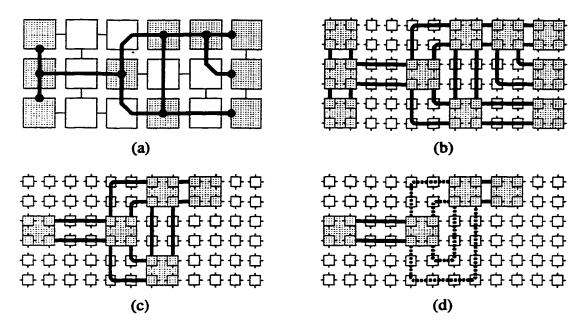

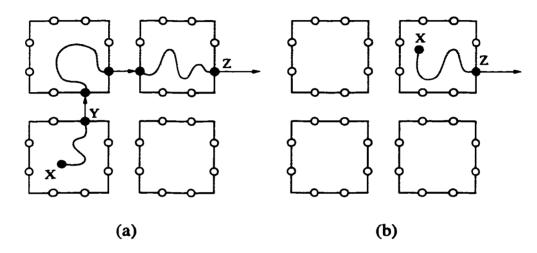

Figure 1.1: A reconfigurable linear array computing the OR function: a) initial configuration and input data for each processor; b) processors holding '1' split the bus and write '1' to their left bus; c) processor  $\alpha$  broadcasts the result to all the processors.

In this example, the RLA calculates the OR function of eight bits. Each processor holds an input bit and assumes the port connection depicted in Figure 1.1(a). The algorithm proceeds as follows.

Each processor that holds a '1' splits the bus by disconnecting its ports; otherwise, it keeps the bus intact (see Figure 1.1(b)). Each processor that holds a '1' writes to the bus through its left port and the leftmost processor,  $\alpha$ , reads the result of the OR function from its left port. If all processors hold '0's, then there is no write to the bus

and processor  $\alpha$  reads a "null value" indicating that the result is '0'. If at least one processor holds a '1', then processor  $\alpha$  reads a '1' from the bus. This value is written by the processor nearest to  $\alpha$  that holds a '1' (processor  $\beta$  in Figure 1.1(b)). Processors holding '0's just provide an unbroken bus, so the value written by processor  $\beta$ reaches processor  $\alpha$ . Finally, processors connect their ports (as in Figure 1.1(c)) and  $\alpha$  broadcasts the result to all processors.

This example illustrates most of the basic features of a reconfigurable model. The method of this example readily generalizes to a constant-time OR algorithm for Nbits on an N-processor RLA. Notice how each processor can disconnect or connect its ports to split the bus or fuse bus segments. Also notice how each processor can change its port connections at each step. This is a local decision (based only on input data or data read from the bus) and is independent of the decision taken by neighboring processors. In general, reconfigurable models are Single-Instruction, Multiple-Data (SIMD) machines, where all processors execute the same program, the program for computing the OR function in this case. These models operate synchronously, so all processors change port connections, write to buses, read from buses, and perform computations at predefined cycles of a master clock. Notice that in this example we assume that the propagation delay is constant, so processor  $\alpha$  broadcasts the result to all the processors connected to the bus in a single step. (This assumption is a good approximation for medium sized machines [26, 30, 33, 42].) In contrast, in an N-processor (non-reconfigurable) linear array, a broadcast takes O(N) time. Notice how the data paths play an important role in determining the answer to the problem in question. The Parallel Random Access Machine (PRAM), a very popular model of parallel computation, requires  $\Omega(\log N)$  time to compute the OR function on N bits, if only exclusive writes are allowed. In the above example, the RLA solves the problem in constant time using only exclusive writes; notice how writing processors (such as  $\beta$  and  $\gamma$  in Figure 1.1(b)) write to different buses.

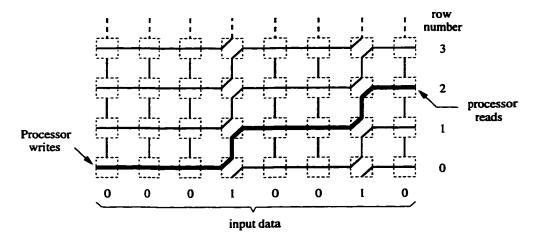

The one-dimensional RLA readily extends to a two-dimensional Reconfigurable Mesh (R-Mesh). An R-Mesh processor has four ports connecting it to its neighbors to the North, South, East, and West. (We formally define the R-Mesh in Chapter 2.) In our next illustration, we use an R-Mesh to compute the sum of 8 bits (Figure 1.2); for simplicity, we show only the bottom four rows of the R-Mesh.

Each processor in the bottom row of the R-Mesh holds one input bit. The algorithm proceeds as follows. The processor at the bottom of each column broadcasts its bit to all the processors in its column. Each processor reading a '1' from its vertical bus, connects its West port to its North port, and its East port to its South port; otherwise, it just connects its West and East ports (see Figure 1.2).

Figure 1.2: Summation of eight binary bits on an R-Mesh.

This internal port connection combined with the external links between processors, creates a staircase-like bus structure. In fact, the bus originating at the bottom left processor (shown in bold in Figure 1.2) steps up by one row for each '1' in the input. The processor on the bottom left corner writes a signal on its West port and each processor of the rightmost column reads from its East port. The sum of the input bits equals x (x = 2 in our example) if and only if the signal arrives at the East port of the rightmost processor of row x. In general, this method sums N bits in constant time on an  $(N + 1) \times N$  R-Mesh.

The main idea of this algorithm is to configure buses so that a signal sent at a fixed point of the R-Mesh "arrives at the answer." Similar techniques can be used to solve a variety of fundamental problems, such as prefix sums, multiplication, Boolean matrix multiplication, and sorting [16, 21, 22, 29, 35, 36, 38].

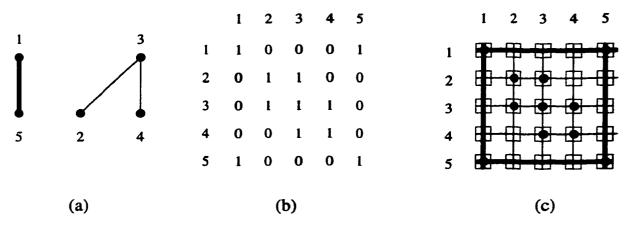

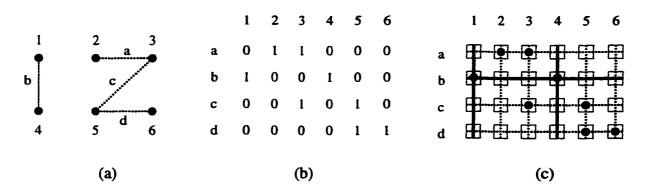

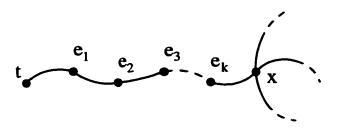

Figure 1.3: Example of a graph algorithm: a) Graph with 2 components; b) Adjacency matrix; c) Embedding on the R-Mesh. The "bold" buses in (c) correspond to the component shown in bold in (a).

Another class of algorithms where reconfiguration is advantageous is graph algorithms. We illustrate one such algorithm in Figure 1.3, where the  $N \times N$  adjacency matrix of an N-node graph is directly embedded into an  $N \times N$  R-Mesh. This embedding has the property that nodes i and j have a path between them in the graph if and only if diagonal R-Mesh processors (i, i) and (j, j) are incident on the same bus. This property allows the R-Mesh to solve problems like s-t connectivity, connected components, and transitive closure in constant time [54]. Similar techniques have been used to construct constant time algorithms for other graph problems, such as spanning trees, biconnected components, Euler tour, and tree traversal [2, 9, 25, 31, 49].

The planar topology of the R-Mesh also makes it suitable for problems in image processing (where each processor represents a pixel of the image) and planar computational geometry. These include image labeling, template matching, histogramming, convex hull, dominance counting, Voronoi diagrams, and other proximity problems [1, 10, 11, 18, 20, 23].

#### **1.2 Scaling Simulations and Previous Work**

Let  $\mathcal{M}(N)$  denote an N-processor instance of a model,  $\mathcal{M}$ , of parallel computation. A scaling simulation for  $\mathcal{M}$  is an algorithm that simulates an arbitrary step of  $\mathcal{M}(N)$ on a smaller instance  $\mathcal{M}(P)$ , for any P < N. In general, this simulation runs in  $\Theta\left(\frac{N}{P}f(N,P)\right)$  steps. Clearly, the work of N processors on P processors takes  $\Omega\left(\frac{N}{P}\right)$ steps, therefore, f(N,P), a non-decreasing function, is the simulation overhead. (The scaling simulation serves to establish that any algorithm designed to run in T steps on  $\mathcal{M}(N)$  can run in  $O\left(\frac{N}{P}f(N,P)\cdot T\right)$  steps on  $\mathcal{M}(P)$ .)

**Definition 1** For any P < N, let  $\mathcal{M}(P)$  simulate a step of  $\mathcal{M}(N)$  in  $O(\frac{N}{P}f(N, P))$  time.

(i) Model  $\mathcal{M}$  has an optimal scaling simulation iff f(N, P) = O(1).

(ii) Model  $\mathcal{M}$  has a strong scaling simulation iff f(N, P) is independent of N and f(N, P) = o(P).

(iii) Model  $\mathcal{M}$  has a weak scaling simulation iff it does not have an optimal or strong scaling simulation.

If a model possesses an optimal scaling simulation, then a programmer need not be concerned with the actual size of the machine on which a program is to run. In this case, the best algorithm serves well on all model and problem sizes. On a model with a strong scaling simulation, a single algorithm will serve all problem sizes as the simulation overhead is independent of N, the simulated model size. A compiler, that is in any case local to the model or machine instance, can map logical processors (defined by the algorithm and problem instance) to physical processors. On a model with a weak scaling simulation, however, the fastest algorithm for given problem and model sizes may not be the fastest (after scaling) for other problem and model sizes; it may have to be fine-tuned or possibly even replaced by another algorithm for different problem sizes. (This approach is taken in practice in some parallel machines, for example [8, 16].) With a weak scaling simulation, however, different problem sizes would call for different algorithms, and so different programs, to run in the best possible time on the same available machine. For a model with an optimal or strong scaling simulation, algorithmic results have significance whether or not problem size matches machine size. Algorithm development itself may be easier on these models (for example, using the work-time framework [19] for PRAM algorithms).

In traditional "non-reconfigurable" models, a large model instance  $\mathcal{M}(N)$  can be simulated optimally by a small model instance  $\mathcal{M}(P)$ , simply by letting a processor of  $\mathcal{M}(P)$  simulate  $\frac{N}{P}$  processors of  $\mathcal{M}(N)$ . Thus these models have optimal scaling simulations. The difficulty in scaling algorithms for reconfigurable models stems from the fundamentally different way in which they perform computation. A sequence of steps typical to many algorithms is as follows: (a) processors configure themselves locally to establish a global pattern of buses interconnecting the processors; (b) a designated processor issues a special signal at a fixed position in the bus structure; (c) the processors deduce an answer depending on where the signal arrives. (The summing algorithm of Figure 1.2 is an example of such an algorithm.) In this setting, consider a problem that has N possible answers. If a model instance is not large enough to accommodate N distinct answers (positions for signal arrival), then the above method will not work.

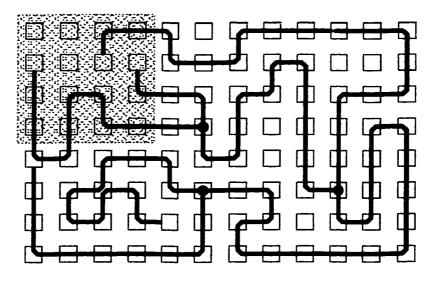

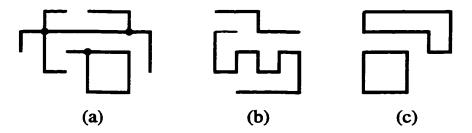

Figure 1.4: Simulating an R-Mesh using an smaller R-Mesh (shadow square).

The great variety of bus shapes in an R-Mesh, especially branches and cycles, make it difficult to design an efficient scaling simulation. To illustrate this problem, consider Figure 1.4, which shows a  $4 \times 4$  R-Mesh (shown as a shaded square) simulating a "window" of an  $8 \times 12$  R-Mesh. In the window, the simulating R-Mesh detects four buses that are separated within the window, but are, in fact, part of a single bus. The simulating machine has to label each bus, keep track of them through the entire simulation, and update their labels when they fuse to other buses. This task is not trivial because of the large number of possible bus configurations and is the main cause of the simulation overhead. This notion of scaling simulation can be generalized to that of scaling simulations between different models. Specifically, we will consider scenarios where a single step of  $\mathcal{M}_1(N)$ , a model of size N is simulated by  $\mathcal{M}_2(P)$  a smaller instance of a different model in  $O\left(\frac{N}{P}f(N,P)\right)$  time.

Reconfigurable models possess a large body of fast algorithms, yet only a handful of results exist for scaling algorithms on these models. Previously, Maresca [30] established that the Polymorphic Processor Array (PPA) possesses an optimal scaling simulation. The PPA restricts the pattern of buses that can be created, severely curtailing the power of the model [50]. Ben-Asher et al. [4] proved that the Linear Reconfigurable Mesh (LR-Mesh), a restriction of the R-Mesh, has an optimal scaling simulation. The LR-Mesh admits only certain patterns of buses, making it unsuitable for some fundamental problems such as graph connectivity. Murshed and Brent [34] defined certain global restrictions on bus configurations and designed simpler optimal scaling simulations for LR-Meshes under these restrictions. Ben-Asher et al. [4] developed a (weak) scaling simulation for an  $N \times N$  (unrestricted) R-Mesh on a  $P \times P$  R-Mesh that has a simulation overhead of  $\log N \log \frac{N}{P}$ . Matias and Schuster [32] proposed a randomized scaling simulation for the unrestricted R-Mesh on the LR-Mesh; their method has a constant (with high probability) simulation overhead, only when  $P \leq \frac{N}{\log N \log \log N}$ , and uses the "ARBITRARY" concurrent-write rule, a rule not easily implementable on a bus. On other reconfigurable models, Trahan et al. [48] developed an  $O(\log N)$  simulation of an  $N \times N$  Directional R-Mesh on an  $O(N^4 \times N^4)$  LR-Mesh. Trahan and Vaidyanathan [51] have shown that, for certain restrictions of local connections, the Reconfigurable Multiple Bus Machine (RMBM) has a strong scaling simulation. Trahan et al. [47] developed a number of algorithms that scale with optimal overhead on the Linear Array with Reconfigurable Pipelined

Bus System (LARPBS), a reconfigurable model that uses pipelined optical buses for communication.

#### **1.3** Scope of the Dissertation

All prior approaches to scaling reconfigurable models either severely restrict the simulated model and/or grant extra capabilities to the simulating model (in order to achieve constant overhead), or incur a high simulation overhead. We consider a restriction of the R-Mesh, called the Fusing Restricted R-Mesh (FR-Mesh), for which we construct a strong scaling simulation. The FR-Mesh is as "powerful" as the unrestricted R-Mesh [45], though it allows only two of the fifteen internal connections possible on the R-Mesh (see Section 2.2). Further, the FR-Mesh admits constant time algorithms for fundamental problems (such as s-t connectivity, connected components, transitive closure, and cycle detection [2, 25, 54]) that are unlikely to be solvable in constant time on the LR-Mesh; many such problems are fundamental to algorithm development in general [53].

In Chapter 3, we construct a strong scaling simulation of the FR-Mesh in which the simulation overhead is logarithmic in the simulating machine size, and entirely independent of the simulated machine size. More precisely, we establish that for any P < N, a step of an  $N \times N$  FR-Mesh (that has  $N^2$  processors) can be simulated by a  $P \times P$  FR-Mesh in  $O(\frac{N^2}{P^2} \log P)$  time.

Additionally, we identify the bottleneck producing the simulation overhead of the FR-Mesh scaling simulation as "leader election." Thus, any improvement in techniques for leader election will immediately translate to a further reduction of the overheads for scaling simulations of both the FR-Mesh and the R-Mesh. Indeed, an FR-Mesh that can resolve concurrent writes by the "PRIORITY" rule has an optimal scaling simulation (Section 3.6).

Although most of the dissertation uses the "COMMON" concurrent write rule, we also consider other rules such as "COLLISION" and "COLLISION<sup>+</sup>" (Section 3.6) that are well known in the context of PRAM algorithms [19, 24]. For these rules, the FR-Mesh still has a strong scaling simulation with a logarithmic simulation overhead.

The strong scaling simulation of the FR-Mesh also leads to an improved (weak) scaling simulation of the R-Mesh (Section 3.7). The simulation overhead for this simulation is  $\log P \log \frac{N}{P}$ ; the previous fastest scaling simulation for the R-Mesh [4] had a simulation overhead of  $\log N \log \frac{N}{P}$  (see Table 1.1).

The R-Mesh can create bus structures of many different shapes (see Figure 2.1). On the one hand, flexibility in shaping buses facilitates algorithm design and can reduce running time, but on the other hand, complex bus shapes complicate implementation of these models. In Chapter 4, we present a procedure called *bus linearization* that transforms a bus of any shape allowed by the R-Mesh into one with an equivalent linear (non-branching) structure.

Specifically, we prove that an  $N \times N$  LR-Mesh (an R-Mesh restriction that permits only linear buses) can simulate an arbitrary step of an  $N \times N$  R-Mesh in  $O(\log N)$  time. We illustrate the use of bus linearization through two important applications. The first constructs the best known deterministic scaling simulation for the R-Mesh. This approach has  $\log N$  simulation overhead, which improves on the simulation overhead of  $\log P \log \frac{N}{P}$  (Chapter 3). The second application adapts algorithms designed for the R-Mesh to run on reconfigurable models that use optical buses [40, 44, 45].

Bus linearization also improves the FR-Mesh scaling simulation of Chapter 3 to a weaker simulating model (see Table 1.1); the simulation in Chapter 3 requires a "CRCW" FR-Mesh (with the ability to perform concurrent writes), while the simulation of Chapter 4 needs only a "CREW" LR-Mesh (without the need to perform concurrent writes).

In Chapter 5, we present the simulation of a Directed Reconfigurable Mesh (DR-Mesh) on an LR-Mesh. The DR-Mesh has directed buses with the ability to restrict data propagation to only one direction. We simulate an  $N \times N$  DR-Mesh in  $O(\log^2 N)$  time on an  $O(N \times N \times \frac{N}{\log N})$  (three-dimensional) R-Mesh and on an  $O(\frac{N^2}{\log N} \times \frac{N^2}{\log N})$  (two-dimensional) R-Mesh. This result is a substantial improvement on the only previous work on this problem [48], where an  $O(N^4 \times N^4)$  R-Mesh achieves  $O(\log N)$  time. Furthermore, we showed that the simulating machine can be a Pipelined Reconfigurable Mesh (PR-Mesh) or an equivalent pipelined optical model, thereby extending the scope of the simulation.

#### **1.4 Contributions of This Work**

On the whole, this dissertation provides a better understanding about scalability of reconfigurable models in general, and the R-Mesh and its variants, in particular. It presents new approaches to problems in scalability, many of which could be useful for scaling simulations on other reconfigurable models as well. We present several simulations among reconfigurable models. Tables 1.1 and 1.2 summarize the contribution of these simulations in the context of existing results.

Some algorithms run more efficiently on LR-Meshes than on FR-Meshes and viceversa. The class of *separable R-Mesh algorithms* comprises algorithms in which each step runs on either an LR-Mesh or an FR-Mesh. Separable algorithms provide an extremely rich array of fast and efficient algorithmic building blocks. The main result in Chapter 3 is a strong scaling simulation of the FR-Mesh. This result, coupled with the optimal scaling simulation for the LR-Mesh [4] allows separable algorithms to scale with an overhead that depends only on the simulating machine size.

| Table 1.1: Summary of scaling simulations |                                     |                              |           |

|-------------------------------------------|-------------------------------------|------------------------------|-----------|

| Simulated model                           | Simulating model                    | Simulation overhead          | Reference |

| CRCW LR-Mesh                              | CRCW LR-Mesh                        | <i>O</i> (1)                 | [4]       |

|                                           | CRCW FR-Mesh                        | $O(\log P)$                  | This work |

| CRCW FR-Mesh                              | CREW LR-Mesh                        | $O(\log P)$                  | This work |

|                                           | CREW PR-Mesh                        | $O(\log P)$                  | This work |

| <u> </u>                                  | CRCW R-Mesh                         | $O(\log N \log \frac{N}{P})$ | [4]       |

|                                           | CRCW R-Mesh                         | $O(\log P \log \frac{N}{P})$ | This work |

| CRCW R-Mesh                               | COLLISION CRCW LR-Mesh <sup>†</sup> | $O(\log P)$ w.h.p.           | [32]      |

|                                           | ARBITRARY CRCW LR-Mesh <sup>†</sup> | <i>O</i> (1) w.h.p.          | [32]      |

|                                           | CREW LR-Mesh                        | $O(\log N)$                  | This work |

|                                           | CREW PR-Mesh                        | $O(\log N)$                  | This work |

The sizes of the simulated and simulating models are  $N \times N$  and  $P \times P$ , respectively.

<sup>†</sup>The simulating model is randomized and its simulation overhead is with high probability.

The main result of Chapter 4 is the construction of a bus linearization algorithm. This algorithm transforms any R-Mesh algorithm to run on the optimally scalable LR-Mesh. Bus linearization gives an algorithm designer the liberty of using buses of arbitrary shape, while automatically translating the algorithm to run on a more implementable platform. Bus linearization runs on an LR-Mesh with only exclusive writes, whereas the simulating machine of all prior scaling simulations required concurrent writes (see Table 1.1).

Furthermore, bus linearization also transforms FR-Mesh algorithms to run on an LR-Mesh. This feature automatically allows any separable algorithm to run on an LR-Mesh maintaining a simulation overhead of  $\log P$ . Bus linearization also facilitates the simulation of the R-Mesh and FR-Mesh on reconfigurable pipelined optical models, which require linear acyclic buses. Thus, the importance of bus linearization

on the LR-Mesh and reconfigurable pipelined optical models.

| Table 1.2: Summary of DR-Mesh simulations |                                                    |                  |               |           |

|-------------------------------------------|----------------------------------------------------|------------------|---------------|-----------|

| Simulated model                           | Simulating model size                              | Simulating model | Time          | Reference |

|                                           | $O(N^4 \times N^4)$                                | CRCW R-Mesh      | $O(\log N)$   | [48]      |

| CRCW DR-Mesh                              | $O\left(N \times N \times \frac{N}{\log N}\right)$ | CREW LR-Mesh     | $O(\log^2 N)$ | This work |

|                                           | $O\left(N^2 \times \frac{N}{\log N}\right)$        | CREW PR-Mesh     | $O(\log^2 N)$ | This work |

The size of the simulated model is  $N \times N$ .

The main result of Chapter 5 is a simulation of a CRCW DR-Mesh on a CREW LR-Mesh and can be extended to reconfigurable pipelined optical models. Ben-Asher *et al.* [5] established that a constant time simulation of an  $N \times N$  DR-Mesh on an R-Mesh bounded with a polynomial number of processors is not likely, while Trahan *et al.* [48] designed a simulation of each DR-Mesh step on an  $O(N^4 \times N^4)$  R-Mesh in  $O(\log N)$  time. The target of our simulation is to reduce the number of processors. Its contribution is a useful technique that dramatically reduces the size of the simulating model by a factor of  $O(N^4 \log^2 N)$ . Table 1.2 shows these results.

In addition to these broad results, this work has also generated several tools and techniques that may be of independent interest, such as prefix assimilation (Section 3.4.1), double bus structure (Section 4.1.2), and a terse representation for connectivity within R-Mesh "tiles" (Section 5.4).

#### **1.5** Organization of the Dissertation

Chapter 2 defines the R-Mesh, some of its variants, and basic concepts such as concurrent write rules and leader election. Chapter 3 describes the FR-Mesh simulation and its use in obtaining an improved scaling simulation for the R-Mesh. Chapter 4 presents bus linearization and its applications. Chapter 5 deals with the simulation of the directed R-Mesh on an LR-Mesh. Finally, Chapter 6 summarizes this work and presents some directions for future work in the area.

## Chapter 2

## **Definitions and Terminology**

This chapter describes the reconfigurable models we use in this work. Also discussed are the definitions of several concurrent write rules and some mapping techniques used in scaling simulations.

#### 2.1 The R-Mesh

An  $R \times C$  Reconfigurable Mesh (R-Mesh) is a two-dimensional array of processors connected in an  $R \times C$  grid. Each processor in the R-Mesh has direct connections to adjacent processors through its North, South, West, and East input/output ports. A processor can internally partition its set of four ports so that all ports in the same block of a partition are fused. This allows the R-Mesh to construct various bus patterns and to change them dynamically according to the requirements of the problem at hand. Figure 2.1 shows a  $3 \times 5$  R-Mesh, depicting the fifteen possible port partitions of a processor. These partitions, along with external connections between processors, define a global bus structure consisting of a set of buses that weave through the ports. A *component* is a set of buses and ports that have a common connection. The R-Mesh and all its restricted versions assume a constant propagation delay on buses [26, 33, 42].

Figure 2.1: Internal connections of a  $3 \times 5$  R-Mesh.

#### 2.2 The FR-Mesh

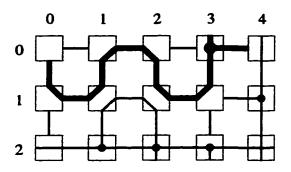

The Fusing Reconfigurable Mesh (FR-Mesh) is a restricted version of the R-Mesh. Trahan *et al.* [45] proved that the class of languages accepted by an FR-Mesh is equivalent to the class SL (the same as the R-Mesh) of languages accepted in symmetric logarithmic space, on a Turing machine. That is, the FR-Mesh is as "powerful" as the R-Mesh though it allows only two of the fifteen internal connections possible on the R-Mesh, a *fusing* and a *cross-over* connection. A fusing connection joins all four ports (processor (0,2) in Figure 2.2), and a cross-over connection joins the North port with the South port and the West port with the East port (processor (0,0) in Figure 2.2). Because of the FR-Mesh has only two ports, the *vertical port* (North and South ports) and the *horizontal port* (East and West ports). The connections in an FR-Mesh allow a processor to directly connect to any other processor in its row (or column) via a *horizontal* (or *vertical*) *bus*. Figure 2.2 shows a  $3 \times 5$  FR-Mesh with one component shown in bold. This component consists of buses in row 1 and column 3 and all the ports connected to these buses.

Figure 2.2:  $3 \times 5$  FR-Mesh.

#### 2.3 The LR-Mesh

The Linear Reconfigurable Mesh (LR-Mesh) is a restricted version of the R-Mesh. Each port in the LR-Mesh can connect to at most one other port in the same processor, so the LR-Mesh allows ten of the fifteen connections of the R-Mesh (all of the configurations of Figure 2.1 except those of processors (0,3), (1,4), (2,1), (2,2), and (2,3)). Ben-Asher *et al.* [4] constructed an optimal scaling simulation for the LR-Mesh. Ben-Asher *et al.* [5] also proved that the class of languages accepted by an LR-Mesh (resp., R-Mesh) is equivalent to the class L (resp., SL) of languages accepted in logarithmic space (resp., symmetric logarithmic space [39]) on a Turing machine. Although it has not been proved, the class L is conjectured to be a proper subset of the class SL, so the LR-Mesh is likely to be a weaker model than the R-Mesh. Figure 2.3 shows a  $3 \times 5$  LR-Mesh with some typical bus configurations. The figure also shows a component in bold.

#### 2.4 Concurrent Writes

Most of this dissertation deals with concurrent read, concurrent write (CRCW) reconfigurable models, in which several processors may simultaneously read from or

Figure 2.3:  $3 \times 5$  LR-Mesh.

write to the same bus. Concurrent writes are resolved by the COMMON, COLLISION, COLLISION<sup>+</sup>, PRIORITY, or ARBITRARY rules. These rules are well known in the context of PRAM algorithms [19, 24]. The COMMON rule allows concurrent writes only if all the values written to a component are equal. Under the COLLISION rule, if more than one processor attempts to write to a component, then a collision symbol is written. The COLLISION<sup>+</sup> rule behaves like the COMMON rule when all processors attempt to write the same value to a component, and like COLLISION otherwise. In the PRIORITY rule, the processor with highest priority among those attempting to write (usually the lowest indexed processor) wins the write conflict and writes its value. In the ARBITRARY rule, an arbitrary processor wins the write conflict and writes its value.

On a distributed shared resource such as a bus, only certain write rules such as COMMON, COLLISION, and COLLISION<sup>+</sup> [4] are feasible. Other rules exist, such as ARBITRARY and PRIORITY, whose physical implementations on a bus are not feasible, on the one hand, but on the other hand, they are a very useful algorithmic abstraction that simplifies algorithm design. In Sections 3.6 and 4.2.3, we present procedures to simulate models with different write rules and in Section 4.2.5, we present a procedure to remove the need of concurrent writes for the LR-Mesh.

In the following discussion, we refer to the process of choosing an element from a candidate pool by the PRIORITY (resp., ARBITRARY) rule as priority resolution (resp., arbitrary selection).

Leader election: This is a procedure that, for each component, selects a leader among a set of marked processors. (Marked processors may, for example, be the processors attempting to write.) The following procedure performs leader election by *priority resolution*. Let each processor have a unique  $O(\log P)$ -bit key (the key may be its index). By examining the keys bit-by-bit, the procedure reduces the set of potential candidates for the leader so that the elected leader is one with a highest (or lowest) key. Consequently, a COMMON CRCW R-Mesh can perform leader election among P processors in  $O(\log P)$  time. Section 3.6.3 describes procedures to perform leader election by priority resolution using the COMMON, COLLISION, and COLLISION<sup>+</sup> rules.

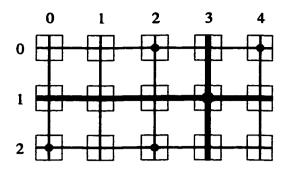

Figure 2.4: Mappings of  $6 \times 9$  R-Mesh to  $3 \times 3$  R-Mesh, where numbers indicate processors of the  $3 \times 3$  R-Mesh: a) Contraction mapping; b) Windows mapping.

#### 2.5 Contraction and Windows Mappings

Let Q be an  $N \times N$  R-Mesh and  $\mathcal{R}$  a  $P \times P$  R-Mesh, where  $P \leq N$ . A scaling simulation for an R-Mesh involves the simulation of a step of Q on  $\mathcal{R}$ . For this, processors of Q must map to processors of  $\mathcal{R}$ .

The most obvious mapping is to let each processor of  $\mathcal{R}$  simulate an  $\frac{N}{P} \times \frac{N}{P}$ "sub-R-Mesh" of  $\mathcal{Q}$ . Ben-Asher *et al.* [4] called this the *contraction mapping* (see Figure 2.4(a), where the bold processors map to processor 1 of  $\mathcal{R}$ ).

The windows mapping [4] divides Q into  $\frac{N^2}{P^2}$  "windows", each a  $P \times P$  sub-R-Mesh. In the simulation, each processor of  $\mathcal{R}$  simulates the same processor from each window (see Figure 2.4(b), where the bold processors map to processor 1 of  $\mathcal{R}$ ).

Ben-Asher *et al.* [4] proved that the contraction mapping will not allow an optimal scaling simulation for the LR-Mesh. Using a similar argument, an FR-Mesh scaling simulation that uses the contraction mapping has an overhead of  $\Omega(\sqrt{N})$  (proved in Section 3.2). Hence, we use the windows mapping to perform the scaling simulation of the FR-Mesh (see Chapter 3).

## Chapter 3

## **FR-Mesh Scaling Simulation**

This chapter presents a strong scaling simulation for the FR-Mesh [13, 14]. The following theorem summarizes the main result of this chapter.

**Theorem 3.1** For any P < N, any step of an  $N \times N$  COMMON CRCW FR-Mesh can be simulated on a  $P \times P$  COMMON CRCW FR-Mesh in  $O\left(\frac{N^2}{P^2} \log P\right)$  time.

The main objective is to simulate an arbitrary step of an  $N \times N$  FR-Mesh, Q, on a  $P \times P$  FR-Mesh,  $\mathcal{R}$ . In the simulation, each processor of  $\mathcal{R}$  simulates  $\frac{N^2}{P^2}$  processors of Q. Therefore,  $\mathcal{R}$  can simulate local actions of processors of Q in  $O\left(\frac{N^2}{P^2}\right)$  time. The global structure of Q is more difficult to simulate.

Chapter 3 is organized as follows. Section 3.2 establishes a lower bound for the FR-Mesh scaling simulation using the contraction mapping. Section 3.3 gives a general description of the FR-Mesh scaling simulation. Sections 3.4 and 3.5 describe the two main parts into which we have divided the FR-Mesh scaling simulation and that constitute the proof of Theorem 3.1. Section 3.6 explains how to modify the FR-Mesh scaling simulation to accommodate different write rules. Finally, Section 3.7 describes a new R-Mesh scaling simulation using the FR-Mesh.

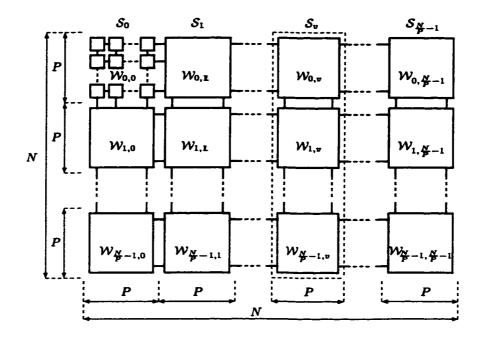

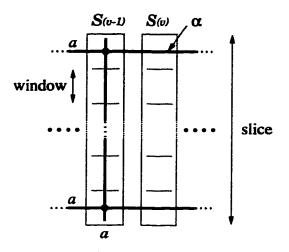

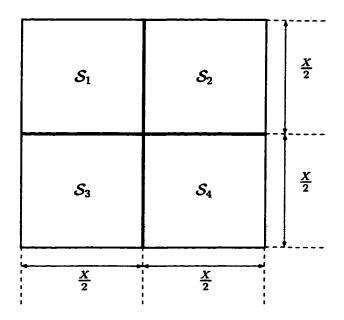

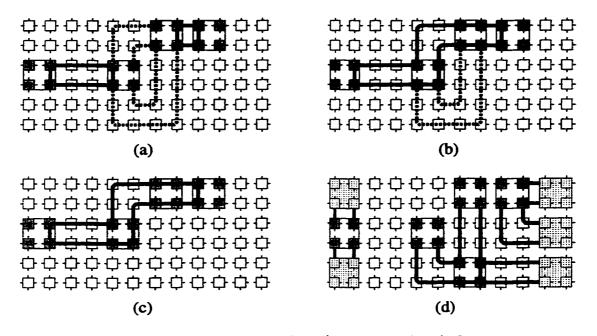

Figure 3.1: Slices and windows of the simulated  $N \times N$  FR-Mesh.

# 3.1 Scaling Simulation Terminology

Let Q be the simulated machine, an  $N \times N$  CRCW FR-Mesh. Let  $\mathcal{R}$  be the simulating machine, a  $P \times P$  CRCW FR-Mesh, where  $P \leq N$ . Without loss of generality, assume that  $\frac{N}{P}$  is an integer. We now define the terminology used in presenting a scaling simulation.

Slice: The simulated FR-Mesh, Q, contains  $\frac{N}{P}$  slices, each an  $N \times P$  sub-FR-Mesh (see Figure 3.1). Denote slice v by  $S_v$ , where  $0 \le v < \frac{N}{P}$ .

Window: Each slice,  $S_v$ , contains  $\frac{N}{P}$  windows, each a  $P \times P$  sub-FR-Mesh (see Figure 3.1). For  $0 \le u, v < \frac{N}{P}$ , denote window u of  $S_v$  by  $\mathcal{W}_{u,v}$ .

Bus index: This is an identifier assigned to each horizontal and vertical bus in Q according to its position. The horizontal bus in row *i* has bus index *i*, while the vertical bus in column *j* has bus index j + N, where  $0 \le i, j < N$ . For  $0 \le b < 2N$ , let bus(b) denote the bus with index *b*.

Bus data: This is the value available on a bus at the end of a write cycle. If there is no write on a bus at the current cycle, then the bus data on the bus is said to be *null*; otherwise, it is *non-null*. Since the FR-Mesh permits resolution of concurrent writes by rules such as COLLISION, the data a port reads from the bus may not be the same as the value the same port wrote to the bus.

Component number: This is an identifier assigned to a component. In the simulation presented in this chapter, the component number is equal to the largest bus index among all buses in the component. Initially, when the simulation is unaware of any connections between buses of Q, it assigns to each bus its bus index as its component number.

# 3.2 Mapping for FR-Mesh

Ben-Asher *et al.* [4] established that simulating the LR-Mesh using the contraction mapping (see Section 2.5) requires  $\Omega(N)$  overhead, which does not allow an optimal or even a strong scaling simulation for the LR-Mesh.

By a similar argument, the required overhead to simulate an FR-Mesh using the contraction mapping is  $\Omega(\sqrt{N})$ , and so we cannot use the contraction mapping to design a strong scaling simulation for the FR-Mesh.

Lemma 3.2 For any P < N, simulating any step of an  $N \times N$  FR-Mesh on a  $P \times P$ FR-Mesh using the contraction mapping requires  $\Omega(\sqrt{N})$  time.

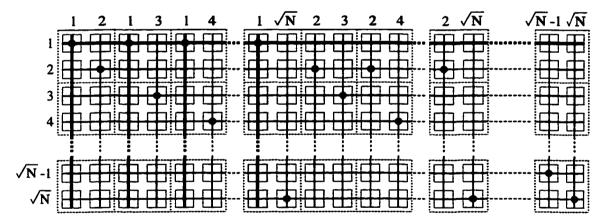

**Proof:** We construct an example of a bus configuration in an  $N \times N$  FR-Mesh, Q, that requires  $\Omega(\sqrt{N})$  steps to simulate using a  $P \times P$  FR-Mesh,  $\mathcal{R}$ . First, we describe this bus configuration.

Assign each vertical and horizontal bus in Q a label between 1 and  $\sqrt{N}$ ; the labels for vertical buses, starting at the left, are as follows:

$1, 2, 1, 3, 1, 4, \dots, 1, \sqrt{N}, 2, 3, 2, 4, \dots, 2, \sqrt{N}, 3, 4, 3, 5, \dots, 3, \sqrt{N}, \dots, \sqrt{N} - 1, \sqrt{N}.$

The labels for horizontal buses, starting at the top, are as follows:

$1, 2, 3, \ldots, \sqrt{N}, 1, 2, 3, \ldots, \sqrt{N}$ , and so on.

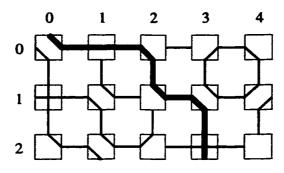

Each processor at the intersection of a vertical bus and a horizontal bus that have the same label sets a fusing connection; all other processors set cross-over connections. Figure 3.2 shows this bus configuration.

Figure 3.2: Contraction mapping for an FR-Mesh prevents a strong scaling simulation.

Assume that  $P = \frac{N}{2}$ . By using the contraction mapping, a single processor of the simulating machine,  $\mathcal{R}$ , performs the work of four processors of  $\mathcal{Q}$  (dotted lines in Figure 3.2). Vertical buses with label 1 share processors with vertical buses with

labels 2, 3, 4, ...,  $\sqrt{N}$ . Each column of processors of  $\mathcal{R}$  only can simulate one vertical bus of  $\mathcal{Q}$  at a time. When  $\mathcal{R}$  simulates the component with label 1 (bold bus in Figure 3.2), it cannot simulate components with labels 2, 3, 4, ...,  $\sqrt{N}$  at the same time. Similarly, vertical buses with label 2 share processors with vertical buses with labels 1, 3, 4, ...,  $\sqrt{N}$ . When  $\mathcal{R}$  simulates the component with label 2, it cannot simulate components with labels 1, 3, 4, ...,  $\sqrt{N}$  at the same time, and so on.

In general, given the above configuration,  $\mathcal{R}$  can simulate at most one component of  $\mathcal{Q}$  at a time. Consequently, the simulation of  $\mathcal{Q}$  by  $\mathcal{R}$  using the contraction mapping takes  $\Omega(\sqrt{N})$  time.

We will therefore use the windows mapping [4] (see Figure 2.4(b)).

## **3.3 General Description of the Simulation**

Ben-Asher *et al.* [4] developed an optimal scaling simulation for the LR-Mesh that uses the windows mapping. This algorithm uses the fact that each bus has only two end-points (as each bus in the LR-Mesh is linear); consequently, it is possible to track buses across windows by considering at most two ports per bus. On the other hand, a bus in the FR-Mesh can have  $\Theta(P)$  end-points in a window (because of fusing connections) and necessitates an entirely different approach.

The simulation of a step of Q, an  $N \times N$  FR-Mesh, on  $\mathcal{R}$ , a  $P \times P$  FR-Mesh, progresses in two phases. During the first phase, *component determination*, the simulating machine  $\mathcal{R}$  labels buses of Q with their component numbers. This allows  $\mathcal{R}$  to treat ports with the same component number as if they were connected by a common bus, without the need to physically configure its buses exactly as in Q.  $\mathcal{R}$ ascertains the connection pattern of Q gradually by performing a window-by-window vertical sweep down each slice of Q, and performing a slice-by-slice horizontal sweep across Q. The biggest obstacle is that fusing connections outside a window can affect the component numbers of buses that are not connected within the window. Our main approach to overcoming this problem is assimilating into the current window the effect of connections in previously examined windows.

After assigning a component number to each bus,  $\mathcal{R}$  proceeds to the second phase, data delivery. This phase conveys data written to one or more ports of a component to all ports of the component (this data depends on the concurrent write rule). During this phase,  $\mathcal{R}$  sweeps over each window of  $\mathcal{Q}$  detecting and recording processors' attempts to write to each component. During a second sweep,  $\mathcal{R}$  delivers the data that appears on each component to all processors that simulate processors of  $\mathcal{Q}$  reading that component. Section 3.4 describes component determination and Section 3.5 describes data delivery.

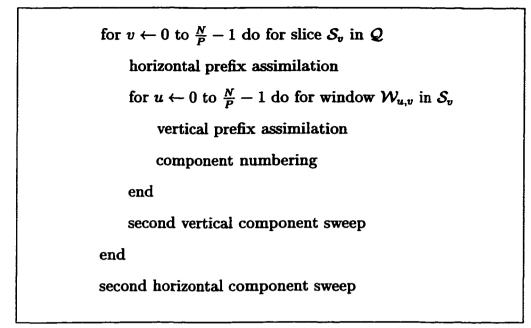

# 3.4 Component Determination

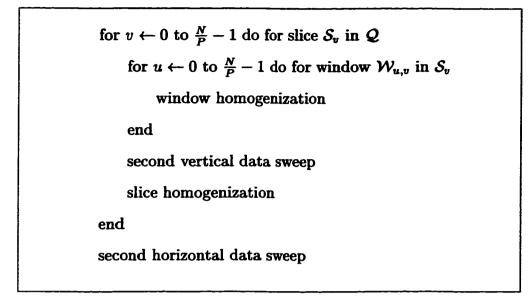

During the simulation,  $\mathcal{R}$  treats  $\mathcal{Q}$  as a series of  $\frac{N}{P}$  slices. Component determination includes two horizontal sweeps across these slices to label the components. In the first sweep,  $\mathcal{R}$  applies the following procedures to each slice of  $\mathcal{Q}$  in turn. Horizontal prefix assimilation embeds in the current slice the effect of bus fusings of all preceding slices by selectively adding fusing connections to the current slice. After horizontal prefix assimilation,  $\mathcal{R}$  can consider the current slice in isolation. To simulate the current slice,  $\mathcal{R}$  now moves downwards, applying a sequence of vertical prefix assimilation and component numbering procedures to each window in the slice. Like horizontal prefix assimilation, vertical prefix assimilation embeds in the current window the effect of bus fusings of all previous windows in the slice. After applying vertical prefix assimilation to a window, component numbering uses the leader election procedure (Section 2.4) to update the component numbers for that window. The update includes the effect of fusing connections in all previously visited windows and slices. The sequence of calls to the vertical prefix assimilation and component numbering procedures concludes in the bottom window of the slice. Component numbers of vertical buses in the bottom window include the effects of the entire slice, so  $\mathcal{R}$  broadcasts these to vertical buses in upper windows, and from here to any horizontal buses connected to them.

At this point in the simulation, for each bus in the slice,  $\mathcal{R}$  holds the component number incorporating the effects of that slice and all slices to its left in  $\mathcal{Q}$ , but none of the slices to the right. After completing the first horizontal sweep across all slices in  $\mathcal{Q}$ ,  $\mathcal{R}$  holds the final component number of each horizontal bus in  $\mathcal{Q}$ . In the second horizontal sweep,  $\mathcal{R}$  broadcasts these values to each vertical bus connected to a horizontal bus. The pseudo-code in Figure 3.3 describes the organization of the component determination phase.

Sections 3.4.1 to 3.4.5 explain horizontal prefix assimilation, vertical prefix assimilation, component numbering, the second vertical component sweep, and the second horizontal component sweep.

## 3.4.1 Horizontal Prefix Assimilation

Horizontal prefix assimilation is key to the scaling simulation. It embeds in  $S_v$  the effect of fusing connections in slices  $S_0, \ldots, S_{v-1}$ .  $\mathcal{R}$  accomplishes this task by strategically adding fusing connections to the slice. Let C be a component such that at least one bus in C is fused within the slice. The essence of horizontal prefix assimilation is to select for each such component C a unique vertical bus b that can be used to connect horizontal buses in component C. That is,  $\mathcal{R}$  fuses all horizontal buses

Figure 3.3: Pseudo-code for component determination.

known to be in component C (because of fusing to the left of the current slice) to vertical bus b within the current slice.

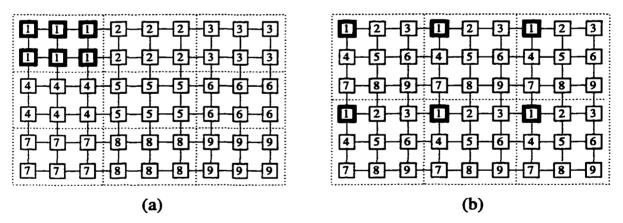

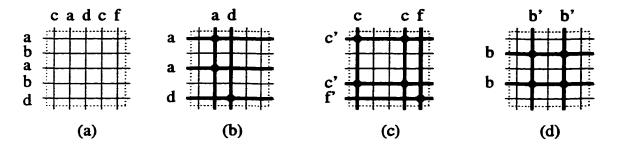

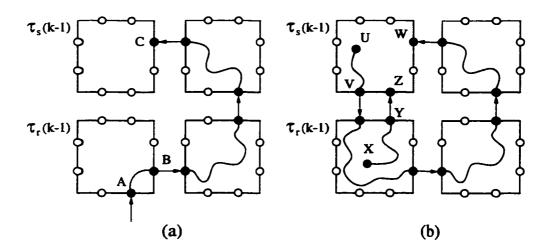

*Example:* Figure 3.4(a) shows the effect of fusings in previous slices on the current slice. Figure 3.4(b) shows how horizontal prefix assimilation embeds these fusings in the current slice by adding some fusing connections (shown circled).  $\mathcal{R}$  chooses vertical bus B to fuse the horizontal buses of component  $\{2, 6\}$  within the slice. Similarly,  $\mathcal{R}$  chooses vertical bus A for component  $\{3, 5\}$ . On the other hand, components  $\{4\}$  and  $\{1, 7\}$  have no fusings within the slice, so they need no extra fusings because nothing in the slice changes their component numbers.

The following is a description of variables and registers used during horizontal prefix assimilation.

Figure 3.4: An illustration of horizontal prefix assimilation: a) Components and fusing connections in a slice before horizontal prefix assimilation; b) Slice after horizontal prefix assimilation, where added fusing connections are circled.

Let the horizontal fusing index of horizontal bus k be the index of the rightmost vertical bus (if any) in  $W_{u,v}$  that is fused to bus k. Denote this index as hfi(k). Each processor connected to horizontal bus k holds this value (if any) in register hfi. Denote as hcomp(k) ( $vcomp(\ell)$ , resp.) the component number of horizontal bus k (vertical bus  $\ell$ , resp.). Each processor connected to horizontal bus k holds this value in register hcomp. Each processor in  $\mathcal{R}$  possesses a set of  $\frac{2N}{P}$  registers  $reg_m$ , where  $0 \leq m < \frac{2N}{P}$ . Register  $reg_m$ , in each processor of column  $\ell$ , where  $0 \leq \ell < P$ , holds the horizontal fusing index for component  $\frac{2N\ell}{P} + m$ .

Assume that each processor in  $\mathcal{R}$  holds the configuration of the processor it simulates in each of the  $\left(\frac{N}{P}\right)^2$  windows of  $\mathcal{Q}$ . Also, assume that each processor in  $\mathcal{R}$  holds the component numbers of its horizontal and vertical buses.

Horizontal prefix assimilation comprises four stages; each of these stages involves  $\frac{N}{P}$  iterations. As we explain them, we will illustrate key ideas through the example of Figure 3.4.

Stage 1. In this stage,  $\mathcal{R}$  determines by leader election (by priority resolution) the fusing index, hfi(k), for each horizontal bus k in  $\mathcal{S}_v$  and stores it in an appropriate processor and register. Stage 1 proceeds as follows.

for  $u \leftarrow 0$  to  $\frac{N}{P} - 1$  perform the following steps in window  $\mathcal{W}_{u,v}$ :

1. Each processor of  $\mathcal{R}$  configures its ports as cross-over.

2. In each row k of  $\mathcal{R}$ , each processor, writing to its horizontal bus, uses leader election (by priority resolution) to find its hfi(k) (if any).

3. In each row k of  $\mathcal{R}$ , the processor in column  $\ell$  that satisfies the relation  $\frac{2N\ell}{P} + m = comp(uP+k)$  for some m, where  $0 \le m < \frac{2N}{P}$ , stores hfi(k) (if any) in its register  $reg_m$ , overwriting any previously stored value.

$\mathcal{R}$  executes the leader election (by priority resolution) of Step 2 in  $O(\log P)$  time, and Steps 1 and 3 in O(1) time.  $\mathcal{R}$  performs the steps above in  $\frac{N}{P}$  windows, so it executes Stage 1 in  $O(\frac{N}{P}\log P)$  time.

*Example:* In Figure 3.4(a), buses 2, 3, and 5 have fusing connections within the slice. The fusing indices for these buses are B, B, and A, respectively. Registers responsible for storing the fusing indices of component  $\{2,6\}$  hold only index B. On the other hand, registers for component  $\{3,5\}$  hold indices A and B.

Stage 2. Stage 1 places the set of possible fusing indices for a component in processors of the same column. Stage 2 uses leader election (by priority resolution) to select one fusing index for each of the  $\frac{2N}{P}$  components per column of  $\mathcal{R}$ . Stage 2 proceeds as follows.

for  $m \leftarrow 0$  to  $\frac{2N}{P} - 1$  perform the following steps:

1. Each processor of  $\mathcal{R}$  configures its ports as cross-over.

2. For each vertical bus of  $\mathcal{R}$ , use leader election (by priority resolution) to select a processor (if any) that has a non-null fusing index in register  $reg_m$ .

3. The selected processor broadcasts such a fusing index (if any) to all the processors in its column. Each processor in the column stores this index (if any) in register  $reg_m$ , overwriting any previously stored value.

$\mathcal{R}$  performs  $\frac{2N}{P}$  leader elections (by priority resolution) in each column. Therefore,  $\mathcal{R}$  executes Stage 2 in  $O(\frac{N}{P} \log P)$  time.

*Example:* In Figure 3.4, this step selects index B (the only one available) for component  $\{2, 6\}$ . Although it is not clear in Figure 3.4, assume that this step chooses index A (from the set  $\{A, B\}$ ) for component  $\{3, 5\}$ .

Stage 3 This stage completes horizontal prefix assimilation by adding a fusing connection between a horizontal bus and the vertical bus given by the fusing index selected in Stage 2 for its component. Stage 3 proceeds as follows.

for  $u \leftarrow 0$  to  $\frac{N}{P} - 1$  perform the following steps in window  $\mathcal{W}_{u,v}$ :

1. Each processor of  $\mathcal{R}$  configures its ports as cross-over.

2. In each row k of  $\mathcal{R}$ , the processor in column  $\ell$  that satisfies the relation  $\frac{2N\ell}{P} + m = comp(uP+k)$  for some m, where  $0 \le m < \frac{2N}{P}$ , broadcasts the contents (if any) of register  $reg_m$  to all processors in its row.

3. Each processor reads the horizontal bus. If the column index of some processor matches the value on the bus, then that processor replaces the original port configuration of the processor it simulates in Q by a fusing connection.

$\mathcal{R}$  performs these operations in each window in constant time, so  $\mathcal{R}$  executes Stage 3 in  $O(\frac{N}{P})$  time.

*Example:* In Figure 3.4, notice the circled fusing connections on vertical bus B (to embed component  $\{2, 6\}$ ) and on vertical bus A (to embed component  $\{3, 5\}$ ).

Altogether,  $\mathcal{R}$  performs horizontal prefix assimilation in  $O\left(\frac{N}{P}\log P\right)$  time.

Because horizontal prefix assimilation exploits the continuity of horizontal and vertical buses, this method does not extend to a scaling simulation of the (unrestricted) R-Mesh. For example, in Figure 3.4, if bus B was broken between buses 2 and 6, then placing a fusing connection at the intersection of buses 6 and B no longer accurately embeds the effects of buses 2 and 6 being in the same component. Since both buses are in different components of  $\mathcal{R}$ , one of them will be assigned a wrong component number, and a new problem that arises is that the segment of bus B below the break should be in a different component than bus 6. Furthermore, the number of possible components would be  $O(N^2)$  instead of 2N.

### 3.4.2 Vertical Prefix Assimilation

Vertical prefix assimilation embeds in  $W_{u,v}$  the effects of bus fusings in upper windows,  $W_{0,v}, \ldots, W_{u-1,v}$ . The procedure is a special case of horizontal prefix assimilation that uses  $P \times P$  windows rather than  $N \times P$  slices.

Vertical prefix assimilation includes an initial stage, described below, that provisionally replaces the component number of each vertical bus in window  $W_{u,v}$  by another that is log *P*-bits long. This transformation maintains the size relation among the transformed component numbers. This stage proceeds as follows. Small Component Numbers This stage assigns a component number of length  $\log P$  bits to each of the P vertical buses in the window (the original component number is  $\log N + 1$  bits long). This stage consists of the following steps.

1. Each processor of  $\mathcal R$  configures its ports as cross-over.

2. The topmost processor in each column of  $\mathcal{R}$  broadcasts its component number to all processors in its column.

3. Each main diagonal processor of  $\mathcal{R}$  broadcasts the number it read to all processors in its row.

4. Each processor of  $\mathcal{R}$  compares these two numbers. If both are equal, then the processor sets a provisional fusing connection in its ports.

5. The first row processors of  $\mathcal{R}$ , writing on their vertical buses, use leader election (by priority resolution) to find the largest column index for each component. Call the resulting index as the *small component number*.

$\mathcal{R}$  executes Steps 1-4 in O(1) time and Step 5 in  $O(\log P)$  time (since the length of a column index  $\ell$  is  $\log P$  bits). Therefore,  $\mathcal{R}$  executes this stage in  $O(\log P)$  time.

From this point,  $\mathcal{R}$  applies a variation of horizontal prefix assimilation to window  $\mathcal{W}_{u,v}$ . We will describe vertical prefix assimilation by pointing out the differences with respect to horizontal prefix assimilation.

Notice that the prefix assimilation proceeds in a vertical fashion rather than horizontal. The number of possible small component numbers is at most P, so each processor in  $\mathcal{R}$  has only one register ( $reg_1$ ) (rather than the  $\frac{2N}{P}$  registers  $reg_m$ ) for storing the fusing index that corresponds to the small component number of its vertical bus. Stage 1 In this stage,  $\mathcal{R}$  determines by leader election (by priority resolution) the fusing index for each vertical bus  $\ell$  in  $\mathcal{W}_{u,v}$ . Assume that vertical bus  $\ell$  has small component number  $\alpha$ , where  $0 \leq \alpha < P$ . Then,  $\mathcal{R}$  stores the fusing index of column  $\ell$  (if any) in register  $reg_1$  of the processor located in row  $\alpha$  and column  $\ell$ .

Stage 2. The processors in each row  $\alpha$ , writing on their horizontal bus, use leader election (by priority resolution) to select one fusing index for all vertical buses with small component  $\alpha$ . Each processor in row  $\alpha$  stores this index in its register  $reg_1$ .

**Stage 3** This stage completes vertical prefix assimilation by adding the respective fusing connections as in horizontal prefix assimilation.

Component numbering also uses the small component number of each vertical bus.  $\mathcal{R}$  performs vertical prefix assimilation in  $O(\log P)$  time.

### 3.4.3 Component Numbering

The component numbering procedure assigns component numbers to buses (ports) in the current window. It incorporates the embedded effects of previous windows (gathered by the horizontal and vertical prefix assimilation procedures). The component numbering procedure works as follows.

Stage 1 Each processor of  $\mathcal{R}$  configures its ports according to the configuration of the processor it simulates in  $\mathcal{Q}$  (as altered by the prefix assimilation phases).

Stage 2 The processors at the top of each column, writing on the vertical buses, use leader election (by priority resolution) to find the vertical bus (column) with largest index in each component.

Stage 3 The processor at the top of a column with largest index in its component writes its original  $\log N + 1$  bits long component number on its vertical bus. Each processor reads its vertical (horizontal, resp.) bus and stores the value in its register *vcomp* (*hcomp*, resp.).

The values in registers *vcomp* and *hcomp* are the new component numbers for vertical and horizontal buses, respectively, at this point in the simulation.

$\mathcal{R}$  performs the leader election (by priority resolution) of Stage 2 in  $O(\log P)$  time and the remaining stages in O(1) time. Therefore,  $\mathcal{R}$  executes component numbering in  $O(\log P)$  time.

Remark: If  $\mathcal{R}$  used leader election (by priority resolution) to directly identify component numbers instead of Stages 2 and 3, then this would take  $O(\log N)$  time, as the component numbers in  $\mathcal{Q}$  could be  $O(\log N)$  bits long.

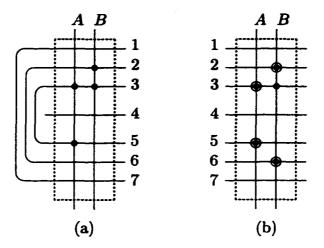

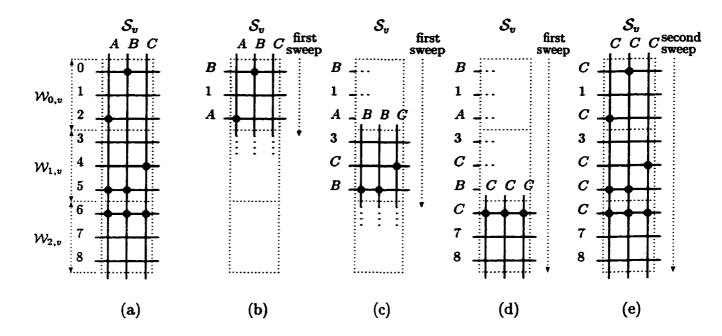

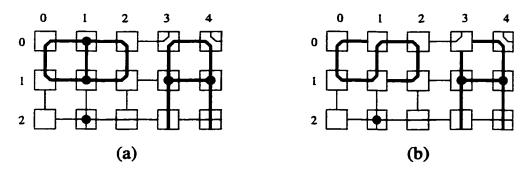

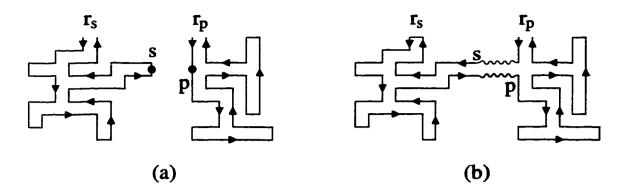

*Example:* Figure 3.5 illustrates component numbering. For simplicity, it is designed to not require vertical prefix assimilation. Figure 3.5(a) shows the configuration of  $S_v$  after horizontal prefix assimilation. After applying component numbering to window  $W_{0,v}$  (Figure 3.5(b)), all buses in the same component receive the same component number, buses 0 and 2 are numbered B and A, respectively. The same effect occurs in windows  $W_{1,v}$  and  $W_{2,v}$  (Figures 3.5(c),(d)). Note that as the first vertical sweep advances, component numbers of vertical buses change (from A, B, C in  $W_{0,v}$ , to B, B, C in  $W_{1,v}$ , and finally to C, C, C in  $W_{2,v}$ ). These changes do not manifest themselves in upper windows until the second vertical component sweep.

#### 3.4.4 Second Vertical Component Sweep

The second vertical component sweep propagates component numbers to each window in slice  $S_v$ . After the first vertical sweep, all buses in window  $W_{\frac{N}{2}-1,v}$  include the

Figure 3.5: Example of vertical component sweep: a) Original slice connections and component numbers; b-d) First vertical component sweep; e) Second vertical component sweep.

effect of all fusing connections in the slice  $S_v$  and all previous slices (see window  $W_{2,v}$  in Figure 3.5(d)). During the second vertical component sweep, vertical buses convey these updated component numbers to horizontal buses in each window (see Figure 3.5(e)). For simplicity, this sweep follows the same direction as the first vertical sweep, starting in window  $W_{0,v}$  and moving down till window  $W_{\frac{N}{P}-1,v}$ . Because vertical buses have the same component number in each window of the slice, the sweep over the windows can follow any order.  $\mathcal{R}$  performs the following steps.

for  $u \leftarrow 0$  to  $\frac{N}{P} - 1$  perform the following steps in window  $\mathcal{W}_{u,v}$ .

1. Each processor of  $\mathcal{R}$  configures its ports according to the configuration of the simulated window in  $\mathcal{Q}$ , plus the additional fusing connections obtained during the prefix assimilation sub-phases.

38

2. The topmost processor of each column writes its component number (the value of its register vcomp) on its vertical bus.

3. Each processor reads this value (if any) from its horizontal bus and stores it in its register *hcomp*, overwriting any previous value.

If some processor does not read any value in Step 3, then its horizontal bus is not fused to any vertical bus. In this case, each processor in that row retains the component number of its horizontal bus (in register hcomp) it had at the beginning of the simulation of the present slice.

$\mathcal{R}$  executes the second vertical component sweep in  $O\left(\frac{N}{P}\right)$  time.

#### 3.4.5 Second Horizontal Component Sweep

This phase propagates final component numbers to vertical buses in all slices in Q. After the first horizontal sweep, all vertical and horizontal buses in the rightmost slice,  $S_{\frac{N}{P}-1}$ , have the correct component number while vertical buses in other slices may not. Since each horizontal bus passes unbroken through all slices,  $\mathcal{R}$  simply copies the final component number of a horizontal bus from the rightmost slice.

For each slice  $S_v$  of Q (the order of this sweep does not matter, but for simplicity start the sweep in  $S_0$  and finish it in  $S_{\frac{N}{p}-1}$ ) follow the next procedure:

for  $u \leftarrow 0$  to  $\frac{N}{P} - 1$  perform the following steps in window  $\mathcal{W}_{u,v}$ .

1. Each processor of  $\mathcal{R}$  configures its ports according to the configuration of the simulated window  $\mathcal{W}_{u,v}$ , plus the additional fusing connections obtained during the prefix assimilation sub-phases.

2. The leftmost processor in each window writes its component number on its hori-

zontal bus, then each processor in the window reads its vertical bus and stores this value (if any) in its register *ucomp*, overwriting any previous value.