# Scaling Trends of Digital Single-Event Effects: A Survey of SEU and SET Parameters and Comparison With Transistor Performance

Daisuke Kobayashi<sup>©</sup>, Senior Member, IEEE

Abstract—The history of integrated circuit (IC) development is another record of human challenges involving space. Efforts have been made to protect ICs from sudden malfunctions due to single-event effects (SEEs). These effects are triggered by only a single strike of particle radiation, such as an  $\alpha$ -ray or cosmic ray, originating from our solar activity and galactic events including supernovas. This article explores how SEEs have evolved along with the progress in complementary metal-oxide-semiconductor (CMOS) digital IC technology, or device scaling, from the early micrometer-scale generations to the current nanometerscale generations. For this purpose, focusing on basic digital elements, that is, inverters and static random access memories (SRAMs), this study collected more than 100 sets of data on four characteristic parameters of single-event upsets (SEUs) and single-event transients (SETs), both of which are undesired flips in digital logic states. The results show that all the examined parameters, such as the SEU critical charge, decrease with the device feature size. Analysis involving structure classification, such as bulk versus silicon-on-insulator (SOI) substrates and planar versus fin channels, reveals relationships between the examined SEE parameters and other device features such as the power supply voltage. All the data collected in this survey are explicitly given in tables for future exploration of IC reliability.

Index Terms—Error analysis, ion radiation effects, neutron radiation effects, semiconductor device reliability, single-event transients (SETs), single-event upsets (SEUs), soft errors, static random-access memories (SRAMs).

### I. INTRODUCTION

**R** ADIATION causes a variety of reliability problems in integrated circuits (ICs). Even a single strike of particle radiation such as an  $\alpha$ -ray can lead to a catastrophic malfunction. A single-event effect (SEE) is such an undesired effect due to a single strike of particle radiation. SEEs have

Manuscript received September 16, 2020; revised November 30, 2020; accepted December 6, 2020. Date of publication December 14, 2020; date of current version February 16, 2021. This work was supported in part by the Japan Society for the Promotion of Science (JSPS) through JSPS KAKENHI under Grant JP20H02217. This article was presented in part at Section I, "Basics of Single Event Effect Mechanisms and Predictions," in the 2019 IEEE Nuclear and Space Radiation Effects Conference (NSREC) Short Course, San Antonio, TX, July 8, 2019.

The author is with the Institute of Space and Astronautical Science (ISAS), Japan Aerospace Exploration Agency (JAXA), Sagamihara 252-5210, Japan, also with the Research and Development Directorate, JAXA, Tsukuba 305-8505, Japan, and also with the Department of Space and Astronautical Science, School of Physical Sciences, The Graduate University for Advanced Studies, SOKENDAI, Hayama 240-0193, Japan (e-mail: d.kobayashi@isas.jaxa.jp).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TNS.2020.3044659.

Digital Object Identifier 10.1109/TNS.2020.3044659

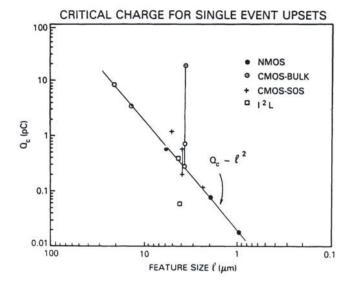

Fig. 1. Scaling trend revealed by Petersen et al. [4]. ©1982, IEEE.

been serious for more than half a century [1], causing actual financial losses in both space and terrestrial IC systems.

Understanding the evolution of SEEs requires deep knowledge of the evolution of IC devices, including even parasitic elements, which are byproducts of the intended purposes of target devices. Without advance notice, an incidence of particle radiation deposits energy inside an IC chip along its track. This forcible injection of energy wrongly activates not only target devices but also parasitic elements, even though parasitic elements are originally designed not to be activated during normal operation. In particular, knowledge of device miniaturization or scaling, which is associated with Moore's law [2] and Dennard's rules [3], is important because of its crucial role in the progress of digital IC technology. In fact, the history of SEEs started from a theoretical discussion of their influence on the progress of device scaling [1].

In 1982, which was about five years after the first observations of SEEs in space [5] and on the ground [6], Petersen *et al.* [4] surveyed the literature on one type of SEE, a single-event upset (SEU), which is an undesired bit flip of digital memory caused by a single strike of particle radiation. They examined the minimum amount of charge, called the critical charge ( $Q_C$ ), that is necessary for an SEU in dynamic and

TABLE I

EXAMPLES OF PREVIOUS WORKS RELATED TO DEVICE SCALING EFFECTS ON SEES

| Ref. | Year | Fe             | ature size | (1)  |     |              | Structure (see Table III)                                | SEE      | Note                      |

|------|------|----------------|------------|------|-----|--------------|----------------------------------------------------------|----------|---------------------------|

| [4]  | 1982 | 21 15 6 5      | 4.5 4      | 2.5  | 2   | 1            | Bulk-Planar*, SOI-Planar <sup>‡</sup> , I <sup>2</sup> L | SEU      |                           |

| [7]  | 1982 | 4 3 2 1        | 0.8 0.6    | 0.4  |     |              | Bulk-Planar*, SOI-Planar <sup>‡</sup>                    | SEU      | Based on scaling rule     |

| [13] | 1982 | 2 1            |            |      |     |              | Bulk-Planar (DRAM)                                       | SEU      |                           |

| [14] | 1984 | 3.6 2.9 2.7 1. | 3          |      |     |              | SOI-Planar <sup>‡</sup>                                  | SEU      |                           |

| [15] | 1987 | 2 1            |            |      |     |              | Bulk-Planar                                              | SEU      |                           |

| [16] | 1990 | 2 1.8 1.6 1.:  | 5 1.25 1   |      |     |              | Bulk-Planar                                              | SEL      |                           |

| [17] | 1996 | 2 1 0.5        |            |      | (in | μm)          | Bulk-Planar                                              | SEU      |                           |

| [18] | 2000 | 800 600 350 10 | 0          |      | (in | nm)          | Bulk-Planar                                              | SEU      | Based on scaling rule?    |

| [19] | 2003 | 280 250 210 20 | 0 180      |      |     |              | Bulk-Planar                                              | SEU      |                           |

| [20] | 2002 | 500 350 250 18 | 0 130 90   |      |     |              | Bulk-Planar                                              | SEU      |                           |

| [21] | 2002 | 350 280 180    |            |      |     |              | Bulk-Planar                                              | SEU      |                           |

| [22] | 2002 | 600 350 250 18 | 0 130 100  | 70   | 50  |              | Bulk-Planar                                              | SEU      | Based on scaling rule     |

| [23] | 2003 | 250 180 130 90 | 65         |      |     |              | Bulk-Planar                                              | SEU      |                           |

| [24] | 2004 | 180 130 90     |            |      |     |              | Bulk-Planar, SOI-Planar                                  | SEU      |                           |

| [25] | 2005 | 180 130 90 65  | i          |      |     |              | Bulk-Planar                                              | SEL      |                           |

| [26] | 2005 | 250 180 130 90 | 65         |      |     |              | Bulk-Planar                                              | SEL      |                           |

| [27] | 2006 | 180 130 90     |            |      |     |              | Bulk-Planar                                              | SEU      |                           |

| [28] | 2009 | 180 130 90 65  | 45         |      |     |              |                                                          | SEU      |                           |

| [29] | 2010 | 250 180 130 90 | 65 45      | 32   | 22  |              | Bulk-Planar                                              | SEU      | Based on scaling rule     |

| [30] | 2010 | 130 90 65      |            |      |     |              | Bulk-Planar                                              | SET      |                           |

| [31] | 2011 | 250 220 210 18 | 0 170 160  | 150  | 140 | $\leftarrow$ | Bulk-Planar*                                             | SEU      | Collection of error rates |

|      |      | → 130 120 11   | 0 100 100  | 5 96 | 95  | $\leftarrow$ |                                                          |          | from various vendors      |

|      |      | → 92 90 80     | 70 65      | 45   | 40  |              |                                                          |          |                           |

| [32] | 2011 | 250 180 90 65  | i          |      |     |              | Bulk-Planar                                              | SEU, SET |                           |

| [33] | 2011 | 65 55 45 40    | 32 22      | 16   |     |              | Bulk-Planar                                              | SEU      | Based on scaling rule     |

| [12] | 2011 | 90 73 72 65    | 63 51      | 50   |     |              | Bulk-Planar (Flash)                                      | SEU      |                           |

| [34] | 2013 | 350 250 180 13 | 0 90 65    | 40   | 28  |              | Bulk-Planar                                              | SEU      |                           |

| [35] | 2013 | 250 180 130 90 | 65 45      | 32   | 28  | 14           | Bulk-Planar, SOI-Planar                                  | SEU      | Comparison with [4]       |

| [36] | 2013 | 45 32          |            |      |     |              | SOI-Planar                                               | SET      |                           |

| [37] | 2014 | 65 40 28       |            |      |     |              | Bulk-Planar                                              | SEU      |                           |

| [38] | 2015 | 180 130 90 65  | 45 32      | 22   | 14  |              | Bulk-Planer, Bulk-Fin                                    | SEU, SET |                           |

| [11] | 2017 | 500 120 90     |            |      |     |              | SiGe BiCMOS                                              | SET      |                           |

| [39] | 2018 | 14 10          |            |      |     |              | Bulk-Fin                                                 | SEU      |                           |

| [40] | 2018 | 16 7           |            |      |     |              | Bulk-Fin                                                 | SEU      |                           |

<sup>\*</sup> Includes DRAMs.

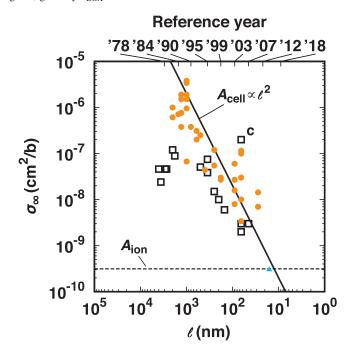

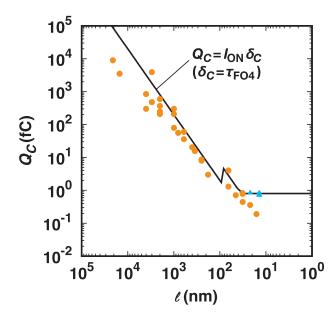

static random access memories (DRAMs and SRAMs). The energy injected by radiation creates a huge amount of charge. Once this charge exceeds  $Q_C$ , the struck memory exhibits an upset (see Section II for details). As shown in Fig. 1, Petersen *et al.* [4] revealed a scaling trend of  $Q_C = 0.023l^2$ , where l denotes the feature size of the device. In the same year, Pickel revealed a similar trend,  $Q_C = 0.85(l/4)^{1.5}$ , in his own work [7]. As listed in Table I,<sup>1</sup> since those pioneering studies, many other studies have investigated the impacts of device scaling on SEEs, including SEUs, single-event transients (SETs), and single-event latch-ups (SELs). These previous studies have tested a wide range of IC structures, from the standard complementary metal-oxide-semiconductor (CMOS) structure

to state-of-the-art structures such as a SiGe bipolar CMOS (BiCMOS) [11] and flash memory [12]. To date, however, no attempt has been made to examine SEEs across all generations, from the early micrometer-scale generations to today's nanometer-scale generations.

Hence, the aim of this study is to explore the whole history of SEE evolution from the viewpoint of device scaling. For this purpose, as summarized in Table II, this study collected data on four key parameters for SEUs and SETs, both of which are particularly serious in the core of CMOS digital IC systems, where device scaling plays its crucial role. In this regard, other SEEs such as SELs and single-event functional interrupts (SEFIs) are not addressed in this study. Together with reasons for not addressing these SEEs, Section II gives detailed information about the examined SEEs (SEUs and SETs) and parameters, as well as the data collection and

<sup>&</sup>lt;sup>‡</sup> Silicon-On-Sapphire (SOS) structures were also examined. For simplicity, the present study classifies SOS structures as Silicon-On-Insulator (SOI) structures (see the text).

<sup>&</sup>lt;sup>1</sup>During the course of the review of this article, further works were presented [8]–[10].

analysis procedures used in this study. The bulk of this article consists of Section III, which shows how the parameters have evolved along with l. That section also seeks the physical mechanisms behind the revealed evolution, through comparison with various device features such as the power supply voltage ( $V_{\rm DD}$ ). Note that all the collected data are given in tabular form for future study.

#### II. METHOD

#### A. Tested SEEs and Devices

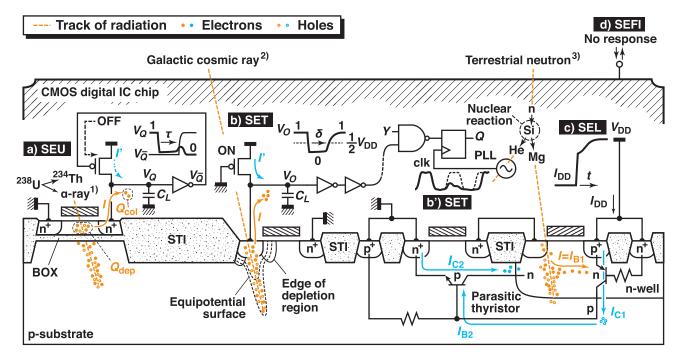

As illustrated in Fig. 2, CMOS digital ICs typically suffer from four kinds of SEEs: (a) SEUs, (b and b') SETs, (c) SELs, and (d) SEFIs. They all originate from charge injected by an incidence of particle radiation such as

- 1)  $\alpha$ -rays: He nuclei from radioactive materials [41];

- galactic cosmic rays (GCRs): charged nuclei originating in space, including heavy ions such as Fe nuclei [42]; and

- terrestrial neutrons: constituents of terrestrial cosmic rays resulting from interactions between GCRs and Earth's atmosphere [41].

When entering Si, for example, a 4-MeV  $\alpha$ -ray emitted from  $^{238}$ U loses 150 keV of energy during its first 1  $\mu$ m of passage [6]. Ionization consumes 99.9% of the energy.  $\alpha$ -rays can excite electrons through Coulomb force because of their charge of +2q, where q represents the elementary charge. This ionization process deposits electron–hole pairs (ehps) with as much charge as 6.7 fC, which is obtained by dividing 150 keV by the pair-creation energy of 3.6 eV/ehp or 22.5 keV/fC [43]–[45]. Moreover, although terrestrial neutrons are not charged, they can cause the above-mentioned SEEs through the same charge-deposition process, but with additional nuclear reactions that create energetic nuclei.

Among the four SEEs, this study focuses on SEUs in SRAMs [Fig. 2(a)] and SETs in inverters [Fig. 2(b)]. These are continuous or instant flips in digital logic states. This study selected SRAMs and inverters as the target logic elements because they are the most basic building blocks of CMOS digital ICs, whose performance is crucially influenced by device scaling and often characterized in the literature to discuss the benefits of new ideas. In this regard, although CMOS digital IC circuitry is sometimes modified by using additional circuit elements for increasing SEE hardness (e.g., a dual interlocked storage cell or DICE [46]), this study does not concern such radiation hardening by design (RHBD). Instead, unless otherwise specified, it concentrates on standard (non-RHBD) SRAM cells and inverters to investigate the native responses of SEEs to device scaling.

Note that although this study focuses only on SEUs and SETs in the basic digital elements, it does not lessen the significance of the other SEEs. As illustrated in Fig. 2(b'), phase-locked loops (PLLs) are sensitive to SETs, which typically manifest themselves in analog or frequency domains with effects such as severe jitter and signal losses [47]–[49]. This PLL SET is not addressed in this study because of the small amount of literature data. An anomalous increase in current caused by an erroneous activation of parasitic thyristors, that

TABLE II

TESTED SEES AND PARAMETERS

|     |          |                               | Parameter                                                                                                           |

|-----|----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------|

| SEE | Device   | Symbol                        | Description                                                                                                         |

| SEU | SRAM     | $Q_C \ L_T \ \sigma_{\infty}$ | Critical charge (fC) Threshold LET <sup>†</sup> (MeVcm <sup>2</sup> /mg) Saturated cross section (cm <sup>2</sup> ) |

| SET | Inverter | δ                             | Duration of digital flip (ps)                                                                                       |

$<sup>\</sup>dagger$  Linear Energy Transfer, denoted by L in the text.

is, an SEL [Fig. 2(c)], is still significant and exhibits complex responses to device design. As suggested in [50], SEL depends on parameters that do not always shrink along with device scaling, such as the dimension of wells and the depth of shallow-trench isolation (STI). Hence, SEL is not addressed here—A literature survey, however, suggests that CMOS digital ICs generally become less sensitive to SEL along with the scaling of  $V_{\rm DD}$  [51, Fig. 39]. CMOS digital ICs also suffer from SEFIs [Fig. 2(d)], that is, interruptions in operation, such as a reset or lock-up while running a task [52]. SEFI is known to be caused by SEUs, SETs, and SELs in IC control blocks. Although it is interesting to see how SEFI has evolved, it is not addressed here because of the complexity that originates from the variety of tested circuitry. Furthermore, although not shown in Fig. 2, single-event displacement damage might soon become significant. As typified by nuclear reactions induced by neutrons, radiation transfers energy to matter through nonionizing processes, such as knockout, that cause displacement damage. Such single-event displacement damage has already been observed in various electronic devices (see [53] and references therein), but so far, it has been negligible in the logic elements of CMOS digital ICs; hence, this study ignores it. A very recent simulation study [54] predicted, however, that terrestrial neutrons may cause significant impacts on the electrical characteristics of transistors in the 6-nm generation. In this regard, note also that a large-scale study on simulating single-event displacement damage has been conducted in recent years [55]-[57].

## B. Tested Parameters

As explained above, this article investigates SEUs in SRAMs and SETs in inverters from the viewpoint of device scaling. Here, brief descriptions are given for the tested phenomena and parameters.

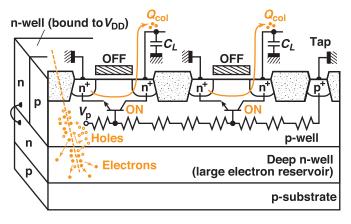

1) Single-Event Upsets: As conceptually illustrated in Fig. 2(a), which concerns a cross-coupled inverter latch in an SRAM cell, charge collection results in a nonzero current I, leading to an undesired voltage change at the output of the struck inverter  $(V_Q)$ . In this example, particle radiation strikes an OFF-state n-type MOS transistor, hereinafter abbreviated as NMOS (along with PMOS for the counterpart p-type transistor). The struck NMOS collects electrons (I < 0), and thus  $V_Q$  drops from its original level at  $V_{\rm DD}$  or logic 1. After propagating through the succeeding inverter, this  $V_Q$  drop turns off the pull-up PMOS connected to the struck NMOS.

Fig. 2. Conceptual drawing of SEEs in a CMOS digital IC. A hybrid substrate structure (bulk+SOI) is assumed for illustrative purposes.

This feedback prevents the PMOS from providing current for recovery (I'). As a result, the memory state is completely flipped and becomes stable in the wrong state of logic 0 (see [58] for more details). This study investigates the following two parameters, which are commonly used to describe the threshold for this flip:

- $Q_C$  The minimum amount of charge required for an SEU, or the critical charge. This is typically gauged in terms of  $Q_{col}$ , the amount of charge collected at the drain terminal of a struck transistor (see also Section III-A).

- $L_T$  The minimum linear energy transfer (LET or L) necessary for an SEU, often called the threshold LET. The value of L describes the ability of radiation to deposit energy (or charge) along its track. This value is usually given in a charge-based unit (fC/nm) or an energy-based unit normalized by the target matter's density (MeVcm²/mg). Unless otherwise specified, this study uses the latter energy-based unit; when needed, the former charge-based unit is converted with a conversion factor for Si: 1 fC/nm = 100 MeVcm²/mg.

The study also investigates the following parameter that indicates sensitive locations in an SRAM cell:

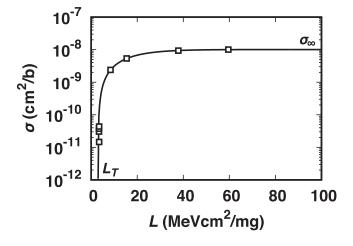

$\sigma_{\infty}$  Saturated cross section. In general, the cross section  $(\sigma)$  describes the sensitive area of a tested device and is often estimated through the following relationship when the device is a memory:

$$\sigma = \frac{U}{fM} \tag{1}$$

where U, f, and M denote the number of upsets observed, the total fluence of particle radiation during the irradiation, and the total number of memory cells

Fig. 3. Measured evolution of  $\sigma$  in an SOI-Planar SRAM as a function of L [59]. The symbols represent measurement results obtained from (1), while the line represents the best-fit Weibull function,  $\sigma = \sigma_{\infty} \exp\left[-\{(L - L_T)/W\}^S\right]$ , where W and S are arbitrary fitting parameters.

exposed to radiation, respectively. As shown in Fig. 3, in general,  $\sigma$  abruptly develops at  $L_T$  and saturates to  $\sigma_{\infty}$  as L increases. This study measures  $\sigma_{\infty}$  in the units of cm<sup>2</sup>/b, where b denotes bit, with a proper unit conversion when necessary.

2) Single-Event Transients: When exposed to particle radiation [Fig. 2(b)], an inverter exhibits an instantaneous change in its output voltage ( $V_O$ ). Unlike SRAM SEUs that rely on a self-shutoff mechanism,  $V_O$  returns to the original level after some time, because the struck transistor's counterpart, for example, the pull-up PMOS in the figure, continues to feed I'. Then, however, the resultant glitch or transient false state, also called "digital SET (DSET)," can propagate through the

TABLE III

FOUR CATEGORIES OF CMOS DEVICE STRUCTURES EXAMINED IN THIS

STUDY

|         | Substrate     |                        |  |  |  |  |  |

|---------|---------------|------------------------|--|--|--|--|--|

| Channel | Bulk          | $\mathrm{SOI}^\dagger$ |  |  |  |  |  |

| Planar  | Bulk-Planar • | SOI-Planar □           |  |  |  |  |  |

| Fin*    | Bulk-Fin 🔺    | SOI-Fin 💠              |  |  |  |  |  |

- † Includes similar substrate structures such as

- \* Includes similar three-dimensional channel structures such as a tri-gate.

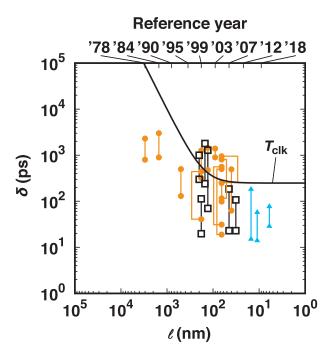

chains of logic gates and finally overwrite the bit information stored in flip-flops (FFs) at the ends (see [60] for more details). Hence, this study investigates the following parameter because of its importance for the propagation and latch probabilities [61]:

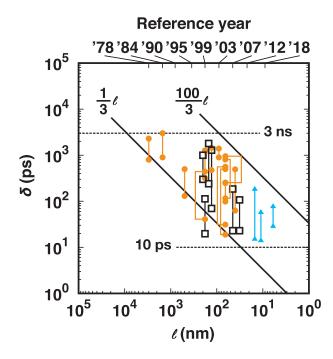

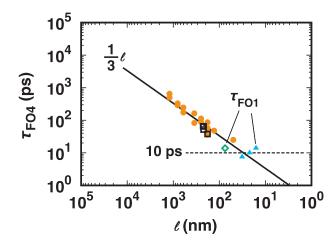

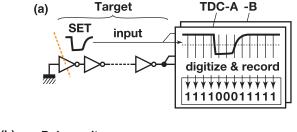

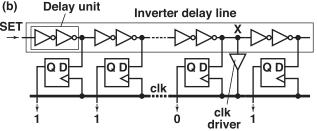

$\delta$  The temporal width of a false state, specifically the SET pulsewidth measured at a logic threshold (when needed, this study uses  $V_{\rm DD}/2$  as the threshold level). Because  $\delta$  usually exhibits a range, this study investigates its maximum and minimum values. Moreover, the study makes no distinction between  $\delta$  before and after propagation, although it can change while propagating through a logic chain [62].

#### C. Data Collection and Analysis

The four SEE parameters described above were collected from articles already published. The parameter values were simply copied when given numerically in the reference articles. When not given numerically, they were extracted from figures. In either case, this data collection process did not attempt to assess the validity of the collected values. In other words, the values were not subjected to any correction or selection process. Hence, the analysis in Section III mainly focuses on global trends in the groups of collected values.

To investigate the evolution of the SEE parameters, l values were also recorded from the reference articles. When an article did not explicitly give the value l, the gate length was used instead. Additional information such as the test conditions and device structures was also recorded for analysis. The device structures were classified into four categories as summarized in Table III, consisting of  $2 \times 2$  combinations of channel and substrate structures. Although the silicon-on-insulator (SOI) substrates can be categorized as fully depleted (FD) and partially depleted (PD) SOI substrates, such further categorization was not applied because of the limited amount of data. Instead, the thicknesses of the SOI and buried oxide (BOX) layers ( $d_{SOI}$ and  $d_{\text{BOX}}$ , respectively) were collected whenever possible. Regarding the use of terms for structure classification, note that, for example, when the term of "Bulk" is used alone (e.g., "Bulk SRAM"), it includes both Bulk-Planar and Bulk-Fin SRAMs. The symbols in this table are consistently used in the following section's figures.

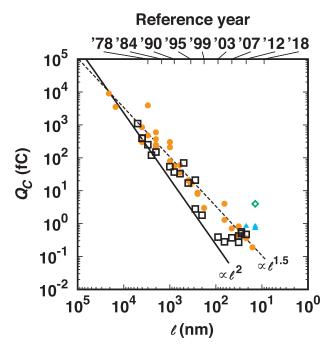

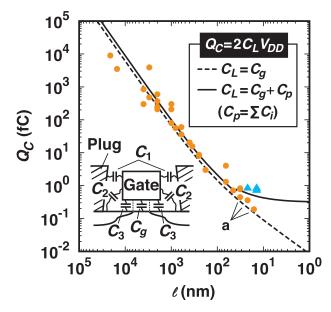

Fig. 4. Evolution of  $Q_C$ . The solid and dashed lines represent the trends reported by Petersen *et al.* [4] and Pickel [7], respectively.

#### III. RESULTS AND DISCUSSION

#### A. SRAM $Q_C$

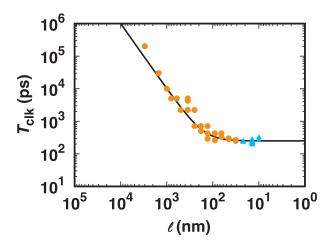

Tables IV and V list SRAM  $Q_C$  values collected from the literature. Fig. 4 shows a graphical representation of this collection, displaying the evolution of  $Q_C$  as a function of l. In general (regardless of the categories of device structures),  $Q_C$  constantly decreases with l across five orders of magnitude. Interestingly, this scaling trend seemingly halts at  $Q_C \approx 0.5$  fC. Note that the top axis in this figure provides a reference timescale that corresponds to the progress of Intel logic technologies, summarized in Table VI [84].

Fig. 4 shows that the data conform well overall to the trends predicted by Petersen *et al.* [4] and Pickel [7] in 1982. A closer look suggests that Petersen's  $l^2$  trend provides the lower boundary of all the data, consisting mainly of the data for SOI-Planar SRAMs. On the other hand, the Bulk-Planar data spread around Pickel's  $l^{1.5}$  trend. Note that although Pickel investigated trends for both SOI-Planar and Bulk-Planar SRAMs, Fig. 4 presents only the Bulk-Planar trend for illustrative purpose (see also the last paragraph of this section).

The following analysis suggests that the revealed trends depend mainly on the scaling trends of  $V_{\rm DD}$  and load capacitance ( $C_L$ ), where  $C_L$  represents the total capacitance of the inverter output node in an SRAM cell. As explained in Section II-B1, an SEU is triggered by a  $V_Q$  drop due to undesired dissipation of signal charge, that is,  $C_L V_{\rm DD}$ . Hence,  $Q_C$  is widely expressed as  $Q_C = aC_L V_{\rm DD}$ , with the constant a varying across articles. This study uses a = 2 according to [85], which models  $Q_C$  as follows:

$$Q_C = C_L V_{\rm DD} + I_{\rm ON} \tau. \tag{2}$$

The second term on the right-hand side corresponds to additional charge due to the recovery current I'. In (2), this

TABLE IV SEU  $Q_C$  Values Collected From the Literature for the Bulk Structures (see Table V for SOI)

| l (nm) | $Q_C$ (fC) | ${Q_{ m col}}^\dagger$ | Exp.* | Structure   | Reference       | Note <sup>b</sup>                    |

|--------|------------|------------------------|-------|-------------|-----------------|--------------------------------------|

|        |            |                        |       | Bulk-Planar |                 |                                      |

| 21 000 | 9000       | 1                      |       | •           | [4, Table I]    | Theory: $0.8C_L V_{DD}$ [63]         |

| 15 000 | 3500       | 1                      |       | •           | [4, Table I]    | Theory: $0.8C_LV_{DD}$ [63]          |

| 4000   | 300        |                        | 1     | •           | [4, Table I]    | $L_T d_{\mathrm{DR}}$ [64]           |

| 4000   | 840        | 1                      |       | •           | [7, Fig. 4]     | SPICE                                |

| 3000   | 478        | 1                      |       | •           | [7, Fig. 4]     | <b>↓</b>                             |

| 2000   | 249        | 1                      |       | •           | [7, Fig. 4]     | ↓ Miniaturized from 4000 nm          |

| 1000   | 78.8       | 1                      |       | •           | [7, Fig. 4]     | ↓ through a scaling rule             |

| 800    | 55.4       | 1                      |       | •           | [7, Fig. 4]     | <b>↓</b>                             |

| 600    | 36.0       | 1                      |       | •           | [7, Fig. 4]     | <b>↓</b>                             |

| 400    | 20.3       | 1                      |       | •           | [7, Fig. 4]     | 4                                    |

| 3000   | 3900       | 1                      |       | •           | [65, Fig. 1]    | SPICE; R: 3600-4250 fC               |

| 2000   | 600        | 1                      |       | •           | [65, Fig. 2]    | SPICE                                |

| 2000   | 210        | 1                      |       | •           | [66, Table III] | Theory: $C_L V_{DD}$ ; $l$ from [67] |

| 2000   | 360        | 1                      |       | •           | [68, Fig. 3]    | SPICE                                |

| 1500   | 300        | 1                      |       | •           | [69, Table 1]   | SPICE                                |

| 1000   | 210        | 1                      |       | •           | [70]            | SPICE                                |

| 250    | 8          | 1                      |       | •           | [71, Table II]  | SPICE                                |

| 180    | 3          | 1                      |       | •           | [71, Table II]  | SPICE                                |

| 600    | 60         | 1                      |       | •           | [72, Fig. 2]    | TCAD; R: 60–98 fC                    |

| 350    | 16         | 1                      |       | •           | [72, Fig. 2]    | TCAD; R: 16–22 fC                    |

| 250    | 8.6        | 1                      |       | •           | [72, Fig. 2]    | TCAD; R: 8.6–15 fC                   |

| 65     | 4.0        | 1                      |       | •           | [73, Table I]   | SPICE                                |

| 65     | 1.3        | 1                      |       | •           | [33, Table I]   | SPICE                                |

| 45     | 0.71       | 1                      |       | •           | [33, Table I]   | $\downarrow$                         |

| 32     | 0.44       | 1                      |       | •           | [33, Table I]   | ↓ Miniaturized from 65 nm            |

| 22     | 0.36       | 1                      |       | •           | [33, Table I]   | ↓ through a scaling rule             |

| 16     | 0.19       | 1                      |       | •           | [33, Table I]   | Ą                                    |

| 32     | 0.83       | 1                      |       | •           | [74, Table I]   | SPICE                                |

| 32     | 0.78       | 1                      |       | •           | [75, Table IV]  | TCAD+SPICE                           |

|        |            |                        |       | Bulk-Fin    |                 |                                      |

| 22     | 0.83       | 1                      |       | <b>A</b>    | [74, Table I]   | SPICE                                |

| 14     | 0.71       | 1                      |       | <b>A</b>    | [74, Table I]   | SPICE                                |

| 14     | 0.73       | 1                      |       | <b>A</b>    | [75, Table IV]  | TCAD+SPICE                           |

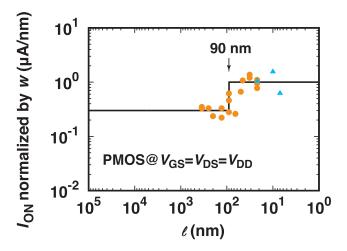

additional charge was estimated from the time taken for the  $V_Q$  drop to be latched  $(\tau)$  and the ON-current  $(I_{ON})$ , that is, the saturated drain current in the ON-state transistor when  $|V_{\rm GS}| = |V_{\rm DS}| = V_{\rm DD}$ , where  $V_{\rm GS}$  and  $V_{\rm DS}$  represent the gateand drain-source voltages, respectively. This study further assumes that  $\tau$  is given by an inverter propagation delay model as  $0.79C_LV_{\rm DD}/I_{\rm ON}$  [86], thus giving  $a\approx 2$ .

Fig. 5 compares  $2C_LV_{DD}$  with the literature data for Bulk SRAMs. The dashed line indicates  $2C_LV_{DD}$ , where  $C_L$  is assumed to be the same as the intrinsic gate capacitance of the succeeding inverter

$$C_g = 2 \frac{\varepsilon_{\text{OX}}}{d_{\text{OX}}} lw. \tag{3}$$

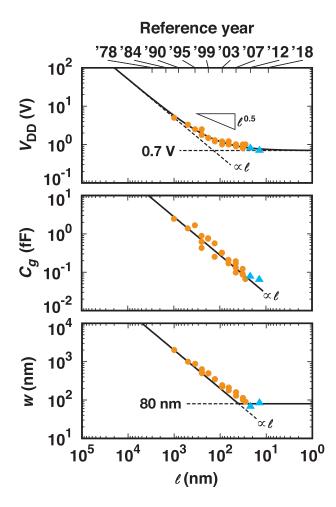

Here  $\varepsilon_{OX}$ ,  $d_{OX}$ , and w represent parameters of a single transistor in a cell, that is, the gate oxide film's permittivity, its thickness, and the gate width, respectively. The factor of 2 is used for estimating the capacitance of the inverter input. The transistor parameters were extracted from a survey of Bulk SRAM cells, as shown in Fig. 6 [87], [88], and modeled as follows:

$$V_{\rm DD} = 0.005l + 0.7 \tag{4}$$

$$C_g = 0.003l \tag{5}$$

$$w = \begin{cases} 2l, & \text{for } l \ge 40 \text{ nm}; \\ 80, & \text{for } l < 40 \text{ nm}. \end{cases}$$

(6)

$<sup>^\</sup>dagger$   $Q_C$  was defined by  $Q_{\rm col}$ . The other values were defined by  $Q_{\rm dep}$ . \*  $Q_C$  was determined experimentally. The other values were obtained by theory or simulation (see the "Note" column: "SPICE" indicates that the analysis used a circuit simulator, while "TCAD" indicates a numerical device simulator).

$<sup>^{\</sup>flat}$  Some papers reported a range of  $\mathcal{Q}_{\mathcal{C}}$  values. For those cases, the second column lists a representative value, while the "Note" column gives the range, denoted by "R:".

| TABLE V                                                                                       |

|-----------------------------------------------------------------------------------------------|

| SEU $Q_C$ Values Collected From the Literature for the SOI Structures (see Table IV for Bulk) |

| l (nm) | $Q_C$ (fC) | $Q_{ m col}^{\dagger}$ | Exp.* | Structure  | Reference      | Note♭                   |                         |                                                    |

|--------|------------|------------------------|-------|------------|----------------|-------------------------|-------------------------|----------------------------------------------------|

|        |            |                        |       | SOI-Planar |                | $d_{\mathrm{SOI}}$ (nm) | $d_{\mathrm{BOX}}$ (nm) |                                                    |

| 5000   | 1100       |                        | 1     |            | [4, Table I]   | 500                     |                         | $L_T d_{SOI}$ [64]; see Table VIII                 |

| 4000   | 400        |                        | 1     |            | [4, Table I]   | 550                     |                         | $L_T d_{SOI}$ [76]; see Table VIII; R: 200–600 fC  |

| 2500   | 120        |                        | 1     |            | [4, Table I]   | 500                     |                         | $L_T d_{SOI}$ [77]; see Table VIII; $l = 2000$ nm? |

| 4000   | 390        | 1                      |       |            | [7, Fig. 6]    | 400                     |                         | SPICE                                              |

| 3000   | 251        | 1                      |       |            | [7, Fig. 6]    | $\downarrow$            |                         | $\downarrow$                                       |

| 2000   | 149        | 1                      |       |            | [7, Fig. 6]    | $\downarrow$            |                         | ↓ Miniaturized from 4000 nm                        |

| 1000   | 53.8       | 1                      |       |            | [7, Fig. 7]    | $\downarrow$            |                         | ↓ through a scaling rule                           |

| 800    | 37.0       | 1                      |       |            | [7, Fig. 7]    | $\downarrow$            |                         | $\downarrow$                                       |

| 600    | 32.9       | 1                      |       |            | [7, Fig. 6]    | $\downarrow$            |                         | $\downarrow$                                       |

| 400    | 17.1       | 1                      |       |            | [7, Fig. 7]    | Ą                       |                         | Ą                                                  |

| 500    | 70         |                        | 1     |            | [78]           | 85                      | 400                     | $L_T d_{SOI}$ ; see Table VIII                     |

| 280    | 21         | 1                      |       |            | [79, Fig. 4]   | 100                     | 500                     | TCAD+SPICE; R: 21–42 fC                            |

| 280    | 2.8        |                        |       |            | [79]           | 100                     | 500                     | TCAD+SPICE                                         |

| 200    | 1.8        |                        | 1     |            | [71, Table II] | 50                      | 100                     | $L_T d_{SOI}$ ; $d_{SOI}$ , $d_{BOX}$ from [59]    |

| 90     | 0.39       |                        |       |            | [80, Table I]  |                         |                         | TCAD                                               |

| 65     | 0.28       |                        |       |            | [80, Table I]  |                         |                         | TCAD; Exp. R: 0.38-0.47 fC                         |

| 45     | 0.37       |                        |       |            | [80, Table I]  |                         |                         | TCAD                                               |

| 32     | 0.27       |                        |       |            | [80, Table I]  |                         |                         | TCAD; Exp. R: 0.27-0.36 fC                         |

| 32     | 0.42       |                        |       |            | [80, Table I]  |                         |                         | TCAD; Exp. R: 0.53-0.69 fC                         |

| 22     | 0.47       |                        |       |            | [80, Table I]  |                         |                         | TCAD                                               |

| 28     | 0.56       | 1                      |       |            | [81, Table IV] | 70                      | 100                     | SPICE; $d_{SOI}$ , $d_{BOX}$ from [82]             |

| 28     | 0.5        | ✓                      |       |            | [83]           | 7                       | 25                      | SPICE; R: 0.5 or 0.1 fC                            |

|        |            |                        |       | SOI-Fin    |                |                         |                         |                                                    |

| 14     | 4.0        |                        |       | <b>♦</b>   | [80, Table I]  |                         |                         | TCAD; $R: > 4.0 \text{ fC}$                        |

As is evident in Fig. 5, the assumption of  $C_L = C_g$  well describes the evolution of  $Q_C$  in Bulk-Planar SRAMs across generations (note that the three latest generations, denoted by "a" in the figure, are results forecast by simulation based on a scaling rule). The observed agreement suggests the reason why  $Q_C$  decreases in proportion to  $l^{1.5}$  rather than  $l^2$ . Although the scaling of  $C_g$  keeps pace with  $l^1$ , as shown in Fig. 6, that of  $V_{\rm DD}$  is roughly proportional to  $l^{0.5}$ , because it gradually departs from the beginning  $l^1$  trend and finally becomes almost constant at 0.7 V. Fig. 5 also demonstrates that the  $C_L$  =  $C_g$  assumption underestimates and exhibits a discrepancy as large as one order of magnitude in comparison with Bulk-Fin SRAMs. This discrepancy almost disappears when  $C_L =$  $C_g + C_p$ , where  $C_p$  denotes the parasitic capacitance. This study estimated  $C_p$  from w and a unit value of 0.7e-3 fC/nm, extracted from [89, Fig. 7], which suggests that the total parasitic components of the gate capacitance, such as overlap and fringe capacitance (see the inset and caption of Fig. 5), are almost constant at this value for a wide range of technology generations (l = 11-130 nm). The significance of  $C_p$  as revealed in Fig. 5 accords with the famous issue of Fin devices: Their RF performance is severely restricted by a relatively

TABLE VI REFERENCE YEARS FOR THE SCALING TREND, WITH VALUES OBTAINED BY DIGITIZING [84, FIG. 2], WHICH SHOWS THE SCALING TREND FOR Intel LOGIC TECHNOLOGIES

| Year | l (nm) | Year | l (nm) | Year | l (nm) |

|------|--------|------|--------|------|--------|

| 1978 | 3000   | 1995 | 350    | 2007 | 45     |

| 1984 | 1500   | 1999 | 180    | 2012 | 22     |

| 1990 | 800    | 2003 | 90     | 2018 | 9      |

large  $C_p$  inherently due to their 3-D gate structure [90]–[92]. In this regard, efforts have been made to boost the speed of Fin devices by decreasing  $C_p$ , but note that such efforts essentially involve undesired  $Q_C$  degradation. Successfully solving this  $C_p$  dilemma will require close collaboration between SEE researchers and device or process professionals from a deep level of device development such as material selection (see also Section III-B).

Although future study will be needed to identify the mechanism behind the  $l^2$  trend for SOI-Planar SRAMs (Fig. 4), one should first take into account that the definition of  $Q_C$  varies

$<sup>^{\</sup>dagger}$   $Q_C$  was defined by  $Q_{\rm col}$ . The other values were defined by  $Q_{\rm dep}$ . \*  $Q_C$  was determined experimentally. The other values were obtained by theory or simulation (see the "Note" column: "SPICE" indicates that the analysis used a circuit simulator, while "TCAD" indicates a numerical device simulator).

Some papers reported a range of  $Q_C$  values. For those cases, the second column lists a representative value, while the "Note" column gives the range, denoted by"R:".

Fig. 5. Comparison of Bulk SRAM  $Q_C$  values between the literature data (symbols) and model estimations (lines). The inset conceptually illustrates the components of  $C_p$  used in this calculation;  $C_1$ : gate-to-plug capacitance,  $C_2$ : outer fringe capacitance, and  $C_3$ : overlap capacitance.

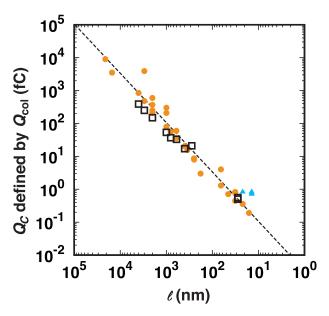

across articles. As seen in Table IV, the  $Q_C$  of Bulk SRAMs is mostly defined by  $Q_{col}$ . On the other hand (Table V), SOI SRAMs often rely on  $Q_C$  measured in terms of  $Q_{dep}$ , which represents the amount of charge deposited in a region in question, such as a body region [Fig. 2(a)]. Although Fig. 4 shows that the  $Q_C$  of SOI SRAMs is lower overall than that of Bulk SRAMs, the comparison is not straightforward because of this difference in definition. In SOI SRAMs,  $Q_C$  defined by  $Q_{\rm col}$  is usually larger than that defined by  $Q_{\rm dep}$ . For example (Table V), the 280-nm SOI SRAM tested in [79] exhibited 21 fC of  $Q_C$  as defined by  $Q_{col}$ , which is 10 times larger than the 2.8 fC as defined by  $Q_{\rm dep}$ . The physical mechanism behind the factor of 10 is related to the existence of the BOX layer (see Section III-B for the details). Hence, Fig. 7 again compares Bulk and SOI SRAMs, but with  $Q_C$  only defined by  $Q_{col}$ . Interestingly, the  $l^2$  trend disappears and is instead replaced by a universal curve showing the  $l^{1.5}$  trend. The appearance of this universal curve seems inconsistent with the common agreement that SOI SRAMs have lower  $Q_C$  than Bulk SRAMs do—even when both  $Q_C$  values are defined by  $Q_{\text{col}}$ —because of their lower parasitic (junction) capacitance. This inconsistency is attributed to the limited amount of data in this survey and the spread of its distribution, which do not allow one to identify the difference between the SOI and Bulk SRAM data. A close look at Fig. 7 suggests that the SOI  $Q_C$  is approximately half the Bulk  $Q_C$  for  $l \ge 400$  nm, for which all the data came from Pickel's simulation study [7]. His simulation relied on well-controlled SOI-Planar and Bulk-Planar SRAM samples, which both consisted of the same transistors except for the presence or lack of BOX.

# B. SRAM $L_T$

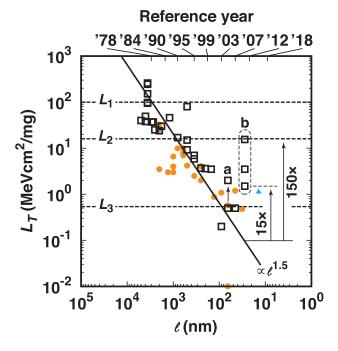

Tables VII and VIII compile  $L_T$  values collected in this survey. As revealed in Fig. 8, except for the dramatic increase

Fig. 6. Evolutions of transistor parameters in Bulk SRAM cells [87], [88].  $C_g$  and w denote the gate capacitance and width of a single transistor, respectively. The symbols represent the data in [88], except for the w values for Bulk-Fin SRAMs. Those w values for Bulk-Fin SRAMs are not reported in [88] and hence were estimated by the author of the present study as  $2H_{\rm fin}$ , where  $H_{\rm fin}$  denotes the Fin height reported in [88]. The lines are eye guides (see text). The triangle for  $V_{\rm DD}$  shows a reference slope for the dependence on l.

in  $L_T$  for the recent SOI-Planar SRAMs denoted by "a" and "b,"  $L_T$  globally exhibits a scaling trend that is roughly proportional to  $l^{1.5}$ . Note that this study determined the slope parameter of 1.5 from the  $Q_C$  trend (Fig. 4) and the value of  $1.6 \pm 0.2$  predicted by Brucker *et al.* [14] for SOI-Planar SRAMs. Fig. 8 also presents three reference values ( $L_1$ – $L_3$ ) that correspond to the typical upper bounds of the distribution of L in various radiation environments. Comparing  $L_T$  with these reference values underscores the increasing complexity of SEE mechanisms in the context of the variety of radiation, as follows

First, Fig. 8 shows that  $L_T$  was already lower than  $L_1$  in the very early 4- $\mu$ m generation. This  $L_1$  of 100 MeVcm²/mg corresponds to the maximum value of L in the space radiation environment, or more specifically GCRs. Hence, the  $L_1$  comparison suggests that CMOS SRAMs have been sensitive to GCRs since their inception, which dates back to the late 1970s, as seen from the top axis in the figure. This period corresponds to the historic year of 1975 when Binder *et al.* first demonstrated GCR-induced satellite anomalies [5]—It seems challenging to find a meaning behind this agreement, because

| l (nm) | $L_T$ (MeVcm <sup>2</sup> /mg) | Exp.* | Structure   | Reference       | Note <sup>b</sup>                             |

|--------|--------------------------------|-------|-------------|-----------------|-----------------------------------------------|

|        |                                |       | Bulk-Planar |                 |                                               |

| 2000   | 32.8                           | 1     | •           | [66]            |                                               |

| 2000   | 3.5                            | 1     | •           | [66, Table III] | <i>l</i> from [67]                            |

| 1300   | 3                              | 1     | •           | [93, Table I]   | NMOS cell                                     |

| 1000   | 4                              | 1     | •           | [93, Table I]   | NMOS cell                                     |

| 1000   | 3                              | 1     | •           | [93, Table I]   | NMOS cell                                     |

| 800    | 10                             | 1     | •           | [93, Table I]   |                                               |

| 2000   | 25                             |       | •           | [17, Fig. 5]    | TCAD; Exp. R: 14–30 MeVcm <sup>2</sup> /mg    |

| 1000   | 6.6                            |       | •           | [17, Fig. 5]    | TCAD                                          |

| 500    | 4.2                            |       | •           | [17, Fig. 5]    | TCAD; Exp. R: 2.34–6.99 MeVcm <sup>2</sup> /n |

| 600    | 7                              |       | •           | [94, Fig. 3]    | TCAD                                          |

| 600    | 10                             | ✓     | •           | [95, Fig. 4]    |                                               |

| 600    | 8                              |       | •           | [85]            | TCAD                                          |

| 350    | 2.5                            |       | •           | [85]            | TCAD                                          |

| 130    | 0.88                           |       | •           | [96, Fig. 10]   | TCAD                                          |

| 90     | 1.08                           |       | •           | [96, Fig. 10]   | TCAD                                          |

| 60     | 0.58                           |       | •           | [96, Fig. 10]   | TCAD                                          |

| 250    | 2.0                            | 1     | •           | [97]            |                                               |

| 250    | 4.1                            | ✓     | •           | [98]            |                                               |

| 60     | 0.01                           | 1     | •           | [99]            | Block RAM of FPGA                             |

| 45     | 1.2                            | 1     | •           | [100]           |                                               |

| 32     | 0.48                           |       | •           | [75]            |                                               |

TABLE VII SEU  $L_T$  Values Collected From the Literature for the Bulk Structures (see Table VIII for SOI)

[75]

Bulk-Fin

Some papers reported a range of  $L_T$  values. For those cases, the second column lists a representative value, while "Note" column gives the range, denoted by "R:".

1.12

14

Fig. 7. Copy of Fig. 4 but with  $Q_C$  measured only in terms of  $Q_{col}$ . The line represents the trend reported by Pickel [7].

their study was based on an FF fabricated in a bipolarjunction-transistor (BJT) process, not on a CMOS SRAM. Note that one would obtain a similar result when using 30 MeVcm<sup>2</sup>/mg for comparison instead of 100 MeVcm<sup>2</sup>/mg. Here, 30 MeVcm<sup>2</sup>/mg corresponds to the maximum L produced by Fe in GCRs and is widely used as a GCR reference because of its abundance [77].

Next, Fig. 8 confirms that device scaling to the submicrometer generations results in  $L_T < L_2$  or 16 MeVcm²/mg, which is the maximum value of L produced by nuclear reactions between Si and space protons [112] or terrestrial neutrons [113]. For their small charge and Coulomb barrier, highenergy protons and neutrons can collide with nuclei in device materials and produce various secondary charged particles, as in the following example [114]:²

$$n^{0} + {}^{28}_{14}\text{Si}^{14+} \rightarrow p^{+} + {}^{28}_{13}\text{Al}^{13+} \rightarrow n^{0} + {}^{4}_{2}\text{He}^{2+} + {}^{24}_{12}\text{Mg}^{12+} \rightarrow \text{etc.}$$

(7)

The resultant secondary ions such as Al<sup>13+</sup> then deposit charge along their tracks through ionization, as with GCRs. The year axis suggests that the concern for indirect ionization has been serious since the late 1980s, which correspond to the years when a team of International Business Machines Corporation (IBM) conducted an extensive study on SEEs

<sup>2</sup>The author of the present study added atomic and charge numbers to the original expressions for clarity.

<sup>\*</sup>  $L_T$  was determined experimentally. The other values were obtained by theory or simulation (see the "Note" column: "SPICE" indicates that the analysis used a circuit simulator, while "TCAD" indicates a numerical device simulator).

TABLE VIII SEU  $L_T$  Values Collected From the Literature for the SOI Structures (see Table VII for Bulk)

| l (nm) | $L_T$ (MeVcm <sup>2</sup> /mg) | Exp.* | Structure      | Reference        | Note <sup>b</sup>       |                         |                                                                         |

|--------|--------------------------------|-------|----------------|------------------|-------------------------|-------------------------|-------------------------------------------------------------------------|

|        |                                |       | SOI-Planar     |                  | $d_{\mathrm{SOI}}$ (nm) | $d_{\mathrm{BOX}}$ (nm) |                                                                         |

| 5000   | 40                             | 1     |                | [64]             | 500                     |                         |                                                                         |

| 4000   | 38                             | 1     |                | [76]             | 550                     |                         |                                                                         |

| 4000   | 49.2                           | 1     |                | [77]             | 500                     |                         |                                                                         |

| 3600   | 260                            | 1     |                | [14, Table II]   | 530                     |                         | $R: > 260 \text{ MeVcm}^2/\text{mg}$                                    |

| 3600   | 245                            | 1     |                | [14, Table II]   | 530                     |                         |                                                                         |

| 3600   | 152                            | ✓     |                | [14, Table II]   | 530                     |                         |                                                                         |

| 3600   | 98                             | ✓     |                | [14, Table II]   | 530                     |                         |                                                                         |

| 3600   | 95                             | ✓     |                | [14, Table II]   | 530                     |                         |                                                                         |

| 2900   | 37                             | ✓     |                | [14, Table II]   | 530                     |                         |                                                                         |

| 2700   | 37                             | ✓     |                | [14, Table II]   | 530                     |                         |                                                                         |

| 2500   | 25                             | 1     |                | [101, Fig. 4]    | 550                     | 500                     |                                                                         |

| 2000   | 24                             | 1     |                | [77]             | 500                     |                         | l = 2500  nm? [4]                                                       |

| 1800   | 30                             | 1     |                | [14, Table II]   | 530                     |                         |                                                                         |

| 1200   | 46                             | 1     |                | [102, Table II]  | 150                     |                         |                                                                         |

| 800    | 17                             | 1     |                | [102, Table II]  | 1200                    |                         |                                                                         |

| 500    | 80                             | 1     |                | [78]             | 85                      | 400                     |                                                                         |

| 500    | 15                             | 1     |                | [102, Table II]  | 150                     |                         | $R: < 15 \text{ MeVcm}^2/\text{mg}$                                     |

| 500    | 9.21                           | 1     |                | [103]            | 260                     | 130                     |                                                                         |

| 350    | 5.87                           | 1     |                | [103]            | 260                     | 130                     |                                                                         |

| 350    | 7                              | 1     |                | [95]             | 250                     | 200                     |                                                                         |

| 250    | 3.7                            | 1     |                | [98]             | 150                     | 400                     |                                                                         |

| 200    | 3.6                            | 1     |                | [104]            | 50                      | 100                     |                                                                         |

| 150    | 3.5                            | 1     |                | [105]            | 150                     |                         |                                                                         |

| 90     | 0.46                           | 1     |                | [106]            | 70                      | 145                     | $l, d_{\mathrm{SOI}}, \text{ and } d_{\mathrm{BOX}} \text{ from [107]}$ |

| 65     | 0.5                            | 1     |                | [108, Fig. 1]    |                         |                         |                                                                         |

| 45     | 0.5                            | 1     |                | [108, Fig. 1]    |                         |                         |                                                                         |

| 65     | 2                              |       | □ "a"          | [109, Fig. 19]   | 10                      | 12                      | TCAD                                                                    |

| 28     | 15.5                           |       | □ "b"          | [110, Table III] | 7                       | 25                      | TCAD                                                                    |

| 28     | 3.5                            |       | □ "b"          | [83]             | 7                       | 25                      | TCAD; R: 3.5 or 7 MeVcm <sup>2</sup> /mg                                |

| 28     | 1.5                            | 1     | "b"            | [111, Fig. 3]    | 7                       | 25                      |                                                                         |

|        |                                |       | SOI-Fin        |                  |                         |                         |                                                                         |

|        |                                |       | (Not reported) |                  |                         |                         |                                                                         |

<sup>\*</sup>  $L_T$  was determined experimentally. The other values were obtained by theory or simulation (see the "Note" column: "SPICE" indicates that the analysis used a circuit simulator, while "TCAD" indicates a numerical device simulator).

caused by terrestrial neutrons and other cosmic rays [115]. Today's IC makers thus need knowledge of astronomy, such as solar activity, to assure the reliability of their products, even if they are producing devices only for terrestrial use. This is because terrestrial neutrons are products of reactions between GCRs and Earth's atmosphere, and their abundance depends on solar activity and galactic events. IC makers further need knowledge of their products at the atomic level. Evaluating the risk of this indirect ionization process becomes more complex with the introduction of new elements into devices. In this regard, the impacts of tungsten (W) are often discussed [116]–[119]. In addition to its proximity to transistors (W is used to make the plug connecting the source/drain region to a metal wire), it has a nuclear-reaction cross section larger than that of Si, and it generates secondary ions heavier than Si because of

its high atomic number (Z=74). The use of W thus increases the frequency of secondary ion strikes and also increases L, which may exceed  $L_2$  and reach 30 MeVcm<sup>2</sup>/mg [120, Fig. 6]. Even the residue of gases during fabrication cannot be ignored. Studies [121]–[123] suggest that <sup>10</sup>B atoms from the  $B_2H_6$  gas used for W-plug formation remain inside final products and cause SEUs through a fission process, in which a <sup>10</sup>B nucleus absorbs a low-energy (thermal) neutron and breaks into two charged particles, that is, <sup>4</sup>He and <sup>7</sup>Li nuclei [124]. Note that heavy ions with energy sufficiently high to overcome the Coulomb barrier can collide and induce the indirect ionization process [118], [125], [126].

Fig. 8 also shows that further scaling results in  $L_T$  <  $L_3$  or 0.54 MeVcm<sup>2</sup>/mg, which corresponds to the maximum value of L produced by protons though direct ionization. The

b Some papers reported a range of  $L_T$  values. For those cases, the second column lists a representative value, while "Note" column gives the range, denoted by "R:".

Fig. 8. Evolution of  $L_T$ . The solid line is an eye guide, given by  $L_T = 20 \, (l/1000)^{1.5}$ . The dashed lines represent references for comparison:  $L_1 = 100 \, \text{MeVcm}^2/\text{mg}$ , the maximum value of L produced by GCRs through direct ionization in Si;  $L_2 = 16 \, \text{MeVcm}^2/\text{mg}$ , the maximum value of L produced by nuclear reactions between Si and protons or neutrons;  $L_3 = 0.54 \, \text{MeVcm}^2/\text{mg}$ , the maximum value of L produced by protons through direct ionization in Si.

proton charge is small but no longer negligible in sub-100-nm SRAMs dating from the 21st century onward. In fact, since this SEU was experimentally demonstrated for the first time in a 65-nm SRAM in 2007 [127], it has been observed in succeeding generations [108], [128], [129]. Moreover,  $L_T < L_3$  induces SEUs due to positive muons in the Earth's atmosphere, which have as much charge as protons do. In fact, 31 years after the prediction by Ziegler and Lanford in 1979 [130], Sierawski *et al.* [131] tested Bulk SRAMs with  $l \le 65$  nm and presented the first experimental evidence of the positive-muon-induced SEUs. It is now imperative to evaluate the risk of SEUs due to muons, including negative ones [132], [133], for terrestrial applications, although the risk has so far been claimed as insignificant because of the overwhelming frequency of neutron SEUs [33], [74].

A close look at Fig. 8 indicates that the tested SOI SRAMs have higher  $L_T$ , in general, than their Bulk counterparts do

$$L_{T(SOI)} \ge L_{T(Bulk)}.$$

(8)

This is opposite to the finding and common belief for  $Q_C$  (note that  $Q_C$  is hereafter defined by  $Q_{col}$ )

$$Q_{C(SOI)} \le Q_{C(Bulk)}.$$

(9)

The following paragraph discusses this reversal of order.

Regardless of the structure category (SOI or Bulk), the SEU criterion is widely given as  $Q_{\rm col} \geq Q_C$ . Then,  $Q_{\rm col}$  can be expressed as

$$Q_{\rm col} = \eta Q_{\rm dep} \tag{10}$$

where typically

$$\eta = \begin{cases}

\alpha \le 1, & \text{for Bulk} \\

\beta \ge 1, & \text{for SOI.}

\end{cases}$$

(11a)

Here,  $\alpha$  and  $\beta$  represent the charge collection efficiency and parasitic BJT amplification factor, respectively. Assuming a certain region of Si, called a sensitive volume (SV),  $Q_{\rm dep}$  can be estimated from Ls, where L is given in a charge-based unit (e.g., fC/nm) and s represents a chord length, that is, the travel distance of an incident radiation particle across the SV [134]. Note that here L is assumed to be constant along s to simplify the integration to obtain  $Q_{\rm dep}$ . As a result, the two critical and threshold parameters can be linked as follows:

$$Q_C = \eta L_T s. \tag{12}$$

Because both  $\eta$  and  $L_T$  are larger for SOI SRAMs than for Bulk SRAMs, this equation necessitates  $s_{(SOI)} \leq s_{(Bulk)}$  to establish the reversed order for  $Q_C$ . In fact, such superiority of SOI over a Bulk substrate in the context of s is often highlighted [35]. As illustrated in Fig. 2(a), SOI substrates rely on BOX to separate transistors electrically from the bottom substrate. This separation makes the SV physically restricted by  $d_{SOI}$ , which is typically on the order of 10 (FD) or 100 nm (PD). As illustrated in Fig. 2(b), on the other hand, a Bulk substrate has an open-bottom structure, which can collect charge deposited in the substrate's deep region. This collection process is associated with the dramatic stretch-out of the electric field profile, which is called field funneling. It works as if a funnel were drawing charge from the deep region. As a result, Bulk SVs typically range over 100–10000 nm in depth,  $\sim 10 \times$  deeper than SOI SVs.

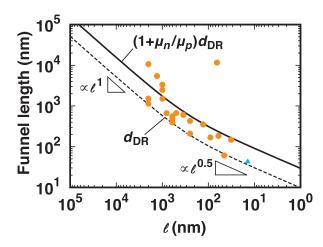

Precise description of field funneling requires a set of differential equations for high-level injection, for which an exact solution cannot be obtained analytically. Hence, researchers often use an a posteriori approach to determine s from measured  $Q_{\rm col}$  and L via  $s = Q_{\rm col}/L$ ; the resultant s is called the funnel length [135], [136]. Similarly, this study estimated the funnel length from  $L_T/Q_C$ .  $L_T$  was obtained directly from Table VII and  $Q_C$  from  $Q_C = 2(C_g + C_p)V_{\rm DD}$  in Fig. 5. For comparison, this study also calculated two theoretical reference values, which are related to  $d_{\rm DR}$ , the length of the depletion region (DR) that is originally established in a p-1 junction. Assuming a one-sided abrupt p-1 junction in a p-1 type Si substrate, this study obtained  $d_{\rm DR}$  from the textbook formula [137]

$$d_{\rm DR} = \sqrt{\frac{2\varepsilon_{\rm Si}}{aN}(\phi_b + V_{\rm DD})}.$$

(13)

Here,  $\varepsilon_{Si}$  and N represent the substrate's permittivity and carrier density, respectively, while  $\phi_b$  denotes the built-in

<sup>3</sup>This estimation relies on  $\eta$  (=  $\alpha$ ) = 1 in (11a), and this unity assumption is commonly used for  $\alpha$ . This study explicitly uses (11a) for ease of comparison between the Bulk and SOI cases by providing a universal expression for both structures. Building the universal expression took into account the case of  $\alpha$  < 0 that is used in a multiple-SV model [97], in which an SV is modeled with a combination of arbitrary regions. Here,  $Q_{\text{coll}}$  is given by  $\sum_i \alpha_i L_i s_i$ , where i represents the index of each region, and  $\sum_i \alpha = 1$ .

Fig. 9. Estimated funnel lengths of Bulk SRAMs. Estimations from  $Q_C/L_T$  (symbols) are compared with the depletion length for a one-sided abrupt junction  $(d_{\rm DR})$  and Hu's funnel length model giving  $(1+\mu_n/\mu_p)d_{\rm DR}$ . The two triangles show reference slopes for the dependence l.

potential of the p-n junction in question. Here  $\phi_b$  was also theoretically estimated from

$$\phi_b = 2\frac{kT}{q} \ln \left(\frac{N}{n_i}\right) \tag{14}$$

where k, T, and  $n_i$  denote the Boltzmann constant, temperature, and the intrinsic carrier density, respectively. Regardless of the type of channel structure (Planar or Fin), this study simply used  $N = (5 \times 10^{15}) \cdot (5000/l)$  [cm<sup>-3</sup>], which was extracted from [3]. The other reference value was the funnel length modeled by Hu [138], given by  $(1 + \mu_n/\mu_p)d_{DR}$  where  $\mu_n$  and  $\mu_p$  denote the respective mobilities of electrons and holes in the substrate. This study used a constant mobility ratio across generations, that is,  $\mu_n/\mu_p = 980/410$  [138], after confirming that the ratio remains almost intact (within a factor of  $\sim$ 2) even when considering the mobility dependence on N, at least in the range examined in this study. As shown in Fig. 9, this attempt found that the a posteriori funnel length obtained from the literature data  $(Q_C/L_T)$  decreased along the evolution of the two reference values related to  $d_{\rm DR}$ . The funnel lengths obtained from the literature data are clearly longer than  $d_{DR}$ . This result confirms that the tested Bulk SRAMs underwent field funneling and collected charge from the region deeper than  $d_{DR}$ . Fig. 9 also shows that Hu's model overall describes the upper bound of the funnel lengths obtained from the literature data (particularly for  $l \lesssim 1000$  nm). This agreement between the upper bound and Hu's model is interesting. Some studies have suggested that Hu's model underestimates the funnel length for high-L ions because of the lack of an additional charge component due to diffusion [139]. Hu derived his model by assuming a strike of a low-L ion, or more specifically an  $\alpha$ -ray, that is,  $L \leq 1.5 \text{ MeVcm}^2/\text{mg}$ . As seen in Table VII, however,  $L_T$  values in the literature are mostly larger than this value. Despite such underestimation, Hu's model has provided the upper bound in this analysis. This is probably due to the influence of  $\tau$  in (2). Both the discussion in [139] and that of Hu are based on a constant-biased discrete p-n diode. Without

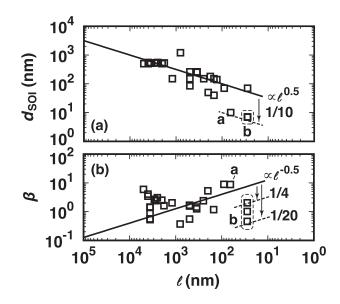

Fig. 10. (a)  $d_{\rm SOI}$  values collected from the literature. The solid line is an eye guide, given by  $d_{\rm SOI}=10l^{0.5}$ . (b)  $\beta$  values calculated from the literature data. The solid line is an eye guide, given by  $\beta=40l^{-0.5}$ .

any time constraints, they both counted charge as long as charge flows. In contrast, the funnel length estimated from  $Q_C/L_T$  is a result of the circuit response, with charge counted only for the duration of  $\tau$  [140]. The diffusion process for additional charge could be too slow in comparison with  $\tau$ , thus being insignificant in relation to  $Q_C$  and the resultant funnel length. In this regard, Fig. 9 indicates that Hu's model can underestimate funnel lengths in the early micrometer-scale generations ( $l \gtrsim 1000$  nm). In these generations, the responses of the tested Bulk SRAMs could be slow, and their  $\tau$  values could be comparable to the time for the total charge collection.

Moreover, Fig. 9 shows that the funnel length of the tested Bulk SRAMs is around  $\sim 100$  nm when  $l \lesssim 100$  nm. This suggests that the superiority of SOI over Bulk in the context of s can no longer always be expected. In fact, some SOI SRAMs exhibit  $L_T$  lower than that of Bulk SRAMs when  $l \lesssim 100$  nm (Fig. 8). Furthermore, Fig. 9 indicates that the funnel length of the tested Bulk-Fin SRAM was shorter than would be predicted by Hu's model. Although further investigation is needed because of the small amount of data, this finding seemingly agrees with the narrow-fin effect [38], [39]: fin width reduction narrows the path from a transistor to its substrate and restricts charge collection from the substrate's deep region.

Similarly, this paragraph analyzes the  $L_T$  values of SOI-Planar SRAMs, but in terms of  $\beta$ , because s of SOI devices is explicitly given by  $d_{\rm SOI}$ , unlike their Bulk counterparts. Fig. 10(a) shows the  $d_{\rm SOI}$  data collected from the literature. Overall,  $d_{\rm SOI}$  exhibits a monotonically decreasing trend, which is roughly proportional to  $l^{0.5}$ . This slope parameter of 0.5 was mathematically determined from  $Q_C = L_T d_{\rm SOI}$ , with  $Q_C$  defined by  $Q_{\rm dep}$ , not by  $Q_{\rm col}$ . To satisfy this relationship, the parameter must be 0.5 because, as shown in Figs. 4 and 8,  $Q_C$  and  $L_T$  are proportional to  $l^2$  and  $l^{1.5}$ , respectively.

Fig. 10(a) also highlights that the two recent generations labeled "a" and "b" attained a large ( $\sim 1/10$ ) reduction in  $d_{SOI}$ . The increase in  $L_T$  observed in Fig. 8 is attributed to this  $d_{SOI}$ reduction. The factor of 1/10 is seemingly too small, however, to explain the large (15–150×)  $L_T$  increase at the latest node, "b", although this large increase might be an artifact because it is measured with respect to the solid line or an extrapolation of the  $l^{1.5}$  trend (Fig. 8). Moreover, the  $L_T$  variations observed in the node "b" cannot be explained by the  $d_{SOI}$  reduction because the three cases examined here all rely on the same  $d_{SOI}$ . On the other hand, Fig. 10(b) shows  $\beta$  values calculated from (12) by combining the collected data ( $L_T$  and  $d_{SOI}$ ) and Pickel's  $l^{1.5}$  trend for  $Q_C$  as defined by  $Q_{\rm col}$ . An increasing trend is evident for  $\beta$ , roughly conforming to  $l^{-0.5}$ , where the exponent of -0.5 was mathematically deduced as with  $d_{SOI}$ . The node "b" departs, however, from this trend and demonstrates a large  $(1/4-1/20\times)$  reduction. This reduction in  $\beta$  could cause the dramatic  $L_T$  increase in concert with the reduction in  $d_{SOI}$ .

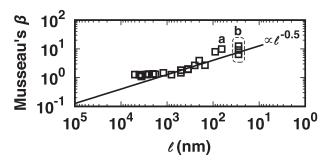

To seek the physical mechanism behind this  $\beta$  reduction, this paragraph further analyzes  $\beta$  by using a model developed by Musseau *et al.* [141]<sup>4</sup>:

$$\beta = c \frac{1 + 0.65w}{l\sqrt{L_T d_{SOI}}} + 1 \tag{15}$$

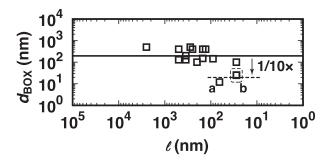

where c is a technology-independent parameter, assumed here to have a constant value of 3. Interestingly, as shown in Fig. 11, this model reproduces the  $l^{-0.5}$  trend but not the reduction at "b." This discrepancy suggests that  $\beta$  is influenced by a parameter other than those in the model. In this regard, Fig. 12 indicates that the two generations in question, "a" and "b," also achieved a significant reduction in  $d_{BOX}$ . The fact that  $d_{\rm BOX} \approx d_{\rm SOI} \approx 10$  nm suggests that the transistors in those generations operate in a double-gate mode. In such a mode, the body potential is tightly controlled from both the top metal gate and the bottom Si gate (substrate), with the latter fixed at a certain voltage such as 0 V. As seen from its definition,  $\beta$  quantifies the parasitic BJT amplification. Particle radiation provides charge, and the resultant majority carriers can accumulate in the body region, which electrically floats because of the presence of BOX. This accumulation can change the body potential and turn on a parasitic BJT that inherently consists of the source-body-drain connection in the transistor. As a result, the drain terminal collects not only charge created by radiation but also charge injected from the source. Hence, how large  $\beta$  is strongly depends on how much the body floats. In this regard, double-gate transistors are known to have a fairly stable body region because of the tight electrical connection to the top and bottom gates [142]. The reduction in  $\beta$  observed at the node "b" in Fig. 10(b) could reflect this double-gate feature because of  $d_{BOX}$  and  $d_{SOI}$  both scaling down to 10 nm. Of course, the cause of the variations in  $\beta$  must be examined in the future. Interestingly, Fig. 10(b) also indicates that the node "a" does not receive the benefit of the double-gate mode, despite its thin  $d_{SOI}$  and  $d_{BOX}$ . Further analysis of the differences between generations "a" and

Fig. 11.  $\beta$  calculated from a model developed by Musseau *et al.* (see text). The solid line is the same eye guide as in Fig. 10(b).

Fig. 12.  $d_{\rm BOX}$  values collected from the literature. The solid line is an eye guide, given by  $d_{\rm BOX}=200$ .

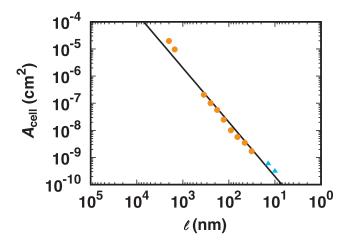

Fig. 13.  $\sigma_{\infty}$  values collected from the literature. The solid line represents the evolution of the SRAM cell area  $A_{\rm cell}$  (see the text). The dashed line represents the typical area of an ion track  $(A_{\rm ion})$ , as estimated from  $\pi \, r^2$  with r=100 nm.

"b" would help locate the threshold at which the double-gate feature takes effect.

### C. SRAM $\sigma_{\infty}$

Tables IX and X list  $\sigma_{\infty}$  values collected from the literature, while Fig. 13 shows how this parameter has evolved.

<sup>&</sup>lt;sup>4</sup>The second term consisting of 1 on the right-hand side indicates the difference in the definitions of  $\beta$  between their study and the present study. They defined  $Q_{\rm col}=(1+\beta)Q_{\rm dep}$ , which is also widely used.

TABLE IX SEU  $\sigma_{\infty}$  Values Collected From the Literature for the Bulk Structures (see Table X for SOI)

| l (nm) | $\sigma_{\infty} \ (\mathrm{cm}^2/\mathrm{b})^{\ddagger}$ | Exp.* | Structure   | Reference     | Note <sup>b</sup>                                        |

|--------|-----------------------------------------------------------|-------|-------------|---------------|----------------------------------------------------------|

|        |                                                           |       | Bulk-Planar |               |                                                          |

| 2000   | $1 \times 10^{-6}$                                        | ✓     | •           | [66, Fig. 4]  | <i>l</i> from [67]                                       |