# Scheduling and Optimization of Fault-Tolerant Embedded Systems with Transparency/ Performance Trade-Offs

VIACHESLAV IZOSIMOV Embedded Intelligent Solutions (EIS) By Semcon AB PAUL POP Technical University of Denmark and PETRU ELES AND ZEBO PENG Linköping University

In this paper, we propose a strategy for the synthesis of fault-tolerant schedules and for the mapping of faulttolerant applications. Our techniques handle transparency/performance trade-offs and use the fault-occurrence information to reduce the overhead due to fault tolerance. Processes and messages are statically scheduled, and we use process re-execution for recovering from multiple transient faults. We propose a fine-grained transparent recovery, where the property of transparency can be selectively applied to processes and messages. Transparency hides the recovery actions in a selected part of the application so that they do not affect the schedule of other processes and messages. While leading to longer schedules, transparent recovery has the advantage of both improved debuggability and less memory needed to store the fault-tolerant schedules.

Categories and Subject Descriptors: C.3 [Computer Systems Organization]: Special-Purpose and Application-Based Systems - *Real-time and Embedded Systems*; C.4 [Computer Systems Organization]: Performance of Systems - *Design Studies; Fault Tolerance*; D.2.5 [Software]: Testing and Debugging; D.4.5 [Software]: Reliability - *Checkpoint/Restart*; C.1.4 [Computer Systems Organization]: Parallel Architectures - *Distributed Architectures*; D.4.1 [Software]: Process Management - *Scheduling*; G.1.6 [Mathematics of Computing]: Optimization - *Global Optimization*

General Terms: Design, Performance, Reliability

Additional Key Words and Phrases: Fault-tolerant embedded systems, safety-critical applications, design optimization, transient faults, intermittent faults, debuggability, real-time scheduling, conditional scheduling, process mapping

# 1. INTRODUCTION

Modern embedded systems are complex computer systems with sophisticated software

running on often distributed hardware platforms. Such systems can provide very high

Received April 2009; revised February 2010; accepted October 2010.

This research was partially supported by the Swedish National Graduate School in Computer Science (CUGS). This work was done while Viacheslav Izosimov was working at Dept. of Computer and Information Science at Linköping University in Sweden.

Authors' addresses: Viacheslav Izosimov, Embedded Intelligent Solutions (EIS) By Semcon AB, Box 407, SE-58104 Linköping, Sweden; Paul Pop, Dept. of Informatics and Mathematical Modelling, Technical University of Denmark, DK-2800 Kongens Lyngby, Denmark; Petru Eles and Zebo Peng, Dept. of Computer and Information Science, Linköping University, SE-58183 Linköping, Sweden.

Permission to make digital/hard copy of part of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage, the copyright notice, the title of the publication, and its date of appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee.

levels of service and are replacing mechanical and hydraulic parts of control systems in aircraft, automobiles, production lines, switching systems, and medical equipment. They can be responsible for safety-critical operations in, for example, automatic flight control, electronic steering, or car braking systems.

Safety-critical embedded systems have to deliver correct results even in the presence of faults. Faults can be permanent (e.g., damaged links or microcontrollers), transient, and intermittent [Koren and Krishna, 2007]. Transient and intermittent faults<sup>1</sup> (or "soft errors") appear for a short time, cause miscalculation in logic [Rossi et al., 2005] and/or corruption of data, and then disappear without physical damage to the circuit. Causes of transient faults can be radiation [Velazco et al., 2007; May and Woods, 1978], electromagnetic interference [Strauss et al., 2006; Wang, 2003], lightning storms [Heine et al., 2005], crosstalk [Metra et al., 1998], temperature variations [Wei et al., 2004], and power supply fluctuations [Junior et al., 2004]. In this paper we will deal with transient faults. Transient faults have become one of the main concerns in the design of modern embedded systems due to the increased levels of integration in semiconductors, e.g. smaller transistor sizes, higher frequencies, and lower voltages [Constantinescu, 2003; Maheshwari et al., 2004; Hareland et al., 2001; Shivakumar et al., 2002]. According to recent studies [Kopetz et al., 2004; Shivakumar et al., 2002], the rate of transient-topermanent faults can be 100:1 or even higher.

Traditionally, transient faults have been addressed with hardware replication [Kopetz et al., 1990; Alstrom and Torin, 2001; Poledna, 1995; Claesson et al., 1998]. However, solutions based on the replication of hardware are very costly, in particular, with the increasing number of transient faults that have to be tolerated. In order to reduce the cost, other techniques are required, such as re-execution [Kandasamy et al., 2003a], replication [Xie et al., 2004; Xie et al., 2007; Chevochot and Puaut, 1999] and recovery with checkpointing [Punnekkat and Burns, 1997; Zhang and Chakrabarty, 2006; Orailoglu and Karri, 1994; Xu and Randell, 1996; Krishna and Singh, 1993; Lee et al., 1999; Melhem et al., 2004; Ayav et al., 2008]. The above techniques can also tolerate some of the software errors that manifest themselves as transient faults, for example, Heisenbugs [Kopetz et al., 2004], caused by wrongly initialized data or synchronization-related problems.

Safety-critical embedded systems have to satisfy cost and performance constraints besides reliability requirements. For example, automotive applications that are responsible for such safety-critical functions as braking or stabilization have to be fault-

<sup>&</sup>lt;sup>1</sup> We will refer to both transient and intermittent faults as "transient" faults.

tolerant and, at the same time, meet cost and timing constraints. However, re-execution, replication and recovery with checkpointing, if applied in a straightforward manner, will lead to significant time overheads and, hence, to solutions that do not meet performance constraints. Thus, faster components or more resources will be demanded to satisfy performance constraints, which, on the other hand, may not be acceptable due to cost limitations. Therefore, efficient design approaches are needed to satisfy cost and timing requirements imposed on fault-tolerant embedded systems. Researchers have proposed design strategies for the synthesis of fault-tolerant embedded systems in the past years. Liberato et al. [2000] have proposed an approach for design optimization of monoprocessor systems in the presence of multiple transient faults and in the context of pre-emptive earliest-deadline-first (EDF) scheduling. Hardware/software co-synthesis with fault tolerance has been addressed in [Srinivasan and Jha, 1995] in the context of event-driven scheduling. Xie et al. [2004] have proposed a technique to decide how replicas are selectively inserted into the application, based on process criticality. Ayav et al. [2008] have achieved fault tolerance for real-time programs with automatic transformations, where recovery with checkpointing is used to tolerate one single fault at a time. Power-related optimization issues of fault-tolerant embedded systems have been studied in [Zhang and Chakrabarty, 2006; Melhem et al., 2004]. Ying Zhang et al. [2006] have studied fault tolerance and dynamic power management in the context of messagepassing distributed systems. Fault tolerance has been applied on top of a pre-designed system, whose process mapping and scheduling ignore the fault tolerance issue. Melhem et al. [2004] have considered checkpointing for rollback recovery in the context of online earliest-deadline-first (EDF) scheduling on a monoprocessor embedded system. We have proposed a number of design optimization and scheduling techniques [Pop et al., 2009; Izosimov et al., 2005, 2006a, 2006b], including mapping and policy assignment, that are able to deliver efficient fault-tolerant embedded systems under limited amount of resources.

Fault tolerance techniques not only reduce the performance and increase the cost but also increase the complexity of embedded software. Compexity often leads to serious difficulties during debugging and testing of fault-tolerant embedded systems.

A common systematic approach for debugging embedded software is to insert observation points into software and hardware [Vranken et al., 1997; Tripakis, 2005; Savor and Seviora, 1997] for observing the system behavior under various circumstances. The observation points are usually inserted by an expert, or can be automatically injected based on statistical methods [Bourret et al., 2004]. In order to efficiently trace design errors, the results produced with the observation points have to be easily monitored, even in the recovery scenarios against transient faults. Unfortunately, the number of recovery scenarios is often very high and, thus, monitoring observation points for all these scenarios is often infeasible. Moreover, due to the increased number of fault scenarios, the number of possible system states substantially increases. It results in a very complex system behavior that is difficult to test and verify. The overall number of possible recovery scenarios can be considerably reduced by restricting the system behavior, in particular, by introducing *transparency requirements*.

A transparent recovery scheme has been proposed in [Kandasamy et al., 2003a], where recovering from a transient fault on one computation node does not affect the schedule of any other node. In general, transparent recovery has the advantage of increased debuggability, where the occurrence of faults in a certain process does not affect the execution of other processes. This reduces the total number of execution scenarios. At the same time, with increased transparency, the amount of memory needed to store the schedules decreases. However, transparent recovery increases the worst-case delay of processes, potentially reducing the overall performance of the embedded system. Thus, efficient design optimization techniques are even more important in order to meet time and cost constraints in the context of fault-tolerant embedded systems with transparency requirements. However, to our knowledge, most of the design strategies proposed so far [Zhang and Chakrabarty, 2006; Xie et al., 2004; Pinello et al., 2008; Srinivasan and Jha, 1995; Melhem et al., 2004; Ayav et al., 2008]have not explicitly addressed the transparency requirements for fault tolerance. If at all addressed, these requirements have been applied, at a very coarse-grained level, to a whole computation node, as in the case of the original transparent re-execution proposed in [Kandasamy et al., 2003a]. In such a schema, system behavior can be observed only by monitoring messages sent to and out of the computation node. In this case, designers neither can observe intraprocessor process inputs nor observe intraprocessor messages. Moreover, the coarse-grained transparency also leads to unnecessary end-to-end delays since, by far, not all of the fixed interprocessor messages have to be observed.

In this paper we propose a design optimization strategy that efficiently handles more elaborate transparency requirements and, at the same time, provides schedulable faulttolerant solutions under limited amount of resources.

## 1.1 Related Work

In the context of fault-tolerant real-time systems, researchers have tried to integrate fault tolerance techniques and task scheduling [Han et al., 2003; Bertossi and Mancini, 1994; Burns et al., 1996; Zhang and Chakrabarty, 2006; Xie et al., 2004; Wei et al., 2006]. Girault et al. [2003] have proposed a generic approach to address multiple failures with active replication. Ahn et al. [1997] have proposed a scheduling algorithm that generates efficient schedules with encapsulated primary-backup replicas against processor failures in a multiprocessor system. Passive replication has been used in [Al-Omari et al., 2001] to handle a single failure in multiprocessor systems so that timing constraints are satisfied. Liberato et al. [2000] have proposed an approach for design optimization of monoprocessor systems under presence of multiple transient faults. Conner et al. [2005] have introduced redundant processes into a pre-designed schedule to improve error detection. Hardware/software co-synthesis of fault-tolerant embedded systems has been addressed in [Srinivasan and Jha, 1995]. Ayav et al. [2008] have achieved fault tolerance for real-time programs with automatic transformations, where recovery with checkpointing is used to tolerate one single fault at a time. Xie et al. [2004; 2007] have proposed an approach to selectively insert replicas into the application with minimization of overall system criticality. Shye et al. [2007] have developed a process-level redundancy approach against multiple transient faults with active replication on multicore processors. Power-related optimization issues of fault-tolerant embedded systems have been studied in [Zhang and Chakrabarty, 2006; Han and Li, 2005; Zhu et al., 2005; Melhem et al., 2004; Wei et al., 2006; Pop et al., 2007].

Kandasamy et al. [2003a] have proposed *transparent* re-execution, where recovering from a transient fault on one computation node is hidden (masked) from other nodes, i.e., they have considered *node-level transparency*. Later this work has been extended with fault-tolerant transmission of messages on the bus [Kandasamy et al., 2003b]. Pinello et al. [2004; 2008] have addressed primarily permanent faults and have proposed mapping and scheduling algorithms for embedded control software. In [Izosimov et al., 2005; Pop et al., 2009] we have extended the approach of [Kandasamy et al., 2003a] with active replication and checkpointing optimization, and have proposed a fault-tolerance policy assignment strategy to decide which fault tolerance technique, e.g., checkpointing, active replication, or their combination, is the best suited for a particular process in the application.

However, the scheduling approach in [Izosimov et al., 2005; Pop et al., 2009] is very limited in its capacity to accommodate various fault scenarios and, thus, will lead to

unnecessary long schedules. The approach also considers only coarse-grained, node-level transparency and cannot handle more elaborate transparency requirements applied to a particular process or message, or to a set of processes and messages. Such fine-grained transparency approaches are needed for, e.g., a selective insertion of observation points, where only a particular subset of processes and messages needs to be monitored [Bourret et al., 2004; Tripakis, 2005].

# **1.2 Contributions**

In this paper, we present a novel algorithm for the synthesis of fault tolerant schedules that handles the transparency/performance trade-offs. The proposed algorithm not only handles fine-grained transparency, but, as the experimental results will show, also significantly reduces the schedule length compared to the previous scheduling approach [Izosimov et al., 2005; Pop et al., 2009].

A fine-grained approach to transparency, proposed in this paper, handles transparency requirements at the application level instead of resource level, selectively applying transparency to a particular process or message, or to a set of processes and messages. Thus, our fine-grained approach to transparency offers the designer the opportunity to gradually trade-off between debuggability and memory requirements on one side, and performance on the other side.

Our approach makes use of the fault-occurrence information in order to adapt schedules to the current fault scenario and, thus, reduce the overhead due to fault tolerance. We use a fault-tolerant process graph representation (FTPG) to model the application: conditional edges are used for modelling fault occurrences, while synchronization nodes capture the fine-grained transparency requirements. The synthesis problem is formulated as an FTPG scheduling problem.

In this work, we also present an optimization algorithm that produces a mapping of processes on computation nodes such that the application is schedulable and the fault tolerance and transparency properties imposed by the designer are satisfied.

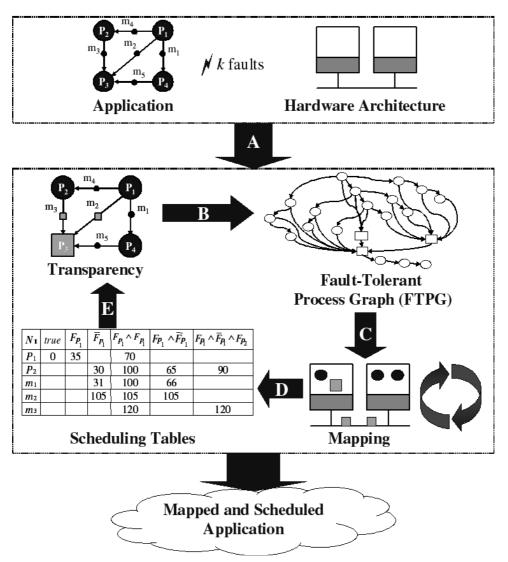

## 2. OVERALL SYNTHESIS FLOW

Our overall synthesis flow is outlined in Fig. 1. The application is modelled as a set of processes communicating using messages, which runs on the hardware architecture composed of a set of computation nodes connected to a communication bus (as described in Section 3). The fault tolerance and real-time constraints, such as the maximum number k of transient faults and process deadlines, are provided as input.

The actual synthesis and optimization is performed in several steps:

(A) The designer introduces transparency requirements, by selecting a set of processes and messages to be frozen. For example, designers can select important data communications as frozen for observing process inputs and outputs and for evaluation of timing properties of processes and messages.

(B) The application, with introduced transparency requirements, is translated into a fault-tolerant process graph (FTPG). The FTPG representation, presented in Section 7.1, captures the transparency properties and all possible combinations of fault occurrences.

Fig. 1. Overall Synthesis Flow.

(C) The FTPG is passed over to the mapping optimization algorithm (Section 6.3). The algorithm optimizes the placement of application processes on the computation nodes and uses as a cost function the estimated schedule length (Section 7.4).

(D) Considering the mapping solution produced in the previous step, a fault-tolerant conditional schedule is synthesized as a set of schedule tables (Section 7.3). A distributed run time scheduler will use these schedule tables for execution of the application processes on the computation nodes.

(E) If the application is unschedulable, the designer has to change the transparency setup, re-considering the transparency/performance trade-offs.

The rest of the paper is organized as follows. Section 3 presents our application and system model. Section 4 introduces our fault model for multiple transient faults. Section 5 introduces transparency and illustrates the performance/transparency trade-offs on a set of motivational examples. Section 6 presents our problem formulation and overall design optimization strategy. Section 7 introduces the FTPG representation and presents our conditional scheduling algorithm for synthesis of fault-tolerant schedules as well as our schedule length estimation heuristic. The proposed scheduling and mapping algorithms are evaluated on a set of synthetic applications and a real-life example in Section 8. Conclusions are presented in Section 9.

## 3. APPLICATION AND SYSTEM MODEL

We consider a set of real-time applications. Each application  $A_k$  is represented as an acyclic directed graph  $G_k(V_k, E_k)$ . Each process graph  $G_k$  is executed with period  $T_k$ . The graphs for all applications are merged into a single graph with a period T obtained as a least common multiple (LCM) of all periods  $T_k$  [Pop et al., 2004]. This graph corresponds to a virtual application A, represented as a directed acyclic graph G(V, E). Each node  $P_i \in V$  represents one process. An edge  $e_{ij} \in E$  from  $P_i$  to  $P_j$  indicates that the output of  $P_i$  is the input of  $P_i$ .

Processes are not preempted during their execution. A process can be activated after all its inputs have arrived. The process issues its outputs, encapsulated in messages, when it completes.

Time constraints are imposed with a global hard deadline  $D \le T$ , at which the application *A* has to complete. In addition, processes can be associated with individual deadlines. An individual hard deadline  $d_i$  of a process  $P_i$  is modelled as a dummy node

inserted into the application graph with the execution time  $C_{dummy} = D - d_i$  [Pop et al., 2004]. This dummy node however, is not allocated to any resource.

We consider that the application is running on a set of computation nodes N connected to a bus B. The mapping of processes in the application is determined by a function  $M: V \to N$ . For a process  $P_i \in V$ ,  $M(P_i)$  is the node to which  $P_i$  is assigned for execution. Let  $N_{P_i} \subseteq N$  be the set of nodes, to which  $P_i$  can be potentially mapped. We know the worst-case execution time (WCET)  $C_{P_i}^{N_k}$  of process  $P_i$ , when executed on each node  $N_k \in N_{P_i}$  [Puschner and Burns, 2000]. Processes mapped on different computation nodes communicate with a message sent over the bus. We consider that the worst-case size of messages is given and we implicitly translate it into the worst-case transmission time on the bus. If processes are mapped on the same node, the message transmission time between them is accounted for in the worst-case execution time of the sending process.

Each computation node  $N_j$  has a real-time kernel as its main component. The kernel invokes processes, mapped on  $N_j$ , according to the schedule table located in this node. This local schedule table contains all the information that is needed for activation of processes and for sending and receiving communication messages [Pop et al., 2004]. We consider a static bus, which allows sending messages at different times as long as these times are specified in the bus schedule. However, our work can be also used with the static bus that has a limited number of mode changes such as, for example, a TTP bus [Kopetz and Bauer, 2003]. In this case, a frame-packing mechanism can be implemented for incorporating messages [Pop et al., 2005].

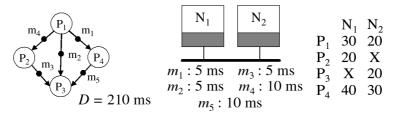

In Fig. 2 we have an application A consisting of the process graph G with four processes,  $P_1$ ,  $P_2$ ,  $P_3$ , and  $P_4$ . Processes communicate with messages  $m_1$ ,  $m_2$ ,  $m_3$ ,  $m_4$  and  $m_5$ . The deadline is D = 210 ms. The execution times for the processes, if mapped on computation nodes  $N_1$  and  $N_2$ , are shown in the table on the right side. "X" in the table

Fig. 2. Application Example.

indicates a mapping restriction, i.e., process  $P_2$  can only be mapped on node  $N_1$ , and process  $P_3$  can only be mapped on node  $N_2$ . The transmission times of messages, if transmitted over the bus, are also indicated in the figure.

## 4. FAULT TOLERANCE

In this paper we are interested in fault-tolerance techniques for transient faults. In our model, we consider that at most k transient faults may occur anywhere in the system during one operation cycle of the application. The number of faults can be larger than the number of computation nodes in the system. Several transient faults may occur simultaneously on several computation nodes as well as several faults may occur on the same computation node. In this paper, we assume that transient faults on the bus are addressed at the communication level, for example, with the use of efficient error correction codes [Piriouet al., 2006; Balakirsky and Vinck, 2006; Emani et al., 2007]and/or through hardware replication of the bus [Kopetz and Bauer, 2003; Silva et al., 2007].

The fault-tolerance mechanisms against transient faults on computation nodes are part of the software architecture. The software architecture, including the real-time kernel, error detection and fault-tolerance mechanisms, are themselves fault-tolerant.

We first need to detect the transient faults in order to apply fault tolerance techniques. Error detection can be hardware-based (e.g., watchdogs [Benso et al., 2003], signature checking [Sciuto et al., 1998]) or software-based [Oh et al., 2002a; Nicolescu et al., 2004; Oh et al., 2002b]. We assume that all faults can be found using the above error detection methods. The time needed for detection of faults is accounted for as part of the worstcase execution time (WCET) of the process.

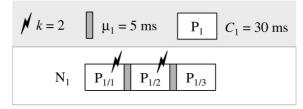

We use process re-execution as a fault tolerance mechanism. The process reexecution operation requires an additional recovery overhead denoted in this paper as  $\mu$ . The recovery overhead includes the worst-case time that is needed in order to restore process inputs, clean up the node's memory, and re-start process execution. Let us consider the example in Fig. 3, where we have process  $P_1$  and a fault-scenario consisting of k = 2 transient faults that can happen during one cycle of operation. In the worst-case fault scenario depicted in Fig. 3, the first fault happens during the process  $P_1$ 's first execution, and is detected by the error detection mechanism. After a worst-case *recovery overhead* of  $\mu_1 = 5$  ms, depicted with a light gray rectangle,  $P_1$  will be executed again. Its second execution in the worst-case could also experience a fault. Finally, the third execution of  $P_1$  will succeed.

Fig. 3. Re-execution.

# 5. TRANSPARENCY

In this paper, we propose a fine-grained approach to transparency offering the designer the possibility to trade-off transparency for performance. Given an application A(V, E) we will capture the transparency using a function  $T: W \rightarrow \{Frozen, Regular\}$ , where W is the set of all processes and messages. If  $T(w_i) = Frozen$ , our scheduling algorithm will handle this transparency requirement (a) by scheduling  $w_i$ , if it is a message, at the same transmission time in all alternative execution scenarios and (b) by scheduling the *first* execution instance of  $w_i$ , if it is a process, at the same start time in all alternative execution scenarios. In a fully transparent system, all messages and processes are frozen. Systems with a node-level transparency [Kandasamy et al., 2003a; Izosimov et al., 2005; Pop et al., 2009] support a limited transparency setup, in which all the inter-processor messages are frozen while all processes are regular. In such a scheme, system behavior can be observed only by monitoring messages sent to and out of the computation node. It leads to both reduced observability and unnecessary end-to-end delays.

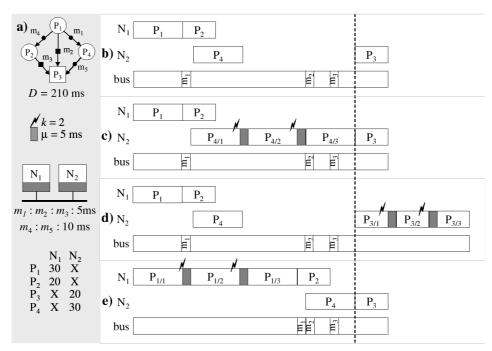

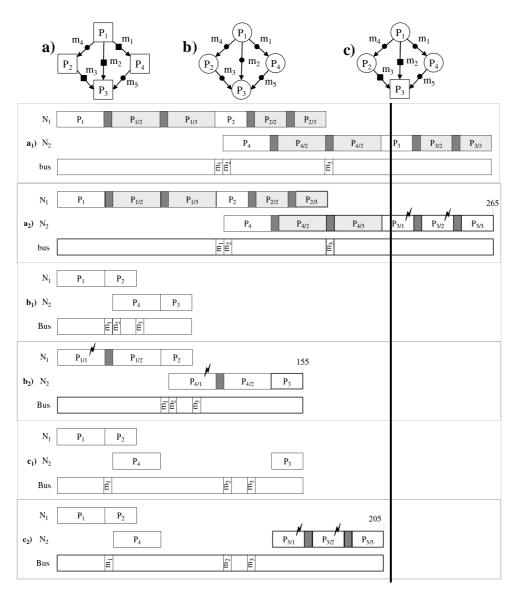

In the example in Fig. 4a, we introduce transparency properties into the application A from Fig. 2. We make process  $P_3$  and messages  $m_2$  and  $m_3$  frozen, i.e.,  $T(m_2) = Frozen$ ,  $T(m_3) = Frozen$  and  $T(P_3) = Frozen$ . We will depict frozen processes and messages with squares, while the regular ones are represented by circles. The application has to tolerate k = 2 transient faults, and the recovery overhead  $\mu$  is 5 ms. Processes  $P_1$  and  $P_2$  are mapped on  $N_1$ , and  $P_3$  and  $P_4$  are mapped on  $N_2$ . Messages  $m_1$ ,  $m_2$  and  $m_3$  are scheduled on the bus. Four alternative execution scenarios are illustrated in Fig. 4b-e.

The schedule in Fig. 4b corresponds to the fault free scenario. Once a fault occurs in  $P_4$ , for example, the scheduler on node  $N_2$  will have to switch to another schedule. In this schedule,  $P_4$  is delayed with  $C_4 + \mu$  to account for the fault, where  $C_4$  is the worst-case execution time of process  $P_4$  and  $\mu$  is the recovery overhead. If, during the second

Fig. 4. Application with Transparency.

execution of  $P_4$ , a second fault occurs, the scheduler has to switch to another schedule illustrated in Fig. 4c.

Since  $P_3$ ,  $m_2$  and  $m_3$  are frozen they should be scheduled at the same time in all alternative fault scenarios. For example, re-executions of process  $P_4$  in case of faults in Fig. 4c must not affect the start time of process  $P_3$ . The first instance of process  $P_3$  has to be always scheduled at the same latest start time in all execution scenarios, as illustrated with a dashed line crossing Fig. 4. Even if no faults happen in process  $P_4$ , in the execution scenarios depicted in Fig. 4d and Fig. 4b, process  $P_3$  will have to be delayed. It leads to a worst-case schedule as in Fig. 4d. Similarly, idle times are introduced before messages  $m_2$  and  $m_3$ , such that possible re-executions of processes  $P_1$  and  $P_2$  do not affect the sending times of these messages. Message  $m_1$ , however, will be sent at different times depending on fault occurrences in  $P_1$ , as illustrated in Fig. 4e.

In Section 5.1, we further illustrate the transparency/performance trade-offs. In Section 5.2, we will discuss the importance of considering transparency properties during mapping.

# 5.1 Transparency/Performance Trade-offs

In Fig. 5 we illustrate three alternatives, representing different transparency/performance setups for the application A in Fig. 2. The entire system has to tolerate k = 2 transient faults in the hyperperiod of the application, and the recovery overhead  $\mu$  is 5 ms. Processes  $P_1$  and  $P_2$  are mapped on  $N_1$ , and  $P_3$  and  $P_4$  are mapped on  $N_2$ . For each transparency alternative (a–c), we show the schedule when no faults occur (a<sub>1</sub>–c<sub>1</sub>) and also depict the worst-case scenario, resulting in the longest schedule (a<sub>2</sub>–c<sub>2</sub>). The end-to-

Fig. 5. Trade-off between Transparency and Performance

end worst-case delay of an application will be given by the maximum finishing time of any alternative schedule. Thus, we would like the worst-case schedules in Fig.  $5a_2$ - $c_2$  to meet the deadline of 210 ms depicted with a thick vertical line.

In Fig.  $5a_1$  and  $5a_2$  we show a schedule produced with a *fully transparent* alternative, in which all processes and messages are frozen. We can observe that processes and messages are scheduled at the same time, indifferent of the actual occurrence of faults. The shaded slots in the schedules indicate the intervals reserved for re-executions that are needed to recover from fault occurrences. In general, a *fully transparent* approach, as depicted in Fig.  $5a_1$  and Fig.  $5a_2$ , has the drawback of producing long schedules due to complete lack of flexibility. The worst-case end-to-end delay in the case of full transparency, for this example, is 265 ms, which means that the deadline is missed.

The alternative in Fig. 5b does not have any transparency restrictions. Fig. 5b<sub>1</sub> shows the execution scenario if no fault occurs, while 5b<sub>2</sub> illustrates the worst-case scenario. In the case without frozen processes/messages, a fault occurrence in a process  $P_i$  can affect the schedule of another process  $P_j$ . This allows to build schedules customized to the actual fault scenarios and, thus, are more efficient. In Fig. 5b<sub>2</sub>, for example, a fault occurrence in  $P_1$  on  $N_1$  will cause another node  $N_2$  to switch to an alternative schedule that delays the activation of  $P_4$ .  $P_4$  receives message  $m_1$  from  $P_1$ . This would lead to a worst-case end-to-end delay of only 155 ms, as depicted in Fig. 5b<sub>2</sub>, that meets the deadline.

However, transparency could be highly desirable and a designer would like to introduce transparency at certain points of the application without violating the timing constraints. In Fig. 5c, we show a setup with a fine-grained, customized transparency, where process  $P_3$  and its input messages  $m_2$  and  $m_3$  are frozen. In this case, the worst-case end-to-end delay of the application is 205 ms, as depicted in Fig. 5c<sub>2</sub>, and the deadline is still met.

## 5.2 Mapping with Transparency Constraints

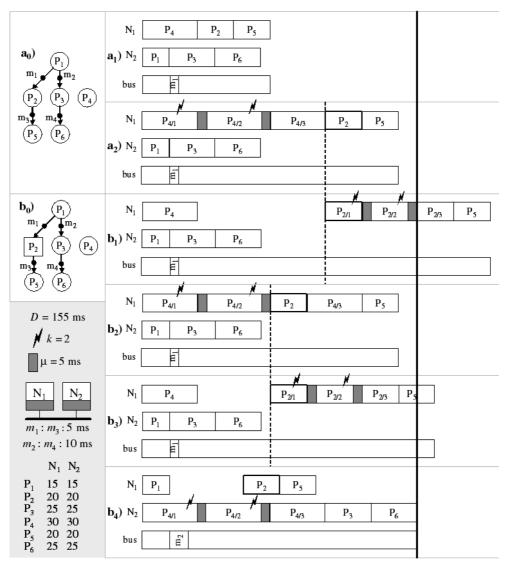

In Fig. 6 we consider an application consisting of six processes,  $P_1$  to  $P_6$ , that have to be mapped on an architecture consisting of two computation nodes connected to a bus. We assume that there can be at most k = 2 faults during one cycle of operation. The worstcase execution times for each process on each computation node are depicted in the figure. We impose a deadline of 155 ms for the application.

If we do not impose any transparency requirements, i.e., all processes and messages are regular, the optimal mapping is the following: processes  $P_2$ ,  $P_4$  and  $P_5$  are mapped on

node  $N_1$ , while  $P_1$ ,  $P_3$  and  $P_6$  on node  $N_2$ . For this mapping, Fig. 6a<sub>1</sub> shows the non-fault scenario, while Fig. 6a<sub>2</sub> depicts the worst-case scenario. As observed, the application is schedulable.

If the same mapping determined in Fig. 6a is used with considering process  $P_2$  frozen, the worst-case scenario is depicted in Fig. 6b<sub>1</sub>. In order to satisfy transparency (start time of  $P_2$  identical in all scenarios) the start time of  $P_2$  is delayed according to the worst-case finishing time of  $P_4$ . Thus, the deadline is violated. We will improve the schedule for the worst-case scenario if process  $P_2$  is inserted between re-executions of process  $P_4$ , as

Fig. 6. Mapping and Transparency.

shown in Fig. 6b<sub>2</sub>. In this case, process  $P_2$  will always start at 70 ms. Even though the worst-case scenario depicted in Fig. 6b<sub>3</sub> is better than the one in Fig. 6b<sub>1</sub>, the deadline is, as before, violated. Only another mapping will make the system schedulable with a frozen  $P_2$ : processes  $P_1$ ,  $P_2$  and  $P_5$  are mapped on node  $N_1$ , while processes  $P_3$ ,  $P_4$  and  $P_6$  are mapped on node  $N_2$ . The worst-case scenario, according to this mapping, is depicted in Fig. 6b<sub>4</sub>. Counterintuitively, this mapping is less balanced and the amount of communications is increased compared to the previous solution, since we send message  $m_2$  that is two times larger than  $m_1$ . Nevertheless, in this case the deadline is satisfied. This illustrates that a mapping optimal for an unrestricted design is unsuitable if transparency is imposed.

# 6. FAULT-TOLERANT SCHEDULING AND DESIGN OPTIMIZATION

In this section, we formulate the design problem and present our design optimization strategy.

# 6.1 Problem Formulation

As an input, we get a virtual application A, composed from a set of applications  $A_k$  (see Section 3). Application A runs on a bus-based architecture consisting of a set of hardware nodes N interconnected via a broadcast bus B. The transparency requirements T on the application, the deadlines, the maximum number k of transient faults, and the recovery overhead  $\mu$  are given. We know the worst-case execution times for each process on each computation node. The maximum transmission time for all messages, if sent over the bus B, is given.

As an output, we have to produce (1) the mapping of the processes to the computation nodes and (2) the fault-tolerant schedule S, such that maximum k transient faults are tolerated by re-execution, the transparency requirements are considered, and deadlines are satisfied even in the worst-case fault scenario.

## 6.2 Overall Strategy

The design problem outlined above is NP complete [Ullman, 1975] and is, therefore, addressed using heuristics. In our strategy, illustrated in Fig. 7, we start by determining an initial mapping  $M_{init}$  with the InitialMapping function (line 1). This is a straightforward mapping that balances computation node utilization and minimizes communications. The schedulability of the resulted system is evaluated with the conditional scheduling algorithm (lines 2–3) from Section 7.3. If the initial mapping is unschedulable, then we iteratively improve the mapping of processes on the critical path of the worst-case fault scenario aiming at finding a schedulable solution (lines 4–9). For this purpose, we use a hill-climbing mapping heuristic that combines a greedy algorithm and a method to recover from local optima.

A new mapping alternative  $M_{new}$  is obtained with a greedy algorithm, IterativeMapping (line 5), presented in Section 6.3. The algorithm uses as a cost function the schedule length estimated with the heuristic presented in Section 7.4, in order to evaluate the intermediate mapping decisions. This approach, where we use estimation instead of the actual scheduling, reduces the runtime and speeds-up the optimization. However, the final mapping solution obtained with the IterativeMapping has to be evaluated with the actual conditional scheduling algorithm (line 6) from Section 7.3. The scheduling algorithm will produce the schedule tables and will determine exactly if the application with the proposed mapping is schedulable.

Since IterativeMapping is a greedy heuristic it will very likely end up in a local minimum  $M_{new}$ . If  $M_{new}$  is not schedulable, in order to explore other areas of the design space, we will restart the IterativeMapping heuristic with a new initial solution  $M_{init}$ . This

```

Optimization Strategy(G, T, k, N, B, D)

M_{init} = InitialMapping(G, N, B)

g = FTScheduleSynthesis(G, T, k, N, B, M_{init})

if deadlines are met then return M_{init}

while not_termination do

M_{new} = IterativeMapping(G, T, k, N, B, M)

g = FTScheduleSynthesis(G, T, k, N, B, M)

g = FTScheduleSynthesis(G, T, k, N, B, M_{new})

if deadlines are met then return {M_{new}, S}

M_{init} = FindNewInit(G, N, B, M_{new})

end while

return no_solution

end OptimizationStrategy

```

Fig. 7. Optimization Strategy.

solution is constructed such that it will reduce the likelihood of ending in the same local minimum again. As recommended in literature [Reevs, 1993], we perform a diversification of the current solution by running another mapping optimization with a cost function different from the "goal" cost function of the lterativeMapping algorithm. This optimization will produce a new mapping  $M_{init}$  and is implemented by the function FindNewInit (line 8). This function runs a simple greedy iterative mapping, which, instead of the schedule length, is aiming at an optimal load balancing of the nodes.

If the solution produced by IterativeMapping is schedulable then the optimization will stop (line 7). However, a termination criterion is needed in order to terminate the mapping optimization if no solution is found. A termination criterion, which we have obtained empirically, is to limit the number of consecutive iterations without any improvement of the schedule length to  $N_{proc} \times k \times ln(N_{compnodes})$ , where  $N_{proc}$  is the number of processes,  $N_{compnodes}$  is the number of computation nodes, and k is the maximum number of faults in the system period. An increase in any of these parameters would contribute to the increase of the design space exploited by our mapping heuristic. In particular, the number of computation nodes contributes to the most significant increase in the design space. Thus, we use  $ln(N_{compnodes})$  to capture this issue. Note that the design space does not grow linearly with the increase of these parameters, i.e., it grows exponentially. However, formula  $N_{proc} \times k \times ln(N_{compnodes})$  allows us to efficiently capture this growth, yet without dramatic increase in the execution time of the algorithm.

## 6.3 Iterative Mapping Heuristic

Our mapping algorithm, IterativeMapping, depicted in Fig. 8 is a greedy algorithm that incrementally changes the mapping M until no further improvement (line 3) is produced. Our approach is to tentatively change the mapping of processes on the critical path of the application graph G. The critical path CP is found by the function FindCP (line 6). Each process  $P_i$  in the list CP is then tentatively moved to each node in N. We evaluate each move in terms of schedule length, considering transparency properties T and the number of faults k (line 10).

The calculation of the schedule length should, in principle, be performed by conditional scheduling (FTScheduleSynthesis function, see Section 7.3). However, conditional scheduling takes too long time to be used inside such an iterative optimization loop. Therefore, we have developed a fast schedule length estimation heuristic, ScheduleLengthEstimation, presented in Section 7.4. This heuristic is used to guide the lterativeMapping algorithm.

Iterative Mapping (GT, K, N, B, M) improvement := true  $I_{\text{hest}}$  := ScheduleLength Estimation(G, T, k, N, B, M) while improvement do improvement := false P<sub>best</sub> := ; N<sub>best</sub> := CP := FindCP(G)for processes  $P_i \in CP$  do for each  $N_i = N_c$  do Change Mapping  $(M, P_i, N_i)$ Inew := ScheduleLengthEstimation (G T, K, N, B, M) RestoreMapping(M) if I<sub>new</sub> < I<sub>best</sub> then  $P_{best} := P_i N_{best} := N_i I_{best} := I_{new}$ *improvement* := true end if end for end for if improvement then ChangeMapping  $(M, P_{best}, N_{best})$ end while return M endIterativeMapping

Fig. 8. Iterative Mapping Heuristic (IMH).

After evaluating possible alternatives, the best move consisting of the best process  $P_{best}$  and the best target computation node  $N_{best}$  is selected (lines 12–15). This move is executed if leading to an improvement (line 18). IterativeMapping will stop if there is no further improvement.

The final solution produced with the IterativeMapping heuristic will have to be evaluated with the conditional scheduling algorithm, as discussed in the previous section (see line 6 in Fig. 7). If the final solution is valid according to this evaluation, we will conclude that the system is schedulable. If the solution is not valid, IterativeMapping will be run once again after performing diversification of the obtained mapping solution with the FindNewInit function (line 8, Fig. 7).

# 7. CONDITIONAL SCHEDULING

Our conditional scheduling technique is based on the fault-tolerant process graph (FTPG) representation and generates, as output, a set of schedule tables. Schedule tables, discussed in Section 7.2, are used by a distributed run time scheduler for executing processes on the computation nodes.

## 7.1 Fault-Tolerant Process Graph

The scheduling technique presented in this section is based on the fault-tolerant process graph (FTPG) representation. FTPG captures alternative schedules in the case of different fault scenarios. Every possible fault occurrence is considered as a condition that is "true" if the fault happens and "false" if the fault does not happen. FTPG allows to efficiently and correctly model recovery in the context of multiple transient faults, which is utilized by our conditional scheduling algorithm.

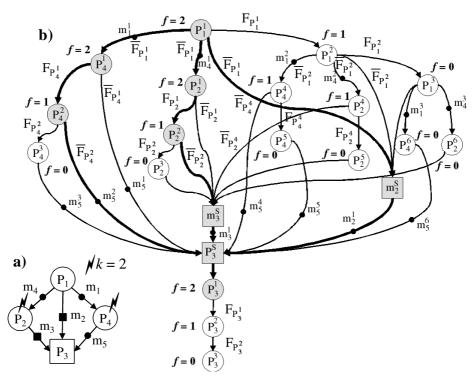

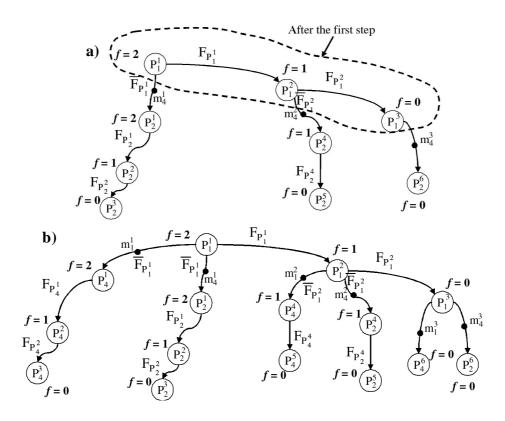

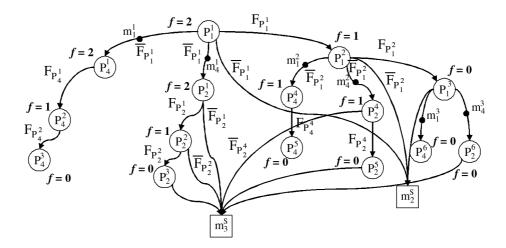

In Fig. 9a we have an application A modelled as a process graph G. The application A can experience at most two transient faults (for example, one during the execution of process  $P_2$ , and one during  $P_4$ , as illustrated in the figure). Transparency requirements are depicted with rectangles on the application graph, where process  $P_3$ , message  $m_2$  and message  $m_3$  are set to be frozen. For scheduling purposes we will convert the application A to a fault-tolerant process graph (FTPG) G, represented in Fig. 9b. In an FTPG the fault occurrence information is represented as *conditional edges* and the frozen processes/messages are captured using *synchronization nodes*. One of the conditional edges, for

Fig. 9. Fault-Tolerant Process Graph.

example, is  $P_1^1$  to  $P_4^1$  in Fig. 9b, with the associated condition  $\overline{F}_{P_1^1}$  denoting that  $P_1^1$  has no faults. Message transmission on conditional edges takes place only if the associated condition is satisfied.

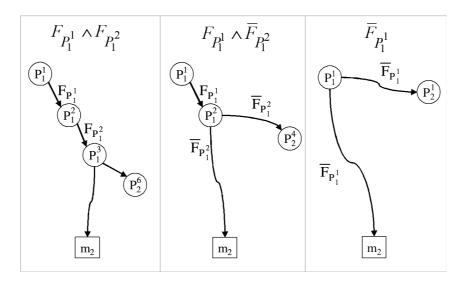

The FTPG in Fig. 9b captures all the fault scenarios that can happen during the execution of application A in Fig. 9a. The subgraph marked with thicker edges and shaded nodes in Fig. 9b captures the execution scenario when processes  $P_2$  and  $P_4$ experience one fault each. We will refer to every such subgraph corresponding to a particular execution scenario as an alternative trace of the FTPG. The fault occurrence possibilities for a given process execution, for example  $P_2^1$ , the first execution of  $P_2$ , are captured by the conditional edges  $F_{P_1^{i}}$  (fault) and  $\overline{F}_{P_2^{i}}$  (no-fault). The transparency requirement that, for example,  $P_3$  has to be frozen, is captured by the synchronization node  $P_3^{S}$ , which is inserted, as shown in Fig. 9b, before the copies corresponding to the possible executions of process  $P_3$ . The first execution copy  $P_3^1$  of process  $P_3$  has to be immediately scheduled after its synchronization node  $P_3^S$ . In Fig. 9b, process  $P_1^1$  is a conditional process because it "produces" condition  $F_{P_1^1}$ , while  $P_1^3$  is a regular process. In the same figure,  $m_2^S$  and  $m_3^S$ , similarly to  $P_3^S$ , are synchronization nodes (depicted with a rectangle). Messages  $m_2$  and  $m_3$  (represented with their single copies  $m_2^1$  and  $m_3^1$ in the FTPG) have to be immediately scheduled after synchronization nodes  $m_2^S$  and  $m_3^S$ , respectively.

Regular and conditional processes are activated when all their inputs have arrived. A synchronization node, however, is activated after inputs coming on one of the alternative paths, corresponding to a particular fault scenario, have arrived. For example, a transmission on the edge  $e_{12}^{1S_m}$ , labeled  $\overline{F}_{p_1}$ , will be enough to activate  $m_2^S$ .

A guard is associated to each node in the graph. An example of a guard associated to a node is, for example,  $K_{P_2^2} = \overline{F}_{P_1^1} \wedge F_{P_2^1}$ , indicating that  $P_2^2$  will be activated in the fault scenario where  $P_2$  will experience a fault, while  $P_1$  will not. A node is activated only in a scenario corresponding to which the value of the associated guard is true. **Definition.** Formally, an FTPG corresponding to an application A = G(V, E) is a directed acyclic graph  $G(V_P \cup V_C \cup V_T, E_S \cup E_C)$ . We will denote a node in the FTPG with that will correspond to the  $m^{th}$  copy of process  $P_i \in V$ . Each node  $P_i^m \in V_P$ , with simple edges at the output, is a regular node. A node  $P_i^m \in V_C$ , with *conditional edges* at the output, is a *conditional process* that produces a condition.

Each node  $v_i \in V_T$  is a synchronization node and represents the synchronization point corresponding to a frozen process or message. We denote with  $P_i^S$  the synchronization node corresponding to process  $P_i \in A$  and with  $m_i^S$  the synchronization node corresponding to message  $m_i \in A$ . Synchronization nodes will take zero time to execute.

$E_S$  and  $E_C$  are the sets of simple and conditional edges, respectively. An edge  $e_{ij}^{mn} \in E_S$  from  $P_i^m$  to  $P_j^n$  indicates that the output of  $P_i^m$  is the input of  $P_j^n$ . Synchronization nodes  $P_i^S$  and  $m_i^S$  are also connected through edges to regular and conditional processes and other synchronization nodes:

- $e_{ii}^{mS} \in E_S$  from  $P_i^m$  to  $P_i^S$ ;

- $e_{ij}^{Sn} \in E_S$  from  $P_i^S$  to  $P_j^n$ ;

- $e_{ij}^{mS_m} \in E_S$  from  $P_i^m$  to  $m_j^S$ ;

- $e_{ij}^{S_m n} \in E_S$  from  $m_i^S$  to  $P_j^n$ ;

- $e_{ij}^{SS} \in E_S$  from  $P_i^S$  to  $P_j^S$ ;

- $e_{ij}^{S_mS} \in E_S$  from  $m_i^S$  to  $P_j^S$ ;

- $e_{ij}^{SS_m} \in E_S$  from  $P_i^S$  to  $m_j^S$ ; and

- $e_{ij}^{S_m S_m} \in E_S$  from  $m_i^S$  to  $m_j^S$ .

Edges  $e_{ij}^{mn} \in E_C$ ,  $e_{ij}^{mS} \in E_C$ , and  $e_{ij}^{mS_m} \in E_C$  are *conditional edges* and have an associated condition value. The condition value produced is "true" (denoted with  $F_{P_i^m}$ ) if  $P_i^m$  experiences a fault, and "false" (denoted with  $\overline{F}_{P_i^m}$ ) if  $P_i^m$  does not experience a fault. Alternative paths starting from such a process, which correspond to complementary

values of the condition, are disjoint<sup>2</sup>. Note that edges  $e_{ij}^{Sn}$ ,  $e_{ij}^{S_mn}$ ,  $e_{ij}^{SS}$ ,  $e_{ij}^{S_mS}$ ,  $e_{ij}^{Sm}$ , and  $e_{ii}^{S_mS_m}$  coming from a synchronization node cannot be conditional.

A boolean expression  $K_{P_i^m}$ , called guard, is associated to each node  $P_i^m$  in the graph. The guard captures the necessary activation conditions (fault scenario) for the respective node.<sup>3</sup>

## 7.2 Schedule Table

The output produced by the FTPG scheduling algorithm that will be discussed in the next section is a schedule table that contains all the information needed for a distributed run time scheduler to take decisions on activation of processes and sending of messages. It is considered that, during execution, a very simple non-preemptive scheduler located in each node decides on process and communication activation depending on the actual fault occurrences.

Only one part of the table has to be stored in each node, namely, the part concerning decisions that are taken by the corresponding scheduler, i.e., decisions related to processes located on the respective nodes. Fig. 10 presents the schedules for nodes  $N_1$  and  $N_2$ , which will be produced by the conditional scheduling algorithm in Fig. 11 for the FTPG in Fig. 9. Processes  $P_1$  and  $P_2$  are mapped on node  $N_1$ , while  $P_3$  and  $P_4$  on node  $N_2$ .

In each table there is one row for each process and message from application A. A row contains activation times corresponding to different guards, or *known conditional values*, that are depicted as a conjunction in the head of each column in the table. A particular conditional value in the conjunction indicates either a success or a failure of a certain process execution. The value, "true" or "false", respectively, is produced at the end of each process execution (re-execution) and is immediately *known* to the computation node on which this process has been executed. However, this conditional value generated on one computation node has to be *broadcasted* to the other computation nodes, encapsulated in a *signalling message*. Signalling messages have to be sent at the earliest possible time since the conditional values are used to take the best possible decisions on process activation [Eles et al., 2000]. Only when the condition is known,

<sup>&</sup>lt;sup>2</sup>They can only meet in a synchronization node.

<sup>&</sup>lt;sup>3</sup>We present the algorithm for FTPG generation in Appendix I.

i.e., has arrived with a signalling message, a decision will be taken that depends on this condition. In the schedule table, there is one row for each signalling message with the condition whose value has to be broadcasted to other computation nodes.

According to the schedule for node  $N_1$  in Fig. 10a, process  $P_1$  is activated unconditionally at the time 0, given in the first column of the table. Activation of the rest of the processes, in a certain execution cycle, depends on the values of the conditions, i.e., the occurrence of faults during the execution of certain processes. For example, process  $P_2$  has to be activated at t = 30 if  $\overline{F}_{P_1^{1}}$  is true (no fault in  $P_1$ ), at t = 100 if

$F_{P_1^1} \wedge F_{P_1^2}$  is true (faults in  $P_1$  and its first re-execution), etc.

To produce a deterministic behavior globally consistent for any combination of conditions (faults), the table has to fulfill several requirements:

- 1. No process will be activated if, for a given activation, the conditions required for its activation are not fulfilled.

- 2. Activation times have to be uniquely determined by the conditions.

- 3. Activation of a process  $P_i$  at a certain time *t* has to depend only on condition values determined at the respective moment *t* and are *known* to the processing element that executes  $P_i$ .

| $F_{P_2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                                       |                 |       | _   |             |             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------|-----------------|-------|-----|-------------|-------------|--|

| $\overline{F}_{P_1} \sim$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                                       |                 |       | 120 |             |             |  |

| $\tilde{N}_{P_2}^{-1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        |                                       |                 |       | 120 |             |             |  |

| $\bar{F}_{P_1} \wedge F_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |                                       |                 |       | 12  |             |             |  |

| $\overline{F}_{P_1} {\sim} F_{P_2} {\sim} F_{P_2} {\sim} F_{P_2} {\sim}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        | $80(P_2^3)$                           |                 |       | 120 |             |             |  |

| $\overline{F}_{P_1} \sim F_{P_2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        | 55 $(P_2^2)$                          |                 |       |     |             |             |  |

| $F_{\vec{P_l}} \wedge \bar{F}_{\vec{P_2}} \wedge \bar{F}_{\vec{P_2}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |                                       |                 |       | 120 |             |             |  |

| $\bar{F}_{\vec{P}^{1}} = \left[ F_{\vec{P}^{1}} \wedge F_{\vec{P}^{2}} \right] \left[ F_{\vec{P}^{1}} \wedge \bar{F}_{\vec{P}^{2}} = \left[ F_{\vec{P}^{1}} \wedge \bar{F}_{\vec{P}^{2}} + \bar{F}_{\vec{P}^{2}} + \bar{F}_{\vec{P}^{1}} + \bar{F}_{\vec{P}^{$ |                        | 90 $(P_2^5)$                          |                 |       | 120 |             |             |  |

| $F_{P_{\rm l}} \stackrel{-}{\sim} F_{P_{\rm l}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        | $30 (P_2^1)  100 (P_2^6)  65 (P_2^4)$ | $66(m_1^2)$     | 105   |     |             |             |  |