# Selective Harmonic Mitigation Technique for Cascaded H-Bridge Converters with Non-Equal DC Link Voltages

J. Napoles, *Member, IEEE*, A. J. Watson, *Member, IEEE*, J. J. Padilla, J. I. Leon, *Member*, L. G. Franquelo, *Fellow Member, IEEE*, P. W. Wheeler, *Member, IEEE* and M. A. Aguirre, *Member, IEEE*

Abstract-Multilevel converters have received increased interest recently as a result of their ability to generate high quality output waveforms with a low switching frequency. This makes them very attractive for high power applications. A Cascaded H-Bridge converter is a multilevel topology which is formed from the series connection of H-Bridge cells. Optimized pulse width modulation techniques such as Selective Harmonic Elimination (SHE-PWM) or Selective Harmonic Mitigation (SHM-PWM) are capable of pre-programming the harmonic profile of the output waveform over a range of modulation indices. Such modulation methods may however not perform optimally if the DC links of the Cascaded H-Bridge Converter are not balanced. This paper presents a new SHM-PWM control strategy which is capable of meeting grid codes even under non-equal DC link voltages. The method is based on the interpolation of different sets of angles obtained for specific situations of imbalance. Both simulation and experimental results are presented to validate the proposed control method.

## I. INTRODUCTION

Multilevel converters have become the focus of research in recent years as a result of their suitability for high power applications [1]. Amongst the available topologies are the Neutral Point Clamped (NPC), Flying Capacitor (FC) and Cascaded H-Bridge converters (CHB) [2]. The latter is constructed from a series cascade of three-level H-bridges. This connection enables the converter to produce high quality, high voltage waveforms whilst utilizing low or medium voltage switching devices. This functionality makes this converter an attractive option for grid connected applications such as Uninterruptible Power Supplies, Static VAR compensators, Series and Shunt Compensators etc. [3]–[10].

The use of power electronic converters at high power levels usually demands a reduction in switching frequency in order to ensure that losses caused by the imperfect nature of practical

Manuscript received July 27, 2011. Accepted for publication March 11, 2012. Copyright (c) 2009 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org.

J. J. Padilla is with the automotive division in Infineon A.G., Germany (e-mail: Jose.Padilla@infineon.com).

switching devices does not significantly reduce the converter efficiency. Selective Harmonic Elimination (SHE-PWM), Total Harmonic Distortion Minimization (THDM) and Selective Harmonic Mitigation (SHM-PWM) methods are known to produce waveforms with low switching frequency without compromising waveform quality. For these methods, mathematical functions can be derived using the Fourier analysis of a general switched converter waveform which may be solved to meet a certain pre-defined objective in the waveform [11], [12]. The waveform objectives may include complete elimination (SHE-PWM) or reduction (SHM-PWM) of certain harmonics in the generated waveform or an optimization of this waveform in order for it to meet a particular harmonic code for a certain application [13]. The derived functions, which are transcendental and nonlinear in nature, can be solved for a range of modulation indices using a variety of methods [14]–[18]. The solutions can be stored in lookup tables for use with an appropriate converter control scheme.

For CHB based inverter applications it may be desirable to ensure that each cell of the converter draws equal energy from the DC source that it is connected to. This can be achieved over a single or several fundamental cycles. This would ensure that these sources discharge at the same rate and that each cell of the cascade is utilized evenly. In applications where the DC sources are not exactly equal, distortion may be present in the converter waveform. This occurs because the switching angles for the modulation may have been derived assuming that the DC sources were equal and therefore complete harmonic elimination or the required level of harmonic suppression no longer occurs.

In [19], it was found that a large number of different waveform solutions are required in order to manipulate the power flow through a CHB converter whilst achieving optimal harmonic performance. This large number of solutions can be avoided by decoupling the cells and independently controlling the modulation index of each cell separately. Unfortunately, this reduction in the number of required lookup tables potentially reduces the waveform quality of the CHB converter as the degrees of freedom available in the multilevel converter waveform are not fully utilized.

This paper presents a SHM-PWM technique based on multilevel waveforms which enables the required control of power flow in a CHB converter whilst fully utilizing the waveform degrees of freedom. The method uses the interpolation of

J. Napoles, J. I. Leon, L. G. Franquelo and M. A. Aguirre are with the Electronic Engineering Department, University of Seville (Spain), (e-mail: jnl@gte.esi.us.es).

A. J. Watson and P. W. Wheeler are with the School of Electrical and Electronic Engineering, The University of Nottingham, NG7 2RD Nottingham, U.K. (email: Alan.Watson@nottingham.ac.uk, Pat.Wheeler@nottingham.ac.uk).

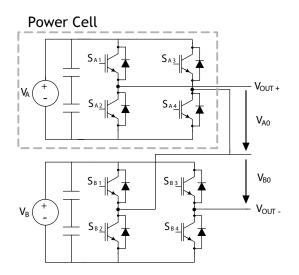

Fig. 1. Five-level cascaded H-bridge converter based on the series connection of two three-level power cells.

lookup table based solutions for a number of imbalances to control the power flow through the H-Bridges asymmetrically, thus avoiding the requirement of very large lookup tables apparent in previous methods [19]. Theoretical and simulated result are experimentally verified using a five level Cascaded H-Bridge topology operating as an inverter.

# II. CASCADED H-BRIDGE CONVERTERS

Several three-level power cells, formed using full H-bridges, can be series connected to build a converter with a higher number of levels as can be observed from Fig. 1. This can be extended to produce converters with as many levels as required for a particular application [20], [21]. In general, if n power cells are connected in series to build the converter and all the cells have the same DC voltage, the number of levels that can be achieved is 2n+1. This topology is named the n-cell CHB converter and it presents a high level of modularity and redundancy as well as an ability to produce high quality output voltage waveforms.

If different DC voltages are used, as is the case in an asymmetric CHB converter, the number of levels can be increased. For example, using two cells, up to nine levels may be achieved in the output waveform. This topology is presented in Fig. 1 where  $V_A$  is the DC voltage of the upper cell and  $V_B$  represents the voltage of the lower cell. However, this increase in voltage levels is achieved at a cost of reduced converter structure modularity.

# A. The problem of imbalance

Each cell of a CHB converter must be fed from an isolated DC source to avoid short circuits. Divergences of the DC link voltages from the desired or assumed values will have an effect on the operation of the converter [6]. If the converter is designed to operate with balanced DC link voltages and this is not the case then the converter is said to be operating under non-equal DC link voltages. Such operation may have an undesirable effect on the output voltage waveform of the

converter. This is especially the case when pre-computed modulation strategies such as SHE-PWM or SHM-PWM are used as the angles may have been derived under the assumption that the DC link voltages are balanced. The SHE-PWM methods require special considerations when used in multilevel converters with non-equal DC link voltages [22].

In many applications it is desirable to share the power flow amongst all the cells equally in order to avoid overheating of some specific switching devices and consequently extend the lifetime of all the elements of the converter [19], [23]. Other, more complicated, CHB based converter structures may require the power flow to be controlled asymmetrically through the converter cells as was required in [24]. In both cases, assuming that the current is undistorted, the power flow from each cell of the converter can be determined by considering the fundamental frequency component of each cell only. It is possible to manipulate SHE-PWM and SHM-PWM techniques to control the power flow through a CHB converter as was shown in [19]. The method considered the use of a low switching frequency SHE-PWM to control power flow through the cells of a CHB converter whilst still producing high quality waveforms. Unfortunately, a disadvantage of the approach presented in [19] is that a specific set of angles must be calculated for each possible imbalance scenario for the converter and therefore a very large number of lookup tables and a complicated lookup table selection scheme would be required to practically implement the method. This paper presents a method which may overcome this disadvantage by attempting to interpolate between lookup tables.

## **III. SHM-PWM PRINCIPLE**

#### A. Three-level converters

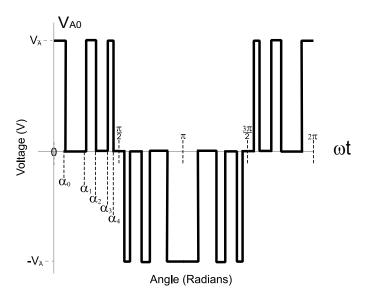

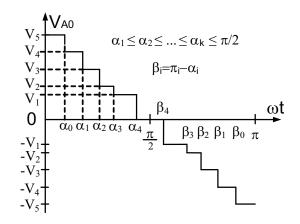

Fourier analysis can be used to study a typical three-level waveform with k switching angles  $\alpha_i$  (*i*=0,...,*k* - 1) (Fig. 2). The amplitude of each harmonic can be obtained using the following expression where  $H_j$  is the amplitude of the  $j^{th}$  harmonic:

$$H_j = \frac{4}{j\pi} \sum_{i=0}^{k-1} \left[ (-1)^i \sin(j\alpha_i) \right]$$

(1)

This expression can be used to set a specific value for each harmonic amplitude using the switching angles as degrees of freedom. The well known SHE-PWM technique is based on this theory i.e. the switching angles are used to set the amplitude of the fundamental harmonic and cancel a set of specific harmonics [11], [12]. The relationship between the DC link voltage of the converter and the amplitude of the generated fundamental component is called the modulation index  $(M_a)$  and can be defined as  $M_a = H_1 \pi / 4V_{dc}$ . As a result of half wave symmetry in the waveform, even harmonics have zero amplitude so the chosen harmonic orders would be 3,5,7,... and up to k-1 harmonics can be canceled using k switching angles. In balanced three-phase topologies without a neutral connection, the triplen harmonics are also canceled and so it is possible to eliminate a very high number of the low order harmonics with a low switching frequency.

Fig. 2. Three-level pre-programmed PWM switching pattern with five switching angles  $(\alpha_0, \alpha_1, \alpha_2, \alpha_3, \alpha_4)$ . Typical output waveform of the top power cell represented in Fig.1

Summarizing, the SHE-PWM technique for three-level converters is based on solving the following system of equations where q is the highest harmonic order that will be canceled:

$$H_{1} = \frac{4}{\pi} \sum_{i=0}^{k-1} \left[ (-1)^{i} \sin(\alpha_{i}) \right]$$

$$0 = \frac{4}{j\pi} \sum_{i=0}^{k-1} \left[ (-1)^{i} \sin(j\alpha_{i}) \right],$$

where  $j = 3, 5, 7, 9, 11, \dots, q.$  (2)

The SHM-PWM technique was presented in [13] and is based on the idea that it is not necessary to completely cancel the harmonics in the converter AC waveform. Instead, they just have to be reduced to levels where they can be considered acceptable. The maximum harmonic content for a grid connected inverter can be obtained from the limits specified in the actual grid codes ( $L_j$  represents the limit for the  $j^{th}$  harmonic). The SHM-PWM technique can be formulated using a system of inequalities (3) which can be arranged into an objective function to be minimized using an optimization method as in 4.

$$\begin{aligned} |\frac{4M_a V_{dc}}{\pi} - H_1| &\leq L_1 \\ \frac{1}{|H_1|} \frac{4}{j\pi} \sum_{i=0}^{k-1} \left[ (-1)^i \sin(j\alpha_i) \right] &\leq L_j, \\ \text{where } j = 3, 5, 7, 9, 11, \dots, 49. \end{aligned}$$

(3)

$$OF(\alpha_0, \dots, \alpha_{k-1}) = \sum_{i=1,3,5,\dots,49} c_i E_i^2 + c_{THD} THD.$$

(4)

The extra flexibility given by the SHM-PWM principle can be used for different objectives, for example reducing the

Fig. 3. Nine-level pre-programmed PWM switching pattern with ten switching angles ( $\alpha_i$ , *i*=0,...,9). The waveform is symmetrical in order to eliminate the even harmonics.

THD, considering a higher number of harmonics using the same number of switching angles, or extending the modulation index range for the same set of valid solutions.

## B. Extension to converters with a higher number of levels

Considering, for instance, a waveform similar to the pattern shown in Fig. 3 but with N levels and k switching angles  $\alpha_i$  (*i*=0,...,*k* - 1) the Fourier analysis gives:

$$H_{j} = \frac{4}{j\pi} \Big( V_{1} \sin(\alpha_{0}) + \sum_{i=1}^{k-1} \Big[ V_{i} [\sin(j\alpha_{i}) - \sin(j\alpha_{i-1})] \Big] \Big)$$

(5)

The SHE-PWM can be applied with this kind of waveform [25]. Again, solving the equations, the fundamental harmonic can be set to the desired value and k - 1 harmonics can be reduced to zero  $(H_j = 0$  where  $j = 3, 5, 7, 9, 11, \ldots, q)$ .

In order to guarantee that all the cells are sharing the same power this system of equations needs to be modified. Instead of using the fundamental harmonic of the global waveform, the fundamental component generated by each cell is forced to be equal to the desired value. This way, for a N-cell converter working with k switching angles per cell only N(k-1) extra harmonics can be canceled. The new system of equations can be formed with (6) and (7) considering that in (7) it is assumed that the angles of all the cells are rearranged to generate the suitable multilevel global waveform.

$$H_{1} = \frac{4}{\pi} \sum_{i=0}^{k-1} \left[ (-1)^{i} \sin(\alpha_{i-Cell-n}) \right],$$

where  $n = 1, 2, \dots, N$  (6)

$$0 = \frac{4}{j\pi} \Big( V_1 \sin(\alpha_0) + \sum_{i=1}^{k-1} \Big[ V_i [\sin(j\alpha_i) - \sin(j\alpha_{i-1})] \Big] \Big),$$

where  $j = 3, 5, 7, 9, 11, \dots, q.$  (7)

The SHM-PWM technique can also be applied to converters with more than three levels [26]. Using the SHM-PWM

principle, based on reducing the harmonic amplitudes to a reduced but non-zero value, the system of equations changes to the system of inequalities detailed in (8) and (9). Again, in (9), it is assumed that the angles of all the cells are used to generate a global waveform as in Fig. 3. The whole system of equations can be grouped in the same objective function (4) shown in section III-A.

$$\left|\frac{4V_{dc}}{\pi}M_{a-Cell-n} - H_1\right| \le L_1,$$

where  $n = 1, 2, \dots, N$  (8)

$$|H_j| \le L_j,$$

where  $j = 3, 5, 7, 9, 11, \dots, 49.$  (9)

Several optimization methods such as Tabu Search, Ant Colony or Particle Swarm [27] can be used to optimize the system. As in previous work, in this paper, the well known Simulated Annealing optimization method [28] has been chosen because it can be adapted very easily to problems with many different constraints. In any case, it has to be noted that since the solutions are calculated only once and then are stored in lookup tables for use with the power converter, the optimization method itself is of little consequence.

## IV. SHM-PWM FOR BALANCING

Under unbalanced conditions it is necessary to use a strategy to adjust the modulation index in order to share the power among all the cells. In [19] a method was presented based on the SHE-PWM technique that could tolerate any imbalance situation by decoupling all of the cells of the converter. This required a single table of solutions which could be applied to each H-Bridge of the converter to independently control the power flow. The disadvantage of this method is that since it does not consider the multilevel waveform of the converter during angle calculation, a lower number of harmonics can be eliminated compared with the use of global multilevel solutions.

In the case of this paper, the global output waveform of the converter is used in order to increase the number of considered harmonics. Consequently, a higher number of harmonics can meet the grid code requirements increasing the quality of the output waveform. In this work, for a given number of switching angles, the amplitude of the fundamental harmonic of each cell is set to the desired value and a certain number of extra harmonics of the global waveform are considered to meet the grid code requirements. In this paper three switching angles have been considered for CHB converters with two and three cells. For the case of two different cells up to four extra harmonics can be considered. When three cells are used up to six extra harmonic components can meet the grid code requirements. Since the number of degrees of freedom is equal to the number of switching angles, in this case the extra flexibility given by the SHM-PWM method is used to find a new set of solutions for different dc-link imbalance conditions close to the previous one.

To obtain the specific switching angles for a certain dclink imbalance situation, a linear interpolation is used among different pre-calculated lookup tables in order to be able to tolerate any imbalance up to a maximum unbalancing range (previously defined and considered when formulating the mathematical equations).

Considering a multi-cell cascaded converter, specific lookup tables can be previously obtained for different unbalancing conditions. When the DC voltages of each cell are normalized, the imbalance of each cell can be referred as an increment or decrement with respect to the theoretical mean value. In the rest of the paper the following nomenclature will be used to define the conditions of each lookup table (LUT):  $(X_1, X_2, ..., X_n)$  where  $X_n$  represents the imbalance of cell n, in percent, of the average desired voltage (perfect balanced situation).

For example, considering a two-cell converter with a maximum tolerable imbalance of 3%, two lookup tables, S1(0,0)and S2(-3,3) are required. Interpolation between the elements of these two lookup tables can be used in order to find the required switching angles which achieve the required waveform objectives over this 0 - 3% imbalance range. For higher imbalance conditions, extra LUTS could be added to extend the range. For instance, the range could be extended to tolerate an imbalance of up to 6% using S3(-6,6), or 9% using S4(-9,9) etc. The linear interpolation between the switching angles stored in the two lookup tables can be achieved using the following equation on each element of the two lookup tables:

$$\alpha(i) = A\alpha_{LUT1}(i) + B\alpha_{LUT2}(i) \tag{10}$$

This interpolation method is advantageous when compared to other methods considered in literature as it limits the number of required lookup tables that are needed to achieve the waveforms objectives in the presence of a DC imbalance. For example, using the LUTs described above, for an imbalance of 1% the constants would be A = 1/3 and B = 2/3.

#### A. Extension to three-cell cascaded converters

For a three-cell converter, the imbalance may be shared amongst all of the cells in the converter. For this case, three lookup tables are required as shown in (11), where X represents the percentage imbalance (referred to the average voltage), as previously noted.

$$S1 = (0, 0, 0)$$

$$S2 = (-2X/3, X/3, X/3)$$

$$S3 = (-X/3, -X/3, 2X/3)$$

(11)

Care should be taken with the maximum imbalance which can be tolerated in this case as excessive values of X will inhibit the ability to linearly interpolate between lookup tables (compared to low values of X). Now the final set of angles would be obtained from the three tables. The interpolation constants can be obtained by solving the linear system of equations obtained by forcing the same amplitude in the fundamental harmonics generated by all the cells (this amplitude has been normalized to 1 for simplicity).

$$AV_{1} + B \frac{V_{1}}{(1+2X/3)} + C \frac{V_{1}}{(1+X/3)} = 1$$

$$AV_{2} + B \frac{V_{2}}{(1-X/3)} + C \frac{V_{2}}{(1+X/3)} = 1$$

$$AV_{3} + B \frac{V_{3}}{(1-X/3)} + C \frac{V_{3}}{(1-2X/3)} = 1$$

(12)

The principle of the proposed method is based on exploiting the flexibility given by the SHM-PWM method to obtain a new set of solutions under different dc-link imbalance conditions but from a previous set of solutions in such a way that the switching angles are very similar. This leads with a very small variation form one table to the other allowing the use of linear interpolation between both tables to obtain all the unbalancing conditions not directly stored in the LUTs. The angles obtained from such similar sets of solutions should share the same characteristics in terms of power flow control and output spectrum. We are assuming that the amplitude of each harmonic component corresponds to the linear interpolating of the corresponding amplitudes of each set of solutions (based on the linear property of the Discrete Fourier Transform). It should be noted that the linear system of equations can be solved offline and the solution computed by a DSP on demand.

The next sections show some examples for both two and three-cell CHB converters.

#### V. SIMULATION RESULTS

This section presents the simulation results that have been obtained using the SHM-PWM technique in a two and a three-cell CHB converter. In order to obtain solutions which could be easily implemented in a real converter, real power semiconductors have been considered. A minimum margin of 0.01 radians between two consecutive switching angles has been taken into account as a valid safe margin. In the computing process the limits specified in the EN 50160 [29]and CIGRE WG 36-05 [30] grid codes have been considered but any other could have been chosen. These standards include specific limits for each harmonic up to  $49^{th}$  harmonic the waveform THD calculated up to  $40^{th}$  harmonic. Table I shows the harmonic limits specified in these standards.

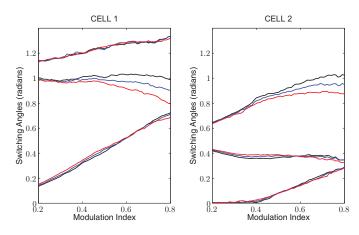

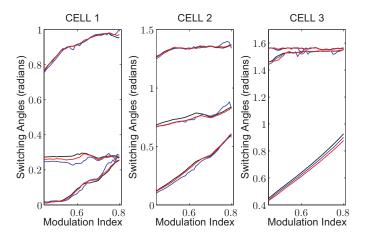

Fig. 4 shows the switching angles for a two-cell topology and a switching frequency of 150Hz per H-Bridge. Four extra harmonics are considered in the global waveform and a maximum imbalance of 10% has been considered in the computing process.

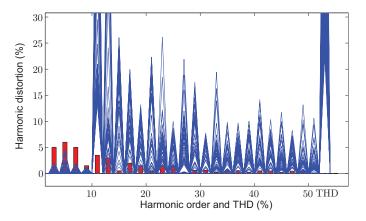

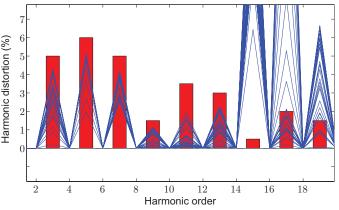

In Fig. 5 the harmonic content obtained for an imbalance of 3% for the complete modulation index range from 0.2 to 0.8 in steps of 0.01 can be observed. It can be seen that in all the cases the lowest harmonics are fulfilling the grid code. The bars on this figure represent the limits specified in the grid code. The triangular waveforms show the amplitude of the corresponding harmonic component for each value of  $M_a$

| Odd       | non-triplen | Odd t | riplen  | Even      |         |  |

|-----------|-------------|-------|---------|-----------|---------|--|

| harmonics |             | harm  | onics   | Harmonics |         |  |

| Order     | Limit       | Order | Limit   | Order     | Limit   |  |

| (n)       | $(L_i)$     | (n)   | $(L_i)$ | (n)       | $(L_i)$ |  |

| 5         | 6%          | 3     | 5%      | 2         | 2%      |  |

| 7         | 5%          | 9     | 1.5%    | 4         | 1%      |  |

| 11        | 3.5%        | 15    | 0.5%    | 610       | 0.5%    |  |

| 13        | 3%          | 21    | 0.5%    | >10       | 0.2%    |  |

| 17        | 2%          | >21   | 0.2%    |           |         |  |

| 19        | 1.5%        |       |         |           |         |  |

| 23        | 1.5%        |       |         |           |         |  |

| 25        | 1.5%        |       |         |           |         |  |

| >25       | 0.2+32.5/n  |       |         |           |         |  |

Fig. 4. SHM-PWM switching angles for the case of two cells and three angles per cell in the  $M_a$  range from 0.20 to 0.80 for a balanced situation (black), an imbalance of 5% (blue) and an imbalance of 10% (red).

Fig. 5. Global Harmonic content and THD (on the right) generated by the converter for each modulation index value for a (-3,3) imbalance and  $0.20 < M_a < 0.80$  (more detailed in Fig. 6).

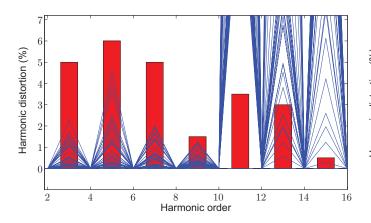

in the whole range. A detailed plot showing the lowest order harmonics is presented in Fig. 6. The maximum theoretical imbalance level achieved with this method is below 0.1% for all the values of the modulation index from 0.2 to 0.8 and all the conditions of imbalance from 0% to 5%.

Fig. 6. Detail of the low order harmonic amplitudes generated by the converter for each value of the modulation index for a (-3,3) imbalance and  $0.20 < M_a < 0.80$ .

Fig. 7. Switching angles for a set of imbalance conditions of (0,0,0) in black, (-2,-2,4) in red and (-4,2,2) in blue.

## A. Three-cell Converters

This section presents simulation results obtained using a three-cell converter.

Fig. 7 shows the switching angles corresponding to a set of imbalance conditions of (0,0,0), (-2,-2,4) and (-4,2,2) for the three cells.

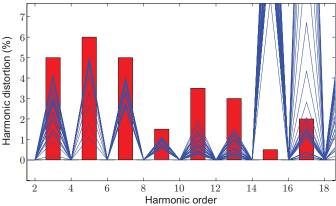

Fig. 8 presents the spectrum obtained for an imbalance of (-1.2,1,1.5) for the range  $0.44 < M_a < 0.80$ . It can be observed that for all the values of  $M_a$  the lower harmonic components are below the limits specified in the grid code.

Using the same set of angles but for an imbalance of (-2.5,1,3) produces the output spectrum presented in Fig. 9. The low order harmonics are meeting the grid code. Again, for three-cell converters, the simulation results obtained using the presented switching angles give very low theoretical final imbalance for all the conditions considered in the computing process.

It must be noted that this strategy can be very useful to tolerate low unbalancing conditions because a high number of harmonics can be controlled using a low number of switching angles. Using a three-cell topology and three angles per cell it is possible to set the amplitude of the fundamental component and to control up to six undesirable harmonic components. In

Fig. 8. Output spectrum for an imbalance of (-1.2,1,1.5) and  $0.44 < M_a < 0.80.$

Fig. 9. Output spectrum for an imbalance of (-2.5,1,3) and  $0.44 < M_a < 0.80.$

comparison with the decoupled technique presented in [19] a higher number of harmonics can be controlled using a lower number of switching angles. This technique could however be used in conjunction with the decoupled technique presented in [19] for use in systems which may present higher imbalance situations.

# VI. EXPERIMENTAL RESULTS

## A. Description of the converter

The methods presented have been experimentally supported using a single phase, five-level cascaded H-Bridge converter and three switching angles per cell. This converter is configured as an inverter feeding an RL load ( $R = 360\Omega$  and L = 15mH). The H-Bridges are constructed using Semikron SK60GB128 modules. The DC link for each H-Bridge is fed from a separate DC voltage supply with a maximum output of 300V which is adjusted to obtain the desired imbalance for an average value of 200V. The total imbalance range from 0% to 10% in steps of 1% has been studied for the particular case of  $M_a = 0.70$ .

# B. Results

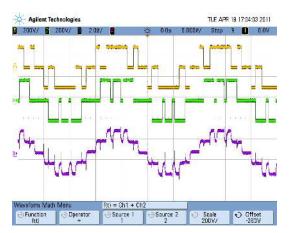

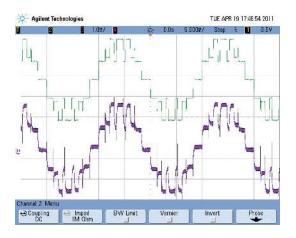

All the experimental data have been captured using a digital oscilloscope and post processed using Matlab. Fig. 10 shows

Fig. 10. Voltage of both cells and current(bottom) for an imbalance of 0%. The scales are 200V/div, 0.5A/div and 5ms/div.

Fig. 11. Global output waveform and current(bottom) for an imbalance of 10%. The scales are 100V/div, 0.25A/div and 5ms/div.

the voltages of both cells and the output current of the converter for a balanced situation. Fig. 11 shows the global output voltage and the current for an imbalance of 10%. Due to the limited availability of loads in the laboratory the currents have an important harmonic content similar to the voltage waveforms. Using a more practical load the harmonic content would be reduced.

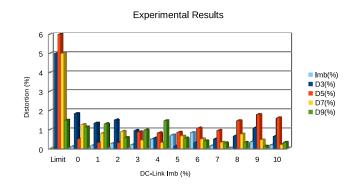

Table II shows a comparison between the theoretical values and the experimental results of the real balance obtained in the converter and the distortion levels of the global output under different imbalance conditions. From left to right the table shows the forced DC-Link imbalance, the amplitude of the fundamental harmonic of the global waveform, the different distortion levels of the global output and the final  $H_1$ imbalance between both cells obtained using the method for both the theoretical and the experimental results. The effects of using real switching devices and drivers generate the small differences shown in the table. It can be observed that in all the cases the real balance achieved by the method is always below 1% which is a very good result considering the very low switching frequency that is being used. It must be also noted that the corresponding limits of the grid code for all the considered harmonics (up to  $9^{th}$ ) are always met in the global output of the converter. Fig. 12 shows the experimental results

Fig. 12. Experimental results obtained using SHM-PWM for  $M_a=0.7$  and two cells. The DC-Link imbalance range is from 0% to 10% in steps of 1%.

presented in the table and the grid code limits.

## VII. CONCLUSION

This paper presents a new control strategy, based on the SHM-PWM technique, that can tolerate different capacitor voltage levels for Cascaded H-Bridge Multilevel Converters. In comparison with other techniques, in this case it is possible to control the amplitude of each cell under balanced or unbalanced conditions with a reduced number of lookup tables whilst still producing very high quality waveforms at low switching frequency. An example of an applications which may benefit from such a scheme is in a multilevel UPS. In this case the technique could be able to meet grid voltage standards even when the batteries are charged to different voltages.

Different simulation results for two and three-cell converters have been included to show the viability of the technique. Experimental results supporting the method in a two-cell converter validating the technique for an imbalance range from 0% to 10% have been included.

#### REFERENCES

- [1] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L.G. Franquelo, B. Wu, J. Rodriguez, M.A. Perez, and J.I. Leon. Recent advances and industrial applications of multilevel converters. *Industrial Electronics*, *IEEE Transactions on*, 57(8):2553–2580, 2010.

- [2] J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. Leon, R. C. Portillo, M. A. M. Prats, and M. A. Perez. Multilevel converters: An enabling technology for high-power applications. *Proceedings of the IEEE*, 97(11):1786–1817, November 2009.

- [3] H. Akagi, S. Inoue, and T. Yoshii. Control and performance of a transformerless cascade PWM STATCOM with star configuration. *IEEE Transactions on Industry Applications*, 43(4):1041–1049, July/August 2007.

- [4] E. Villanueva, P. Correa, J. Rodriguez, and M. Pacas. Control of a single-phase cascaded h-bridge multilevel inverter for grid-connected photovoltaic systems. *IEEE Transactions on Industrial Electronics*, 56(11), November 2009.

- [5] P. Cortes, A. Wilson, S. Kouro, J. Rodriguez, and H. Abu-Rub. Model predictive control of multilevel cascaded h-bridge inverters. *Industrial Electronics, IEEE Transactions on*, 57(8):2691–2699, 2010.

- [6] S. Vazquez, J.I. Leon, J.M. Carrasco, L.G. Franquelo, E. Galvan, M. Reyes, J.A. Sanchez, and E. Dominguez. Analysis of the power balance in the cells of a multilevel cascaded h-bridge converter. *Industrial Electronics, IEEE Transactions on*, 57(7):2287–2296, 2010.

- [7] J.I. Leon, S. Kouro, S. Vazquez, R. Portillo, L.G. Franquelo, J.M. Carrasco, and J. Rodriguez. Multidimensional modulation technique for cascaded multilevel converters. *Industrial Electronics, IEEE Transactions on*, 58(2):412–420, 2011.

TABLE II THEORETICAL AND EXPERIMENTAL RESULTS OBTAINED USING SHM-PWM AND TWO CELLS FOR  $M_a = 0.7$ .

| Imb. | Theoretical |       |       |       |       |        | Experimental |        |       |       |       |       |        |      |

|------|-------------|-------|-------|-------|-------|--------|--------------|--------|-------|-------|-------|-------|--------|------|

| (%)  | H1(V)       | D3(%) | D5(%) | D7(%) | D9(%) | THD(%) | l(%)         | H1(V)  | D3(%) | D5(%) | D7(%) | D9(%) | THD(%) | l(%) |

| 0    | 356.55      | 1.45  | 0.23  | 0.63  | 0.66  | 27.40  | 0.00         | 348.08 | 1.86  | 0.52  | 1.27  | 1.15  | 27.51  | 0.13 |

| 1    | 356.59      | 1.11  | 0.07  | 0.50  | 0.63  | 27.31  | 0.03         | 347.92 | 1.36  | 0.32  | 0.82  | 1.32  | 27.41  | 0.18 |

| 2    | 356.69      | 0.80  | 0.13  | 0.34  | 0.56  | 27.22  | 0.05         | 346.49 | 1.52  | 0.32  | 0.91  | 0.60  | 27.68  | 0.29 |

| 3    | 356.58      | 0.49  | 0.30  | 0.25  | 0.41  | 27.20  | 0.03         | 346.92 | 0.97  | 0.89  | 0.46  | 0.99  | 27.58  | 0.22 |

| 4    | 356.56      | 0.22  | 0.51  | 0.18  | 0.22  | 27.17  | 0.04         | 350.01 | 0.59  | 0.84  | 0.33  | 1.48  | 26.93  | 0.52 |

| 5    | 356.52      | 0.05  | 0.76  | 0.09  | 0.04  | 27.18  | 0.00         | 348.72 | 0.15  | 0.87  | 0.68  | 0.56  | 27.23  | 0.72 |

| 6    | 356.59      | 0.28  | 0.89  | 0.00  | 0.09  | 27.08  | 0.06         | 348.16 | 0.33  | 1.09  | 0.52  | 0.42  | 27.39  | 0.85 |

| 7    | 356.59      | 0.49  | 1.09  | 0.06  | 0.11  | 27.03  | 0.06         | 345.84 | 0.52  | 0.96  | 0.34  | 0.31  | 27.46  | 0.17 |

| 8    | 356.58      | 0.65  | 1.31  | 0.06  | 0.00  | 27.03  | 0.04         | 346.91 | 0.68  | 1.48  | 0.78  | 0.34  | 27.21  | 0.04 |

| 9    | 356.51      | 0.78  | 1.54  | 0.05  | 0.15  | 27.09  | 0.02         | 347.88 | 1.11  | 1.81  | 0.48  | 0.14  | 27.53  | 0.37 |

| 10   | 356.43      | 0.88  | 1.77  | 0.08  | 0.41  | 27.20  | 0.02         | 345.85 | 0.66  | 1.63  | 0.22  | 0.34  | 27.43  | 0.20 |

- [8] F. Khoucha, S. M. Lagoun, K. Marouani, A. Kheloui, and M. El Hachemi Benbouzid. Hybrid cascaded h-bridge multilevel-inverter induction-motor-drive direct torque control for automotive applications. *IEEE Transactions on Industrial Electronics*, 57(3):892–899, March 2010.

- [9] W. Song and A.Q. Huang. Fault-tolerant design and control strategy for cascaded h-bridge multilevel converter-based statcom. *Industrial Electronics, IEEE Transactions on*, 57(8):2700–2708, 2010.

- [10] A.I. Bratcu, I. Munteanu, S. Bacha, D. Picault, and B. Raison. Cascaded dc–dc converter photovoltaic systems: Power optimization issues. *Industrial Electronics, IEEE Transactions on*, 58(2):403–411, 2011.

- [11] Hasmukh S. Patel and Richard G. Hoft. Generalized techniques of harmonic elimination and voltage control in thyristor inverters: Part i harmonic elimination. *IEEE Transactions on Industry Applications*, 9(3):310–317, May 1973.

- [12] Hasmukh S. Patel and Richard G. Hoft. Generalized techniques of harmonic elimination and voltage control in thyristor inverters: Part II voltage control techniques. *IEEE Transactions on Industry Applications*, 10(5):666–673, September 1974.

- [13] L. G. Franquelo, J. Napoles, R. C. P. Guisado, J. I. Leon, and M. A. Aguirre. A flexible selective harmonic mitigation technique to meet grid codes in three-level PWM converters. *IEEE Transactions on Industrial Electronics*, 54(6):3022–3029, December 2007.

- [14] A. Mehrizi-Sani and S. Filizadeh. An optimized space vector modulation sequence for improved harmonic performance. *IEEE Transactions on Industrial Electronics*, 56(8), August 2009.

- [15] Na He, Dianguo Xu, and L. Huang. The application of particle swarm optimization to passive and hybrid active power filter design. *IEEE Transactions on Industrial Electronics*, 56(8):2841–2851, August 2009.

- [16] L. M. Tolbert, J. N. Chiasson, Zhong Du, and K. J. McKenzie. Elimination of harmonics in a multilevel converter with nonequal DC sources. *IEEE Transactions on Industry Applications*, 41(1):75–82, January/February 2005.

- [17] H. Taghizadeh and M. Tarafdar Hagh. Harmonic elimination of multilevel inverters using particle swarm optimization. In *Industrial Electronics*, 2008. ISIE 2008. IEEE International Symposium on, pages 393–396, Cambridge, June/July 2008.

- [18] M. S. A. Dahidah and V. G. Agelidis. Selective harmonic elimination PWM control for cascaded multilevel voltage source converters: A generalized formula. *IEEE Transactions on Power Electronics*, 23(4):1620– 1630, July 2008.

- [19] A. J. Watson, P. W. Wheeler, and J. C. Clare. A complete harmonic elimination approach to DC link voltage balancing for a cascaded multilevel rectifier. *IEEE Transactions on Industrial Electronics*, 54(6):2946–2953, December 2007.

- [20] C. Rech and J.R. Pinheiro. Hybrid multilevel converters: Unified analysis and design considerations. *Industrial Electronics, IEEE Transactions on*, 54(2):1092 –1104, april 2007.

- [21] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats. The age of multilevel converters arrives. *IEEE Industrial Electronics Magazine*, 2(2):28–39, June 2008.

- [22] D. Ahmadi and Jin Wang. Selective harmonic elimination for multilevel inverters with unbalanced dc inputs. In *Vehicle Power and Propulsion Conference, 2009. VPPC '09. IEEE*, pages 773 –778, sept. 2009.

- [23] J. Vassallo, J. C. Clare, and P. W. Wheeler. A utility connected multi cellular converter with optimised harmonic performance and equalization of cell powers. In *Proc. 11th Int. Conf. EPE PEMC*, 2004., 2004.

- [24] Stefano Bifaretti, Pericle Zanchetta, Mihai Ciobotaru, Florin Iov, and Jon C. Clare. Power flow control through the uniflex-pm under different network conditions. *E P E Journal*, 19(4), 2009.

- [25] Zhong Du, L. M. Tolbert, J. N. Chiasson, and B. Ozpineci. Reduced switching-frequency active harmonic elimination for multilevel converters. *IEEE Transactions on Industrial Electronics*, 55(4):1761–1770, April 2008.

- [26] J. Napoles, J. I. Leon, L. G. Franquelo, R. C. P. Guisado, and M. A. Aguirre. Selective harmonic mitigation technique for multilevel cascaded h-bridge converters. In *Industrial Electronics*, 2009. *IECON 2009. 35th Annual Conference of IEEE*, Oporto, November 2009.

- [27] K. Sundareswaran, K. Jayant, and T. N. Shanavas. Inverter harmonic elimination through a colony of continuously exploring ants. *IEEE Transactions on Industrial Electronics*, 54(5):2558–2565, October 2007.

- [28] S. C. Kirkpatrick S., Gelart and M. P. Vecchi. Optimization by simulated annealing. *Science*, 220(4598):671–680, May 1983.

- [29] CENELEC EN 50160. Voltage characteristics of electricity supplied by public distribution systems. Wiley IEEE Press, 2001.

- [30] CIGRE WG 36-05. Harmonics, characteristic parameters, methods of study, estimates of existing values in the network. Electra no.77, 1981.

**Javier Napoles** (S'07, M'10) was born in Seville in 1978. He received the B.S. and M.S. and PhD degrees in telecommunications engineering from the University of Seville (US), Spain, in 2005, 2008 and 2010 respectively. In 2005, he joined to the Department of Electronic Engineering, Seville University, working on R+D projects. His interests include the development of techniques and algorithms to improve the energy quality from utility grid specially focused to harmonic content implemented on FPGA.

Alan J. Watson received the Masters and PhD degrees in Electronic Engineering and Electrical and Electronic Engineering from the University of Nottingham, UK in 2004 and 2008 respectively.

He is currently a Research Fellow in the Power Electronics, Machines and Control Group at the University of Nottingham, UK, and is a Member of the IET and the IEEE. His research interests include high power and high voltage converters, advanced modulation schemes and power converter control.

**Patrick W. Wheeler** (M'00) received his BEng [hons] in 1990 from the University of Bristol, UK. He received his PhD degree in Electrical Engineering for his work on Matrix Converters from the University of Bristol, UK, in 1994. In 1993 he moved to the University of Nottingham and worked as a research assistant in the Department of Electrical and Electronic Engineering. In 1996 he became a Lecturer in the Power Electronics, Machines and Control Group at the University of Nottingham, UK. Since January 2008 he has been a Full Professor in

the same research group.

His research interests are are in power conversion, Energy and More Electric Aircraft technology. He has published over 250 papers in leading international conferences and journals.

**Jose J. Padilla** was born in Cordoba, Spain, in 1983. He received the B.S. degree in industrial electronics engineering from the University of Cordoba in 2004. In 2007, he joined the Power Electronics Group, University of Seville, where he was involved in R&D projects and where, in 2011, he worked as project manager.

He is currently a system engineer within the automotive division in Infineon A.G., Germany. Areas of interest are: power electronics systems, hybrid and electric vehicle's powertrain, on-board and fast

chargers and electric and electronic design and control hardware for automotive power converters.

Electronics Magazine.

**Jose I. Leon** (S'04, M'07) was born in Cádiz, Spain, in 1976. He received the B.S. and M.S. and PhD degrees in telecommunications engineering from the University of Seville (US), Spain, in 1999, 2001 and 2006 respectively.

Currently, he is an Associate Professor with the Department of Electronic Engineering, US. His research interests include electronic power systems, modulation and control of power converters and industrial drives. He was recipient as co-author of the 2008 Best Paper Award of the IEEE Industrial

**Leopoldo G. Franquelo** (M'84, SM'96, F'05) received the M.Sc. and Ph.D. degrees in electrical engineering from the University of Seville, Spain, in 1977 and 1980, respectively. He was the Head of the Electronics Engineering Department (1998-2005). He is currently a full professor and head of the Power Electronics Group with the University of Seville. He was the vice president of the IES Spanish Chapter (2002-03) and a member at large of the IES Administrative Committee (2002-03). He was the vice president for conferences (2004-07), in

which he has also been a Distinguished Lecturer since 2006. He has been an associate editor for IEEE Transactions on Industrial Electronics since 2007. He has been the president of IES (2010-11). He is author of more than 60 publications in international journals and over 200 papers in international conference proceedings. He is the holder of ten patents and participated in more than 100 R&D projects.

His current research interests include modulation techniques for multilevel inverters and its application to power electronic systems for renewable energy systems.

Miguel A. Aguirre (M'97) was born in Madrid, Spain in 1963. He obtained the Master degree in 1991, in Electrical and Electronic Engineering by the University of Sevilla, Spain. He obtained the PhD degree in 1994 in the same University. He is currently teaching digital microelectronics in the Electronic Engineering Department of the University of Sevilla, as Assistant Professor. He is the author of more than 10 publications in the IEEE. He made his thesis in algorithm and heuristics for placement and routing integrated, and currently he is working

in tools for dependable design of integrated circuits.